# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

| (51) 。Int. Cl. <sup>7</sup><br>G09G 3/36 |                                               | (45) 공고일자<br>(11) 등록번호<br>(24) 등록일자 | 2005년10월18일<br>10-0522093<br>2005년10월10일 |  |

|------------------------------------------|-----------------------------------------------|-------------------------------------|------------------------------------------|--|

| (21) 출원번호<br>(22) 출원일자                   | 10-2003-0090764<br>2003년12월12일                | (65) 공개번호<br>(43) 공개일자              | 10-2004-0052194<br>2004년06월22일           |  |

| (30) 우선권주장                               | JP-P-2002-00363037 2002년12월13일 일본(JP)         |                                     |                                          |  |

| (73) 특허권자                                | 샤프 가부시키가이샤<br>일본 오사까후 오사까시 아베노꾸 나가이께쪼 22방 22고 |                                     |                                          |  |

| (72) 발명자                                 | 와시오하지메<br>일본나라633-0061사쿠라이시카미노소6-6            |                                     |                                          |  |

|                                          | 마에다카즈히로<br>일본나라630-8424나라시후루이치초2339-1-에이203   |                                     |                                          |  |

|                                          | 온다마모루<br>일본나라632-0004텐리시이치노모토초2613-1-1033     |                                     |                                          |  |

| (74) 대리인                                 | 백덕열<br>이태희                                    |                                     |                                          |  |

| 심사관 : 정병락                                |                                               |                                     |                                          |  |

# (54) 표시장치

요약

구동회로에 서로 관계가 있는 복수의 신호가 입력되고, 그 중 적어도 하나의 신호가 다른 회로에도 인회되어 공통으로 입력되는 구성에 있어서, 관계가 있는 신호 사이의 배선부하의 차이에 의한 위상 관계의 어긋남을, 소비전력 상승을 초래하는 신호 자체에 가공을 행하지 않고 억제한다. 제1 및 제2 클록신호가 제1 데이터 신호선 구동회로에 입력된다. 그 중 제1 클록신호는 공통으로 제2 데이터 신호선 구동회로에도 입력되어 있다. 배선(1)과 배선(2) 사이의 인회의 차이에 의한 배선부하를 이퀄라이징(equalizing)시켜야 하여, 배선(2)에는 더미 배선이 제공되어 있고, 더미 배선과 액정층과 대향 전극에의해 부가용량부가 형성되어 있다.

#### 대표도

도 1

#### 명세서

도면의 간단한 설명

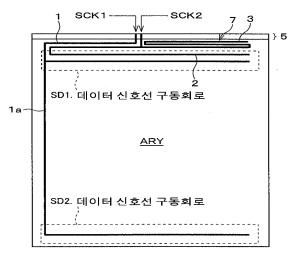

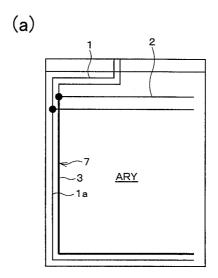

도1은, 본 발명의 일 실시예를 나타내는 것으로, 더미 배선이 제공된 액정표시장치의 배선 주요부를 개략적으로 도시하는 평면도이다.

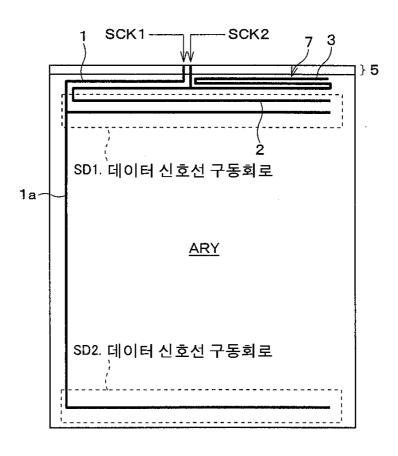

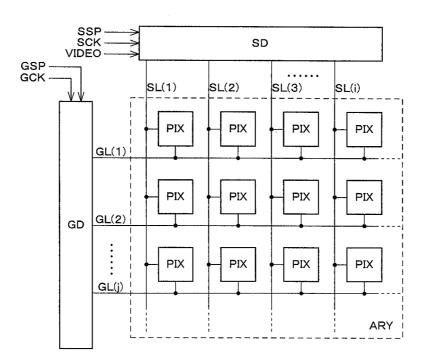

도2는, 상기 액정표시장치의 구성의 개략을 도시하는 블록도이다.

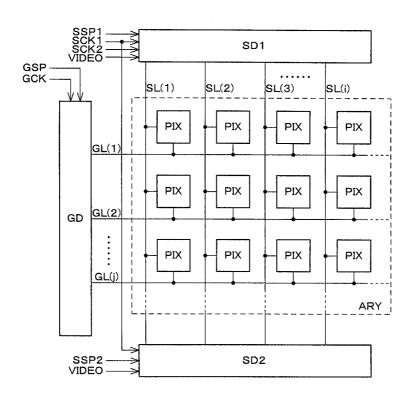

도3은, 상기 액정표시장치에서의 화소의 구성을 도시하는 등가 회로도이다.

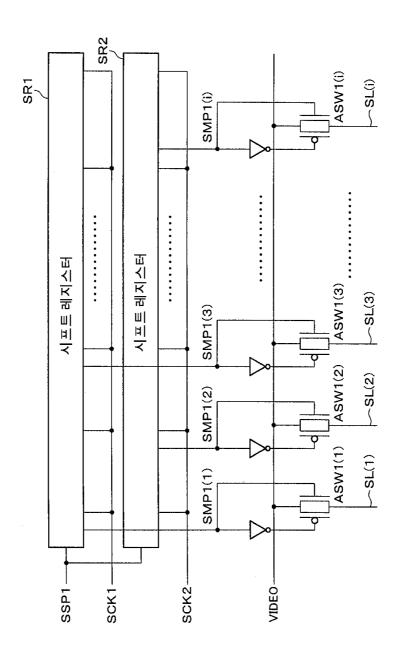

도4는, 상기 액정표시장치에서의 제1 데이터 신호선 구동회로의 일 구성예를 도시하는 회로 블록도이다.

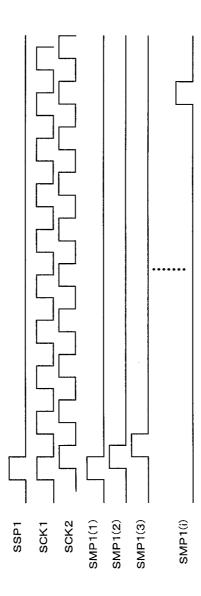

도5는, 도4의 제1 데이터 신호선 구동회로에 관계되는 각 신호의 타이밍챠트이다.

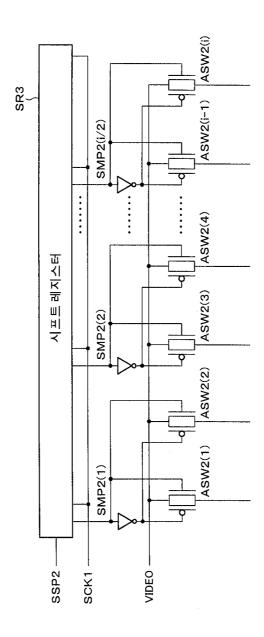

도6은, 상기 액정표시장치에서의 제2 데이터 신호선 구동회로의 일 구성예를 도시하는 회로 블록도이다.

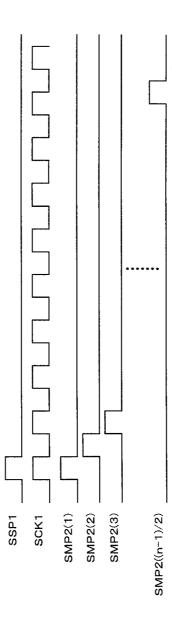

도7은, 도6의 제2 데이터 신호선 구동회로에 관계되는 각 신호의 타이밍챠트이다.

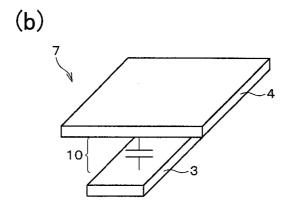

도8a는, 더미 배선의 일례를 확대하여 도시하는 도면이다.

도8b는, 배선부하 조정수단을 구성하는 용량부의 구성을 도시하는 도면이다.

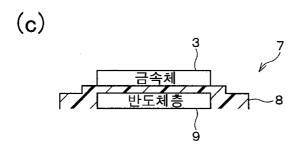

도8c는, 박막트랜지스터의 반도체층을 사용하여 구성되는 배선부하 조정수단을 도시하는 도면이다.

도9a는, 더미 배선을 형성하여 배선부하 조정수단을 구성하는 용량을 제공하는 위치의 예를 도시하는 평면도이다.

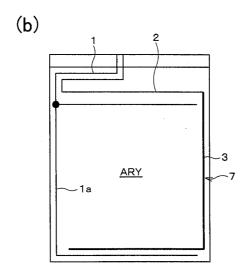

도9b는, 더미 배선을 형성하여 배선부하 조정수단을 구성하는 용량을 제공하는 위치의 예를 도시하는 평면도이다.

도10은, 종래의 일반적인 액정표시장치의 구성의 개략을 도시하는 블록도이다.

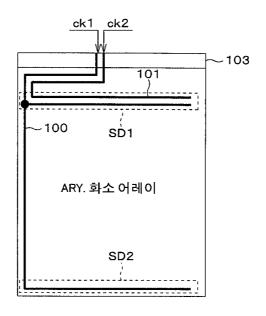

도11은, 데이터 신호선 구동회로를 2개 구비한 액정표시장치에 있어서, 2개의 데이터 신호선 구동회로 사이에서 하나의 클록신호 ck1·ck2를 공통으로 입력시키고 있는 구성을 도시하는 평면도이다.

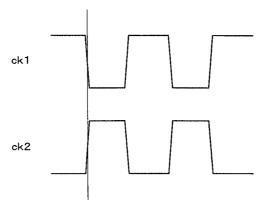

도12는, 상기 2개의 데이터 신호선 구동회로에 입력되는 클록신호 ck1·ck2의 파형도이다.

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 액티브 매트릭스형의 액정표시장치 등에 적합한, 복수의 주사신호선을 구동하는 주사신호선 구동회로와, 상기 주사신호선에 교차하도록 배치된 복수의 데이터 신호선을 구동하는 데이터 신호선 구동회로를 구비한 표시장치에 관한 것이다.

종래, 표시장치의 하나로서, 액티브 매트릭스 구동 방식의 액정표시장치가 알려져 있다. 또, 본 명세서에서는, 본 발명의 대상 기술인 표시장치 예로서, 액정표시장치에 대해 설명하지만, 본 발명은 이에 한정되지 않고, 다른 표시장치에 대해서도 유효한 것이다.

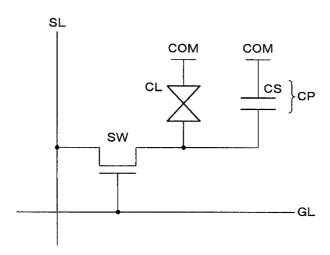

액티브 매트릭스형의 액정표시장치는, 도10에 도시된 바와 같이, 화소 어레이 ARY와, 주사신호선 구동회로 GD와, 데이터 신호선 구동회로 SD를 구비하고 있다.

화소 어레이 ARY는, 서로 교차하는 복수의 주사신호선  $GL(1) \sim GL(j)$  및 데이터 신호선  $SL(1) \sim SL(i)$ 를 구비하고 있고, 인접하는 2개의 주사신호선  $GL \cdot GL(0)$ 하, 총칭할 때 및 임의의 것을 가리킬 때, 참조 부호 GL로 한다)과, 인접하는 2개의 데이터 신호선  $SL \cdot SL(0)$ 하, 총칭할 때 및 임의의 것을 가리킬 때, 참조 부호 SL로 한다)에 의해 구획된 부분마다, 화소 PIX가 하나씩 배치되어 있다. 화소  $PIX \cdot \cdot \cdot$ 는, 매트릭스 형태로 배열되어 있다.

데이터 신호선 구동회로 SD는, 주로 시프트 레지스터와 샘플링 회로로 이루어지고, 도시되지 않은 외부 회로로부터, 영 상신호 VIDEO와 함께, 제어신호로서의 스타트 펄스신호 SSP 및 클록신호 SCK가 입력되게 되어 있다. 데이터 신호선 구 동회로 SD는, 스타트 펄스신호 SSP의 펄스가 입력되면, 클록신호 SCK의 타이밍 신호에 동기하여, 입력된 영상신호 VIDEO를 샘플링하고, 필요에 따라 증폭하여, 데이터 신호선 SL(1)~SL(i)에 기입한다.

주사신호선 구동회로 GD는, 주로 시프트 레지스터로 이루어지고, 도시되지 않은 외부 회로로부터, 제어신호로서의 스타트 필스신호 GSP 및 클록신호 GCK가 입력되게 되어 있다. 주사신호선 구동회로 GD는, 스타트 필스신호 GSP의 필스가 입력되면, 클록신호 GCK의 타이밍 신호에 동기하여, 주사신호선 GL(1)~GL(j)를 순차적으로 선택하여 구동한다. 이에 의해, 화소 PIX내에 있는 후술하는 스위칭 소자의 개폐가 제어되어, 데이터 신호선 SL에 기입된 영상신호(데이터)를 화소 PIX에 기입하는 동시에, 화소 PIX에 기입된 데이터는 유지된다.

그리고, 본원 출원인은, 이와 같은 표시장치에 있어서, 상기 데이터 신호선 구동회로 SD 및 주사신호선 구동회로 GD 중 적어도 일방의 구동회로를, 복수의 구동회로로 구성하고, 화소 어레이에 대해 복수의 구동회로를, 서로 독립적으로 또는 연동하여 구동하는 것을 제안하고 있다(예컨대, 일본국 공개특허공보 제2002-32048호(2002년 1월 31일 공개)(미국 공 개공보인 NO.US2002/0075249A1에 대응) 참조).

이에 있어서는, 입력되는 영상의 종류나 사용 환경에 따라, 화소 어레이를 구동하는 구동회로를 적절히 절환함으로써, 최적의 표시 포맷에서의 표시가 가능하게 되고, 또한 저소비전력화를 도모할 수도 있다.

예컨대, 흑백 표시와 컬러 표시를 하나의 표시장치에 의해 실현함에 있어서, 흑백 데이터를 컬러 표시용의 구동회로로 처리함으로써, 흑백 표시를 행하는 것은 가능하다. 그렇지만, 흑백 표시인 것에 컬러 표시와 동등한 전력이 구동회로에서 소비되는 결과, 흑백 표시를 행하는 데 있어서의 메리트가 없어지게 된다. 그래서, 구동회로를 복수개로 하는 구성을 채용하고, 흑백 표시용의 구동회로를 컬러 표시용의 구동회로와는 별도로 탑재시킴으로써, 흑백 표시에 알맞는 소비전력으로 억제할 수 있다.

또한, 복수의 구동회로를 사용하여 시간차를 두고 데이터 신호선에 영상신호를 기입함으로써, 화상의 오버라이트를 행할 수 있기 때문에, 영상신호를 외부에서 신호처리하지 않고, 슈퍼임포즈 표시가 가능하게 된다.

상기한 바와 같이, 본원 출원인은, 데이터 신호선 구동회로, 또는 주사신호선 구동회로를, 서로 독립적으로 또는 연동하여 구동하는 복수개의 구성으로 하는 것을 이미 제안하고 있다.

그런데, 이와 같은 구성에서는, 예컨대, 복수개 구비된 것 중 임의의 구동회로에는, 2계통의 클록신호가 사용되는 것에 대해, 다른 구동회로에는, 그 중 1계통의 클록신호만이 사용되는 구성이 고려된다.

보다 구체적으로 설명하면, 예컨대, 데이터 신호선의 양측에 2개의 데이터 신호선 구동회로가, 데이터 신호선을 통해 서로가 접속되도록 제공되어 있는 구성이 있고, 이에 있어서, 일방의 데이터 신호선 구동회로는, 시프트 레지스터를 2계열구비하고 있고, 개개의 시프트 레지스터에 대응하여 2계통의 클록신호를 사용하는 것에 대해, 다른 일방의 데이터 신호선구동회로는, 시프트 레지스터를 1계열만 구비하고 있고, 2계통의 클록신호 중 일방밖에 사용하지 않는 구성이다.

이와 같은 경우, 외부 인터페이스의 구조의 간략화때문에, 2개의 데이터 신호선 구동회로에서 공용되는 클록신호는, 2개의 데이터 신호선 구동회로에 공통으로 입력되는 것으로 되지만, 여기에서 2계통의 클록신호를 사용하는 데이터 신호선 구동회로에 있어서는, 영상신호의 샘플링 타이밍이 어긋나게 되어, 화면 품위가 저하된다고 하는 문제가 일어난다.

이는, 2계통의 클록신호를 공급하는 배선의 인회(引回)의 차이에 의한, 배선부하의 차이에 기인한다. 즉, 도11에 도시된 바와 같이, 신호 입력부(103) 측에 제공된 제1 데이터 신호선 구동회로 SD1과 함께, 신호 입력부(103) 측과는 반대측의 단(端) 근처에 배열된 제2 데이터 신호선 구동회로 SD2에도 공통으로 입력되는 제1 클록신호 ck1의 배선(100)은, 제1 데이터 신호선 구동회로 SD1에만 입력되는 제2 클록신호 ck2의 배선(101)보다, 배선 길이가 길어진다. 그 때문에, 당연히 배선부하가 커져, 배선(100)과 배선(101)에서는 배선부하가 상이하게 된다.

이와 같이 배선부하가 상이한 배선(100·101)에, 예컨대, 도12에 도시된 바와 같이, 서로 역상의 관계에 있는 제1 및 제2의 각 클록신호 ck1·ck2를 입력하면, 배선부하가 큰 배선(100)에서 공급되는 제1 클록신호 ck1이, 제2 클록신호 ck2보다

지연된다. 그 결과, 예컨대 신호입력측(103)으로부터 거의 같은 거리 위치이더라도, 배선(100)에서 공급되는 제1 클록신호 ck1과, 배선(101)에서 공급되는 제2 클록신호 ck2에서는, 위상 관계가 어긋나게 된다. 데이터 신호선 구동회로 SD1의 경우, 이와 같은 클록신호 사이의 위상 어긋남은, 영상신호의 샘플링 타이밍의 어긋남으로서 나타난다.

한편, 배선(100)과 배선(101)의 배선부하의 차이에서 발생하는, 제1 및 제2 클록신호 ck1·ck2 사이의 상기한 위상차를 고려하여, 제1 및 제2 클록신호 ck1·ck2를 작성하는 외부 회로에서, 각 클록신호 ck1·ck2를 상기 위상차를 해소할 수 있도록 사전에 보정하여 놓는 것도 고려된다.

그렇지만, 예컨대, 그 보정치가 25ns의 시간이라고 하면, 외부회로의 원(源) 클록(시스템 클록)으로서는, 20Mhz 이상인 것이 필요하게 되어, 소비전력을 증가시킨다. 최근, 이와 같은 표시장치는, 모바일 기기의 표시장치에 이용되는 것이 많아, 저소비전력화의 관점때문에, 원 클록은 감소되는 경향이 있다. 따라서, 이와 같은 위상차의 보정을 외부 회로에서 행하는 방법을 채용하는 것은 곤란하다.

또한, 표시장치가 상기한 바와 같은 액정표시장치인 경우, 배선부하는, 상기 배선과, 대향 전극과, 이들의 사이에 협지된 유전체인 액정층으로 구성되는 용량에 의한 경우가 크다. 그 때문에, 액정층에 사용하는 액정 재료나 액정층의 두께에 의해서도 변화하고, 외부 회로에 의해 대응하려면, 표시 패널마다 보정량을 조정할 필요가 있어, 비용 상승은 부정할 수 없다.

#### 발명이 이루고자 하는 기술적 과제

본 발명은, 상기 과제를 감안하여 이루어진 것으로, 그 목적은, 복수 계통의 클록신호 등의 서로 관계가 있는 복수의 신호가 구동회로에 입력되는 경우에 있어서, 외부 인터페이스의 구조의 간략화를 도모해야 하여, 일부는 단독으로 입력되고, 일부는 다른 회로와 공통으로 입력되는, 관계가 있는 복수의 신호 사이에서 상이한 배선의 인회에 의해 입력되었다고 해도, 소비전력을 증가시키지 않고, 인회의 차이에 의한 영향을 받지 않고 양호한 표시를 행할 수 있는 표시장치를 제공하는 것에 있다.

본 발명의 표시장치는, 상기 과제를 해결하기 위해, 주사신호선을 구동하는 주사신호선 구동회로와, 상기 주사신호선에 교차하도록 배치된 데이터 신호선을 구동하는 데이터 신호선 구동회로를 구비하고, 또한 상기 주사신호선 구동회로 또는 데이터 신호선 구동회로의 적어도 일방의 구동회로에, 적어도 제1, 제2 신호가 입력되고, 다른 회로에 제1 신호가 공통으로 입력되도록 구성되어 있고, 상기 구동회로에 입력되는 제2 신호의 배선부하와, 상기 다른 회로에도 공통으로 입력되는 제1 신호의 배선부하를 이퀄라이징시키는 배선부하 조정수단이 제공되어 있는 것을 특징으로 하고 있다.

상기 다른 회로로서는, 상기 주사신호선 또는 데이터 신호선을 구동하는 구동회로 등이 있다. 또한, 상기 제1, 제2 신호로서는, 복수 계통의 클록신호나, 복수의 비트로 구성되는 디지털 영상신호이고, 적어도 2개의 비트군으로 분리되어 있는 디지털 영상신호 등이 있다.

예컨대, 데이터 신호선의 양측에 2개의 데이터 신호선 구동회로가, 데이터 신호선을 통해 서로가 접속되도록 제공되어 있는 구성에 있어서는, 일방의 데이터 신호선 구동회로는 2계통의 클록신호를 사용하고, 다른 일방의 데이터 신호선 구동회로는, 그 중 1계통의 클록신호만을 사용하는 구성이 고려된다.

이와 같은 경우, 외부 인터페이스의 구조의 간략화때문에, 2개의 데이터 신호선 구동회로에서 함께 사용되는 제1 클록신호는, 2개의 데이터 신호선 구동회로에 공통으로 입력되는 것이 많다. 그렇지만, 이와 같이, 2개의 데이터 신호선 구동회로에서 사용되는 제1 클록신호를 공통으로 입력시키면, 제1 클록신호(제1 신호)와, 단독으로 입력되는 제2 클록신호(제2 신호)를 함께 사용하는 데이터 신호선 구동회로에 있어서, 제1 및 제2 클록신호에서의 배선부하의 차이에 의해 신호 지연량에 차가 발생한다. 이와 같은 신호 지연량에 차가 발생하면, 제1 및 제2 클록신호 사이에서 위상 관계가 신호 설계시의 최적의 관계로부터 어긋나기 때문에, 데이터 신호선 구동회로의 경우, 영상신호의 샘플링 타이밍의 어긋남으로서 나타나, 화면 품위가 저하된다.

또, 배선부하의 차이에서 발생하는 제1 및 제2 클록신호 사이의 상기한 위상차를 고려하여, 이들 클록신호를 작성하는 외부 회로에서, 제1 및 제2 클록신호를 상기 위상차를 해소할 수 있도록 사전에 보정하여 놓는 것도 가능하지만, 전술한 바와같이, 외부 회로의 원 클록(시스템 클록)으로서, 매우 높은 주파수의 것이 필요하게 되어, 소비전력이 높아진다. 모바일 기기의 표시장치로서 이용하는 경우, 소비전력의 증가는, 매우 문제이다.

그래서, 본 발명에서는, 상기한 바와 같이, 다른 회로에도 공통으로 입력되는 제1 신호의 배선부하와, 구동회로에 단독으로 입력되는 제2 신호의 배선부하를 이퀄라이징시키는 배선부하 조정수단을 제공하고 있다.

이에 의해, 외부 회로에 있어서 제1 및 제2 클록신호에 보정을 행하여, 소비전력의 상승을 수반하지 않고, 데이터 신호선 구동회로에만 단독으로 입력되는 제2 클록신호(제2 신호)의 배선부하와, 다른 일방의 데이터 신호선 구동회로에도 공통으로 입력되는 제1 클록신호(제2 신호)의 배선부하를 이퀄라이징시켜, 양 클록신호 사이에서의 신호 지연량의 차를 허용된 범위로 할 수 있다. 그 결과, 제1 및 제2 클록신호를 양방 사용하는 데이터 신호선 구동회로에서의 영상신호의 샘플링이 정확하게 행해져, 화면 품위를 양호하게 유지하는 것이 가능하게 된다.

또, 여기에서는, 데이터 신호선 구동회로를 예로 들어 설명했지만, 주사신호선 구동회로에 있어서도, 복수 계통의 클록신호를 하나의 주사신호선 구동회로에서 사용하는 경우, 각 계통의 클록신호 사이의 상기한 위상차는, 주사신호선의 선택 타이밍의 어긋남을 초래한다. 단, 주사신호선 구동회로에서의 클록신호의 주파수는, 데이터 신호선 구동회로의 클록신호의 주파수에 비해 낮기 때문에, 상기한 위상차에 의한 영향은 작으므로, 데이터 신호선 구동회로에 있어서 사용하는 것이, 보다 효과적이다.

즉, 데이터 신호선 구동회로나 주사신호선 구동회로가, 복수개 제공되는 구성에서는, 외부 인터페이스의 구조의 간략화 때문에, 예컨대 임의의 구동회로에서 사용되는 2계통의 제1 및 제2 클록신호 중 1계통의 제1 클록신호(제1 신호)만이 다른 구동회로에도 공통으로 입력되는 구성으로 되는 경우가 있다. 이와 같은 경우, 제1 및 제2 클록신호를 사용하는 구동회로에 있어서, 단독으로 입력되는 제2 클록신호(제2 신호)와, 공통으로 입력되는 제1 클록신호(제1 신호)의 배선부하의 차이에 의해 신호 지연량에 차가 발생하는 결과, 양 클록신호의 위상 관계에 어긋남이 생겨, 화면 품위가 저하되게 된다. 또한, 상기 위상 관계의 어긋남을, 외부 회로에 있어서 클록신호를 보정하는 것으로 대처하고자 하면, 소비전력의 증가를 수반한다.

그렇지만, 이와 같이, 구동회로에 단독으로 입력되는 제2 신호의 배선부하와, 다른 회로에도 공통으로 입력되는 제1 신호의 배선부하를 이퀄라이징시키는 배선부하 조정수단을 제공함으로써, 외부 회로에 있어서 클록신호에 보정을 행하여, 소비전력의 증가를 수반하지 않고, 상기한 양 클록신호 사이에서의 신호 지연량의 차에 의한 위상 관계의 차를 허용된 범위로 하여, 화면 품위를 양호하게 유지하는 것이 가능하게 된다.

즉, 상기 구성에 의해, 복수 계통의 클록신호 등의 서로 관계가 있는 복수의 신호가 구동회로에 입력됨에 있어서, 외부 인터페이스의 구조의 간략화를 도모해야 하여, 일부는 단독으로 입력되고(제2 신호), 일부는 다른 회로와 공통으로 입력되는 (제1 신호), 관계가 있는 복수의 신호 사이에서 상이한 배선의 인회에 의해 입력되었다고 해도, 소비전력을 증가시키지 않고, 인회의 차이에 의한 영향을 받지 않고 양호한 표시를 행할 수 있는 표시장치를 제공하는 것이 가능하다고 하는 효과를 나타낸다.

본 발명의 다른 목적, 특징 및 우수한 점은, 이하에 나타내는 기재에 의해 충분히 알 수 있을 것이다. 또한, 본 발명의 이점은, 첨부 도면을 참조한 다음의 설명에서 명백하게 될 것이다.

#### 발명의 구성 및 작용

본 발명에 따른 일 실시에에 대해, 도1 내지 도9b를 사용하여 이하에 설명한다.

본 실시예에서는, 표시장치로서, 액티브 매트릭스형의 액정표시장치를 예시한다.

본 실시예에서의 액티브 매트릭스형의 액정표시장치는, 도2에 도시된 바와 같이, 화소 어레이 ARY와, 주사신호선 구동회로 GD1과, 화소 어레이 ARY의 상하에 배치된 제1 및 제2의 2개의 데이터 신호선 구동회로 SD1·SD2를 구비하고 있다.

화소 어레이 ARY는, 서로 교차하는 복수의 주사신호선  $GL(1) \sim GL(j)$  및 데이터 신호선  $SL(1) \sim SL(i)$ 를 구비하고 있고, 인접하는 2개의 주사신호선  $GL \cdot GL$ 과, 인접하는 2개의 데이터 신호선  $SL \cdot SL$ 에 의해 구획된 부분에, 화소 PIX가 하나씩 배치되어 있다. 화소  $PIX \cdot \cdots$ 는, 매트릭스 형태로 배열되어 있다.

제1 및 제2 데이터 신호선 구동회로 SD1·SD2는, 어느 것이나, 주로 시프트 레지스터와 샘플링 회로로 구성되어 있다. 이 중, 제1 데이터 신호선 구동회로 SD1에는, 도시되지 않은 외부 회로로부터, 영상신호 VIDEO와 함께, 제어신호로서의 스

타트 펄스신호 SSP1 및 2계통의 제1 및 제2 클록신호 SCK1·SCK2가 입력되게 되어 있다. 또한, 제2 데이터 신호선 구동회로 SD2에는, 도시되지 않은 외부 회로로부터, 영상신호 VIDEO와 함께, 제어신호로서의 스타트 펄스신호 SSP2 및 제1데이터 신호선 구동회로 SD1에 입력되는 제1 클록신호 SCK1이 공통으로 입력되게 되어 있다.

이들 제1 및 제2 데이터 신호선 구동회로 SD1·SD2의 상세한 구성이나 동작에 대해서는, 도4~도7을 사용하여 후술하지만, 2개의 데이터 신호선 구동회로 SD1·SD2는, 데이터 신호선 SL(1)~SL(i)를 그 양단측으로부터 협지하도록 제공되어 있고, 데이터 신호선 구동회로 SD1·SD2의 양방이 데이터 신호선 SL(1)~SL(i)를 구동할 수 있게 되어 있다.

주사신호선 구동회로 GD는, 주로 시프트 레지스터로 이루어지고, 도시되지 않은 외부회로로부터, 제어신호로서의 스타트 필스신호 GSP 및 클록신호 GCK가 입력되게 되어 있다. 주사신호선 구동회로 GD는, 스타트 필스신호 GSP의 필스가 입력되면, 클록신호 GCK의 타이밍 신호에 동기하여, 주사신호선  $GL(1) \sim GL(j)$ 를 순차적으로 선택하여 구동한다. 이에 의해, 화소 PIX내에 있는 후술하는 스위칭 소자의 개폐가 제어되어, 데이터 신호선 SL에 기입된 영상신호(데이터)를 화소 PIX에 기입하는 동시에, 화소 PIX에 기입된 데이터는 유지된다.

화소 PIX는, 도3에 도시된 바와 같이, 액티브 소자인 전계 효과형의 박막트랜지스터 SW와, 화소 용량 CP에 의해 구성된다. 화소 용량 CP는, 액정 용량 CL, 및 필요에 따라 부가되는 보조 용량 CS로 형성된다. 액티브 소자인 박막트랜지스터 SW의 드레인 및 소스를 통해 데이터 신호선 SL과 화소 용량 CP를 구성하는 액정 용량 CL 및 보조 용량 CS의 각 일방의 전극이 접속된다. 또한, 박막트랜지스터 SW의 게이트는 주사신호선 GL에 접속되어 있다. 액정 용량 CL의 타방의 전극은, 전(全) 화소에 공통으로 제공된 대향전극 COM에 접속되고, 보조 용량의 타방의 전극도, 전(全) 화소에 공통으로 제공된 공통 전극선을 통해 대향 전극 COM에 접속되어 있다. 그리고, 각 액정 용량 CL에 인가되는 전압에 의해, 액정의 투과율 또는 반사율이 변조되어, 표시에 이바지한다.

다음, 도4~도7을 사용하여, 상기 제1 및 제2 데이터 신호선 구동회로 SD1·SD2에서의 구성 및 동작의 일례를 설명한다. 여기에서는, 2개의 데이터 신호선 구동회로 SD1·SD2는 서로 독립적으로 구동하는 고해상도용의 데이터 신호선 구동회로 와, 저해상도용의 데이터 신호선 구동회로인 경우를 설명한다.

도4에, 도2에 있어서 상방에 배치된 제1 데이터 신호선 구동회로 SD1의 회로 구성을 도시한다. 고해상도용인 제1 데이터 신호선 구동회로 SD1은, 2계열의 시프트 레지스터 SR1·SR2와, 상기 시프트 레지스터 SR1·SR2로부터의 각 출력이 입력됨으로써, 별도 입력되는 영상신호 VIDEO를 샘플링하는 아날로그 스위치  $ASW1(1) \sim ASW1(i)$ 를 구비하고 있다. 이들아날로그 스위치  $ASW1(1) \sim ASW1(i)$ 에 의해, 샘플링 회로가 구성된다.

시프트 레지스터 SR1에는, 스타트 펄스신호 SSP1과, 제1 클록신호 SCK1이 입력되게 되어 있고, 시프트 레지스터 SR1로부터 순차 출력되는 샘플링 신호 SMP1(1), SMP1(3) ··· SMP1(i-1)은, 아날로그 스위치 ASW1(1), ASW1(3)~ASW1(i-1)로 공급되고, 아날로그 스위치 ASW1(1), ASW1(3)~ASW1(i-1)을 순차적으로 ON 시킨다. 아날로그 스위치 ASW1(1), ASW1(1), ASW1(3)~ASW1(i-1)이 ON 되어 있는 기간, 별도 입력되어 있는 영상신호 VIDEO가 샘플링되고, 대응하는 데이터 신호선 SL(1), SL(3), ~ SL(i-1)로 출력된다.

한편, 시프트 레지스터 SR2에는, 스타트 펄스신호 SSP1과, 제2 클록신호 SCK2가 입력되게 되어 있고, 시프트 레지스터 SR2로부터 순차적으로 출력되는 샘플링 신호 SMP1(2), SMP1(4) ··· SMP1(i)는, 아날로그 스위치 ASW1(2), ASW1(4)~ASW1(i)로 공급되고, 아날로그 스위치 ASW1(2), ASW1(4)~ASW1(i)를 순차적으로 ON 시킨다. 아날로그 스위치 ASW1(2), ASW1(2), ASW1(4)~ASW1(i)이 ON 되어 있는 기간, 영상신호 VIDEO가 샘플링되고, 대응하는 데이터 신호선 SL(2), SL(4), ~ SL(i)로 출력된다.

이와 같은 제1 데이터 신호선 구동회로 SD1에 관계되는 각 신호의 타이밍챠트를 도5에 도시한다. 제1 클록신호 SCK1과 제2 클록신호 SCK2는, 위상이 1/4 주기 어긋나 있는 관계에 있고, 스타트 펄스신호 SSP1이, 시프트 레지스터 SR1과 시프트 레지스터 SR2에 공급되면, 각 시프트 레지스터 SR1·SR2는, 공급되어 있는 제1 클록신호 SCK1 또는 제2 클록신호 SCK2에 동기하여, 샘플링 신호 SMP1(1), SMP1(2) … SMP1(i)를 순차적으로 출력한다.

한편, 도6에, 도2에 있어서 하방에 배치된 제2 데이터 신호선 구동회로 SD2의 회로 구성을 도시한다. 제2 데이터 신호선 구동회로 SD2는, 저해상도용의 데이터 신호선 구동회로이고, 시프트 레지스터 SR3만을 하나 구비하고 있다. 시프트 레지스터 SR3에는, 스타트 펄스신호 SSP2와 제1 클록신호 SCK1이 입력된다.

시프트 레지스터 SR3으로부터 순차적으로 출력되는 SMP2(1), SMP2(2) ··· SMP2(i/2)는, 아날로그 스위치 ASW2(1), ASW2(2) ~ ASW2(i)로 공급되고, 아날로그 스위치 ASW2(1), ASW2(2)~ASW2(i)를 2개 동시에 순차적으로 ON 시킨다. 아날로그 스위치 ASW2(1), ASW2(2) ~ ASW2(i)가 ON 되어 있는 기간, 영상신호 VIDEO가, 대응하는 데이터 신호선 SL(1), SL(2), ~ SL(i)로 2개씩 출력된다.

이와 같은 제2 데이터 신호선 구동회로 SD2에 관계되는 각 신호의 타이밍챠트를 도7에 도시한다. 스타트 펄스신호 SSP2가, 상기 시프트 레지스터 SR3에 공급되면, 시프트 레지스터 SR3은, 공급되어 있는 제1 클록신호 SCK1에 동기하여, 샘플링 신호 SMP2(1), SMP2(2) … SMP2(i/2)를 순차적으로 출력한다.

이와 같이, 제2 데이터 신호선 구동회로 SD2에서는, 2개의 아날로그 스위치가 동시에 제어되고, 영상신호 VIDEO가 2개의 데이터 신호선 SL·SL에 동시에 공급되게 되어 있다. 따라서, 제1 데이터 신호선 구동회로 SD1을 사용하여 화소 어레이 ARY에 표시를 행한 경우와 비교하여, 표시상의 해상도가 반으로 된다.

그런데, 제1 및 제2의 2개의 데이터 신호선 구동회로 SD1·SD2를 구비한 상기 구성에 있어서는, 2개의 데이터 신호선 구동회로 SD1·SD2에서 공용되는 제1 클록신호(제1 신호) SCK1은, 2개의 데이터 신호선 구동회로 SD1·SD2에 공통으로 입력시키고 있다. 이에 의해, 제1 클록신호 SCK1을 제2 데이터 신호선 구동회로 SD2에 별도 입력시키는 구성에 비해, 외부 인터페이스의 구조를 간략화할 수 있다.

또, 제1 클록신호 SCK1을, 2개의 데이터 신호선 구동회로 SD1·SD2에 공통으로 입력시키는 구성으로 한 경우, 제1 데이터 신호선 구동회로 SD1이 구동되는 경우, 제2 데이터 신호선 구동회로 SD2에도 공급되지만, 제2 데이터 신호선 구동회로 SD2에는, 스타트 펄스신호 SSP2가 입력되어 있지 않기 때문에, 제2 데이터 신호선 구동회로 SD2가 동작하지 않는다.

그렇지만, 제1 클록신호 SCK1을 간단히 공통으로 입력시키면, 전술한 바와 같이, 제1 클록신호 SCK1과, 단독으로 입력되는 제2 클록신호 SCK2(제2 신호)에서의 배선 부하의 차이에 기인하여, 제1 클록신호 SCK1 및 제2 클록신호 SCK2의 양방을 사용하는 제1 데이터 신호선 구동회로 SD1에 있어서, 제1 및 제2 클록신호 SCK1·SCK2 사이에서 신호 지연량에 차가 생겨, 위상 관계가 어긋난다. 제1 및 제2 클록신호 SCK1·SCK2의 위상 관계가 어긋나면, 제1 데이터 신호선 구동회로 SD1에서의 영상신호 VIDEO의 샘플링 타이밍에 미묘한 어긋남이 생겨, 화면 품위가 저하된다. 또한, 상기 위상 관계의 어긋남을, 외부 회로에 있어서 클록신호를 보정하는 것으로 대처하고자하면, 소비전력의 증가를 수반한다.

그래서, 본 실시예에서는, 도1에 도시된 바와 같이, 단독으로 입력되는 제2 클록신호 SCK2용의 배선(2)에 더미 배선(3)을 제공하여, 공통으로 입력되는 제1 클록신호 SCK1용의 배선(1)과 단독으로 입력되는 제2 클록신호 SCK2용의 배선(2)의 배선부하를 이퀄라이징시키도록 되어 있다. 여기에서는, 배선부하의 조정은, 각 배선(1·2)의 시정수, 즉 전술한 바와 같이 시정수  $\tau = 8$ 량 C \* 저항 R( $\tau = CR$ )을 조정하게 되어 있다. 배선(2)의 배선부하가 배선(1)의 배선부하와 이퀄라이징하도록 조정함에 있어서, 시정수에 의해 근사되는 각 배선의 시정수를 이퀄라이징시킴으로써, 배선부하의 조정을 용이하게 행할 수 있다.

상세하게는, 도1에 도시된 바와 같이, 더미 배선(3)은, 데이터 신호선 구동회로 SD1보다 기판단부 측의 신호 입력부(5)에 가까운 빈 영역에 있어, 표시에 기여하는 표시부로는 되지 않지만, 대향 전극 COM을 갖는 대향 기판과의 사이에 액정 층을 협지하고 있는 영역에, 꾸불꾸불한 모양으로 형성되어 있다(도8a 참조). 이와 같은 영역에 더미 배선(3)을 제공함으로써, 도8b에 도시된 바와 같이, 상기 더미 배선(3)을 일방의 전극, 대향 전극 COM을 다른 전극(4)으로 하고, 액정층을 유전체(10)로 하여 부가용량부(7)가 형성되고, 이것이 배선부하 조정수단으로서 기능하게 된다.

이와 같은 더미 배선(3)을 제공하여 배선(2)의 배선부하를 배선(1)의 배선부하와 이퀄라이징시킴으로써, 제1 및 제2 클록신호 SCK1·SCK2의 배선부하가 이퀄라이징하고, 제1 데이터 신호선 구동회로 SD1에서의 제1 및 제2 클록신호 SCK1·SCK2 사이에서의 신호 지연량의 차를 허용된 범위로 할 수 있어, 위상 관계를 바르게 유지할 수 있다. 그 결과, 제1 데이터 신호선 구동회로 SD1에 있어서, 영상 신호 VIDEO의 샘플링을 정확하게 실시할 수 있어, 화면 품위가 향상된다.

또한, 이 경우, 표시장치로서 처음부터 구비하고 있는 부재를 이용하여 배선부하 조정 수단으로서의 부가용량부(7)를 구성하고 있기 때문에, 배선부하 조정수단을 구비한 것에 의한 비용 상승을 최소한으로 억제할 수 있다.

또, 본 실시예와 같은 액정층을 구비한 액정표시장치의 경우, 배선(1)과 배선(2)에서 배선부하가 상이하게 되는 최대의 원인은, 제2 데이터 신호선 구동회로 SD2에까지 인회되는 배선 부분(1a)이, 액정층과 대향 전극 COM 사이에서 용량을 형성하기 때문이다(도1 참조). 따라서, 특히 액정표시장치의 경우, 이와 같이, 더미 배선(3)과 액정층과 대향 전극 COM에서

용량을 형성하여 부가용량부(7)로 함으로써, 배선(2)에 제공하는 더미 배선(3)을 상기한 인회배선 부분(1a)과 동일한 재질을 사용하여, 배선(1)과 배선(2) 사이에서 각 배선 자신이 갖는 저항 R을 같게 함으로써, 배선(1·2) 사이에서 용이하게 시정수를 이퀄라이징시킬 수 있어, 간단히 배선부하를 조정할 수 있다.

또, 여기에서는 더미 배선(3)을, 신호 입력부(5) 근방의 빈 영역에 꾸불꾸불한 형태로 형성했지만, 대향 전극 COM과 평행 평판을 이루도록 더미 배선을 평판 모양으로 해도 좋다. 또한, 도9a 및 도9b에 도시된 바와 같이, 표시부의 주위에 더미배선(3)(태선으로 기재)을 형성하여 부가용량부(7)로 해도 좋다. 이와 같이, 더미 배선(3)을, 제2 데이터 신호선 구동회로 SD2에까지 인회되는 배선 부분(1a)을 따라, 또는 배선 부분(1a)과 대칭을 이루도록 화소 어레이 ARY의 반대측에 제공함으로써, 재질, 배선폭을 같게 한 경우, 배선 길이를 동일하게 하는 것만으로, 배선(1·2) 사이에서 용이하게 시정수를 이퀄라이징시킬 수 있다.

또한, 부가용량부(7)로서는, 더미 배선(3)과 액정층과 대향 전극 COM에 의해 용량을 형성하는 구성 이외에, 예컨대 도 8b에 도시된 더미 배선(3)에 의해 용량을 형성하는 다른 전극(4)으로서, 액정 용량 CL의 도시되지 않은 화소 전극을 형성하면 동일한 투명도전막이나, 콘택트홀을 사용하여 배선의 교차를 실현하기 위해 별도 제공되는 다른 금속층을 사용하여, 이들 투명도전막이나 금속층인 도전막과, 더미 배선(3) 사이에 개재되는 층간절연막을 유전체(10)로 하여 용량을 형성하여, 부가용량부(7)로 해도 좋다.

또는, 화소 어레이 ARY에 형성되는 액티브 소자인 박막트랜지스터 SW를 구성하는 층을 이용하고, 도8c에 도시된 바와 같이, 다른 전극(4)으로서는 박막트랜지스터 SW의 반도체층(9)에 불순물을 첨가하는 등 하여, 고저항의 금속과 같은 특성을 갖게 하여 전극으로서 기능시켜, 금속과 같은 특성을 갖는 상기 반도체층(9)과, 더미 배선(3) 사이에 개재되는 게이트 절연막(8)을 유전체(10)로 하여 용량을 형성하여, 부가용량부(7)로 해도 좋다.

어떠한 부가용량부(7)에 있어서도, 표시장치로서 처음부터 구비하고 있는 부재를 이용하여 구성할 수 있기 때문에, 부가용량부(7)로서 배선부하 조정수단을 구비한 것에 의한 비용 상승을 최소한으로 억제할 수 있다. 또, 이와 같이, 액정층과 대향전극 COM을 이용하지 않는 구성은, 시정수를 이퀄라이징시켜 배선부하를 조정함에 있어서는, 액정층을 이용한 것 정도로 용이하지 않지만, 액정층이나 대향 전극 COM이 적층되어 있지 않는 부분에도 제공할 수 있어, 레이아웃상의 자유도가 높다.

#### 발명의 효과

이상과 같이, 본 실시예의 액티브 매트릭스형의 액정표시장치에서는, 제1 데이터 신호선 구동회로 SD1에서 사용되는 제1 및 제2 클록신호 SCK1·SCK2 중 제1 클록신호 SCK1만이 제2 데이터 신호선 구동회로 SD2에도 공통으로 입력되는 구성에 있어서도, 제1 및 제2 클록신호 SCK1·SCK2의 배선부하(정확하게는, 제1 및 제2 클록신호 SCK1·SCK2를 공급하는 각 배선(1·2)의 배선부하)를 이퀄라이징시키는 부가용량부(7)가 제공되어 있기 때문에, 외부 회로측에서 제1 및 제2 클록신호 SCK1·SCK2의 가공을 행하여 소비전력을 상승시키지 않고, 배선 인회의 차이에 의한 영향을 받지 않고 양호한 표시를 행할 수 있다.

또, 본 실시예에서는, 제1 클록신호 SCK1이 공통으로 입력되는 회로를 데이터 신호선 구동회로 SD2로 했지만, 다음에 프레임에서의 데이터 신호선 SL(1)~SL(i)로의 기입을 안정하게 행하기 위해, 데이터 신호선 SL(1)~SL(i)를 귀선기간에 예비 충전시키는 예비 충전 회로이더라도 좋다. 또한, 여기에서는, 2개의 데이터 신호선 구동회로 SD1·SD2는, 대응 해상 도가 상이한 것으로 했지만, 컬러 표시용과 흑백 표시용의 데이터 신호선 구동회로이어도 좋고, 또한 2개의 데이터 신호선 구동회로 SD1·SD2가 연동하여 구동되어, 슈퍼임포즈 표시 등을 가능하게 하는 구성 등이어도 좋고, 또는 배선부하 조정 수단이 주사신호선 구동회로에 제공되어 있는 구성이어도 좋다.

요컨대, 적어도 하나의 구동회로(데이터 신호선 구동회로에 한정되지 않는다)에, 서로 관계가 있는 복수의 신호(2종류에 한정되지 않는다)가 입력되고, 그 중 적어도 하나의 신호가 다른 회로(구동회로가 아니어도 좋다)에도 인회되어 공통으로 입력되는 구성에 있어서, 이와 같은 더미 배선(평판 모양도 포함한다)(3)을 제공하여 용량을 형성시켜, 관계가 있는 신호사이의 배선부하를 이퀄라이징시키면 좋다.

또, 본 발명에서는, 서로 관계가 있는 복수의 신호로서, 제1 및 제2 신호 사이의 배선부하를 이퀄라이징시킨다는 표현을 사용하고 있는데, 이는, 예컨대 상기한 배선(1·2)의 배선부하를 같게 이퀄라이징시키는 경우를 물론 포함하지만, 요컨대 제1 및 제2 신호가 함께 사용되는 구동회로내에 있어서, 단독으로 입력되는 제2 신호와 다른 회로에도 공통으로 입력되는 제1 신호 사이에서, 각 배선부하에서 각각의 양 지연된 각 신호의 위상 관계가, 신호 설계시와 동일하면 좋고, 극단적으로 말하면 일방의 신호를 크게 지연시켜 위상을 1주기분 지연시킴으로써, 위상을 맞춰도 좋다.

또한, 여기에서는, 서로 관계가 있는 복수의 신호인 제1 및 제2 신호로서, 클록신호를 예시했지만, 예컨대 복수의 비트로 구성되는 디지털 영상신호이고, 적어도 2개의 비트군으로 분리되어 있는 디지털 영상신호인 경우도 있다. 즉, 6비트의 디지털 영상신호를, 제1 데이터 신호선 구동회로 SD1에 입력시키는 한편, 상기 6비트의 디지털 영상신호 중, 상위 3bit만을 제2 데이터 신호선 구동회로 SD2에 입력하여, 데이터 신호선 구동회로 SD1과 SD2에서, 상이한 계조에 대응하는 경우를 고려할 수 있다.

이와 같은 경우도, 외부 인터페이스의 간략화때문에, 영상신호 VIDEO를 상위 3비트와 하위 3비트로 분리하여, 상위 3비트만을 다른 회로에도 입력시키는 구성이 취해진다.

이와 같은 경우에, 상기한 배선부하에 기인하여, 제1 데이터 신호선 구동회로 SD1에 입력되는 6비트의 디지털 영상신호 중, 상위 3비트의 신호의 배선부하가 하위 3비트의 신호의 배선부하와 상이한 경우, 제1 데이터 신호선 구동회로 SD1에 있어서, 디지털 영상신호를 샘플링할 때, 위상차가 발생하여, 샘플링 미스가 일어날 가능성이 있지만, 본 발명을 사용하여 위상차를 이퀄라이징시킴으로써, 상기 샘플링 미스를 일으키지 않고, 회로는 정상적으로 기능하는 것이 가능하게 된다.

또한, 상술한 바와 같이, 본 발명은, 상기 제1 신호가, 공통의 입력단으로부터 신호선을 공용하여, 상기 구동회로 및 상기 다른 회로에 입력되는 구성의 조합이 적합하다. 제1 신호를, 공통의 입력단으로부터 신호선을 공용하여 입력시키는 구성으로 함으로써, 예컨대 입력 신호의 입력단의 수를 줄일 수 있어, 기판 면적을 효과적으로 활용할 수 있다.

본 발명의 표시장치는, 또한 상기 배선부하 조정수단이, 각 배선의 시정수를 이퀄라이징시키도록 되어 있는 것이 바람직하다.

배선부하를 조정함에 있어서, 시정수, 즉 배선 용량치 C, 배선 저항치 R에 의해 산출하는 것이 가능하게 된다. 배선 용량치 C는, 용량을 구성하기 위한 배선의 폭이나 길이와 배선 사이에 협지되는 유전체의 비유전율에 의해 산출된다. 이 때, 용량치를 조정하기 위해 예컨대 배선폭이나 길이를 변경하면 좋고, 또한 부하를 구성하는 배선 저항치도 배선 길이, 배선 폭을 변경함으로써 조정이 가능하게 된다. 이에 의해, 시정수  $\tau = 8$ 량 C \* 저항  $R(\tau = CR)$ 에 의해 근사되는 각 배선의 시정수를 이퀄라이징시키도록 설계함으로써, 배선부하의 조정을 용이하게 행할 수 있다.

본 발명의 표시장치는, 또한 상기 주사신호선과 상기 데이터 신호선은 기판상에 형성되는 동시에, 상기 기판과 대향 전극이 형성된 기판 사이에 액정층을 협지하고 있고, 상기 배선부하 조정수단은, 상기 액정층을 유전체로서 사용하고, 상기 구동회로에 입력되는 제2 신호의 배선에 접속된 더미 배선과, 상기 더미 배선상의 상기 액정층과, 상기 대향 전극을 구비하고 있는 것이 바람직하다.

상기 구성에 의하면, 배선부하가 작은, 구동회로에 단독으로 입력되는 제2 신호의 배선에 더미 배선을 제공하고, 상기 더미 배선과, 대향 전극과, 액정층에 의해, 배선부하 조정을 위한 용량을 구성하고 있다.

이와 같은 배선부하 조정수단은, 표시장치로서 처음부터 구비하고 있는 부재를 이용하여 구성할 수 있기 때문에, 배선부하 조정수단을 구비한 것에 의한 비용 상승을 최소한으로 억제할 수 있다.

또한, 액정층을 갖는 액정표시장치의 경우, 구동회로에 단독으로 입력되는 제2 신호의 배선부하와, 다른 회로에도 공통으로 입력되는 제1 신호의 배선부하가 상이하게 되는 최대의 원인은, 제1 신호에서의 다른 회로로 인회되는 배선부분이, 액정층과 대향 전극 사이에서 용량을 형성하고, 이것이, 무시할 수 없을 정도로 크기 때문이다.

따라서, 이와 같은 구성으로 함으로써, 더미 배선을, 제1 신호의 상기한 다른 회로로 인회되는 배선 부분과 조건적으로 같 게 제공함으로써, 간단히 배선부하를 조정할 수 있다.

본 발명의 표시장치는, 또한 상기 주사신호선과 상기 데이터 신호선은 기판상에 형성되는 동시에, 상기 기판상에는 층간 절연막과 도전막이 더 형성되어 있고, 상기 배선부하 조정수단은, 상기 층간절연막을 유전체로서 사용하고, 상기 구동회로에 입력되는 제2 신호의 배선에 접속된 더미 배선과, 상기 층간절연막과, 상기 도전막을 구비하고 있는 것이 바람직하다.

상기 구성에 의하면, 배선부하가 작은, 구동회로에 단독으로 입력되는 제2 신호의 배선에 더미 배선을 제공하고, 상기 더미 배선상에 형성된 층간절연막과 도전막에 의해, 배선부하 조정을 위한 용량을 구성하고 있다.

상기 주사신호선과 상기 데이터 신호선의 위에는, 충간절연막을 통해 투명도전막 등으로 이루어지는 화소 전극이 형성되거나, 또는 배선의 교차를 실현하기 위한 금속층이 충간절연막을 통해 제공되거나 한다. 따라서, 충간절연막을 유전체로서사용하고, 그 위에 형성되어 있는 도전막을 타방의 전극으로 하여 용량을 구성하는 것이 가능하다.

즉, 이와 같은 배선부하 조정수단에 있어서도, 표시장치로서 처음부터 구비하고 있는 부재를 이용하여 구성할 수 있기 때문에, 배선부하 조정수단을 구비한 것에 의한 비용 상승을 최소한으로 억제할 수 있다.

본 발명의 표시장치는, 또한 상기 주사신호선과 상기 데이터 신호선의 각 교점에는 박막트랜지스터가 제공되어 있고, 상기 배선부하 조정수단은, 박막트랜지스터의 게이트 절연막을 구성하는 층을 유전체로서 사용하고, 상기 구동회로에 입력되는 제2 신호의 배선에 접속된 더미 배선과, 상기 더미 배선에 적층하여 배치된 상기 박막트랜지스터의 게이트 절연막층 및 반도체층을 각각 구성하는 각 층을 구비하고 있는 것이 바람직하다.

상기 구성에 의하면, 배선부하가 작은, 구동회로에 단독으로 입력되는 제2 신호의 배선에 더미 배선을 제공하고, 상기 더미 배선과, 박막트랜지스터의 게이트 절연막을 구성하는 층과, 박막트랜지스터의 반도체층을 구성하는 층에 의해, 배선부하 조정을 위한 용량을 구성하고 있다.

상기 주사신호선과 상기 데이터 신호선의 교점에는 액티브 소자로서 박막트랜지스터가 제공되어 있는 구성이 많고, 이와 같은 구성에 있어서는, 박막트랜지스터의 구성 재료인 게이트 절연막의 구성층을 유전체로 하고, 반도체층에 불순물을 첨가하는 등 하여, 고저항의 금속과 같은 특성을 갖게 하여 전극으로 기능시킴으로써, 용량을 구성할 수 있다.

즉, 이와 같은 배선부하 조정수단에 있어서도, 표시장치로서 처음부터 구비되어 있는 부재를 이용하여 구성할 수 있기 때문에, 배선부하 조정수단을 구비한 것에 의한 비용 상승을 최소한으로 억제할 수 있다.

발명의 상세한 설명의 항에 있어서 이루어진 구체적인 실시 형태 또는 실시예는, 어디까지나, 본 발명의 기술 내용을 명백히 하는 것이며, 그와 같은 구체예에만 한정하여 협의로 해석되어야 하는 것이 아니라, 본 발명의 정신과 다음에 기재하는 특허 청구 사항의 범위내에서, 여러가지로 변경하여 실시할 수 있는 것이다.

#### (57) 청구의 범위

#### 청구항 1.

주사신호선을 구동하는 주사신호선 구동회로와, 상기 주사신호선에 교차하도록 배치된 데이터 신호선을 구동하는 데이터 신호선 구동회로를 구비하고,

또한, 상기 주사신호선 구동회로 또는 데이터 신호선 구동회로의 적어도 일방의 구동회로에, 적어도 제1, 제2 신호가 입력되는 동시에, 상기 제1, 제2 신호가 입력된 구동회로 이외의 다른 회로에 있어서, 주사신호선 구동회로, 데이터 신호선 구동회로 또는 데이터 신호선을 예비 충전시키는 예비 충전 회로의 어느 회로에 제1 신호가 공통으로 입력되도록 구성되어 있고, 상기 구동회로에 입력되는 제2 신호의 배선부하와, 상기 다른 회로에도 공통으로 입력되는 제1 신호의 배선부하를 이퀄라이징시키는 배선부하 조절수단이 제공되어 있는 것을 특징으로 하는 표시장치.

#### 청구항 2.

주사신호선을 구동하는 주사신호선 구동회로와, 상기 주사신호선에 교차하도록 배치된 데이터 신호선을 구동하는 데이터 신호선 구동회로를 구비하고.

또한, 상기 주사신호선 구동회로 또는 데이터 신호선 구동회로의 적어도 일방의 구동회로에, 적어도 제1, 제2 신호가 입력되고, 다른 회로에 제1 신호가 공통으로 입력되도록 구성되어 있고, 상기 구동회로에 입력되는 제2 신호의 배선부하와, 상기 다른 회로에도 공통으로 입력되는 제1 신호의 배선부하를 이퀄라이징시키는 배선부하 조정수단이 제공되어 있는 것을 특징으로 하는 표시장치.

#### 청구항 3.

제2항에 있어서, 상기 다른 회로는, 상기 주사신호선 또는 데이터 신호선을 구동하는 구동회로인 것을 특징으로 하는 표시장치.

#### 청구항 4.

제2항에 있어서, 상기 제1 신호는, 공통의 입력단으로부터 신호선을 공용하여, 상기 구동회로 및 상기 다른 회로에 입력되는 것을 특징으로 하는 표시장치.

#### 청구항 5.

제2항에 있어서, 상기 제1, 제2 신호가, 복수 계통의 클록신호인 것을 특징으로 하는 표시장치.

#### 청구항 6.

제2항에 있어서, 상기 제1, 제2 신호가, 복수의 비트로 구성되는 디지털 영상신호이고, 적어도 2개의 비트군으로 분리되어 있는 디지털 영상신호인 것을 특징으로 하는 표시장치.

#### 청구항 7.

제2항에 있어서, 상기 배선부하 조정수단이, 각 배선의 시정수를 이퀄라이징시키도록 되어 있는 것을 특징으로 하는 표시장치.

#### 청구항 8.

제2항에 있어서, 상기 주사신호선과 상기 데이터 신호선은 기판상에 형성되는 동시에, 상기 기판과 대향 전극이 형성된 기판 사이에 액정층을 협지하고 있고.

상기 배선부하 조정수단은, 상기 액정층을 유전체로서 사용하고, 상기 구동회로에 입력되는 제2 신호의 배선에 접속된 더미 배선과, 상기 더미 배선상의 상기 액정층과, 상기 대향 전극을 구비하고 있는 것을 특징으로 하는 표시장치.

#### 청구항 9.

제8항에 있어서, 상기 더미 배선은, 데이터 신호선 구동회로보다 기판단부측에 가까운 빈 영역에 있어서, 대향 전극이 형성된 기판과의 사이에 액정층을 협지하고 있는 영역의 표시에 기여하는 표시부로는 되지 않는 영역에, 꾸불꾸불한 형태로 형성되어 있는 것을 특징으로 하는 표시장치.

#### 청구항 10.

제8항에 있어서, 상기 더미 배선은, 대향 전극과 평행 평판을 이루도록 평판 형태로 형성되어 있는 것을 특징으로 하는 표시장치.

#### 청구항 11.

제8항에 있어서, 상기 더미 배선은, 표시에 기여하는 표시부의 주위에 형성되어 있는 것을 특징으로 하는 표시장치.

#### 청구항 12.

제2항에 있어서, 상기 주사신호선과 상기 데이터 신호선은 기판상에 형성되는 동시에, 상기 기판상에는 층간절연막과 도 전막이 더 형성되어 있고,

상기 배선부하 조정수단은, 상기 충간절연막을 유전체로서 사용하고, 상기 구동회로에 입력되는 제2 신호의 배선에 접속된 더미 배선과, 상기 충간절연막과, 상기 도전막을 구비하고 있는 것을 특징으로 하는 표시장치.

#### 청구항 13.

제12항에 있어서, 상기 더미 배선은, 표시에 기여하는 표시부의 주위에 형성되어 있는 것을 특징으로 하는 표시장치.

#### 청구항 14.

제2항에 있어서, 상기 주사신호선과 상기 데이터 신호선의 각 교점에는 박막트랜지스터가 제공되어 있고,

상기 배선부하 조정수단은, 박막트랜지스터의 게이트 절연막을 구성하는 층을 유전체로서 사용하고, 상기 구동회로에 입력되는 제2 신호의 배선에 접속된 더미 배선과, 상기 더미 배선에 적층하여 배치된 상기 박막트랜지스터의 게이트 절연막 및 반도체층을 구성하는 각 층을 구비하고 있는 것을 특징으로 하는 표시장치.

#### 청구항 15.

제14항에 있어서, 상기 더미 배선은, 표시에 기여하는 표시부의 주위에 형성되어 있는 것을 특징으로 하는 표시장치.

#### 청구항 16.

제2항에 있어서, 상기 다른 회로는, 데이터 신호선을 예비 충전시키는 예비 충전 회로인 것을 특징으로 하는 표시장치.

#### 청구항 17.

제2항에 있어서, 상기 배선부하 조정수단은, 주사신호선 구동회로에 제공되어 있는 것을 특징으로 하는 표시장치.

도면11

도면12

| 专利名称(译)        | 显示设备                                                                                    |         |            |  |

|----------------|-----------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | KR100522093B1                                                                           | 公开(公告)日 | 2005-10-18 |  |

| 申请号            | KR1020030090764                                                                         | 申请日     | 2003-12-12 |  |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                  |         |            |  |

| 申请(专利权)人(译)    | 夏普株式会社                                                                                  |         |            |  |

| 当前申请(专利权)人(译)  | 夏普株式会社                                                                                  |         |            |  |

| [标]发明人         | WASHIO HAJIME<br>와시오하지메<br>MAEDA KAZUHIRO<br>마에다카즈히로<br>ONDA MAMORU<br>온다마모루            |         |            |  |

| 发明人            | 와시오하지메<br>마에다카즈히로<br>온다마모루                                                              |         |            |  |

| IPC分类号         | G02F1/1345 G02F1/133 G09G3/20 G09G3/36                                                  |         |            |  |

| CPC分类号         | G09G2300/043 G09G2330/021 G09G3/3677 G09G3/3607 G09G2320/0223 G09G3/3688 G09G2310 /0248 |         |            |  |

| 代理人(译)         | LEE,金泰熙                                                                                 |         |            |  |

| 优先权            | 2002363037 2002-12-13 JP                                                                |         |            |  |

| 其他公开文献         | KR1020040052194A                                                                        |         |            |  |

| 外部链接           | Espacenet                                                                               |         |            |  |

#### 摘要(译)

在输入与驱动电路相关的多个信号并且至少一个信号也输入到另一个电路并且彼此共同输入的配置中,由于具有关系的信号之间的布线负载的差异导致的相位关系偏差不经处理就抑制了导致功耗增加的信号本身。第一和第二时钟信号输入到第一数据信号线驱动电路。并且它们中的第一时钟信号也共同输入到第二数据信号线驱动电路。由于布线1和布线2之间的间隙的差异,通过均衡布线负载,在布线2中提供虚设布线。虚设布线,液晶层,形成附加。1