# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) Int. Cl.

**GO2F 1/133** (2006.01)

(21) 출원번호 10-2002-0002090

(22) 출원일자 **2002년01월14일** 심사청구일자 **2007년01월09일**

(65) 공개번호10-2003-0061553(43) 공개일자2003년07월22일

(56) 선행기술조사문헌 JP12244320 A\* \*는 심사관에 의하여 인용된 문헌 (45) 공고일자 2008년06월24일

(11) 등록번호 10-0840675

(73) 특허권자

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

2008년06월17일

(72) 발명자

(24) 등록일자

이석우

경상북도구미시진평동642-3번지

송진경

경상북도구미시진평동642-3번지

(74) 대리인 김용인, 박영복

전체 청구항 수 : 총 2 항

심사관 : 하정균

## (54) 액정표시장치의 데이터 구동 장치 및 방법

#### (57) 요 약

본 발명은 DAC부를 시분할구동하여 기존 칩면적 대비 크게 칩면적을 증가시키기 않거나 오히려 칩면적을 감소시키면서 데이터 구동 IC의 출력 채널수를 증가시킴으로써 데이터 구동 IC 및 TCP의 수를 줄일 수 있는 액정표시장치의 데이터 구동 장치 및 방법을 제공하는 것이다.

본 발명은 입력된 화소데이터를 시분할하여 공급하기 위한 멀티플렉서부와; 멀티플렉서부로부터의 화소데이터를 화소전압신호로 변환하기 위한 디지탈-아날로그 변환부와; 디지탈-아날로그 변환부로부터의 화소전압신호를 다수 의 출력라인에 선택적으로 공급하기 위한 디멀티플렉서부와; 디멀티플렉서부로부터의 화소전압신호를 샘플링 및 홀딩하여 다수의 데이터라인들에 출력하기 위한 샘플링 및 홀딩부를 구비하는 것을 특징으로 한다.

#### *대표도* - 도4

## 특허청구의 범위

#### 청구항 1

입력된 화소데이터를 시분할하여 공급하기 위한 멀티플렉서부와;

상기 멀티플렉서부로부터의 화소데이터를 화소전압신호로 변환하기 위한 디지탈-아날로그 변환부와;

상기 디지탈-아날로그 변환부로부터의 화소전압신호를 다수의 출력라인에 선택적으로 공급하기 위한 디멀티플렉 서부와;

상기 디멀티플렉서부로부터의 화소전압신호를 샘플링 및 홀딩하여 다수의 데이터라인들에 출력하기 위한 샘플링 및 홀딩부와;

샘플링신호를 순차적으로 발생하기 위한 쉬프트 레지스터부와;

상기 샘플링신호에 응답하여 상기 적어도 2n개 이상의 화소데이터를 미리 정해진 단위로 순차적으로 래치하여 상기 멀티플렉서부로 출력하기 위한 래치부와;

상기 샘플링 및 홀딩부로부터의 화소전압신호를 버퍼링하여 상기 다수의 데이터라인들로 출력하기 위한 버퍼부를 포함하며;

상기 멀티플렉서부는 적어도 2n/3(n은 자연수임)개의 멀티플렉서를 구비하여 적어도 2n개 이상의 화소데이터를 적어도 2n/3개씩 시분할하여 공급하며;

상기 디지탈-아날로그 변환부는 상기 적어도 2n/3개의 디지탈-아날로그 변환기를 구비하여 상기 적어도 2n/3개의 화소데이터를 화소전압신호로 변환하며;

상기 디멀티플렉서부는 적어도 2n/3개의 디멀티플렉서를 구비하여 상기 적어도 2n/3개씩의 화소전압신호를 적어도 2n개 이상의 출력라인들에 선택적으로 공급하며;

상기 디지탈-아날로그 변환기 각각은 상기 화소데이터를 정극성 화소전압신호로 변환하기 위한 정극성부와 부극성 화소전압신호로 변환하기 위한 부극성부와, 정극성부 및 부극성부의 출력을 선택하는 멀티플렉서를 구비하며;

상기 멀티플렉서 각각은 제1 내지 제3 스위칭 제어신호 각각에 응답하여 적어도 3개의 화소데이터를 하나의 디지탈-아날로그 변환기에 시분할하여 공급하기 위한 제1 내지 제3 스위칭소자를 구비하며;

상기 디멀티플렉서 각각은 상기 제1 내지 제3 스위칭 제어신호 각각에 응답하여 상기 디지탈-아날로그 변환기로 부터의 화소전압신호를 적어도 3개의 출력라인에 선택적으로 공급하기 위한 제4 내지 제6 스위칭소자를 구비하며;

상기 샘플링 및 홀딩부는 상기 디멀티플렉서부의 적어도 2n개의 출력라인 각각에 접속되는 적어도 2n개의 샘플러-홀더를 구비하며;

상기 샘플러-홀더 각각은, 상기 디멀티플렉서부의 출력라인 각각에 병렬로 접속되는 제1 및 제2 샘플링 스위칭소자와; 상기 샘플링 스위칭소자를 경유한 화소전압신호를 충전하기 위한 제1 및 제2 캐패시터와; 상기 제1 및 제2 캐패시터에 충전된 화소전압신호를 홀딩되게 한 후 상기 데이터라인으로 방전되게 하는 제1 및 제2 홀딩 스위칭소자를 구비하며;

상기 제1 캐패시터에 충전되어질 화소전압신호를 샘플링하는 제1 샘플링 스위칭소자와 상기 제2 캐패시터에 충전된 화소전압신호를 홀딩 및 방전되게 제2 홀딩 스위칭소자는 동일한 제1 스위칭 제어신호에 응답하여 구동되며;

상기 제2 캐패시터에 충전되어질 화소전압신호를 샘플링하는 제2 샘플링 스위칭소자와 상기 제1 캐패시터에 충전된 화소전압신호를 홀딩 및 방전되게 하는 제1 홀딩 스위칭소자는 상기 제1 스위칭 제어신호와 논리상태가 반전되는 동일한 제2 스위칭 제어신호에 응답하여 구동되는 것을 특징으로 하는 액정표시장치의 데이터 구동장치.

## 청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

#### 청구항 8

샘플링신호를 순차적으로 발생하는 단계와;

상기 샘플링신호에 응답하여 상기 적어도 2n개 이상의 화소데이터를 미리 정해진 단위로 순차적으로 래치하여 공급하는 단계와;

화소데이터를 시분할하여 공급하는 단계와,

상기 시분할된 화소데이터를 화소전압신호로 변환하는 단계와;

상기 변환된 화소전압신호를 다수의 출력라인에 선택적으로 공급하는 단계와;

상기 선택적으로 공급된 화소전압신호를 샘플링 및 홀딩하여 다수의 데이터라인들에 출력하는 단계와;

상기 샘플링 및 홀딩된 화소전압신호를 버퍼링하여 상기 적어도 2n개 이상의 데이터라인에 공급하는 단계를 포함하며;

상기 화소데이터를 시분할하는 단계는 제1 내지 제3 스위칭 제어신호에 응답하여 적어도 2n개의 화소데이터를 적어도 3구간으로 시분할하여 공급하는 단계이고;

상기 화소전압신호를 다수의 출력라인에 선택적으로 공급하는 단계는 상기 제1 내지 제3 스위칭 제어신호에 응답하여 상기 화소전압신호 각각을 적어도 3개의 출력라인에 선택적으로 공급하는 단계이고;

상기 화소전압신호를 샘플링 및 홀딩하는 단계는, 임의의 수평기간에서 상기 변환된 화소전압신호를 제1 스위칭 신호에 의해 샘플링하여 제1 캐패시터에 충전되게 함과 동시에 이전 수평기간에 제2 캐패시터에 충전되어 있던 화소전압신호를 제2 스위칭 신호에 의해 해당 데이터라인으로 방전되게 하는 단계와; 다음 수평기간에서 상기 화소전압신호와 다른 화소전압신호를 제 2 스위칭 신호에 의해 샘플링하여 상기 제2 캐패시터에 충전되게 함과 동시에 이전 수평기간에 제1 캐패시터에 충전되어 있던 화소전압신호를 제1 스위칭 신호에 의해 해당 데이터라 인으로 방전되게 하는 단계를 포함하는 것을 특징으로 하는 액정표시장치의 데이터 구동 방법.

## 청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

## 명 세 서

### 발명의 상세한 설명

## 발명의 목적

## 발명이 속하는 기술 및 그 분야의 종래기술

- <23> 본 발명은 액정표시장치에 관한 것으로, 특히 디지털-아날로그 변환부를 시분할 구동하여 데이터 구동 집적회로 와 테이프 캐리어 패키지의 수를 줄일 수 있게 하는 액정표시장치의 데이터 구동 장치 및 방법에 관한 것이다.

- 통상의 액정표시장치는 전계를 이용하여 액정의 광투과율을 조절함으로써 화상을 표시하게 된다. 이를 위하여 <24> 액정표시장치는 액정셀들이 매트릭스 형태로 배열되어진 액정패널과 이 액정패널을 구동하기 위한 구동회로를 구비한다. 액정패널에는 게이트라인들과 데이터라인들이 교차하게 배열되고 그 게이트라인들과 데이터라인들의 교차로 마련되는 영역에 액정셀들이 위치하게 된다. 이 액정패널에는 액정셀들 각각에 전계를 인가하기 위한 화소전극들과 공통전극이 마련된다. 화소전극들 각각은 스위칭 소자인 박막트랜지스터(Thin Film Transistor) 의 소스 및 드레인 단자들을 경유하여 데이터라인들 중 어느 하나에 접속된다. 박막트랜지스터의 게이트단자는 화소전압신호가 1라인분씩의 화소전극들에게 인가되게 하는 게이트라인들 중 어느 하나에 접속된다. 구동회로 는 게이트라인들을 구동하기 위한 게이트 드라이버와, 데이터라인들을 구동하기 위한 데이터 드라이버와, 공통 전극을 구동하기 위한 공통전압 발생부를 구비한다. 게이트 드라이버는 스캐닝신호를 게이트라인들에 순차적으 로 공급하여 액정패널 상의 액정셀들을 1라인분씩 순차적으로 구동한다. 데이터 드라이버는 게이트라인들 중 어느 하나에 게이트신호가 공급될 때마다 데이터라인들 각각에 화소전압신호를 공급한다. 공통전압 발생부는 공통전극에 공통전압신호를 공급한다. 이에 따라, 액정표시장치는 액정셀별로 화소전압신호에 따라 화소전극과 공통전극 사이에 인가되는 전계에 의해 광투과율을 조절함으로써 화상을 표시한다. 데이터 드라이버와 게이트 드라이버는 다수개의 집적회로(Integrated Circuit; 이하, IC라 함)로 집적화된다. 집적화된 데이터 구동 IC와 게이트 구동 IC 각각은 테이프 캐리어 패키지(Tape Carrier Package;이하, TCP라 함) 상에 실장되어 탭(TAB; Tape Automated Bonding) 방식으로 액정패널에 접속되거나, COG(Chip On Glass) 방식으로 액정패널 상에 실장 된다.

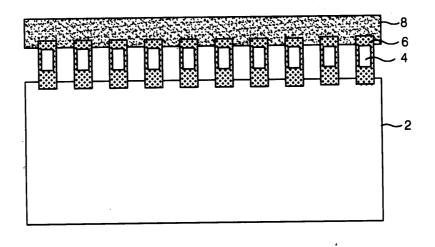

- <25> 도 1은 종래 액정표시장치의 데이터 구동 장치를 개략적으로 도시한 것으로, 데이터 구동 장치는 TCP(6)를 통해 액정패널(2)과 접속되어진 데이터 구동 IC들(4)과, TCP(6)를 통해 데이터 구동 IC들(4)과 접속되어진 데이터 인쇄회로기판(Printed Circuit Board; 이하, PCB라 함)(8)을 구비한다.

- <26> 데이터 PCB(8)는 타이밍 제어부(도시하지 않음)로부터 공급되는 각종 제어신호들 및 데이터 신호들과 파워부(도시하지 않음)로부터의 구동전압신호들을 입력하여 데이터 구동 IC들(4)로 중계하는 역할을 한다. TCP(6)는 액정패널(2)의 상단부에 마련된 데이터 패드들과 전기적으로 접속됨과 아울러 데이터 PCB(8)에 마련된 출력 패드들과 전기적으로 접속된다. 데이터 구동 IC들(4)은 디지털 신호인 화소데이터 신호를 아날로그 신호인 화소전 압신호로 변화하여 액정패널(2) 상의 데이터라인들에 공급한다.

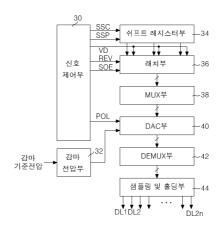

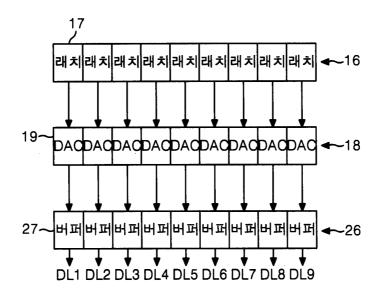

- <27> 이를 위하여, 데이터 구동 IC들(4) 각각은 도 2에 도시된 바와 같이 순차적인 샘플링신호를 공급하는 쉬프트 레지스터부(14)와, 샘플링신호에 응답하여 화소데이터(VD)를 순차적으로 래치하여 동시에 출력하는 래치부(16)와, 래치부(16)로부터의 화소데이터(VD)를 화소전압신호로 변환하는 디지털-아날로그 변환부(이하, DAC부라 함)(18)와, DAC(18)로부터의 화소전압신호를 완충하여 출력하는 출력 버퍼부(26)를 구비한다. 또한, 데이터 구동 IC(4)는 타이밍 제어부(도시하지 않음)로부터 공급되는 각종 제어신호들과 화소데이터(VD)를 중계하는 신호 제어부(10)와, DAC부(18)에서 필요로 하는 정극성 및 부극성 감마전압들을 공급하는 감마 전압부(12)를 추가로 구비한다. 이러한 구성을 가지는 데이터 구동 IC들(4) 각각은 n개씩의 데이터라인들(DL1 내지 DLn)을 구동하게 된다.

- <28> 신호제어부(10)는 타이밍 제어부(도시하지 않음)로부터의 각종 제어신호들(SSP, SSC, SOE, REV, POL 등)과 화소 데이터(VD)가 해당 구성요소들로 출력되게 제어한다.

- <29> 감마전압부(12)는 감마 기준전압 발생부(도시하지 않음)로부터 입력되는 다수개의 감마 기준전압을 그레이별로 세분화하여 출력한다.

- <30> 쉬프트 레지스터부(14)에 포함된 n/6개의 쉬프트 레지스터들은 신호제어부(10)로부터의 소스 스타트 펼스(SSP)를 소스 샘플링 클럭신호(SSC)에 따라 순차적으로 쉬프트시켜 샘플링신호로 출력한다.

- <32> DAC부(18)는 래치부(16)로부터의 화소데이터(VD)를 동시에 정극성 및 부극성 화소전압신호로 변환하여 출력하게 된다. 이를 위하여, DAC부(18)는 래치부(16)에 공통 접속된 P(Positive) 디코딩부(20) 및 N(Negative) 디코딩 부(22)와, P 디코딩부(20) 및 N 디코딩부(22)의 출력신호를 선택하기 위한 멀티플렉서(MUX; 24)를 구비한다.

- <33> P 디코딩부(20)에 포함되는 n개의 P 디코더들은 래치부(16)로부터 동시에 입력되는 n개의 화소데이터들을 감마 전압부(12)로부터의 정극성 감마전압들을 이용하여 정극성 화소전압신호로 변환하게 된다. N 디코딩부(22)에 포함되는 n개의 N 디코더들은 래치부(16)로부터 동시에 입력되는 n개의 화소데이터들을 감마 전압부(12)로부터 의 부극성 감마전압들을 이용하여 부극성 화소전압신호로 변환하게 된다. 멀티플렉서부(24)에 포함되는 n개의 멀티플렉서들은 신호제어부(10)로부터의 극성제어신호(POL)에 응답하여 P 디코더(20)로부터의 정극성 화소전압 신호 또는 N 디코더(22)로부터의 부극성 화소전압신호를 선택하여 출력하게 된다.

- <34> 출력버퍼부(26)에 포함되는 n개의 출력버퍼들은 n개의 데이터라인들(DL1 내지 DLn)들에 직렬로 각각 접속되어진 전압추종기(Voltage follower) 등으로 구성된다. 이러한 출력버퍼들은 DAC부(18)로부터의 화소전압신호들을 신호완충하여 데이터라인들(DL1 내지 DLn)에 공급하게 된다.

- <35> 도 3은 도 2에 도시된 데이터 구동 IC(4) 내에서의 일부 화소데이터의 전송경로를 구체적으로 도시한 것이다.

- <36> 도 3에서 래치부(16)의 래치들(17)은 9개의 화소데이터들을 DAC부(18)를 구성하는 9개의 DAC(디지탈-아날로그 변환기)들(19) 각각으로 출력하여 화소전압신호로 변환되게 한다. 화소전압신호는 출력버퍼부(26)의 버퍼들 (27)을 통해 제1 내지 제9 데이터라인들(DL1 내지 DL9) 각각에 공급된다.

- <37> 이와 같이 종래의 데이터 구동 IC들 각각은 n개의 데이터라인들(DL1 내지 DLn)을 구동하기 위하여 P 디코더 및 N 디코더와 멀티플렉서 각각을 포함하는 n개의 DAC들을 구비해야만 한다. 이에 따라, 데이터 구동 IC는 그 구성이 복잡하여 제조단가가 상대적으로 높다. 이 결과, 액정표시장치의 제조비용을 절감하기 위해서는 데이터 구동 IC의 수를 줄이는 것이 요구된다.

- <38> 데이터 구동 IC의 수를 줄이는 방법으로 데이터 구동 IC가 구동할 수 있는 데이터라인들의 수, 측 출력 채널수를 증가시키는 방법이 고려되고 있다. 그러나, 데이터 구동 IC의 구동 채널수를 증가시키게 되는 경우 복잡한 구성의 DAC수가 증가하게 되므로 칩 면적이 증대됨으로써 면적에 비례하는 TCP의 비용이 상승될 뿐만 아니라 집 적화가 어려워 제조비용 및 불량율 상승과 같은 문제점이 초래된다.

# 발명이 이루고자 하는 기술적 과제

<39> 따라서, 본 발명의 목적은 DAC부를 시분할구동하여 기존 칩면적 대비 크게 칩면적을 증가시키기 않거나 오히려 칩면적을 감소시키면서 데이터 구동 IC의 출력 채널수를 증가시킴으로써 데이터 구동 IC 및 TCP의 수를 줄일 수 있는 액정표시장치의 데이터 구동 장치 및 방법을 제공하는 것이다.

### 발명의 구성 및 작용

- <40> 상기 목적을 달성하기 위하여, 본 발명에 따른 액정표시장치의 데이터 구동 장치는 입력된 화소데이터를 시분할 하여 공급하기 위한 멀티플렉서부와; 멀티플렉서부로부터의 화소데이터를 화소전압신호로 변환하기 위한 디지탈 -아날로그 변환부와; 디지탈-아날로그 변환부로부터의 화소전압신호를 다수의 출력라인에 선택적으로 공급하기 위한 디멀티플렉서부와; 디멀티플렉서부로부터의 화소전압신호를 샘플링 및 홀딩하여 다수의 데이터라인들에 출력하기 위한 샘플링 및 홀딩부를 구비하는 것을 특징으로 한다.

- <41> 여기서, 멀티플렉서부는 적어도 2n/3개(n은 자연수)의 멀티플렉서를 구비하여 적어도 2n개 이상의 화소데이터를 적어도 2n/3개씩 시분할하여 공급하고; 디지탈-아날로그 변환부는 적어도 2n/3개의 디지탈-아날로그 변환기를 구비하여 적어도 2n/3개의 화소데이터를 화소전압신호로 변환하고; 디멀티플렉서부는 적어도 2n/3개의 디멀티플렉서를 구비하여 적어도 2n/3개씩의 화소전압신호를 적어도 2n개 이상의 출력라인들에 선택적으로 공급하는 것을 특징으로 한다.

- <42> 또한, 본 발명의 액정표시장치의 데이터 구동 장치는 샘플링신호를 순차적으로 발생하기 위한 쉬프트 레지스터 부와; 샘플링신호에 응답하여 적어도 2n개 이상의 화소데이터를 미리 정해진 단위로 순차적으로 래치하여 멀티 플렉서부로 출력하기 위한 래치부와; 샘플링 및 홀딩부로부터의 화소전압신호를 버퍼링하여 다수의 데이터라인 들로 출력하기 위한 버퍼부를 추가로 구비하는 것을 특징으로 한다.

- <43> 그리고, 디지탈-아날로그 변환기 각각은 화소데이터를 정극성 화소전압신호로 변환하기 위한 정극성부와 부극성 화소전압신호로 변환하기 위한 부극성부와, 정극성부 및 부극성부의 출력을 선택하는 멀티플렉서를 구비하는 것을 특징으로 한다.

- <44> 특히, 멀티플렉서 각각은 제1 내지 제3 스위칭 제어신호 각각에 응답하여 적어도 3개의 화소데이터를 하나의 디지탈-아날로그 변환기에 시분할하여 공급하기 위한 제1 내지 제3 스위칭소자를 구비하고, 디멀티플렉서 각각은 제1 내지 제3 스위칭 제처신호 각각에 응답하여 상기 디지탈-아날로그 변환기로부터의 화소전압신호를 적어도 3 개의 출력라인에 선택적으로 공급하기 위한 제4 내지 제6 스위칭소자를 구비하는 것을 특징으로 한다.

- <45> 샘플링 및 홀딩부는 디멀티플렉서부의 적어도 2n개의 출력라인 각각에 접속되는 적어도 2n개의 샘플러-홀더를 구비하고; 샘플러-홀더 각각은 디멀티플렉서부의 출력라인 각각에 병렬로 접속되는 제1 및 제2 샘플링 스위칭소자와; 샘플링 스위칭소자를 경유한 화소전압신호를 충전하기 위한 제1 및 제2 캐패시터와; 제1 및 제2 캐패시터 에 충전된 화소전압신호를 홀딩되게 한 후 데이터라인으로 방전되게 하는 제1 및 제2 홀딩 스위칭소자를 구비하는 것을 특징으로 한다.

- <46> 여기서, 제1 캐패시터에 충전되어질 화소전압신호를 샘플링하는 제1 샘플링 스위칭소자와 제2 캐패시터에 충전 된 화소전압신호를 홀딩 및 방전되게 제2 홀딩 스위칭소자는 동일한 제1 스위칭 제어신호에 응답하여 구동되고, 제2 캐패시터에 충전되어질 화소전압신호를 샘플링하는 제2 샘플링 스위칭소자와 제1 캐패시터에 충전된 화소전 압신호를 홀딩 및 방전되게 하는 제1 홀딩 스위칭소자는 제1 스위칭 제어신호와 논리상태가 반전되는 동일한 제 2 스위칭 제어신호에 응답하여 구동되는 것을 특징으로 한다,

- 본 발명에 따른 액정표시장치의 데이터 구동 방법은 화소데이터를 시분할하여 공급하는 단계와; 시분할된 화소데이터를 화소전압신호로 변환하는 단계와; 변환된 화소전압신호를 다수의 출력라인에 선택적으로 공급하는 단계와; 선택적으로 공급된 화소전압신호를 샘플링 및 홀딩하여 다수의 데이터라인들에 출력하는 단계를 포함하는 것을 특징으로 한다.

- <48> 또한, 본 발명의 액정표시장치의 데이터 구동 방법은 화소 데이터를 시분할하여 공급하는 단계전에, 샘플링신호를 순차적으로 발생하는 단계와; 샘플링신호에 응답하여 적어도 2n개 이상의 화소데이터를 미리 정해진 단위로 순차적으로 래치하여 공급하는 단계를 추가로 포함하고, 샘플링 및 홀딩된 화소전압신호를 버퍼링하여 적어도 2n개 이상의 데이터라인에 공급하는 단계를 추가로 포함하는 것을 특징으로 한다.

- <49> 그리고, 화소데이터를 시분할하는 단계는 제1 내지 제3 스위칭 제어신호에 응답하여 적어도 2n개의 화소데이터를 적어도 3구간으로 시분할하여 공급하는 단계이고, 화소전압신호를 다수의 출력라인에 선택적으로 공급하는 단계는 제1 내지 제3 스위칭 제어신호에 응답하여 화소전압신호 각각을 적어도 3개의 출력라인에 선택적으로 공급하는 단계인 것을 특징으로 한다.

- <50> 또한, 화소전압신호를 샘플링 및 홀딩하는 단계는, 임의의 수평기간에서 변환된 화소전압신호를 제1 스위칭 신호에 의해 샘플링하여 제1 캐패시터에 충전되게 함과 동시에 이전 수평기간에 제2 캐패시터에 충전되어 있던 화

소전압신호를 제2 스위칭 신호에 의해 해당 데이터라인으로 방전되게 하는 단계와; 다음 수평기간에서 상기 화소전압신호와 다른 화소전압신호를 제 2 스위칭 신호에 의해 샘플링하여 상기 제2 캐패시터에 충전되게 함과 동시에 이전 수평기간에 제1 캐패시터에 충전되어 있던 화소전압신호를 제1 스위칭 신호에 의해 해당 데이터라인으로 방전되게 하는 단계를 포함하는 것을 특징으로 한다.

- <51> 상기 목적 외에 본 발명의 다른 목적 및 이점들은 첨부한 도면들을 참조한 본 발명의 바람직한 실시예에 대한 설명을 통하여 명백하게 드러나게 될 것이다.

- <52> 이하, 도 4 내지 도 8을 참조하여 본 발명의 바람직한 실시예에 대하여 설명하기로 한다.

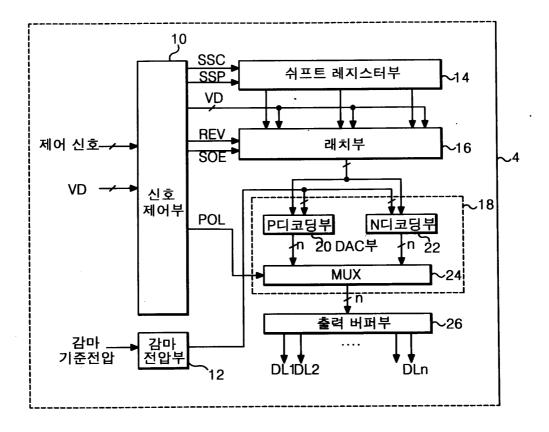

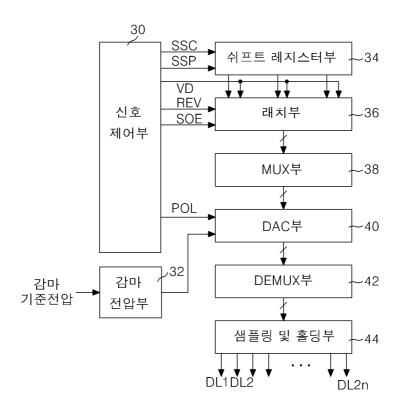

- <53> 도 4는 본 발명의 실시 예에 따른 LCD의 데이터 구동 장치를 도시한 블록도이다.

- <54> 도 4에 도시된 LCD의 데이터 구동 장치는 순차적인 샘플링신호를 공급하는 쉬프트 레지스터부(34)와, 샘플링신호에 응답하여 화소데이터(VD)를 순차적으로 래치하여 출력하는 래치부(36)와, 래치부(36)로부터의 화소데이터(VD)를 시분할하여 공급하는 멀티플렉서부(38)와, 멀티플렉서부(38)로부터의 화소데이터(VD)를 화소전압신호로 변환하는 DAC부(40)와, 출력라인들을 시분할 구동하여 DAC부(40)로부터의 화소전압신호를 공급하는 디멀티플렉서부(42)와, 디멀티플렉서부(42)로부터 입력되는 화소전압신호를 샘플링 및 홀딩하여 데이터라인들(DL1 내지 DL2n)에 동시에 공급하는 샘플링 및 홀딩부(44)를 구비한다. 또한 데이터 구동 장치는 타이밍 제어부(도시하지 않음)로부터 공급되는 제어신호들과 화소데이터(VD)를 중계하는 신호 제어부(30)와, DAC부(40)에서 필요로 하는 정극성 및 부극성 감마전압들을 공급하는 감마 전압부(32)를 추가로 구비한다. 이러한 구성을 가지는 데이터 구동 장치는 하나의 데이터 구동 IC로 집적화되어 종래의 데이터 구동 IC 보다 2배 증가된 2n개의 데이터라인들 (DL1 내지 DL2n)을 구동하게 된다.

- <55> 신호제어부(30)는 타이밍 제어부(도시하지 않음)로부터의 각종 제어신호들(SSP, SSC, SOE, REV, POL 등)과 화소 데이터(VD)를 해당 구성요소들로 출력되게 제어한다.

- <56> 감마 전압부(32)는 감마 기준전압 발생부(도시하지 않음)로부터 입력되는 다수개의 감마 기준전압을 그레이별로 세분화하여 출력한다.

- <57> 쉬프트 레지스터부(34)에 포함되는 쉬프트 레지스터들은 신호제어부(30)로부터의 소스 스타트 펄스(SSP)를 소스 샘플링 클럭신호(SSC)에 따라 순차적으로 쉬프트시켜 샘플링신호로 출력한다.

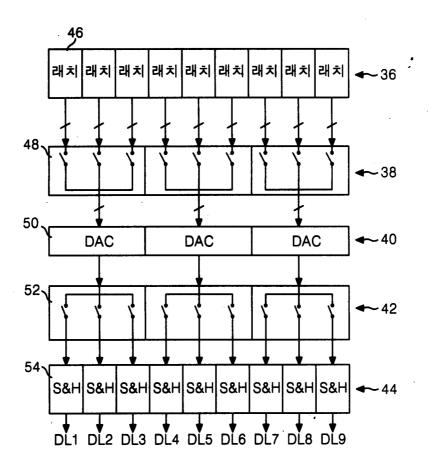

- <58> 래치부(36)는 쉬프트 레지스터부(34)로부터의 샘플링신호에 응답하여 신호 제어부(30)로부터의 화소데이터(VD)를 일정단위씩 순차적으로 샘플링하여 래치하게 된다. 이를 위하여 래치부(36)는 도 5에 도시된 바와 같이 2n 개의 화소데이터(VD)를 래치하기 위해 2n개의 래치들(46)로 구성되고, 그 래치들(46) 각각은 화소데이터(VD)의 비트수(3비트 또는 6비트)에 대응하는 크기를 갖는다. 이러한 래치부(36)는 샘플링신호마다 신호 제어부(30)를 경유하여 공급되는 짝수 화소데이터(VDeven)와 홀수 화소데이터(VDodd), 즉 6개의 화소데이터를 래치하게 된다. 이어서 래치부(36)는 신호 제어부(30)로부터의 소스 출력 이네이블신호(SOE)에 응답하여 래치된 2n개의 화소데이터들(VD)을 출력한다. 이 경우 래치부(36)는 데이터반전 선택신호(REV)에 응답하여 트랜지션 비트수가 줄어들게끔 변조된 화소데이터(VD)들을 복원시켜 출력하게 된다.

- <59> 멀티플렉서부(38)는 래치부(36)로부터 입력되는 2n개의 화소데이터를 시분할하여 출력하게 된다. 이 2n개의 화소데이터를 3구간으로 시분할 하는 경우 멀티플렉서부(38)는 도 5에 도시된 바와 같이 3개씩의 래치들(46)에 접속된 2n/3개의 멀티플렉서들(48)을 구비한다. 멀티플렉서들(48) 각각은 3개씩의 래치들(46)로부터 입력된 화소데이터를 시분할하여 하나의 출력라인에 순차적으로 공급한다. 다시 말하여 멀티플렉서부(38)는 래치부(36)로부터 입력되는 2n개의 화소데이터를 2n/3개씩 시분할하여 DAC부(40)로 출력하게 된다.

- <61> 디멀티플렉서부(42)는 출력라인들을 시분할 구동하여 DAC부(40)로부터의 화소전압신호를 선택적으로 공급하게

된다. 이를 위하여 디멀티플렉서부(42)는 도 5에 도시된 바와 같이 DAC(50)와 동일한 2n/3개의 디멀티플렉서들 (52)를 구비한다. 디멀티플렉서들(52) 각각은 3개의 출력라인들을 시분할 구동하여 DAC(50)로부터 공급되는 화소전압신호를 선택적으로 공급한다. 다시 말하여, 디멀티플렉서부(42)는 DAC부(40)로부터 입력되는 2n/3개씩의 화소전압신호를 출력라인을 달리하여 순차적으로 샘플링 및 홀딩부(44)로 출력하게 된다.

- <62> 샘플링 및 홀딩부(44)는 디멀티플렉서부(42)로부터 입력되는 화소전압신호를 샘플링하여 홀딩한 다음 데이터라 인들(DL1 내지 DL2n)에 동시에 출력한다. 이를 위하여, 샘플링 및 홀딩부(44)는 도 5에 도시된 바와 같이 데이터라인들(DL1 내지 DL2n)에 각각 연결되는 동일한 2n개의 샘플러-홀더(54)를 구비한다. 샘플러-홀더(54) 각각은 디멀티플렉서(52)로부터 시간차를 두고 입력되는 화소전압신호를 샘플링하여 홀딩한 다음 데이터라인들(DL1 내지 DL2n) 각각에 동시에 출력한다. 다시 말하여, 샘플러-홀더(44)는 디멀티플렉서부(42)로부터 2n/3개씩 입력되는 화소전압신호를 샘플링하여 홀딩한 다음 2n개의 화소전압신호가 모두 샘플링되면 그 화소전압신호들을 제1 내지 제2n 데이터라인들(DL1 내지 DL2n)에 동시에 출력하게 된다.

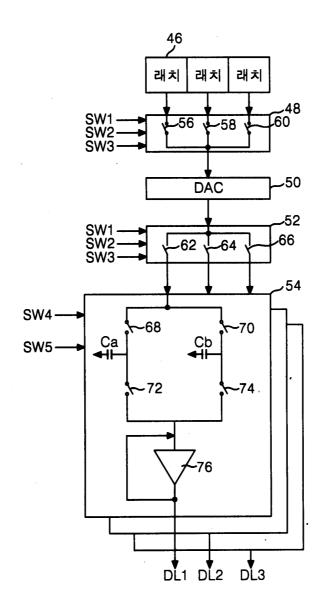

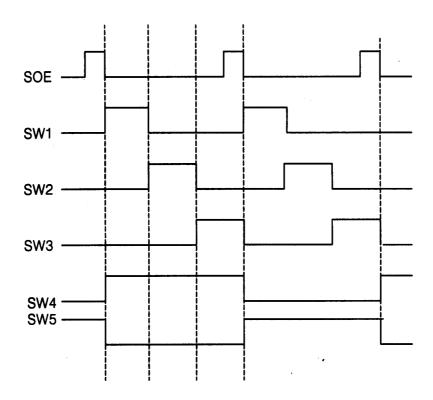

- <63> 도 6은 도 5에 도시된 데이터 구동 IC내에서 3개의 R, G, B 화소데이터에 대한 전송경로를 구체적으로 도시한 것이고, 도 7은 도 6에 도시된 구성요소들의 구동을 제어하기 위한 제어신호들의 도시한 것이다.

- <64> 도 6에서 3개의 래치들(46) 각각은 타이밍제어부(도시하지 않음)로부터 도 4에 도시된 신호제어부(30)를 경유하여 입력되는 출력 이네이블 신호(SOE)에 응답하여 R, G, B 화소데이터를 멀티플렉서(48)로 출력한다. 출력 이네이블 신호(SOE)는 통상 도 7에 도시된 바와 같이 1수평기간(1H)마다 래치들(46)에 공통적으로 공급된다.

- <65> 멀티플렉서(48)는 3개의 래치들(46)로부터 입력되는 R, G, B 화소데이터를 시분할하여 하나의 DAC(50)에 순차적으로 공급한다. 이를 위하여, 멀티플렉서(48)는 입력라인이 3개의 래치들(46) 각각에 접속되고 출력라인이 하나의 DAC(50)에 공통접속된 제1 내지 제3 스위치(56, 58, 60)를 구비한다. 제1 내지 제3 스위치(56, 58, 60)는 타이밍제어부로부터 신호제어부(30)를 경유하여 입력되는 제1 내지 제3 스위치 제어신호(SW1, SW2, SW3) 각각에 응답하여 래치(46)로부터의 화소데이터를 출력하게 된다. 예를 들면, 제1 내지 제3 스위치(56, 58, 60)는도 7에 도시된 바와같이 순차적으로 이네이블되는 제1 내지 제3 스위치 제어신호(SW1, SW2, SW3)에 응답하여 래치들(46)로부터 입력되어진 R, G, B 화소데이터를 순차적으로 하나의 DAC(50)로 출력한다.

- <66> DAC(50)는 멀티플렉서(48)로부터 순차적으로 입력되는 R, G, B 화소데이터를 R, G, B 화소전압신호로 변환하여 디멀티플렉서(52)로 출력한다.

- <67> 디멀티플렉서(52)는 DAC(50)로부터 순차적으로 입력되는 R, G, B 화소전압신호를 서로 다른 출력라인을 통해 3 개의 샘플러-홀더(54) 각각으로 출력하게 된다. 이를 위하여 디멀티플렉서(52)는 입력라인이 하나의 DAC(50) 출력라인에 공통접속되고 출력라인이 3개의 샘플러-홀더(54) 각각에 접속된 제4 내지 제6 스위치(62, 64, 66)를 구비한다. 제4 내지 제6 스위치(62, 64, 66)는 타이밍제어부로부터 신호제어부(30)를 경유하여 입력되는 제1 내지 제3 스위치 제어신호(SW1, SW2, SW3) 각각에 응답하여 DAC(50)로부터의 화소데이터를 서로 다른 출력라인을 통해 출력하게 된다. 이 경우, 디멀티플렉서(52)는 멀티플렉서(48)와 동일한 제1 내지 제3 스위치 제어신호(SW1, SW2, SW3)를 이용한다. 예를 들면, 제4 내지 제6 스위치(62, 64, 66)는 도 7에 도시된 바와 같이 순차적으로 이네이블되는 제1 내지 제3 스위치 제어신호(SW1, SW2, SW3)에 응답하여 DAC(50)로부터 순차적으로 입력되는 R, G, B 화소전압신호를 3개의 샘플러-홀더(54)에 분리하여 공급하게 된다.

- <68> 3개의 샘플러-홀더(54)는 디멀티플렉서(52)로부터 순차적으로 입력되는 R, G, B 화소전압신호를 샘플링하여 홀딩한 다음 동시에 제1 내지 제3 데이터라인(DL1 내지 DL3) 각각으로 출력하게 된다. 이를 위하여 각각의 샘플러-홀더(54)는 입력라인이 디멀티플렉서(52)의 하나의 출력라인에 공통 접속된 제7 및 제8 스위치(68, 70)와, 제7 및 제8 스위치(68, 70) 각각의 출력라인에 접속된 제1 및 제2 캐패시터(Ca, Cb)와, 입력라인이 제7 및 제8 스위치(68, 70)의 출력라인 각각에 접속되고 출력라인이 하나의 데이터라인(DL)에 공통접속된 제9 및 제10 스위치(72, 74)를 구비한다. 또한 샘플러-홀더(54)는 제9 및 제 10 스위치(72, 74)의 출력라인과 데이터라인 사이에 접속된 버퍼(76)를 더 구비한다.

- <69> 대각선방향으로 위치하는 제7 및 제10 스위치(68, 74)는 동일한 제4 스위치 제어신호(SW4)에 응답하고, 제8 및 제9 스위치(70, 72)는 제4 스위치 제어신호(SW4)와 상반된 논리상태를 갖는 제5 스위치 제어신호(SW5)에 응답한다. 제4 및 제5 스위치 제어신호(SW4, SW5)는 다른 제어신호들과 동일하게 타이밍제어부로부터 신호제어부(30)를 통해 공급된다. 제1 및 제2 캐패시터(Ca, Cb)는 서로 다른, 즉 시간적으로 인접한 수평라인의 데이터를충전하게 된다.

- <70> 예를 들면, 한 수평기간에서 도 7에 도시된 바와 같이 하이상태로 공급되는 제4 스위치 제어신호(SW4)에 응답하

여 제7 및 제10 스위치(68, 74)가 턴-온된다. 이에 따라, 턴-온된 제7 스위치(68)에 의해 디멀티플렉서(52)로 부터 공급되는 화소전압신호가 샘플링되고 제1 캐패시터(Ca)에 충전되어 홀딩된다. 이와 동시에, 이전 수평기간에서 제2 캐패시터(Cb)에 충전되어 있던 화소전압신호가 턴-온된 제10 스위치(74)와 버퍼(76)를 경유하여 해당 데이터라인(DL)으로 공급된다.

- <71> 그 다음 수평기간에서 도 7에 도시된 바와 같이 하이상태로 공급되는 제5 스위치 제어신호(SW5)에 응답하여 제8 및 제9 스위치(70, 72)가 턴-온된다. 이에 따라, 턴-온된 제8 스위치(70)에 의해 디멀티플렉서(52)로부터 공급되는 화소전압신호가 샘플링되고 제2 캐패시터(Cb)에 충전되어 홀딩된다. 이와 동시에, 이전 수평기간에서 제1 캐패시터(Ca)에 충전되어 있던 화소전압신호가 턴-온된 제9 스위치(72)와 버퍼(76)를 경유하여 해당 데이터라인 (DL)으로 공급된다.

- <72> 이렇게, 샘플러-홀더(54)가 화소전압신호 샘플링을 위한 한쌍의 제7 및 제8 스위치(68, 70)과, 화소전압신호 충전을 위한 한쌍의 제1 및 제2 캐패시터(Ca, Cb)와, 화소전압신호 홀딩을 위한 한쌍의 제9 및 제10 스위치(72, 74)를 구비하여 서로 교번적으로 구동되게 함으로써 샘플링 및 홀딩 동작에 의한 신호지연을 방지할 수 있게 된다.

- <73> 이상 설명한 바와 같이 본 발명의 실시 예에 따른 데이터 구동 IC는 DAC부의 시분할 구동으로 DAC수를 적어도 1/3로 줄임으로써 IC내에서 DAC부가 차지하는 공간이 줄어들게 한다. 이에 따라 기존 칩면적 대비 크게 칩면적을 증가시키기 않거나 오히려 칩면적을 감소시키면서 데이터 구동 IC가 구동하는 데이터라인 수, 즉 출력채널수를 종래대비 2배로 증가시키는 것이 가능하게 됨으로써 데이터 구동 IC와 그 IC가 실장되는 TCP의 수를 1/2로 줄일 수 있게 된다.

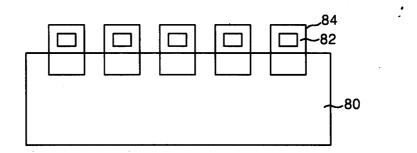

- <74> 상세히 하면, 도 8에 도시된 바와 같이 종래대비 2배의 출력채널을 갖는 데이터 구동 IC(82)가 TCP(84) 상에 실 장되어 액정패널(80)에 접속된다.

- <75> 예를 들어, SXGA 모드(1280\*1024)의 액정패널(80)을 구동하기 위해 종래에는 384채널의 데이터 구동 IC 10개가 필요했던 반면에, 전술한 본 발명의 데이터 구동 IC(82)를 사용하는 경우 칩면적 증대없이 768채널을 확보할 수 있게 되므로 종래대비 1/2인 5개의 데이터 구동 IC(82)만이 필요하게 된다. 이에 따라, 데이터 구동 IC(82) 및 TCP(84)의 수를 종래보다 적어도 1/2로 줄일 수 있게 되므로 액정표시장치의 제조비용을 낮출 수 있게 된다.

#### 발명의 효과

- <76> 상술한 바와 같이, 본 발명에 따른 액정표시장치의 데이터 구동 장치 및 방법에서는 DAC부를 시분할구동함으로 써 기존 칩면적 대비 크게 칩면적을 증가시키기 않거나 오히려 칩면적을 감소시키면서 데이터 구동 IC의 채널수를 종래대비 2배로 증가시킬 수 있게 된다. 이에 따라, 본 발명에 따른 액정표시장치의 데이터 구동 장치 및 방법에 의하면 데이터 구동 IC의 채널수를 증가시켜 데이터 구동 IC 및 TCP의 수를 종래대비 1/2로 줄일 수 있게 되므로 액정표시장치의 제조비용을 낮출 수 있게 된다.

- <77> 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

# 도면의 간단한 설명

- <!> 도 1은 종래 액정표시장치의 데이터 구동 장치를 개략적으로 도시한 도면.

- <2> 도 2는 도 1에 도시된 데이터 구동 집적회로의 상세 구성을 도시한 블록도.

- <3> 도 3은 도 2에 도시된 데이터 구동 집적회로 내에서의 일부 데이터 전송경로를 구체적으로 도시한 도면.

- <4> 도 4는 본 발명의 실시 예에 따른 액정표시장치의 데이터 구동 집적회로의구성을 도시한 블록도.

- <5> 도 5는 도 4에 도시된 데이터 구동 집적회로내에서의 일부 데이터 전송경로를 도시한 도면.

- <6> 도 6은 도 5에 도시된 샘플러-홀더의 구성을 구체화하여 데이터 전송경로를 도시한 도면.

- <7> 도 7은 도 6에 도시된 스위치들을 제어하는 스위치 제어신호 파형도.

<8> 도 8은 본 발명에 따른 데이터 구동 집적회로를 포함하는 액정표시장치의 데이터 구동장치를 개략적으로 도시한 도면.

<9> <도면의 주요부분에 대한 설명>

<10> 2, 80 : 액정패널 4, 82 : 데이터 구동 집적회로(IC)

<11> 6, 84 : 테이프 캐리어 패키지(TCP)

<12> 8 : 데이터 인쇄회로기판(PCB) 10, 30 : 신호 제어부

<13> 12, 32 : 감마 전압부 14, 34 : 쉬프트 레지스터부

<14> 16, 36 : 래치부 17, 46 : 래치

<15> 18, 40 : 디지털-아날로그 변환(DAC)부

<16> 19, 50 : 디지털-아날로그 변환기(DAC)

<17> 20 : P 디코딩부 22 : N 디코딩부

<18> 24, 38 : 멀티플렉서(MUX)부 26 : 출력 버퍼부

<19> 27, 76 : 버퍼 42 : 디멀티플렉서(DEMUX)부

<20> 44 : 샘플링 및 홀딩부 48 : 멀티플렉서(MUX)

<21> 52 : 디멀티플렉서(DEMUX) 54 : 샘플러-홀더

<22> 56, 58, 60, 62, 64, 66, 68, 70, 72, 74 : 스위치

#### 도면

| 用于驱动液晶显示装置的装置和方法                                             | 去                                                                                                                                                                                                 |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KR100840675B1                                                | 公开(公告)日                                                                                                                                                                                           | 2008-06-24                                                                                                                                                                                                                 |                                                                                                                                                                                                                       |

| KR1020020002090                                              | 申请日                                                                                                                                                                                               | 2002-01-14                                                                                                                                                                                                                 |                                                                                                                                                                                                                       |

| 乐金显示有限公司                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

| LG显示器有限公司                                                    |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

| LG显示器有限公司                                                    |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

| LEE SEOKWOO<br>이석우<br>SONG JINKYUNG<br>송진경                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

| 이석우<br>송진경                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

| G02F1/133 G09G3/20 G09G3/36                                  |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

| G09G2310/027 G09G3/3688 G09G3/3685 G09G2310/0297 G09G2352/00 |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

| 金勇<br>年轻的小公园                                                 |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

| KR1020030061553A                                             |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

| <u>Espacenet</u>                                             |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

|                                                              | KR100840675B1  KR1020020002090  乐金显示有限公司  LG显示器有限公司  LG显示器有限公司  LEE SEOKWOO 이석우 SONG JINKYUNG 송진경 이석우 송진경  G02F1/133 G09G3/20 G09G3/36  G09G2310/027 G09G3/3688 G090  金勇 年轻的小公园  KR1020030061553A | KR100840675B1 公开(公告)日  KR1020020002090 申请日  乐金显示有限公司  LG显示器有限公司  LEE SEOKWOO 이석우 SONG JINKYUNG 송진경  이석우 송진경  G02F1/133 G09G3/20 G09G3/36  G09G2310/027 G09G3/3688 G09G3/3685 G09G2310/0297 G09G金勇 年轻的小公园  KR1020030061553A | KR100840675B1 公开(公告)日 2008-06-24  KR1020020002090 申请日 2002-01-14  乐金显示有限公司  LG显示器有限公司  LEE SEOKWOO 이석우 SONG JINKYUNG 송진경 이석우 송진경 G02F1/133 G09G3/20 G09G3/3685 G09G2310/0297 G09G2352/00  金勇 年轻的小公园  KR1020030061553A |

## 摘要(译)

本发明的目的是提供一种用于驱动液晶显示数据的方法和装置,用于减少数据驱动集成电路和TCP的数量,同时不用时间共享和驱动DAC部分,并通过现有芯片面积比较增加芯片面积或相反减小芯片面积,增加了数据驱动集成电路的输出通道数。本发明包括用于对来自多路复用器的像素电压信号进行采样的采样,用于分时输入的像素数据和提供以及数字-模拟转换部分:用于将来自多路复用器的像素数据转换为像素电压信号和用于选择性地提供的多路分解器单元像素电压信号从数字-模拟转换部分到多个输出线和多路分解器单元并保持和输出到多个数据线和保持部分。