(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2009-0041255

(43) 공개일자 2009년04월28일

(51) Int. Cl.

G09G 3/36 (2006.01) G09G 3/20 (2006.01)

G02F 1/133 (2006.01)

(21) 출원번호 10-2007-0106863

(22) 출원일자 2007년10월23일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

이환주

대구 동구 덕곡동 134번지 22/1

신정옥

서울 마포구 성산2동 성산시영아파트 16동 906호

(74) 대리인

박장원

전체 청구항 수 : 총 5 항

(54) 액정표시장치의 전자파 장해 저감 장치

### (57) 요 약

본 발명은 액정표시장치의 타이밍 콘트롤러에서 RGB 데이터를 처리하여 데이터 구동부에 출력하는 과정에서 높은 리드 클럭신호에 의해 전자파 장해를 입는 것을 최소화 하는 기술에 관한 것이다. 이와 같은 본 발명은 외부로부터 입력되는 RGB 데이터를 재정렬하여 데이터구동부에 출력함에 있어서, 두 개의 기본 라인메모리에 라인메모리를 추가하고 그 추가된 라인메모리의 개수에 상응되게 그 RGB 데이터의 리드 클럭신호의 주파수를 낮추는 타이밍 콘트롤러와; 액정 패널의 각 게이트라인에 게이트펄스를 공급하는 게이트 구동부 및, 상기 타이밍 콘트롤러로부터 입력되는 RGB 데이터에 대응하여, 상기 액정 패널의 각 데이터라인에 화소신호를 공급하는 데이터 구동부를 포함하여 구성함을 특징으로 한다.

**대 표 도** - 도3

## 특허청구의 범위

### 청구항 1

외부로부터 입력되는 RGB 데이터를 재정렬하여 데이터구동부에 출력함에 있어서, 두 개의 기본 라인메모리에 라인메모리를 추가하고 그 추가된 라인메모리의 개수에 상응되게 그 RGB 데이터의 리드 클럭신호의 주파수를 낮추는 타이밍 콘트롤러와;

액정 패널의 각 게이트라인에 게이트펄스를 공급하는 게이트 구동부와;

상기 타이밍 콘트롤러로부터 입력되는 RGB 데이터에 대응하여, 상기 액정 패널의 각 데이터라인에 화소신호를 공급하는 데이터 구동부를 포함하여 구성한 것을 특징으로 하는 액정표시장치의 전자파 장해 저감 장치.

### 청구항 2

제1항에 있어서, 타이밍 콘트롤러는 총 3개의 라인메모리를 구비한 경우 데이터인에이블신호의 '하이' 구간마다 그 각각의 라인메모리에 1수평라인 분량의 RGB 데이터를 순차적으로 라이트하고, 나머지 두 주기동안에는 바로 이전에 라이트된 RGB 데이터를 리드하여 출력하도록 구성된 것을 특징으로 하는 액정표시장치의 전자파 장해 저감 장치.

### 청구항 3

제2항에 있어서, 타이밍 콘트롤러는 리드된 RGB 데이터를 소스 아웃 인에이블신호의 폴링 에지에 동기시켜 출력하도록 구성된 것을 특징으로 하는 액정표시장치의 전자파 장해 저감 장치.

### 청구항 4

제1항에 있어서, 타이밍 콘트롤러는 적어도 3개 이상의 라인메모리를 구비하여 구성된 것을 특징으로 하는 액정 표시장치의 전자파 장해 저감 장치.

### 청구항 5

제1항에 있어서, 데이터 구동부는 상기 타이밍 콘트롤러에서 RGB 데이터의 리드 클럭신호가 줄어드는 것에 대응하여, RGB 데이터의 래치 회수를 증가시키게 구성된 것을 특징으로 하는 액정표시장치의 전자파 장해 저감 장치.

## 명세서

### 발명의 상세한 설명

#### 기술분야

<1> 본 발명은 액정표시장치의 구동기술에 관한 것으로, 특히 고주파수의 데이터 리드 클럭신호에 의한 전자파 장해(EMI)를 저감하는데 적당하도록 한 액정표시장치의 전자파 장해 저감 장치에 관한 것이다.

#### 배경기술

<2> 최근, 정보기술(IT)의 발달에 따라 평판표시장치는 시각정보 전달매체로서 그 중요성이 한층 강조되고 있으며, 향후 보다 향상된 경쟁력을 확보하기 위해 저소비전력화, 박형화, 경량화, 고화질화 등이 요구되고 있다.

<3> 평판표시장치의 대표적인 표시장치인 액정표시장치(LCD: Liquid Crystal Display)는 액정의 광학적 이방성을 이용하여 화상을 표시하는 장치로서, 박형, 소형, 저소비전력 및 고화질 등의 장점이 있다.

<4> 이와 같은 액정 표시장치는 매트릭스(matrix) 형태로 배열된 화소들에 화상정보를 개별적으로 공급하여, 그 화소들의 광투과율을 조절함으로써, 원하는 화상을 표시할 수 있도록 한 표시장치이다. 따라서, 액정 표시장치는 화상을 구현하는 최소 단위인 화소들이 액티브 매트릭스 형태로 배열되는 액정 패널과, 상기 액정 패널을 구동하기 위한 구동부를 구비한다. 그리고, 상기 액정표시장치는 스스로 발광하지 못하기 때문에 액정표시장치에 광을 공급하는 백라이트 유닛이 구비된다. 상기 구동부는 타이밍 콘트롤러를 비롯하여 데이터 구동부와 게이트 구동부를 구비한다.

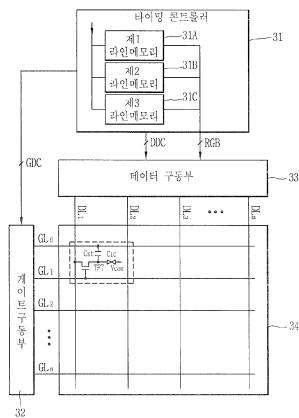

- <5> 도 1은 종래 기술에 의한 액정표시장치의 블록도로서 이에 도시한 바와 같이, 게이트 구동부(12) 및 데이터 구동부(13)의 구동을 제어하기 위한 게이트 제어신호(GDC) 및 데이터 제어신호(DDC)를 출력함과 아울러, 디지털 비디오 데이터(RGB)를 샘플링한 후에 재정렬하여 출력하는 타이밍 콘트롤러(11)와; 액정 패널(14)의 각 게이트 라인(GL<sub>1</sub>~GL<sub>n</sub>)에 게이트펄스를 공급하는 게이트 구동부(12)와; 상기 액정 패널(14)의 각 데이터라인(DL<sub>1</sub>~DL<sub>m</sub>)에 화소신호를 공급하는 데이터 구동부(13)와; 상기 게이트펄스와 화소신호에 의해 구동되는 액정셀들을 매트릭스 형태로 구비하여 화상을 표시하는 액정패널(14)로 구성된 것으로, 이의 작용을 설명하면 다음과 같다.

- <6> 타이밍 콘트롤러(11)는 시스템으로부터 공급되는 수직/수평 동기신호와 클럭신호를 이용하여 게이트 구동부(12)를 제어하기 위한 게이트 제어신호(GDC)와 데이터 구동부(13)를 제어하기 위한 데이터 제어신호(DDC)를 출력한다. 또한, 상기 타이밍 콘트롤러(11)는 상기 시스템으로부터 입력되는 데이터(RGB)를 샘플링한 후 이를 재정렬하여 데이터 구동부(13)에 공급한다.

- <7> 게이트 구동부(12)는 상기 타이밍 콘트롤러(11)로부터 입력되는 게이트 제어신호(GDC)에 응답하여 게이트라인(GL<sub>1</sub>~GL<sub>n</sub>)에 게이트펄스를 순차적으로 공급하고, 이에 의해 액정패널(14)의 각 게이트라인 상에 형성되어 각 화소신호를 단속하는 박막트랜지스터(TFT)가 터온된다.

- <8> 데이터 구동부(13)는 상기 타이밍 콘트롤러(11)로부터 입력되는 데이터 제어신호(DDC)에 응답하여 디지털 데이터(RGB)를 계조값에 대응하는 아날로그의 화소신호(데이터신호 또는 데이터전압)로 변환하고, 이렇게 변환된 화소신호가 데이터라인(DL<sub>1</sub>~DL<sub>m</sub>)과 상기 박막트랜지스터(TFT)들을 통해 해당 화소의 스토리지 캐퍼시터(C<sub>ST</sub>)에 전달되어 1 프레임 동안 유지된다.

- <9> 액정패널(14)은 데이터라인(DL<sub>1</sub>~DL<sub>m</sub>)과 게이트라인(GL<sub>1</sub>~GL<sub>n</sub>)의 교차부마다 형성된 다수의 액정셀(C<sub>LC</sub>)을 구비하는데, 이 다수의 액정셀(C<sub>LC</sub>)들이 상기 스토리지 캐퍼시터(C<sub>ST</sub>)에 저장된 전압에 의해 구동되어 목적한 화상을 표시할 수 있게 된다.

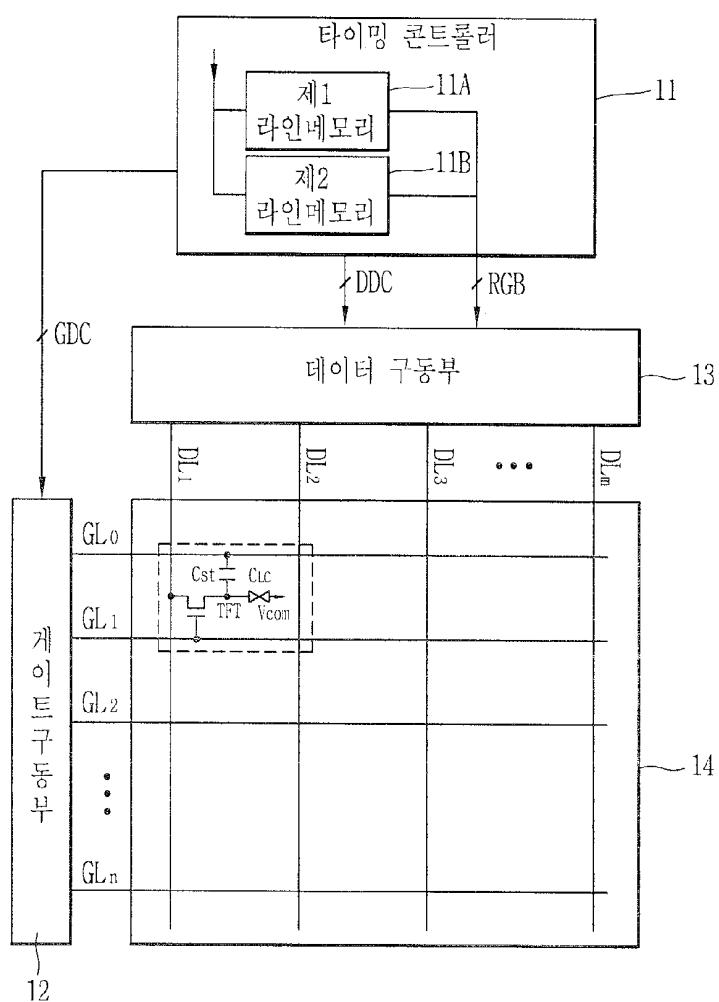

- <10> 한편, 상기 타이밍 콘트롤러(11)는 상기 시스템으로부터 입력되는 RGB 데이터를 두 개의 라인메모리(11A), (11B)를 이용하여 상기 액정패널(14)의 수평라인 단위로 출력하게 되는데, 도 2는 그에 따른 각 신호의 타이밍도를 나타낸 것이다.

- <11> 즉, 데이터인에이블신호(DE)를 기준으로 첫 번째 주기(T1)의 '로우' 구간에서 제1라인메모리(11A)에 저장된 1 수평라인 분량의 RGB 데이터를 리드(Read)하고, 두 번째 주기(T2)의 '하이' 구간에서는 다음의 1 수평라인 분량의 RGB 데이터를 제2라인메모리(11B)에 라이트(Write)한다.

- <12> 그리고, 두 번째 주기(T2)의 '로우' 구간이 시작되는 시점에서 게이트라인(GL1)에 게이트펄스(G1)가 출력된다. 이와 거의 동시에 소스아웃인에이블신호(SOE)가 출력되는데 이의 폴링 엣지(falling edge)에 동기하여, 상기 제1라인메모리(11A)로부터 리드한 1 수평라인 분량의 RGB 데이터를 데이터 구동부(13)에 출력한다.

- <13> 이와 함께, 상기 두 번째 주기(T2)의 '로우' 구간에서 상기 제2라인메모리(11B)로부터 1 수평라인 분량의 RGB 데이터를 리드하고, 세 번째 주기(T3)의 '하이' 구간에서는 다음의 1 수평라인 분량의 RGB 데이터를 제1라인메모리(11A)에 라이트한다.

- <14> 그리고, 세 번째 주기(T3)의 '로우' 구간이 시작되는 시점에서 게이트라인(GL2)에 게이트펄스(G2)가 출력된다. 이와 거의 동시에 소스아웃인에이블신호(SOE)가 출력되는데 이의 폴링 엣지에 동기하여, 상기 제2라인메모리(11B)로부터 리드한 1 수평라인 분량의 RGB 데이터를 데이터 구동부(13)에 출력한다.

- <15> 이후에도 순차적으로 입력되는 1 수평라인 분량의 RGB 데이터를 상기와 같이 제1,2라인메모리(11A), (11B)에 교번되게 리드/라이트하면서 해당 시점에서 그 리드한 RGB 데이터를 데이터 구동부(13)에 출력한다.

- <16> 이와 같이 종래의 액정표시장치에 있어서는 타이밍 콘트롤러에 두 개의 라인메모리를 구비하여 순차적으로 입력되는 1 수평라인 분량의 RGB 데이터를 교번되게 리드/라이트하면서 해당 시점에서 그 리드한 RGB 데이터를 데이터 구동부에 출력하게 되어 있으므로, 이때의 리드 클럭신호의 주파수가 비교적 높아 전자파 장해를 많이 유발시키는 문제점이 있었다.

## 발명의 내용

### 해결 하고자하는 과제

<17> 따라서, 본 발명의 목적은 타이밍 콘트롤러에 라인메모리를 추가하고 이를 이용하여 데이터 리드 클럭신호의 주파수를 낮추어 전자파 장해(EMI: Electro Magnetic Interference)가 줄어들도록 하는데 있다.

### 과제 해결수단

<18> 상기와 같은 목적을 달성하기 위한 본 발명은, 시스템으로부터 입력되는 RGB 데이터를 데이터구동부에 출력하기 위하여, 라인메모리를 추가로 구비하고, 추가된 라인메모리의 개수에 상응되게 RGB 데이터의 리드 클럭신호의 주파수를 낮추는 타이밍 콘트롤러와; 액정 패널의 각 게이트라인에 게이트펄스를 공급하는 게이트 구동부와; 상기 타이밍 콘트롤러로부터 입력되는 RGB 데이터에 대응하여, 상기 액정 패널의 각 데이터라인에 화소신호를 공급하는 데이터 구동부를 포함하여 구성함을 특징으로 한다.

### 효과

<19> 본 발명은 타이밍 콘트롤러에 라인메모리를 추가하고 이를 이용하여 RGB 데이터의 리드 클럭신호의 주파수를 낮추어 줌으로써, 별다른 추가비용 없이 전자파 장해를 줄일 수 있는 효과가 있다.

### 발명의 실시를 위한 구체적인 내용

<20> 이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시예를 상세히 설명하면 다음과 같다.

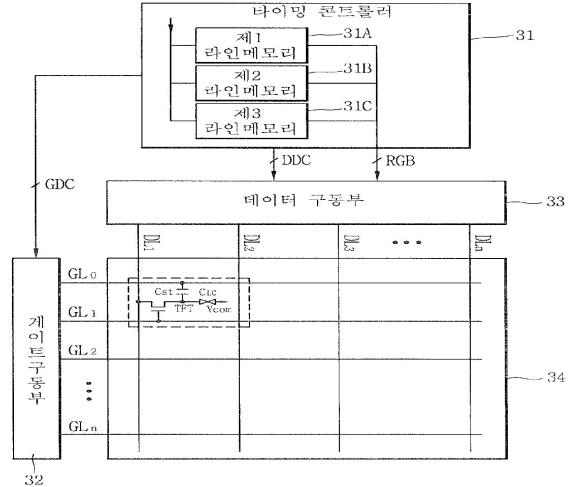

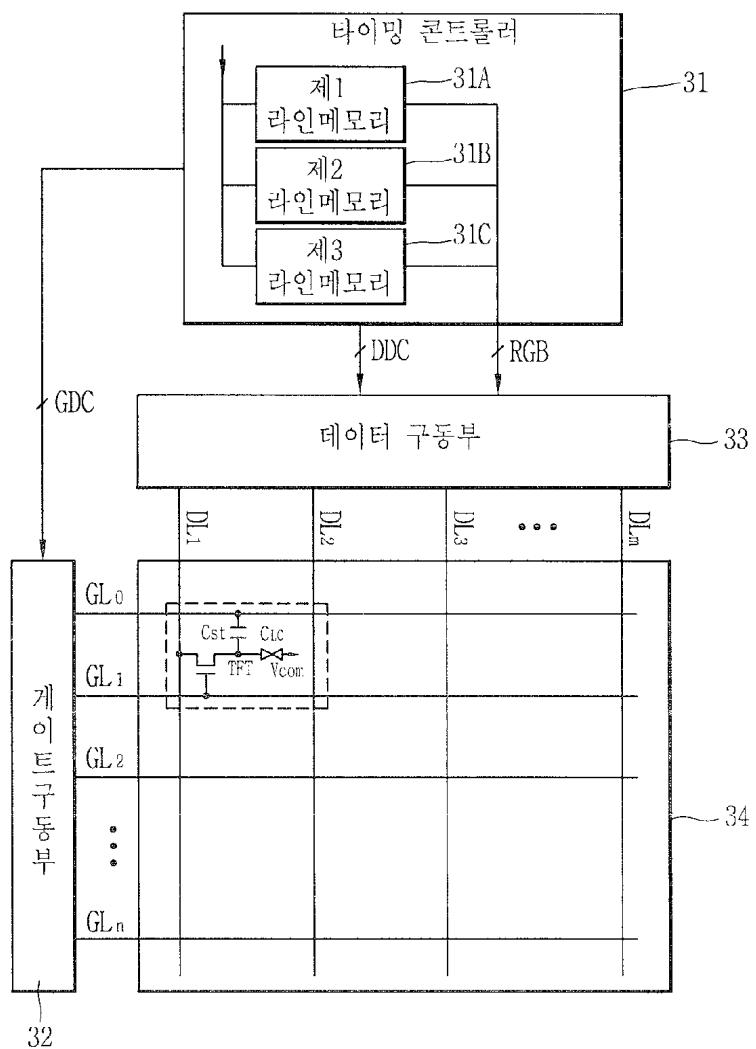

<21> 도 4는 본 발명에 의한 액정표시장치의 휘도 보상 장치의 일실시 구현예를 보인 블록도로서 이에 도시한 바와 같이, 시스템으로부터 입력되는 RGB 데이터를 샘플링한 후 재정렬하여 출력함에 있어서, 라인메모리를 추가로 구비하고 이를 이용하여 RGB 데이터의 리드 클럭신호의 주파수를 낮추는 타이밍 콘트롤러(31)와; 상기 타이밍 콘트롤러(31)로부터 입력되는 게이트 제어신호(GDC)에 응답하여, 액정 패널(34)의 각 게이트라인(GL<sub>1</sub>~GL<sub>n</sub>)에 게이트펄스를 공급하는 게이트 구동부(32)와; 상기 타이밍 콘트롤러(31)로부터 입력되는 데이터 제어신호(DDC)에 응답하여, 상기 액정 패널(34)의 각 데이터라인(DL<sub>1</sub>~DL<sub>m</sub>)에 화소신호를 공급하는 데이터 구동부(33)와; 상기 게이트펄스와 화소신호에 의해 구동되는 액정셀들이 매트릭스 형태로 배열되어 화상을 표시하는 액정패널(34)로 구성한다.

<22> 이와 같이 구성한 본 발명의 작용을 첨부한 도 5 및 도 6을 참조하여 상세히 설명하면 다음과 같다.

<23> 타이밍 콘트롤러(31)는 시스템으로부터 공급되는 수직/수평 동기신호와 클럭신호를 이용하여 게이트 구동부(32)를 제어하기 위한 게이트 제어신호(GDC)와 데이터 구동부(33)를 제어하기 위한 데이터 제어신호(DDC)를 출력한다. 상기 게이트 제어신호(GDC)의 예로써, 게이트 스타트 펄스(GSP), 게이트 시프트 클럭(GSC), 게이트 아웃 인에이블(GOE) 등이 있고, 데이터 제어신호(DDC)의 예로써, 소스 스타트 펄스(SSP), 소스 시프트 클럭(SSC), 소스 아웃 인에이블(SOE), 극성신호(POL) 등이 있다. 또한, 상기 타이밍 콘트롤러(31)는 상기 시스템으로부터 입력되는 데이터(RGB)를 샘플링한 후 이를 재정렬하여 데이터 구동부(33)에 공급한다.

<24> 게이트 구동부(32)는 상기 타이밍 콘트롤러(31)로부터 입력되는 상기 게이트 제어신호(GSP,GSC,GOE)들에 응답하여 게이트라인(GL<sub>1</sub>~GL<sub>n</sub>)에 게이트펄스(스캔펄스 또는 게이트 온신호)를 순차적으로 공급하고, 이에 의해 게이트라인(GL<sub>1</sub>~GL<sub>n</sub>)에 접속된 박막트랜지스터(TFT)가 게이트라인 단위로 구동된다.

<25> 데이터 구동부(33)는 상기 타이밍 콘트롤러(31)로부터 입력되는 데이터 제어신호(SSP,SSC,SOE,POL)에 응답하여 수평 주기마다 한 라인분씩의 화소신호(데이터신호 또는 데이터전압)를 액정패널(34)상의 데이터라인(DL<sub>1</sub>~DL<sub>m</sub>)에 공급한다.

<26> 액정패널(34)은 매트릭스 형태로 배열된 액정셀(CLc)들과 상기 게이트라인(GL<sub>1</sub>~GL<sub>n</sub>)과 데이터라인(DL<sub>1</sub>~DL<sub>m</sub>)의 교차부마다 형성되어 액정셀들 각각과 접속된 박막트랜지스터(TFT)를 구비한다.

<27> 상기 박막트랜지스터(TFT)는 게이트라인(GL)으로부터 게이트펄스 즉, 게이트 하이 전압(VGH)이 공급될 때 턴온되어 데이터라인(DL)을 통해 공급되는 화소신호를 액정셀에 전달한다. 그리고, 상기 박막트랜지스터(TFT)는 게이트라인(GL)을 통해 게이트 로우 전압(VGL)이 공급될 때 턴오프되어 액정셀에 충전된 화소신호가 유지되게 한다.

<28> 상기 액정셀은 등가적으로 액정 용량 캐패시터(CLc)로 표현되며, 액정을 사이에 두고 대면하는 공통 전극과 박막트랜지스터(TFT)에 접속된 화소전극을 포함한다. 그리고, 상기 액정셀은 충전된 화소 신호가 다음 화소 신호가 충전될 때까지 안정적으로 유지되게 하기 위하여 스토리지 캐패시터(Cst)를 더 구비한다. 상기 스토리지 캐패시터(Cst)는 화소전극과 이전단 게이트 라인 사이에 형성된다. 이러한 액정셀은 박막트랜지스터(TFT)를 통해

충전되는 화소 신호에 따라 유전 이방성을 가지는 액정의 배열 상태가 가변하여 광투과율을 조절함으로써 계조를 구현하게 된다.

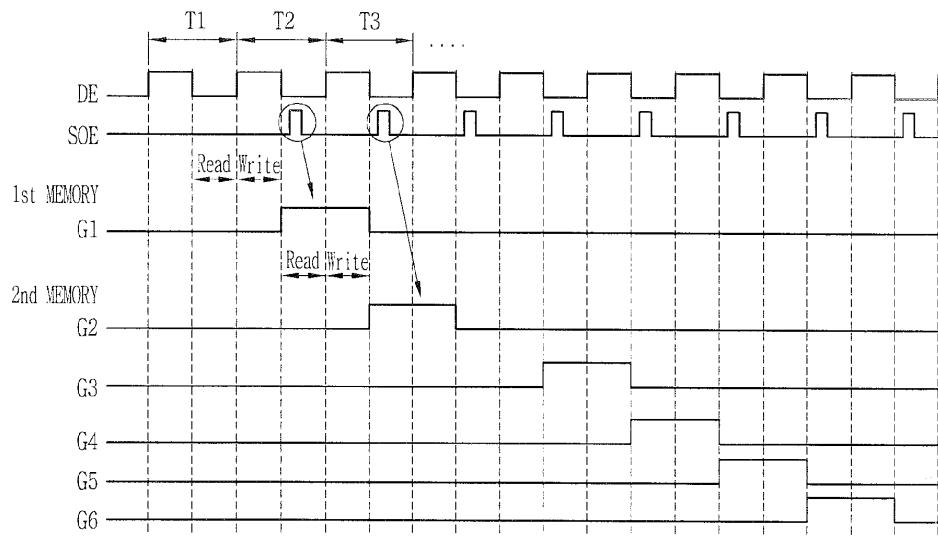

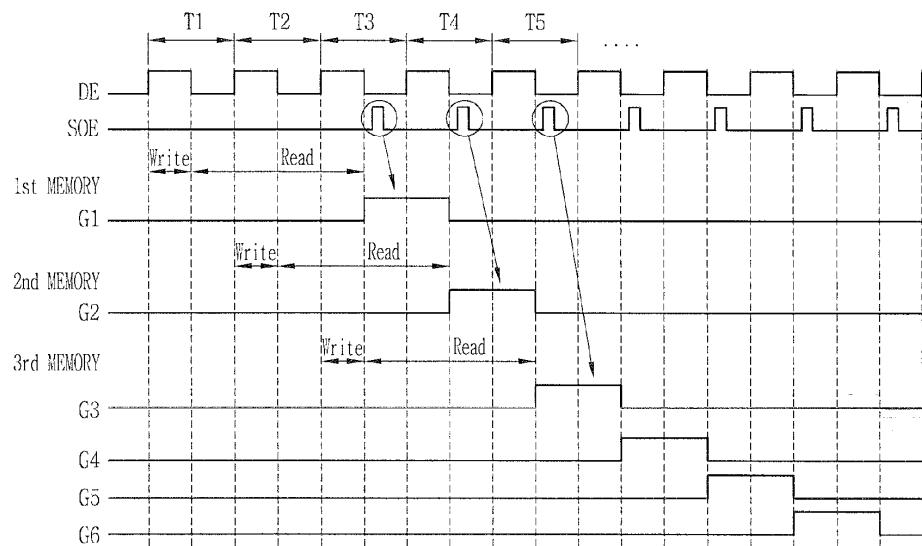

- <29> 한편, 상기 타이밍 콘트롤러(31)는 상기 시스템으로부터 입력되는 RGB 데이터를 세 개의 라인메모리(31A), (31B), (31C)를 이용하여 상기 액정패널(34)의 수평라인 단위로 출력하게 되는데, 도 4는 그에 따른 각 신호의 타이밍도를 나타낸 것이다.

- <30> 즉, 데이터인에이블신호(DE)를 기준으로 첫 번째 주기(T1)의 '하이' 구간에서 제1라인메모리(31A)에 1 수평라인 분량의 RGB 데이터를 라이트(Write)한 후 이로부터 2 주기(T1의 '로우' 구간~T3의 '하이' 구간까지) 동안 그 제1라인메모리(31A)에 라이트된 1 수평라인 분량의 RGB 데이터를 리드한다.

- <31> 그리고, 세 번째 주기(T3)의 '로우' 구간이 시작되는 시점에서 게이트라인(GL1)에 게이트펄스(G1)가 출력된다. 이와 거의 동시에 첫 번째의 소스아웃인에이블신호(SOE)가 출력되는데 이의 폴링 엣지(falling edge)에 동기하여, 상기 제1라인메모리(31A)로부터 리드한 1 수평라인 분량의 RGB 데이터를 데이터 구동부(33)에 출력한다.

- <32> 이와 마찬가지로, 상기 데이터인에이블신호(DE)를 기준으로 두 번째 주기(T2)의 '하이' 구간에서 제2라인메모리(31B)에 1 수평라인 분량의 RGB 데이터를 라이트한 후 이로부터 2 주기(T2의 '로우' 구간~T4의 '하이' 구간까지) 동안 그 제2라인메모리(31B)에 라이트된 1 수평라인 분량의 RGB 데이터를 리드한다.

- <33> 그리고, 네 번째 주기(T3)의 '로우' 구간이 시작되는 시점에서 게이트라인(GL2)에 게이트펄스(G2)가 출력된다. 이와 거의 동시에 두 번째의 소스아웃인에이블신호(SOE)가 출력되는데 이의 폴링 엣지에 동기하여, 상기 제2라인메모리(31B)로부터 리드한 1 수평라인 분량의 RGB 데이터를 데이터 구동부(33)에 출력한다.

- <34> 이와 마찬가지로, 상기 데이터인에이블신호(DE)를 기준으로 세 번째 주기(T3)의 '하이' 구간에서 제3라인메모리(31C)에 1 수평라인 분량의 RGB 데이터를 라이트한 후 이로부터 2 주기(T3의 '로우' 구간~T5의 '하이' 구간까지) 동안 그 제3라인메모리(31C)에 라이트된 1 수평라인 분량의 RGB 데이터를 리드한다.

- <35> 그리고, 다섯 번째 주기(T5)의 '로우' 구간이 시작되는 시점에서 게이트라인(GL3)에 게이트펄스(G3)가 출력된다. 이와 거의 동시에 세 번째의 소스아웃인에이블신호(SOE)가 출력되는데 이의 폴링 엣지에 동기하여, 상기 제3라인메모리(31C)로부터 리드한 1 수평라인 분량의 RGB 데이터를 데이터 구동부(33)에 출력한다.

- <36> 참고로, 상기 도 4에서 "1st MEMORY"는 상기 제1라인메모리(31A)를 의미하고, "2nd MEMORY"는 상기 제2라인메모리(31B)를 의미하고, "3rd MEMORY"는 상기 제3라인메모리(31C)를 의미한다.

- <37> 이후에도 순차적으로 입력되는 1 수평라인 분량의 RGB 데이터를 상기와 같이 제1,2,3라인메모리(31A), (31B), (31C)에 교번되게 리드/라이트하면서 해당 시점에서 그 리드한 RGB 데이터를 데이터 구동부(33)에 출력한다.

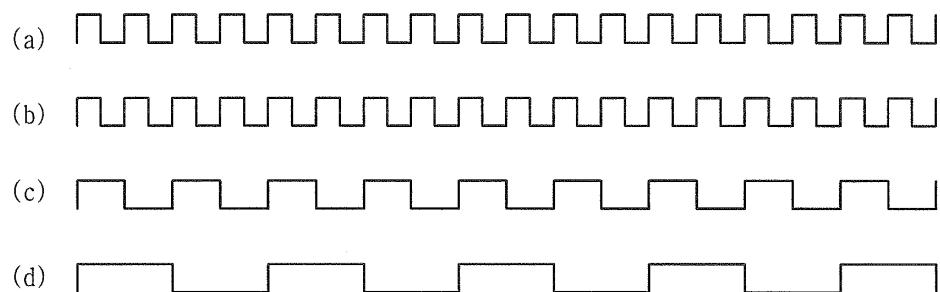

- <38> 이렇게 함으로써, 상기 제1,2,3라인메모리(31A), (31B), (31C)로부터 상기 RGB 데이터를 리드하기 위한 클럭신호의 주파수를 종래에 비하여 2배 이하로 낮출 수 있다. 즉, 도 5에서와 같이 타이밍 콘트롤러(31)에 입력되는 클럭신호가 도 5의 (a)와 같을 때, 상기 제1,2,3라인메모리(31A), (31B), (31C)에 RGB 데이터를 라이트하기 위한 클럭신호의 주파수가 도 5의 (b)와 같다. 즉, 상기 입력 클럭신호와 같이 라이트 클럭신호의 주파수는 서로 동일하다.

- <39> 그리고, 종래의 경우 제1,2라인메모리에서 RGB 데이터를 리드하는 클럭신호의 주파수가 데이터인에이블신호(DE)의 주파수와 동일하고, 상기 입력 클럭신호나 라이트 클럭신호의 주파수의 1/2에 해당된다.

- <40> 이에 비하여 본 발명의 경우 제1,2,3라인메모리(31A), (31B), (31C)에서 RGB 데이터를 리드하는 클럭신호의 주파수가 데이터인에이블신호(DE)의 주파수의 1/2에 해당되므로, 상기 입력 클럭신호나 라이트 클럭신호의 주파수의 1/4에 해당되고, 종래의 리드 클럭신호 주파수의 1/2에 해당된다.

- <41> 이와 같이 본 발명을 이용하는 경우 제1,2,3라인메모리(31A), (31B), (31C)에서 RGB 데이터를 리드하는 클럭신호의 주파수가 종래에 비하여 1/2에 불과하므로, 그만큼 전자파 장해를 줄일 수 있게 된다.

- <42> 물론, 이와 같은 경우 상기 타이밍 콘트롤러(31)에서 데이터 구동부(33)로 RGB 데이터가 전달되는 타이밍이 1/2로 줄어들게 되므로, 이에 대응하여 그 데이터 구동부(33)에서 한번의 래치 동작을 두 번으로 늘려야 한다.

- <43> 본 발명에 의해 상기 타이밍 콘트롤러(31)에 사용되는 라인메모리의 개수는 상기와 같이 3개로 한정되는 것이 아니라 필요에 따라 더 많이 사용될 수 있다.

<44> 만약, 상기 제1,2,3라인메모리(31A),(31B),(31C)를 더 추가하고 상기와 같은 방식으로 RGB 데이터를 라이트/리드하는 경우 리드 클럭신호의 주파수를 더 줄일 수 있게 되며, 이에 의해 전자파 장해가 더 줄어든다.

### 도면의 간단한 설명

<45> 도 1은 종래 기술에 의한 액정표시장치의 블록도.

<46> 도 2는 도 1의 각부에 적용되는 신호의 과정도.

<47> 도 3은 본 발명에 의한 액정표시장치의 전자파 장해 저감 장치의 블록도.

<48> 도 4는 도 3의 각부에 적용되는 신호의 과정도.

<49> 도 5의 (a)-(d)는 본 발명에 의한 RGB 데이터의 리드 클럭신호의 주파수를 상대적으로 보이기 위한 각종 클럭신호의 과정도.

<50> \*\*\*도면의 주요 부분에 대한 부호의 설명\*\*\*

<51> 31 : 타이밍 콘트롤러 31A-31C : 라인메모리

<52> 32 : 게이트 구동부 33 : 데이터 구동부

<53> 34 : 액정패널

### 도면

#### 도면1

## 도면2

## 도면3

**도면4****도면5**

|                |                                              |         |            |

|----------------|----------------------------------------------|---------|------------|

| 专利名称(译)        | 一种液晶显示装置的电磁干扰降低装置                            |         |            |

| 公开(公告)号        | KR1020090041255A                             | 公开(公告)日 | 2009-04-28 |

| 申请号            | KR1020070106863                              | 申请日     | 2007-10-23 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                     |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                    |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                    |         |            |

| [标]发明人         | LEE HWAN JOO<br>이한주<br>SHIN JUNG WOOK<br>신정욱 |         |            |

| 发明人            | 이한주<br>신정욱                                   |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                  |         |            |

| 代理人(译)         | PARK , JANG WON                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                    |         |            |

### 摘要(译)

本发明涉及一种用于在液晶显示器的定时控制器中处理RGB数据并将RGB数据输出到数据驱动器的过程中最小化由于高读取时钟信号引起的电磁波干扰的产生的技术。在本发明中，从外部输入的RGB数据被重新排列并输出到数据驱动器，行存储器被添加到两个基本行存储器，并且RGB数据的读取时钟信号对应于所添加的行存储器的数量。用于降低频率的定时控制器，用于向液晶面板的每条栅极线提供栅极脉冲的栅极驱动器和用于向与从时序控制器输入的RGB数据相对应地向液晶面板的每条数据线提供像素信号的数据驱动器它应。