(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0087508

(43) 공개일자 2008년10월01일

(51) Int. Cl.

G02F 1/133 (2006.01) G02F 1/1335 (2006.01)

(21) 출원번호 10-2007-0029851

(22) 출원일자 2007년03월27일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

김상규

경상북도 구미시 비산동 전원리빙필아파트 101동

1309호

(74) 대리인

박장원

전체 청구항 수 : 총 14 항

**(54) 액정표시장치****(57) 요 약**

본 발명은 화상구현시 신호지연을 방지하기 위하여 종래 60Hz의 프레임주파수 대비 픽셀의 차징 타임(charging time)을 증가시키고자 한 액정표시장치에 관한 것으로서, 그 구성은 다수개의 게이트 라인 및 데이터 라인이 종횡으로 교차되게 배열되어 화소영역을 정의하되, 상기 화소영역은 다수 개의 단위화소들로 구성된 제1 및 제2화소영역으로 분할하고, 상기 제1 및 제2화소영역 각각에 구비된 다수개의 단위화소에 연결되는 제1 및 제2데이터 라인을 구비하되, 상기 제2데이터 라인은 제2영역에 구비된 각 단위화소에 연결된 제1기판과; 상기 제1기판상의 게이트 라인 및 데이터 라인의 교차영역에 형성된 스위칭 소자와; 상기 제1기판상의 화소영역에 대응하여 형성된 화소 전극; 및 상기 제1기판상에 대향하여 배치되고, 블랙매트릭스 및 컬러필터가 형성된 제2기판을 포함하여 구성되는 것을 특징으로 한다.

**대 표 도** - 도4

## 특허청구의 범위

### 청구항 1

다수개의 게이트 라인 및 데이터 라인이 종횡으로 교차되게 배열되어 화소영역을 정의하되, 상기 화소영역은 다수개의 단위 화소들로 구성된 복수 개의 화소영역으로 분할하고, 상기 복수 개의 화소영역 각각에 구비된 다수 개의 단위화소에 연결되는 복수 개의 데이터 라인을 구비하되, 상기 복수 개의 데이터 라인 각각은 상기 복수 개의 화소영역 각각에 구비된 다수개의 단위화소에 연결된 제1기판;

상기 제1기판상의 게이트 라인 및 데이터 라인의 교차영역에 형성된 스위칭 소자;

상기 제1기판상의 화소 영역에 대응하여 형성된 화소 전극; 및

상기 제1기판상에 대향하여 배치되고, 블랙매트릭스 및 컬러필터가 형성된 제2기판을 포함하여 구성되는 것을 특징으로 하는 액정표시장치.

### 청구항 2

제1항에 있어서, 상기 다수 개의 단위화소들로 구성된 복수 개의 화소영역 각각은 서로 동일한 면적을 갖는 것을 특징으로 하는 액정표시장치.

### 청구항 3

제1항에 있어서, 상기 복수 개의 데이터 라인은 데이터가 유입되는 초기 화소영역에서 마지막 화소영역으로 갈 수록 그 데이터 라인의 개수가 점차 감소하여 형성되는 것을 특징으로 하는 액정표시장치.

### 청구항 4

제3항에 있어서, 상기 데이터가 유입되는 초기 화소영역에 형성된 복수 개의 데이터 라인은 복수 개의 화소영역 개수와 동일한 것을 특징으로 하는 액정표시장치.

### 청구항 5

제3항에 있어서, 상기 데이터가 유입되는 초기 화소영역에 형성된 복수 개의 데이터 라인 중 초기 화소영역의 스위칭소자에 근접하는 데이터 라인이 단위 화소에 전기적으로 접속하는 것을 특징으로 하는 액정표시장치.

### 청구항 6

제3항에 있어서, 상기 데이터가 유입되는 마지막 화소영역에 형성된 데이터 라인은 초기 화소영역의 스위칭소자에 가장 이격되어 형성된 데이터 라인이 연장되어 마지막 화소영역의 단위화소에 전기적으로 접속하는 것을 특징으로 하는 액정표시장치.

### 청구항 7

제1항에 있어서, 상기 복수 개로 분할되는 화소영역을 각각 관할하는 게이트 라인은 제1게이트 라인에 동시에 전압이 인가되어 제n번째 게이트 라인까지 순차적으로 전압이 인가되는 것을 특징으로 하는 액정표시장치.

### 청구항 8

제1항에 있어서, 상기 복수 개로 분할되는 화소영역에는 복수 개의 데이터 라인을 통해 외부로부터 데이터가 동시에 유입되는 것을 특징으로 하는 액정표시장치.

### 청구항 9

제1항에 있어서, 상기 제2기판상에는 공통전극이 형성되는 것을 특징으로 하는 액정표시장치.

### 청구항 10

다수개의 게이트 라인 및 데이터 라인이 종횡으로 교차되게 배열되어 화소영역을 정의하되, 상기 화소영역은 다수 개의 단위화소들로 구성된 제1 및 제2화소영역으로 분할하고, 상기 제1 및 제2화소영역 각각에 구비된 다수 개의 단위화소에 연결되는 제1 및 제2데이터 라인을 구비하되, 상기 제2데이터 라인은 제2영역에 구비된 각 단

위화소에 연결된 제1기판;

상기 제1기판상의 게이트 라인 및 데이터 라인의 교차영역에 형성된 스위칭 소자;

상기 제1기판상의 화소영역에 대응하여 형성된 화소 전극; 및

상기 제1기판상에 대향하여 배치되고, 블랙매트릭스 및 컬러필터가 형성된 제2기판을 포함하여 구성되는 것을 특징으로 하는 액정표시장치.

### 청구항 11

제10항에 있어서, 상기 제1 및 제2영역 각각의 전체 화소영역은 서로 동일한 면적을 갖는 것을 특징으로 하는 액정표시장치.

### 청구항 12

제10항에 있어서, 상기 제1 및 제2영역을 각각 관할하는 게이트 라인은 각각의 제1게이트 라인에 동시에 전압이 인가되어 제n번째 게이트 라인까지 순차적으로 전압이 인가되는 것을 특징으로 하는 액정표시장치.

### 청구항 13

제10항에 있어서, 상기 제1 및 제2영역의 단위화소에는 외부로부터 데이터가 동시에 유입되는 것을 특징으로 하는 액정표시장치.

### 청구항 14

제10항에 있어서, 상기 제2기판상에는 공통전극이 형성되는 것을 특징으로 하는 액정표시장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <15> 본 발명은 액정표시장치에 관한 것으로서, 더 자세하게는 고해상도 모델에 있어서 화상구현시 신호지연을 방지하기 위하여 종래의 프레임 주파수 대비 픽셀의 차징 타임(charging time)을 증가시키고자 한 액정표시장치에 관한 것이다.

- <16> 정보화 사회가 급진전함에 따라 대량의 정보를 처리하고 이를 표시하는 디스플레이(display) 분야가 나날이 발전해 가고 있다. 최근 들어서는 특히 박형화, 경량화, 저소비전력화 등의 시대상에 부응하기 위하여 평판표시장치(Flat Panel Display)의 필요성이 대두되었고, 이에 따라 색 재현성이 우수하고 박형인 박막트랜지스터 액정 표시장치에 초점이 맞추어져 있다.

- <17> 이러한 액정표시장치의 디스플레이 방법은 액정분자의 광학적 이방성과 분극성질을 이용하는데, 이는 액정분자의 구조가 가늘고 길며 그 배열에 있어서 방향성을 갖는 선경사각(pretilt angle)을 갖고 있기 때문에 인위적으로 액정에 전압을 인가하면 액정분자가 갖는 선경사각을 변화시켜 액정분자의 배열 방향을 제어할 수 있다.

- <18> 따라서, 액정표시장치는 액정층에 적절한 전압을 인가함으로써 그 액정분자의 배열 방향을 임의로 조절하여 액정의 분자배열을 변화시키고, 이러한 액정이 가지고 있는 광학적 이방성에 의하여 편광된 빛을 임의로 변조함으로써 원하는 화상정보를 표현한다.

- <19> 일반적인 액정표시장치를 이루는 기본적인 소자인 액정패널은 상부의 컬러필터기판과 하부의 어레이기판이 서로 대향하여 소정의 간격을 두고 이격되어 있고, 이러한 두 기판 사이에 액정분자를 포함하는 액정이 충진되어 있는 구조이다. 이때 이러한 액정에 전압을 인가하는 전극은 컬러필터기판에 위치하는 공통전극과 어레이기판에 위치하는 화소전극이 되고, 이러한 두 개의 전극에 전압이 인가되면 그 인가되는 전압의 차이에 의하여 형성되는 상하의 수직선 전기장이 그 사이에 위치하는 액정분자의 방향을 제어하는 방식이 사용된다.

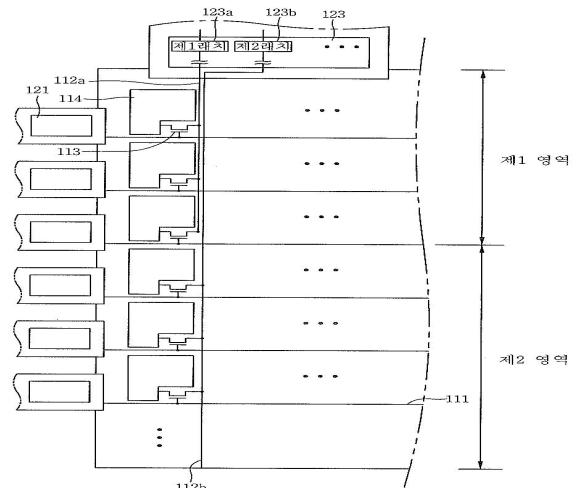

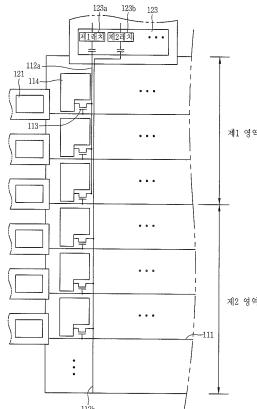

- <20> 이와 관련하여, 종래기술에 따른 액정표시장치에 대해 도 1을 참조하여 좀더 구체적으로 살펴보고자 한다.

- <21> 도 1은 종래기술에 따른 액정표시장치의 구조를 나타내는 도면이다.

- <22> 도 1을 참조하면, 박막트랜지스터 어레이기판(미도시)상에는 복수 개의 게이트 라인 및 데이터 라인(21, 22)이 서로 직교하여 형성되고, 그 게이트 라인 및 데이터 라인(21, 22)이 교차하는 교차부에는 화소전극(24)과 박막 트랜지스터(23)가 형성되어 있다.

- <23> 또한, 상기 박막 트랜지스터 어레이기판(미도시)상의 외곽으로 위치하는 게이트 라인 및 데이터 라인(21, 22)의 패드(미도시)에는 신호를 전달하기 위한 게이트 드라이브 IC 및 데이터 드라이브 IC(25, 26)가 전기적으로 접속하게 된다.

- <24> 이때 보통 게이트 드라이브 IC 및 데이터 드라이브 IC(25, 26)는 연성회로기판(flexible printed circuit board; FPCB)(27)상에 실장되어 게이트 라인 및 데이터 라인(21, 22)과 접속하게 된다.

- <25> 그러나 최근 들어 고해상도 모델(QSXGA: 2560×2048)의 경우에 있어서 어레이기판과 이에 합착되는 컬러필터기판 사이에 액정 적하시 수반되는 기타 요인들에 의하여 부득이하게 종래와 같이 게이트 및 데이터 드라이브 IC(25, 26)를 액정패널의 일측에 구성하는 싱글뱅크 방식을 사용하게 된다.

- <26> 이때 고해상도 모델(QSXGA: 2560×2048)의 프레임 주파수를 종래와 같이 60Hz로 구동하여 화상을 구현하게 되면 단위 화소당 화소 전압의 차징 타임이  $7.5\mu s$ 로서 정상 규격인  $10\mu s$ 를 만족하지 못하게 되고 그 결과 블랙 및 화이트와 같은 색 구현이 불가능하게 됨으로써 정상적인 색상을 갖는 화상을 구현할 수 없게 된다.

- <27> 반면, 이를 만족하기 위하여 프레임 주파수를 30Hz로 구동하여 화상을 구현하게 되는 경우에는 낮은 동작주파수로 인하여 화면에 플리커(flicker) 현상이 나타나게 된다.

### 발명이 이루고자 하는 기술적 과제

- <28> 따라서, 본 발명은 이와 같은 종래기술의 제반 문제점을 개선하기 위하여 안출한 것으로서, 복 발명의 목적은 복수 개의 데이터 드라이브 IC가 액정패널의 일측에 하나의 수평 라인을 이루어 구성되는 싱글뱅크 구조로서, 외부로부터 유입되는 화상 신호를 신호지연 없이 빠르게 구현할 수 있는 액정표시장치를 제공함에 있다.

### 발명의 구성 및 작용

- <29> 상기 목적을 달성하기 위한 본 발명에 따른 액정표시장치는 다수개의 게이트 라인 및 데이터 라인이 종횡으로 교차되게 배열되어 화소영역을 정의하되, 상기 화소영역은 다수개의 단위 화소들로 구성된 복수 개의 화소영역으로 분할하고, 상기 복수 개의 화소영역 각각에 구비된 다수개의 단위화소에 연결되는 복수 개의 데이터 라인을 구비하되, 상기 복수 개의 데이터 라인 각각은 상기 복수 개의 화소영역 각각에 구비된 다수개의 단위화소에 연결된 제1기판과; 상기 제1기판상의 게이트 라인 및 데이터 라인의 교차영역에 형성된 스위칭 소자와; 상기 제1기판상의 화소 영역에 대응하여 형성된 화소 전극; 및 상기 제1기판상에 대향하여 배치되고, 블랙매트릭스 및 컬러필터가 형성된 제2기판을 포함하여 구성되는 것을 특징으로 한다.

- <30> 상기 목적을 달성하기 위한 본 발명에 따른 액정표시장치는 다수개의 게이트 라인 및 데이터 라인이 종횡으로 교차되게 배열되어 화소영역을 정의하되, 상기 화소영역은 다수 개의 단위화소들로 구성된 제1 및 제2화소영역으로 분할하고, 상기 제1 및 제2화소영역 각각에 구비된 다수개의 단위화소에 연결되는 제1 및 제2데이터 라인을 구비하되, 상기 제2데이터 라인은 제2영역에 구비된 각 단위화소에 연결된 제1기판과; 상기 제1기판상의 게이트 라인 및 데이터 라인의 교차영역에 형성된 스위칭 소자와; 상기 제1기판상의 화소영역에 대응하여 형성된 화소 전극; 및 상기 제1기판상에 대향하여 배치되고, 블랙매트릭스 및 컬러필터가 형성된 제2기판을 포함하여 구성되는 것을 특징으로 한다.

- <31> 이하, 본 발명에 따른 액정표시장치에 대해 첨부된 도면을 참조하여 상세히 설명한다.

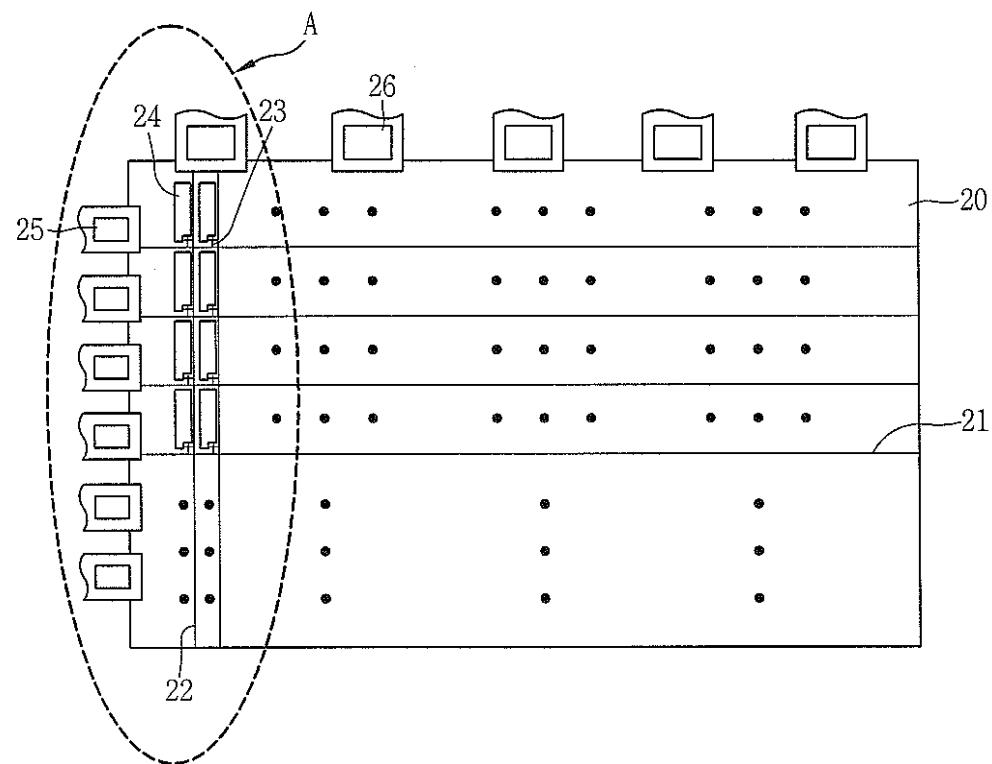

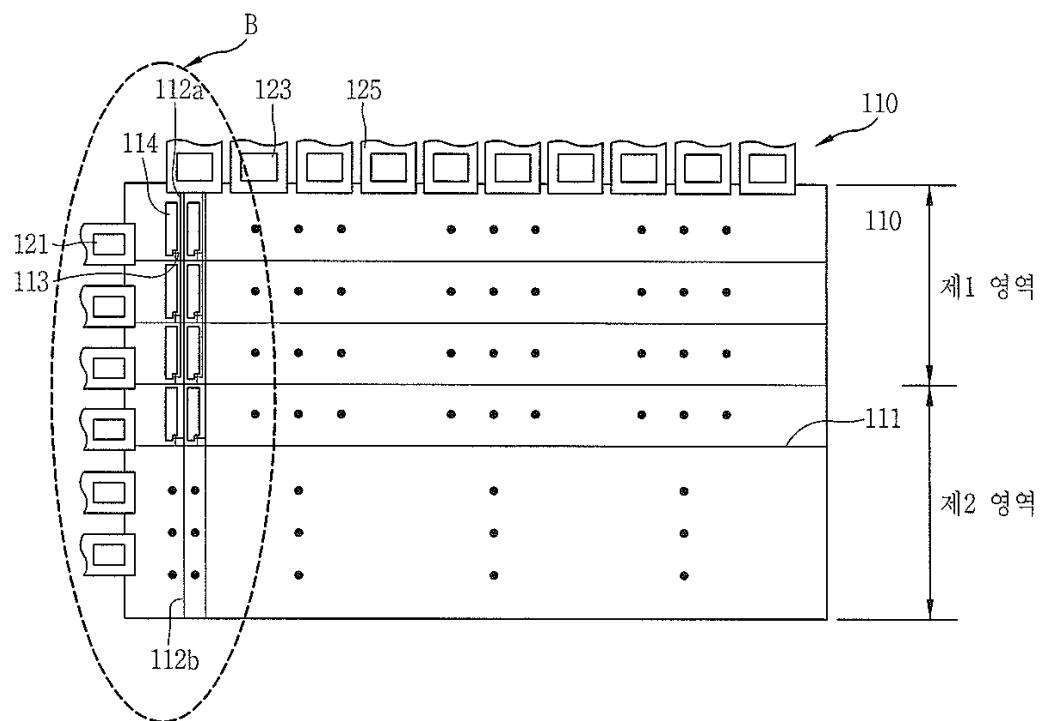

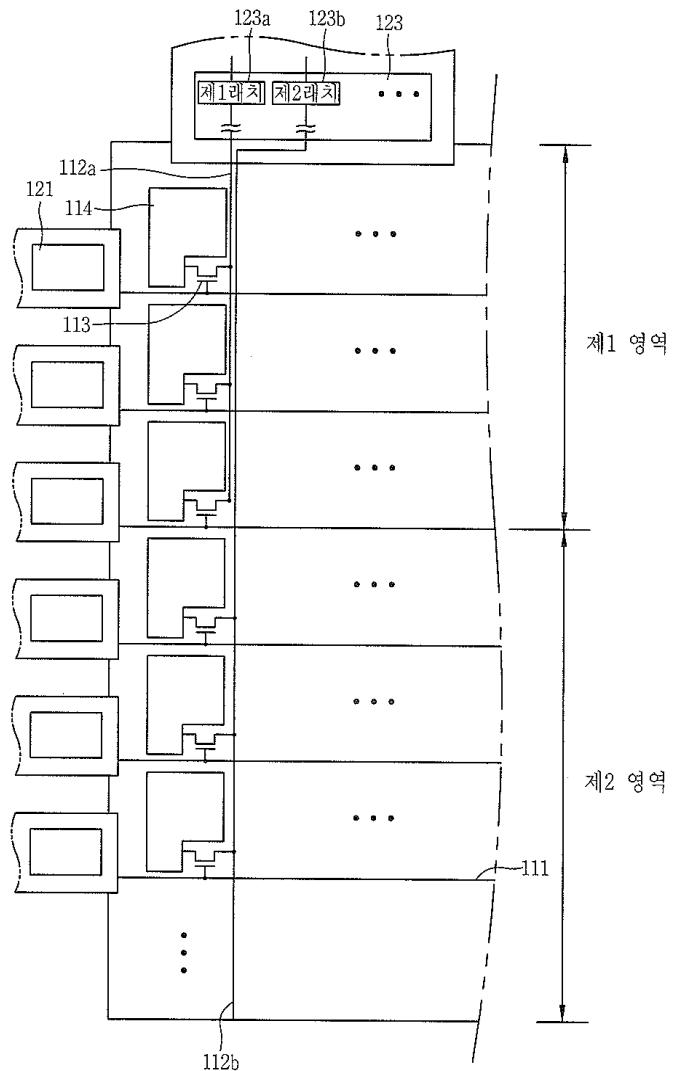

- <32> 도 3은 본 발명에 따른 액정표시장치의 구조를 나타내는 도면이다.

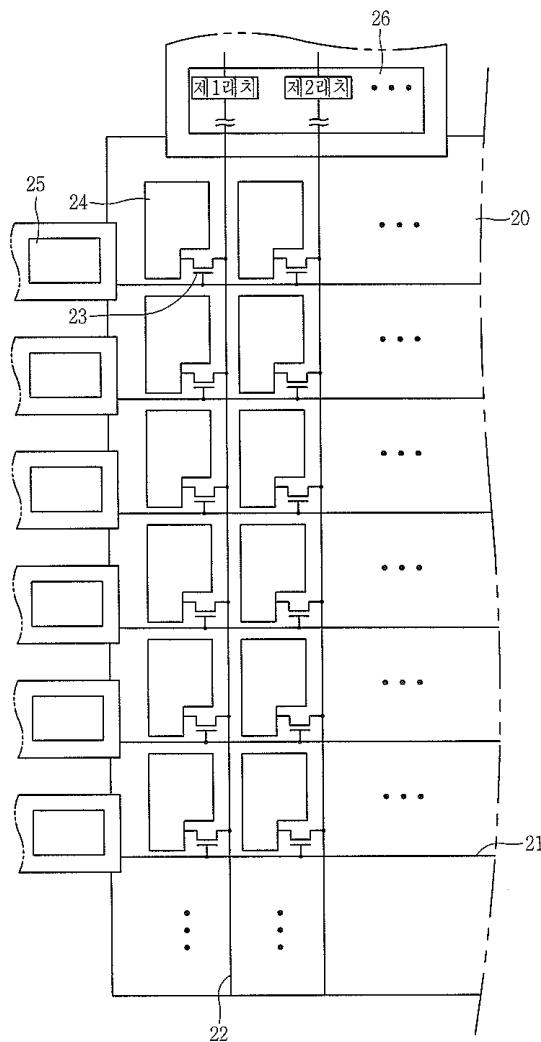

- <33> 도 4는 도 3의 "B"부의 확대평면도로서, 각 단위화소영역에 연결된 데이터 라인의 확대평면도이다.

- <34> 본 발명에 따른 액정표시패널(110)은 도면에 도시하지 않았지만, 상부의 컬러필터기판(미도시)과 하부의 어레이 기판(미도시)이 서로 대향하여 소정의 간격을 두고 이격되어 있고, 이러한 두 기판 사이에 액정분자를 포함하는 액정이 충진되어 있는 구조로 구성되어 있다.

- <35> 또한, 액정에 전압을 인가하는 전극으로는 컬러필터기판에 형성된 공통전극(미도시)과 어레이기판에 형성된 화

소전극(미도시)이 있다.

- <36> 이러한 두 개의 전극에 전압이 인가되면, 그 인가되는 전압의 차이에 의하여 형성되는 상하의 수직선 전기장이 그 사이에 위치하는 액정분자의 방향을 제어하는 방식이 사용된다.

- <37> 도 3 및 도 4를 참조하면, 본 발명에 따른 액정패널(110)은 화상영역을 상단부의 화면을 관할하는 제1영역과 하단부의 화면을 관할하는 제2영역으로 나누어 영상을 구현하게 된다.

- <38> 이러한 영상구현은 액정패널(110)상에 형성되어 제1영역 및 제2영역을 관할하는 서로 다른 데이터 라인(112a, 112b)에 의하여 영향을 받는다.

- <39> 이는 다시 말해 도 3에 도시된 바와 같이 액정패널(110)이 예를 들어 고해상도 모델(QSXGA: 2560×2048)이라 가정할 때 데이터 드라이브 IC(123)로부터 데이터가 출력되는 부위를 시작으로 하여 상위 1024개의 게이트 라인(111)에 해당하는 영역이 제1영역이 되고, 그 제1영역에 연이은 하위 1024개의 게이트 라인(111)을 관할하는 영역이 제2영역이 된다.

- <40> 이때 상기 제1영역 및 제2영역 각각은 제1번째 내지 제n번째의 동일 개수의 게이트 라인을 관할하므로 전체 화소 영역은 서로 동일 면적을 갖는다.

- <41> 이와 더불어 두 영역의 화소 전극은 각각 서로 다른 데이터 라인(112a, 112b)에 관여한다.

- <42> 즉, 상기 액정패널(110)의 제1영역상에는 단위화소영역간 데이터 드라이브 IC(123)와 전기적으로 접속하는 제1데이터 라인(112a) 및 제2데이터 라인(112b)이 형성되지만, 제1영역의 화소 전극(114)은 그 중 제1영역의 스위칭소자에 근접하는 제1데이터 라인(112a)으로부터 화소 전압을 인가받는다.

- <43> 그리고, 상기 액정패널(110)의 제2영역상에는 단위화소영역간 제1데이터 라인(112a) 및 제2데이터 라인(112b) 중 제2데이터 라인(112b)이 연장되어 형성되고 그 제2데이터 라인(112b)이 제2영역의 화소 전극(114)에 관여하게 된다.

- <44> 즉 상기 제2데이터 라인(112b)으로부터의 화소 전압이 제2영역의 화소 전극(114)으로 인가된다.

- <45> 물론 이와 같은 액정패널(110)은 그 일측 가장자리영역으로 싱글 뱅크 형태로 구성되는 게이트 드라이브 IC 및 데이터 드라이브 IC(121, 121)로부터 제어신호 및 데이터를 입력받기 위한 전기적 접속이 필요하다.

- <46> 즉, 액정패널(110)상의 게이트 라인(111)의 패드부에는 신호를 전달하기 위한 게이트 드라이브 IC(121)가 전기적으로 접속하여 구성되고, 또한 액정패널(110)상의 제1데이터 라인 및 제2데이터 라인(112a, 112b)의 패드부에 신호를 전달하는 데이터 드라이브 IC(123)가 전기적으로 접속하여 구성된다.

- <47> 이때 게이트 드라이브 IC 및 데이터 드라이브 IC(121, 123)는 연성회로기판(flexible printed circuit board; FPCB)(125)상에 실장되어 게이트 라인(111) 및 데이터 라인(112a, 112b)과 각각 접속하게 된다.

- <48> 물론 이러한 게이트 드라이브 IC 및 데이터 드라이브 IC(121, 123)는 도면에 별도로 나타내지 않은 타이밍 컨트롤러로부터 적(R), 녹(G), 청(B) 데이터 및 제어신호를 전달받아 동작하게 된다.

- <49> 그러면, 본 발명에 따른 싱글 뱅크 구조의 액정표시장치를 적용해 화상이 구현되는 과정을 설명하면 다음과 같다.

- <50> 도면에 도시된 바와 같이, 먼저 게이트 드라이브 IC 및 데이터 드라이브 IC(121, 123)는 타이밍 컨트롤러(미도시)에 의하여 제어된다. 여기에서 타이밍 컨트롤러(미도시)는 외부로부터 적(R), 녹(G), 청(B) (영상)데이터 및 수직/수평 동기신호를 인가받아 그 R, G, B 데이터를 재정렬하고, 새로운 제어신호를 생성하게 된다.

- <51> 이때 R, G, B 데이터는 홀수(odd) 및 짝수(even frame) 단위로 구분되어 타이밍 컨트롤러(미도시)와 연동하는 프레임 메모리(미도시)에 저장되고, 타이밍 컨트롤러(미도시)는 이 프레임 메모리(미도시)로부터 액정패널(110)의 제1데이터 라인(112a)을 통해 제1영역에 구현되는 영상 데이터와 액정패널(110)의 제2데이터 라인(112b)을 통해 제2영역에 구현되는 영상 데이터를 읽어내어 데이터 드라이브 IC(123) 내의 제1래치(123a), 제3래치(미도시)와 같은 홀수번재 래치 및 제2래치(123b), 제4래치(미도시)와 같은 짝수번재 래치에 교번(交番)하여 저장하게 된다.

- <52> 그리고 상기 게이트 드라이브 IC(121)는 외부의 전원전압생성부(미도시)로부터 게이트 로우(Low) 및 하이(High) 전압을 인가받아 타이밍 컨트롤러(미도시)로부터의 제어신호에 따라 게이트 라인(111)에 게이트 전압을 인가하

게 된다.

- <53> 이때 상기 액정패널(110)의 제1영역 및 제2영역을 각각 관할하는 제1번째 게이트 라인(111)에 동시에 게이트 전압이 인가되어 순차적으로 제n번째 게이트 라인(111)에까지 전압이 이르게 된다.

- <54> 예를 들어 고해상도 모델(QSXGA: 2560×2048)의 경우, 액정패널의 제1영역을 관할하는 제1번째 게이트 라인(121)과 제2영역을 관할하는 제1025번째 게이트 라인(121)에 동시에 게이트 전압이 인가되어 제1영역의 제1024 번째 게이트 라인(111)과 제2영역의 제2048번째 게이트 라인(111)에 이르기까지 게이트 전압이 각각 순차적으로 인가되는 것은 미루어 짐작할 수 있다.

- <55> 이와 같이 2개의 게이트 라인(111)에 동시에 게이트 전압이 인가되고 나면, 이어서는 타이밍 컨트롤러(미도시)로부터의 제어신호에 따라 데이터 드라이브 IC(123) 내의 제1래치(123a) 및 제2래치(123b)에 저장되어 있던 화소 전압이 단위화소영역을 지나는 제1데이터 라인(112a) 및 제2데이터 라인(112b)으로 각각 출력된다.

- <56> 이는 다시 말해, 상기 제1데이터 라인(112a)을 통해서는 액정패널(110)의 제1영역의 제1수평 라인을 시작으로 하여 화상이 구현되고, 제2데이터 라인(112b)을 통해서는 액정패널의 제2영역의 제1수평 라인을 시작으로 하여 화상이 구현됨으로써 그 결과 제1영역과 제2영역의 화상은 서로 일체화되어 구현된다.

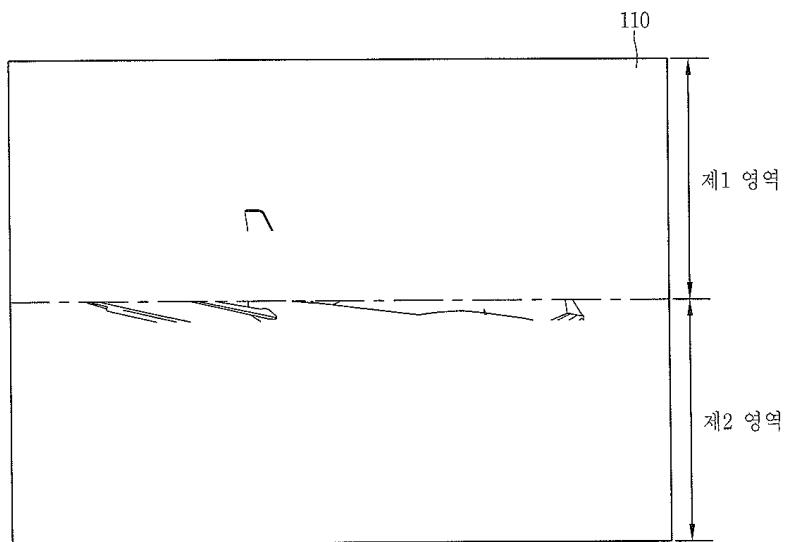

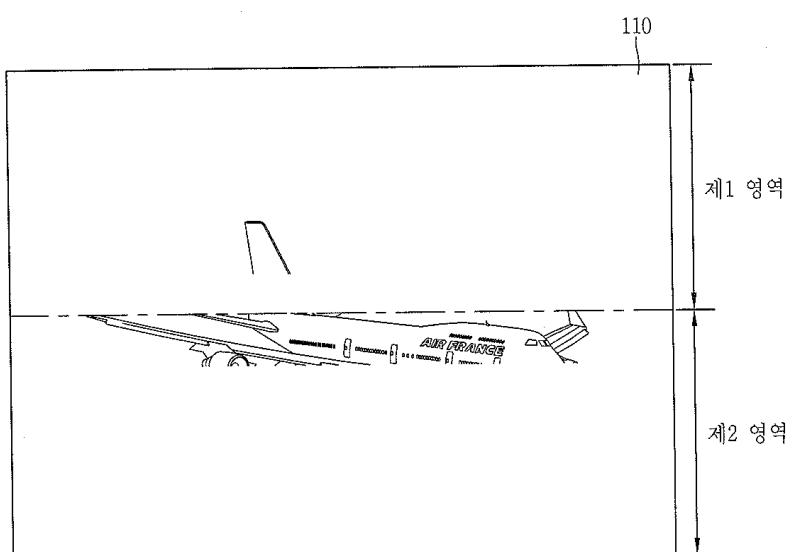

- <57> 이와 관련해 첨부된 도 5a 내지 도 5c를 함께 참조하여 좀더 구체적으로 살펴보면 다음과 같다.

- <58> 도 5a 내지 도 5c는 도 3에 나타낸 액정표시패널(110)에 화상이 구현되는 과정을 나타내는 도면으로서, 제1영역의 화상부분과 제2영역의 화상부분이 동시에 구현되는 과정을 도시한 도면이다.

- <59> 도 5a는 액정표시패널(110)의 제1영역 및 제2영역상에 화소 전압이 인가되어 초기 영상이 구현되는 상태를 나타내 보인 것이다.

- <60> 그리고, 도 5b는 도 5a의 상태에서 액정표시패널(110)상에 순차적으로 영상이 구현되는 상태를 나타내는 것이다.

- <61> 도 5c는 최종적으로 액정표시패널(110)상의 제1영역과 제2영역의 화상이 서로 일체화되어 구현된 상태를 나타내는 것이다.

- <62> 이에 기초해 볼 때, 본 발명에서는 상기 액정패널(110)의 제1영역 및 제2영역에 서로 다른 영상이 구현되는 것이 아니라, 하나의 프레임 단위의 영상이 분할되어 제1영역 및 제2영역에 각각 구현되고 이것이 결합되어 하나의 영상을 이루게 된다.

- <63> 한편, 상기와 같이 화상을 구현하는 본 발명에 따른 액정표시패널의 구성에 대하여 도 6을 참조하여 설명하면 다음과 같다.

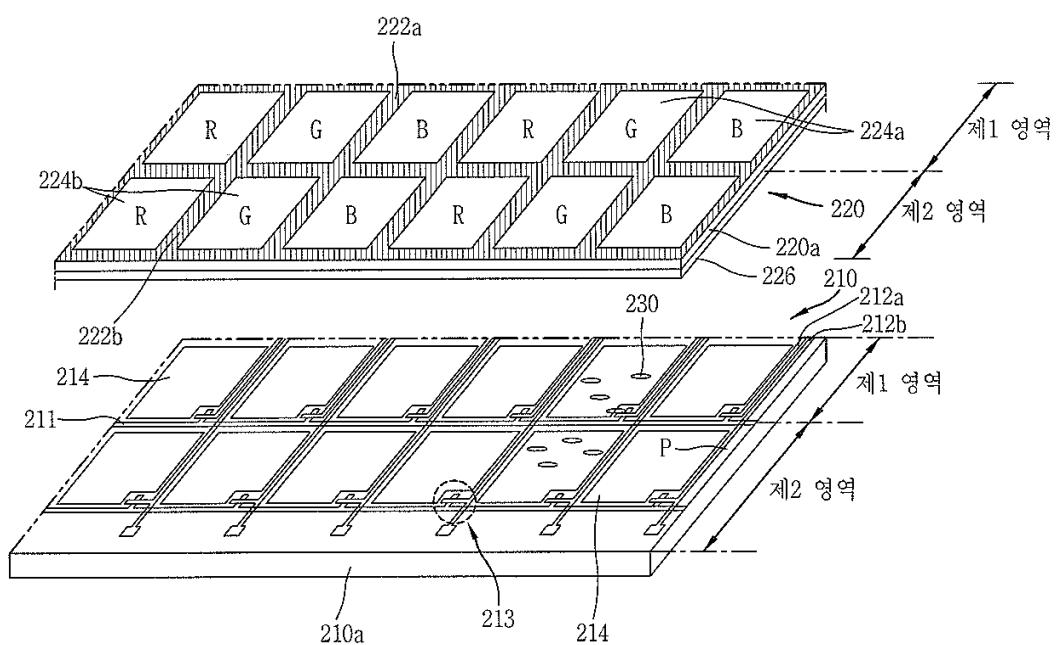

- <64> 도 6은 본 발명에 따른 액정표시패널의 어레이기판(210)과 컬러필터기판(220)의 분해사시도로서, 액정표시패널을 제1영역과 제2영역으로 분할하여 정의한 상태를 도시한 사시도이다.

- <65> 도 6을 참조하면, 액정표시패널(110)은 상부의 컬러필터기판(220)과 하부의 어레이기판(210)이 서로 대향하여 소정의 간격을 두고 이격되어 있고, 이러한 두 기판 사이에 액정분자를 포함하는 액정(230)이 충진되어 있는 구조로 구성되어 있다.

- <66> 여기서 하부의 어레이기판(210)상에는 다수개의 게이트 라인(211)과 제1데이터 리인 및 제2데이터 라인(212a, 212b)이 직교하여 화소 영역을 정의하고, 그 게이트 라인(211)과 제1데이터 라인 및 제2데이터 라인(212a, 212b)이 교차하는 교차부에는 화소전극(214)과 박막 트랜지스터(213)가 형성되어 있다.

- <67> 이때 상기 제1데이터 라인 및 제2데이터 라인(212a, 212b)은 액정표시패널(110)의 제1영역상에 정의되는 단위화소영역의 단위화소 사이마다 형성되고, 그 중 제2데이터 라인(212b)은 제1영역에서 제2영역으로 연장되어 단위화소 사이에 형성된다. 물론 여기에서의 제1데이터 라인(212a)은 제1영역상의 화소 전극(214)과 전기적으로 접속하고, 제2데이터 라인(212b)은 제2영역상의 화소 전극(214)과 전기적으로 접속한다.

- <68> 또한 상부의 컬러필터기판(220)상에는 하부의 어레이기판(210)상에 형성되는 게이트 라인(211)과 제1데이터 라인 및 제2데이터 라인(212a, 212b)에 대응하여 제1블랙매트릭스 및 제2블랙매트릭스(222a, 222b)가 형성되어 있으며, 상기 제1블랙매트릭스 및 제2블랙매트릭스(222a, 222b) 사이에 제1컬러필터 및 제2컬러필터(224a, 224b)가 형성되어 있다.

- <69> 한편, 본 발명에 따른 액정표시패널의 제조방법에 대해 도 6을 참조하여 설명하면 다음과 같다.

- <70> 도면에 도시하지 않았지만, 먼저 제1기판(210a)상에는 게이트 전극을 형성하고, 이어 게이트 절연막을 형성한다.

- <71> 이때, 게이트 절연막을 형성하기 전에 그 하부에 게이트 전극과 연결된 게이트 라인(211)이 추가적으로 형성된다.

- <72> 그 다음, 도면에 도시하지는 않았지만 상기 게이트 절연막 위로는 액티브층과 오믹 콘택층이 차례로 형성되고, 그 오믹 콘택층 위로는 다시 소스 및 드레인 전극을 형성한다.

- <73> 이때, 상기 소스 및 드레인 전극은 게이트 전극과 함께 박막 트랜지스터(213)를 이루게 된다.

- <74> 물론 여기에서도 소스 및 드레인 전극과 같은 동일 물질로 하여 제1기판(210a)상의 제1영역에는 제1 및 제2데이터 라인(212a, 212b)을 게이트 절연막 위에 추가적으로 형성하고, 제1기판(210a)상의 제2영역에는 제1영역의 제2데이터 라인(212b)을 연장하여 게이트 절연막 위에 형성한다.

- <75> 이때 상기 제1데이터 라인 및 제2데이터 라인(212a, 212b)은 제1영역 및 제2영역의 소스 전극과 각각 연결되고, 상기 게이트 라인(211)과 교차하여 화소 영역(P)을 정의하게 된다.

- <76> 이어서, 상기 소스 및 드레인 전극 위로는 유기 물질로 이루어진 보호층을 형성하여 박막 트랜지스터(213)를 덮는다. 이때, 보호층에는 드레인 전극을 드러내는 콘택홀(contact hole)을 형성한다.

- <77> 그 다음, 상기 보호층(미도시) 위의 화소 영역(P)에는 투명도전물질로 이루어진 화소 전극(214)을 형성하여 상기 콘택홀(미도시)을 통해 상기 드레인 전극과 연결되도록 한다. 이때, 상기 화소 전극(214)은 투과 전극의 역할을 한다.

- <78> 한편, 제2기판(220a)상에는 제1기판(210a)와 마찬가지로 제1영역과 제2영역으로 구분되어 동일한 폭을 갖는 제1블랙매트릭스(222a) 및 제2블랙매트릭스(222b)를 형성한다.

- <79> 이어서는 상기 제1블랙매트릭스(222a) 및 제2블랙매트릭스(222b) 사이의 제2기판(220a)상에 적(R), 녹(G), 청(B)의 제1 및 제2컬러필터(224a, 224b)를 순차적으로 반복하여 형성한다.

- <80> 이때, 상기 제1영역의 제1컬러필터(224a)는 제1기판(220a)상의 제1영역의 화소 전극(214)에 대응하고, 제2영역의 제2컬러필터(224b)는 제1기판(210a)상의 제2영역의 화소 전극(214)에 대응하게 된다.

- <81> 또한, 도면에 도시하지 않았지만 상기 제1컬러필터 및 제2컬러필터(224a, 224b)상에는 그 제1컬러필터 및 제2컬러필터(224a, 224b)의 보호와 평탄화를 위하여 오버코트층(overcoat layer)을 형성한다.

- <82> 이때, 상기 오버코트층으로는 보통 아크릴계와 폴리이미드계 수지를 사용한다.

- <83> 그 다음 상기 오버코트층(미도시)상에 투명도전물질로 이루어진 공통 전극(226)을 형성한다.

- <84> 이어서, 상기 제1기판(210a) 및 제2기판(220a)상에는 배향막을 형성하고 그 배향막 사이에는 액정층이 위치하게 한다.

- <85> 이때 여기에서 사용되는 액정은 보통 트위스트 네마티ック(twisted nematic) 액정으로서 액정층의 액정분자는 기판에 대해 선경사각(pretilt angle)을 가지면서 일정하게 배열하게 되는 것이다.

- <86> 다른 한편, 본 발명에 따른 액정표시패널은 더 나아가서 다른 구조로도 얼마든지 변경되어 형성될 수 있다.

- <87> 다시 말해, 외부로부터 데이터가 유입되는 액정표시패널의 화소 영역은 단순히 제1영역 및 제2영역으로만 분할되는 것이 아니라, 3개 이상의 복수 개 영역으로 얼마든지 형성될 수 있다.

- <88> 이때, 데이터가 유입되는 초기 화소 영역에는 그 분할되는 개수만큼의 데이터 라인이 단위화소영역간 형성될 것이고, 그 데이터 라인은 다시 데이터가 유입되는 마지막 화소 영역에 이르면서 점차 그 개수가 감소하다가 마지막 단위화소영역간 하나의 데이터 라인이 형성되어 단위 화소에 전기적으로 접속하게 된다.

- <89> 예컨대, 데이터가 유입되는 전체 화소 영역을 4개의 화소 영역으로 분할하여 액정패널을 구동한다고 가정할 때, 데이터가 유입되는 제1영역에는 4개의 데이터 라인이 단위화소영역간 형성되어 그 중 제1영역의 스위칭소자와 근접하는 데이터 라인이 단위화소와 전기적으로 접속한다. 또한 제2영역에는 그 중 제1영역의 단위 화소에 접속하는 데이터 라인을 제외한 나머지 3개의 데이터 라인이 연장되어 형성되고 그 중 제2영역의 스위칭 소자와 근

접하는 데이터 라인이 다시 제2영역의 단위화소와 접속하게 된다.

<90> 이와 같은 방식으로 제3영역에는 제2영역의 단위화소와 접속하는 데이터 라인을 제외한 나머지 2개의 데이터 라인이 연장되어 형성되고, 그 중 제3영역의 스위칭 소자와 근접한 데이터 라인이 제3영역의 단위 화소와 접속된다.

<91> 그리고 그 제3영역의 단위 화소에 접속하는 데이터 라인을 제외한 나머지 1개의 데이터 라인이 제4영역에 연장되어 형성되고 제4영역의 단위화소에 접속하게 된다.

<92> 그 외에 이와 같이 구성된 액정표시패널의 영상처리방법과 관련해서는 앞서서의 내용들로 대체하고자 한다.

### **발명의 효과**

<93> 상기에서 설명한 바와 같이, 본 발명에 따른 액정표시장치에 의하면 다음과 같다.

<94> 본 발명에 따른 액정표시장치는 고해상도 모델(QSXGA: 2560×2048)의 경우 화상구현시 단위 화소당 화소 전압의 차킹 타임이 규격을 만족하게 됨으로써 블랙 및 화이트와 같은 정상적인 색상 구현이 가능하게 되어 종래 대비 신호지연에 의한 화질의 이상 현상을 개선할 수 있고, 뿐만 아니라 종래와 같이 일정한 프레임 주파수로 구동하여 화상을 구현할 수 있게 됨으로써 전력소모를 줄일 수 있다.

### **도면의 간단한 설명**

<1> 도 1은 종래기술에 따른 액정표시장치의 구조를 나타내는 도면

<2> 도 2는 도 1의 "A"부의 확대평면도로서, 각 단위화소영역에 연결된 데이터 라인의 확대평면도

<3> 도 3은 본 발명에 따른 액정표시장치의 구조를 나타내는 도면

<4> 도 4는 도 3의 "B"부의 확대평면도로서, 각 단위화소영역에 연결된 데이터 라인의 확대평면도

<5> 도 5a 내지 도 5c는 도 3에 나타낸 액정표시패널의 화상이 구현되는 과정을 나타내는 도면으로서, 제1영역의 화상부분과 제2영역의 화상부분이 동시에 구현되는 과정을 도시한 도면

<6> 도 6은 본 발명에 따른 액정표시패널의 어레이기판과 컬러필터기판의 분해사시도로서, 액정표시패널을 제1영역과 제2영역으로 분할하여 정의한 상태를 도시한 사시도

<7> ※도면의 주요부분에 대한 부호의 설명※

<8> 210: 박막트랜지스터 어레이기판      210a: 제1기판

<9> 211: 게이트 라인                          212a: 제1데이터 라인

<10> 212b: 제2데이터 라인                    213: 박막트랜지스터

<11> 214: 화소 전극                            220: 컬러필터기판

<12> 220a: 제2기판                            222a: 제1블랙매트릭스

<13> 222b: 제2블랙매트릭스                224a: 제1컬러필터

<14> 224b: 제2컬러필터                        226: 공통전극

도면

도면1

도면2

## 도면3

## 도면4

도면5a

도면5b

도면5c

도면6

|                |                                                  |         |            |

|----------------|--------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                            |         |            |

| 公开(公告)号        | <a href="#">KR1020080087508A</a>                 | 公开(公告)日 | 2008-10-01 |

| 申请号            | KR1020070029851                                  | 申请日     | 2007-03-27 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                         |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                        |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                        |         |            |

| [标]发明人         | KIM SANG GYU                                     |         |            |

| 发明人            | KIM,SANG GYU                                     |         |            |

| IPC分类号         | G02F1/133 G02F1/1335                             |         |            |

| CPC分类号         | G02F1/13624 G02F1/134363 G02F1/136286 G02F1/1368 |         |            |

| 代理人(译)         | PARK , JANG WON                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                        |         |            |

## 摘要(译)

本发明包括第一和第二数据线，其配置使得多条栅极线和数据线在长度和宽度上交叉并限定像素区域作为与液晶显示器有关的发明，其试图增加充电时间。常规60Hz的帧频比较像素，以防止图像实现中的信号延迟，并划分为第一和第二像素区域，其中像素区域由多个单位像素组成，并连接到分别配备有第一像素区域的多个单位像素和第二像素区域。并且面对与在第一基板上的栅极线的交叉域中形成的开关元件上的像素区域相对应的像素电极，第一基板上的第二数据线连接到第二基板和第一基板中的每个单元像素数据线和第一基板形成并且第一板形状和它被布置。像素电极包括其中形成黑矩阵和滤色器的第二基板。单库，液晶面板，帧频，充电时间。