## (19) 대한민국특허청(KR)

### (12) 공개특허공보(A)

(51) Int. Cl.

G02F 1/136 (2006.01)

(11) 공개번호 10-2006-0057308

(43) 공개일자 2006년05월26일

(21) 출원번호 10-2004-0096416

(22) 출원일자 2004년11월23일

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 김혁진

경기 수원시 영통구 영통동 벽적골8단지아파트 821동 1906호

서동욱

충남 천안시 두정동 1080번지 대아이이투빌아파트 102동 1503호

(74) 대리인 허성원

윤창일

심사청구 : 없음

#### (54) 박막 트랜지스터 기판, 이를 제조하는 방법 및 이를포함하는 액정 표시 패널

#### 요약

본 발명은 게이트 배선과, 상기 게이트 배선과 교차영역을 가지며 형성되는 데이터 배선과, 상기 게이트 배선과 상기 데이터 배선 사이에 개재되어 있는 액티브층을 포함하는 박막 트랜지스터 기판에 있어서, 상기 액티브층은 상기 교차영역에서 상기 데이터 배선의 길이방향의 양 측면 중 적어도 어느 일측을 넘어서 형성된 연장부를 더 포함하는 것을 특징으로 한다. 이에 의해, 게이트 배선과 데이터 배선간 단차로 인해 발생하는 스텝오픈에 대한 CVD 수리 성공률을 높일 수 있다.

#### 대표도

도 4

#### 명세서

#### 도면의 간단한 설명

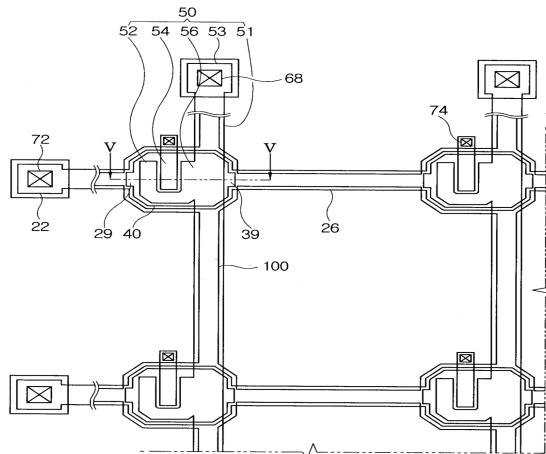

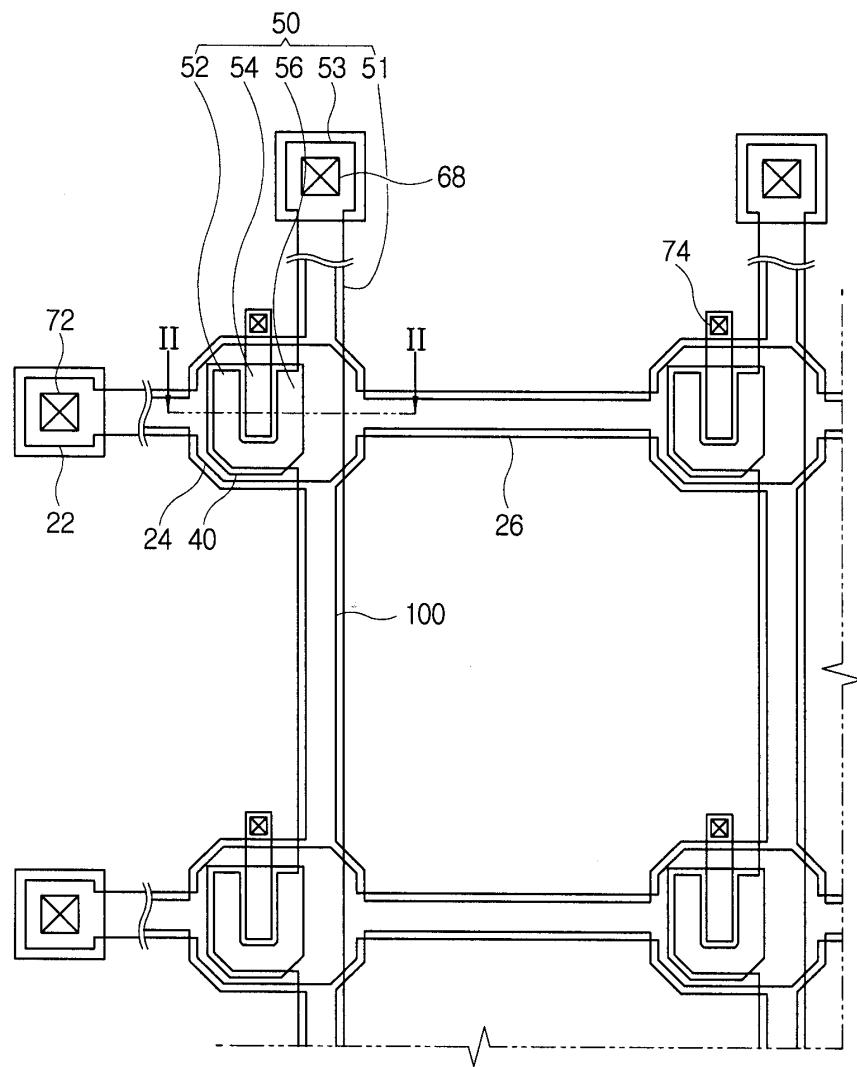

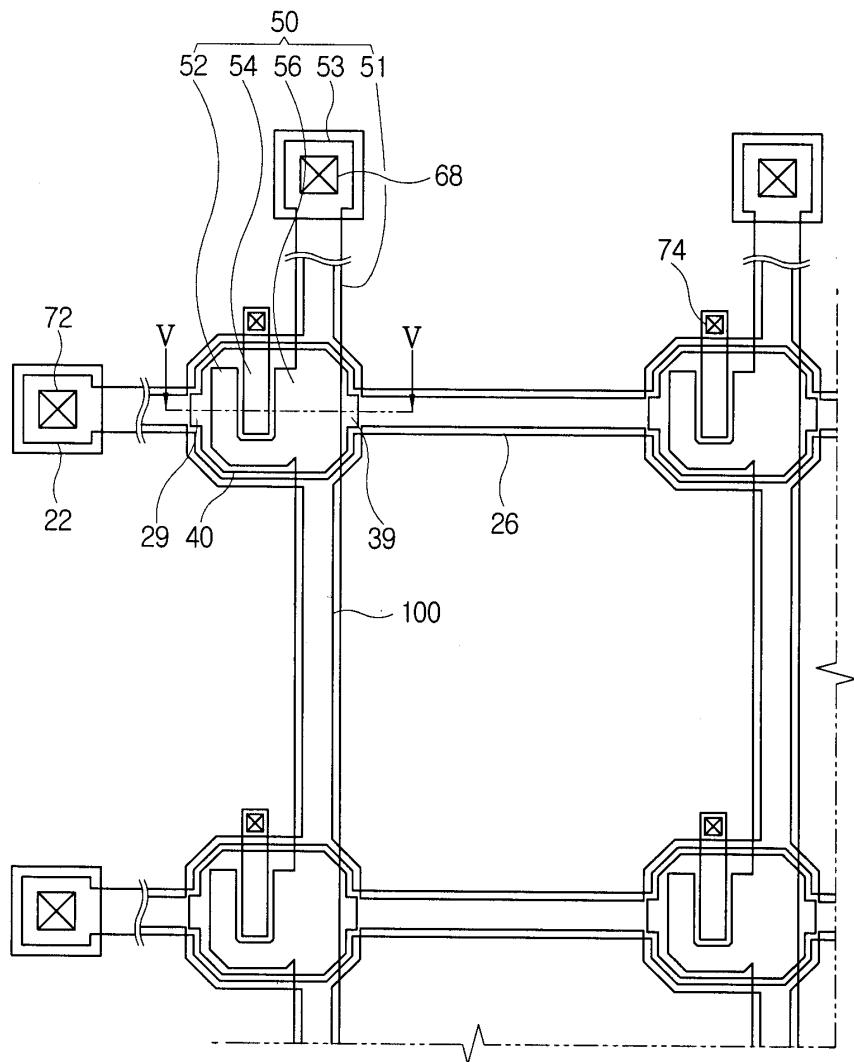

도 1은 종래 기술에 따른 박막 트랜지스터 기판의 배치도이고,

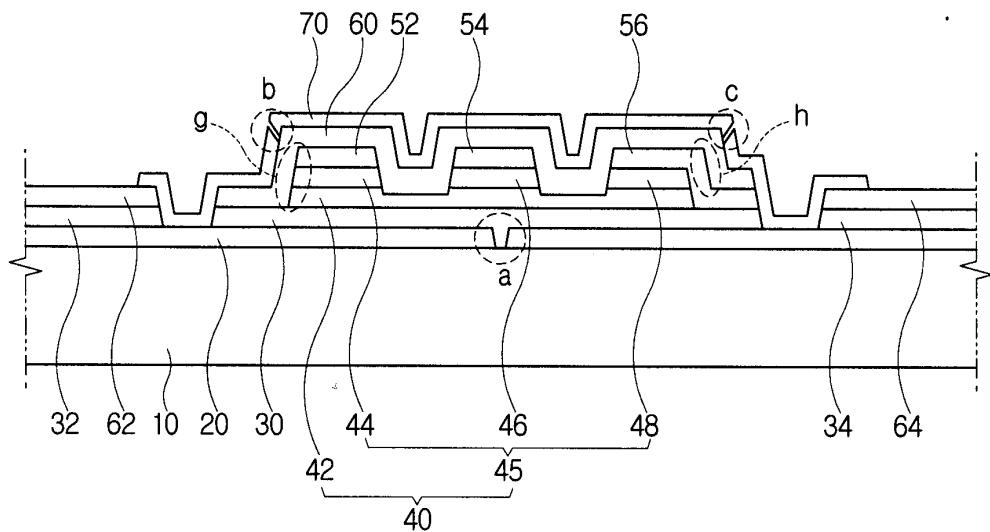

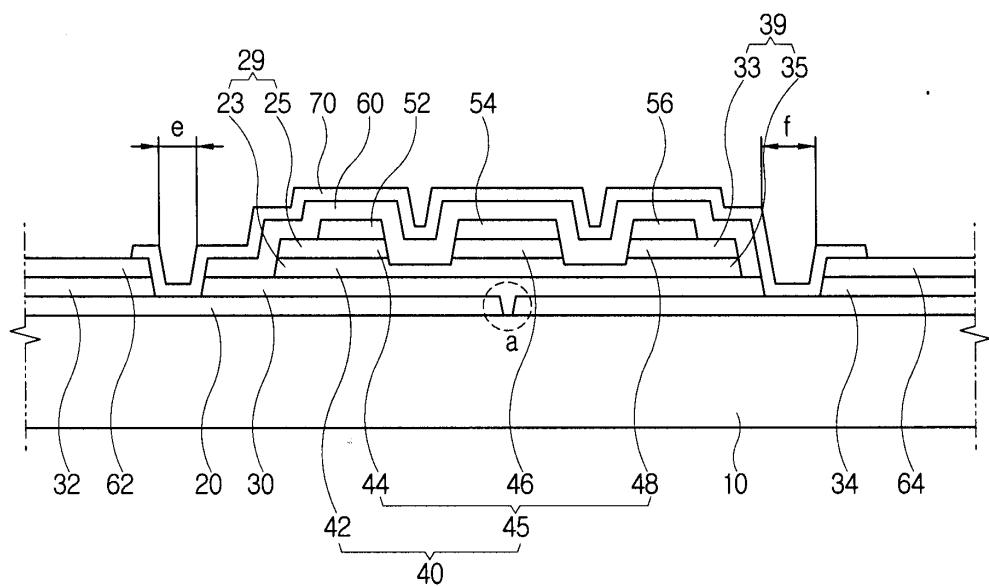

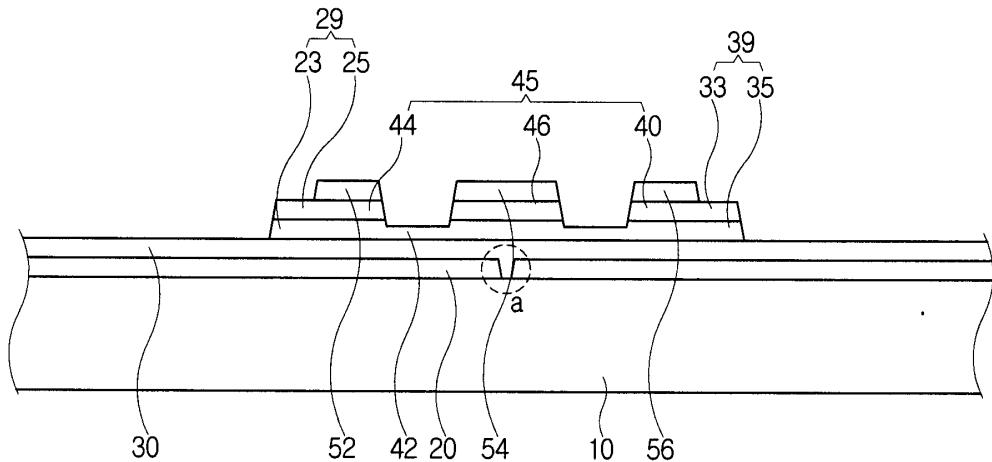

도 2는 도1의 II-II 선을 따른 단면도이고,

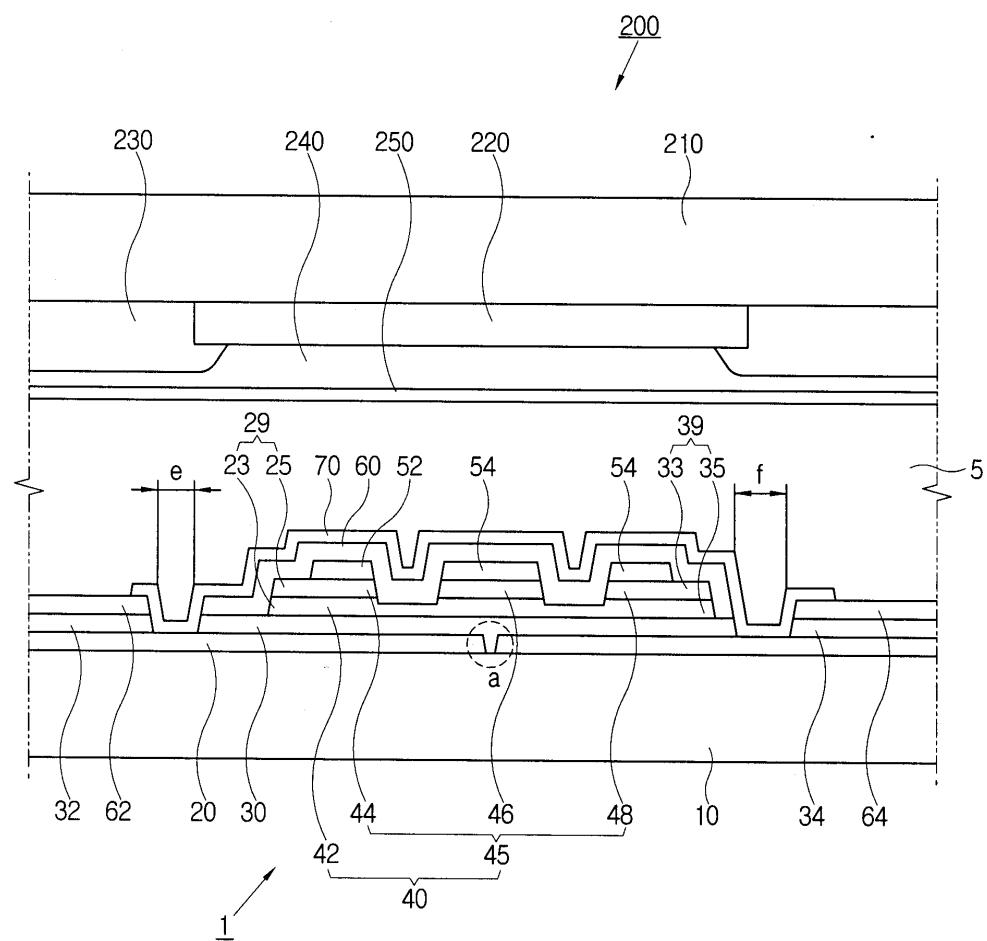

도 3는 본 발명에 따른 액정 표시 패널의 단면도이고,

도 4은 본 발명에 따른 박막 트랜지스터 기판의 배치도이고,

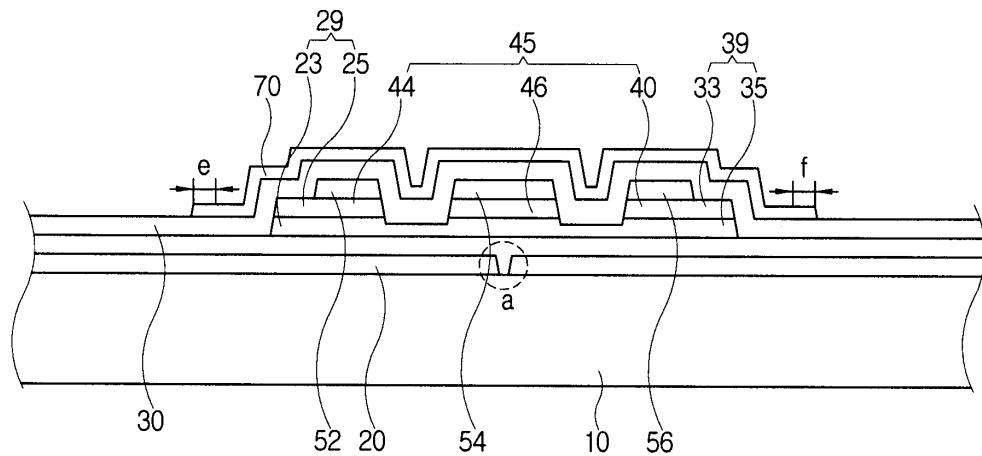

도 5는 도4의 V-V 선에 따른 단면도이고,

도 6 내지 도 9은 본 발명에 따른 박막 트랜지스터 기판의 제조 단계를 순서대로 나타낸 단면도이다.

\* 도면의 주요 부분에 대한 부호의 설명

1 : 제 2 기판 5 : 액정층

10 : 제 2 절연 기판 20 : 게이트 배선

22 : 게이트 패드 24 : 게이트 전극

26 : 게이트 라인 29,39 : 연장부

30 : 게이트 절연막 40 : 액티브층

42 : 반도체층 45 : 저항성 접촉층

50 : 데이터 배선 51 : 데이터 배선

52,56 : 소스 전극 53 : 데이터 패드

54 : 드레인 전극 60 : 보호막

70 : 금속층 68,72,74 : 접촉구멍

100 : 화소전극 200 : 제 1기판

210 : 제 1 절연기판 220 : 블랙 매트릭스

230 : 컬러 필터 240 : 오버코트층

250 : 공통전극

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 박막 트랜지스터 기판, 이를 제조하는 방법 및 이를 포함하는 액정 표시 패널에 관한 것으로서, 보다 상세하게는, 상호 절연 교차되는 금속배선의 교차영역에서의 단차를 완화시킨 박막 트랜지스터, 이를 제조하는 방법 및 이를 포함하는 액정 표시 패널에 관한 것이다.

액정 표시 패널(Liquid Crystal Display Panel)은 매트릭스(Matrix) 형태로 배열된 액정 셀들의 광 투과율을 화상 신호 정보에 따라 조절하여 원하는 화상을 표시하는 것이다. 액정 표시 패널은 박막 트랜지스터 기판과, 박막 트랜지스터 기판에 대향 되도록 상호 부착되며 컬러 필터, 블랙 매트릭스, 오버코트층 및 공통전극을 포함하는 컬러 필터 기판과, 상기 박막 트랜지스터 기판과 상기 컬러 필터 기판 사이에 주입되는 액정을 포함한다.

일반적으로 박막 트랜지스터 기판(Thin Film Transistor; TFT)은 액정 표시장치(LCD; Liquid Crystal Display)나 유기 EL(Electro Luminescence) 표시 장치 등에서 각 화소를 독립적으로 구동하기 위한 회로 기판으로서 사용된다. 박막 트랜지스터 기판은 주사신호를 전달하는 주사 신호 배선 또는 게이트 배선과, 화상 신호를 전달하는 화상 신호선 또는 데이터 배선과, 게이트 배선과 데이터 배선 사이에 개재되어 있는 반도체층과 저항성 접촉층을 포함하는 액티브층이 형성되어 있다.

박막 트랜지스터 기판은 이러한 게이트 배선 및 데이터 배선과 연결되어 있는 박막 트랜지스터, 박막 트랜지스터와 연결되어 있는 화소 전극, 게이트 배선을 덮어 절연하는 게이트 절연막 및 박막 트랜지스터와 데이터 배선을 덮어 절연하는 보호막을 포함한다.

박막 트랜지스터는 게이트 배선의 일부인 게이트 전극, 게이트 전극 상에 형성되는 섬모양의 반도체층과 저항성 접촉층을 포함하는 액티브층, 데이터 배선의 일부인 소스 전극과 드레인 적극, 게이트 절연막 및 보호막 등으로 이루어진다. 박막 트랜지스터는 게이트 배선을 통하여 전달되는 주사신호에 따라 데이터 배선을 통해 전달되는 화상 신호를 화소 전극에 전달 또는 차단하는 스위칭(Switching) 소자이다.

박막 트랜지스터 기판의 제조공정은 게이트 금속을 절연기판 상에 적층하고 패터닝하여 게이트 배선을 형성하는 게이트 공정, 반도체층과 저항성 접촉층을 적층하고 패터닝하는 액티브 공정, 화소전극을 적층하고 패터닝하는 화소공정, 데이터 금속을 적층하고 패터닝하여 소스와 드레인을 형성하는 데이터 공정, 채널을 형성하고 보호막을 형성하는 공정 및 검사공정을 포함하는 일련의 프로세스로 이루어진다.

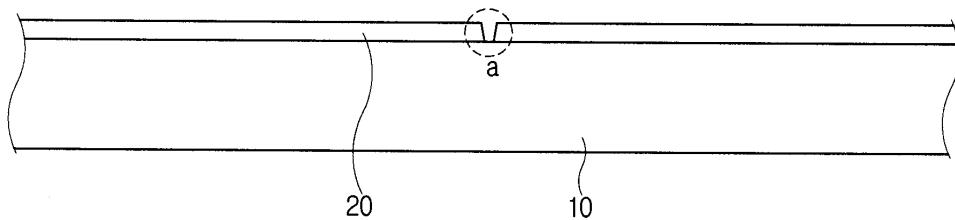

박막 트랜지스터 기판을 제조하는 과정 중 게이트 공정에서, 환경 파티클(미세 입자, 먼지 등)이 증착된 게이트 금속층 상에 존재하는 경우, 환경 파티클이 존재하는 영역에는 감광성 물질이 도포되지 않거나 얇게 도포된다. 또는, 환경 파티클이 없더라도 감광성 물질이 국부적으로 얇게 도포될 수 있다. 환경 파티클이 존재하는 영역에 감광성 물질이 도포되지 않아 게이트 금속층을 게이트 배선으로 패터닝하기 위해 에칭하는 과정에서, 게이트 배선도 에칭되어 도2에 도시된 a영역과 같이 끊어져 버리게 된다. 그러나, 게이트 배선의 단선은 CVD(Chemical Vapor Deposition) 방법에 의해 수리가 가능하다.

그러나, 상기 불량이 게이트 배선과 데이터 배선이 교차되는 교차영역에서 발생된 경우 각 층들이 이루는 단차로 인하여 CVD 수리의 성공률이 저하되는 문제점이 있다. 도 1과 도 2의 g 및 h영역과 같이, 데이터 배선에서 분기된 소스 전극이 액티브층의 외측면과 맞닿게 형성되므로 액티브층과 데이터 배선에 의하여 이루어진 단차가 발생한다. 그러므로 도 2의 b 및 c영역과 같이, 단선된 게이트 배선을 수리하기 위해 증착되는 금속층이 단차로 인해 충돌함성(Step Coverage)이 취약해져 식각액 침투에 의해 끊어지는 스텝오픈(Step Open)이 발생하는 문제점이 있다. 또는, 단차 때문에 생기는 막 스트레스로 인해 균열 등이 발생하여 금속층이 스텝오픈 되어 CVD 수리 성공률이 낮은 문제점이 있다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명의 목적은 게이트 배선과 데이터 배선간 단차로 인해 발생하는 스텝오픈에 대한 CVD 수리 성공률이 높은 박막 트랜지스터 기판과 그 제조방법을 제공하는 것이다.

### 발명의 구성 및 작용

상기 목적은, 게이트 배선과, 상기 게이트 배선과 교차영역을 가지며 형성되는 데이터 배선과, 상기 게이트 배선과 상기 데이터 배선 사이에 개재되어 있는 액티브층을 포함하는 박막 트랜지스터 기판에 있어서, 상기 액티브층은 상기 교차영역에서 상기 데이터 배선의 길이방향의 양 측면 중 적어도 어느 일측을 넘어서 형성된 연장부를 포함하는 것을 특징으로 하는 박막 트랜지스터 기판에 의해 달성된다.

여기서, 상기 액티브층은 상기 게이트 배선의 영역 내에 형성되어 있는 것이 바람직하다.

또한, 상기 게이트 배선은 게이트 라인과, 상기 게이트 라인과 상기 데이터 배선의 상기 교차영역에서 라인의 폭이 증가되는 게이트 전극을 포함하며, 상기 액티브층은 상기 게이트 전극 상에 위치하며 상기 연장부는 상기 게이트 라인 상에 위치하고 있는 것이 바람직하다.

그리고, 상기 데이터 배선은 데이터 라인과, 상기 데이터 라인에서 분기되어 J 또는 U형으로 형성된 소스전극을 포함하며, 상기 연장부는 상기 소스 전극의 외측방향으로 연장되어 있는 것이 바람직하다.

또한, 상기 목적은, 박막 트랜지스터 기판을 제조하는 방법에 있어서, 절연기판 상에 게이트 배선을 형성하는 단계와; 상기 게이트 배선 상에 액티브층을 형성하는 단계와; 및 상기 액티브층 상에 상기 게이트 배선과 교차영역을 가지며 형성되는

데이터 배선을 형성하는 단계를 포함하는 하는 박막 트랜지스터 기판의 제조방법에 있어서, 상기 액티브층은 상기 교차영역에서 상기 데이터 배선의 길이방향의 양 측면 중 적어도 어느 일측을 넘어서 형성된 연장부를 가지는 것을 특징으로 하는 박막 트랜지스터 기판의 제조방법에 의해 달성된다.

여기서, 상기 액티브층은 상기 게이트 배선 영역 내에 형성되도록 제조하는 것이 바람직하다.

또한, 상기 목적은, 제 1 기판과; 상기 제 1 기판과 대향 배치되며 게이트 배선과, 상기 게이트 배선과 교차영역을 가지며 형성되는 데이터 배선과, 상기 게이트 배선과 상기 데이터 배선 사이에 개재되어 있는 액티브층을 포함하는 제 2 기판과; 상기 제 1 기판과 상기 제 2 기판사이에 주입되는 액정을 포함하는 액정 표시 패널에 있어서, 상기 액티브층은 상기 교차영역에서 상기 데이터 배선의 길이 방향의 양 측면 중 적어도 어느 일측을 넘어서 형성된 연장부를 포함하는 것을 특징으로 하는 액정 표시 패널에 의해 달성된다.

여기서, 상기 액티브층은 상기 게이트 배선의 영역 내에 형성되어 있는 것이 바람직하다.

또한, 상기 게이트 배선은 게이트 라인과, 상기 게이트 라인과 상기 데이터 배선의 상기 교차영역에서 라인의 폭이 증가되는 게이트 전극을 포함하며, 상기 액티브층은 상기 게이트 전극 상에 위치하며 상기 연장부는 상기 게이트 라인 상에 위치하고 있는 것이 바람직하다.

그리고, 상기 데이터 배선은 데이터 라인과, 상기 데이터 라인에서 분기되어 J 또는 U형으로 형성된 소스전극을 포함하며, 상기 연장부는 상기 소스 전극의 외측방향으로 연장되어 있는 것이 바람직하다.

이하에서는 본 발명에 따른 박막 트랜지스터 기판, 이를 제조하는 방법 및 이를 포함하는 액정 표시 패널을 첨부도면을 참조하여 설명한다. 종래의 기술과 동일한 부분에 대하여는 동일한 참조번호를 사용하여 설명한다.

액정 표시 패널은 컬러 필터 기판(이하, 제 1 기판이라고 한다.)과, 컬러 필터 기판과 대향 되도록 부착되는 박막 트랜지스터 기판(이하, 제 2 기판이라고 한다.)과, 제 1 기판과 제 2 기판 사이에 주입되는 액정을 포함한다.

도 3에 도시된 바와 같이, 제 1 기판(200)은 유리, 석영, 세라믹 또는 플라스틱 등의 절연 재질을 포함하여 만들어진 제 1 절연기판(210) 상에 개구영역을 가지도록 스트라이프 또는 격자형상으로 형성된 블랙 매트릭스(220)와, 블랙 매트릭스(220)의 개구영역에 각각 형성된 적색, 녹색 및 청색의 컬러필터(230)와, 블랙 매트릭스(220) 및 컬러필터(230) 상에 차례로 적층되는 오버코트층(240)과 공통전극(250)을 포함한다.

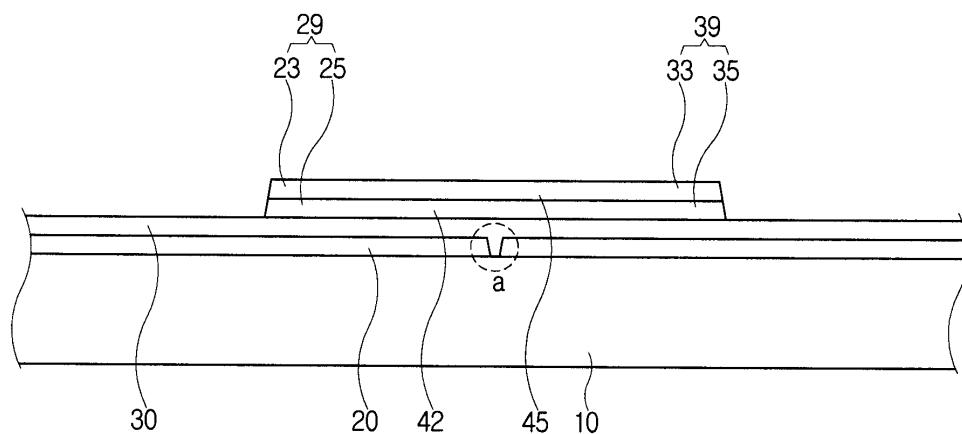

제 2 기판은, 도 5과 도 6에 도시 된 바와 같이, 유리, 석영, 세라믹 또는 플라스틱 등의 절연성 재질을 포함하여 만들어진 제 2 절연기판(10) 상에 게이트 금속을 증착한 후, 패터닝하여 게이트 배선(20)을 형성한다. 게이트 배선(20)은 단층으로도 형성 가능하고 이중층 이상으로도 형성될 수 있다. 다층으로 게이트 배선을 형성하는 이유는 각 금속 또는 합금의 단점을 보완하고 원하는 물성을 얻기 위함이다. 이중층을 예로 들어 설명하면, 제1게이트 배선층에는 알루미늄 또는 알루미늄 합금을 포함하고, 제2게이트 배선층에는 크롬을 포함한다. 즉, 하부층으로 배선저항에 의한 신호저항을 막기 위해 비저항이 작은 알루미늄 또는 알루미늄 합금을 사용하고, 상부층으로 화학약품에 의한 내식성이 약하며 쉽게 산화되어 단선이 발생하는 알루미늄 또는 알루미늄 합금의 단점을 보안하기 위해 화학약품에 내식성이 강한 크롬, 몰리브덴, 몰리브덴-텅스텐 및 몰리브덴-텅스텐 나이트라이드 중에서 선택된 적어도 하나 이상을 사용한다.

게이트 배선(20)은 가로방향으로 뻗어있는 게이트 라인(26)과 게이트 라인(26)의 일부의 폭이 증가되어 분기된 게이트 전극(24) 및 게이트 라인(26)의 일단에 형성된 게이트 패드(22)를 포함하여 이루어져 있다.

여기서, 환경 파티클(미세 입자, 먼지 등)이 증착된 게이트 금속층 상에 존재하는 경우, 환경 파티클이 존재하는 영역에는 감광성 물질이 도포되지 않거나 얇게 도포된다. 또는, 환경 파티클이 없더라도 감광성 물질이 국부적으로 얇게 도포될 수 있다. 환경 파티클이 존재하는 영역에 감광성 물질이 도포되지 않아 게이트 금속층을 게이트 배선(20)으로 패터닝하기 위해 에칭하는 과정에서, 게이트 배선(20)도 에칭되어 도5에 도시된 a영역과 같이 끊어져 버리게 된다. 그러나, 상기 불량은 제 2기판의 검사단계에서 검출된 경우 CVD(Chemical Vapor Deposition) 방법에 의해 수리가 가능하다.

여기서, CVD 방법이란 기체상태의 화합물을 가열된 모재표면에서 반응시키고 생성물을 모재표면에 증착시키는 것이다. 제 2 기판 제조 후, 검사단계에서 상술한 환경 파티클에 의해 도 5의 a영역에 표시된 봄과 같은 단선이 검출될 수 있다. 단선된 게이트 배선을 수리하기 위해 도 9에 도시된 바와 같이, 텅스텐 등의 금속층(70)을 CVD방법에 의해 적층한다. 게이트 배선의 단선된 부분을 가운데 두고 e영역과 f영역에 레이저를 조사하여, 보호막(60, 62, 64) 및 게이트 절연막(30, 32,

34)을 녹이면서 상부에 적층된 금속층(70)이 레이저에 의해 형성된 구멍으로 녹아 내리게 된다. 그래서, 상기 단선된 게이트 배선이 금속층(70)에 의하여 연결되어 불량이 수리된다. 그러나, 상기 금속층(70)이 하부에 적층된 여러 층들에 의해 형성된 단차로 인해 끊어져 CVD 수리 성공률이 낮은 문제점이 있다.

상기의 문제점은 후술하는 액티브층(40)의 패턴을 변경함으로 인해 해결된다.

게이트 배선(20) 위에는 질화규소(SiNx)로 이루어진 게이트 절연막(30)이 형성되어 게이트 배선(20)을 덮는다.

게이트 절연막(30) 위에는 수소화 비정질 규소(hydrogenated amorphous silicon)의 반도체로 이루어진 반도체층(42)이 형성되며, 반도체층(42) 위에는 인(P) 따위의 n형 불순물이 고농도로 도핑되어 있는 비정질 규소로 이루어진 저항성 접촉층(45)이 형성된다. 반도체층(42)과 저항성 접촉층(45)을 포함하여 액티브층(40)이라고 한다. 게이트 절연막(30), 반도체층(42) 및 저항성 접촉층(45)이 연속하여 중첩되고, 반도체층(42) 및 저항성 접촉층(45)을 포함하는 액티브층(40)은 패터닝되어 게이트 전극(24) 상에 섬모양으로 형성된다. 저항성 접촉층(45)은 그 하부의 반도체층(42)과 상부의 데이터 배선(50)의 접촉 저항을 낮추어 주는 역할을 한다.

게이트 배선(20)과 데이터 배선(50)의 교차영역에서, 특히 게이트 전극(24)상에서 반도체층(42), 저항성 접촉층(44, 48) 및 소스 전극(52, 56)으로 이루어진 층이 너무 높아 단차가 형성되고, 상술한 문제가 발생한다. 그래서 본 발명에서는 반도체층과 저항성 접촉층을 포함하는 액티브층을 데이터 배선의 길이방향으로 양 외측면을 연장시킨 연장부(29, 39)를 형성한다. 연장부(29, 39)는 게이트 배선 영역 내에 있는 것이 바람직하며, 특히 액티브층은 게이트 전극상에, 연장부(29, 39)는 게이트 라인상에 위치하는 것이 바람직하다. 연장부(29, 39)로 인하여 액티브층(40)과 소스 전극(52, 58)이 계단 형상을 이루게 된다. 그러므로 게이트 배선(20)의 단선을 수리할 금속층(70)이 적층 되더라도 단차가 낮아서 막 스트레스나 층 덮힘의 취약성으로 인한 금속층(70)의 단선을 방지할 수 있다. 특히, 액티브층(40)의 재료의 특성상 경사가 완만하게 형성되므로 단차를 보상하는 효과는 더욱 증대된다.

섬모양의 액티브층(40) 위에 데이터 금속이 적층되고, 데이터 배선(50)으로 형성된다. 데이터 배선(50)도 전술한 게이트 배선(20)과 같이 하나의 재질로 이루어지거나 이중층 등의 다층으로 형성될 수 있다. 데이터 배선(50)은 전술한 게이트 배선(20)과 동일한 금속뿐만 아니라 다른 금속재질로 형성될 수 있다.

데이터 배선(50)은 세로 방향으로 형성되어 있으며, 데이터 라인(51)과 데이터 라인(51)의 단부에 연결되어 있으며 외부로부터 화상 신호를 인가 받아 데이터 라인(51)에 전달하는 데이터 패드(53)와, 데이터 배선(50)의 분지인 박막 트랜지스터의 소스 전극(52, 56) 및 데이터 라인(51)과 분리되어 있는 박막 트랜지스터의 드레인 전극(54)을 포함한다. 게이트 전극(24) 위의 소스 전극(52, 56)은 데이터 라인에서 J 또는 U형으로 분기되어 있으며, 데이터 라인(52)에 분리되어 있는 드레인 전극(54)은 소스 전극(52, 56) 안쪽에 형성된다.

도 5의 단면도에 도시된 바와 같이, 데이터 배선의 길이방향의 소스 전극(52, 56)과 액티브층(40)의 연장부(29, 39)는 계단형상을 이룬다. 즉, 액티브층(40)의 연장부(29, 39)는 소스 전극(52, 56)의 외측면보다 소정의 길이로 더 길게 형성되어 단차를 보상한다. 한편, 채널부를 형성하는 영역의 저항성 접촉층(45)은 소스 전극(52, 56) 및 드레인 전극(54)과 동일한 형상으로 형성된다.

한편, 반도체층(42)은 박막 트랜지스터의 채널부를 제외하면 저항성 접촉층(44, 46, 48)과 동일하게 데이터 배선(50)과 층을 이루는 계단형상으로 형성된다. 구체적으로, 박막 트랜지스터의 채널부에서 데이터 배선(42)이 소스 전극(52, 56)과 드레인 전극(54)이 분리되어 있고, 저항성 접촉층(44, 46, 48)도 소스 전극(52, 56)과 드레인 전극(54)과 유사한 형상으로 서로 분리되어 형성된다. 그러나 반도체층(42)은 서로 끊어져 있지 않고 연결되어 박막 트랜지스터의 채널을 형성한다.

데이터 배선(50) 위에는 질화규소나 PECVD(plasma enhanced chemical vapor deposition) 방법에 의하여 증착된 a-Si:C:O 막 또는 a-Si:O:F 막(저유전율 CVD 막) 또는 유기 절연막으로 이루어진 보호막(60)이 형성된다. 보호막(60)은 드레인 전극(54), 데이터 패드(53)의 일부를 드러내는 접촉구멍(74, 68)을 가지고 있으며, 또한 게이트 패드(22)의 일부를 드러내는 접촉구멍(72)을 가진다.

보호막(60) 위에는 박막 트랜지스터로부터 화상 신호를 전달 받아 상판의 공통전극과 함께 전기장을 생성하는 화소전극(100)이 형성된다. 화소전극(100)은 ITO(indium tin oxide) 또는 IZO(indium zinc oxide) 따위의 투명한 도전 물질로 만들어지며, 접촉 구멍(74)을 통하여 드레인 전극(54)과 물리적·전기적으로 연결되어 화상신호를 전달 받는다. 화소전극(100)은 이웃하는 게이트 라인(26) 및 데이터 라인(51)과 중첩되어 개구율을 높이고 있으나 중첩되지 않을 수도 있다.

한편, 게이트 패드(22) 및 데이터 패드(53) 위에는 접촉 구멍(72, 68)을 통하여 각각 외부 회로장치와 게이트 배선(20) 및 데이터 배선(50)과 연결되는 접촉보조부재(미도시)가 형성된다. 이 접촉보조부재(미도시)는 끝 부분과 외부 회로장치와의 접착성을 보완하고 게이트 패드(22) 및 데이터 패드(53)를 보호하는 역할을 하는 것으로 필수적인 것은 아니며, 이들의 적용여부는 선택적이다.

이하에서는, 본 발명에 따른, 도 4 및 도5의 구조를 가지는 제 2기판을 제조하는 방법에 관하여 간략히 설명한다.

도 6 내지 도 9는 본 발명에 따른 제 2 기판의 제조 단계를 순서대로 나타낸 단면도이다

도 6에 도시된 바와 같이, 제 1절연성 기판(10) 상에 게이트 금속을 증착한 다음, 사진 식각 공정을 거쳐 게이트 라인(26), 게이트 패드(22) 및 게이트 전극(24)을 포함하는 게이트 배선(20)을 형성한다. 이중층의 게이트 배선을 예로 들면, 절연성 기판 상에 저항이 작은 알루미늄 또는 알루미늄 합금 등을 증착하여 제 1 게이트 배선층을 적층하고, 물리적 화학적 특성이 우수한 크롬, 몰리브덴, 몰리브덴-텅스텐 및 몰리브덴-텅스텐 나이트라이드에서 선택된 적어도 하나 이상을 증착하여 제 2 게이트 배선층을 적층한 다음 전술한 바와 같이 사진 식각 공정을 거쳐 게이트 배선을 형성한다.

전술한 바와 같이, 환경 파티클 등에 의해 식각공정에서 게이트 배선(20)이 도5의 a영역과 같이 단선되는 문제가 있다. 그러나 상기 불량이 검사단계에서 검출된 경우에는 상술할 CVD 수리 방법에 의해 보완 가능하다.

다음, 도 7에 도시된 바와 같이, 질화 규소(SiNx)로 이루어진 게이트 절연막, 반도체층 및 저항성 접촉층을 화학 기상 증착법을 이용하여 의 두께로 연속하여 증착한다. 여기서, 게이트 절연막(30)은 1,500Å 내지 5,000Å으로, 반도체층(42)은 500Å 내지 2000Å으로, 저항성 접촉층(45)은 300 내지 600Å의 두께로 연속 증착하고, 반도체층(42)과 저항성 접촉층(45)을 사진 식각하여 게이트 전극(24) 상부와 게이트 절연막(30) 위에 섬모양의 반도체층(42)과 저항성 접촉층(45)을 형성한다.

여기서, 본 발명에서는 반도체층과 저항성 접촉층을 포함하는 액티브 층을 데이터 배선의 길이방향으로 양 외측면을 연장시킨 연장부(29, 39)를 형성한다. 연장부(29, 39)는 게이트 배선 영역 내에 있는 것이 바람직하며, 특히 액티브층은 게이트 전극상에, 연장부(29, 39)는 게이트 라인상에 위치하는 것이 바람직하다. 연장부(29, 39)로 인하여 액티브층(40)과 소스 전극(52, 58)이 계단 형상을 이루게 된다. 그러므로 게이트 배선(20)의 단선을 수리할 금속층(70)이 적층되더라도 단차가 낮아서 막 스트레스나 충돌힘의 취약성으로 인한 금속층(70)의 단선을 방지할 수 있다. 특히, 액티브층(40)의 재료의 특성상 경사가 완만하게 형성되므로 단차를 보상하는 효과는 더욱 증대된다.

그 후, 도 8에 도시된 것과 같이, 데이터 금속층을 적층하고, 마스크를 이용한 사진 식각 공정으로 패터닝하여 게이트 라인(26)과 교차하는 데이터 라인(51), 데이터 라인(51)과 연결되어 게이트 전극(24) 상부까지 연장되어 있는 J 또는 U형상의 소스 전극(52, 56) 및 소스 전극(52, 56)과 분리되어 있으며 게이트 전극(24)을 중심으로 소스 전극(52, 56) 안쪽에 위치하는 드레인 전극(54)을 포함하는 데이터 배선(50)을 형성한다. 소스 전극(52, 56)과 드레인 전극(54)은 2500Å 내지 3000Å의 두께로 적층된다. 소스 전극(52, 56)은 액티브층(40)과 함께 계단형상을 이루며 형성하여 단차를 보상한다.

이어, 저항성 접촉층(45)은 마스크 공정을 거쳐 상술한 연장부(29)를 남겨두고, 그 외의 부분은 소스 전극(52, 56) 및 드레인 전극(54)과 유사한 형상으로 식각되어 형성된다. 그리고, 소스 전극과 드레인 전극 사이에 반도체층(42)을 노출 시켜 채널부를 형성한다. 이어, 노출된 반도체층(42)의 표면을 안정화시키기 위하여 산소 플라즈마를 실시하는 것이 바람직하다.

다음으로, 도9에서 보는 바와 같이, 질화규소막, a-Si:C:O 막 또는 a-Si:O:F 막을 화학 기상 증착(CVD) 법에 의하여 성장시키거나 유기 절연막을 도포하여 보호막(60)을 형성한다.

다음, 도 4 및 도5에 도시된 바와 같이, 사진 식각 공정으로 게이트 절연막(30)과 함께 보호막(60)을 패터닝하여, 게이트 패드(22), 드레인 전극(54) 및 데이터 패드(53)를 드러내는 접촉구멍(72, 74, 68)을 형성한다.

다음, ITO 또는 IZO 막을 증착하고 사진 식각하여 접촉구멍(74)을 통하여 드레인 적극(54)과 연결되는 화소 전극(100)과 접촉구멍(72, 68)을 통하여 게이트 패드(22) 및 데이터 패드(53)와 각각 연결되어 있는 접촉 보조 부재(미도시)를 각각 형성한다. ITO 또는 IZO를 적층하기 전의 예열(pre-heating) 공정에서 사용하는 기체는 질소를 이용하는 것이 바람직하다.

그 후, 제조된 제 2 기판의 불량여부를 검사하고, 불량이 없으면 마련된 제 1 기판과 제 2 기판 사이에 액정을 주입한 후 액정 표시 패널을 완성한다.

검사단계에서 게이트 배선의 단선과 같은 불량이 발생한 경우, 게이트 배선의 단선된 부분을 가운데 두고 도 9에 도시된 바와 같이, 텅스텐 등의 금속층을 적층한 후, e영역과 f영역에 레이저를 조사하여, 보호막(60, 62) 및 게이트 절연막(30, 32)을 녹이면서 상부에 적층된 금속층(70)이 레이저에 의해 형성된 구멍으로 녹아내리게 된다. 그래서, 상기 단선된 게이트 배선이 금속층(70)에 의하여 연결되어 불량이 수리된다. 그리고, 상술한 액티브층의 연장부로 인하여 단차가 낮아져서 금속층(70)의 단선이 예방되어 CVD 수리 성공률이 높아진다.

### 발명의 효과

이상 설명한 바와 같이, 본 발명에 따르면, 상호 교차되는 금속배선을 갖는 제 2 기판에 있어서, 교차영역의 구조를 개선하여 게이트 배선과 데이터 배선간 단차로 인해 발생하는 스텝오픈에 대한 CVD 수리 성공률을 높일 수 있다

### (57) 청구의 범위

#### 청구항 1.

게이트 배선과, 상기 게이트 배선과 교차영역을 가지며 형성되는 데이터 배선과, 상기 게이트 배선과 상기 데이터 배선 사이에 개재되어 있는 액티브층을 포함하는 박막 트랜지스터 기판에 있어서,

상기 액티브층은 상기 교차영역에서 상기 데이터 배선의 길이방향의 양 측면 중 적어도 어느 일측을 넘어서 형성된 연장부를 포함하는 것을 특징으로 하는 박막 트랜지스터 기판.

#### 청구항 2.

제1항에 있어서,

상기 액티브층은 상기 게이트 배선의 영역 내에 형성되어 있는 것을 특징으로 하는 박막 트랜지스터 기판.

#### 청구항 3.

제1항에 있어서,

상기 게이트 배선은 게이트 라인과, 상기 게이트 라인과 상기 데이터 배선의 상기 교차영역에서 라인의 폭이 증가되는 게이트 전극을 포함하며,

상기 액티브층은 상기 게이트 전극 상에 위치하며 상기 연장부는 상기 게이트 라인 상에 위치하고 있는 것을 특징으로 하는 박막트랜지스터 기판.

#### 청구항 4.

제1항에 있어서,

상기 데이터 배선은 데이터 라인과, 상기 데이터 라인에서 분기되어 J 또는 U형으로 형성된 소스전극을 포함하며,

상기 연장부는 상기 소스전극의 외측방향으로 연장되어 있는 것을 특징으로 하는 박막 트랜지스터 기판.

#### 청구항 5.

박막 트랜지스터 기판을 제조하는 방법에 있어서,

절연기판 상에 게이트 배선을 형성하는 단계와;

상기 게이트 배선 상에 액티브층을 형성하는 단계와; 및

상기 액티브층 상에 상기 게이트 배선과 교차영역을 가지며 형성되는 데이터 배선을 형성하는 단계를 포함하는 하는 박막 트랜지스터 기판의 제조방법에 있어서,

상기 액티브층은 상기 교차영역에서 상기 데이터 배선의 길이방향의 양 측면 중 적어도 어느 일측을 넘어서 형성된 연장부를 가지는 것을 특징으로 하는 박막 트랜지스터 기판의 제조방법.

## 청구항 6.

제5항에 있어서,

상기 액티브층은 상기 게이트 배선 영역 내에 형성되는 것을 특징으로 하는 박막 트랜지스터 기판의 제조방법.

## 청구항 7.

제 1 기판과;

상기 제 1 기판과 대향 배치되며 게이트 배선과, 상기 게이트 배선과 교차영역을 가지며 형성되는 데이터 배선과, 상기 게이트 배선과 상기 데이터 배선 사이에 개재되어 있는 액티브층을 포함하는 제 2 기판과;

상기 제 1 기판과 상기 제 2 기판사이에 주입되는 액정을 포함하는 액정 표시 패널에 있어서,

상기 액티브층은 상기 교차영역에서 상기 데이터 배선의 길이 방향의 양 측면 중 적어도 어느 일측을 넘어서 형성된 연장부를 포함하는 것을 특징으로 하는 액정 표시 패널.

## 청구항 8.

제7항에 있어서,

상기 액티브층은 상기 게이트 배선의 영역 내에 형성되어 있는 것을 특징으로 하는 액정 표시 패널.

## 청구항 9.

제7항에 있어서,

상기 게이트 배선은 게이트 라인과, 상기 게이트 라인과 상기 데이터 배선의 상기 교차영역에서 라인의 폭이 증가하는 게이트 전극을 포함하며,

상기 액티브층은 상기 게이트 전극 상에 위치하며 상기 연장부는 상기 게이트 라인상에 위치하고 있는 것을 특징으로 하는 액정 표시 패널.

## 청구항 10.

제7항에 있어서,

상기 데이터 배선은 데이터 라인과, 상기 데이터 라인에서 분기되어 J 또는 U형으로 형성된 소스전극을 포함하며,

상기 연장부는 상기 소스전극의 외측방향으로 연장되어 있는 것을 특징으로 하는 액정 표시 패널.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

|                |                                                           |         |            |

|----------------|-----------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管基板，其制造方法以及液晶显示面板                                     |         |            |

| 公开(公告)号        | <a href="#">KR1020060057308A</a>                          | 公开(公告)日 | 2006-05-26 |

| 申请号            | KR1020040096416                                           | 申请日     | 2004-11-23 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                  |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                  |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                  |         |            |

| [标]发明人         | KIM HYUKJIN<br>김현진<br>SEO DONGWUUK<br>서동욱                 |         |            |

| 发明人            | 김현진<br>서동욱                                                |         |            |

| IPC分类号         | G02F1/136                                                 |         |            |

| CPC分类号         | H01L27/1222 G02F1/136286 G02F1/1368 H01L27/124 H01L27/127 |         |            |

| 代理人(译)         | PARK , YOUNG WOO                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                 |         |            |

## 摘要(译)

一种薄膜晶体管基板，包括栅极布线，形成为具有与栅极布线交叉区域的数据布线，以及插入在栅极布线和数据布线之间的有源层，并且，在该区域中的数据线的两个纵向侧的至少一侧上形成延伸部分。结果，可以增加由栅极布线和数据布线之间的台阶引起的阶梯开口的CVD修复成功率。 4