## (19) 대한민국특허청(KR)

### (12) 공개특허공보(A)

(51) Int. Cl.

G02F 1/1343 (2006.01)

(11) 공개번호

10-2006-0019224

(43) 공개일자

2006년03월03일

(21) 출원번호 10-2004-0067773

(22) 출원일자 2004년08월27일

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 서희상

충청남도 천안시 성정동 주공5단지 106-403

(74) 대리인 박영우

**심사청구 : 없음**

### (54) 표시장치용 기판, 이를 갖는 액정 표시 장치 및 그 불량제거 방법

#### 요약

게이트 라인들은 게이트 신호를 전달한다. 상기 데이터 라인들은 상기 게이트 라인들과 교차되도록 배치되고, 데이터 신호를 전달한다. 리페어 패턴들은 상기 각 데이터 라인들의 일부와 오버랩되도록 배치되고, 스토리지 캐패시터 패턴들과 전기적으로 연결된다. 브릿지 패턴들은 서로 인접하는 스토리지 캐패시터 패턴들을 전기적으로 연결한다. 화소 전극들은 서로 인접하는 게이트 라인들 및 데이터 라인들에 의해 정의되는 영역 내에 배치되고, 상기 각 스토리지 캐패시터 패턴들과 오버랩되어 스토리지 캐패시터를 형성한다. 스위칭 소자들은 상기 게이트 신호에 응답하여 상기 데이터 신호를 상기 각 화소 전극들에 인가한다. 따라서, 액정 표시 장치의 개구율이 향상되고 불량이 용이하게 제거되어 화질이 향상된다.

#### 내표도

도 18

#### 명세서

##### 도면의 간단한 설명

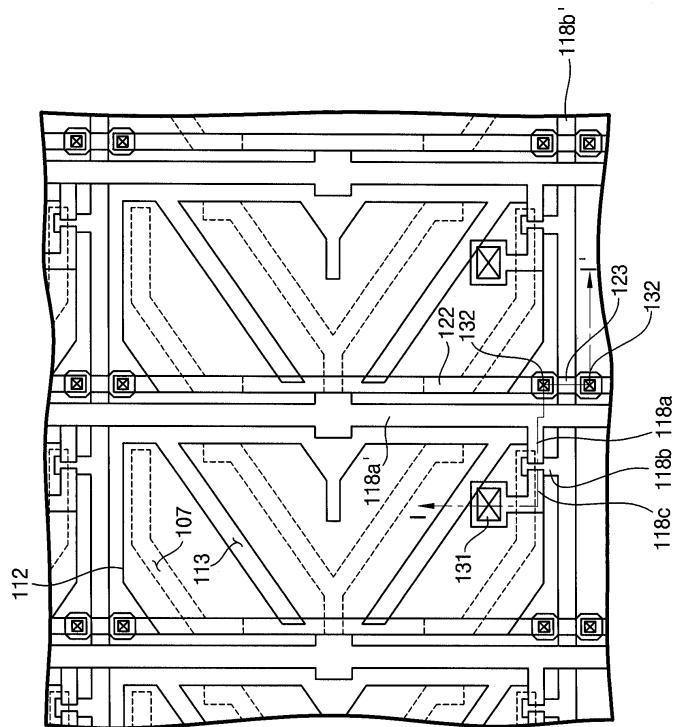

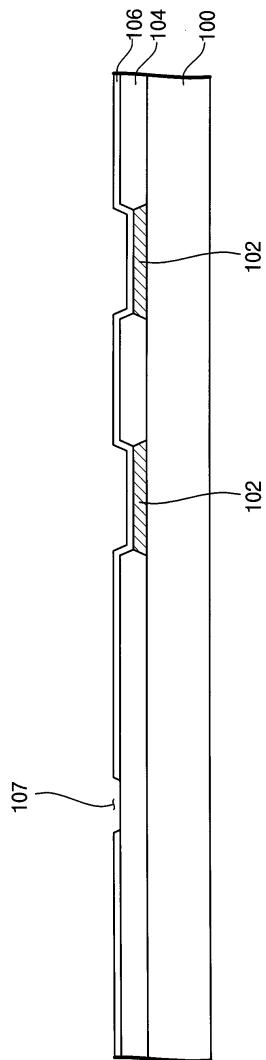

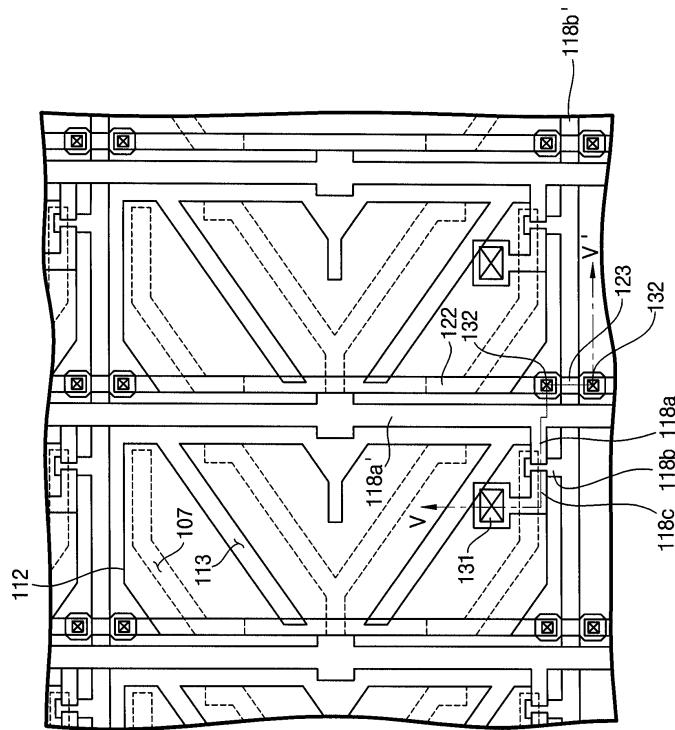

도 1은 본 발명의 제1 실시예에 따른 액정 표시 장치를 나타내는 평면도이다.

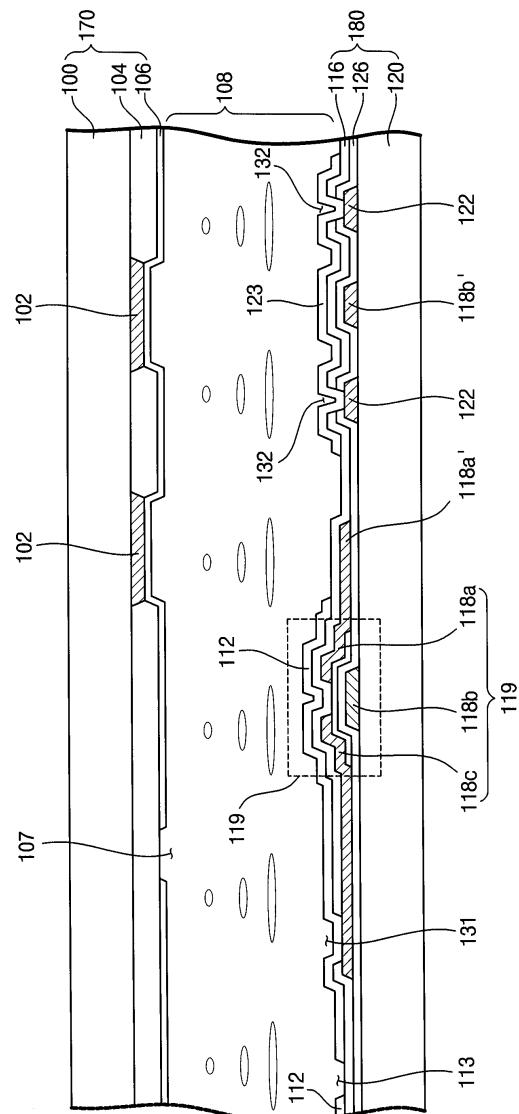

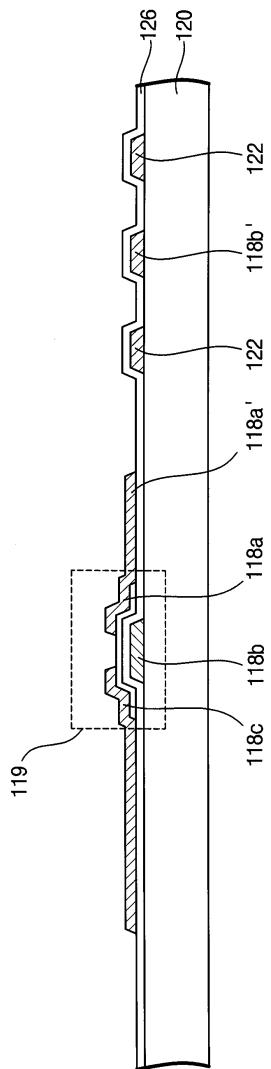

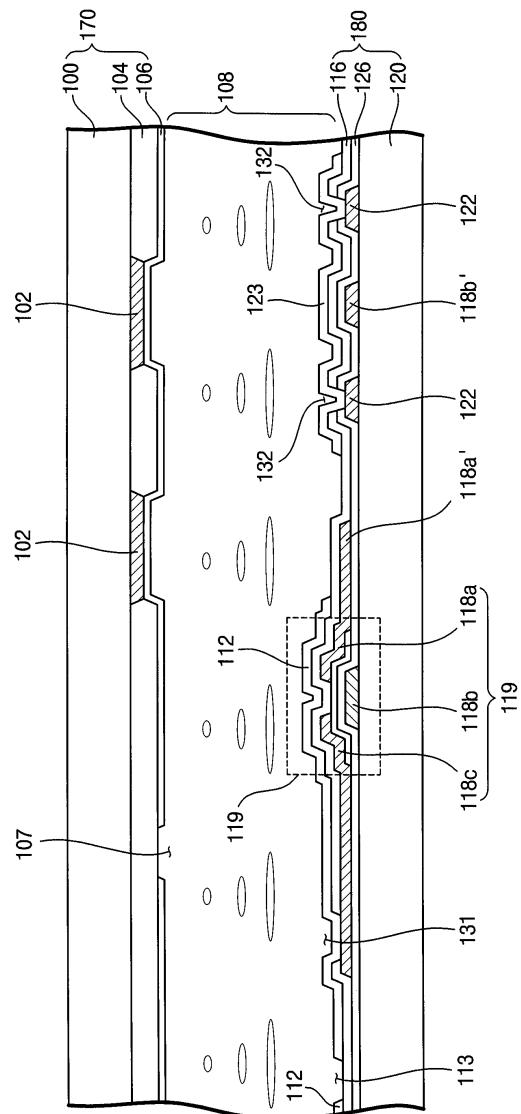

도 2는 상기 도 1의 I-I'라인의 단면도이다.

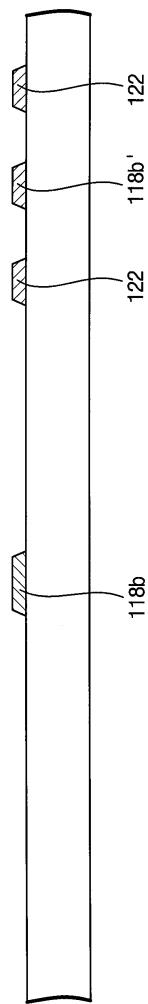

도 3은 상기 도 1의 게이트 전극, 게이트 라인, 스토리지 캐패시터 패턴 및 리페어 패턴을 나타내는 평면도이다.

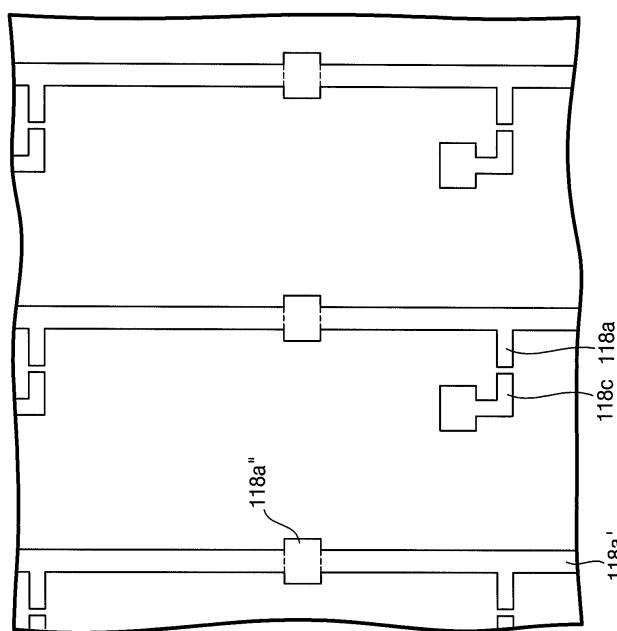

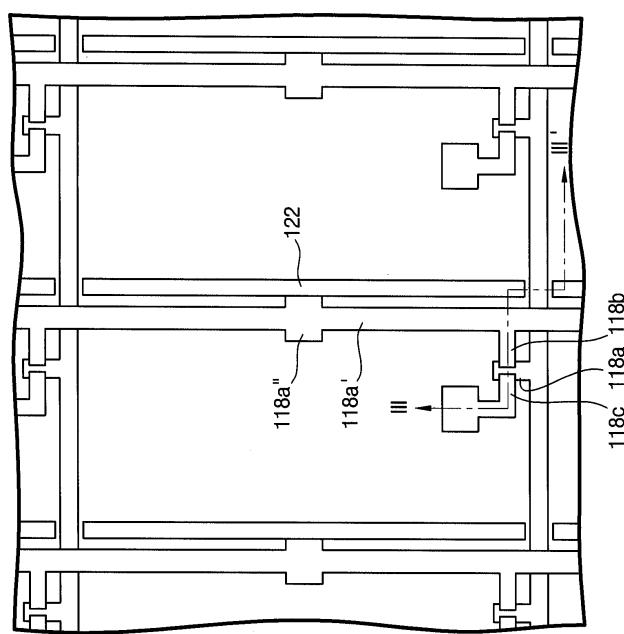

도 4는 상기 도 1의 소오스 전극, 데이터 라인, 드레인 전극 및 리페어 부분을 나타내는 평면도이다.

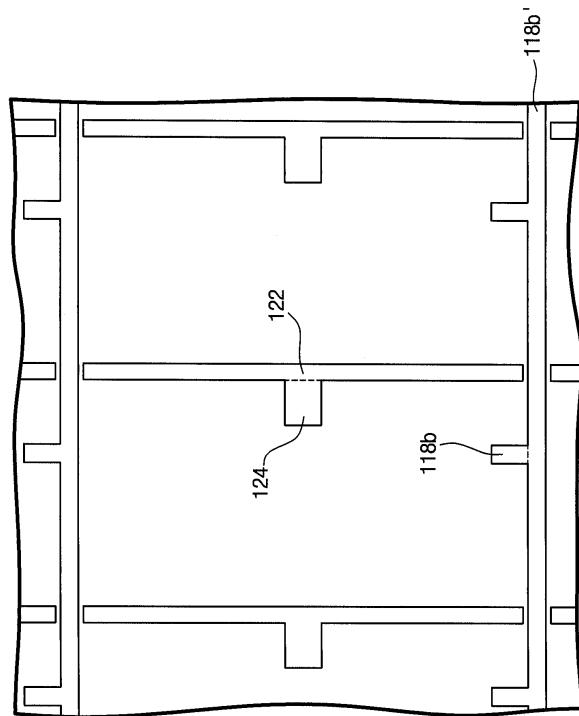

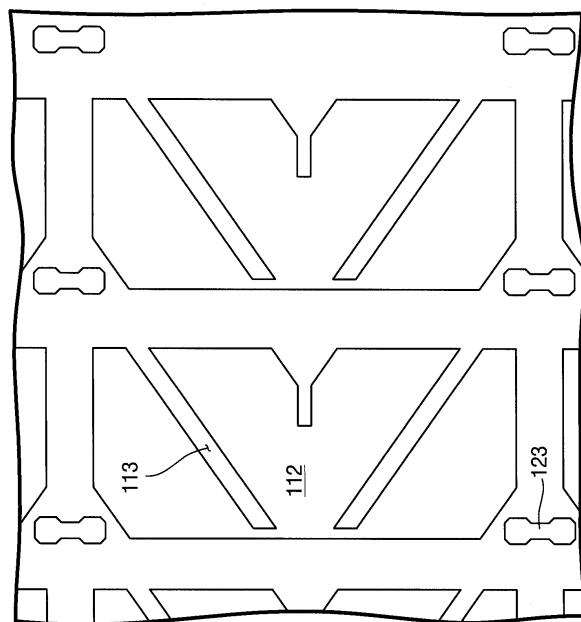

도 5는 상기 도 1의 화소 전극 및 브릿지 패턴을 나타내는 평면도이다.

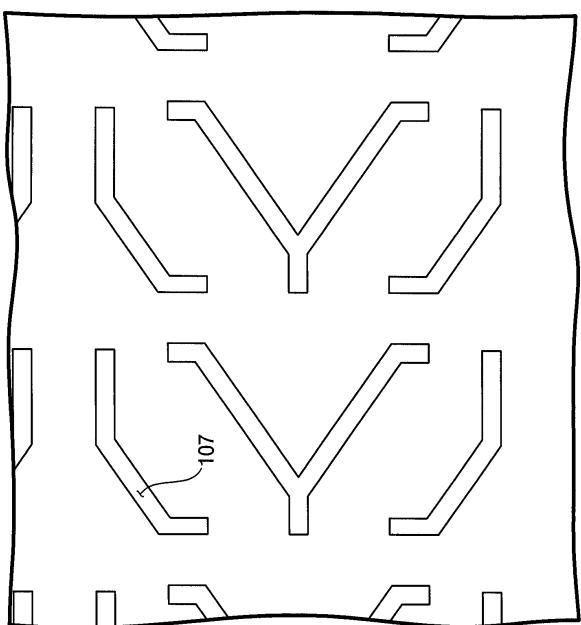

도 6은 상기 도 1의 공통 전극을 나타내는 평면도이다.

도 7 내지 도 15는 본 발명의 제1 실시예에 따른 액정 표시 장치의 제조방법을 나타낸다.

도 16은 도 1에 도시된 액정 표시 장치에 발생한 불량을 나타내는 평면도이다.

도 17은 상기 도 16의 VI-VI'라인의 단면도이다.

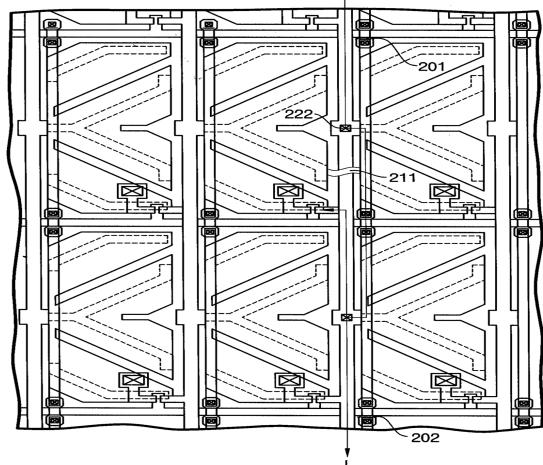

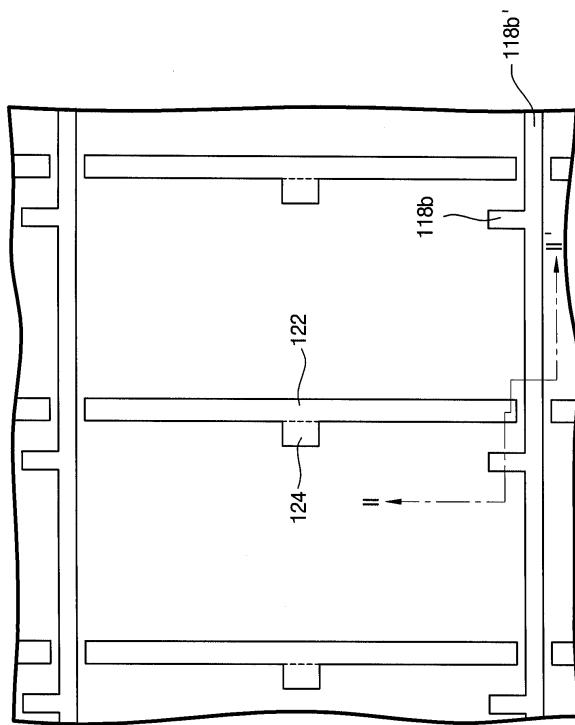

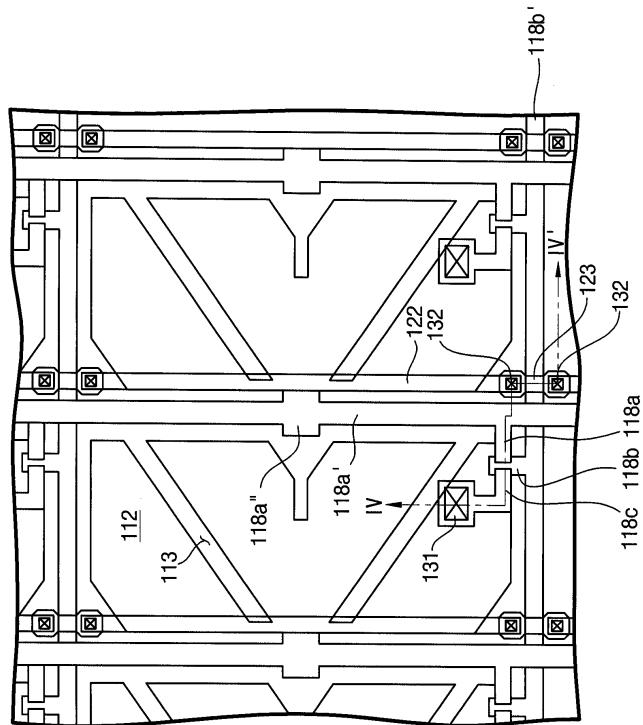

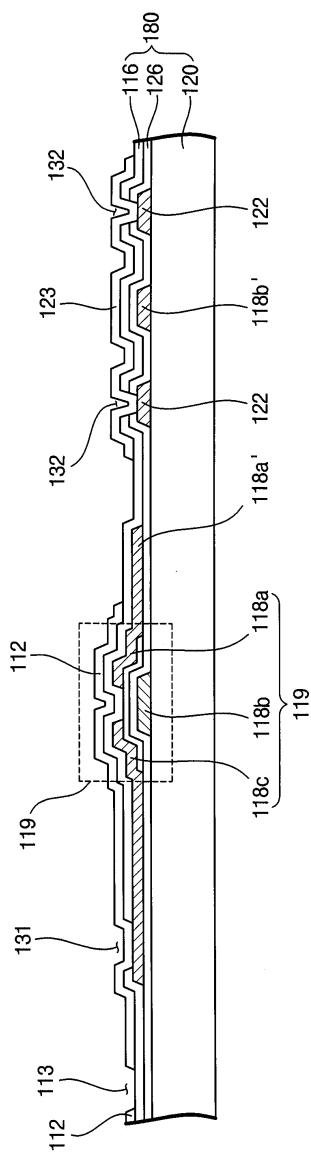

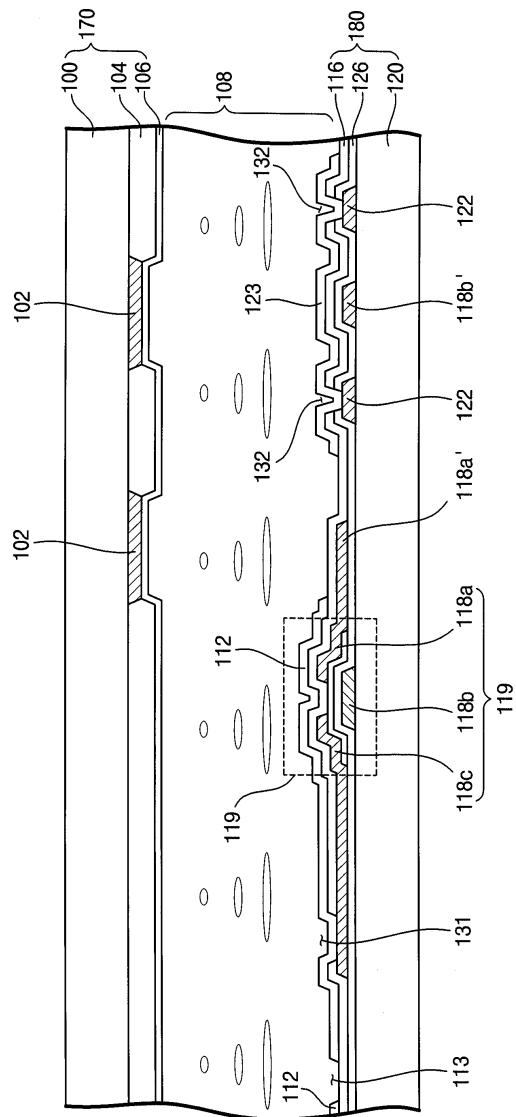

도 18은 본 발명의 제1 실시예에 따른 액정 표시 장치의 불량 제거 방법을 나타내는 평면도이다.

도 19는 본 발명의 제2 실시예에 따른 액정 표시 장치를 나타내는 평면도이다.

도 20은 상기 도 19의 VII-VII'라인의 단면도이다.

\* 도면의 주요부분에 대한 부호의 설명 \*

100 : 상부 플레이트 102 : 블랙 매트릭스

104 : 컬러 필터 106 : 공통 전극

107 : 제1 그루부(Groove) 108 : 액정층

112 : 화소 전극 113 : 제2 그루부(Groove)

116 : 패시베이션막 118a : 소오스 전극

118a' : 데이터 라인 118a'' : 리페어 부분

118b : 게이트 전극 118b' : 게이트 라인

118c : 드레인 전극 119 : 박막 트랜지스터

120 : 하부 플레이트 122 : 스토리지 캐패시터 패턴

123 : 브릿지 패턴 124 : 리페어 패턴

131 : 제1 콘택홀 132 : 제2 콘택홀

170 : 제1 기판 180 : 제2 기판

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 표시장치용 기판, 이를 갖는 액정 표시 장치 및 그 불량 제거 방법에 관한 것으로 보다 상세하게는 화질이 향상된 표시 장치용 기판, 이를 갖는 액정 표시 장치 및 그 불량 제거 방법에 관한 것이다.

액정 표시 장치(Liquid Crystal Display, LCD)는 박막 트랜지스터가 형성된 어레이 기판(Array Substrate) 및 대향 기판(Counter Substrate) 사이에 주입되어 있는 이방성 유전율을 갖는 액정 물질에 전계(Electric Field)를 인가하고, 이 전계의 세기를 조절하여 기판에 투과되는 광의 양을 조절함으로써 원하는 화상 신호를 얻는 표시 장치이다.

상기 어레이 기판은 박막 트랜지스터, 게이트 라인 및 데이터 라인을 포함한다. 상기 박막 트랜지스터는 상기 게이트 라인과 전기적으로 연결된 게이트 전극, 상기 데이터 라인과 전기적으로 연결된 소오스 전극, 드레인 전극 및 반도체층 패턴을 포함한다. 상기 박막 트랜지스터, 상기 게이트 라인 및 상기 데이터 라인은 복수회의 박막 증착 공정을 통하여 형성된다.

이때, 상기 박막 증착 공정 중에 식각 불량이 발생하는 경우, 상기 게이트 전극이 상기 게이트 라인과 전기적으로 절연될 수 있다. 또한, 상기 박막 증착 공정 중에 불순물이 존재하는 경우, 상기 게이트 전극이 상기 소오스 전극 또는 상기 드레인 전극과 단락될 수 있다.

상기 게이트 전극이 상기 게이트 라인과 전기적으로 절연되는 경우, 상기 어레이 기판의 화소 전극과 상기 대향 기판의 공통 전극의 사이에 전압이 인가되지 않는다.

상기 게이트 전극이 상기 소오스 전극 또는 상기 드레인 전극과 단락되는 경우, 상기 박막 트랜지스터가 오작동하여 콘트라스트비가 감소한다.

특히, 상기 콘트라스트비가 감소하는 경우, 상기 액정 표시 장치의 화질이 급격히 감소한다.

또한, 상기 어레이 기판은 상기 화소 전극과 상기 공통 전극 사이의 전위차를 한 프레임동안 유지시켜주는 스토리지 캐퍼시터를 포함할 수 있다. 상기 스토리지 캐퍼시터가 별도의 스토리지 라인을 포함하는 경우, 상기 스토리지 라인의 형상에 따라 상기 액정 표시 장치의 개구율이 감소할 수 있다. 상기 개구율은 상기 액정 표시 장치의 전체 화소면적과 실제로 상기 광이 통과하는 화소면적의 비를 나타낸다. 상기 액정 표시 장치의 개구율이 감소하는 경우, 상기 액정 표시 장치의 휙도가 감소한다.

### 발명이 이루고자 하는 기술적 과제

상기와 같은 문제점을 해결하기 위한 본 발명의 제1 목적은, 화질이 향상된 표시장치용 기판을 제공하는데 있다.

본 발명의 제2 목적은 화질이 향상된 액정 표시 장치를 제공하는데 있다.

본 발명의 제3 목적은 상기 표시장치용 기판의 불량을 제거하는 방법을 제공하는데 있다.

### 발명의 구성 및 작용

상기 제1 목적을 달성하기 위한 본 발명의 일 실시예에 따른 표시장치용 기판은 복수의 게이트 라인들, 복수의 스토리지 캐퍼시터 패턴들, 복수의 데이터 라인들, 복수의 리페어 패턴들, 복수의 브릿지 패턴들, 복수의 화소 전극들 및 복수의 스위칭 소자들을 포함한다. 상기 게이트 라인들은 플레이트 상에 배치되고 게이트 신호를 전달한다. 상기 스토리지 캐퍼시터 패턴들은 상기 플레이트 상에 배치된다. 상기 데이터 라인들은 상기 게이트 라인들과 교차되도록 배치되고, 데이터 신호를 전달한다. 상기 리페어 패턴들은 상기 플레이트 상에 상기 각 데이터 라인들의 일부와 오버랩되도록 배치되고, 상기 스토리지 캐퍼시터 패턴들과 전기적으로 연결된다. 상기 브릿지 패턴들은 서로 인접하는 스토리지 캐퍼시터 패턴들을 전기적으로 연결한다. 상기 화소 전극들은 서로 인접하는 게이트 라인들 및 데이터 라인들에 의해 정의되는 영역 내에 배치되고, 상기 각 스토리지 캐퍼시터 패턴들과 오버랩되어 스토리지 캐퍼시터를 형성한다. 상기 스위칭 소자들은 상기 플레이트 상에 배치되고, 상기 게이트 신호에 응답하여 상기 데이터 신호를 상기 각 화소 전극들에 인가한다.

상기 제2 목적을 달성하기 위한 본 발명의 일 실시예에 따른 액정 표시 장치는 제1 기판, 제2 기판 및 액정층을 포함한다. 상기 제1 기판은 상부 플레이트 및 상기 상부 플레이트 상에 배치된 공통 전극을 구비한다. 상기 제2 기판은 하부 플레이트 상에 배치되고 게이트 신호를 전달하는 복수의 게이트 라인들과, 상기 하부 플레이트 상에 배치되는 복수의 스토리지 캐퍼시터 패턴들과, 상기 게이트 라인들과 교차되도록 배치되고 데이터 신호를 전달하는 복수의 데이터 라인들과, 상기 플레이트 상에 상기 각 데이터 라인들의 일부와 오버랩되도록 배치되고 상기 스토리지 캐퍼시터 패턴들과 전기적으로 연결되는 복수의 리페어 패턴들과, 서로 인접하는 스토리지 캐퍼시터 패턴들을 전기적으로 연결하는 복수의 브릿지 패턴들과, 서로 인접하는 게이트 라인들 및 데이터 라인들에 의해 정의되는 영역 내에 배치되고 상기 각 스토리지 캐퍼시터 패턴들과 오버랩되어 스토리지 캐퍼시터를 형성하는 복수의 화소 전극들과, 상기 플레이트 상에 배치되고 상기 게이트 신호에 응답하여 상기 데이터 신호를 상기 각 화소 전극들에 인가하는 복수의 스위칭 소자들을 포함한다. 상기 제2 기판은 상기 제1 기판에 대향한다. 상기 액정층은 상기 제1 기판과 상기 제2 기판의 사이에 배치된다.

상기 제3 목적을 달성하기 위한 본 발명의 일 실시예에 따른 표시장치용 기판의 불량을 제거하기 위하여, 먼저 오픈된 부분을 갖는 데이터 라인과 평행하게 배열되고 복수의 브릿지 패턴들을 통하여 서로 전기적으로 연결되어 스토리지 캐패시터 라인을 형성하는 복수의 스토리지 캐패시터 패턴들 중에서 상기 오픈된 부분에 인접하는 두 개의 스토리지 캐패시터 패턴들에 전기적으로 연결되는 리페어 패턴들과 상기 데이터 라인을 전기적으로 연결한다. 이어서, 상기 리페어 패턴들을 기준으로 상기 오픈된 부분의 맞은편에 배치된 브릿지 패턴들을 오픈시킨다.

상기와 같은 본 발명에 따르면, 상기 액정 표시 장치의 개구율이 향상되어 휙도가 상승한다. 또한, 상기 액정 표시 장치의 수리가 용이하여 액정 표시 장치의 제조비용 및 수리비용이 감소하고 수율이 향상된다. 따라서, 상기 액정 표시 장치의 화질이 향상된다.

아하, 본 발명에 따른 바람직한 실시예들을 첨부된 도면을 참조하여 상세하게 설명한다.

### 실시예 1

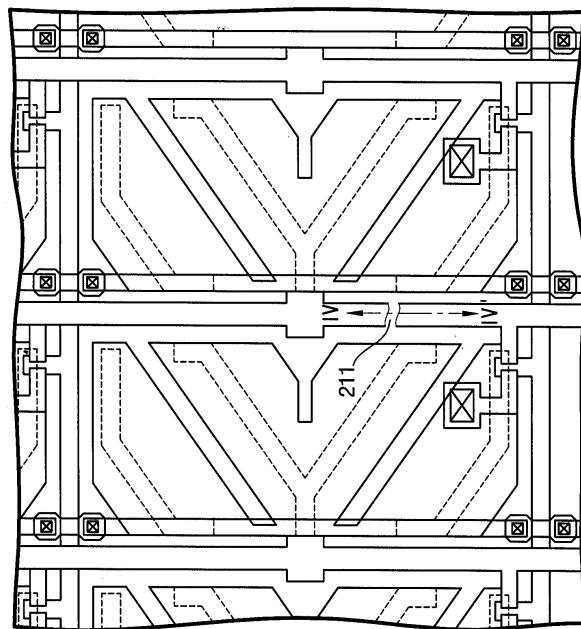

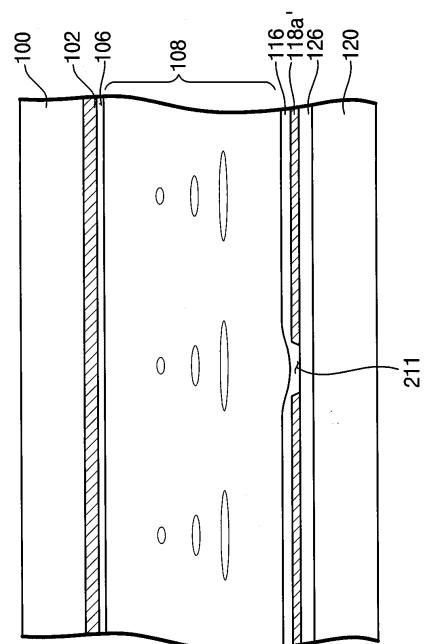

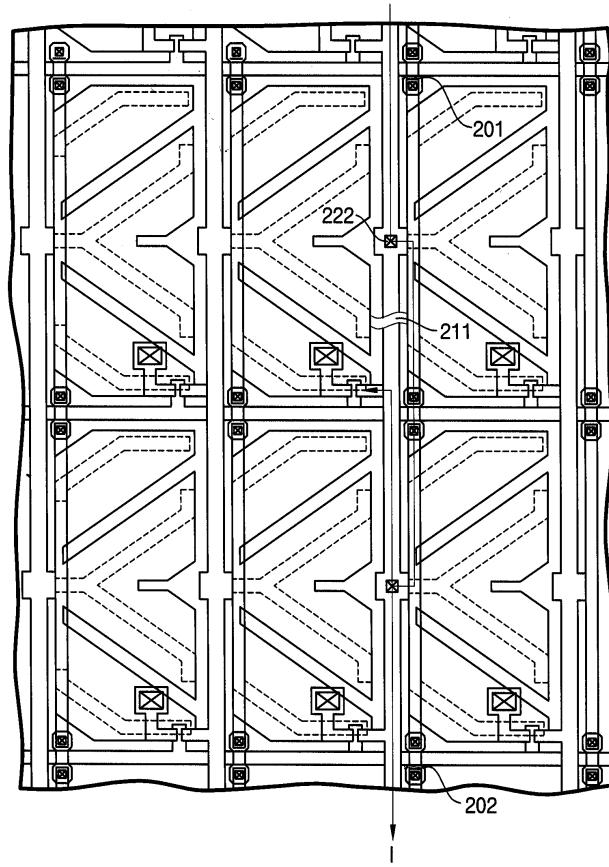

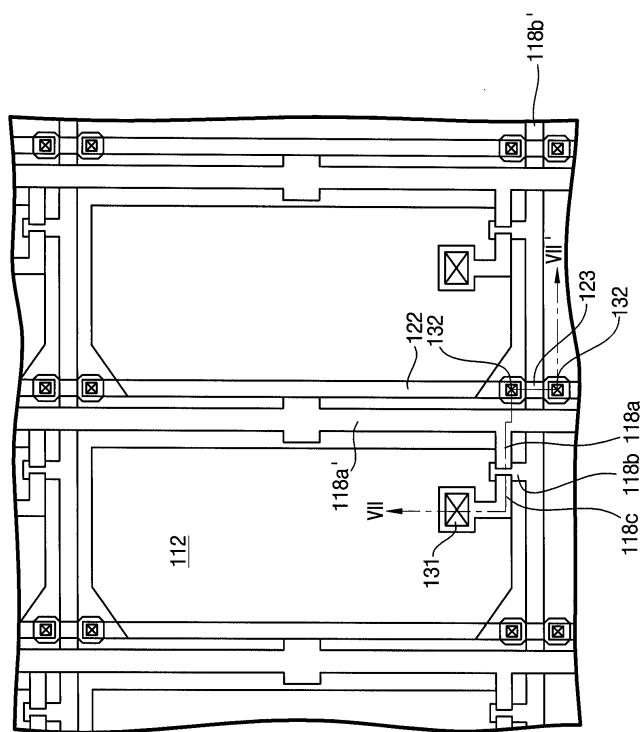

도 1은 본 발명의 제1 실시예에 따른 액정 표시 장치를 나타내는 평면도이고, 도 2는 상기 도 1의 I-I'라인의 단면도이다. 또한, 도 3은 상기 도 1의 게이트 전극, 게이트 라인, 스토리지 캐패시터 패턴 및 리페어 패턴을 나타내는 평면도이고, 도 4는 상기 도 1의 소오스 전극, 데이터 라인, 드레인 전극 및 리페어 부분을 나타내는 평면도이며, 도 5는 상기 도 1의 화소 전극 및 브릿지 패턴을 나타내는 평면도이고, 도 6은 상기 도 1의 공통 전극을 나타내는 평면도이다.

도 1 내지 도 6을 참조하면, 상기 액정 표시 장치는 제1 기판(170), 제2 기판(180) 및 액정층(108)을 포함한다.

상기 제1 기판(170)은 상부 플레이트(100), 블랙 매트릭스(102), 컬러 필터(104) 및 공통 전극(106)을 포함한다.

상기 제2 기판(180)은 하부 플레이트(120), 복수의 박막 트랜지스터(119), 복수의 스토리지 캐패시터 패턴(122), 복수의 브릿지 패턴(123), 복수의 리페어 부분들(118a')을 갖는 복수의 데이터 라인(118a'), 복수의 게이트 라인(118b'), 게이트 절연막(126), 패시베이션막(116), 복수의 화소 전극(112) 및 복수의 리페어 패턴(123)을 포함한다.

상기 액정 표시 장치는 복수의 화소들을 포함하고, 상기 화소들은 서로 인접하는 상기 데이터 라인들(118a')과 상기 게이트 라인들(118b')에 의해 정의된다.

상기 액정층(108)은 상기 제1 기판(170) 및 상기 제2 기판(180)의 사이에 배치된다.

상기 상부 플레이트(100) 및 상기 하부 플레이트(120)는 광을 통과시킬 수 있는 투명한 재질의 유리를 사용한다. 상기 유리는 무알칼리 특성이다. 상기 유리가 알칼리 특성인 경우, 상기 유리에서 알칼리 이온이 액정 셀 중에 용출되면 액정 비저항이 저하되어 표시 특성이 변하게 되고, 셀런트(Sealant)와 유리와의 부착력을 저하시키고, 스위칭 소자의 동작에 악영향을 준다.

이때, 상기 상부 플레이트(100) 및 상기 하부 플레이트(120)는 트리아세틸셀룰로오스 (Triacetylcellulose; TAC), 폴리카보네이트 (Polycarbonate; PC), 폴리에테르설폰 (Polyethersulfone; PES), 폴리에틸렌테라프탈레이트 (Polyethyleneterephthalate; PET), 폴리에틸렌나프탈레이트 (Polyethylenenaphthalate; PEN), 폴리비닐알콜 (Polyvinylalcohol; PVA), 폴리메틸메타아크릴레이트 (Polymethylmethacrylate; PMMA), 싸이클로올핀 폴리머 (Cyclo-Olefin Polymer; COP) 등을 포함할 수도 있다.

바람직하게는, 상기 상부 플레이트(100) 및 상기 하부 플레이트(120)는 광학적으로 등방성이다.

상기 박막 트랜지스터(119)는 상기 화소에 대응하는 상기 하부 플레이트(120) 상에 배치되며, 소오스 전극(118a), 게이트 전극(118b), 드레인 전극(118c) 및 반도체층 패턴을 포함한다. 데이터 구동부(도시되지 않음)는 데이터 전압을 출력하여 상기 데이터 라인(118a')을 통하여 상기 소오스 전극(118a)에 인가하고, 게이트 구동부(도시되지 않음)는 선택 신호를 출력하여 상기 게이트 라인(118b')을 통하여 상기 게이트 전극(118b)에 인가한다.

상기 게이트 라인(118b')은 상기 하부 플레이트(120) 상에 배치되어 상기 게이트 전극(118b)과 전기적으로 연결된다.

상기 스토리지 캐패시터 패턴들(122)은 상기 하부 플레이트(120) 상에 상기 게이트 전극(118b) 및 상기 게이트 라인(118b')과 이격되어 배치된다. 상기 스토리지 캐패시터 패턴들(122)은 상기 데이터 라인들(118a')과 나란하게 배열된다. 상기 스토리지 캐패시터 패턴들(122)은 상기 화소 전극(112)의 일부와 오버랩되어 스토리지 캐패시터를 형성된다. 상기 스토리지 캐패시터 패턴들(122)은 상기 브릿지 패턴들(123)을 통하여 서로 전기적으로 연결되어 스토리지 캐패시터 라인을 형성한다. 상기 스토리지 캐패시터 라인의 양단에는 공통 전압이 인가된다. 다른 실시예에 의할 경우, 상기 스토리지 캐패시터 패턴들이 상기 데이터 라인들과 나란하게 배열된 제1 캐패시터 부분들, 상기 게이트 라인들과 나란하게 배열되고 상기 제1 캐패시터 부분들과 전기적으로 연결되는 제2 캐패시터 부분들, 및 'V'형상으로 배열되고 상기 제1 캐패시터 부분들 및 상기 제2 캐패시터 부분들과 전기적으로 연결된 제3 캐패시터 부분들을 더 포함할 수도 있다.

상기 리페어 패턴들(124)은 상기 스토리지 캐패시터 패턴들(122)로부터 돌출되어 상기 데이터 라인(118a')의 상기 리페어 부분(118a'')과 오버랩된다. 이때, 상기 스토리지 캐패시터 패턴의 일부가 상기 데이터 라인의 일부와 오버랩되어 상기 리페어 패턴을 형성할 수도 있다.

상기 게이트 절연막(126)은 상기 게이트 전극(118b), 상기 게이트 라인(118b') 및 상기 스토리지 캐패시터 패턴들(122)이 형성된 상기 하부 플레이트(120) 상에 배치되어 상기 게이트 전극(118b), 상기 게이트 라인(118b') 및 상기 스토리지 캐패시터 패턴들(122)을 상기 소오스 전극(118a), 상기 드레인 전극(118c) 및 상기 데이터 라인(118a')과 전기적으로 절연한다. 상기 게이트 절연막(126)은 실리콘 질화물(SiNx), 실리콘 산화물(SiOx) 등을 포함한다. 상기 게이트 절연막(126)은 상기 스토리지 캐패시터 패턴들(122)의 단부를 노출하는 하부 개구부들을 포함한다.

상기 데이터 라인(118a')은 상기 게이트 절연막(126) 상에 배치되고 상기 박막 트랜지스터(119)의 상기 소오스 전극(118a)과 전기적으로 연결된다. 상기 데이터 라인(118a')은 상기 리페어 패턴(124)에 대응하는 상기 리페어 부분(118a'')을 포함한다. 상기 리페어 패턴(124)과 상기 리페어 부분(118a'')은 상기 게이트 절연막(126)에 의해 절연된다. 상기 리페어 부분(118a'') 상에 레이저가 조사되는 경우, 상기 리페어 패턴(124)과 상기 리페어 부분(118a'')을 전기적으로 연결하는 리페어 콘택홀(도시되지 않음)이 형성되어 상기 데이터 라인(118a')과 상기 스토리지 캐패시터 패턴(122)이 전기적으로 연결된다. 본 실시예에서, 상기 리페어 부분(118a'')의 폭은 상기 데이터 라인(118a')의 나머지 부분의 폭보다 크다. 이때, 상기 리페어 부분의 폭이 상기 데이터 라인의 폭과 동일할 수도 있다.

상기 패시베이션막(116)은 상기 박막 트랜지스터(119)가 형성된 상기 하부 플레이트(120) 상에 배치되고, 상기 드레인 전극(118c)의 일부를 노출하는 제1 콘택홀(131) 및 상기 스토리지 캐패시터 패턴들(122)의 단부를 노출하는 상부 개구부들을 포함한다. 상기 게이트 절연막(126)의 상기 하부 개구부와 상기 패시베이션막(116)의 상기 상부 개구부는 제2 콘택홀(132)을 형성한다. 상기 패시베이션막(116)은 실리콘 질화물(SiNx), 실리콘 산화물(SiOx) 등을 포함한다. 이때, 상기 패시베이션막(116) 상에 유기막(도시되지 않음)을 형성하여 상기 액정층(108)의 두께를 조절하고 상기 박막 트랜지스터(119)를 보호할 수도 있다.

상기 화소 전극(112)은 상기 화소에 대응하는 상기 패시베이션막(116)의 표면 및 상기 제1 콘택홀(131)의 내면 상에 형성되어 상기 드레인 전극(118c)과 전기적으로 연결된다. 상기 화소 전극(112)은 'V' 형상으로 배열된 제2 그루부(Groove, 113)를 포함한다. 이때, 상기 화소 전극 상에 'V' 형상으로 배열된 합성수지를 포함하는 제2 돌기(도시되지 않음)가 형성되어 상기 다중 영역을 형성할 수도 있다. 또한, 상기 화소 전극(112)이 복수의 제2 그루부들을 포함할 수도 있고, 복수의 제2 패턴들(도시되지 않음)을 포함할 수도 있다. 상기 화소 전극(112)은 상기 공통 전극(106)과의 사이에 인가된 전압에 의해 상기 액정층(108) 내의 액정을 제어하여 광의 투과를 조절한다. 상기 화소 전극(112)에 상기 전압이 인가되는 경우, 상기 제2 그루부(113)에 인접하는 부분에 전계가 왜곡되어 상기 액정층(108) 내에 다중 영역(Multi Domain)이 형성된다.

상기 화소 전극(112)은 투명한 도전성 물질인 산화 주석 인듐(Indium Tin Oxide, ITO), 산화 아연 인듐(Indium Zinc Oxide, IZO), 산화 아연(Zinc Oxide, ZO), 산화 인듐(Indium Oxide, IO) 등을 포함한다. 이때, 상기 화소 전극이 반사율이 높은 물질을 갖는 반사 전극을 포함할 수도 있다. 또한, 상기 화소 전극이 상기 투명한 도전성 물질을 갖는 투명 전극 및 상기 투명 전극 상에 배치되고 반사율이 높은 물질을 갖는 반사 전극을 포함할 수도 있다.

상기 블랙 매트릭스(102)는 상기 데이터 라인(118a') 및 상기 게이트 라인(118b')에 대응하는 상기 상부 플레이트(100) 상에 형성되어 광을 차단한다. 상기 블랙 매트릭스(102)는 액정을 제어할 수 없는 영역을 통과하는 광을 차단하여 화질을 향상시킨다.

상기 블랙 매트릭스(102)는 금속 또는 금속화합물을 증착하고 식각하여 형성된다. 상기 금속은 크롬(Cr) 등을 포함하고, 상기 금속화합물은 산화 크롬(CrO<sub>x</sub>), 질화 크롬(CrNx) 등을 포함한다. 또한, 상기 블랙 매트릭스(102)는 포토 레지스트 성분을 포함하는 불투명한 유기물을 도포한 후에, 사진 공정을 통해 상기 도포된 유기물을 부분적으로 제거하여 형성될 수 있다. 상기 불투명한 유기물은 카본 블랙(Carbon Black), 안료 혼합물, 염료 혼합물 등을 포함한다. 상기 안료 혼합물은 적색, 녹색 및 청색 안료를 포함하고, 상기 염료 혼합물은 적색, 녹색 및 청색 염료를 포함한다. 이때, 복수의 컬러 필터들(104)을 오버랩하여 상기 제2 기판(180)의 상기 패시베이션막(116) 상에 블랙 매트릭스를 형성할 수도 있다.

상기 컬러 필터(104)는 상기 블랙 매트릭스(102)가 형성된 상기 상부 플레이트(100) 상에 배치되어 소정의 파장을 갖는 광만을 투과시킨다. 상기 컬러 필터(104)는 적색 컬러 필터부, 녹색 컬러 필터부 및 청색 컬러 필터부를 포함한다. 상기 컬러 필터(104)는 광중합 개시제, 모노머, 바인더, 안료, 분산제, 용제, 포토레지스트 등을 포함한다.

상기 공통 전극(106)은 상기 블랙 매트릭스(102) 및 상기 컬러 필터(104)가 형성된 상기 상부 플레이트(100) 상에 배치된다. 상기 공통 전극(106)은 상기 제2 그루부(113)에 대응하여 'V' 형상으로 배열된 제1 그루부(Groove, 107)를 포함한다. 이때, 상기 공통 전극 상에 'V' 형상으로 배열된 합성수지를 포함하는 제1 돌기(도시되지 않음)가 형성되어 상기 다중 영역을 형성할 수도 있다. 이때, 상기 공통 전극(106)이 복수의 제2 그루부들을 포함할 수도 있고, 복수의 제2 패턴들(도시되지 않음)을 포함할 수도 있다. 본 실시예에서, 상기 제1 그루부(107) 및 상기 제2 그루부(113)는 서로 엇갈리게 배치된다. 상기 공통 전극(106)에 상기 전압이 인가되는 경우, 상기 제1 그루부(107)에 인접하는 부분에 전계가 왜곡되어 상기 액정층(108) 내에 다중 영역(Multi Domain)이 형성된다. 상기 다중 영역은 상기 제1 그루부(107) 및 상기 제2 그루부(113)에 의해 강화되어 상기 액정 표시 장치의 시야각(Viewing Angle)이 향상된다. 상기 시야각은 상기 액정 표시 장치의 정면 방향을 기준으로 콘트라스트비가 10:1인 각도이다.

도 7 내지 도 15는 본 발명의 제1 실시예에 따른 액정 표시 장치의 제조방법을 나타낸다.

도 7은 본 발명의 제1 실시예에 따른 액정 표시 장치의 제조방법을 나타내는 평면도이고, 도 8은 상기 도 7의 II-II'라인의 단면도이다.

도 7 및 도 8을 참조하면, 먼저 상기 하부 플레이트(120) 상에 도전성 물질을 증착한다. 이때, 둘 이상의 금속을 적층하여 복합층을 형성할 수도 있다. 이어서, 상기 증착된 도전성 물질의 일부를 식각하여 상기 게이트 전극(118b), 상기 게이트 라인(118b'), 상기 스토리지 캐패시터 패턴(122) 및 상기 리페어 패턴(124)을 형성한다.

도 9는 본 발명의 제1 실시예에 따른 액정 표시 장치의 제조방법을 나타내는 평면도이고, 도 10은 상기 도 9의 III-III'라인의 단면도이다.

도 9 및 도 10을 참조하면, 이후에 상기 게이트 전극(118b), 상기 게이트 라인(118b'), 상기 스토리지 캐패시터 패턴(122) 및 상기 리페어 패턴(124)이 형성된 하부 플레이트(120) 상에 제1 절연물질을 증착한다. 상기 제1 절연물질은 산화 실리콘, 질화 실리콘 등을 포함한다. 계속해서, 상기 증착된 제1 절연물질 상에 아몰퍼스 실리콘층을 형성한다. 이어서, 상기 아몰퍼스 실리콘층 상에 N<sup>+</sup> 이온을 주입하여, 상기 아몰퍼스 실리콘층 상에 N<sup>+</sup> 아몰퍼스 실리콘층을 형성한다. 이후에, 상기 N<sup>+</sup> 아몰퍼스 실리콘층 및 상기 N<sup>+</sup> 아몰퍼스 실리콘층의 하부에 배치된 아몰퍼스 실리콘층의 일부를 제거하여 상기 반도체층을 형성한다. 계속해서, 상기 반도체층이 형성된 제1 절연물질 상에 도전성 물질을 증착한다. 이어서, 상기 증착된 도전성 물질의 일부를 식각하여 상기 소오스 전극(118a), 상기 리페어 부분(118a'')을 갖는 상기 데이터 라인(118a') 및 상기 드레인 전극(118c)을 형성한다. 따라서, 상기 증착된 제1 절연물질 상에 상기 박막 트랜지스터(119) 및 상기 데이터 라인(118a')이 형성된다.

도 11은 본 발명의 제1 실시예에 따른 액정 표시 장치의 제조방법을 나타내는 평면도이고, 도 12는 상기 도 11의 IV-IV'라인의 단면도이다.

도 11 및 도 12를 참조하면, 이후에 상기 박막 트랜지스터(119) 및 상기 데이터 라인(118a')이 형성된 상기 증착된 제1 절연물질 상에 제2 절연물질을 증착한다. 본 실시예에서, 상기 제2 절연물질은 상기 제1 절연물질과 동일하다.

계속해서, 상기 증착된 제1 절연물질 및 상기 증착된 제2 절연물질의 일부를 식각하여 상기 제1 콘택홀(131) 및 상기 제2 콘택홀(132)을 형성하여 상기 게이트 절연막(126) 및 상기 패시베이션막(126)을 완성한다.

이어서, 상기 패시베이션막(126) 상에 투명한 도전성 물질을 증착한다. 이후에, 상기 증착된 투명한 도전성 물질의 일부를 식각하여 상기 제2 그루부(113)를 갖는 상기 화소 전극(112) 및 상기 브릿지 패턴(123)을 형성한다. 상기 스토리지 캐패시터 패턴(122)과, 상기 화소 전극(112)의 일부와, 상기 스토리지 캐패시터 패턴(122) 및 상기 화소 전극(112)의 사이에 배치된 절연막은 상기 스토리지 캐패시터를 형성한다. 이때, 상기 스토리지 캐패시터 패턴(122)의 두께를 조절하여 상기 스토리지 캐패시터의 커패시턴스(Capacitance)를 조절할 수 있다.

따라서, 상기 하부 플레이트(120), 상기 박막 트랜지스터들(119), 상기 스토리지 캐패시터 패턴들(122), 상기 브릿지 패턴들(123), 상기 리페어 부분들(118a")을 갖는 상기 데이터 라인들(118a'), 상기 게이트 라인들(118b'), 상기 게이트 절연막(126), 상기 패시베이션막(116), 상기 화소 전극들(112) 및 상기 리페어 패턴들(123)을 포함하는 상기 제2 기판(180)이 형성된다.

도 13은 본 발명의 제1 실시예에 따른 액정 표시 장치의 제조방법을 나타내는 단면도이다.

도 13을 참조하면, 이어서 상기 상부 플레이트(100) 상에 불투명한 물질을 증착한다. 계속해서, 상기 불투명한 물질의 일부를 제거하여 상기 블랙 매트릭스(102)를 형성한다. 이때, 불투명한 물질 및 포토레지스트를 상기 상부 기판(100) 상에 도포한 후에 사진 공정(Photo Process)을 이용하여 상기 블랙 매트릭스(102)를 형성할 수도 있다. 상기 사진 공정(Photo Process)은 노광 공정(Exposure Process) 및 현상 공정(Development Process)을 포함한다.

이후에, 상기 블랙 매트릭스(102)가 형성된 상기 상부 플레이트(100) 상에 적색 컬러필터 혼합물을 도포한다. 계속해서, 사진공정을 이용하여 상기 도포된 적색 컬러필터 혼합물의 일부를 제거하여 적색 컬러필터부를 형성한다. 이어서, 상기 블랙 매트릭스(102) 및 상기 적색 컬러필터부가 형성된 상기 상부 플레이트(100) 상에 상기 녹색 컬러필터부 및 상기 청색 컬러필터부를 형성한다.

이후에, 상기 블랙 매트릭스(102) 및 상기 컬러 필터(104)가 형성된 상기 상부 플레이트(100) 상에 투명한 도전성 물질을 도포한다. 이어서, 상기 투명한 도전성 물질의 일부를 식각하여 상기 제1 그루부(107)를 갖는 상기 공통 전극(106)을 형성한다. 본 실시예에서 상기 식각공정들은 사진식각공정(Photolithography Process)을 포함한다.

따라서, 상기 상부 플레이트(100), 상기 블랙 매트릭스(102), 상기 컬러 필터(104) 및 상기 공통 전극(106)을 갖는 상기 제1 기판(170)이 완성된다.

도 14는 본 발명의 제1 실시예에 따른 액정 표시 장치의 제조방법을 나타내는 평면도이고, 도 15는 상기 도 14의 V-V'라인의 단면도이다.

도 14 및 도 15를 참조하면, 이어서, 상기 제1 기판(170) 및 상기 제2 기판(180)을 대향하여 결합한다.

계속해서, 상기 제1 기판(170) 및 상기 제2 기판(180) 사이에 액정을 주입한 후에 셀런트(Sealant, 도시되지 않음)에 의해 밀봉하여 상기 액정층(108)을 형성한다. 이때, 상기 셀런트(도시되지 않음)가 형성된 상기 제1 기판(170) 또는 상기 제2 기판(180) 상에 액정을 적하(Drop)한 후에 상기 제1 기판(170) 및 상기 제2 기판(180)을 대향하여 결합하여 상기 액정층(108)을 형성할 수도 있다.

도 16은 도 1에 도시된 액정 표시 장치에 발생한 불량을 나타내는 평면도이고, 도 17은 상기 도 16의 VI-VI'라인의 단면도이다.

도 16 및 도 17을 참조하면, 상기 데이터 라인(118a')의 일부가 오픈되는 불량이 존재한다. 상기 데이터 라인(118a')의 일부가 오픈되는 경우, 상기 오픈된 부분(211)의 하부에 배치된 데이터 라인(118a')에는 데이터 신호가 차단되어 상기 액정 표시 패널의 화질이 저하된다.

도 18은 본 발명의 제1 실시예에 따른 액정 표시 장치의 불량 제거 방법을 나타내는 평면도이다.

도 18을 참조하면, 먼저 상기 데이터 라인(118a')의 오픈된 부분(211)에 인접하는 상기 리페어 패턴들(124)과 상기 리페어 부분들(118a")이 오버랩되는 부분에 레이저를 조사하여, 상기 리페어 패턴들(124)이 상기 리페어 부분들(118a")과 전기적으로 연결되는 리페어 콘택홀들(222, 224)을 형성하여 상기 데이터 라인(118a')과 상기 스토리지 캐패시터 패턴(122)을 전기적으로 연결한다.

계속해서, 상기 리페어 콘택홀들(222, 224)을 기준으로 상기 오픈된 부분(211)의 맞은편에 배치된 브릿지 패턴들(123)에 레이저를 조사하여 상기 오픈된 부분에 인접하는 두 개의 스토리지 캐패시터 패턴들(122)을 나머지 스토리지 캐패시터 패턴들(122)과 전기적으로 절연시킨다.

상기 데이터 신호(I)는 상기 오픈된 부분(211)의 상부에 배치된 데이터 라인, 상기 오픈된 부분(211)의 상부에 배치된 리페어 콘택홀(222), 상기 오픈된 부분(211)의 상부에 배치된 스토리지 캐패시터 패턴, 상기 오픈된 부분(211)에 인접하는 브릿지 패턴(123), 상기 오픈된 부분(119)의 하부에 배치된 스토리지 캐패시터 패턴, 상기 오픈된 부분(211)의 하부에 배치된 리페어 콘택홀(224), 및 상기 오픈된 부분(211)의 상부에 배치된 데이터 라인을 통하여 나머지 박막 트랜지스터들에 인가된다.

따라서, 상기 오픈된 부분(211)을 우회하는 리페어 회로가 형성된다. 당해 기술분야의 숙련된 당업자는 상기 단계들의 순서에 상관없이 상기 리페어 회로가 형성되는 것을 알 수 있을 것이다. 또한, 상기와 같이 데이터 라인이 오픈되는 불량뿐만 아니라 박막 트랜지스터가 오동작하는 경우에도 적용될 수 있음을 알 수 있을 것이다. 다만, 상기 박막 트랜지스터가 오동작하는 경우에는 상기 오동작하는 박막 트랜지스터를 상기 데이터 라인과 전기적으로 절연시키는 단계가 더 필요하다.

상기와 같은 본 실시예에 따르면, 상기 스토리지 캐패시터 라인이 상기 화소의 가장자리를 따라서 배치되어 상기 액정 표시 장치의 개구율이 향상된다. 또한, 상기 제2 기판(180)이 상기 리페어 패턴들(124)을 포함하여 상기 데이터 라인(118a')의 상기 오픈된 부분(211)의 수가 3개 이상인 경우에도 상기 우회회로를 형성할 수 있다.

## 실시예 2

도 19는 본 발명의 제2 실시예에 따른 액정 표시 장치를 나타내는 평면도이고, 도 20은 상기 도 19의 VII-VII'라인의 단면도이다. 본 실시예에서 화소 전극 및 공통 전극을 제외한 나머지 구성 요소들은 실시예 1과 동일하므로 중복된 부분에 대해서는 상세한 설명을 생략한다.

도 19 및 도 20을 참조하면, 상기 액정 표시 장치는 제1 기판(170), 제2 기판(180) 및 액정층(108)을 포함한다.

상기 제1 기판(170)은 상부 플레이트(100), 블랙 매트릭스(102), 컬러 필터(104) 및 공통 전극(106)을 포함한다.

상기 제2 기판(180)은 하부 플레이트(120), 복수의 박막 트랜지스터(119), 복수의 스토리지 캐패시터 패턴(122), 복수의 브릿지 패턴(123), 복수의 리페어 부분들(118a")을 갖는 복수의 데이터 라인(118a'), 복수의 게이트 라인(118b'), 게이트 절연막(126), 패시베이션막(116), 복수의 화소 전극(112) 및 복수의 리페어 패턴(123)을 포함한다.

상기 액정 표시 장치는 복수의 화소들을 포함하고, 상기 화소들은 서로 인접하는 상기 데이터 라인들(118a')과 상기 게이트 라인들(118b')에 의해 정의된다.

상기 박막 트랜지스터(119)는 상기 화소에 대응하는 상기 하부 플레이트(120) 상에 배치되며, 소오스 전극(118a), 게이트 전극(118b), 드레인 전극(118c) 및 반도체층 패턴을 포함한다.

상기 화소 전극(112)은 상기 화소에 대응하는 상기 패시베이션막(116)의 표면 및 상기 드레인 전극(118c)의 일부를 노출하는 제1 콘택홀(131)의 내면 상에 형성되어 상기 드레인 전극(118c)과 전기적으로 연결된다. 상기 화소 전극(112)은 균일한 표면을 갖는다.

상기 공통 전극(106)은 상기 블랙 매트릭스(102) 및 상기 컬러 필터(104)가 형성된 상기 상부 플레이트(100) 상에 배치된다. 상기 공통 전극(106)은 균일한 표면을 갖는다.

상기와 같은 본 실시예에 따르면, 상기 화소 전극(112) 및 상기 공통 전극(106)이 균일한 표면을 갖는 경우에도, 우회회로를 형성하여 상기 데이터 라인(118a')이 오픈된 부분을 리페어(Ripar)할 수 있다.

## 발명의 효과

상기와 같은 본 발명에 따르면, 스토리지 캐패시터 라인이 화소의 가장자리를 따라서 배치되어 액정 표시 장치의 개구율이 향상된다. 또한, 상기 액정 표시 장치의 제2 기판이 리페어 패턴들을 포함하여 불량이 발생된 부분의 수가 3개 이상인 경우에도 우회회로를 형성할 수 있다. 따라서, 상기 액정 표시 장치의 화질이 향상된다.

상기에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

#### (57) 청구의 범위

##### 청구항 1.

플레이트 상에 배치되고 게이트 신호를 전달하는 복수의 게이트 라인들;

상기 플레이트 상에 배치되는 복수의 스토리지 캐패시터 패턴들;

상기 게이트 라인들과 교차되도록 배치되고, 데이터 신호를 전달하는 복수의 데이터 라인들;

상기 플레이트 상에 상기 각 데이터 라인들의 일부와 오버랩되도록 배치되고, 상기 스토리지 캐패시터 패턴들과 전기적으로 연결되는 복수의 리페어 패턴들;

서로 인접하는 스토리지 캐패시터 패턴들을 전기적으로 연결하는 복수의 브릿지 패턴들;

서로 인접하는 게이트 라인들 및 데이터 라인들에 의해 정의되는 영역 내에 배치되고, 상기 각 스토리지 캐패시터 패턴들과 오버랩되어 스토리지 캐패시터를 형성하는 복수의 화소 전극들; 및

상기 플레이트 상에 배치되고, 상기 게이트 신호에 응답하여 상기 데이터 신호를 상기 각 화소 전극들에 인가하는 복수의 스위칭 소자들을 포함하는 표시장치용 기판.

##### 청구항 2.

제1항에 있어서, 상기 스토리지 캐패시터 패턴은 상기 화소 전극의 가장자리와 오버랩되는 것을 특징으로 하는 표시장치용 기판.

##### 청구항 3.

제1항에 있어서, 상기 스토리지 캐패시터 패턴들은 상기 데이터 라인들과 평행하게 배치되는 것을 특징으로 하는 표시장치용 기판.

##### 청구항 4.

제3항에 있어서, 상기 각 스토리지 캐패시터 패턴이 'V'형상으로 배열된 복수의 보조 캐패시터 부분들을 더 포함하는 것을 특징으로 하는 표시장치용 기판.

##### 청구항 5.

제1항에 있어서, 상기 스토리지 캐패시터 패턴들 및 상기 리페어 패턴들은 상기 게이트 라인들과 동일한 층에 형성되는 것을 특징으로 하는 표시장치용 기판.

### 청구항 6.

제1항에 있어서, 상기 브릿지 패턴들은 상기 화소 전극과 동일한 층에 형성되는 것을 특징으로 하는 표시장치용 기판.

### 청구항 7.

제1항에 있어서, 상기 화소 전극은 'V'형상으로 배열된 복수의 그루부들을 포함하는 것을 특징으로 하는 표시장치용 기판.

### 청구항 8.

상부 플레이트 및 상기 상부 플레이트 상에 배치된 공통 전극을 구비하는 제1 기판;

하부 플레이트와, 상기 하부 플레이트 상에 배치되고 게이트 신호를 전달하는 복수의 게이트 라인들과, 상기 하부 플레이트 상에 배치되는 복수의 스토리지 캐패시터 패턴들과, 상기 게이트 라인들과 교차되도록 배치되고 데이터 신호를 전달하는 복수의 데이터 라인들과, 상기 플레이트 상에 상기 각 데이터 라인들의 일부와 오버랩되도록 배치되고 상기 스토리지 캐패시터 패턴들과 전기적으로 연결되는 복수의 리페어 패턴들과, 서로 인접하는 스토리지 캐패시터 패턴들을 전기적으로 연결하는 복수의 브릿지 패턴들과, 서로 인접하는 게이트 라인들 및 데이터 라인들에 의해 정의되는 영역 내에 배치되고 상기 각 스토리지 캐패시터 패턴들과 오버랩되어 스토리지 캐패시터를 형성하는 복수의 화소 전극들과, 상기 플레이트 상에 배치되고 상기 게이트 신호에 응답하여 상기 데이터 신호를 상기 각 화소 전극들에 인가하는 복수의 스위칭 소자들을 포함하며, 상기 제1 기판에 대향하는 제2 기판; 및

상기 제1 기판과 상기 제2 기판의 사이에 배치된 액정층을 포함하는 액정 표시 장치.

### 청구항 9.

제8항에 있어서, 상기 스토리지 캐패시터 패턴은 상기 화소 전극의 가장자리와 오버랩되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 10.

제8항에 있어서, 상기 스토리지 캐패시터 패턴들은 상기 데이터 라인들과 평행하게 배치되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 11.

제8항에 있어서, 상기 공통 전극은 'V'형상으로 배열된 복수의 제1 그루부들을 포함하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 12.

제8항에 있어서, 상기 화소 전극은 'V'형상으로 배열된 복수의 제2 그루부들을 포함하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 13.

제12항에 있어서, 상기 공통 전극은 'V'형상으로 배열된 복수의 제1 그루부들을 포함하고, 상기 제1 그루부들과 상기 제2 그루부들은 서로 엇갈리게 배치되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 14.

오픈된 부분을 갖는 데이터 라인과 평행하게 배열되고 복수의 브릿지 패턴들을 통하여 서로 전기적으로 연결되어 스토리지 캐패시터 라인을 형성하는 복수의 스토리지 캐패시터 패턴들 중에서 상기 오픈된 부분에 인접하는 두 개의 스토리지 캐패시터 패턴들에 전기적으로 연결되는 리페어 패턴들과 상기 데이터 라인을 전기적으로 연결하는 단계; 및

상기 리페어 패턴들을 기준으로 상기 오픈된 부분의 맞은편에 배치된 브릿지 패턴들을 오픈시키는 단계를 포함하는 표시 장치용 기판의 불량 제거 방법.

### 청구항 15.

제14항에 있어서, 상기 리페어 패턴들과 상기 데이터 라인을 전기적으로 연결하는 단계는, 상기 리페어 패턴들과 상기 데이터 라인이 오버랩되는 부분에 레이저를 조사하는 단계를 포함하는 것을 특징으로 하는 표시장치용 기판의 불량 제거 방법.

### 청구항 16.

제14항에 있어서, 상기 브릿지 패턴들을 오픈시키는 단계는, 상기 브릿지 패턴들의 일부에 레이저를 조사하는 단계를 포함하는 것을 특징으로 하는 표시장치용 기판의 불량 제거 방법.

**도면**

도면1

## 도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

## 도면14

도면15

도면16

도면17

도면18

도면19

도면20

|                |                                                                     |         |            |

|----------------|---------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于显示装置的基板，具有该基板的液晶显示装置和缺陷去除方法                                       |         |            |

| 公开(公告)号        | <a href="#">KR1020060019224A</a>                                    | 公开(公告)日 | 2006-03-03 |

| 申请号            | KR1020040067773                                                     | 申请日     | 2004-08-27 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                            |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                            |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                            |         |            |

| [标]发明人         | SUH HEESANG                                                         |         |            |

| 发明人            | SUH,HEESANG                                                         |         |            |

| IPC分类号         | G02F1/1343                                                          |         |            |

| CPC分类号         | G02F1/136213 G02F1/134309 G02F1/136227 G02F1/136259 G02F2001/136272 |         |            |

| 代理人(译)         | PARK , YOUNG WOO                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                           |         |            |

### 摘要(译)

栅极线提供栅极信号。设置数据线以与栅极线交叉。传递数据信号。修复图案设置为与每条数据线的一部分重叠。它与存储电容器模式电连接。它是相邻的存储电容器图案是电连接的。它被安排在相邻的栅极线和用数据线定义的区域内。它与每个存储电容器图案重叠并形成存储电容器。开关元件响应于每个像素电极中的栅极信号而授权数据信号。因此，改善了液晶显示器的孔径比，并且容易去除故障并且改善了图像质量。