(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년09월01일

(11) 등록번호 10-0855502

(24) 등록일자 2008년08월26일

(51) Int. Cl.

*G02F 1/1345* (2006.01) *G02F 1/133* (2006.01)

*G09G 3/36* (2006.01)

(21) 출원번호 10-2007-0046126

(22) 출원일자 2007년05월11일

심사청구일자 2007년06월27일

(30) 우선권주장

1020070030323 2007년03월28일 대한민국(KR)

(56) 선행기술조사문현

KR1020040100756 A

KR1020060020056 A

KR1020050000994 A

JP2004139012 A

전체 청구항 수 : 총 10 항

(73) 특허권자

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

장수혁

대구 북구 동천동 영남2차타운 103동 902호

송홍성

경북 구미시 구평동 474-7 부영아파트 803동 706호

(뒷면에 계속)

(74) 대리인

특허법인로얄

**(54) 액정표시장치와 그 구동방법****(57) 요약**

본 발명은 콘트롤 PCB를 간소화하도록 한 액정표시장치와 그 구동방법에 관한 것이다.

이 액정표시장치는 각각 다수의 데이터라인들을 포함한 제1 및 제2 데이터라인군, 상기 제1 및 제2 데이터라인군과 교차하는 다수의 게이트라인, 및 기판 가장자리에 형성되는 LOG 배선을 포함하고 다수의 액정셀들이 매트릭스 형태로 배치된 액정표시장치; 상기 제1 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제1 데이터 회로군; 상기 제1 데이터 회로군이 접속된 제1 소스 PCB; 상기 제2 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제2 데이터 회로군; 상기 제2 데이터 회로군이 접속된 제2 소스 PCB; 상기 제1 및 제2 데이터 회로군들을 제어하기 위한 타이밍 제어신호와 상기 데이터를 싱글 출력포트를 통해 출력하는 타이밍 콘트롤러; 상기 타이밍 콘트롤러가 실장된 콘트롤 PCB; 및 상기 싱글 출력포트를 상기 제1 소스 PCB에 전기적으로 연결하기 위한 연결부를 구비한다.

**대표도 - 도4**

(72) 발명자

**민용기**

대구 북구 동천동 891번지 동화골든빌 103동 1205

호

**최병진**

경북 구미시 고아읍 원호리 455번지 원호점보타운

103동 1401호

**차동훈**

경북 구미시 진평동 98B 인의주공아파트 202동

1509호

## 특허청구의 범위

### 청구항 1

각각 다수의 데이터라인들을 포함한 제1 및 제2 데이터라인군, 상기 제1 및 제2 데이터라인군과 교차하는 다수의 케이트라인, 및 기판 가장자리에 형성되는 LOG 배선을 포함하고 다수의 액정셀들이 매트릭스 형태로 배치된 액정표시패널;

상기 제1 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제1 데이터 회로군;

상기 제1 데이터 회로군이 접속된 제1 소스 PCB;

상기 제2 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제2 데이터 회로군;

상기 제2 데이터 회로군이 접속된 제2 소스 PCB;

상기 제1 및 제2 데이터 회로군들을 제어하기 위한 타이밍 제어신호와 상기 데이터를 싱글 출력포트를 통해 출력하는 타이밍 콘트롤러;

상기 타이밍 콘트롤러가 실장된 콘트롤 PCB; 및

상기 싱글 출력포트를 상기 제1 소스 PCB에 전기적으로 연결하기 위한 연결부를 구비하고;

상기 제1 소스 PCB와 상기 제2 소스 PCB는 상기 LOG 배선을 통해 상호 전기적으로 접속되는 것을 특징으로 하는 액정표시장치.

### 청구항 2

제 1 항에 있어서,

상기 콘트롤 PCB에 형성되어 상기 액정표시패널의 구동전압을 발생하는 전원 발생회로를 더 구비하고;

상기 연결부와 상기 LOG 배선은 상기 데이터, 상기 타이밍 제어신호 및 상기 구동전압을 전송하는 것을 특징으로 하는 액정표시장치.

### 청구항 3

제 2 항에 있어서,

상기 제1 및 제2 데이터 회로군 각각은,

상기 데이터 IC가 실장되고 더미 배선이 형성된 COF(Chip on film)와 더미 배선이 형성된 TCP(Tape Carrier Package) 중 어느 하나를 구비하는 것을 특징으로 하는 액정표시장치.

### 청구항 4

제 3 항에 있어서,

상기 더미배선은 상기 연결부와 상기 LOG 배선 사이에서 상기 데이터, 상기 타이밍 제어신호 및 상기 구동전압을 전송하는 것을 특징으로 하는 액정표시장치.

### 청구항 5

제 1 항에 있어서,

상기 연결부는,

상기 제1 소스 PCB와 상기 콘트롤 PCB를 전기적으로 연결하기 위한 케이블; 및

상기 콘트롤 PCB 상에 형성되어 상기 싱글 출력포트를 상기 케이블에 전기적으로 연결하기 위한 연결 배선을 구비하는 것을 특징으로 하는 액정표시장치.

### 청구항 6

제 1 항에 있어서,

상기 타이밍 콘트롤러는,

입력 주파수로 입력되는 디지털 비디오 데이터를 기수 화소 데이터와 우수 화소 데이터로 분리하여 그 데이터들을 상기 입력 주파수의 1/2 주파수로 출력하는 2 포트 확장부; 및

상기 2 포트 확장부로부터의 데이터들을 변조하여 상기 싱글 출력포트를 통해 출력되는 데이터의 스윙폭을 줄이고 상기 입력 주파수 대비 2배 높은 주파수로 상기 데이터를 출력하는 데이터 변조부를 구비하는 것을 특징으로 하는 액정표시장치.

#### 청구항 7

제 6 항에 있어서,

상기 데이터 변조부는,

mini LVDS(low-voltage differential signaling) 방식과 RSDS(Reduced Swing Differential Signaling) 방식 중 어느 하나로 상기 데이터를 변조하는 것을 특징으로 하는 액정표시장치.

#### 청구항 8

제 7 항에 있어서,

상기 데이터 IC 각각은

상기 변조된 데이터를 복원하는 데이터 복원부를 구비하는 것을 특징으로 하는 액정표시장치.

#### 청구항 9

제 1 항에 있어서,

상기 제1 소스 PCB에 접속된 상기 데이터 IC의 신호 입력단자들에 접속된 저항을 더 구비하고;

상기 저항의 저항값  $R_{TA}$ 은 아래의 수식과 같은 것을 특징으로 하는 액정표시장치.

$$R_{TA} = \frac{R_{TB}(R_{EQ} + R_{LOG})}{R_{EQ}}$$

여기서,  $R_{TB}$ 는 상기 제2 소스 PCB에 접속된 상기 데이터 IC의 신호 입력단자들에 접속된 저항, " $R_{EQ}$ "는 상기 연결부의 저항, " $R_{LOG}$ "는 상기 LOG 배선의 저항을 각각 의미한다.

#### 청구항 10

각각 다수의 데이터라인들을 포함한 제1 및 제2 데이터라인군, 상기 제1 및 제2 데이터라인군과 교차하는 다수의 게이트라인, 및 기판 가장자리에 형성되는 LOG 배선을 포함하고 다수의 액정셀들이 매트릭스 형태로 배치된 액정표시패널을 포함한 액정표시장치의 구동방법에 있어서,

콘트롤 PCB에 접속된 제1 소스 PCB에 타이밍 제어신호와 데이터를 전송하는 단계; 및

상기 LOG 배선을 통해 상기 제1 소스 PCB와 분리된 제2 소스 PCB에 상기 타이밍 제어신호와 상기 데이터를 전송하는 단계를 포함하고;

상기 제1 소스 PCB에는 상기 제1 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제1 데이터 회로군이 접속되고;

상기 제2 소스 PCB에는 상기 제2 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제2 데이터 회로군이 접속되며;

상기 콘트롤 PCB는 싱글 출력포트를 통해 상기 타이밍 제어신호와 상기 데이터를 출력하는 타이밍 콘트롤러를 포함하는 것을 특징으로 하는 액정표시장치의 구동방법.

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <27> 본 발명은 액정표시장치에 관한 것으로, 특히 콘트롤 인쇄회로보드(Printed Circuit Board 이하 "PCB"라 함)를 간소화하도록 한 액정표시장치와 그 구동방법에 관한 것이다.

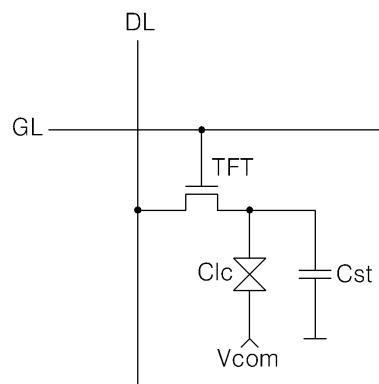

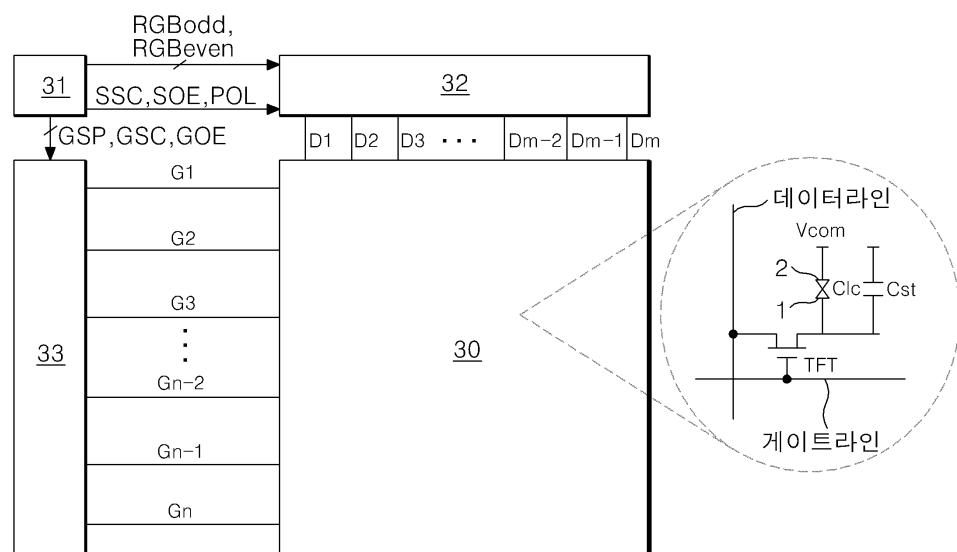

- <28> 액정표시장치는 비디오신호에 따라 액정셀들의 광투과율을 조절하여 화상을 표시한다. 액티브 매트릭스(Active Matrix) 타입의 액정표시장치는 도 1과 같이 액정셀(Clc)마다 형성된 박막트랜지스터(Thin Film Transistor 이하 "TFT"라 함)를 이용하여 액정셀들에 공급되는 데이터전압을 스위칭하여 데이터를 능동적으로 제어하므로 동화상의 표시품질을 높일 수 있다. 도 1에 있어서, 도면부호 "Cst"는 액정셀(Clc)에 충전된 데이터전압을 유지하기 위한 스토리지 커패시터(Storage Capacitor, Cst), 'DL'은 데이터전압이 공급되는 데이터라인, 그리고 'GL'은 스캔전압이 공급되는 게이트라인을 각각 의미한다.

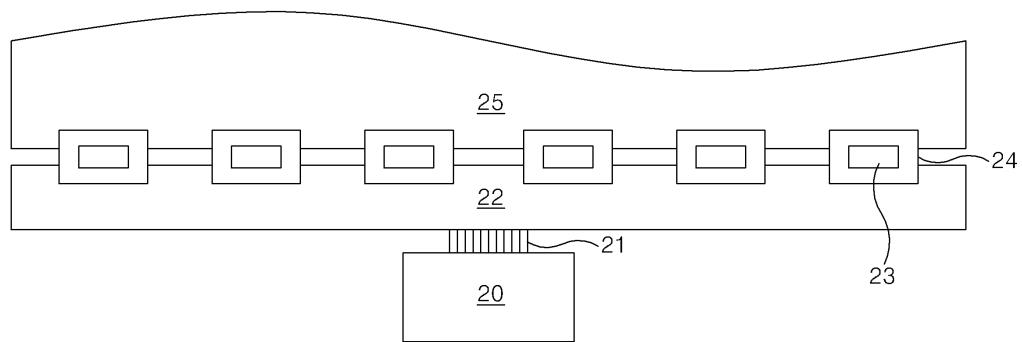

- <29> 액정표시장치는 최근의 텔레비전이나 모니터가 대화면화되면서 소형뿐만 아니라 중대형 모델의 개발이 진행되고 있다. 이러한 액정표시장치는 도 2와 같이 콘트롤 PCB(20), 소스 PCB(22), 소스 PCB(22)와 콘트롤 PCB(20)에 연결된 케이블(21), 소스 PCB(22)와 액정표시패널(25)에 연결된 다수의 소스 COF(Chip on film)를 구비한다.

- <30> 소스 COF(24)는 소스 PCB(22)와 액정표시패널(25)의 데이터패드들에 전기적으로 접속된다. 이 소스 COF(24)에는 데이터 집적회로(Integrated Circuit 이하 "IC"라 함)(23)가 실장된다.

- <31> 소스 PCB(23)에는 콘트롤 PCB(20)로부터의 디지털 비디오 데이터들과 타이밍 제어신호들을 전송하기 위한 신호 배선들이 형성된다.

- <32> 콘트롤 PCB(20)에는 제어회로와 데이터 전송회로 등이 실장된다. 이 콘트롤 PCB(20)는 소스 PCB(22)의 데이터 IC에 데이터를 공급하고 데이터 IC의 동작을 제어하기 위한 타이밍 제어신호들을 케이블(21)을 통해 소스 PCB(22)에 공급한다.

- <33> 도 2와 같은 액정표시장치에서 액정표시패널(25)이 커지게 되면 그 만큼 데이터라인들과 소스 COF들(24)이 많아지고 그 결과, 소스 PCB(22)도 커지게 된다. 이 경우에, 소스 PCB(22)와 소스 COF(24)의 정렬(align)이 어렵게 된다. 소스 PCB(22)가 커지면 기존 SMT(Surface Mount Technology) 장비와 같은 자동화 실장장치는 상대적으로 작은 크기의 소스 PCB(22)를 기준으로 설계되었기 때문에 큰 소스 PCB(22)를 다룰 수 없다. 콘트롤 PCB(20)는 액정표시장치가 대형화될 수록 메모리와 같은 회로소자들이 많아지고 출력핀수가 증가하는 문제점이 있다.

#### 발명이 이루고자 하는 기술적 과제

- <34> 따라서, 본 발명의 목적은 종래 기술의 문제점을 해결하고자 안출된 발명으로써 소스 PCB를 분할하고 콘트롤 PCB의 크기와 출력핀 수를 줄이도록 한 액정표시장치와 그 구동방법을 제공함에 있다.

#### 발명의 구성 및 작용

- <35> 상기 목적을 달성하기 위하여, 본 발명의 실시예에 따른 액정표시장치는 각각 다수의 데이터라인들을 포함한 제

1 및 제2 데이터라인군, 상기 제1 및 제2 데이터라인군과 교차하는 다수의 게이트라인, 및 기판 가장자리에 형성되는 LOG 배선을 포함하고 다수의 액정셀들이 매트릭스 형태로 배치된 액정표시패널; 상기 제1 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제1 데이터 회로군; 상기 제1 데이터 회로군이 접속된 제1 소스 PCB; 상기 제2 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제2 데이터 회로군; 상기 제2 데이터 회로군이 접속된 제2 소스 PCB; 상기 제1 및 제2 데이터 회로군들을 제어하기 위한 타이밍 제어신호와 상기 데이터를 싱글 출력포트를 통해 출력하는 타이밍 콘트롤러; 상기 타이밍 콘트롤러가 실장된 콘트롤 PCB; 및 상기 싱글 출력포트를 상기 제1 소스 PCB에 전기적으로 연결하기 위한 연결부를 구비한다.

- <36> 상기 제1 소스 PCB와 상기 제2 소스 PCB는 상기 LOG 배선을 통해 상호 전기적으로 접속된다.

- <37> 상기 액정표시장치는 상기 콘트롤 PCB에 형성되어 상기 액정표시패널의 구동전압을 발생하는 전원 발생회로를 더 구비한다.

- <38> 상기 연결부와 상기 LOG 배선은 상기 데이터, 상기 타이밍 제어신호 및 상기 구동전압을 전송한다.

- <39> 상기 제1 및 제2 데이터 회로군 각각은 상기 데이터 IC가 실장되고 더미 배선이 형성된 COF(Chip on film)와 더미 배선이 형성된 TCP(Tape Carrier Package) 중 어느 하나를 구비한다.

- <40> 상기 더미배선은 상기 연결부와 상기 LOG 배선 사이에서 상기 데이터, 상기 타이밍 제어신호 및 상기 구동전압을 전송한다.

- <41> 상기 연결부는 상기 제1 소스 PCB와 상기 콘트롤 PCB를 전기적으로 연결하기 위한 케이블; 및 상기 콘트롤 PCB 상에 형성되어 상기 싱글 출력포트를 상기 케이블에 전기적으로 연결하기 위한 연결 배선을 구비한다.

- <42> 상기 타이밍 콘트롤러는 입력 주파수로 입력되는 디지털 비디오 데이터를 기수 화소 데이터와 우수 화소 데이터로 분리하여 그 데이터들을 상기 입력 주파수의 1/2 주파수로 출력하는 2 포트 확장부; 및 상기 2 포트 확장부로부터의 데이터들을 변조하여 상기 싱글 출력포트를 통해 출력되는 데이터의 스윙폭을 줄이고 상기 입력 주파수 대비 2배 높은 주파수로 상기 데이터를 출력하는 데이터 변조부를 구비한다.

- <43> 상기 데이터 변조부는 mini LVDS(low-voltage differential signaling) 방식과 RSDS(Reduced Swing Differential Signaling) 방식 중 어느 하나로 상기 데이터를 변조한다.

- <44> 상기 데이터 IC 각각은 상기 변조된 데이터를 복원하는 데이터 복원부를 구비한다.

- <45> 상기 액정표시장치는 상기 제1 소스 PCB에 접속된 상기 데이터 IC의 신호 입력단자들에 접속된 저항을 더 구비한다. 상기 저항의 저항값  $R_{TA}$ 은 아래의 수식과 같다.

- $$<46> R_{TA} = \frac{R_{TB}(R_{EQ} + R_{LOG})}{R_{EQ}}$$

- <47> 여기서,  $R_{TB}$ 는 상기 제2 소스 PCB에 접속된 상기 데이터 IC의 신호 입력단자들에 접속된 저항, " $R_{EQ}$ "는 상기 연결부의 저항, " $R_{LOG}$ "는 상기 LOG 배선의 저항을 각각 의미한다.

- <48> 본 발명의 실시예에 따른 액정표시장치의 구동방법은 각각 다수의 데이터라인들을 포함한 제1 및 제2 데이터라인군, 상기 제1 및 제2 데이터라인군과 교차하는 다수의 게이트라인, 및 기판 가장자리에 형성되는 LOG 배선을 포함하고 다수의 액정셀들이 매트릭스 형태로 배치된 액정표시패널을 포함한 액정표시장치의 구동방법에 있어서, 콘트롤 PCB에 접속된 제1 소스 PCB에 타이밍 제어신호와 데이터를 전송하는 단계; 및 상기 LOG 배선을 통해 상기 제1 소스 PCB와 분리된 제2 소스 PCB에 상기 타이밍 제어신호와 상기 데이터를 전송하는 단계를 포함한다.

- <49> 상기 제1 소스 PCB에는 상기 제1 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제1 데이터 회로군이 접속된다.

- <50> 상기 제2 소스 PCB에는 상기 제2 데이터라인군에 데이터를 공급하기 위한 데이터 IC들을 포함한 제2 데이터 회로군이 접속된다.

- <51> 상기 콘트롤 PCB는 싱글 출력포트를 통해 상기 타이밍 제어신호와 상기 데이터를 출력하는 타이밍 콘트롤러를

포함한다.

<52> 이하, 도 3 내지 도 15를 참조하여 본 발명의 바람직한 실시예에 대하여 설명하기로 한다.

<53> 도 3을 참조하면, 본 발명의 실시예에 따른 액정표시장치는 액정표시패널(30), 타이밍 콘트롤러(31), 데이터 구동회로(32), 및 게이트 구동회로(33)를 구비한다.

<54> 액정표시패널(30)에서, 두 장의 유리기판 그 사이에는 액정층이 형성된다. 이 액정표시패널(30)은 m 개의 데이터라인들(D1 내지 Dm)과 n 개의 게이트라인들(G1 내지 Gn)이 교차 구조에 의해 매트릭스 형태로 배치된 m×n 개의 액정셀들(Cl<sub>c</sub>)을 포함한다.

<55> 액정표시패널(30)의 하부 유리기판에는 데이터라인들(D1 내지 Dm), 게이트라인들(G1 내지 Gn), TFT들, TFT에 접속된 액정셀(Cl<sub>c</sub>)의 화소전극들(1), 및 스토리지 커패시터(Cst) 등이 형성된다. 이 액정표시패널(30)의 하부 유리기판에는 후술하는 소스 COF들 사이에서 데이터, 데이터 타이밍 제어신호, 구동전압 등을 전송하는 엘오지 (Lines On Glass 이하, "LOG"라 함) 배선들이 형성된다.

<56> 액정표시패널(30)의 상부 유리기판 상에는 블랙매트릭스, 컬러필터 및 공통전극(2)이 형성된다. 공통전극(2)은 TN(Twisted Nematic) 모드와 VA(Vertical Alignment) 모드와 같은 수직전계 구동방식에서 상부 유리기판 상에 형성되며, IPS(In Plane Switching) 모드와 FFS(Fringe Field Switching) 모드와 같은 수평전계 구동방식에서 화소전극(1)과 함께 하부 유리기판 상에 형성된다. 액정표시패널(30)의 상부 유리기판과 하부 유리기판 상에는 광축이 직교하는 편광판이 부착되고 액정과 접하는 내면에 액정의 프리틸트각을 설정하기 위한 배향막이 형성된다.

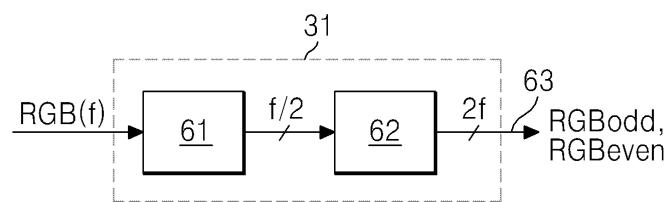

<57> 타이밍 콘트롤러(31)는 수직/수평 동기신호, 데이터인에이블, 클럭신호 등의 타이밍신호를 입력받아 데이터 구동회로(32)와 게이트 구동회로(33)의 동작 타이밍을 제어하기 위한 타이밍 제어신호들을 발생한다. 타이밍 제어신호들은 게이트 스타트 펄스(Gate Start Pulse : GSP), 게이트 쉬프트 클럭신호(Gate Shift Clock : GSC), 게이트 출력 인에이블신호(Gate Output Enable : GOE) 등의 게이트 타이밍 제어신호들을 포함한다. 게이트 스타트 펄스(GSP)는 한 화면이 표시되는 1 수직기간 중에서 스캔이 시작되는 시작 수평라인을 지시한다. 게이트 쉬프트 클럭신호(GSC)는 게이트 구동회로 내의 쉬프트 레지스터에 입력되어 게이트 스타트 펄스(GSP)를 순차적으로 쉬프트시키기 위한 타이밍 제어신호로써 TFT의 온(ON) 기간에 대응하는 펄스폭으로 발생된다. 게이트 출력 신호(GOE)는 게이트 구동회로(33)의 출력을 지시한다. 또한, 타이밍 제어신호들은 소스 샘플링 클럭(Source Sampling Clock : SSC), 소스 출력 인에이블신호(SOE), 극성제어신호(POL) 등을 포함한 데이터 타이밍 제어신호들을 포함한다. 소스 샘플링 클럭(SSC)은 라이징(Rising) 또는 폴링(Falling) 에지에 기준하여 데이터 구동회로(32) 내에서 데이터의 래치동작을 지시한다. 소스 출력 인에이블신호(Source Output Enable : SOE)는 데이터 구동회로(32)의 출력을 지시한다. 극성제어신호(Polarity : POL)는 액정표시패널(30)의 액정셀들(Cl<sub>c</sub>)에 공급될 데이터전압의 극성을 지시한다. 또한, 타이밍 콘트롤러(31)는 디지털 비디오 데이터를 기수 화소 데이터들(RGBodd)과 우수 화소 데이터들(RGBeven)로 분리하고 그 데이터들을 데이터 구동회로(32)에 공급한다. 데이터의 전송경로 상에서 EMI와 데이터전압의 스윙폭을 줄이기 위하여, 타이밍 콘트롤러(31)는 데이터를 mini LVDS(low-voltage differential signaling) 방식 또는 RSDS(Reduced Swing Differential Signaling) 방식으로 변조하여 데이터 구동회로(32)에 공급한다.

<58> 데이터 구동회로(32)는 타이밍 콘트롤러(31)의 제어 하에 디지털 비디오 데이터(RGBodd, RGBeven)를 캐치한다. 그리고 데이터 구동회로(32)는 디지털 비디오 데이터를 극성제어신호(POL)에 따라 아날로그 정극성/부극성 감마보상전압으로 변환하여 정극성/부극성 아날로그 데이터전압을 발생하고 그 데이터전압을 데이터라인들(D1 내지 Dm)에 공급한다.

<59> 게이트 구동회로(33)는 쉬프트 레지스터, 쉬프트 레지스터의 출력신호를 액정셀의 TFT 구동에 적합한 스윙폭으로 변환하기 위한 레벨 쉬프터 및 레벨 쉬프터와 게이트라인(G1 내지 Gn) 사이에 접속되는 출력 버퍼를 각각 포함하는 다수의 게이트 IC들로 구성된다. 이 게이트 구동회로(33)는 스캔펄스들을 순차적으로 출력한다. 이러한 게이트 구동회로(33)의 IC들은 COF 또는 TCP에 실장되어 ACF(anisotropic conductive film)로 액정표시패널(30)의 하부 유리기판에 형성된 게이트 패드들에 접속된다. 또한 게이트 구동회로(33)는 게이트 인 패널(Gate In Panel) 공정을 이용하여 화소 어레이에 형성된 데이터라인(D1 내지 Dm), 게이트라인(G1 내지 Gn) 및 TFT들과 동시에 액정표시패널(30)의 하부 유리기판 상에 직접 형성될 수 있다. 또한, 게이트 구동회로(33)의 IC는 칩온 글래스(Ghip On Galss) 방식으로 액정표시패널(30)의 하부 유리기판 상에 직접 접착될 수도 있다.

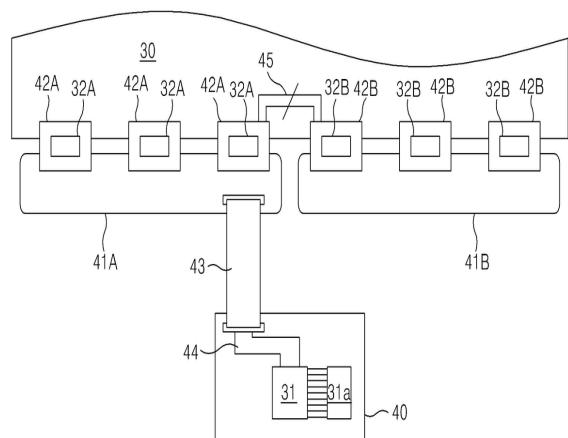

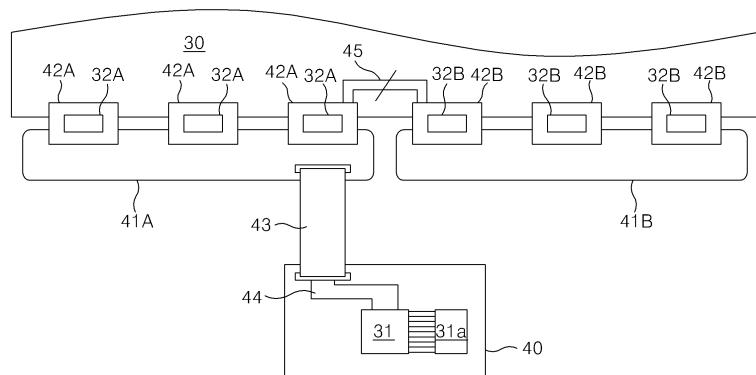

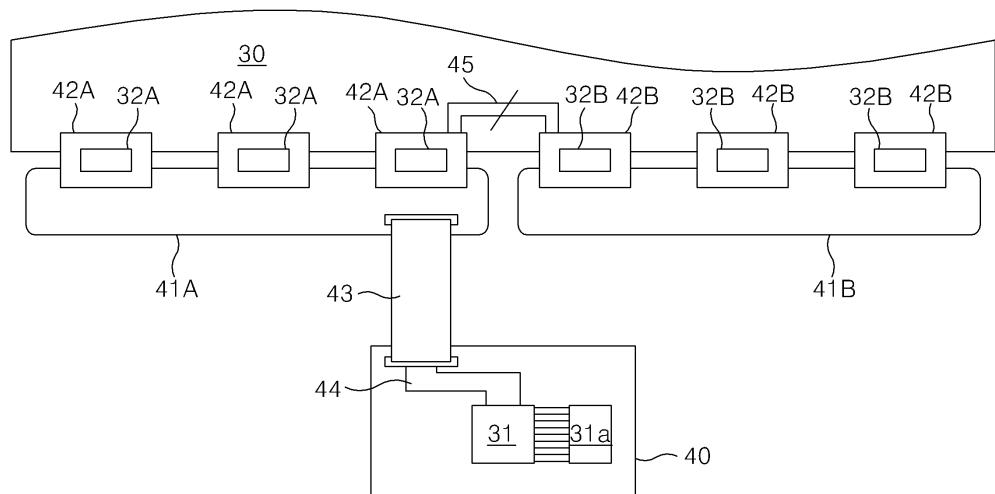

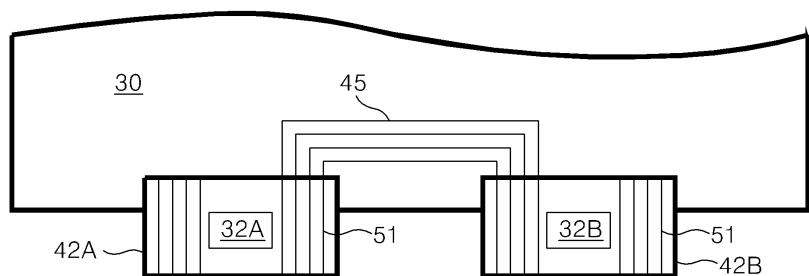

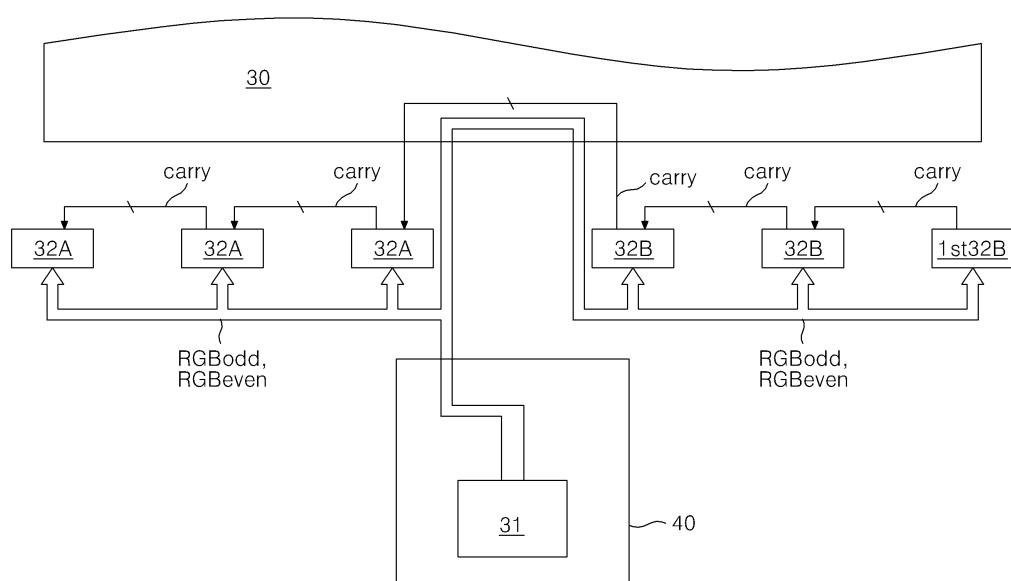

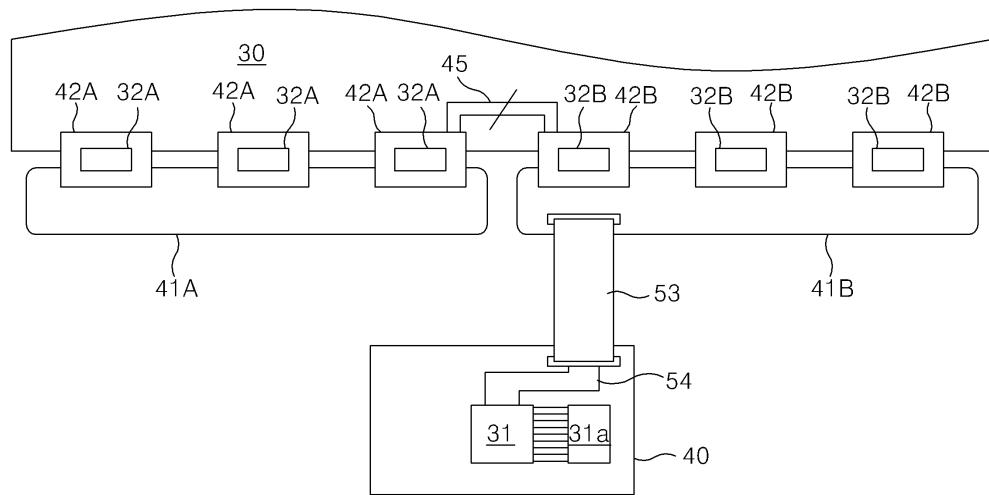

<60> 도 4는 도 3에 도시된 액정표시패널(30), 데이터 구동회로(32) 및 타이밍 콘트롤러(31)의 조립상태를 나타내는

도면이다. 도 5는 소스 COF에 형성된 더미 배선들과 액정표시패널(30)의 기판 상에 형성된 LOG 배선들을 나타내는 도면이다.

<61> 도 4 및 도 5를 참조하면, 데이터 구동회로(32)는 다수의 데이터 IC들(32A, 32B)을 포함한다.

<62> 다수의 데이터 IC들(32A, 32B)은 소스 COF(42A, 42B)에 각각 실장된다. 소스 COF(42A, 42B)는 소스 TCP(Tape Carrier Package)로 대신될 수 있다. 소스 COF(42A, 42B)은 두 개로 분할된 제1 및 제2 소스 PCB들(41A, 41B)에 나누어 연결된다. 표시화면의 우반부에 형성된 데이터라인들에 데이터를 공급하기 위한 소스 COF들(42A)은 제1 소스 PCB(41A)에 연결되고, 표시화면의 좌반부에 형성된 데이터라인들에 데이터를 공급하기 위한 소스 COF들(42B)은 제2 소스 PCB(41B)에 연결된다. 소스 COF들(42A, 42B)의 입력단자들은 소스 PCB들(41A, 41B)의 출력단자들에 전기적으로 접속되고, 소스 COF들(42)의 출력단자들은 ACF를 통해 액정표시패널(30)의 하부 유리기판에 형성된 데이터 패드들에 전기적으로 접속된다. 데이터패드들은 데이터링크배선을 경유하여 데이터라인들(D1 내지 Dm)에 연결된다.

<63> 소스 COF들(42A, 42B)에는 도 5와 같이 더미배선들(51)이 형성된다. 더미배선들(51)에는 이웃한 소스 COF들(42A, 42B)에 전송될 디지털 비디오 데이터(RGBodd, RGBeven)와, 데이터 타이밍 제어신호, 캐리신호가 공급되고 또한, 고전위 전원전압(Vdd), 저전위전압전원(Vss), 및 감마기준전압(Gamma reference voltages) 등의 구동전압이 공급된다. 제1 소스 PCB(41A)에 연결된 소스 COF들(42A) 중에서 제2 소스 PCB(41B)와 이웃하는 소스 COF(42A)의 더미배선들(51)과, 제2 소스 PCB(41B)에 연결된 소스 COF들(42B) 중에서 제1 소스 PCB(41A)와 이웃하는 소스 COF들(42B)의 더미배선들(51)은 액정표시패널(30)의 하부 유리기판에 형성된 LOG 배선들(45)을 경유하여 전기적으로 연결된다.

<64> 제1 및 제2 소스 PCB들(41A, 41B)에는 디지털 비디오 데이터들(RGBodd, RGBeven)이 전송되는 버스배선들, 데이터 타이밍 제어신호들이 전송되는 버스배선들, 구동전압들이 전송되는 버스배선들이 형성된다.

<65> 제1 소스 PCB(41A)의 입력단자들은 FFC(Flexible Flat Cable)(43)를 경유하여 콘트롤 PCB(40) 상에 형성된 연결 배선들(44)에 전기적으로 접속된다. 제2 소스 PCB(41B)는 콘트롤 PCB(40)에 연결되지 않는다. 분할된 소스 PCB들(41A, 41B)은 LOG 배선들(45)과 소스 COF들(42A, 42B)을 경유하여 전기적으로 접속된다. 따라서, 제1 소스 PCB(41A)는 콘트롤 PCB(40)에 형성된 연결배선들(44)을 경유하여 콘트롤 PCB(40)의 싱글 출력포트로부터 디지털 비디오 데이터(RGBodd, RGBeven), 데이터 타이밍 신호 및 구동전압들을 공급받고, 제2 소스 PCB(41B)는 LOG 배선들(45)과 소스 COF들(42A, 42B)을 경유하여 제1 소스 PCB(41A)로부터 디지털 비디오 데이터(RGBodd, RGBeven), 캐리신호, 데이터 타이밍 신호 및 구동전압들을 공급받는다.

<66> 콘트롤 PCB(40)에는 타이밍 콘트롤러(31), EEPROM(31a), 액정표시패널(30)의 구동전압을 발생하기 위한 직류-직류 변환기(DC-DC Converter) 등의 회로와 함께, 연결 배선들(44)이 형성된다. 직류-직류 변환기에서 생성되는 구동전압은 게이트하이전압(Vgh), 게이트로우전압(Vgl), 공통전압(Vcom), 고전위전원전압(Vdd), 저전위전원전압(Vss), 고전위전원전압(Vdd)과 저전위전원전압(Vss) 사이에서 분압되는 다수의 감마기준전압(Gamma reference voltages) 등을 포함한다. 감마기준전압들은 디지털 비디오 데이터들(RGBodd, RGBeven)의 비트수로 표현 가능한 계조 수 만큼 데이터 IC들(32a) 내에서 각 계조에 해당하는 아날로그 감마보상전압으로 세분화된다. 게이트하이전압(Vgh), 게이트로우전압(Vgl)은 스캔펄스의 스윙전압이다. EEPROM(31a)은 타이밍 콘트롤러(31)로부터 생성되는 타이밍 제어신호들에 대한 과형 옵션정보가 다수의 모드별로 저장되어 사용자로부터의 명령에 따라 해당 모드에서 과형 정보를 타이밍 콘트롤러(31)에 공급한다. 타이밍 콘트롤러(31)는 EEPROM(31a)으로부터의 과형 옵션정보에 따라 각각의 모드에서 서로 다른 형태로 타이밍 제어신호들을 생성한다.

<67> 콘트롤 PCB(40)에 형성된 연결 배선들(44)은 도 6에 도시된 타이밍 콘트롤러(31)의 싱글 출력포트(63)를 FFC(43)에 연결한다. 이 연결 배선들(44)을 통해 타이밍 콘트롤러(40)로부터 생성된 디지털 비디오 데이터들(RGBodd, RGBeven) 및 타이밍 제어신호들과, 직류-직류 변환기로부터 생성된 구동전압들이 FFC(43)에 전달된다.

<68> 도 6은 타이밍 콘트롤러(31)에서 데이터 처리부분을 나타내는 도면이다.

<69> 도 6을 참조하면, 타이밍 콘트롤러(31)는 2 포트 확장부(61)와 데이터 변조부(62)를 구비한다.

<70> 2 포트 확장부(61)는 시스템의 메인보드로부터 소정의 입력 주파수(f)로 입력되는 디지털 비디오 데이터(RGB)를 기수 화소 데이터(RGBodd)와 우수 화소 데이터(RGBeven)로 분리하여 그 데이터들(RGBodd, RGBeven)을 1/2 주파수(1/2 f)로 데이터 변조부(62)에 공급한다. 2 포트 확장부(61)로부터 출력되는 데이터들(RGBodd, RGBeven)의

스윙폭은 TTL(transistor-to-transistor) 레벨인 3.3V 정도로 비교적 높다.

<71> 데이터 변조부(62)는 mini LVDS 방식으로 데이터를 변조하여 2 포트 확장부(61)로부터의 데이터들(RGBodd, RGBeven)의 스윙폭을 300mV~600mV 정도로 낮추고 mini LVDS 클럭에 따라 데이터의 주파수를 2배(2f)로 높인다. 데이터 변조부(62)로부터 출력되는 신호들은 3쌍(RGB)의 기수 화소 데이터들(RGBodd), 3쌍의 우수 화소 데이터(RGBeven) 및 1쌍의 mini 클럭(mini CLK)을 포함한다. 각 쌍들은 도 8과 같이 정극성 신호(P)와 부극성 신호(N)를 포함한다. 한편, 데이터 변조부(62)는 RSDS 방식으로 데이터를 변조할 수도 있다.

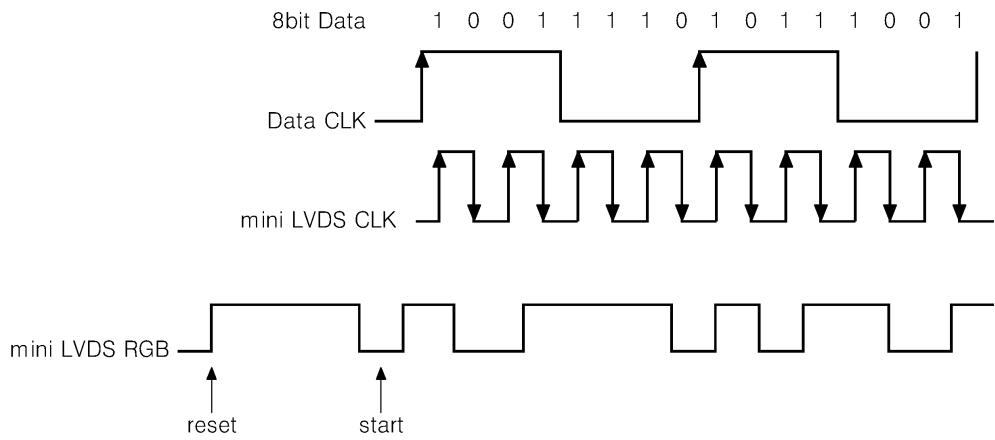

<72> 도 7 및 도 8은 데이터 변조부(72)로부터 출력되는 데이터의 일 예를 나타내는 것으로, mini LVDS 방식으로 변조된 데이터의 일 예이다.

<73> 도 7에서, "Data CLK"은 시스템의 메인보드로부터 생성되는 데이터 클럭이며, "mini LVDS CLK"은 데이터 변조부(62)로부터 생성되어 데이터와 함께 전송되는 클럭이다. 그리고 "mini LVDS RGB"는 리셋파형을 포함하여 데이터 변조부(62)에 의해 변조된 정극성 데이터파형(P)이다.

<74> 데이터 변조부(62)는 정극성 데이터 신호(P)의 역위상으로 부극성 데이터 신호(N)를 생성하고, 각각 정극성 신호(P)와 부극성 신호(N)를 포함한 6 쌍의 데이터들과 한 쌍의 mini LVDS 클럭을 발생한다. 도 9와 같이 첫 번째 데이터를 샘플링하는 제1 데이터 IC(1st 32B)는 리셋파형에 이어서 발생하는 스타트펄스(start)를 데이터 샘플링시작 시점으로 인식하여 스타트펄스(start)에 이어서 공급되는 데이터들을 샘플링하기 시작한다. 따라서, 타이밍 콘트롤러(31)는 별도의 배선을 통해 소스 스타트 펄스(Source Start Pulse, SSP)를 발생하지 않는다.

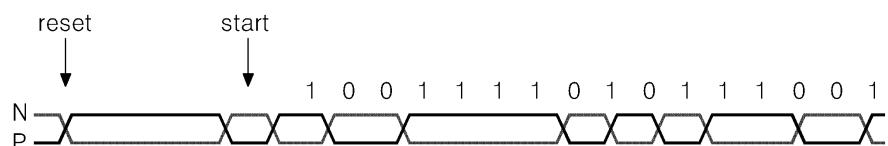

<75> 도 9는 타이밍 콘트롤러(31)와 데이터 IC(32A, 32B)들 사이의 신호전송 경로를 나타낸다.

<76> 도 9를 참조하면, 타이밍 콘트롤러(31)에 의해 mini LVDS 방식 또는 RSDS 방식으로 변조된 디지털 비디오 데이터들 중에서 우측 데이터들(RGBodd, RGBeven)은 타이밍 콘트롤러(31)의 싱글 출력포트(63), 연결 배선(44), 및 FFC(43)를 경유하여 제1 소스 PCB(41A)에 접속된 데이터 IC들(32A)에 전송된다. 우측 데이터들(RGBodd, RGBeven)은 액정표시패널(30)의 우반부 화면에 표시될 데이터들이다. 타이밍 콘트롤러(31)에 의해 mini LVDS 방식 또는 RSDS 방식으로 변조된 좌측 데이터들(RGBodd, RGBeven)은 타이밍 콘트롤러(31)의 싱글 출력포트(63), 연결 배선(44), 제1 소스 PCB(41A), 소스 COF(42A)의 더미배선(51), 및 액정표시패널(30)의 LOG 배선(45)을 경유하여 제2 소스 PCB(41B)에 접속된 데이터 IC들(32B)에 전송된다. 좌측 데이터들(RGBodd, RGBeven)은 액정표시패널(30)의 좌반부 화면에 표시될 데이터들이다.

<77> 타이밍 콘트롤러(31)에서 발생되는 데이터 타이밍 제어신호들은 데이터와 함께 타이밍 콘트롤러(31)의 싱글 출력포트(63), 연결 배선(44), 및 FFC(43)를 경유하여 제1 소스 PCB(41A)에 접속된 데이터 IC들(32A)에 전송된다. 또한, 데이터 타이밍 제어신호들은 타이밍 콘트롤러(31)의 싱글 출력포트(63), 연결 배선(44), 제1 소스 PCB(41A), 소스 COF(42A)의 더미배선(51), 및 액정표시패널(30)의 LOG 배선(45)을 경유하여 제2 소스 PCB(41B)에 접속된 데이터 IC들(32B)에 전송된다.

<78> 첫 번째 데이터를 샘플링하는 최좌측의 제1 데이터 IC(1st 32B)는 도 7 및 도 8에서 스타트펄스 이후의 데이터를 자신의 출력채널 수만큼 샘플링한 후에 그 다음 데이터의 샘플링 타이밍을 지시하는 캐리신호(carry)를 발생하여 이웃한 데이터 IC(32B)에 공급한다. 마찬가지로, 캐리신호(carry)는 이웃한 데이터 IC들(32A, 32B)에 순차적으로 전달된다. 제1 및 제2 소스 PCB들(41A, 41B) 사이에서 캐리신호(carry)는 액정표시패널(30)에 형성된 LOG 배선(45)을 통해 전송된다. 한편, 데이터 IC들(32A)의 데이터 샘플링방향은 반대로 조정될 수 있다. 이 경우, 제1 및 제2 소스 PCB들(41A, 41B) 사이에서 캐리신호(carry)는 반대방향으로 전송된다.

<79> 콘트롤 PCB(40)에 실장된 직류-직류 변환기로부터 발생되는 구동전압들은 직류-직류 변환기의 출력단자, 연결 배선(44) 및 FFC(43)를 경유하여 제1 소스 PCB(41A)에 접속된 데이터 IC들(32A)에 전송된다. 또한, 구동전압들은 직류-직류 변환기의 출력단자, 연결 배선(44), 제1 소스 PCB(41A), 소스 COF(42A)의 더미배선(51), 및 액정표시패널(30)의 LOG 배선(45)을 경유하여 제2 소스 PCB(41B)에 접속된 데이터 IC들(32B)에 전송된다.

<80> 도 10은 본 발명의 다른 실시예에 따른 액정표시장치를 나타낸다.

<81> 도 10을 참조하면, 제2 소스 PCB(41B)는 FFC(53)를 경유하여 콘트롤 PCB(40) 상에 형성된 연결 배선들(54)에 전기적으로 접속된다. 제1 소스 PCB(41A)와 그에 접속된 데이터 COF들(42A)은 콘트롤 PCB(40)에 연결되지 않고 연결 배선들(54), FFC(53), 제2 소스 PCB(41B), LOG 배선들(45)을 경유하여 데이터 타이밍 제어신호, 캐리신호, 및 구동전압들을 공급받는다.

- <82> 도 11 및 도 12는 데이터 IC(32A, 32B)를 상세히 나타내는 회로도이다.

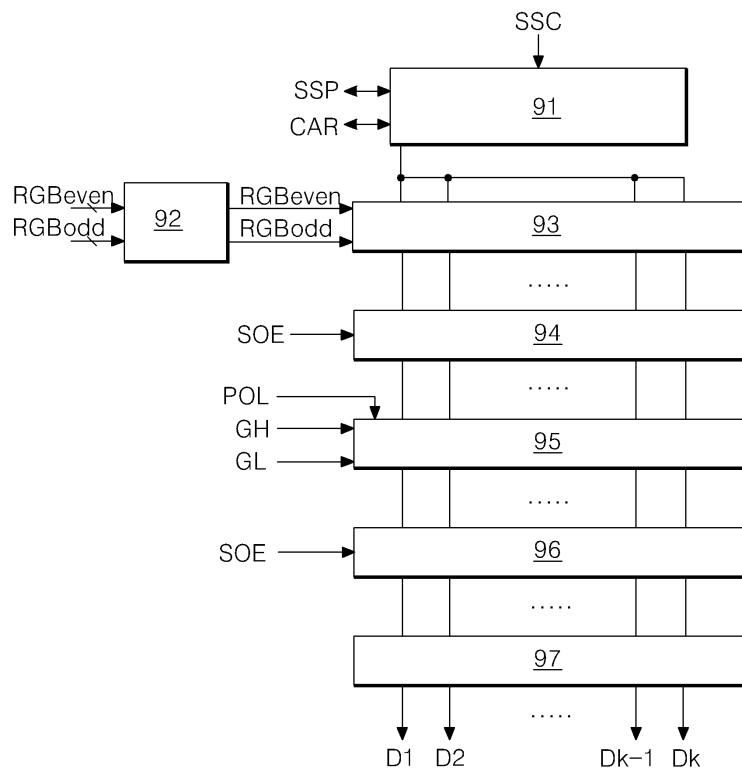

- <83> 도 11 및 도 12를 참조하면, 데이터 IC(32A, 32B) 각각은 쉬프트 레지스(91), 데이터 복원부(92), 제1 래치 어레이(93), 제2 래치 어레이(94), 디지털/아날로그 변환기(이하, "DAC"라 한다)(95), 차지쉐어회로(Charge Share Circuit)(96) 및 출력회로(97)를 포함한다.

- <84> 데이터 복원부(92)는 타이밍 콘트롤러(31)에 의해 분리된 기수 화소 데이터(RGBodd)와 우수 화소 데이터(RGBeven)를 일시 저장하고 타이밍 콘트롤러(31)에 의해 변조방식에 대응하는 복조방식으로 변조된 데이터를 복원한다. 예컨대, 데이터 복원부(92)는 도 8과 같이 정극성 데이터가 하이 논리일 때 '1'을 발생하고, 정극성 데이터가 로우 논리일 때 '0'을 발생하여 데이터를 복원한다. 그리고 데이터 복원부(92)는 복원된 데이터들(RGBodd, RGBeven)을 제1 래치 어레이(93)에 공급한다.

- <85> 쉬프트레지터(91)는 소스 샘플링 클럭(SSC)에 따라 샘플링신호를 쉬프트시킨다. 또한, 쉬프트 레지지터(91)는 제1 래치 어레이(93)의 래치수를 초과하는 데이터가 공급될 때 캐리신호(Carry)를 발생한다. 첫 번째 데이터를 샘플링하는 제1 데이터 IC(1st32B)의 쉬프트레지스터(91)는 데이터버스를 통해 데이터에 앞서 공급되는 리셋신호와 스타트펄스에 이어서 공급되는 데이터를 첫 번째 샘플링할 데이터로 판단한다.

- <86> 제1 래치 어레이(93)는 쉬프트 레지스터(91)로부터 순차적으로 입력되는 샘플링신호에 응답하여 데이터 복원부(92)로부터의 디지털 비디오 데이터들(RGBeven, RGBodd)을 샘플링하고, 그 데이터들(RGBeven, RGBodd)을 1 수평라인 분씩 래치한 다음, 1 수평라인 분의 데이터를 동시에 출력한다.

- <87> 제2 래치 어레이(94)는 제1 래치 어레이(93)로부터 입력되는 1 수평라인분의 데이터를 래치한 다음, 소스 출력 인에이블신호(SOE)의 로우논리기간 동안 다른 데이터 IC들(32a)의 제2 래치 어레이(94)와 동시에 래치된 디지털 비디오 데이터들(RGBeven, RGBodd)을 출력한다.

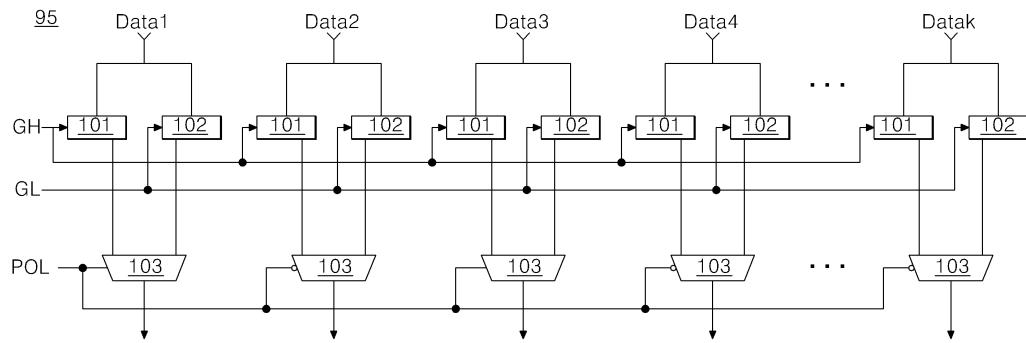

- <88> DAC(95)는 도 10과 같이 정극성 감마보상전압(GH)이 공급되는 P-디코더(PDEC)(101), 부극성 감마보상전압(GL)이 공급되는 N-디코더(NDEC)(102), 극성제어신호들(POL)에 응답하여 P-디코더(101)의 출력과 N-디코더(102)의 출력을 선택하는 멀티플렉서(103)를 포함한다. P-디코더(101)는 제2 래치 어레이(94)로부터 입력되는 디지털 비디오 데이터들(RGBeven, RGBodd)을 디코드하여 그 데이터의 계조값에 해당하는 정극성 감마보상전압(GH)을 출력하고, N-디코더(102)는 제2 래치 어레이(94)로부터 입력되는 디지털 비디오 데이터들(RGBeven, RGBodd)을 디코드하여 그 데이터의 계조값에 해당하는 부극성 감마보상전압(GL)을 출력한다. 멀티플렉서(103)는 극성제어신호(POL)에 응답하여 정극성의 감마보상전압과 부극성의 감마보상전압을 선택한다.

- <89> 차지쉐어회로(96)는 소스 출력 인에이블신호(SOE)의 하이논리기간 동안 이웃한 데이터 출력채널들을 단락(short)시켜 이웃한 데이터전압들의 평균값을 차지쉐어전압으로 출력하거나, 소스 출력 인에이블신호(SOE)의 하이논리기간 동안 데이터 출력채널들에 공통전압(Vcom)을 공급하여 정극성 데이터전압과 부극성 데이터전압의 급격한 변화를 줄인다.

- <90> 출력회로(97)는 버퍼를 포함하여 데이터라인(D1 내지 Dk)으로 공급되는 아날로그 데이터전압의 신호감쇠를 최소화한다.

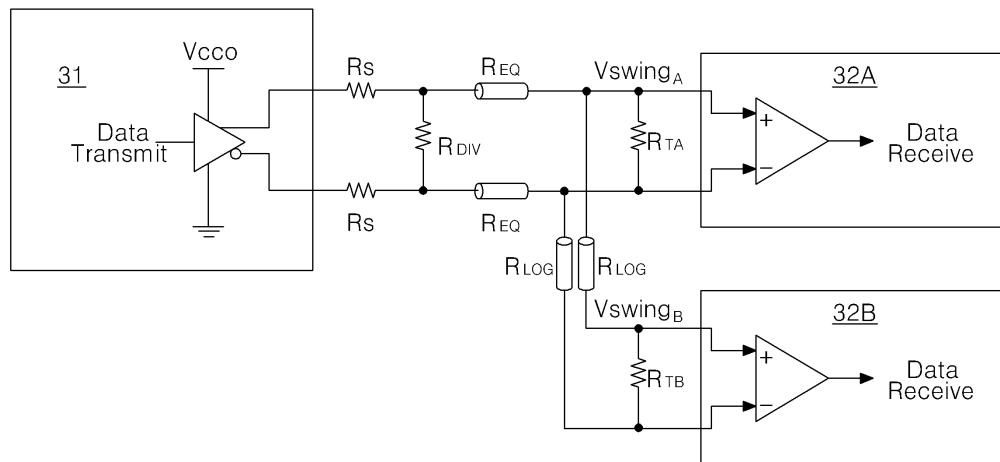

- <91> 도 13은 도 4에 도시된 타이밍 콘트롤러(31), 제1 소스 PCB들(41A)에 접속된 데이터 IC(32A), 제2 소스 PCB들(41B)에 접속된 데이터 IC(32B)와 그 사이의 저항들( $R_s$ ,  $R_{DIV}$ ,  $R_{EQ}$ ,  $R_{LOG}$ ,  $R_{TA}$ ,  $R_{TB}$ )을 등가적으로 나타낸다.

- <92> 타이밍 콘트롤러(31)로부터 출력되는 데이터와 클럭신호 각각은 정극성 신호(P)와 부극성 신호(N)를 포함한다. 이 타이밍 콘트롤러(31)의 정극성 신호 출력단자에는 저항( $R_s$ )이 접속되고, 타이밍 콘트롤러(31)의 부극성 신호 출력단자에는 저항( $R_s$ )이 접속된다. 또한, 타이밍 콘트롤러(31)의 정극성 신호 출력단자와 부극성 신호 출력단자 사이에 저항( $R_{DIV}$ )이 접속된다. 데이터 IC들(32A, 32B) 각각의 정극성 신호 입력단자와 부극성 신호 입력단자 사이에는 저항( $R_{TA}$ ,  $R_{TB}$ )이 접속된다. 이러한 저항들( $R_s$ ,  $R_{DIV}$ ,  $R_{TA}$ ,  $R_{TB}$ )은 정극성 신호(P)와 부극성 신호(N)의 위상을 동기시키고 그 전압을 300mV~600mV 정도로 조정한다. " $R_{EQ}$ "는 직렬저항( $R_s$ )과 제1 소스 PCB(41A)에 접속된 데이터 IC(32A) 사이의 신호 전송 배선과, 직렬저항( $R_s$ )과 LOG 배선들(45) 사이의 신호 전송 배선을 등가적으로 나타낸 저항으로써, 콘트롤 PCB(40)에 형성된 연결 배선(44)과 FFC(43)의 저항을 포함한다.

- <93> 도 13에서 알 수 있는 바, 본 발명의 일 실시예에 따른 액정표시장치에서 제2 소스 PCB(41B)에 접속된 데이터 IC(32B)에 공급되는 데이터, 캐리신호, 및 구동전압들은 LOG 배선들(45)의 저항( $R_{LOG}$ )으로 인하여 전압 강하된다. 따라서, 제1 소스 PCB(41A)에 접속된 데이터 IC(32A)에 공급되는 신호에 비하여, 제2 소스 PCB(41

B)에 접속된 데이터 IC(32B)에 공급되는 신호의 전압이 낮아진다.

<94> LOG 저항을 보상하기 위하여, 본 발명의 실시예는 LOG 저항의 영향을 받지 않는 데이터 IC(32A)의 정극성 신호 입력단자와 부극성 신호 입력단자 사이에 접속된 저항( $R_{TA}$ ,  $R_{TB}$ )의 저항값을 아래와 같이 결정한다.

<95> LOG 저항에 영향을 받지 않는 데이터 IC(32A)에 공급되는 mini LVDS 신호의 전압( $V_{swing_A}$ )은 아래의 수학식 1과 같다.

### 수학식 1

$$V_{swing_A} = \frac{(R_{DIV}/2)}{(R_{DIV}/2) + R_{DRIVER} + R_S} \cdot \frac{(R_{TB}/2)}{(R_{TB/2}) + R_{EQ}} \cdot V_{cco}$$

&lt;96&gt;

<97> LOG 저항에 영향을 받는 데이터 IC(32B)에 공급되는 mini LVDS 신호의 전압( $V_{swing_B}$ )은 수학식 2와 같다.

### 수학식 2

$$V_{swing_B} = \frac{(R_{DIV}/2)}{(R_{DIV}/2) + R_{DRIVER} + R_S} \cdot \frac{(R_{TA}/2)}{(R_{TA/2}) + R_{EQ} + R_{LOG}} \cdot V_{cco}$$

&lt;98&gt;

<99> 수학식 1 및 2에 있어서, " $R_{DRIVER}$ "는 타이밍 콘트롤러(31) 내의 내부 저항이고,  $V_{cco}$ 의 타이밍 콘트롤러(31)의 데이터 송신기 구동전압이다.

&lt;100&gt;

이 데이터 IC들(32A, 32B)의 mini LVDS 신호 입력의 편차를 보정하기 위해서는 아래의 수학식 3과 같이 LOG 저항의 영향을 받지 않는 mini LVDS 신호 입력 전압과, LOG 저항의 영향을 받는 mini LVDS 신호 입력 전압이 같아야 한다.

### 수학식 3

$$V_{swing_A} = V_{swing_B} \\ = \frac{R_{TB}}{R_{TB} + 2R_{EQ}} = \frac{R_{TA}}{R_{TA} + 2R_{EQ} + 2R_{LOG}}$$

&lt;101&gt;

<102> 따라서, 제1 소스 PCB(41A)에 접속된 데이터 IC(32A)의 정극성 신호 입력단자와 부극성 신호 입력단자 사이에 접속된 저항( $R_{TA}$ )는 아래의 수학식 4와 같은 저항값으로 결정된다.

### 수학식 4

$$R_{TA} = \frac{R_{TB}(R_{EQ} + R_{LOG})}{R_{EQ}}$$

&lt;103&gt;

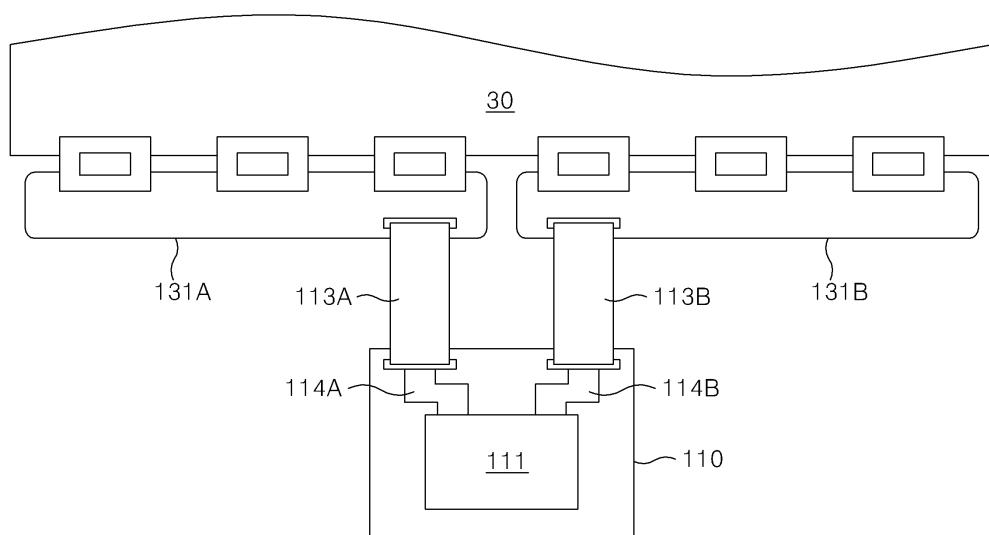

도 14와 같이 소스 PCB들(131A, 131B)을 두 개로 분리하고 타이밍 콘트롤러(111)의 출력포트 역시 두 개로 분리하여 더블 출력포트로 구성하는 방법도 고려할 수 있으나, 이 경우에 타이밍 콘트롤러(111)와 콘트롤 PCB(110)가 커질 수 밖에 없다.

&lt;104&gt;

삭제

&lt;105&gt;

이를 상세히 설명하면 다음과 같다.

&lt;106&gt;

타이밍 콘트롤러(111)의 출력포트가 2 개로 분리된다고 가정할 때 타이밍 콘트롤러(111)는 도 15와 같이 좌/우

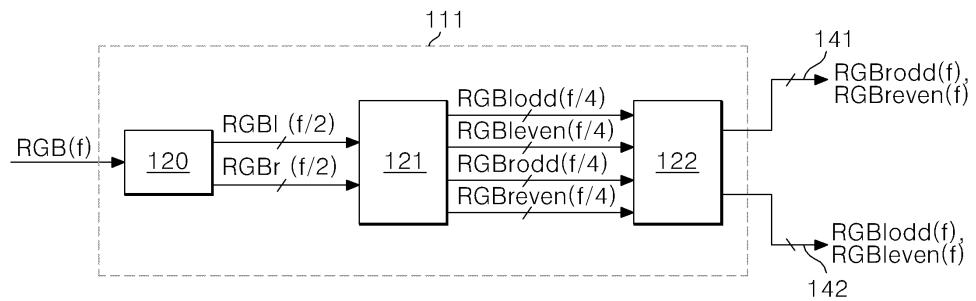

데이터 분리부(120), 2 포트 확장부(121) 및 데이터 변조부(122)를 구비한다.

<107> 좌/우 데이터 분리부(120)는 프레임 메모리를 이용하여 입력 주파수(f)로 입력되는 입력 디지털 비디오 데이터(RGB)를 좌측 데이터(RGB1)와 우측 데이터(RGBr)로 분리한다. 좌/우 데이터 분리부(120)로부터 출력되는 데이터들(RGB1, RGBr)은 입력 주파수의 1/2 주파수(f/2)로 2 포트 확장부(121)에 공급된다.

<108> 이러한 좌/우 데이터 분리부(120)와 두 개의 FFC(113A, 113B)로 인하여, 타이밍 콘트롤러(111)의 출력포트를 더 블 출력포트(141, 142)로 분리하면 타이밍 콘트롤러(111)의 크기가 커질 수 밖에 없다.

<109> 2 포트 확장부(121)는 좌/우 데이터 분리부(120)로부터 1/2 주파수(f/2)로 입력되는 좌/우 데이터들(RGB1, RGBr)을 기수 화소 데이터(RGB1odd, RGB1odd)와 우수 화소 데이터(RGB1even, RGB1even)로 분리하여 그 데이터들(RGB1odd, RGB1even)을 1/4 주파수(f/4)로 데이터 변조부(62)에 공급한다.

<110> 데이터 변조부(122)는 mini LVDS 방식으로 데이터를 변조하는 경우에 4 배속 mini LVDS 클럭에 따라 2 포트 확장부(121)로부터의 데이터들(RGB1odd, RGB1odd, RGB1even, RGB1even)의 주파수를 높여 입력 주파수와 같은 주파수(f)로 좌측 데이터(RGB1odd, RGB1even)와 우측 데이터(RGB1odd, RGB1even)를 서로 다른 출력포트(141, 142)로 분할 출력한다. 좌측 데이터(RGB1odd, RGB1even)와 우측 데이터(RGB1odd, RGB1even) 각각은 3쌍의 기수 화소 데이터들, 3쌍의 우수 화소 데이터들 및 1쌍의 mini 클럭을 포함하므로 타이밍 콘트롤러(111)의 출력핀들의 수는 전술한 본 발명의 실시예에 비하여 2 배 이상 필요하게 된다. 우측 데이터(RGB1odd, RGB1even)는 타이밍 콘트롤러(111)의 제1 출력포트(141), 제1 연결배선(113A), 및 제1 FFC(113B)를 경유하여 제1 소스 PCB(131A)에 전송된다. 좌측 데이터(RGB1odd, RGB1even)는 타이밍 콘트롤러(111)의 제2 출력포트(141), 제2 연결배선(113B), 및 제2 FFC(113B)를 경유하여 제2 소스 PCB(131B)에 전송된다.

<111> 결과적으로, 소스 PCB를 분리하는 경우에 타이밍 콘트롤러와 그 출력핀 수를 줄이고 콘트롤 PCB의 크기를 줄이기 위해서는 타이밍 콘트롤러의 출력포트를 싱글포트로 구성하는 것이 바람직하다.

### 발명의 효과

<112> 상술한 바와 같이, 본 발명에 따른 액정표시장치와 그 구동방법은 소스 PCB를 분할하고 타이밍 콘트롤러의 출력포트를 싱글 출력포트로 구성하여 콘트롤 PCB의 크기와 출력 핀수를 줄일 수 있다. 나아가, 본 발명에 따른 액정표시장치와 그 구동방법은 액정표시패널에 형성된 LOG 배선을 이용하여 하나의 FFC를 제거함으로써 소스 PCB와 콘트롤 PCB의 접속 구조를 단순화할 수 있고 부품 수를 줄일 수 있다.

<113> 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

### 도면의 간단한 설명

- <1> 도 1은 액정표시장치의 액정셀을 보여 주는 등가 회로도.

- <2> 도 2는 싱글 소스 PCB를 가지는 액정표시장치를 나타내는 도면.

- <3> 도 3은 본 발명의 일 실시예에 따른 액정표시장치를 나타내는 블록도.

- <4> 도 4는 도 3에 도시된 타이밍 콘트롤러와 데이터 IC들의 접속 구조를 상세히 나타내는 도면.

- <5> 도 5는 소스 COF에 형성된 더미 배선들과 액정표시패널의 기판 상에 형성된 LOG 배선들을 나타내는 평면도.

- <6> 도 6은 도 3 및 도 4에 도시된 타이밍 콘트롤러의 데이터 처리부를 상세히 나타내는 블록도.

- <7> 도 7 및 도 8은 도 6에 도시된 데이터 변조부의 출력 예를 나타내는 파형도.

- <8> 도 9는 도 4에 도시된 타이밍 콘트롤러와 데이터 IC들 사이의 신호 전송경로를 나타내는 도면.

- <9> 도 10은 본 발명의 다른 실시예에 따른 액정표시장치를 나타내는 블록도.

- <10> 도 11은 도 4에 도시된 데이터 IC를 상세히 나타내는 블록도.

- <11> 도 12는 도 11에 도시된 DAC를 상세히 나타내는 회로도.

- <12> 도 13은 도 4에 도시된 타이밍 콘트롤러, 제1 소스 PCB에 접속된 데이터 IC, 제2 소스 PCB에 접속된 데이터 IC

와 그 사이의 저항들을 등가적으로 나타내는 회로도.

<13> 도 14 및 도 15는 소스 PCB를 분리하고 타이밍 콘트롤러의 출력포트를 더블 출력포트로 구성한 예를 나타내는 도면들.

<14> < 도면의 주요 부분에 대한 부호의 설명 >

|                  |               |

|------------------|---------------|

| <15> 30 : 액정표시패널 | 31 : 타이밍 콘트롤러 |

|------------------|---------------|

|                        |               |

|------------------------|---------------|

| <16> 32A, 32B : 데이터 IC | 33 : 게이트 구동회로 |

|------------------------|---------------|

|                   |                               |

|-------------------|-------------------------------|

| <17> 40 : 콘트롤 PCB | 41A, 41B, 131A, 131B : 소스 PCB |

|-------------------|-------------------------------|

|                        |                          |

|------------------------|--------------------------|

| <18> 42A, 42B : 소스 COF | 43, 53, 113A, 113B : FFC |

|------------------------|--------------------------|

|                                 |                    |

|---------------------------------|--------------------|

| <19> 44, 54, 114A, 114B : 연결 배선 | 61, 121 : 2 포트 확장부 |

|---------------------------------|--------------------|

|                        |              |

|------------------------|--------------|

| <20> 62, 122 : 데이터 변조부 | 63 : 싱글 출력포트 |

|------------------------|--------------|

|                    |              |

|--------------------|--------------|

| <21> 91 : 쉬프트 레지스터 | 92 : 데이터 복원부 |

|--------------------|--------------|

|                  |          |

|------------------|----------|

| <22> 93, 94 : 래치 | 95 : DAC |

|------------------|----------|

|                  |           |

|------------------|-----------|

| <23> 96 : 차지쉐어회로 | 97 : 출력회로 |

|------------------|-----------|

|                  |             |

|------------------|-------------|

| <24> 101 : P-디코더 | 102 : N-디코더 |

|------------------|-------------|

|                  |                   |

|------------------|-------------------|

| <25> 103 : 멀티플렉서 | 120 : 좌/우 데이터 분리부 |

|------------------|-------------------|

|                         |  |

|-------------------------|--|

| <26> 141, 142 : 더블 출력포트 |  |

|-------------------------|--|

## 도면

### 도면1

## 도면2

## 도면3

**도면4**

**도면5**

**도면6**

**도면7****도면8****도면9**

도면10

도면11

도면12

도면13

도면14

도면15

|                |                                                                                                                      |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动方法                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">KR100855502B1</a>                                                                                        | 公开(公告)日 | 2008-09-01 |

| 申请号            | KR1020070046126                                                                                                      | 申请日     | 2007-05-11 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                             |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                                            |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                                            |         |            |

| [标]发明人         | JANG SU HYUK<br>장수혁<br>SONG HONG SUNG<br>송홍성<br>MIN WOONG KI<br>민웅기<br>CHOI BYUNG JIN<br>최병진<br>CHA DONG HOON<br>차동훈 |         |            |

| 发明人            | 장수혁<br>송홍성<br>민웅기<br>최병진<br>차동훈                                                                                      |         |            |

| IPC分类号         | G02F1/1345 G02F1/133 G09G3/36                                                                                        |         |            |

| CPC分类号         | G02F1/13452 G09G3/3406 G09G3/3614 G09G3/3648 G09G3/3696 G09G2320/0646                                                |         |            |

| 优先权            | 1020070030323 2007-03-28 KR                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                            |         |            |

### 摘要(译)

液晶显示装置及其驱动方法技术领域本发明涉及一种简化控制PCB的液晶显示装置及其驱动方法。液晶显示装置包括第一和第二数据线组，每个数据线组包括多条数据线，与第一和第二数据线组交叉的多条栅极线，以及形成在基板边缘的LOG布线，一种液晶显示板，具有以矩阵形式排列的液晶单元;第一数据电路组，包括用于向第一数据线组提供数据的数据IC;第一数据电路组连接的第一源PCB;第二数据电路组，包括用于向第二数据线组提供数据的数据IC;第二数据电路组连接的第二源PCB;一种定时控制器，用于输出定时控制信号，用于通过单个输出端口控制第一和第二数据电路组和数据;安装定时控制器的控制PCB;以及用于将单个输出端口电连接到第一源极PCB的连接单元。