**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl.<sup>7</sup>

G02F 1/13

(11) 공개번호 10-2005-0038216

(43) 공개일자 2005년04월27일

(21) 출원번호 10-2003-0073452

(22) 출원일자 2003년10월21일

(71) 출원인 엘지.필립스 엘시디 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자 박찬일

전라북도 전주시 덕진구 우아동 3가 746-15

(74) 대리인 박장원

심사청구 : 없음

**(54) 액정 표시장치의 테스트 모듈**

**요약**

본 발명은 액정 표시장치의 테스트 모듈에 관한 것으로, 탐침들이 일층 단부에 구비된 전도성 지지체들이 비전도성 몸체를 관통하여 삽입되므로, 테스트 모듈을 구동시켜 비전도성 몸체를 게이트패드, 소스패드 및 드레인패드와 정렬시키면, 탐침들이 게이트패드, 소스패드 및 드레인패드와 동시에 정렬됨에 따라 정렬시간이 단축되고, 탐침들이 파손될 위험을 최소화 하며, 그 탐침들에 상기 게이트패드, 소스패드 및 드레인패드가 긁히는 현상을 방지할 수 있게 된다.

**대표도**

도 4

**명세서**

**도면의 간단한 설명**

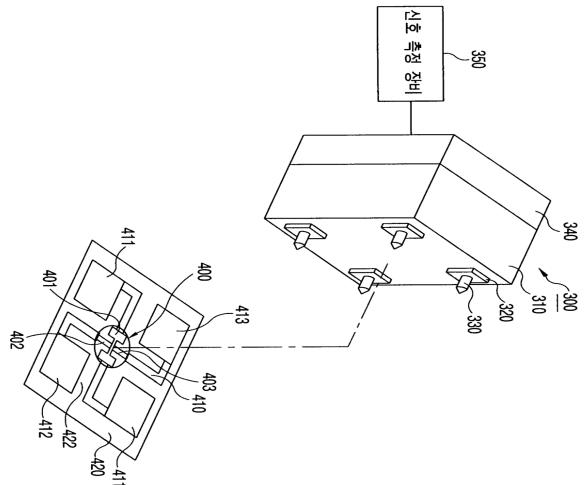

도1은 대면적의 제1모기관 상에 복수의 박막 트랜지스터 어레이 기관들이 형성된 평면구성을 보인 예시도.

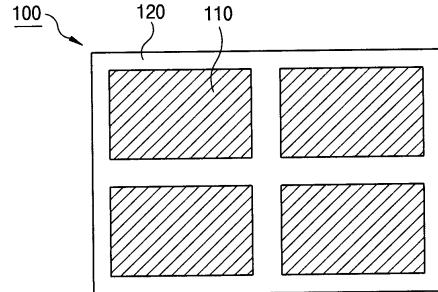

도2는 도1에 있어서, 제1모기관의 더미영역에 형성된 테스트용 박막 트랜지스터를 보인 예시도.

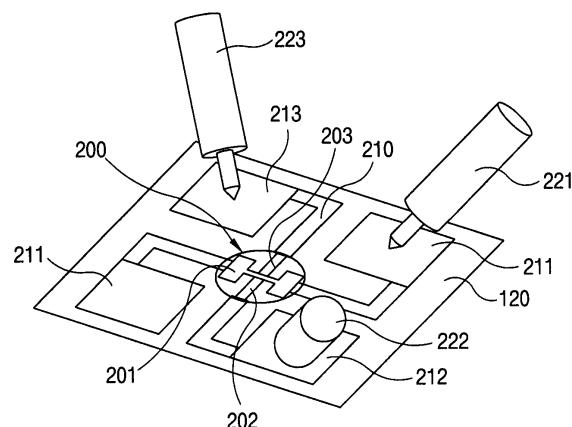

도3은 본 발명에 따른 액정 표시장치의 테스트 모듈을 보인 예시도.

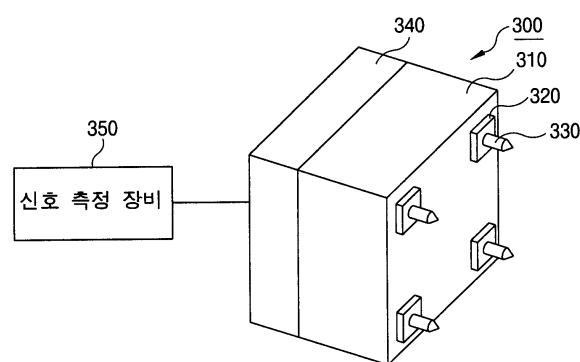

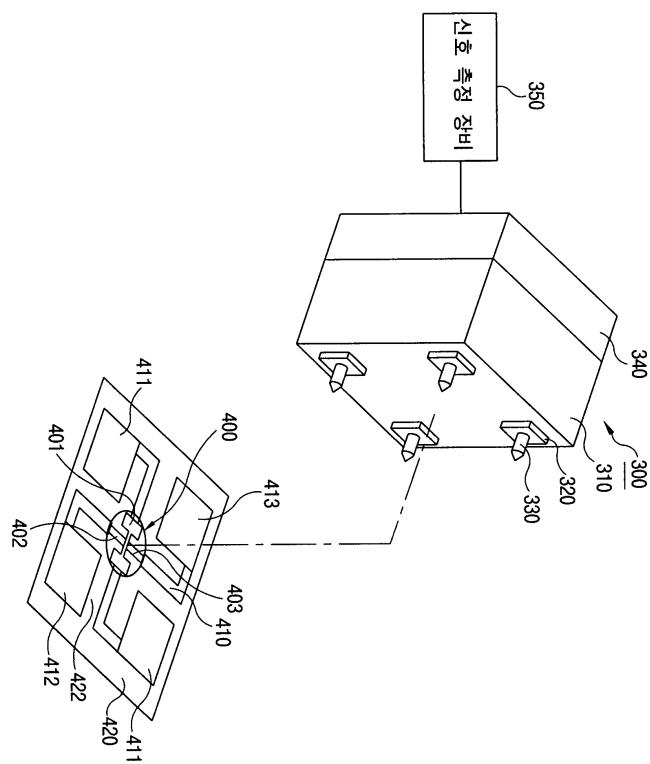

도4는 도3에 도시된 액정 표시장치의 테스트 모듈을 사용하여 제1모기관의 더미영역에 형성된 테스트용 박막 트랜지스터의 특성을 테스트하는 예를 보인 예시도.

\*\*\*도면의 주요부분에 대한 부호의 설명\*\*\*

300: 테스트 모듈 310: 비전도성 몸체

320: 전도성 지지체 330: 탐침

340: 커넥터 350: 신호측정장비

400: 테스트용 박막 트랜지스터 401: 게이트전극

402: 소스전극 403: 드레인전극

410: 연장배선 411: 게이트패드

412: 소스패드 413: 드레인패드

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정 표시장치의 테스트 모듈에 관한 것으로, 보다 상세하게는 대면적 모기판의 더미영역에 형성되는 복수의 테스트 패턴들을 통해 액정 표시장치의 소자특성을 테스트 및 평가할 수 있도록 한 액정 표시장치의 테스트 모듈에 관한 것이다.

일반적으로, 액정 표시장치는 매트릭스(matrix) 형태로 배열된 화소들에 화상정보에 따른 데이터신호를 개별적으로 공급하여, 그 화소들의 광투과율을 조절함으로써, 원하는 화상을 표시할 수 있도록 한 표시장치이다.

따라서, 액정 표시장치에는 화소들이 매트릭스 형태로 배열되는 액정 표시패널과; 상기 화소들을 구동하기 위한 구동회로가 구비된다.

상기 액정 표시패널은 서로 대향하여 균일한 셀-캡을 갖도록 합착된 박막 트랜지스터 어레이(thin film transistor array) 기판 및 컬러필터(color filter) 기판과, 그 컬러필터 기판 및 박막 트랜지스터 어레이 기판의 이격 간격에 형성된 액정층으로 구성된다.

상기 박막 트랜지스터 어레이 기판과 컬러필터 기판이 합착된 액정 표시패널에는 공통전극과 화소전극이 형성되어 상기 액정층에 전계를 인가한다. 즉, 공통전극에 전압을 인가한 상태에서 화소전극에 인가되는 데이터신호의 전압을 제어함으로써, 화소들의 광투과율을 개별적으로 조절할 수 있게 된다. 이와같이 화소전극에 인가되는 데이터신호의 전압을 화소 별로 제어하기 위하여 각각의 화소에는 스위칭 소자로 사용되는 박막 트랜지스터가 형성된다.

상기 한 바와같은 액정 표시패널을 제작함에 있어서, 수율을 향상시키기 위하여 복수의 박막 트랜지스터 어레이 기판들을 대면적의 제1모기판에 형성하고, 복수의 컬러필터 기판들을 대면적의 제2모기판에 형성한 다음 상기 제1모기판과 제2모기판이 균일한 셀-캡을 갖도록 합착함으로써, 복수의 액정 표시패널들을 동시에 형성한 다음 그 복수의 액정 표시패널들이 제작된 제1, 제2모기판을 절단 및 가공하여 액정 표시패널들을 분리하는 방식이 일반적으로 적용되고 있다.

한편, 상기 제1모기판에 복수의 박막 트랜지스터 어레이 기판들이 형성된 다음에는 박막 트랜지스터 어레이 기판들이 형성된 박막 트랜지스터들의 특성을 테스트하여 불량여부를 판정함으로써, 불량이 발생된 제1모기판의 후속 공정 진행을 차단하여 재료비 낭비를 방지하고, 수율 향상을 도모하고 있다.

상기 박막 트랜지스터의 특성을 테스트하기 위한 종래의 방법을 첨부된 도면을 참조하여 상세히 설명하면 다음과 같다.

도1은 대면적의 제1모기판 상에 복수의 박막 트랜지스터 어레이 기판들이 형성된 평면구성을 보인 예시도이다.

도1을 참조하면, 제1모기판(100) 상에는 일정하게 이격된 복수의 박막 트랜지스터 어레이 기판(110)들이 형성된다.

전술한 바와같이 상기 복수의 박막 트랜지스터 어레이 기판(110)들이 형성된 제1모기판(100)은 복수의 컬러필터 기판들이 형성된 제2모기판과 일정한 셀-캡이 유지되도록 합착되어 복수의 액정 표시패널들이 동시에 형성되고, 그 복수의 액정 표시패널들이 형성된 제1모기판(100)과 제2모기판은 절단 및 가공되어 액정 표시패널들이 개별적으로 분리된다.

따라서, 상기 복수의 박막 트랜지스터 어레이 기판(110)들은 상기 제1모기판(100)과 제2모기판의 셀-캡 유지 및 상기 복수의 액정 표시패널들이 형성된 제1모기판(100)과 제2모기판의 절단 및 가공에 따른 공정 마진을 확보하기 위하여 일정하게 이격되도록 형성되며, 이와같이 박막 트랜지스터 어레이 기판(110)들이 서로 이격되도록 형성된 제1모기판(100)은 더미영역(120)을 갖게 된다.

상기 제1모기판(100)의 더미영역(120)은 전술한 제1모기판(100)과 제2모기판을 일정한 셀-캡이 유지되도록 합착하여 복수의 액정 표시패널들을 동시에 형성한 다음 제1모기판(100)과 제2모기판의 절단 및 가공을 통해 액정 표시패널들을 개별적으로 분리할 때, 제거되는 영역으로 액정 표시패널에 아무런 영향을 주지 않지만, 상기 제1모기판(100)에 박막 트랜지스터 어레이 기판(110)들을 형성하기 위한 공정들이 진행될 때, 공정진행 장비와 제1모기판(100)을 정렬시키기 위한 정렬마크나 박막 트랜지스터 어레이 기판(110) 상에 제작되는 박막 트랜지스터들의 특성을 테스트 하기 위한 복수의 테스트용 박막 트랜지스터들이 형성되어 공정 진행을 원활하게 하고, 불량 여부를 판정할 수 있도록 한다.

도2는 상기 도1에 있어서, 제1모기판(100)의 더미영역(120)에 형성된 테스트용 박막 트랜지스터를 보인 예시도이다.

도2를 참조하면, 제1모기판(100)의 더미영역(120)에 형성된 테스트용 박막 트랜지스터(200)는 게이트전극(201), 소스전극(202) 및 드레인전극(203)으로 구성되며, 그 게이트전극(201), 소스전극(202) 및 드레인전극(203)은 연장배선(210)을 통해 게이트패드(211), 소스패드(212) 및 드레인패드(213)와 전기적으로 연결된다.

상기 테스트용 박막 트랜지스터(200)는 제1모기판(100)의 박막 트랜지스터 어레이 기판(110)들에 형성되는 박막 트랜지스터들의 특성을 테스트하기 위하여 제1모기판(100)의 박막 트랜지스터 어레이 기판(110)들에 형성되는 박막 트랜지스터들과 동일한 채널폭 및 채널길이를 갖도록 형성된다.

따라서, 테스트 유닛(221,222,223)들을 통해 테스트용 박막 트랜지스터(200)의 게이트패드(211), 소스패드(212) 및 드레인패드(213)에 전기 신호를 인가하여 테스트용 박막 트랜지스터(200)의 특성을 테스트함으로써, 제1모기판(100)의 박막 트랜지스터 어레이 기판(110)들에 형성되는 박막 트랜지스터들의 특성 평가 및 불량 판정을 할 수 있게 된다.

그러나, 상기 테스트용 박막 트랜지스터(200)의 게이트패드(211), 소스패드(212) 및 드레인패드(213)에 전기 신호를 인가하는 테스트 유닛(221,222,223)들은 독립적으로 구동되어 게이트패드(211), 소스패드(212) 및 드레인패드(213)와 개별적으로 정렬됨에 따라 정렬시간이 길어지고, 이로 인해 테스트에 장시간이 소요되어 액정 표시장치의 생산성이 저하되는 문제점이 있다.

또한, 상기 테스트 유닛(221,222,223)들이 독립적으로 구동되어 게이트패드(211), 소스패드(212) 및 드레인패드(213)와 개별적으로 정렬됨에 따라 상기 테스트 유닛(221,222,223)들의 탐침이 파손될 위험이 크고, 그 테스트 유닛(221,222,223)들의 탐침에 상기 게이트패드(211), 소스패드(212) 및 드레인패드(213)가 긁히는 현상이 발생되어 테스트를 실시할 수 없거나 테스트의 신뢰성이 저하되는 문제점이 있다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명은 상기한 바와같은 종래의 문제점을 해결하기 위하여 창안한 것으로, 본 발명의 목적은 대면적 모기판의 더미영역에 형성되는 복수의 테스트 패턴들을 통해 액정 표시장치의 소자특성을 테스트 및 평가함에 있어 테스트에 소요되는 시간을 단축하고, 테스트의 신뢰성을 향상시킬 수 있는 액정 표시장치의 테스트 모듈을 제공하는데 있다.

### 발명의 구성 및 작용

상기 본 발명의 목적을 달성하기 위한 액정 표시장치의 테스트 모듈은 비전도성 몸체와; 상기 비전도성 몸체를 관통하여 삽입되는 복수의 전도성 지지체들과; 상기 복수의 전도성 지지체들의 일측 단부에 각각 구비되는 탐침들과; 상기 복수의 전도성 지지체들의 타측 단부와 신호측정장비를 전기적으로 연결시키는 커넥터를 구비하여 구성되는 것을 특징으로 한다.

상기한 바와같은 본 발명에 의한 액정 표시장치의 테스트 모듈을 첨부한 도면을 참조하여 상세히 설명하면 다음과 같다.

도3은 본 발명에 따른 액정 표시장치의 테스트 모듈을 보인 예시도이다.

도3을 참조하면, 액정 표시장치의 테스트 모듈(300)은 비전도성 몸체(310)와; 상기 비전도성 몸체(310)를 관통하여 삽입되는 전도성 지지체(320)들과; 상기 전도성 지지체(320)들의 일측 단부에 각각 구비되는 탐침(330)들과; 상기 전도성 지지체(320)들의 타측 단부와 신호측정장비(350)를 전기적으로 연결시키는 커넥터(340)로 구성된다.

도4는 상기 도3에 도시된 액정 표시장치의 테스트 모듈(300)을 사용하여 제1모기판의 더미영역에 형성된 테스트용 박막 트랜지스터의 특성을 테스트하는 예를 보인 예시도이다.

도4를 참조하면, 제1모기판의 더미영역에 형성된 테스트용 박막 트랜지스터(400)는 게이트전극(401), 소스전극(402) 및 드레인전극(403)으로 구성되며, 그 게이트전극(401), 소스전극(402) 및 드레인전극(403)은 연장배선(410)을 통해 게이트패드(411), 소스패드(412) 및 드레인패드(413)와 전기적으로 연결된다. 이때, 연장배선(410)은 테스트용 박막 트랜지스터(400)를 형성하기 위한 액티브층을 사용하여 형성할 수 있다.

상기 도3 및 도4에 도시된 액정 표시장치의 테스트 모듈(300)에는 상기 게이트패드(411), 소스패드(412) 및 드레인패드(413)에 접촉되어 전기신호를 인가하는 탐침(330)들이 4개가 구비되지만, 상기 게이트패드(411)에 접촉되는 2개의 탐침(330)들은 선택적으로 하나만 사용된다.

또한, 상기 도3 및 도4에 도시된 액정 표시장치의 테스트 모듈(300)에는 상기 게이트패드(411), 소스패드(412) 및 드레인패드(413)에 접촉되어 전기신호를 인가하는 탐침(330)들이 3개가 구비될 수 있으며, 테스트 대상 소자들의 단자 구성에 대응하는 갯수가 구비될 수 있다.

전술한 바와같이 액정 표시패널은 서로 대향하여 균일한 셀-캡을 갖도록 합착된 박막 트랜지스터 어레이 기판 및 컬러필터 기판과, 그 컬러필터 기판 및 박막 트랜지스터 어레이 기판의 이격 간격에 형성된 액정층으로 구성된다.

상기 박막 트랜지스터 어레이 기판과 컬러필터 기판이 합착된 액정 표시패널에는 공통전극과 화소전극이 형성되어 상기 액정층에 전계를 인가한다. 즉, 공통전극에 전압을 인가한 상태에서 화소전극에 인가되는 데이터신호의 전압을 제어함으로써, 화소들의 광투과율을 개별적으로 조절할 수 있게 된다. 이와같이 화소전극에 인가되는 데이터신호의 전압을 화소 별로 제어하기 위하여 각각의 화소에는 스위칭 소자로 사용되는 박막 트랜지스터가 형성된다.

상기한 바와같은 액정 표시패널을 제작함에 있어서, 수율을 향상시키기 위하여 복수의 박막 트랜지스터 어레이 기판들을 대면적의 제1모기판에 형성하고, 복수의 컬러필터 기판들을 대면적의 제2모기판에 형성하여 상기 제1모기판과 제2모기판이 균일한 셀-캡을 갖도록 합착함으로써, 복수의 액정 표시패널들을 동시에 형성한 다음 그 복수의 액정 표시패널들이 제작된 제1, 제2모기판을 절단 및 가공하여 액정 표시패널들을 분리하는 방식이 일반적으로 적용되고 있다.

따라서, 상기 복수의 박막 트랜지스터 어레이 기판들은 상기 제1모기판과 제2모기판의 셀-캡 유지 및 상기 복수의 액정 표시패널들이 형성된 제1모기판과 제2모기판의 절단 및 가공에 따른 공정 마진을 확보하기 위하여 일정하게 이격되도록 형성되며, 이와같이 박막 트랜지스터 어레이 기판들이 서로 이격되도록 형성된 제1모기판은 더미영역을 갖게 된다.

상기 제1모기판의 더미영역은 제1모기판과 제2모기판을 일정한 셀-캡이 유지되도록 합착하여 복수의 액정 표시패널들을 동시에 형성한 다음 제1모기판과 제2모기판의 절단 및 가공을 통해 액정 표시패널들을 개별적으로 분리할 때, 제거되는 영역으로 액정 표시패널에 아무런 영향을 주지 않지만, 상기 제1모기판에 박막 트랜지스터 어레이 기판들을 형성하기 위한 공정들이 진행될 때, 공정진행 장비와 제1모기판을 정렬시키기 위한 정렬마크나 박막 트랜지스터 어레이 기판 상에 제작되는 박막 트랜지스터들의 특성을 테스트 하기 위한 복수의 테스트용 박막 트랜지스터(400)들이 형성되어 공정 진행을 원활하게 하고, 불량 여부를 판정할 수 있도록 한다.

따라서, 상기 테스트용 박막 트랜지스터(400)는 제1모기판의 박막 트랜지스터 어레이 기판들에 형성되는 박막 트랜지스터들의 특성을 테스트하기 위하여 제1모기판의 박막 트랜지스터 어레이 기판들에 형성된 박막 트랜지스터들과 동일한 채널폭 및 채널길이를 갖도록 형성된다.

상기 제1모기판의 박막 트랜지스터 어레이 기판들에는 다양한 채널폭 및 채널길이를 갖는 박막 트랜지스터들이 형성될 수 있으며, 상기 제1모기판의 더미영역에는 상기 다양한 채널폭 및 채널길이를 갖는 박막 트랜지스터들 각각에 대응하는 복수의 테스트용 박막 트랜지스터(400)들이 형성된다.

예를 들어, 제1모기판의 박막 트랜지스터 어레이 기판들에 채널 폭/길이 비가 4/6인 박막 트랜지스터들이 형성된 경우에 상기 제1모기판의 더미영역에는 채널 폭/길이 비가 4/6인 테스트용 박막 트랜지스터(400)들이 60개 ~ 수백개 정도 형성되며, 상기 도3에 도시된 액정 표시장치의 테스트 모듈(300)을 통해 상기 게이트패드(411), 소스패드(412) 및 드레인패드(413)에 전기신호를 인가하여 상기 60개 ~ 수백개의 테스트용 박막 트랜지스터(400)들의 전기적 특성을 테스트함으로써, 상기 제1모기판의 박막 트랜지스터 어레이 기판들에 형성된 채널 폭/길이 비가 4/6인 박막 트랜지스터들의 전기적 특성을 평가하고, 불량여부를 판정한다.

한편, 상기 테스트용 박막 트랜지스터(400)들이 다양한 채널폭 및 채널길이를 갖는 경우에 그 게이트전극(401), 소스전극(402) 및 드레인전극(403)의 형성위치가 변경될 수 있지만, 그 게이트전극(401), 소스전극(402) 및 드레인전극(403)과 연장배선(410)을 통해 전기적으로 연결되는 게이트패드(411), 소스패드(412) 및 드레인패드(413)의 형성위치는 테스트용 박막 트랜지스터(400)들의 다양한 채널폭 및 채널길이에 상관없이 동일한 위치에 형성된다. 따라서, 본 발명에 의한 액정 표시장치의 테스트 모듈(300)은 다양한 채널폭 및 채널길이를 갖는 테스트용 박막 트랜지스터(400)들을 테스트하는데 일률적으로 적용할 수 있다.

전술한 바와같이, 종래에는 도2에 도시된 바와같이 테스트용 박막 트랜지스터(200)의 게이트패드(211), 소스패드(212) 및 드레인패드(213)에 전기 신호를 인가하는 테스트 유닛(221,222,223)들이 독립적으로 구동되어 게이트패드(211), 소스패드(212) 및 드레인패드(213)와 개별적으로 정렬됨에 따라 정렬시간이 길어지고, 테스트 유닛(221,222,223)들의 탐침이 파손될 위험이 크며, 그 테스트 유닛(221,222,223)들의 탐침에 상기 게이트패드(211), 소스패드(212) 및 드레인패드(213)가 긁히는 현상을 발생되었다.

그러나, 본 발명에 의한 액정 표시장치의 도3 및 도4에 도시된 바와같이 테스트 모듈(300)은 탐침(330)들이 일측 단부에 구비된 전도성 지지체(320)들이 비전도성 몸체(310)를 관통하여 삽입됨에 따라 테스트 모듈(300)을 구동시키게 되면, 상기 탐침(330)들이 상기 게이트패드(411), 소스패드(412) 및 드레인패드(413)와 동시에 정렬됨에 따라 정렬시간이 단축되고, 탐침(330)들이 파손될 위험을 최소화하며, 그 탐침(330)들에 상기 게이트패드(411), 소스패드(412) 및 드레인패드(413)가 긁히는 현상을 방지할 수 있게 된다.

### 발명의 효과

상술한 바와같이 본 발명에 의한 액정 표시장치의 테스트 모듈은 탐침들이 일측 단부에 구비된 전도성 지지체들이 비전도성 몸체를 관통하여 삽입되므로, 테스트 모듈을 구동시켜 비전도성 몸체를 게이트패드, 소스패드 및 드레인패드와 정렬시키면, 탐침들이 게이트패드, 소스패드 및 드레인패드와 동시에 정렬됨에 따라 정렬시간이 단축되고, 이로 인해 테스트에 소요되는 시간이 단축되어 액정 표시장치의 생산성을 향상시킬 수 있는 효과가 있다.

또한, 상기 탐침들이 파손될 위험을 최소화하며, 그 탐침들에 상기 게이트패드, 소스패드 및 드레인패드가 긁히는 현상을 방지할 수 있게 되어 테스트를 안정적으로 실시할 수 있으며, 테스트의 신뢰성을 향상시킬 수 있는 효과가 있다.

### (57) 청구의 범위

#### 청구항 1.

비 전도성 몸체와; 상기 비 전도성 몸체를 관통하여 삽입되는 복수의 전도성 지지체들과; 상기 복수의 전도성 지지체들의 일측 단부에 각각 구비되는 탐침들과; 상기 복수의 전도성 지지체들의 타측 단부와 신호측정장비를 전기적으로 연결시키는 커넥터를 구비하여 구성되는 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

#### 청구항 2.

제 1 항에 있어서, 상기 탐침들은 테스트 대상 소자들의 단자 구성에 대응하는 갯수가 구비된 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

**청구항 3.**

제 2 항에 있어서, 상기 테스트 대상 소자들은 트랜지스터들인 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

**청구항 4.**

제 1 항에 있어서, 상기 탐침들은 4개가 구비되고, 트랜지스터의 게이트전극, 소스전극 및 드레인전극에 대응되는 3개가 사용되는 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

**청구항 5.**

제 1 항에 있어서, 상기 탐침들은 트랜지스터의 게이트전극, 소스전극 및 드레인전극에 대응되는 3개가 구비된 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

**청구항 6.**

제1모기판의 더미영역에 형성되며, 각각 게이트전극, 소스전극 및 드레인전극이 구비된 적어도 하나의 테스트용 박막 트랜지스터와; 상기 테스트용 박막 트랜지스터의 게이트전극, 소스전극 및 드레인전극과 각각 전기적으로 연결되는 게이트패드, 소스패드 및 드레인패드와; 상기 게이트패드, 소스패드 및 드레인패드에 개별적으로 전기신호를 인가하는 탐침들과; 상기 탐침들을 개별적으로 지지하는 전도성 지지체들과; 상기 전도성 지지체들을 고정시키는 비전도성 몸체와; 상기 전도성 지지체들과 신호측정장비를 전기적으로 연결시키는 커넥터를 구비하여 구성되는 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

**청구항 7.**

제 6 항에 있어서, 상기 테스트용 박막 트랜지스터들은 다양한 채널폭 및 채널길이를 갖는 것을 특징으로 하는 액정 표시 장치의 테스트 모듈.

**청구항 8.**

제 6 항에 있어서, 상기 제1모기판에는 복수의 박막 트랜지스터 어레이 기판들이 형성된 것을 특징으로 하는 액정 표시장 치의 테스트 모듈.

**청구항 9.**

제 8 항에 있어서, 상기 복수의 박막 트랜지스터 어레이 기판들에는 다양한 채널폭 및 채널길이를 갖는 복수의 박막 트랜지스터들이 형성된 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

**청구항 10.**

제 9 항에 있어서, 상기 다양한 채널폭 및 채널길이를 갖는 복수의 박막 트랜지스터들 중에 제1채널폭 및 제1채널길이를 갖는 박막 트랜지스터는 제1모기판의 더미영역에 구비되는 제1채널폭 및 제1채널길이를 갖는 복수의 테스트용 박막 트랜지스터들과 대응되는 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

**청구항 11.**

제 6 항에 있어서, 상기 테스트용 박막 트랜지스터의 게이트전극, 소스전극 및 드레인전극은 연장배선을 통해 상기 게이트패드, 소스패드 및 드레인패드와 전기적으로 연결되는 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

**청구항 12.**

제 11 항에 있어서, 상기 연장배선은 상기 테스트용 박막 트랜지스터를 형성하기 위한 액티브층을 적용하여 형성된 것을 특징으로 하는 액정 표시장치의 테스트 모듈.

### 도면

도면1

도면2

도면3

도면4

|                |                                  |         |            |

|----------------|----------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器的测试模块                       |         |            |

| 公开(公告)号        | <a href="#">KR1020050038216A</a> | 公开(公告)日 | 2005-04-27 |

| 申请号            | KR1020030073452                  | 申请日     | 2003-10-21 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                         |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                        |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                        |         |            |

| [标]发明人         | PARK CHANIL                      |         |            |

| 发明人            | PARK,CHANIL                      |         |            |

| IPC分类号         | G02F1/13                         |         |            |

| 代理人(译)         | PARK , JANG WON                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>        |         |            |

#### 摘要(译)

本发明涉及一种液晶显示装置的测试模块，其中设置在探针一端的导电支撑通过非导电体插入，从而驱动测试模块，使得非导电体连接到栅极焊盘，源极焊盘和漏极焊盘当探针与栅极焊盘，源极焊盘和漏极焊盘对准时，对准可缩短对准时间，最大限度地降低探针断裂的风险，并防止探针上的栅极焊盘，源极焊盘和漏极焊盘刮伤这是可以的。 4