(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0036340

(43) 공개일자 2008년04월28일

(51) Int. Cl.

G02F 1/1343 (2006.01)

(21) 출원번호 10-2006-0102819

(22) 출원일자 2006년 10월 23일

심사청구일자 **없음**

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매향동 416

(72) 발명자

— 1 —

서울특별시 강남구 역삼1동 621-23번지

이계현

충남 천안시 불당동 대원칸타빌아파트 608동 302호

오

9월권

# 윤여전

충청남도 아산시 냉정면 명암리 삼성크리스탈타운

청옥동 906호

(74) 대리인

팬코리아특허법인

전체 청구항 수 : 총 9 항

(54) 액정 표시 장치

### (57) 요약

본 액정 표시 장치는 절연 기판, 절연 기판 위에 형성되어 있는 제1 신호선, 제1 신호선과 절연되어 교차하고 있는 제2 신호선, 제1 신호선과 제2 신호선이 교차하여 정의하는 각 화소 영역마다 형성되어 있는 제1 화소 전극, 화소 영역마다 형성되어 있으며 제1 화소 전극에 용량성으로 결합되어 있는 제2 화소 전극, 제1 신호선, 제2 신호선 및 제1 화소 전극에 3단자가 각각 연결되어 있는 제1 박막 트랜지스터, 제1 신호선, 제2 화소 전극, 그리고 제2 신호선과 절연 교차하고 있으며 유지 전압이 인가되는 제3 신호선에 3단자가 각각 연결되어 있는 제2 박막 트랜지스터, 제1 절연 기판과 대향하고 있는 제2 절연 기판, 그리고 제2 절연 기판 위에 형성되어 있으며 공통 전압이 인가되며 상기 제3 신호선과 전기적으로 분리되어 있는 공통 전극을 포함하며, 제1 박막 트랜지스터와 제2 박막 트랜지스터는 상호 이웃하는 서로 다른 제1 신호선에 각각 연결되어 있다. 이에 의해 측면 시인성이 우수하면서도 잔상이나 플리커(flicker) 현상을 방지하여 표시 성능이 향상된 액정 표시 장치가 제공된다.

대표도 - 도1

## 특허청구의 범위

### 청구항 1

절연 기판,

상기 절연 기판 위에 형성되어 있는 제1 신호선,

상기 제1 신호선과 절연되어 교차하고 있는 제2 신호선,

상기 제1 신호선과 상기 제2 신호선이 교차하여 정의하는 각 화소 영역마다 형성되어 있는 제1 화소 전극,

상기 화소 영역마다 형성되어 있으며 상기 제1 화소 전극에 용량성으로 결합되어 있는 제2 화소 전극,

상기 제1 신호선, 상기 제2 신호선 및 제1 화소 전극에 3단자가 각각 연결되어 있는 제1 박막 트랜지스터,

제1 신호선, 상기 제2 화소 전극, 그리고 상기 제2 신호선과 절연 교차하고 있으며 유지 전압이 인가되는 제3 신호선에 3단자가 각각 연결되어 있는 제2 박막 트랜지스터,

상기 제1 절연 기판과 대향하고 있는 제2 절연 기판, 그리고

상기 제2 절연 기판 위에 형성되어 있으며 공통 전압이 인가되며 상기 제3 신호선과 전기적으로 분리되어 있는 공통 전극

을 포함하며,

상기 제1 박막 트랜지스터와 상기 제2 박막 트랜지스터는 상호 이웃하는 서로 다른 제1 신호선에 각각 연결되어 있는 액정 표시 장치.

### 청구항 2

제1항에서,

상기 제1 화소 전극과 상기 제2 화소 전극 중의 적어도 하나는 도메인 분할 수단을 가지는 액정 표시 장치.

### 청구항 3

제1항에서,

상기 제1 화소 전극과 연결되어 있고, 상기 제2 화소 전극과 절연 상태로 중첩하고 있는 결합 전극을 더 포함하는 액정 표시 장치.

### 청구항 4

제3항에서,

상기 결합 전극은 상기 제1 박막 트랜지스터의 3단자 중 드레인 전극으로부터 연장되어 있는 액정 표시 장치.

### 청구항 5

제3항에서,

상기 제1 신호선과 상기 제2 신호선 사이에 형성되어 있는 게이트 절연막과 상기 제2 신호선과 상기 제1 및 제2 화소 전극 사이에 형성되어 있는 보호막을 더 포함하고,

상기 결합 전극은 상기 보호막에 형성되어 있는 접촉 구멍을 통하여 상기 제1 화소 전극과 연결되어 있는 액정 표시 장치.

### 청구항 6

제3항에서,

상기 제1 신호선, 상기 결합 전극 및 상기 제2 화소 전극에 3단자가 각각 연결되어 있는 제3 박막 트랜지스터를 더 포함하는 액정 표시 장치.

**청구항 7**

제6항에서,

상기 제3 박막 트랜지스터는 상기 제2 박막 트랜지스터와 동일한 화소 영역 내에 형성되어 있으며,

상기 제2 박막 트랜지스터와 상기 제3 박막 트랜지스터는 동일한 제1 신호선에 연결되어 있는 액정 표시 장치.

**청구항 8**

제1항에서,

상기 제3 신호선에 인가되는 상기 유지 전압은 상기 공통 전극에 인가되는 상기 공통 전압보다 킥백 전압만큼 높은 액정 표시 장치

**청구항 9**

제1항에서,

상기 킥백 전압은 0.1V 내지 1V인 액정 표시 장치.

**명세서****발명의 상세한 설명****발명의 목적****발명이 속하는 기술 및 그 분야의 종래기술**

<20> 본 발명은 액정 표시 장치에 관한 것으로서, 보다 상세하게는 SPVA(super-PVA) 모드의 액정 표시 장치에 관한 것이다.

<21> 액정 표시 장치는 일반적으로 공통 전극과 색필터(color filter) 등이 형성되어 있는 상부 표시판과 박막 트랜지스터와 화소 전극 등이 형성되어 있는 하부 표시판 사이에 액정 물질을 주입해 놓고 화소 전극과 공통 전극에 서로 다른 전압을 인가함으로써 전계를 형성하여 액정 문자들의 배열을 변경시키고, 이를 통해 빛의 투과율을 조절함으로써 화상을 표현하는 장치이다.

<22> PVA(patterned vertically aligned) 모드는 액정 표시 장치가 갖는 문제점 중 하나인 시야각을 개선하기 위한 모드로서, VA모드 중 화소 전극과 공통 전극에 각각 절개 패턴을 형성한 것을 가리킨다. 이를 절개 패턴으로 인하여 형성되는 프린지 필드(fringe field)를 이용하여 액정 문자들이 눕는 방향을 조절함으로써 시야각이 향상된다.

<23> 그러나 PVA 모드는 액정이 수직 거동하므로 정면과 측면에서 관찰할 때 액정 문자를 통과하는 광의 위상 지연(retardation) 값의 차이가 시야각에 따라 크게 변한다. 이로 인해 측면에서 낮은 계조의 휘도가 급격히 상승하여 대비비(contrast ratio) 저하를 수반한 시인성 저하를 유발시키는 문제가 있다. 이를 개선하기 위하여 화소 전극을 데이터 전압이 직접 인가되는 제1 화소 전극과 제2 화소 전극과 분리되어 전기적으로 플로팅(floating)되어 있는 제2화소 전극으로 나누는 SPVA (super-PVA) 모드가 개발되었다.

<24> 그러나 SPVA 모드는 제 2 화소 전극이 항상 전기적으로 플로팅되어 있기 때문에 외부적인 요인으로 인하여 제2 화소 전극(190b)에 비정상적인 전하(정전기 등)가 유입되면 빠져나갈 통로가 없어 계속 잔류하면서 유효 구동 전압을 왜곡시키는 문제점이 있다. 유효 구동 전압이 달라지면 원하는 화상을 표시하기 어렵게 되고 잔상이나 플리커(flicker)와 같은 불량이 발생하게 된다.

**발명이 이루고자 하는 기술적 과제**

<25> 따라서, 본 발명이 이루고자 하는 기술적 과제는 측면 시인성이 우수하면서도 잔상이나 플리커(flicker) 현상을 방지하여 표시 성능이 향상된 액정 표시 장치를 제공하는 것이다.

**발명의 구성 및 작용**

- <26> 이러한 과제 해결을 위해 본 발명의 한 실시예에 따른 액정 표시 장치는 절연 기판, 상기 절연 기판 위에 형성되어 있는 제1 신호선, 상기 제1 신호선과 절연되어 교차하고 있는 제2 신호선, 상기 제1 신호선과 상기 제2 신호선이 교차하여 정의하는 각 화소 영역마다 형성되어 있는 제1 화소 전극, 상기 화소 영역마다 형성되어 있으며 상기 제1 화소 전극에 용량성으로 결합되어 있는 제2 화소 전극, 상기 제1 신호선, 상기 제2 신호선 및 제1 화소 전극에 3단자가 각각 연결되어 있는 제1 박막 트랜지스터, 제1 신호선, 상기 제2 화소 전극, 그리고 상기 제2 신호선과 절연 교차하고 있으며 유지 전압이 인가되는 제3 신호선에 3단자가 각각 연결되어 있는 제2 박막 트랜지스터, 상기 제1 절연 기판과 대향하고 있는 제2 절연 기판, 그리고

- <27> 상기 제2 절연 기판 위에 형성되어 있으며 공통 전압이 인가되며 상기 제3 신호선과 전기적으로 분리되어 있는 공통 전극을 포함하며, 상기 제1 박막 트랜지스터와 상기 제2 박막 트랜지스터는 상호 이웃하는 서로 다른 제1 신호선에 각각 연결되어 있다.

- <28> 상기 제1 화소 전극과 상기 제2 화소 전극 중의 적어도 하나는 도메인 분할 수단을 가질 수 있다.

- <29> 상기 제1 화소 전극과 연결되어 있고, 상기 제2 화소 전극과 절연 상태로 중첩하고 있는 결합 전극을 더 포함할 수 있다.

- <30> 상기 결합 전극은 상기 제1 박막 트랜지스터의 3단자 중 드레인 전극으로부터 연장될 수 있다.

- <31> 상기 제1 신호선과 상기 제2 신호선 사이에 형성되어 있는 게이트 절연막과 상기 제2 신호선과 상기 제1 및 제2 화소 전극 사이에 형성되어 있는 보호막을 더 포함하고, 상기 결합 전극은 상기 보호막에 형성되어 있는 접촉 구멍을 통하여 상기 제1 화소 전극과 연결되어 있을 수 있다.

- <32> 상기 제1 신호선, 상기 결합 전극 및 상기 제2 화소 전극에 3단자가 각각 연결되어 있는 제3 박막 트랜지스터를 더 포함할 수 있다.

- <33> 상기 제3 박막 트랜지스터는 상기 제2 박막 트랜지스터와 동일한 화소 영역 내에 형성되어 있으며, 상기 제2 박막 트랜지스터와 상기 제3 박막 트랜지스터는 동일한 제1 신호선에 연결되어 있을 수 있다.

- <34> 상기 제3 신호선에 인가되는 상기 유지 전압은 상기 공통 전극에 인가되는 상기 공통 전압보다 킥백 전압만큼 높을 수 있다.

- <35> 상기 킥백 전압은 0.1V 내지 1V일 수 있다.

- <36> 이하에서는 첨부한 도면을 참고로 하여 본 발명의 실시예에 대하여 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 상세히 설명한다. 그러나 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명하는 실시예에 한정되지 않는다.

- <37> 도면에서 여러 층 및 영역을 명확하게 표현하기 위하여 두께를 확대하여 나타내었다. 명세서 전체를 통하여 유사한 부분에 대해서는 동일한 도면 부호를 붙였다. 층, 막, 영역, 판 등의 부분이 다른 부분 "위에" 있다고 할 때, 이는 다른 부분 "바로 위에" 있는 경우뿐 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다. 반대로 어떤 부분이 다른 부분 "바로 위에" 있다고 할 때에는 중간에 다른 부분이 없는 것을 뜻한다.

- <38> 그러면 첨부한 도면을 참고로 하여 본 발명의 실시예에 따른 액정 표시 장치에 대하여 설명한다.

- <39> 먼저 본 발명의 한 실시예에 따른 액정 표시 장치를 도 1 내지 도 5를 참조하여 설명한다.

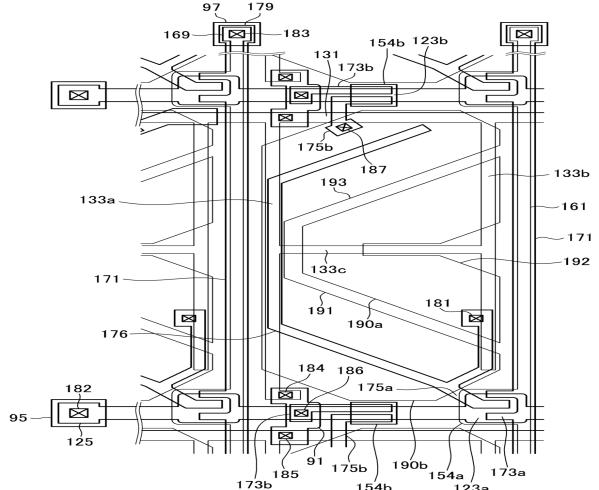

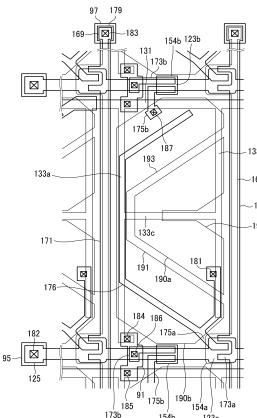

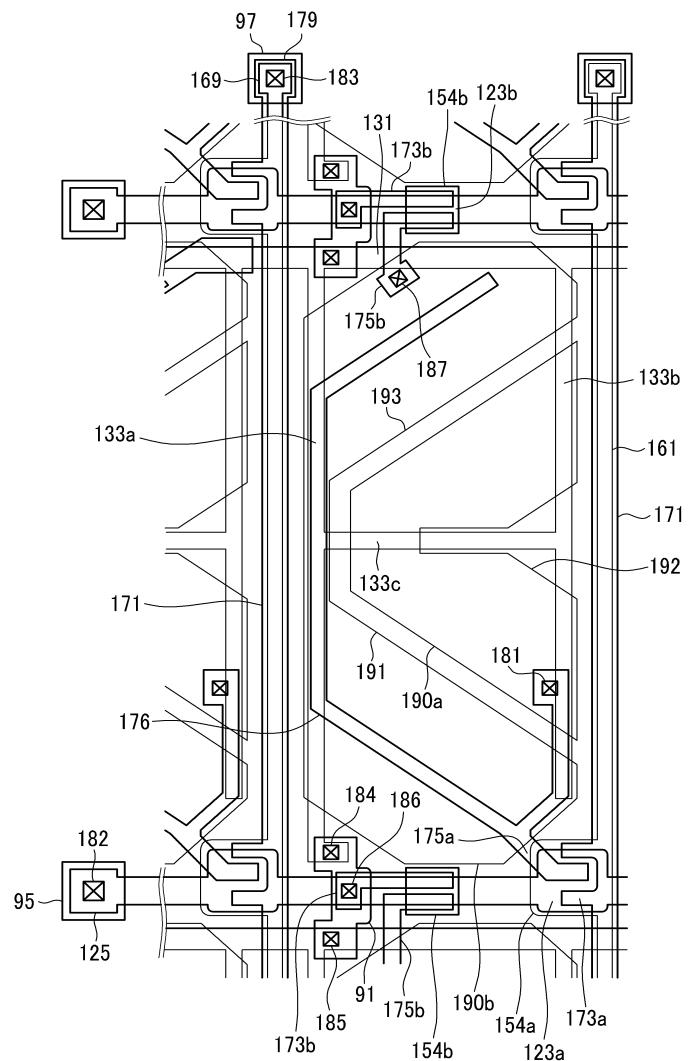

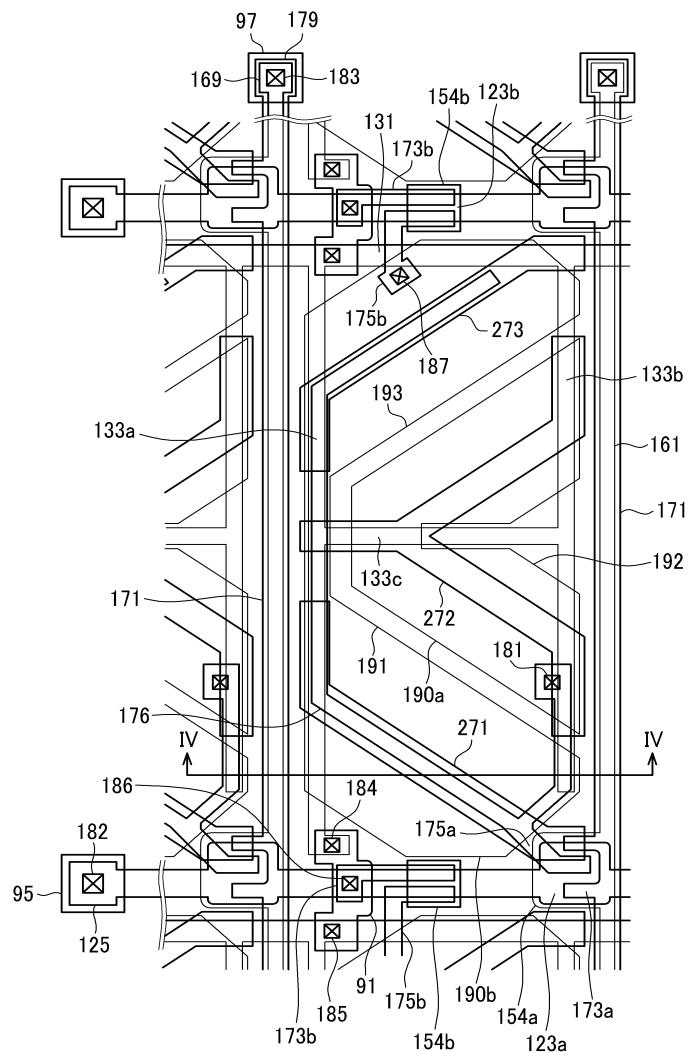

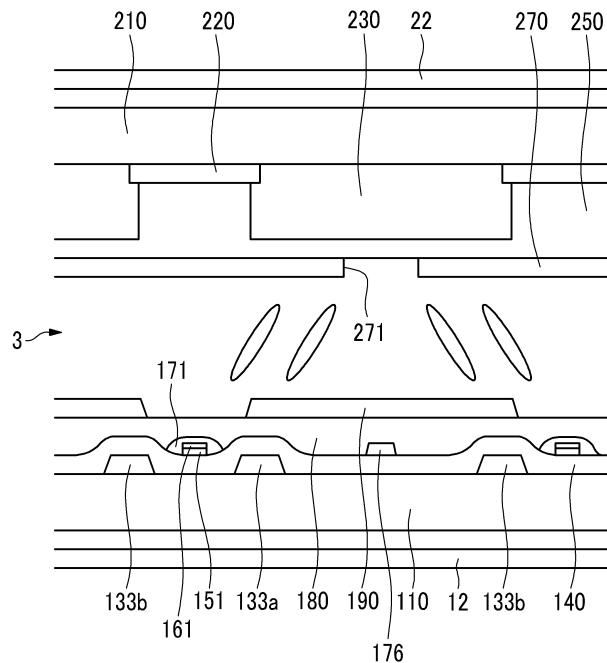

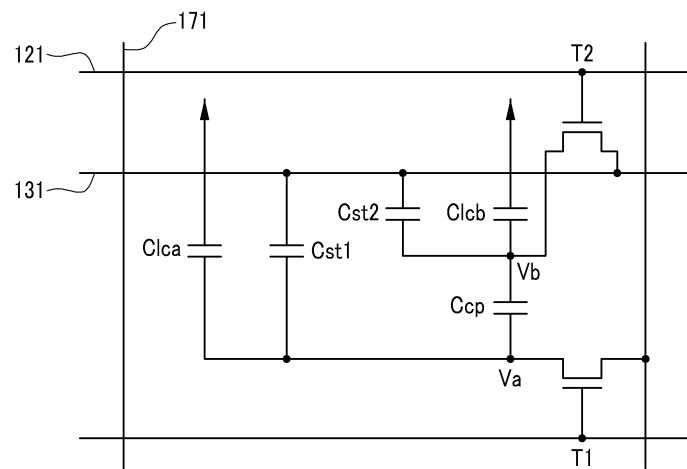

- <40> 도 1은 본 발명의 한 실시예에 따른 액정 표시 장치용 박막 트랜지스터 표시판의 배치도이고, 도 2는 본 발명의 한 실시예에 따른 액정 표시 장치용 색필터 표시판의 배치도이고, 도 3은 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이고, 도 4는 도 3의 IV-IV선을 따라 자른 단면도이고, 도 5는 본 발명의 한 실시예에 따른 액정 표시 장치의 회로도이다.

- <41> 액정 표시 장치는 하부 표시판과 이와 마주보고 있는 상부 표시판 및 하부 표시판과 상부 표시판 사이에 주입되어 표시판에 수직으로 배향되어 있는 액정 분자를 포함하는 액정층(3)으로 이루어진다.

- <42> 먼저, 액정 표시 장치의 하부 표시판은 다음과 같은 구성을 가진다.

- <43> 유리 등의 투명한 절연 물질로 이루어진 절연 기판(110) 위에 ITO(indium tin oxide)나 IZO(indium zinc oxide) 등의 투명한 도전 물질로 이루어져 있는 제1 및 제2 화소 전극(190a, 190b)이 형성되어 있다. 이중 제1 화소 전극(190a)은 제1 박막 트랜지스터의 드레인 전극(175a)에 연결되어 화상 신호 전압을 인가 받는다.

제2 화소 전극(190b)은 제1 화소 전극(190a)과 연결되어 있는 결합 전극(176)과 중첩함으로써 제1 화소 전극(190a)과 전자기적으로 결합(용량성 결합)되어 있고, 제2 박막 트랜지스터의 드레인 전극(175b)에 연결되어 기준 전압을 인가 받는다. 여기서 기준 전압은 공통 전압과 크기가 동일한 전압이다.

- <44> 이 때, 제1 박막 트랜지스터의 게이트 전극(123a)과 소스 전극(173a)은 주사 신호를 전달하는 본단 게이트선(121)과 화상 신호를 전달하는 데이터선(171)에 각각 연결되어 주사 신호에 따라 제1 화소 전극(190a)에 인가되는 화상 신호를 온(on) 오프(off)한다.

- <45> 제2 박막 트랜지스터의 게이트 전극(123b)과 소스 전극(173b)은 전단 게이트선(121)과 유지 전극선 연결 다리(91)에 각각 연결되어 전단 게이트선(121)에 인가되는 주사 신호에 따라 제2 화소 전극(190b)을 공통 전압과 크기가 동일한 전압인 기준 전압으로 리프레시한다.

- <46> 제2 박막 트랜지스터는 전단 게이트선(121)과 중첩하는 섬형 반도체(154b)와 그 위의 저항성 접촉층(도시하지 않음)을 포함하며, 제2 박막 트랜지스터의 소스 전극(173b)은 보호막(180)을 관통하는 접촉 구멍(186)를 통하여 유지 전극선 연결 다리(91)와 연결되어 있고, 제2 박막 트랜지스터의 드레인 전극(175b)은 보호막(180)을 관통하는 접촉 구멍(187)를 통하여 제2 화소 전극(190b)과 연결되어 있다.

- <47> 제1 화소 전극(190a)은 절개부(192)를 가진다. 또, 절연 기판(110)의 아래 면에는 하부 편광판(12)이 부착되어 있다. 여기서, 제1 및 제2 화소 전극(190a, 190b)은 반사형 액정 표시 장치인 경우 투명한 물질로 이루어지지 않을 수도 있고, 이 경우에는 하부 편광판(12)도 불필요하게 된다.

- <48> 다음, 상부 표시판의 구성은 다음과 같다.

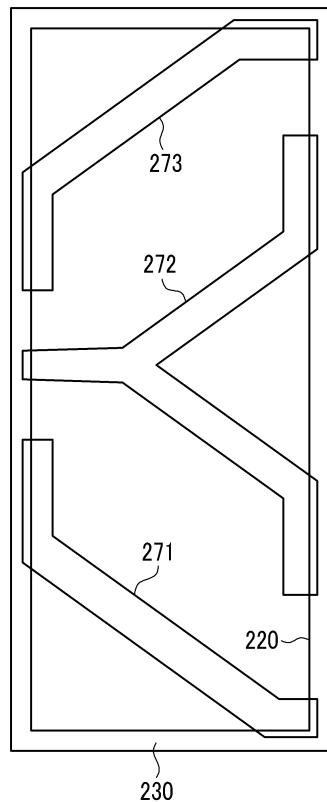

- <49> 역시 유리 등의 투명한 절연 물질로 이루어진 절연 기판(210)의 아래 면에 빛샘을 방지하기 위한 블랙 매트릭스(220)와 적, 녹, 청의 색필터(230) 및 ITO 또는 IZO 등의 투명한 도전 물질로 이루어져 있는 공통 전극(270)이 형성되어 있다. 여기서, 공통 전극(270)에는 절개부(271, 272, 273)가 형성되어 있다. 블랙 매트릭스(220)는 화소 영역의 둘레 부분뿐만 아니라 공통 전극(270)의 절개부(271, 272, 273)와 중첩하는 부분에도 형성할 수 있다. 이는 절개부(271, 272, 273)로 인해 발생하는 빛샘을 방지하기 위함이다.

- <50> 본 발명의 한 실시예에 따른 액정 표시 장치에 대하여 좀 더 상세히 한다.

- <51> 하부의 절연 기판(110) 위에 주로 가로 방향으로 뻗어 있는 복수의 게이트선(121)과 유지 전극선(131)이 형성되어 있다.

- <52> 게이트선(121)은 복수의 부분이 아래 위로 확장되어 게이트 전극(123a, 123b)과 외부 회로와의 연결을 위하여 넓게 확장되어 있는 끝부분(125)를 포함한다.

- <53> 각 유지 전극선(131)은 그로부터 뻗어 나온 여러 별의 유지 전극(storage electrode)(133a, 133b, 133c)을 포함한다. 한 별의 유지 전극(133a, 133b, 133c) 중 두 개의 유지 전극(133a, 133b)은 세로 방향으로 뻗어나오며 가로 방향으로 뻗은 다른 하나의 유지 전극(133c)에 의하여 서로 연결되어 있다. 이 때, 각 유지 전극선(131)은 2개 이상의 가로선으로 이루어질 수도 있다.

- <54> 게이트선(121) 및 유지 전극선(131)은 Al, Al 합금, Ag, Ag 합금, Cr, Ti, Ta, Mo 등의 금속 따위로 만들어진다. 도 4에 나타낸 바와 같이, 본 실시예의 게이트선(121) 및 유지 전극선(131)은 단일층으로 이루어지지만, 물리 화학적 특성이 우수한 Cr, Mo, Ti, Ta 등의 금속층과 비저항이 작은 Al 계열 또는 Ag 계열의 금속층을 포함하는 이중층으로 이루어질 수도 있다. 이외에도 여러 다양한 금속 또는 도전체로 게이트선(121)과 유지 전극선(131)을 만들 수 있다.

- <55> 게이트선(121)과 유지 전극선(131)이 측면은 경사져 있으며 수평면에 대한 경사각은 30~80도인 것이 바람직하다.

- <56> 게이트선(121)과 유지 전극선(131)의 위에는 질화규소(SiNx) 등으로 이루어진 게이트 절연막(140)이 형성되어 있다.

- <57> 게이트 절연막(140) 위에는 복수의 데이터선(171)을 비롯하여 제1 박막 트랜지스터의 드레인 전극(drain electrode)(175a), 복수의 결합 전극(176) 및 제2 박막 트랜지스터의 소스 전극(source electrode)(173b) 및 드레인 전극(175b)이 형성되어 있다.

- <58> 각 데이터선(171)은 주로 세로 방향으로 뻗어 있으며, 각 드레인 전극(175a)을 향하여 복수의 분지를 내어 제1

박막 트랜지스터의 소스 전극(source electrode)(173a)을 이룬다. 결합 전극(176)은 드레인 전극(175a)과 연결되어 있고, V자 모양으로 굴절되어 있다.

<59> 데이터선(171), 드레인 전극(175a, 175b), 결합 전극(176)도 게이트선(121)과 마찬가지로 크롬과 알루미늄 등의 물질로 만들어지며, 단일층 또는 다중층으로 이루어질 수 있다.

<60> 데이터선(171) 및 드레인 전극(175a)의 아래에는 데이터선(171)을 따라 주로 세로로 길게 뻗은 복수의 선형 반도체(151)가 형성되어 있다. 비정질 규소 따위로 이루어진 각 선형 반도체(151)는 각 게이트 전극(123a)을 향하여 뻗어 나와 제1 박막 트랜지스터의 채널부를 이루는 돌출부(154a)를 포함한다.

<61> 한편, 게이트선(121)과 소스 전극(173b) 및 드레인 전극(175b) 사이에는 선형 반도체(151)와 동일한 물질로 이루어져 있으며, 제2 박막 트랜지스터의 채널부를 이루는 섬형 반도체(154b)가 형성되어 있다.

<62> 반도체(151, 154a, 154b)와 데이터선(171) 및 드레인 전극(175a, 175b) 사이에는 둘 사이의 접촉 저항을 감소시키기 위한 복수의 저항성 접촉 부재(ohmic contact)(161)가 형성되어 있다. 저항성 접촉 부재(161)는 실리사이드나 n형 불순물이 고농도로 도핑된 비정질 규소 따위로 만들어진다.

<63> 데이터선(171), 드레인 전극(175a, 175b) 위에는 질화 규소 등의 무기 절연물이나 수지 등의 유기 절연물로 이루어진 보호막(180)이 형성되어 있다.

<64> 보호막(180)에는 제1 박막 트랜지스터의 드레인 전극(175a)의 적어도 일부와 데이터선(171)의 끝 부분(179), 제2 박막 트랜지스터의 소스 전극(173b) 및 드레인 전극(175b)의 적어도 일부를 각각 노출시키는 복수의 접촉 구멍(181, 183, 186, 187)이 구비되어 있다. 그리고 게이트선(121)의 끝 부분(125)과 유지 전극선(131)의 일부를 각각 드러내는 복수의 접촉 구멍(182, 184, 185)이 게이트 절연막(140)과 보호막(180)을 관통하고 있다.

<65> 보호막(180) 위에는 복수의 화소 전극(190a, 190b)을 비롯하여 복수의 접촉 보조 부재(contact assistant)(95, 97) 및 복수의 유지 전극선 연결 다리(storage bridge)(91)가 형성되어 있다. 화소 전극(190a, 190b), 접촉 보조 부재(95, 97) 및 유지 전극선 연결 다리(91)는 ITO(indium tin oxide)나 IZO(indium zinc oxide) 등과 같은 투명 도전체나 알루미늄(Al)과 같은 광 반사 특성이 우수한 불투명 도전체 따위로 만들어진다.

<66> 화소 전극(190a, 190b)은 제1 화소 전극(190a)과 제2 화소 전극(190b)을 포함하며, 제1 화소 전극(190a)은 접촉 구멍(181)을 통하여 제1 박막 트랜지스터의 드레인 전극(175a)과 연결되어 있고, 제2 화소 전극(190b)은 결합 전극(176)과 중첩하고 있다. 따라서, 제2 화소 전극(190b)은 제1 화소 전극(190a)에 전자기적으로 결합(용량성 결합)되어 있다.

<67> 제1 화소 전극(190a)과 제2 화소 전극(190b)을 나누는 경계는 게이트선(121)에 대하여 45도를 이루는 부분(191, 193)과 수직을 이루는 부분으로 구분되고, 이중 45도를 이루는 두 부분(191, 193)이 수직을 이루는 부분에 비하여 길이가 길다. 또, 45도를 이루는 두 부분(191, 193)은 서로 수직을 이루고 있다.

<68> 제1 화소 전극(190a)은 절개부(192)를 가지며, 절개부(192)는 제1 화소 전극(190a)의 오른쪽 변에서 왼쪽 변을 향하여 파고 들어간 형태이고, 입구는 넓게 확장되어 있다.

<69> 제1 화소 전극(190a)과 제2 화소 전극(190b)은 각각 게이트선(121)과 데이터선(171)이 교차하여 정의하는 화소 영역을 상하로 이등분하는 선(게이트선과 나란한 선)에 대하여 실질적으로 거울상 대칭을 이루고 있다.

<70> 또, 보호막(180)의 위에는 게이트선(121)을 건너 그 양쪽에 위치하는 두 유지 전극선(131)을 연결하는 유지 전극선 연결 다리(91)가 형성되어 있다. 유지 전극선 연결 다리(91)는 보호막(180)을 관통하는 접촉 구멍(186)를 통하여 제2 박막 트랜지스터의 소스 전극(173a)과 접촉하고 있으며, 보호막(180)과 게이트 절연막(140)을 관통하는 접촉 구멍(184, 185)를 통하여 유지 전극(133a) 및 유지 전극선(131)에 접촉하고 있다.

<71> 유지 전극선 연결 다리(91)는 하부 기판(110) 위의 유지 전극선(131) 전체를 전기적으로 연결하는 역할을 하고 있다. 이러한 유지 전극선(131)은 필요할 경우 게이트선(121)이나 데이터선(171)의 결함을 수리하는데 이용할 수 있다.

<72> 또한 유지 전극선 연결 다리(91)는 유지 전극선(131)으로부터 인가되는 유지 전압을 제2 박막 트랜지스터의 소스 전극(173b)으로 전달한다.

<73> 접촉 보조 부재(95, 97)는 각각 접촉 구멍(182, 183)를 통하여 게이트선의 끝부분(125)과 데이터선의 끝부분(179)에 연결되어 있다.

- <74> 상부의 절연 기판(210)에는 빛이 새는 것을 방지하기 위한 블랙 매트릭스(220)가 형성되어 있다. 블랙 매트릭스(220) 위에는 적, 녹, 청색 색필터(230)가 형성되어 있다.

- <75> 색필터(230)의 위에는 복수 별의 절개부(271, 272, 273)를 가지는 공통 전극(270)이 형성되어 있다. 공통 전극(270)은 ITO 또는 IZO(indium zinc oxide) 등의 투명한 도전체로 형성한다. 공통 전극(270)은 유지 전극선(131)과 전기적으로 분리되어 외부로부터 유지 전압과 다른 별도의 전압을 인가 받는다.

- <76> 공통 전극(270)의 한 별의 절개부(271, 272, 273)는 두 화소 전극(190a, 190b)의 경계 중 게이트선(121)에 대하여 45도를 이루는 부분(191, 193)을 가운데에 끼고 있으며 이와 나란한 사선부와 화소 전극(190)의 변과 중첩되어 있는 단부를 포함하고 있다. 이 때, 단부는 세로 방향 단부와 가로 방향 단부로 분류된다.

- <77> 이상과 같은 구조의 박막 트랜지스터 표시판과 색필터 표시판을 정렬하여 결합하고 그 사이에 액정 물질을 주입하여 수직 배향하면 본 발명의 한 실시예에 따른 액정 표시 장치의 기본 구조가 마련된다.

- <78> 박막 트랜지스터 표시판과 색필터 표시판을 정렬했을 때 공통 전극(270)의 한 별의 절개부(271, 272, 273)는 두 화소 전극(190a, 190b)을 각각 복수의 부영역(subarea)으로 구분하는데, 본 실시예에서는 도 3에 도시한 바와 같이 두 화소 전극(190a, 190b)을 각각 4개의 부영역으로 나눈다. 도 3에서 알 수 있는 바와 같이, 각 부영역은 길쭉하게 형성되어 있어서 폭 방향과 길이 방향이 구별된다.

- <79> 화소 전극(190a, 190b)의 각 부영역과 이에 대응하는 공통 전극(270)의 각 부영역 사이에 있는 액정층(3) 부분을 앞으로는 소영역(sugregion)이라고 하며, 이들 소영역은 전계 인가시 그 내부에 위치하는 액정 분자의 평균 장축 방향에 따라 4개의 종류로 분류되며 앞으로는 이를 도메인(domain)이라고 한다.

- <80> 이러한 구조의 액정 표시 장치에서 제1 화소 전극(190a)은 제1 박막 트랜지스터를 통하여 화상 신호 전압을 인가 받음에 반하여 제2 화소 전극(190b)은 결합 전극(176)과의 용량성 결합에 의하여 전압이 변동하게 되므로 제2 화소 전극(190b)의 전압은 제1 화소 전극(190a)의 전압에 비하여 절대값이 항상 낮게 된다. 이와 같이, 하나의 화소 영역 내에서 전압이 다른 두 화소 전극을 배치하면 두 화소 전극이 서로 보상하여 감마 곡선의 왜곡을 줄일 수 있어 시인성을 향상할 수 있다.

- <81> 그러면 제2 화소 전극(190b)의 전압이 제1 화소 전극(190a)의 전압보다 낮게 유지되는 이유를 도 5를 참고로 하여 설명한다.

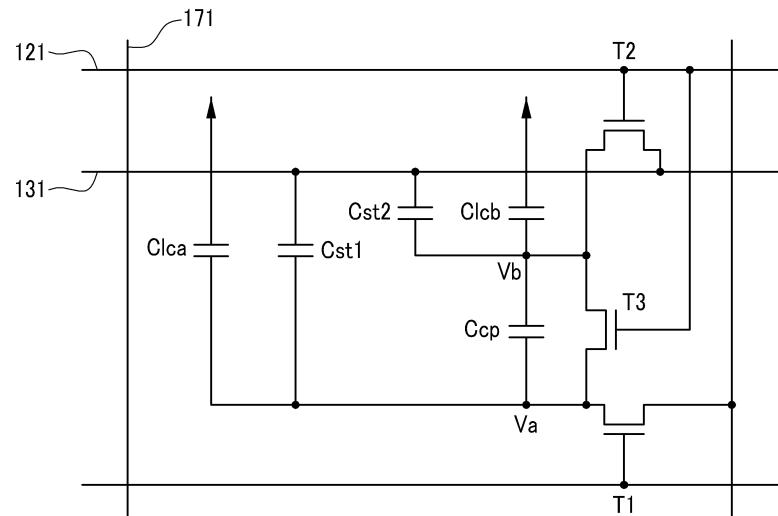

- <82> 도 5에서 Clca는 제1 화소 전극(190a)과 공통 전극(270) 사이에서 형성되는 액정 용량을 나타내고, Cst1은 제1 화소 전극(190a)과 유지 전극선(131) 사이에서 형성되는 유지 용량을 나타낸다. Clcb는 제2 화소 전극(190b)과 공통 전극(270) 사이에서 형성되는 액정 용량을 나타내고, Cst2는 제2 화소 전극(190b)과 유지 전극선(131) 사이에서 형성되는 유지 용량을 나타낸다. 또한 Ccp는 제1 화소 전극(190a)과 제2 화소 전극(190b) 사이에서 형성되는 결합 용량을 나타낸다.

- <83> 공통 전극(270)의 공통 전압에 대한 제1 화소 전극(190a)의 화소 전압을 Va라 하고, 제2 화소 전극(190b)의 화소 전압을 Vb라 하면, 전압 분배 법칙에 의하여,

- $$Vb=Va \times [Ccp / (Ccp + Clcb)]$$

- <84>이고,  $Ccp / (Ccp + Clcb)$ 는 항상 1보다 작으므로 Vb는 Va에 비하여 항상 작다.

- <85> 한편, Ccp를 조절함으로써 Va에 대한 Vb의 비율을 조정할 수 있다. Ccp의 조절은 결합 전극(176)과 제2 화소 전극(190b)의 중첩 면적과 거리를 조정함으로써 가능하다. 중첩 면적은 결합 전극(176)의 폭을 변화시킴으로써 용이하게 조정할 수 있고, 거리는 결합 전극(176)의 형성 위치를 변화시킴으로써 조정할 수 있다. 즉, 본 발명의 실시예에서는 결합 전극(176)을 데이터선(171)과 같은 충에 형성하였으나, 게이트선(121)과 같은 충에 형성함으로써 결합 전극(176)과 제2 화소 전극(190b) 사이의 거리를 증가시킬 수 있다. 또한 결합 전극(176)의 배치는 다양하게 변형할 수 있다.

- <86> 종래의 액정 표시 장치의 경우 제2 화소 전극(190b)이 항상 부유되어 있어서, 외부적인 요인으로 인하여 제2 화소 전극(190b)에 비정상적인 전하(정전기 등)가 유입되면 빠져나갈 통로가 없기 때문에 계속 잔류하면서 유효 구동 전압을 왜곡시키는 문제점이 있다. 유효 구동 전압이 달라지면 원하는 화상을 표시하기 어렵게 되고 잔상 또는 플리커(flicker)와 같은 불량이 발생하게 된다.

- <87> 그러나 본 발명의 한 실시예에 따른 액정 표시 장치의 구성에 따르면 이러한 문제점이 해결되는데 이를 도 5,

도 6a, 도 6, 도 7a 및 도 7b를 참조하여 설명한다.

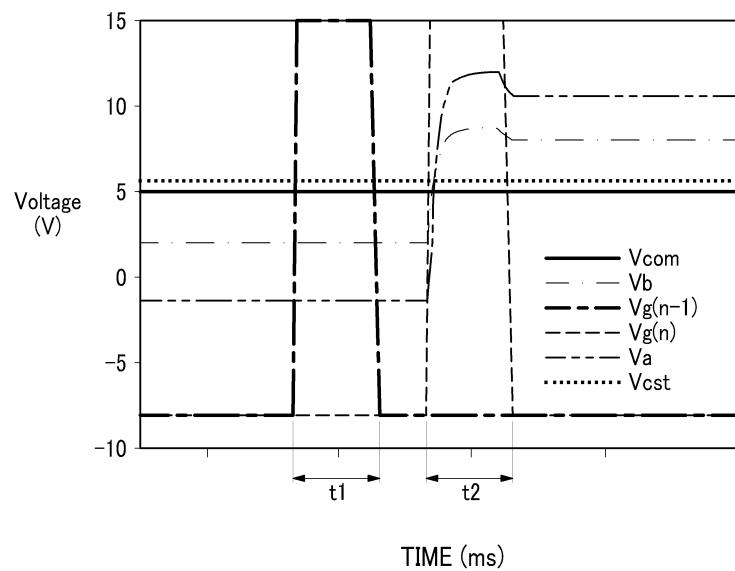

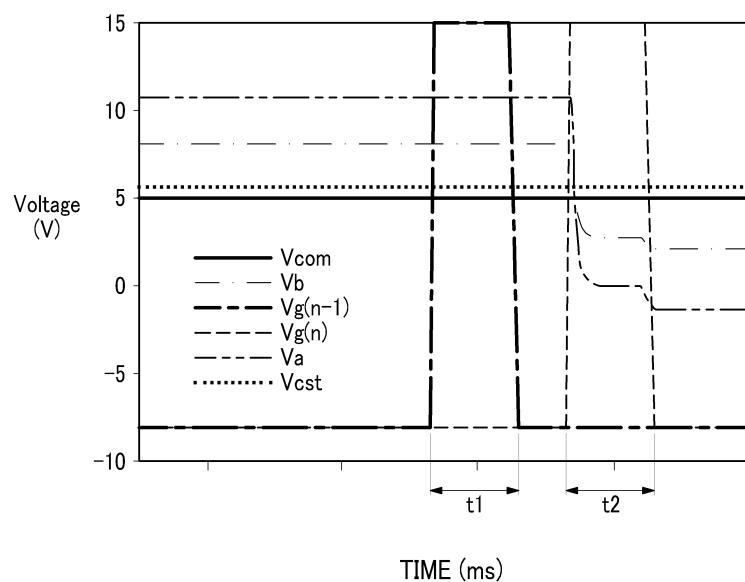

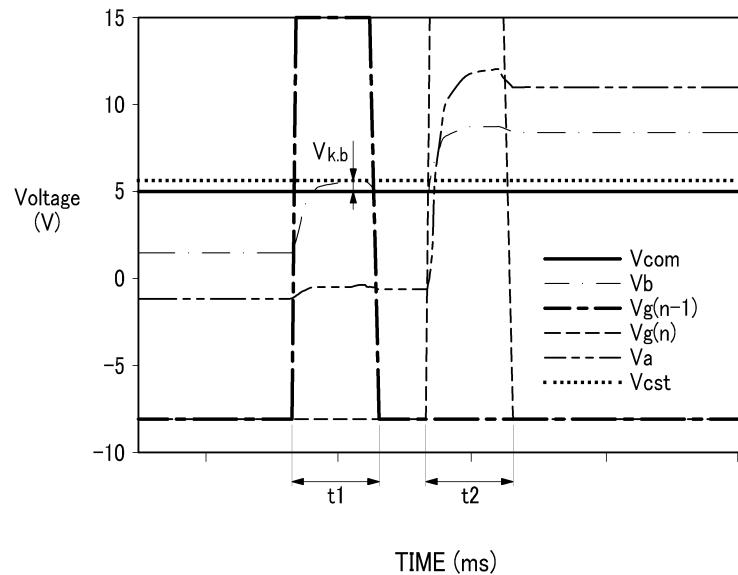

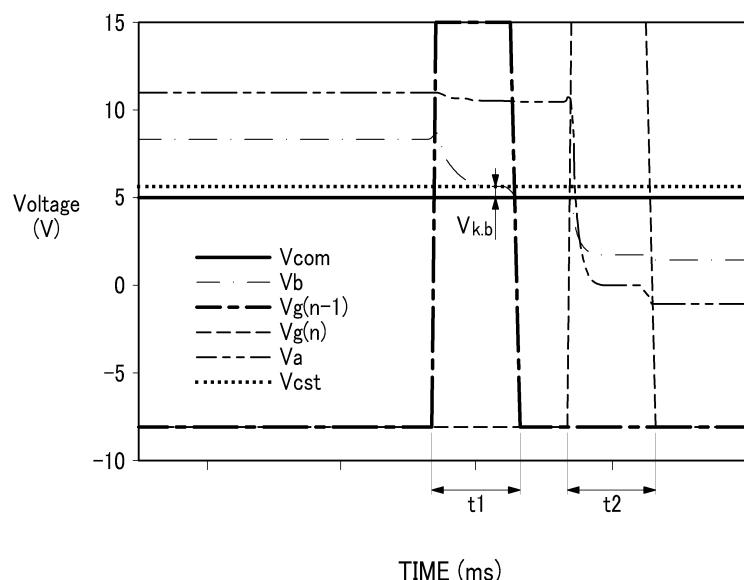

<89> 도 6a 및 도 6b는 종래의 액정 표시 장치의 각 동작 전압을 나타낸 도면이고, 도 7a 및 도 7b는 본 발명의 한 실시예에 따른 액정 표시 장치의 각 동작 전압을 나타낸 도면이다.

<90> 도 5를 보면, 본단 게이트선(121)을 통해 온 신호가 인가되어 제1 박막 트랜지스터(T1)에 연결되어 있는 제1 화소 전극(190a)에 화상 신호인 제1 화소 전압(Va)이 충전되기 이전에 전단 게이트선(121)에 연결되어 있는 제2 박막 트랜지스터(T2)를 통해 제2 화소 전극(190b)은 유지 전극선(131)으로부터 인가된 유지 전압에서 킥백 전압을 뺀 기준 전압으로 리프레시(refresh)된다.

<91> 이렇게 되면 비정상적인 전하가 제2 화소 전극(190b)에 유입되더라도 제2 화소 전극(190b)이 매 프레임마다 공통 전극과 크기가 동일한 기준 전압으로 리프레시되기 때문에 유효 구동 전압의 왜곡 현상을 방지할 수 있다. 따라서 본 발명의 한 실시예에 따른 액정 표시 장치에 의하면 시인성이 우수하면서도 잔상 또는 플리커(flicker)와 같은 불량을 방지할 수 있어 화상 신호를 왜곡하는 일이 없게 되어 표시 성능이 향상되게 된다.

<92> 즉 본 발명에 따른 액정 표시 장치는 도 7a 및 도 7b에 도시한 바와 같이 도 6a 및 도 6b에 도시한 종래의 액정 표시 장치와 달리 본단 게이트선(121)을 통해 소정 시간(t2) 동안 제1 박막 트랜지스터(T1)의 게이트 전극에 온 신호인 소정 크기의 게이트 전압(Vg(n))이 인가되어 화상 신호인 제1 화소 전압(Va)이 제1 화소 전극(190a)에 충전되기 이전에 전단 게이트 선(121)을 통해 소정 시간(t1) 동안 제2 박막 트랜지스터(T2)의 게이트 전극에 온 신호인 소정 크기의 게이트 전압(Vg(n-1))이 인가된다. 소정 시간(t1) 동안 제2 박막 트랜지스터(T2)의 게이트 전극에 온 신호가 인가되면 유지 전극선(131)과 연결된 소스 전극(173b)을 통해 유지 전압(Vcst)이 제2 화소 전극(190b)에 인가된다.

<93> 그리고 게이트 전극에 소정 시간(t1) 인가된 온 신호가 오프 신호로 바뀌면 유지 전압(Vcst)은 킥백 전압(Vk.b)만큼 감소하게 되고 이에 따라 제2 화소 전극(190b)은 유지 전극선(131)으로부터 인가된 유지 전압(Vcst)에서 킥백 전압(Vk.b)을 뺀 기준 전압으로 리프레시(refresh)되어 유효 구동 전압의 왜곡 현상이 방지되게 된다.

<94> 기준 전압은 공통 전압(Vcom)과 크기가 동일한 전압이며, 또한 유지 전압(Vcst)에서 킥백 전압(Vk.b)을 뺀 값과 동일한 전압이다. 즉 유지 전압(Vcst)은 킥백 전압(Vk.b)을 고려하여 공통 전압(Vcom)보다 높다. 따라서 본 실시예에서는 유지 전극선(131)과 공통 전극(270)을 전기적으로 분리하여 크기가 서로 다른 전압을 각각 유지 전극선(131)과 공통 전극(270)에 인가하게 되는 것이다.

<95> 여기서 킥백 전압의 크기는 0.1V 내지 1V이며 본 실시예에서는 0.4V를 사용하였다.

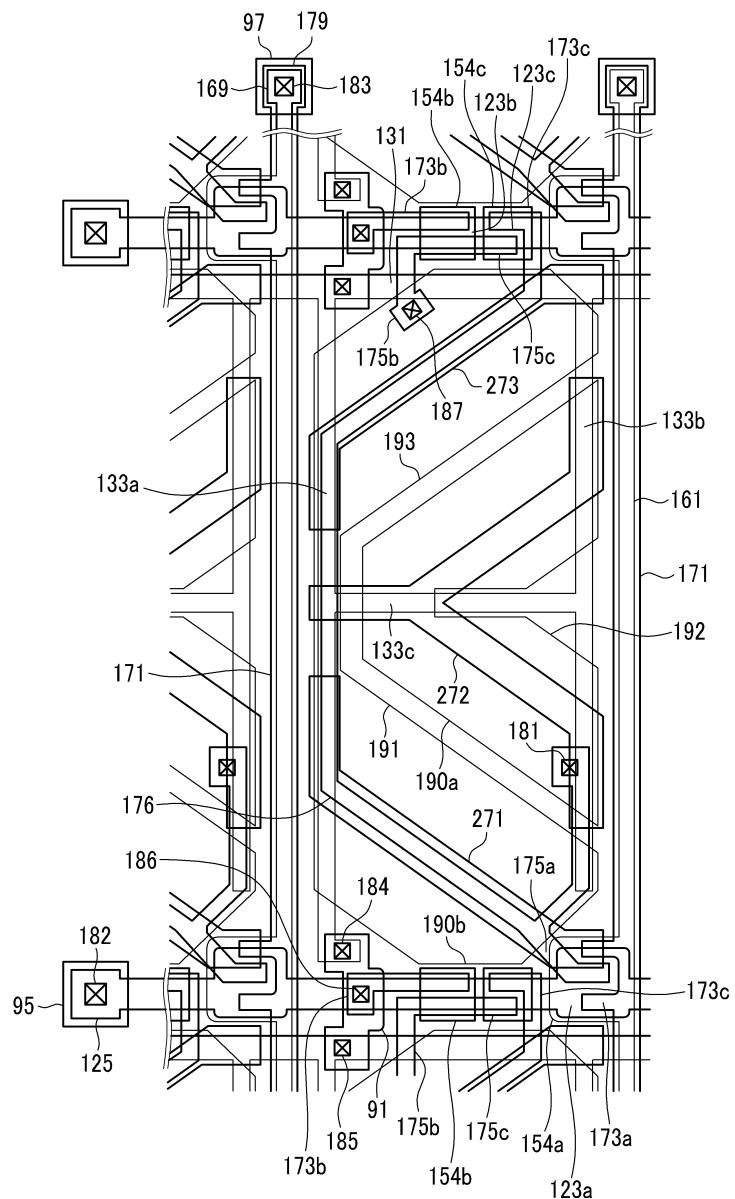

<96> 이하에서는 본 발명의 다른 실시예에 따른 액정 표시 장치를 도 8 및 도 9를 참조하여 설명한다.

<97> 도 8은 본 발명의 다른 실시예에 따른 액정 표시 장치의 배치도이고, 도 9는 도 8에 도시한 액정 표시 장치의 회로도이다.

<98> 본 발명의 다른 실시예에 따른 액정 표시 장치는 도 1의 액정 표시 장치와 달리 제1 화소 전극(190a)과 제2 화소 전극(190b)를 연결하는 제3 박막 트랜지스터(T3)가 더 형성되어 있다. 제3 박막 트랜지스터(T3)의 게이트 전극은 제2 박막 트랜지스터(T2)와 마찬가지로 전단 게이트선(121)에 연결되어 있다. 따라서, 본단 게이트선(121)에 온 신호가 인가되어 화상 신호가 제1 화소 전극(190a)에 충전되기 이전에 제1 화소 전극(190a) 및 제2 화소 전극(190b)은 모두 기준 전압으로 리프레시(refresh)된다.

<99> 이렇게 되면 비정상적인 전하가 제2 화소 전극(190b)에 유입되더라도 제1 및 제2 화소 전극(190a, 190b)이 매 프레임마다 기준 전압으로 리프레시되기 때문에 화상 신호를 왜곡하는 일이 없게 된다. 또한, 제2 화소 전극의 화소 전압(Vb)이 이전 프레임에 인가된 화소 전압과는 무관하게 되어 이전 프레임의 화상이 다음 프레임의 화상에 영향을 미치는 것을 방지할 수 있다.

<100> 도 8을 참조하여 본 발명의 다른 실시예에 따른 액정 표시 장치의 구성을 자세히 살펴보면, 역시 하부 표시판과 이와 마주보고 있는 상부 표시판 및 하부 표시판과 상부 표시판 사이에 주입되어 표시판에 수직으로 배향되어 있는 액정 분자를 포함하는 액정층으로 이루어진다.

<101> 여기서 하부 표시판은 다음과 같은 구성을 가진다.

<102> 유리 등의 투명한 절연 물질로 이루어진 절연 기판(110) 위에 ITO(indium tin oxide)나 IZO(indium zinc

oxide) 등의 투명한 도전 물질로 이루어져 있는 제1 및 제2 화소 전극(190b, 190a)이 형성되어 있다.

<103> 이종 제1 화소 전극(190a)은 제1 박막 트랜지스터의 드레인 전극(175a)에 연결되어 화상 신호 전압을 인가 받는다.

<104> 제2 화소 전극(190b)은 제1 화소 전극(190a)과 연결되어 있는 결합 전극(176)과 중첩함으로써 제1 화소 전극(190a)과 전자기적으로 결합(용량성 결합)되어 있고, 제2 박막 트랜지스터의 드레인 전극(175b)에 연결되어 기준 전압을 인가 받는다.

<105> 또, 결합 전극(176)은 제3 박막 트랜지스터의 소스 전극(173c)과 연결되어 있고, 제3 박막 트랜지스터의 드레인 전극(175c)은 제2 박막 트랜지스터의 드레인 전극(175b)과 연결되어 있어서, 결합 전극(176)에도 제2 및 제3 박막 트랜지스터를 통하여 기준 전위가 인가된다. 결합 전극(176)은 제1 화소 전극(190a)과 연결되어 있으므로 제1 화소 전극(190a)에도 제2 화소 전극(190b)과 함께 기준 전압이 인가된다.

<106> 제1 박막 트랜지스터의 게이트 전극(123a)과 소스 전극(173a)은 주사 신호를 전달하는 본단 게이트선(121)과 화상 신호를 전달하는 데이터선(171)에 각각 연결되어 주사 신호에 따라 제1 화소 전극(190a)에 인가되는 화상 신호를 온(on)오프(off)한다.

<107> 제2 박막 트랜지스터의 게이트 전극(123b)과 소스 전극(173b)은 전단 게이트선(121)과 유지 전극선 연결 다리(91)에 각각 연결되어 있어서 전단 게이트선(121)에 인가되는 주사 신호에 따라 제2 화소 전극(190b)은 기준 전압으로 리프레시된다.

<108> 제3 박막 트랜지스터의 게이트 전극(123c)도 제2 박막 트랜지스터와 마찬가지로 전단 게이트선(121)에 연결되어 있어서 제2 화소 전극(190b)이 기준 전위로 리프레시될 때 제1 화소 전극(190a)도 함께 기준 전압으로 리프레시된다.

<109> 제2 박막 트랜지스터는 전단 게이트선(121)과 중첩하는 섬형 반도체(154b)와 그 위의 저항성 접촉층(도시하지 않음)을 포함하며, 제2 박막 트랜지스터의 소스 전극(173b)은 보호막(180)을 관통하는 접촉 구멍(186)를 통하여 유지 전극선 연결 다리(91)와 연결되어 있고, 제2 박막 트랜지스터의 드레인 전극(175b)은 보호막(180)을 관통하는 접촉 구멍(187)을 통하여 제2 화소 전극(190b)과 연결되어 있다.

<110> 제3 박막 트랜지스터도 전단 게이트선(121)과 중첩하는 섬형 반도체(154c)와 그 위의 저항성 접촉층(도시하지 않음)을 포함하며, 제3 박막 트랜지스터의 드레인 전극(175c)은 제2 박막 트랜지스터의 드레인 전극(175b)이 연장되어 있는 형태이고, 제3 박막 트랜지스터의 소스 전극(173c)은 결합 전극(176)이 연장되어 있는 형태이다.

<111> 본 발명의 다른 실시예에 따른 액정 표시 장치에 의해서도 도1의 액정 표시 장치와 동일한 효과를 얻을 수 있다.

<112> 이상에서 본 발명의 바람직한 실시예에 대하여 상세하게 설명하였지만 본 발명의 권리범위는 이에 한정되는 것은 아니고 다음의 청구범위에서 정의하고 있는 본 발명의 기본 개념을 이용한 당업자의 여러 변형 및 개량 형태 또한 본 발명의 권리범위에 속하는 것이다. 특히, 화소 전극과 공통 전극에 형성하는 절개부의 배치는 여러 다양한 변형이 있을 수 있다.

### 발명의 효과

<113> 이상과 같이 본 발명에 의하면, 측면 시인성이 우수하면서도 잔상이나 플리커(flicker) 현상을 방지하여 표시 성능이 향상된 액정 표시 장치가 제공된다.

### 도면의 간단한 설명

<1> 도 1은 본 발명의 한 실시예에 따른 액정 표시 장치용 박막 트랜지스터 표시판의 배치도이고,

<2> 도 2는 본 발명의 한 실시예에 따른 액정 표시 장치용 색필터 표시판의 배치도이고,

<3> 도 3은 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이고,

<4> 도 4는 도 3의 IV-IV선을 따라 자른 단면도이고,

<5> 도 5는 본 발명의 한 실시예에 따른 액정 표시 장치의 회로도이고,

- <6> 도 6a 및 도 6b는 종래의 액정 표시 장치의 각 동작 전압을 나타낸 도면이고,

<7> 도 7a 및 도 7b는 본 발명의 한 실시예에 따른 액정 표시 장치의 각 동작 전압을 나타낸 도면이고,

<8> 도 8은 본 발명의 다른 실시예에 따른 액정 표시 장치의 배치도이고,

<9> 도 9는 도 8에 도시한 액정 표시 장치의 회로도이다.

## &lt;10&gt; &lt;도면의 주요 부분에 대한 부호의 설명&gt;

|      |                         |               |

|------|-------------------------|---------------|

| <11> | 110, 210: 절연기판          | 121: 게이트선     |

| <12> | 123: 게이트 전극             | 131: 유지 전극선   |

| <13> | 133a, 133b, 133c: 유지 전극 | 151, 154: 반도체 |

| <14> | 171: 데이터선               | 173: 소스 전극    |

| <15> | 175: 드레인 전극             | 176: 결합 전극    |

| <16> | 180: 보호막                | 190: 화소 전극    |

| <17> | 191, 192, 193: 절개부      | 220: 블랙 매트릭스  |

| <18> | 230: 색필터                | 270: 공통 전극    |

| <19> | 271, 272, 273: 절개부      |               |

## 도면

## 도면1

도면2

## 도면3

도면4

도면5

도면6a

도면6b

도면7a

도면7b

## 도면8

도면9

|                |                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                            |         |            |

| 公开(公告)号        | <a href="#">KR1020080036340A</a>                                                                 | 公开(公告)日 | 2008-04-28 |

| 申请号            | KR1020060102819                                                                                  | 申请日     | 2006-10-23 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                         |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                                                         |         |            |

| [标]发明人         | KIM KYUNG WOOK<br>김경욱<br>LEE KYE HUN<br>이계훈<br>YOON YEO GEON<br>윤여건                              |         |            |

| 发明人            | 김경욱<br>이계훈<br>윤여건                                                                                |         |            |

| IPC分类号         | G02F1/1343                                                                                       |         |            |

| CPC分类号         | G02F1/134309 G02F1/136213 G02F1/13624 G02F1/136286 G02F1/1368 G02F2001/133397<br>G02F2001/134354 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                        |         |            |

### 摘要(译)

存在于液晶显示装置为，形成在绝缘基板上的第一信号线，在绝缘基板由所述第二信号线，第一信号线和第二信号线交叉交叉限定从第一信号线绝缘的每个像素区域中形成的第一像素电极，形成在每个区域中的像素，并且所述第一薄膜，其是在第一像素被耦合到具有电容，该第一信号线，分别连接到所述第二信号线与所述第一像素电极的第三端子电极的第二像素电极第二薄膜晶体管，其中三个端子连接到与第一信号线，第二像素电极和第二信号线交叉并且施加维持电压的第三信号线，2，绝缘基板，和形成在第二绝缘基板上并与施加有共电压的第三信号线电隔离的公共电极，晶体管和所述第二薄膜晶体管分别连接到为彼此相邻的不同的第一信号线。由此，提供一种液晶显示装置，其侧视能力优异，并且防止了残像和闪烁现象，并且具有改善的显示性能。