# (19)대한민국특허청(KR) (12) 공개특허공보(A)

(51) 。Int. Cl. *G02F 1/136* (2006.01)

(11) 공개번호

10-2006-0036241

(43) 공개일자

2006년04월28일

(21) 출원번호10-2004-0085323(22) 출원일자2004년10월25일

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 이청

경기도 용인시 구성면 상하리 쌍용아파트 315동 702호

(74) 대리인 유미특허법인

심사청구: 없음

## (54) 박막 트랜지스터 표시판 및 그 제조 방법

#### 요약

본 발명에 따른 박막 트랜지스터 표시판은 절연 기판, 절연 기판 위에 형성되어 있으며 소스 영역, 드레인 영역 및 채널 영역을 포함하는 다결정 규소층, 다결정 규소층 위에 형성되어 있는 게이트 절연막, 게이트 절연막 위에 형성되며 있으며 채널 영역과 일부분 중첩하는 게이트 전극을 포함하는 게이트선, 게이트선 위에 형성되어 있는 층간 절연막, 층간 절연막 위에 형성되며 소스 영역과 연결되는 소스 전극을 포함하는 데이터선, 층간 절연막 위에 형성되며 드레인 영역과 연결되는 드레인 전극, 데이터선 및 드레인 전극 위에 형성되어 있는 보호막, 보호막 위에 형성되어 있으며 드레인 전극과 연결되어 있는 화소 전극을 포함하고, 데이터선 중 게이트선과 중첩되는 게이트 중첩부는 굴곡되어 있는 것이 바람직하다. 따라서, 본 발명에 따른 박막 트랜지스터 표시판은 데이터선 중 게이트선 또는 유지 전극선과 각각 중첩되는 게이트 중첩부 또는 유지 중첩부를 ㄷ 형상으로 굴곡되도록 형성함으로써 제조 공정이나 외부 환경 변화에 따른 열수축 및 열팽창에 의해 데이터선이 스트레스를 받는 것을 완충시키고, 단차부가 오픈되는 것을 방지한다는 장점이 있다.

#### 대표도

도 1

#### 색인어

액정표시장치, 스트레스, 단차부, 게이트중첩부, 유지중첩부

### 명세서

#### 도면의 간단한 설명

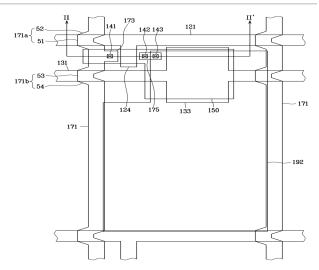

도 1은 본 발명의 일 실시예에 따른 박막 트랜지스터 표시판의 배치도이고,

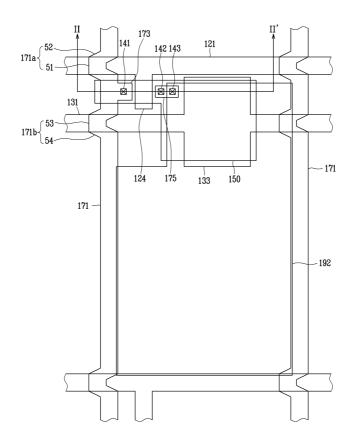

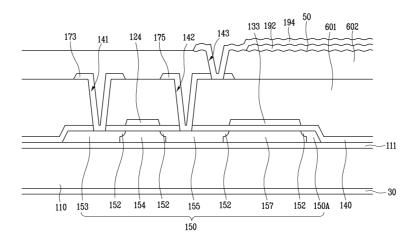

도 2는 도 1의 박막 트랜지스터 표시판을 II-II' 선을 따라 잘라 도시한 단면도이고,

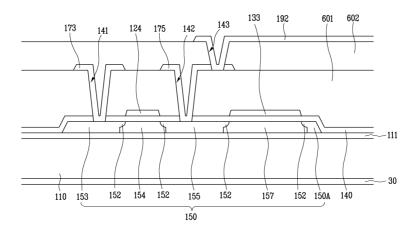

도 3은 본 발명의 다른 실시예에 따른 박막 트랜지스터 표시판의 배치도이고.

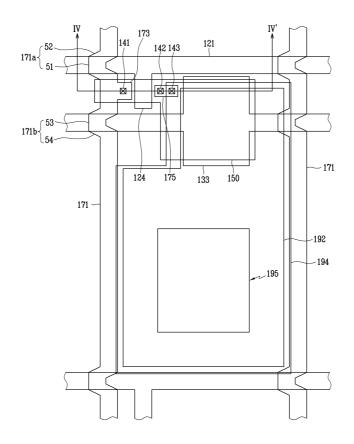

도 4는 도 3의 박막 트랜지스터 표시판을 IV-IV' 선을 따라 잘라 도시한 단면도이다.

<도면의 주요부분에 대한 부호의 설명>

110: 기판 121: 게이트선

124: 게이트 전극 140: 게이트 절연막

150: 반도체층 171: 데이터선

173: 소스 전극 175: 드레인 전극

171a: 게이트 중첩부 171b: 유지 중첩부

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 박막 트랜지스터 표시판에 관한 것이다.

액정 표시 장치는 현재 가장 널리 사용되고 있는 평판 표시 장치 중 하나로서, 전계 생성 전극이 형성되어 있는 두 장의 표 시판과 그 사이에 삽입되어 있는 액정층으로 이루어져, 전극에 전압을 인가하여 액정층의 액정 분자들을 재배열시킴으로 써 액정층을 통과하는 빛의 투과율을 조절하는 표시 장치이다.

액정 표시 장치 중에서도 현재 주로 사용되는 것은 전계 생성 전극이 두 표시판에 각각 구비되어 있는 것이다. 이중에서도 한 표시판에는 복수의 화소 전극이 행렬의 형태로 배열되어 있고 다른 표시판에는 하나의 공통 전극이 표시판 전면을 덮고 있는 구조의 액정 표시 장치가 주류이다. 이 액정 표시 장치에서의 화상의 표시는 각 화소 전극에 별도의 전압을 인가함으로써 이루어진다. 이를 위해서 화소 전극에 인가되는 전압을 스위칭하기 위한 삼단자 소자인 박막 트랜지스터(Thin Film Transistor, TFT)를 각 화소 전극에 연결하고 이 박막 트랜지스터를 제어하기 위한 신호를 전달하는 게이트선과 화소 전극에 인가될 전압을 전달하는 데이터선을 표시판에 설치한다.

이러한 박막 트랜지스터는 비정질 규소층(Amorphous Silicon, a-Si) 또는 다결정 규소층(Polycrystalline Silicon, poly-Si)을 반도체층으로 가지며, 게이트 전극과 반도체층의 상대적인 위치에 따라 탑 게이트(top gate) 방식과 바텀 게이트 (bottom gate) 방식으로 나눌 수 있다. 다결정 규소 박막 트랜지스터 표시판의 경우, 게이트 전극이 반도체층의 상부에 위치하는 탑 게이트 방식이 주로 이용된다. 탑 게이트 방식에서는 다결정 규소층이 절연 기판 위에 형성되고, 다결정 규소층위에 게이트 절연막이 형성되며, 게이트 절연막 위에 게이트선 및 유지 전극선이 형성된다.

다결정 규소를 이용한 박막 트랜지스터 표시판은 종래의 비정질 규소를 이용한 박막 트랜지스터 표시판에 비해 높은 전하이동도(mobility)를 가지고 있어서 액정 패널 내부에 구동 회로가 내장된 액정 표시 장치(Chip On Glass, COG)의 구현이가능하며, 높은 해상도의 고화질 제품의 개발이 가능하다.

그러나, 이러한 액정 패널 내부에 구동 회로가 내장된 액정 표시 장치(COG) 등의 직접도가 높아지면서 금속 배선의 폭이 얇아지고, 두께가 증가하게 되었다. 따라서, 열수축 및 열팽창에 의해 금속 배선이 받는 스트레스(stress)는 증가하게 되었다. 또한, 금속 배선간 커플링 용량(coupling capacitance)이 액정 표시 장치에 민감한 영향을 미치면서 점차로 게이트선과 데이터선간의 중첩 등 금속 배선간 중첩되는 면적을 줄이게 되었다. 따라서, 이러한 금속 배선의 폭 감소에 따라 신뢰성문제 및 공정 마진의 문제가 발생하여 수율 저하로까지 이어지게 된다는 문제점이 있다.

#### 발명이 이루고자 하는 기술적 과제

본 발명의 기술적 과제는 데이터선 중 게이트 중첩부 또는 유지 중첩부가 열수축 및 열팽창 시 스트레스를 받는 것을 완충 시키고, 단차부가 오픈되는 것을 방지하는 박막 트랜지스터 표시판을 제공하는 것이다.

#### 발명의 구성 및 작용

본 발명에 따른 박막 트랜지스터 표시판은 절연 기판, 상기 절연 기판 위에 형성되어 있으며 소스 영역, 드레인 영역 및 채널 영역을 포함하는 다결정 규소층, 상기 다결정 규소층 위에 형성되어 있는 게이트 절연막, 상기 게이트 절연막 위에 형성되며 있으며 상기 채널 영역과 일부분 중첩하는 게이트 전극을 포함하는 게이트선, 상기 게이트선 위에 형성되어 있는 층간 절연막, 상기 충간 절연막 위에 형성되며 상기 소스 영역과 연결되는 소스 전극을 포함하는 데이터선, 상기 층간 절연막위에 형성되며 상기 드레인 영역과 연결되는 드레인 전극, 상기 데이터선 및 상기 드레인 전극 위에 형성되어 있는 보호막, 상기 보호막위에 형성되어 있으며 상기 드레인 전극과 연결되어 있는 화소 전극을 포함하고, 상기 데이터선 중 상기 게이트선과 중첩되는 게이트 중첩부는 굴곡되어 있는 것이 바람직하다.

또한, 상기 데이터선 중 상기 게이트선과 중첩되는 게이트 중첩부는 ㄷ 형상으로 굴곡되어 있는 것이 바람직하다.

또한, 상기 데이터선 중 상기 게이트선과 중첩되는 게이트 중첩부는 사선부 및 직선부로 이루어지며, 상기 사선부는 상기 게이트선의 측선과 중첩되어 그 단면이 경사지게 형성되어 있는 것이 바람직하다.

또한, 상기 게이트선과 동일한 층에 형성되어 있으며, 상기 게이트선과 평행한 유지 전극선을 더 포함하고 있는 것이 바람 직하다.

또한, 상기 데이터선 중 상기 유지 전극선과 중첩되는 유지 중첩부는 굴곡되어 있는 것이 바람직하다.

또한, 상기 데이터선 중 상기 유지 전극선과 중첩되는 유지 중첩부는 ㄷ 형상으로 굴곡되어 있는 것이 바람직하다.

또한, 상기 데이터선 중 상기 유지 전극선과 중첩되는 유지 중첩부는 사선부 및 직선부로 이루어지며, 상기 사선부는 상기 유지 전극선의 측선과 중첩되어 그 단면이 경사지게 형성되어 있는 것이 바람직하다.

그러면, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 본 발명의 실시예에 대하여 첨부한 도면을 참고로 하여 상세히 설명한다. 그러나 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명 하는 실시예에 한정되지 않는다.

도면에서 여러 층 및 영역을 명확하게 표현하기 위하여 두께를 확대하여 나타내었다. 명세서 전체를 통하여 유사한 부분에 대해서는 동일한 도면 부호를 붙였다. 층, 막, 영역, 판 등의 부분이 다른 부분 "위에" 있다고 할 때, 이는 다른 부분 "바로 위에" 있는 경우뿐 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다. 반대로 어떤 부분이 다른 부분 "바로 위에" 있다고 할 때에는 중간에 다른 부분이 없는 것을 뜻한다.

이제 본 발명의 실시예에 따른 박막 트랜지스터 표시판에 대하여 도면을 참고로 하여 상세하게 설명한다.

먼저, 도 1 및 도 2를 참고로 하여 본 발명의 바람직한 한 실시예에 따른 박막 트랜지스터 표시판에 대하여 상세히 설명한다.

도 1은 본 발명의 일 실시예에 따른 박막 트랜지스터 표시판의 배치도이고, 도 2는 도 1의 박막 트랜지스터 표시판을 II-II' 선을 따라 잘라 도시한 단면도이다.

도 1 및 도 2에 도시한 바와 같이, 투명한 절연 기판(10) 위에 산화 규소(SiO $_2$ ) 또는 질화 규소(SiNx)로 이루어진 차단층 (111)이 형성되어 있다. 이때 사용되는 투명한 절연 기판(110)으로는 유리, 석영 또는 사파이어등을 사용할 수 있으며, 차단층(111)은 산화 규소(SiO $_2$ ) 또는 질화 규소(SiNx)를 증착하여 형성한다.

차단층(111) 위에는 소스 영역(153), 드레인 영역(155), 채널 영역(154) 및 저농도 도핑 영역(lightly doped drain)(152) 이 포함된 다결정 규소층(150)이 형성되어 있다.

여기서, 차단층(111)은 절연 기판(110)과 다결정 규소층(30)간의 접착성을 향상시키며, 절연 기판(110) 내부에 존재하는 도전성 불순물이 다결정 규소층(150)으로 확산하는 것을 방지하는 역할을 한다.

이러한 다결정 규소층(150)은 차단층(111)의 상면에 화학 기상 증착(Chemical Vapor Deposition, CVD) 방법으로 비정 질 규소층을 형성하고, 비정질 규소층(150)을 ELA(Eximer Laser Annealing) 결정화 방식 또는 SLS(Sequential Lateral Solidification) 결정화 방식으로 레이저 열처리(laser annealing)함으로써 형성된다.

저농도 도핑 영역(152)은 누설 전류(leakage current)나 편치스루(punch through) 현상이 발생하는 것을 방지한다. 소스 영역(153)과 드레인 영역(155)은 N형 또는 P형 도전형 불순물이 고농도로 도핑되고, 채널 영역(154)에는 불순물이 도핑되지 않는다.

그리고, 다결정 규소층(150) 위에는 게이트 절연막(140)이 형성되어 있다. 그리고 게이트 절연막(140) 위에는 일 방향으로 긴 게이트선(121)이 형성되어 있고, 게이트선(121)의 일부가 연장되어 다결정 규소층(150)의 채널 영역(154)과 중첩되어 있으며, 중첩되는 게이트선(121)의 일부분은 박막 트랜지스터의 게이트 전극(124)으로 사용된다. 게이트선(121)의 한쪽 끝부분(도시하지 않음)은 외부 회로와 연결하기 위해서 게이트선(121) 폭보다 넓게 형성할 수 있다.

또한, 화소의 유지 용량을 증가시키기 위한 유지 전극선(131)이 게이트선(121)과 평행하며, 동일한 물질로 동일한 층에 형성되어 있다. 다결정 규소층(150)과 중첩하는 유지 전극선(131)의 일 부분은 유지 전극(133)이 되며, 유지 전극(133)과 중첩하는 다결정 규소층(150)은 유지 전극 영역(157)이 된다.

게이트선(121) 및 유지 전국선(131)은 비저항(resistivity)이 낮은 은(Ag)이나 은 합금 등 은 계열 금속, 알루미늄(Al)이나 알루미늄 합금 등 알루미늄 계열 금속 따위로 이루어진 도전막을 포함하며, 이러한 도전막에 더하여 다른 물질, 특히 ITO 또는 IZO와의 물리적, 화학적, 전기적 접촉 특성이 좋은 크롬(Cr), 티타늄(Ti), 탄탈륨(Ta), 몰리브덴(Mo) 및 이들의 합금 [보기: 몰리브덴-텅스텐(MoW) 합금] 따위로 이루어진 다른 도전막을 포함하는 다층막 구조를 가질 수도 있다. 하부막과 상부막의 조합의 예로는 크롬(Cr)/알루미늄-네오디뮴(AlNd) 합금을 들 수 있다.

게이트선(121) 및 유지 전극선(131)이 형성되어 있는 게이트 절연막(140) 위에는 층간 절연막(601)이 형성되어 있다. 절 연막(601)은  $\mathrm{SiO}_2/\mathrm{SiN}$ 로 이루어진 이중층으로 형성한다.  $\mathrm{SiO}_2$  단일층보다는  $\mathrm{SiO}_2/\mathrm{SiN}$  이중층으로 형성하면  $\mathrm{SiO}_2$  단일층으로 형성할 때보다 박막 트랜지스터의 신뢰성이 향상된다.

충간 절연막(601)은 소스 영역(153)과 드레인 영역(155)을 각각 노출하는 제1 및 제2 접촉구(141, 142)를 포함하고 있다.

충간 절연막(601) 위에는 게이트선(121)과 교차하여 화소 영역을 정의하는 데이터선(171)이 형성되어 있다. 데이터선 (171)의 일부분 또는 분지형 부분은 제1 접촉구(141)를 통해 소스 영역(153)과 연결되어 있으며 소스 영역(153)과 연결되어 있는 부분은 박막 트랜지스터의 소스 전극(173)으로 사용된다. 데이터선(171)의 한쪽 끝부분은 외부 회로와 연결하기 위해서 데이터선(171) 폭보다 넓게 형성(도시하지 않음)할 수 있다.

그리고 데이터선(171)과 동일한 층에는 소스 전극(173)과 일정거리 떨어져 형성되어 있으며 제2 접촉구(142)를 통해 드레인 영역(155)과 연결되어 있는 드레인 전극(175)이 형성되어 있다.

그리고, 데이터선 중 게이트선(121)과 중첩되는 게이트 중첩부(171a)는 굴곡되어 있다. 데이터선 중 게이트 중첩부(171a)는  $\Box$  형상으로 굴곡되어 있는 것이 바람직하다.

이러한 게이트 중첩부(171a)는 사선부(52) 및 직선부(51)로 이루어지며, 사선부(52)는 게이트선(121)의 측선과 중첩되어 그 단면이 경사지게 형성되어 있다.

이와 같이, 데이터선 중 게이트선(121)과 중첩되는 게이트 중첩부(171a)는 ㄷ 형상으로 굴곡되도록 형성함으로써 제조 공정이나 외부 환경 변화에 따른 열수축 및 열팽창에 의해 데이터선(171)이 스트레스(stress)를 받는 것을 완충시킨다.

또한, 게이트 중첩부(171a)가 ㄷ 형상으로 굴곡되는 경우, 데이터선(171)이 게이트선(121) 위로 올라가며 단차지는 부분 인 사선부(52)가 직선부(51)보다 게이트선(121)과 넓게 중첩함으로써 열수축 및 열팽창 시 단차부가 오픈되는 것을 방지한다는 장점이 있다.

또한, 데이터선 중 유지 전극선(131)과 중첩되는 유지 중첩부(171b)는 굴곡되어 있다. 이러한 유지 중첩부(171b)는 ㄷ 형상으로 굴곡되어 있는 것이 바람직하다.

이러한 유지 중첩부(171b)는 사선부(54) 및 직선부(53)로 이루어지며, 사선부(54)는 유지 전극선(131)의 측선과 중첩되어 그 단면이 경사지게 형성되어 있다.

이와 같이, 데이터선 중 유지 전극선(131)과 중첩되는 유지 중첩부(171b)를 ㄷ 형상으로 굴곡되도록 형성함으로써 제조 공정이나 외부 환경 변화에 따른 열수축 및 열팽창에 의해 데이터선(171)이 스트레스(stress)를 받는 것을 완충시킨다.

또한, 유지 중첩부(171b)가 ㄷ 형상으로 굴곡되는 경우, 데이터선(171)이 유지 전극선(131) 위로 올라가며 단차지는 부분 인 사선부(54)가 직선부(53)보다 유지 전극선(131)과 넓게 중첩함으로써 열수축 및 열팽창 시 단차부가 오픈되는 것을 방지한다는 장점이 있다.

데이터선(171) 및 드레인 전극(175)은 IZO(indium zinc oxide) 또는 ITO(indium tin oxide)와의 물리적, 화학적, 전기적 접촉 특성이 우수한 물질, 이를테면 몰리브덴(Mo), 몰리브덴 합금[보기: 몰리브덴-텅스텐(MoW) 합금] 따위의 몰리브덴 계열의 금속으로 이루어진다. 또한, 데이터선(171) 및 드레인 전극(175) 또한 은 계열 금속 또는 알루미늄 계열 금속 따위로 이루어진 도전막일 수도 있으며, 이러한 도전막에 더하여 크롬(Cr), 티타늄(Ti), 탄탈륨(Ta), 몰리브덴(Mo) 및 이들의 합금 따위로 이루어진 다른 도전막을 포함하는 다층막 구조를 가질 수 있다.

데이터선(171) 및 드레인 전극(175)을 포함하는 충간 절연막(601) 위에 보호막(602)이 유기막 또는 무기막 등으로 형성되어 있다.

이러한 보호막(602)은 드레인 전극(175)을 드러내는 제3 접촉구(143)를 가진다. 그리고 보호막(602) 위에 ITO로 이루어진 화소 전극인 투과 전극(192)이 형성되어 있다.

한편, 본 발명의 일 실시예인 다결정 규소층을 가지는 투과형 액정 표시 장치용 박막 트랜지스터 표시판의 제조 방법에 적용된 다결정 규소층은 다결정 규소층을 가지는 반투과형 액정 표시 장치용 박막 트랜지스터 표시판의 제조 방법에도 적용가능하다.

이하에서 본 발명의 다른 실시예에 따른 다결정 규소층을 가지는 반투과형 액정 표시 장치용 박막 트랜지스터 표시판에 대해 도면을 참고로 하여 상세히 설명한다.

도 3은 본 발명의 다른 실시예에 따른 박막 트랜지스터 표시판의 배치도이고, 도 4는 도 3의 박막 트랜지스터 표시판을 IV-IV' 선을 따라 잘라 도시한 단면도이다.

도 3 및 도 4에 도시한 바와 같이, 투명한 절연 기판(10) 위에 산화 규소(SiO $_2$ ) 또는 질화 규소(SiNx)로 이루어진 차단층 (111)이 형성되어 있다. 차단층(111) 위에는 소스 영역(153), 드레인 영역(155), 채널 영역(154) 및 저농도 도핑 영역 (lightly doped drain)(152)이 포함된 다결정 규소층(150)이 형성되어 있다.

여기서, 차단층(111)은 절연 기판(110)과 다결정 규소층(150)간의 접착성을 향상시키며, 절연 기판(110) 내부에 존재하는 도전성 불순물이 다결정 규소층(150)으로 확산하는 것을 방지하는 역할을 한다.

저농도 도핑 영역(152)은 누설 전류(leakage current)나 편치스루(punch through) 현상이 발생하는 것을 방지한다. 소스 영역(153)과 드레인 영역(155)은 N형 또는 P형 도전형 불순물이 고농도로 도핑되고, 채널 영역(154)에는 불순물이 도핑되지 않는다.

다결정 규소층(150)을 포함하는 기판(110) 위에는 게이트 절연막(140)이 형성되어 있다.

그리고 게이트 절연막(140) 위에는 일 방향으로 긴 게이트선(121)이 형성되어 있고, 게이트선(121)의 일부가 연장되어 다결정 규소층(150)의 채널 영역(154)과 중첩되어 있으며, 중첩되는 게이트선(121)의 일부분은 박막 트랜지스터의 게이트 전극(124)으로 사용된다. 게이트선(121)의 한쪽 끝부분은 외부 회로와 연결하기 위해서 게이트선(121) 폭보다 넓게 형성 (도시하지 않음)할 수 있다.

또한, 화소의 유지 용량을 증가시키기 위한 유지 전극선(131)이 게이트선(121)과 평행하며, 동일한 물질로 동일한 층에 형성되어 있다. 다결정 규소층(150)과 중첩하는 유지 전극선(131)의 일 부분은 유지 전극(133)이 되며, 유지 전극(133)과 중첩하는 다결정 규소층(150)은 유지 전극 영역(157)이 된다.

게이트선(121) 및 유지 전극선(131)은 비저항(resistivity)이 낮은 은(Ag)이나 은 합금 등 은 계열 금속, 알루미늄(Al)이나 알루미늄 합금 등 알루미늄 계열 금속 따위로 이루어진 도전막을 포함하며, 이러한 도전막에 더하여 다른 물질, 특히 ITO 또는 IZO와의 물리적, 화학적, 전기적 접촉 특성이 좋은 크롬(Cr), 티타늄(Ti), 탄탈륨(Ta), 몰리브덴(Mo) 및 이들의 합금 [보기: 몰리브덴-텅스텐(MoW) 합금] 따위로 이루어진 다른 도전막을 포함하는 다층막 구조를 가질 수도 있다. 하부막과 상부막의 조합의 예로는 크롬/알루미늄-네오디뮴(Nd) 합금을 들 수 있다.

게이트선(121) 및 유지 전극선(131)이 형성되어 있는 게이트 절연막(140) 위에는 층간 절연막(601)이 형성되어 있다. 절연막(601)은  $SiO_2/SiN$ 로 이루어진 이중층으로 형성한다.  $SiO_2$  단일층보다는  $SiO_2/SiN$  이중층으로 형성하면  $SiO_2$  단일층으로 형성할 때보다 박막 트랜지스터의 신뢰성이 향상된다.

층간 절연막(601)은 소스 영역(153)과 드레인 영역(155)을 각각 노출하는 제1 및 제2 접촉구(141, 142)를 포함하고 있다.

충간 절연막(601) 위에는 게이트선(121)과 교차하여 화소 영역을 정의하는 데이터선(171)이 형성되어 있다. 데이터선 (171)의 일부분 또는 분지형 부분은 제1 접촉구(141)를 통해 소스 영역(153)과 연결되어 있으며 소스 영역(153)과 연결되어 있는 부분은 박막 트랜지스터의 소스 전극(173)으로 사용된다. 데이터선(171)의 한쪽 끝부분은 외부 회로와 연결하기 위해서 데이터선(171) 폭보다 넓게 형성(도시하지 않음)할 수 있다.

그리고 데이터선(171)과 동일한 층에는 소스 전극(173)과 일정거리 떨어져 형성되어 있으며 제2 접촉구(142)를 통해 드 레인 영역(155)과 연결되어 있는 드레인 전극(175)이 형성되어 있다.

그리고, 데이터선 중 게이트선(121)과 중첩되는 게이트 중첩부(171a)는 굴곡되어 있다. 데이터선 중 게이트 중첩부(171a)는 ㄷ 형상으로 굴곡되어 있는 것이 바람직하다.

이러한 게이트 중첩부(171a)는 사선부(52) 및 직선부(51)로 이루어지며, 사선부(52)는 게이트선(121)의 측선과 중첩되어 그 단면이 경사지게 형성되어 있다.

이와 같이, 데이터선 중 게이트선(121)과 중첩되는 게이트 중첩부(171a)는 ㄷ 형상으로 굴곡되도록 형성함으로써 제조 공 정이나 외부 환경 변화에 따른 열수축 및 열팽창에 의해 데이터선(171)이 스트레스(stress)를 받는 것을 완충시킨다.

또한, 게이트 중첩부(171a)가 ㄷ 형상으로 굴곡되는 경우, 데이터선(171)이 게이트선(121) 위로 올라가며 단차지는 부분인 사선부(52)가 직선부(51)보다 게이트선(121)과 넓게 중첩함으로써 열수축 및 열팽창 시 단차부가 오픈되는 것을 방지한다는 장점이 있다.

또한, 데이터선 중 유지 전극선(131)과 중첩되는 유지 중첩부(171b)는 굴곡되어 있다. 이러한 유지 중첩부(171b)는 ㄷ 형상으로 굴곡되어 있는 것이 바람직하다.

이러한 유지 중첩부(171b)는 사선부(54) 및 직선부(53)로 이루어지며, 사선부(54)는 유지 전극선(131)의 측선과 중첩되어 그 단면이 경사지게 형성되어 있다.

이와 같이, 데이터선 중 유지 전극선(131)과 중첩되는 유지 중첩부(171b)를 ㄷ 형상으로 굴곡되도록 형성함으로써 제조 공정이나 외부 환경 변화에 따른 열수축 및 열팽창에 의해 데이터선(171)이 스트레스(stress)를 받는 것을 완충시킨다.

또한, 유지 중첩부(171b)가 ㄷ 형상으로 굴곡되는 경우, 데이터선(171)이 유지 전극선(131) 위로 올라가며 단차지는 부분인 사선부(54)가 직선부(53)보다 유지 전극선(131)과 넓게 중첩함으로써 열수축 및 열팽창 시 단차부가 오픈되는 것을 방지한다는 장점이 있다.

데이터선(171) 및 드레인 전극(175)은 IZO(indium zinc oxide) 또는 ITO(indium tin oxide)와의 물리적, 화학적, 전기적 접촉 특성이 우수한 물질, 이를테면 몰리브덴(Mo), 몰리브덴 합금[보기: 몰리브덴-텅스텐(MoW) 합금] 따위의 몰리브덴

계열의 금속으로 이루어진다. 또한, 데이터선(171) 및 드레인 전극(175) 또한 은 계열 금속 또는 알루미늄 계열 금속 따위로 이루어진 도전막일 수도 있으며, 이러한 도전막에 더하여 크롬(Cr), 티타늄(Ti), 탄탈륨(Ta), 몰리브덴(Mo) 및 이들의합금 따위로 이루어진 다른 도전막을 포함하는 다층막 구조를 가질 수 있다.

데이터선(171) 및 드레인 전극(175)을 포함하는 충간 절연막(601) 위에 보호막(602)이 형성되어 있다.

이러한 보호막(602)은 드레인 전극(175)을 드러내는 제3 접촉구(143)를 가진다. 보호막(602)의 표면에는 요철 형상을 가지는 엠보싱(Embossing)(50)이 형성되어 있다. 엠보싱(50)은 반사 전극을 이용할 때 반사 능력을 향상시킨다.

그리고 보호막(602) 위에 ITO로 이루어진 투과 전극(192)이 형성되어 있다.

투과 전극(192) 위에 알루미늄-네오디뮴(AlNd)과 같은 금속으로 이루어지며 제3 접촉구(143)를 통하여 드레인 전극 (175)과 연결되는 반사 전극(194)이 형성되어 있다. 이러한 반사 전극(194)과 투과 전극(192)을 화소 전극이라 한다. 또한, 반사 전극(194)에는 투과창(195)이 형성되어 있고, 투과창(195) 부분에는 투과 전극(192)만이 존재한다. 투과창(195)은 투과형으로 사용될 때 백라이트로부터 나오는 빛이 통과할 수 있는 통로로서 사용되어 투과창(195)을 통해 투과 전극 (192)을 투과한 빛이 액정까지 전달한다.

이상에서 본 발명의 바람직한 실시예에 대하여 상세하게 설명하였지만, 당해 기술 분야에서 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시예가 가능하다는 점을 이해할 수 있을 것이다. 따라서, 본 발명의 권리 범위는 이에 한정되는 것은 아니고 다음의 청구범위에서 정의하고 있는 본 발명의 기본 개념을 이용한 당업자의 여러 변형 및 개량 형태 또한 본 발명의 권리범위에 속하는 것이다.

#### 발명의 효과

본 발명에 따른 박막 트랜지스터 표시판은 데이터선 중 게이트선 또는 유지 전극선과 각각 중첩되는 게이트 중첩부 또는 유지 중첩부를 ㄷ 형상으로 굴곡되도록 형성함으로써 제조 공정이나 외부 환경 변화에 따른 열수축 및 열팽창에 의해 데이터선이 스트레스를 받는 것을 완충시키고, 게이트 중첩부 또는 유지 중첩부 중 사선부를 직선부보다 게이트선과 넓게 중첩함으로써 열수축 및 열팽창 시 단차부가 오픈되는 것을 방지한다는 장점이 있다.

#### (57) 청구의 범위

## 청구항 1.

절연 기판,

상기 절연 기판 위에 형성되어 있으며 소스 영역, 드레인 영역 및 채널 영역을 포함하는 다결정 규소층,

상기 다결정 규소층 위에 형성되어 있는 게이트 절연막,

상기 게이트 절연막 위에 형성되며 있으며 상기 채널 영역과 일부분 중첩하는 게이트 전극을 포함하는 게이트선,

상기 게이트선 위에 형성되어 있는 층간 절연막,

상기 층간 절연막 위에 형성되며 상기 소스 영역과 연결되는 소스 전극을 포함하는 데이터선,

상기 층간 절연막 위에 형성되며 상기 드레인 영역과 연결되는 드레인 전극,

상기 데이터선 및 상기 드레인 전극 위에 형성되어 있는 보호막,

상기 보호막 위에 형성되어 있으며 상기 드레인 전극과 연결되어 있는 화소 전극을 포함하고,

상기 데이터선 중 상기 게이트선과 중첩되는 게이트 중첩부는 굴곡되어 있는 박막 트랜지스터 표시판.

## 청구항 2.

제1항에서,

상기 데이터선 중 상기 게이트선과 중첩되는 게이트 중첩부는 ㄷ 형상으로 굴곡되어 있는 박막 트랜지스터 표시판.

## 청구항 3.

제2항에서,

상기 데이터선 중 상기 게이트선과 중첩되는 게이트 중첩부는 사선부 및 직선부로 이루어지며, 상기 사선부는 상기 게이트 선의 측선과 중첩되어 그 단면이 경사지게 형성되어 있는 박막 트랜지스터 표시판.

### 청구항 4.

제1항에서.

상기 게이트선과 동일한 층에 형성되어 있으며, 상기 게이트선과 평행한 유지 전극선을 더 포함하고 있는 박막 트랜지스터 표시판.

## 청구항 5.

제1항에서,

상기 데이터선 중 상기 유지 전극선과 중첩되는 유지 중첩부는 굴곡되어 있는 박막 트랜지스터 표시판.

## 청구항 6.

제5항에서,

상기 데이터선 중 상기 유지 전극선과 중첩되는 유지 중첩부는 ㄷ 형상으로 굴곡되어 있는 박막 트랜지스터 표시판.

### 청구항 7.

제5항에서,

상기 데이터선 중 상기 유지 전극선과 중첩되는 유지 중첩부는 사선부 및 직선부로 이루어지며, 상기 사선부는 상기 유지 전극선의 측선과 중첩되어 그 단면이 경사지게 형성되어 있는 박막 트랜지스터 표시판.

### 도면

## 도면1

## 도면2

## 도면3

## 도면4

| 专利名称(译)        | 薄膜晶体管显示面板及其制造方法                                  |         |            |  |

|----------------|--------------------------------------------------|---------|------------|--|

| 公开(公告)号        | KR1020060036241A                                 | 公开(公告)日 | 2006-04-28 |  |

| 申请号            | KR1020040085323                                  | 申请日     | 2004-10-25 |  |

| [标]申请(专利权)人(译) | 三星电子株式会社                                         |         |            |  |

| 申请(专利权)人(译)    | 三星电子有限公司                                         |         |            |  |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                         |         |            |  |

| [标]发明人         | YI CHUNG                                         |         |            |  |

| 发明人            | YI,CHUNG                                         |         |            |  |

| IPC分类号         | G02F1/136                                        |         |            |  |

| CPC分类号         | G02F1/136286 G02F1/136213 H01L27/124 H01L27/1255 |         |            |  |

| 外部链接           | Espacenet                                        |         |            |  |

### 摘要(译)

根据本发明的薄膜晶体管基板是绝缘基板,并且包括多晶硅层的栅极重叠部分包括区域-源极,并且漏极区域形成在绝缘基板和沟道区域上,数据线包括栅极线,包括栅电极,漏电极,形成在数据线和漏电极上的保护膜,以及像素电极,并且与数据线中的栅极线重叠,是理想的弯曲。包括栅极线的数据线(包括栅极电极)部分地彼此叠置在栅极线上形成的层间绝缘膜,并且区域源极层间绝缘膜形成在层间绝缘膜上并且连接的源电极。漏电极是在形成于层间绝缘膜上的同时连接到漏区。像素电极连接到漏电极,同时形成在保护膜上。因此,根据本发明的薄膜晶体管基板具有以下优点:通过在栅极线或维持电极线的数据线中形成各自的重叠栅极重叠部分或维持重叠部分以使其弯曲成形。该数据线根据制造工艺或外部环境变化和热膨胀接收热收缩应力。维护重叠部分防止台阶部分打开。液晶显示器,应力,台阶部分,栅极重叠部分,维护重叠部分。