(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) Int. Cl.

G02F 1/1339 (2006.01)

(11) 공개번호 10-2007-0058181

(43) 공개일자 2007년06월08일

(21) 출원번호 10-2005-0116516

(22) 출원일자 2005년12월01일

심사청구일자 없음

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 이윤석

충남 천안시 두정동 1078번지 계룡 리슈빌 아파트 103-803

서동진

충남 천안시 신방동 성지새말아파트 106-1204

조우식

서울 동대문구 청량리2동 205-31

(74) 대리인 남승희

전체 청구항 수 : 총 8 항

(54) 다중 도메인 액정 표시 장치 및 이에 사용되는 기판

(57) 요약

본 발명은 다중 도메인 액정 표시 장치 및 이에 사용되는 기판에 관한 것으로, 액정 표시 장치용 하부 패턴 상에 형성된 보호막과, 상기 보호막 상에 형성되어 절개패턴을 갖는 전극과, 상기 절개 패턴 내측의 적어도 일부에 마련된 컬럼 스페이서를 포함하는 다중 도메인 액정 표시 장치에 사용되는 기판과 이를 사용하는 다중 액정 표시 장치를 제공한다.

대표도

도 6

특허청구의 범위

청구항 1.

액정 표시 장치용 하부 패턴 상에 형성된 보호막;

상기 보호막 상에 형성되어 절개패턴을 갖는 전극;

상기 절개 패턴 내측의 적어도 일부에 마련된 컬럼 스페이서;를 포함하는 다중 도메인 액정 표시 장치용 기판.

## 청구항 2.

청구항 1에 있어서,

상기 하부 패턴은, 패터닝된 블랙 매트릭스 및 칼라 필터인 다중 도메인 액정 표시 장치용 기판.

## 청구항 3.

청구항 1에 있어서,

상기 하부 패턴은, 게이트 전극, 소스 전극 및 드레인 전극을 포함하는 박막 트랜지스터와, 이와 접속된 게이트 라인 및 소스 라인을 포함하는 다중 도메인 액정 표시 장치용 기판.

## 청구항 4.

청구항 1에 있어서,

상기 전극은 ITO 또는 IZO를 포함하는 공통 전극을 사용하고, 상기 보호막은 무기 절연막 및 유기 절연막 중 적어도 어느 하나의 막을 사용하는 다중 도메인 액정 표시 장치용 기판.

## 청구항 5.

화소 절개 패턴을 갖는 화소 전극을 포함하는 제 1 기판;

공통 전극 절개 패턴을 갖는 공통 전극을 포함하는 제 2 기판;

상기 공통 전극 절개 패턴 및 상기 화소 절개 패턴 중 적어도 어느 하나의 내부의 적어도 일부에 형성된 컬럼 스페이서;

상기 제 1 및 제 2 기판 사이에 마련된 액정층;을 포함하는 다중 도메인 액정 표시 장치.

## 청구항 6.

박막 트랜지스터와 화소 절개 패턴을 갖는 화소 전극을 포함하는 제 1 기판과, 칼라 필터 패턴과 공통 전극 절개 패턴을 갖는 공통 전극을 포함하는 제 2 기판을 마련하는 단계;

상기 제 2 기판의 상기 공통 전극 절개 패턴 및 상기 제 1 기판의 상기 화소 절개 패턴 중 적어도 어느 하나의 내측의 적어도 일부에 컬럼 스페이서를 형성하는 단계;

상기 제 1 기판의 가장자리에 밀봉부재를 도포하는 단계;

상기 제 1 및 제 2 기판을 압축 밀봉하는 단계;

상기 제 1 및 제 2 기판 사이에 액정을 주입하는 단계;을 포함하는 다중 도메인 액정 표시 장치의 제조 방법.

## 청구항 7.

청구항 6에 있어서, 상기 컬럼 스페이서를 형성하는 단계는,

상기 제 2 기판 상에 컬럼 스페이서용 유기막을 형성하는 단계;

상기 유기막을 마스크를 이용하여 노광 및 현상하는 단계를 포함하는 다중 도메인 액정 표시 장치의 제조 방법.

## 청구항 8.

청구항 7에 있어서,

상기 마스크는 상기 공통 전극 절개 패턴의 적어도 일부와 중첩되는 차광영역과, 상기 차광 영역 이외의 투광영역을 갖는 다중 도메인 액정 표시 장치의 제조 방법.

명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 다중 도메인 액정 표시 장치 및 이에 사용되는 기판에 관한 것으로서, 보다 상세하게는 컬럼 스페이서에 의한 ITO막의 손상을 방지할 수 있는 다중 도메인 액정 표시 장치 및 이에 사용되는 기판에 관한 것이다.

액정 표시 장치(Liquid Crystal Display Device; LCD)는 종래의 표시 장치인 CRT(Cathode Ray Tube)와 비교하여 소형, 경량화 및 대화면화의 장점을 갖고 있어, 이의 개발이 활발히 이루어지고 있다. 특히, 액정 표시 소자는 평판 표시 장치로서의 역할을 충분히 수행할 수 있을 정도로 개발되어 핸드 폰, 피디에이(PDA), 디지털 카메라, 캠코더의 액정으로 사용될 뿐 아니라, 데스크 탑형 컴퓨터의 모니터와 대형 표시장치에도 사용되고 있어 그의 사용범위가 급속도로 확대되고 있다.

이러한 액정 표시 장치는 각기 전극이 형성된 두 기판을 두 전극이 서로 마주보도록 배치하고, 두 기판 사이에 액정 물질을 주입한 다음 두 전극 사이에 전기장을 인가하여 전기장에 의해 액정 분자들을 움직이게 함으로써 빛의 투과율을 달리하여 화상을 표시하는 장치이다. 이는 액정의 광학적 이방성과 분극성을 이용한 것으로, 액정은 구조가 가늘고 길기 때문에 문자 배열에 방향성과 분극성을 갖고 있는 액정 분자들에 인위적으로 전기장을 인가하게 되면 문자 배열 방향을 조절할 수 있다. 이에 배향 방향을 임으로 조절하면 액정의 광학적 이방성에 의해 액정 분자의 배열 방향에 따라 빛을 투과 또는 차단 할 수 있게 되어 색상 및 화상을 표현 할 수 있게 된다.

이러한 액정 표시 장치는 그 시야각이 좁은 것이 큰 단점으로 작용한다. 이에 근래에는 액정 표시 장치의 시야각을 넓히기 위한 다양한 방안이 개발되고 있으며, 그 중에서도 액정 분자를 상하 기판에 대하여 수직으로 배향하고 화소 전극과 그 대향 전극인 공통 전극에 도메인 규제수단을 형성하는 방법이 유력하다.

그 중에서도 액정 분자를 상하 기판에 대하여 수직으로 배향하고 화소 전극과 공통전극에 일정한 절개 패턴을 형성하거나 돌기를 형성하는 방법을 이용하는 수직 배향형 액정 표시 장치(Patterned Vertically Aligned, PVA)가 유력시되고 있다. 이때 절개 패턴을 형성하는 방법으로는 화소 전극과 공통 전극에 각각 절개 패턴을 형성하여 이를 절개 패턴으로 인하여 형성되는 프린지 필드(fringe field)를 이용하여 액정 분자들이 놓는 방향을 조절함으로써 시야각을 넓히는 방법이 있다.

이와 같이 시야각이 넓어진 액정 표시 장치를 제작하기 위해서는 화소 전극 절개 패턴을 갖는 TFT 기판과 공통 전극 절개 패턴을 갖는 컬러 필터 기판을 결합하여 제작하였다.

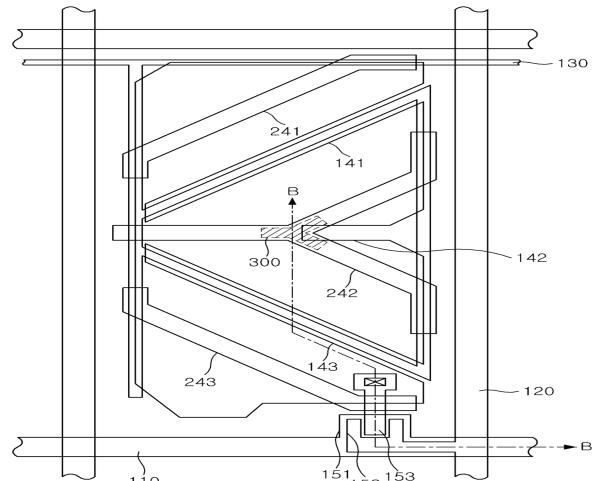

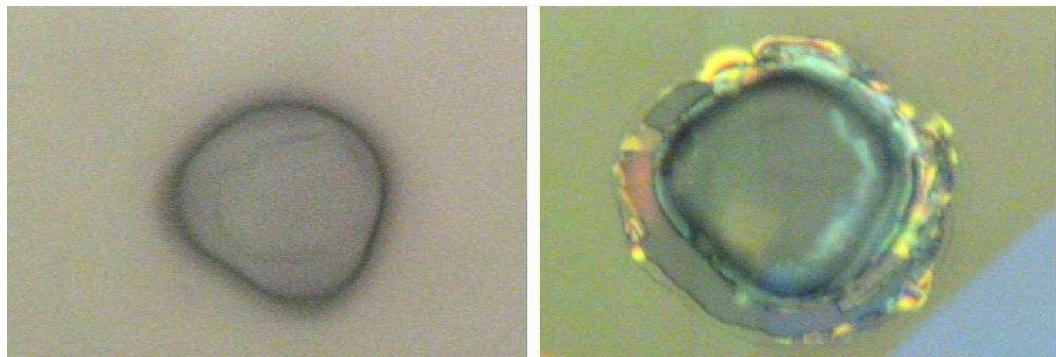

도 1은 종래의 다중 도메인 액정 표시 장치의 평면 개념도이고, 도 2는 도 1의 A-A선에 따라 자른 단면도이다. 도 3은 종래의 문제를 설명하기 위한 사진이다.

도 1 및 도 2를 참조하면, 종래의 다중 도메인 액정 표시 장치는 박막 트랜지스터(51, 52, 53), 게이트 라인(10), 소스 라인(20), 스토리지 커패시터용 유지 배선(30) 및 화소 전극(40)이 형성된 박막 트랜지스터 기판(1)과, 칼라 필터(60), 오버코

트막(70) 및 공통 전극(80)이 형성된 칼라 필터 기판(2)을 포함한다. 칼라 필터 기판(2) 상에 형성되어 두 기판 사이의 셀 캡을 유지하는 스페이서(90)와, 박막 트랜지스터 기판(1) 상에 형성되어 두 기판 사이를 밀봉하는 실란트 등의 밀봉 수단(미도시)과, 상기 두 기판 사이 공간에 주입된 액정층(미도시)을 포함한다.

상기 화소 전극(40)과 공통 전극(80) 각각에는 앞서 설명한 바와 같이 액정 표시 장치의 시야각을 넓이기 위해 다수의 절개 패턴(41, 42, 43, 81, 82, 83)이 마련되어 있다.

이러한 액정 표시 장치는 먼저 상기 칼라 필터 기판(2)의 공통 전극(80) 상에 스페이서(90)를 형성하고, 박막 트랜지스터 기판(1)에 밀봉 수단을 형성한다. 이후, 절개 패턴(41, 42, 43)이 형성된 화소 전극(40)과 절개 패턴(81, 82, 83)이 형성된 공통 전극(80)이 대향하도록 두 기판을 압착 밀봉하고, 압착 밀봉된 두 기판 사이로 액정을 주입하여 제작한다.

이때, 종래의 컬럼 스페이서(90)는 도 2에 도시된 바와 같이 공통 전극(80) 상에 형성되어 있기 때문에 두 기판 합착을 위한 압력인가시 컬럼 스페이서(90)가 압축이 된다. 그러나 컬럼 스페이서(90)의 탄성 변형량의 범위를 넘어 압축이 될 경우에는 더 이상 압축되지 않고, 그 힘이 하부막에 전달된다. 이로인해 컬럼 스페이서(90)에 인가되는 압축력이 그 하부의 공통 전극(80)에 전달되어 도 3의 사진과 같이 공통 전극(80)이 깨지게 되고 이는 액정 표시 장치의 블랙(black gap)을 유발하게 된다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명은 상기의 문제점을 해결하기 위하여 도출된 것으로서, 컬럼 스페이서의 위치와 형상을 변경하여 전극의 손상을 방지할 수 있는 다중 도메인 액정 표시 장치 및 이에 사용되는 기판을 제공하는 것을 그 목적으로 한다.

### 발명의 구성

본 발명에 따른 액정 표시 장치용 하부 패턴 상에 형성된 보호막과, 상기 보호막 상에 형성되어 절개패턴을 갖는 전극과, 상기 절개 패턴 내측의 적어도 일부에 마련된 컬럼 스페이서를 포함하는 다중 도메인 액정 표시 장치용 기판을 제공한다.

여기서, 상기 하부 패턴은, 패터닝된 블랙 매트릭스 및 칼라 필터인 것이 바람직하다. 이뿐 아니라, 상기 하부 패턴은, 게이트 전극, 소스 전극 및 드레인 전극을 포함하는 박막 트랜지스터와, 이와 접속된 게이트 라인 및 소스 라인을 포함할 수도 있다.

상술한 전극은 ITO 또는 IZO를 포함하는 공통 전극을 사용하고, 상기 보호막은 무기 절연막 및 유기 절연막 중 적어도 어느 하나의 막을 사용하는 것이 바람직하다.

또한, 본 발명에 따른 화소 절개 패턴을 갖는 화소 전극을 포함하는 제 1 기판과, 공통 전극 절개 패턴을 갖는 공통 전극을 포함하는 제 2 기판과, 상기 공통 전극 절개 패턴 및 상기 화소 절개 패턴 중 적어도 어느 하나의 내부의 적어도 일부에 형성된 컬럼 스페이서와, 상기 제 1 및 제 2 기판 사이에 마련된 액정층;을 포함하는 다중 도메인 액정 표시 장치를 제공한다.

또한, 본 발명에 따른 박막 트랜지스터와 화소 절개 패턴을 갖는 화소 전극을 포함하는 제 1 기판과, 칼라 필터 패턴과 공통 전극 절개 패턴을 갖는 공통 전극을 포함하는 제 2 기판을 마련하는 단계와, 상기 제 2 기판의 상기 공통 전극 절개 패턴 및 상기 제 1 기판의 상기 화소 절개 패턴 중 적어도 어느 하나의 내측의 적어도 일부에 컬럼 스페이서를 형성하는 단계와, 상기 제 1 기판의 가장자리에 밀봉부재를 도포하는 단계와, 상기 제 1 및 제 2 기판을 압축 밀봉하는 단계와, 상기 제 1 및 제 2 기판 사이에 액정을 주입하는 단계를 포함하는 다중 도메인 액정 표시 장치의 제조 방법을 제공한다.

여기서, 상기 컬럼 스페이서를 형성하는 단계는, 상기 제 2 기판 상에 컬럼 스페이서용 유기막을 형성하는 단계와, 상기 유기막을 마스크를 이용하여 노광 및 현상하는 단계를 포함하는 것이 바람직하다. 그리고, 상기 마스크는 상기 공통 전극 절개 패턴의 적어도 일부와 중첩되는 차광영역과, 상기 차광 영역 이외의 투광영역을 갖는 것이 바람직하다.

이하, 첨부된 도면을 참조하여 본 발명의 실시예를 더욱 상세히 설명한다. 그러나 본 발명은 이하에서 개시되는 실시예에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이다.

도면에서 여러 층 및 각 영역을 명확하게 표현하기 위하여 두께를 확대하여 표현하였으며 도면상에서 동일 부호는 동일한 요소를 지칭하도록 하였다. 또한, 층, 막, 영역, 판 등의 부분이 다른 부분 상부에 또는 위에 있다고 표현되는 경우는 각 부분이 다른 부분의 바로 상부 또는 바로 위에 있는 경우뿐만 아니라 각 부분과 다른 부분의 사이에 또 다른 부분이 있는 경우도 포함한다.

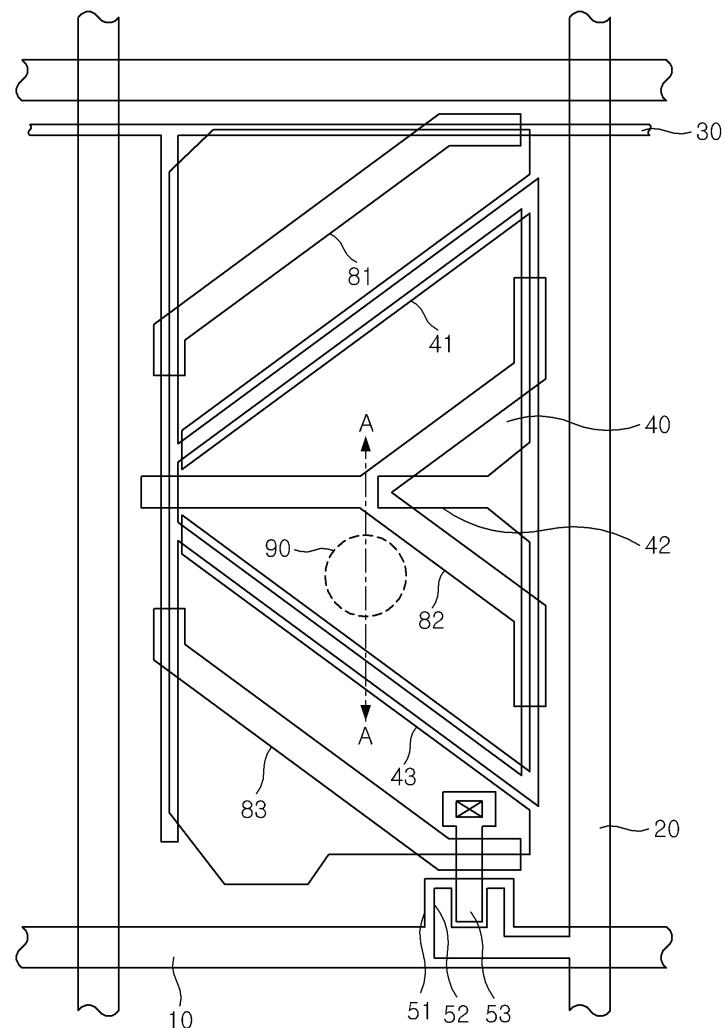

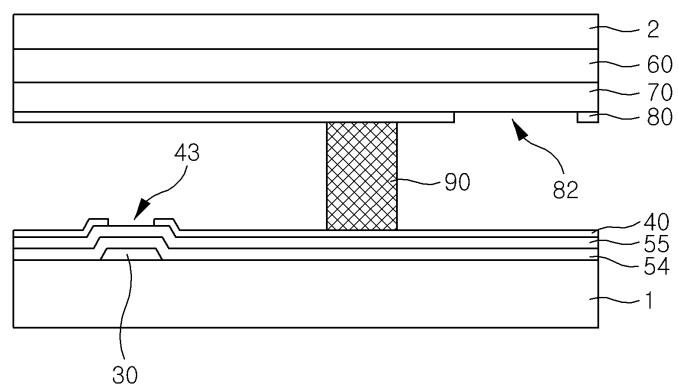

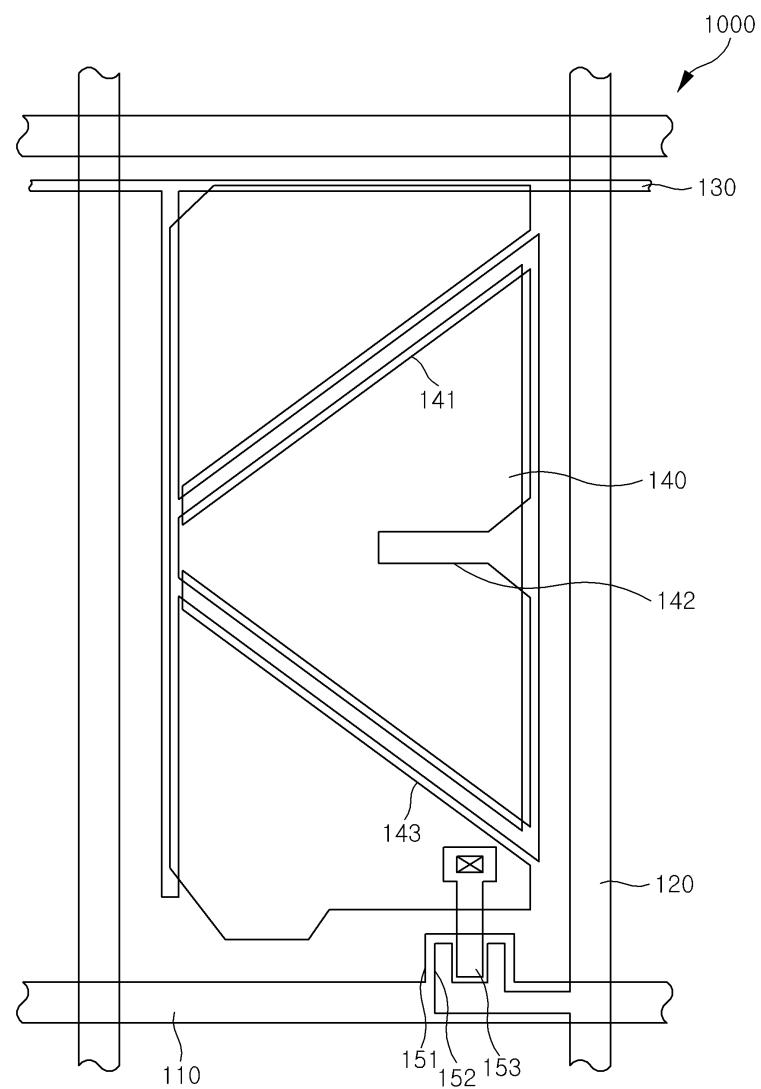

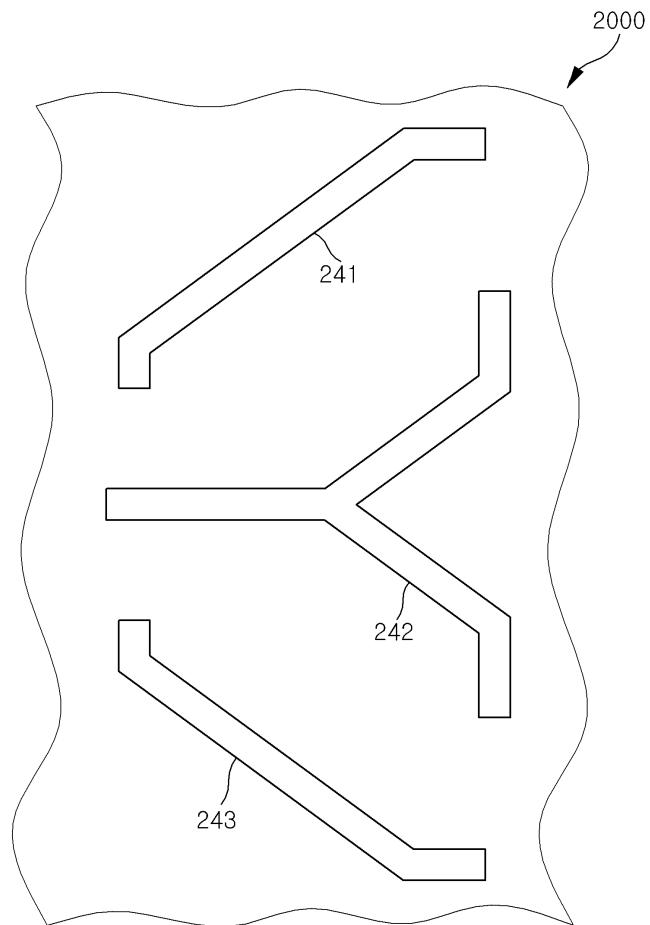

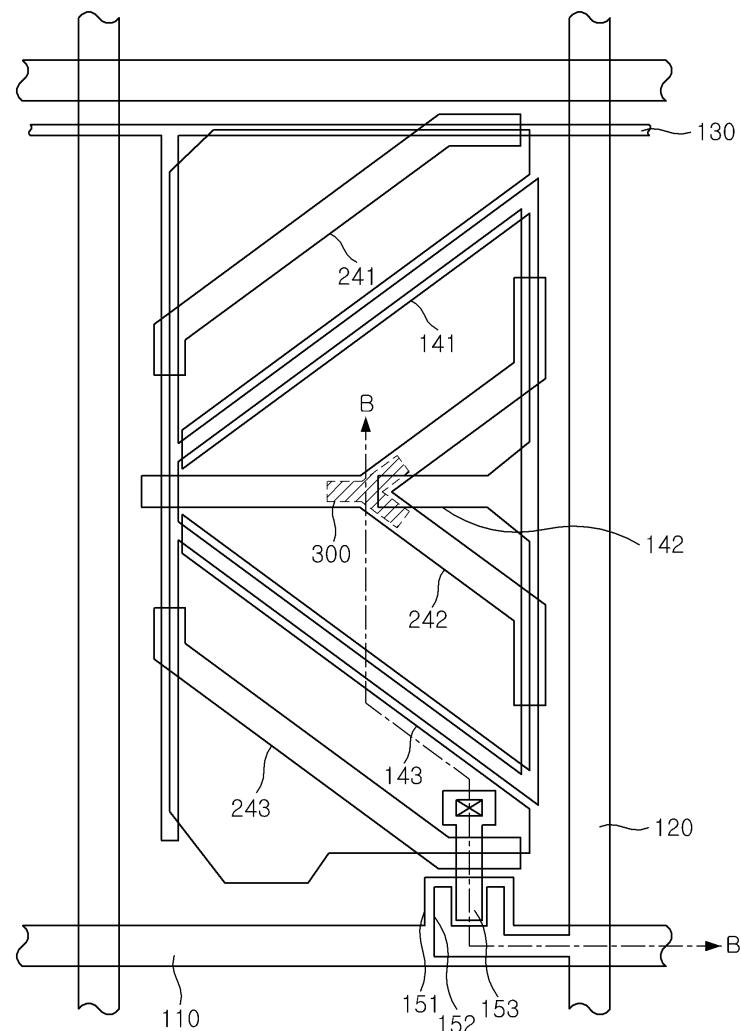

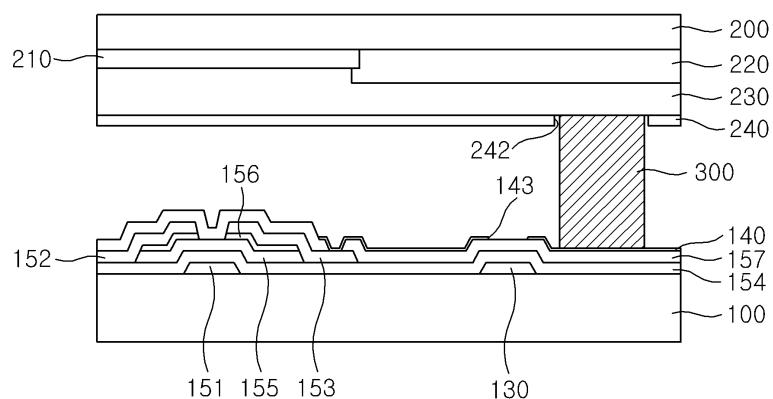

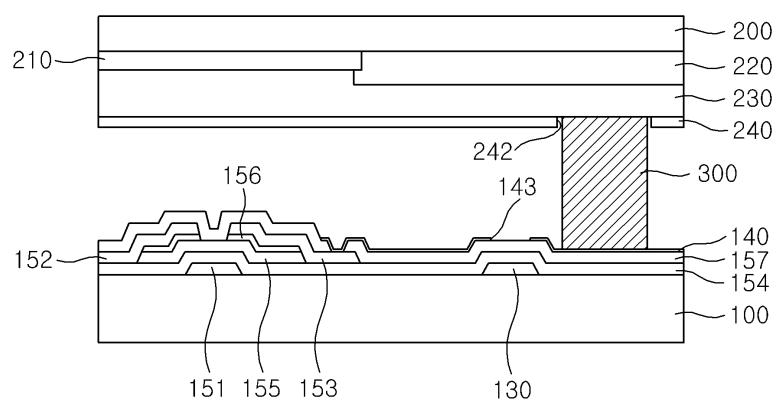

도 4는 본 발명의 일 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판의 사시도이고, 도 5는 본 발명의 일 실시예에 따른 액정 표시 장치용 칼라 필터 기판의 사시도이다. 도 6은 본 발명의 일 실시예에 따른 액정 표시 장치의 사시도이다. 도 7은 도 6의 액정 표시 장치를 B-B 선에 대해 자른 단면도이다.

도 4 내지 도 7을 참조하면, 본 실시예에 따른 액정 표시 장치는 하부 기판인 박막 트랜지스터 기판(1000)과, 이와 대향하여 배치되는 상부 기판인 컬러 필터 기판(2000)과, 이들 두 기판 사이에 마련되어 상기 두 기판의 셀 잭을 유지하는 컬럼 스페이서(300)와, 상기 두 기판을 밀봉하는 실란트와 같은 밀봉부재(미도시)와, 상기 두 기판의 밀봉 영역 내에 마련된 액정층(미도시)을 포함한다. 이때 상기 액정층의 액정 분자의 배향은 각 기판에 대하여 수직이 되도록 하는 수직 배향 모드인 것이 바람직하나, 수직 배향이 아닐 수도 있다. 상기 컬럼 스페이서(300)는 상기 컬러 필터 기판(2000)의 공통 전극(240)의 절개패턴(242) 영역 내에 형성되는 것이 바람직하다. 즉, 공통 전극(240)의 절개패턴(242)에 의해 노출된 오버 코트막(230) 상에 형성될 수 있다. 그리고, 상기 밀봉 부재(미도시)는 박막 트랜지스터 기판(1000)에 형성되는 것이 바람직하다.

박막 트랜지스터 기판(1000)은 도 4 및 도 7에 도시된 바와 같이 투광성 절연 기판(100) 위에 게이트 신호를 전달하며 제 1 방향으로 연장되고 제 2 방향으로 소정 간격을 갖도록 배열된 복수의 게이트 라인(110)과, 게이트 라인(110)에 교차하여 형성된 복수의 소스 라인(120)과, 게이트 라인(110)과 소스 라인(120)에 의해 정의된 화소 영역에 형성된 화소 전극(140)과, 상기 화소 전극과 접속되고 게이트 라인(110)과 소스 라인(120)의 교차점에 매트릭스 형태로 형성된 복수의 박막 트랜지스터(151, 152, 153)과, 상기 게이트 라인(110)에 평행하게 연장된 유지 전극 라인과 이로부터 화소 영역 내부로 연장된 유지 전극을 포함하는 다수의 유지 배선(130)을 포함한다.

게이트 라인(110)은 주로 가로 방향으로 뻗어 있고, 게이트 라인(110)의 일부가 상하로 돌출하여 게이트 전극(151)을 이룬다. 게이트 라인(110)의 끝단에는 게이트 패드(미도시)가 형성되어 있다.

소스 라인(120)은 주로 세로 방향으로 뻗어 있고, 그 일부가 돌출하여 소스 전극(152)을 이룬다. 소스 라인(120)의 끝단에는 데이터 패드(미도시)가 형성되어 있다. 여기서는 직선형의 소스 라인(120)을 예시하였으나, 소스 라인(120)은 소정의 굽은 영역을 가질 수도 있고, 이때는 화소 전극(140)이 데이터 선의 굽은 영역을 따라 형성될 수도 있다.

박막 트랜지스터(151, 152, 153)는 게이트 선(110)에 공급되는 신호에 응답하여 데이터 선(120)에 공급되는 화소 신호가 화소 전극(140)에 충전되도록 한다. 따라서, 박막 트랜지스터(151, 152, 153)는 게이트 선(110)에 접속된 게이트 전극(151)과, 데이터 선(120)에 접속된 소스 전극(152)과, 화소 전극(140)에 접속된 드레인 전극(153)과, 게이트 전극(151)과 소스 전극(152) 및 드레인 전극(153) 사이에 순차적으로 형성된 게이트 절연막(154) 및 활성층(155)과, 활성층(155)의 적어도 일부에 형성된 오믹 접촉층(156)을 포함한다. 이때 오믹 접촉층(156)은 채널부를 제외한 활성층(155) 상에 형성될 수 있다.

박막 트랜지스터(151, 152, 153)의 상부에는 절연성 보호막(157)이 형성되어 있다. 보호막(157)은 질화 실리콘 또는 산화 실리콘 등의 무기 물질로 형성될 수도 있고, 저유전율 유기막으로 형성될 수도 있다. 물론 무기 절연막과 유기막의 이중층으로 형성될 수도 있다.

화소 전극(140)은 보호막(157) 상에 형성되며 드레인 전극(153)과 콘택홀을 통해 접속되어 있다. 화소 전극(140)은 액정의 배열 방향을 조정하기 위한 도메인 규제수단으로 다수의 화소 절개 패턴(141, 142, 143)를 갖는다. 절개 패턴은 화소 전극(140)을 상하로 반분하는 위치에 가로 방향으로 형성되어 있는 제 2 화소 절개 패턴(142)과, 반분된 화소 전극(140)의 상하부에 각각 사선 방향으로 형성되어 있는 제 1 및 제 3 화소 절개 패턴(141, 143)을 포함한다. 제 1 화소 절개 패턴(141)은 화소 전극(140)의 우측 가장자리에서 좌측 가장자리를 향해 뻗어 있으며, 그 입구인 우측 가장자리측이 확장되어 있다. 제 2 및 제 3 화소 절개 패턴(142, 143)은 서로 직각을 이루는 것이 바람직하다. 이러한 화소 절개 패턴(141, 142, 143)은 프린지 필드의 방향을 4 방향으로 고르게 분산시키기 위함이다.

유지 배선은 상기 화소 전극과 그 일부가 중첩되도록 형성하여 유지 커패시터를 형성한다. 상기 화소 전극의 절개 패턴 하부에 까지 연장되도록 형성하여 화소 전극의 절개부에서의 빛 샘을 방지하는 역할도 할 수 있다. 도면에 도시된 바와 같이 화소 전극의 제 1 및 제 3 화소 절개 패턴(141, 143)과 유지 배선의 연장 라인의 일부가 중첩되도록 형성되는 것이 바람직하다. 물론 이때, 화소 전극은 액정 분자의 배향을 위한 도메인 규제수단으로 절개 패턴 대신에 돌기를 포함할 수도 있다.

한편, 공통 전극은 도 5 및 도 7에 도시된 바와 같이 블랙 매트릭스(210)와, 컬러 필터(220)와, 오버 코트층(230)과, 다수의 절개 패턴(241, 242, 243)을 갖는 공통 전극(240)을 포함한다.

블랙 매트릭스(210)는 박막 트랜지스터 영역에 형성되어 화소 영역 이외의 영역으로 빛이 새는 것과 인접한 화소 영역들 사이의 광 간섭을 방지한다. 즉, 블랙 매트릭스(210)는 박막 트랜지스터 기판(100)의 화소 전극(140) 영역을 개방하는 개구부를 갖는다. 컬러 필터(220)는 적(R), 녹(G), 청(B)으로 구분되며 형성되어 적, 녹, 청색 광으로 각각 투과시키기 위해 블랙 매트릭스(210)의 개구부를 덮도록 형성된다. 컬러 필터(220)의 배면 상에는 유기물질로 이루어진 오버 코트막(230)이 형성된다.

공통 전극(240)은 오버 코트막(230)의 배면 상에 전면 도포된 투명 도전층으로 다수의 절개 패턴(241, 242, 243)을 갖는다. 화소 전극(140)의 제 1 및 제 3 화소 절개 패턴(141, 143) 사이에 마련된 제 2 절개 패턴(242)과, 제 1 및 제 3 화소 절개 패턴(141, 143) 외측에 이와 나란한 사선부와, 사선부의 양단에서 연장되어 화소 전극(140)의 가장자리와 중첩되는 굴절부를 갖는 제 1 및 제 3 절개 패턴(241, 243)을 포함한다.

도시되지는 않았지만, 상기 박막 트랜지스터 기판(1000)과 칼라 필터 기판(2000)의 서로 마주하는 면 상부에 배양막이 형성되어 있고, 각각의 배양막은 액정 분자를 기판 면에 대하여 수직으로 배양하는 배양막인 것이 바람직하고 물론 그렇지 않을 수도 있다.

상술한 바와 같이 절개 패턴(241, 242, 243)을 갖는 공통 전극(240)과 그 하부에 형성된 하부 패턴을 갖는 칼라 필터 기판(2000)의 상기 절개 패턴(241, 242, 243) 내에 컬럼 스페이서(300)를 형성한다. 이때, 도면에서와 같이 제 2 절개 패턴(242)의 내측의 일부에 컬럼 스페이서(300)를 배치하여 박막 트랜지스터 기판(1000)과 칼라 필터 기판(2000) 사이의 셀 갭을 유지하게 된다. 이과 같이 절개 패턴(241, 242, 243) 내측의 적어도 일부에 컬럼 스페이서(300)를 형성하여 컬럼 스페이서(300)의 일측면이 단단한 전극이 아닌 충격 흡수가 가능한 절연막 즉, 오버 코트막(230)과 접하도록 하는 것이 바람직하다.

이를 통해 두 기판을 압축 밀봉할 경우, 종래의 경우 기판에 가해지는 압축력은 컬럼 스페이서에 인가되고, 컬럼 스페이서의 탄성 변형량의 범위를 넘는 압축력은 공통 전극에 인가되어 공통 전극이 손상되는 문제가 발생하였고, 컬럼 스페이서가 뭉개져 셀 갭을 유지하지 못하는 문제가 발생하였다. 하지만 본 발명에서는 컬럼 스페이서가 공통 전극의 절개 패턴 내측의 일부 영역에 마련되어 있기 때문에 두 기판에 가해지는 압축력은 컬럼 스페이서에 전달되고, 컬럼 스페이서의 탄성 변형량의 범위를 넘어서는 압축력은 공통 전극 하부의 절연막 즉, 오버 코트막에 흡수되어 공통 전극의 손상을 방지할 수 있을 뿐 아니라, 컬럼 스페이서의 변형을 방지할 수 있다.

상기와 같이 컬럼 스페이서에 의해 유지된 두 기판 사이의 셀 갭에 액정을 주입하여 액정 표시 장치를 제작한다.

하기에서는 상기의 칼라 필터 기판의 제작 방법을 중심으로 본 실시예에 따른 액정 표시 장치의 제작 방법을 설명한다.

도 8a 내지 도 8e는 본 실시예에 따른 액정 표시 장치의 제작 방법을 설명하기 위한 단면도이다.

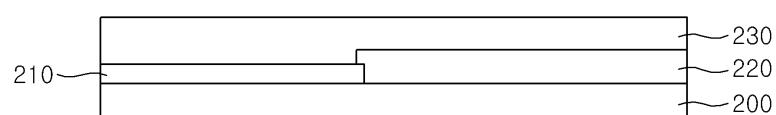

도 8a를 참조하면, 투광성 절연기판(200) 상에 블랙 매트릭스(210)와 컬러 필터(220)를 패터닝하고 그 상부에 오버 코트막(230)을 형성한다.

상기의 블랙 매트릭스(210)와 컬러 필터(220)의 패터닝은 투광성 절연기판(200) 상에 블랙 매트릭스용 유기막을 도포한다. 이때, 상기 블랙 매트릭스용 유기막은 차광성을 갖는 크롬/산화크롬 이중층 또는 카본블랙, 산화티탄 등으로 된 유기막을 사용하는 것이 바람직하다. 블랙 매트릭스(210) 패터닝을 위한 마스크를 이용한 사진 현상 공정을 실시하여 블랙 매트릭스용 유기막을 패터닝한다.

패터닝된 블랙 매트릭스(210) 상에 순차적으로 레드 칼라(R), 그린 칼라(G) 및 블루 칼라(B)의 칼라 필터(220)를 형성한다.

이를 위해 블랙 매트릭스(210)가 형성된 기판(200) 상에 적색안료를 포함하는 감광막, 녹색안료를 포함하는 형광체 및 청색 안료를 포함하는 형광체를 각기 도포하고 노광하여 레드 칼라, 그린 칼라 및 블루 칼라의 칼라 필터(220)를 형성한다.

상기와 같이 패터닝된 칼라 필터(220) 상에 유기 물질로 이루어진 오버 코트막(230)을 형성한다. 본 발명은 상기의 오버 코트막(230)을 형성하지 않을 수도 있다.

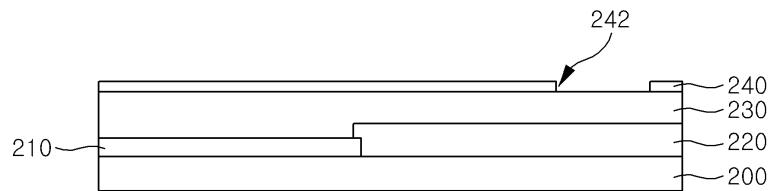

도 8b를 참조하면, 상기 오버 코트막(230) 상에 공통 전극(240)을 형성하고, 마스크를 이용한 패터닝 공정을 통해 공통 전극(240)의 일부를 제거하여 절개 패턴(241, 242, 243)을 형성한다.

이때, 상기 공통 전극(240) 층으로는 인듐 틴 옥사이드(indium tin oxide: ITO) 또는 인듐 징크 옥사이드(indium zinc oxide: IZO)를 사용하는 것이 바람직하다. 공통 전극(240) 상에 감광막을 도포한 다음 사진 현상 공정을 통해 도 5에 도시된 바와 같은 절개 패턴(241, 242, 243) 영역을 개방하는 감광막 패턴을 형성한다. 이후, 감광막 패턴을 식각 마스크로 하는 식각 공정을 실시하여 상기 공통 전극(240)의 일부를 제거하여 절개 패턴(241, 242, 243)을 형성하고, 상기 감광막 패턴을 제거한다.

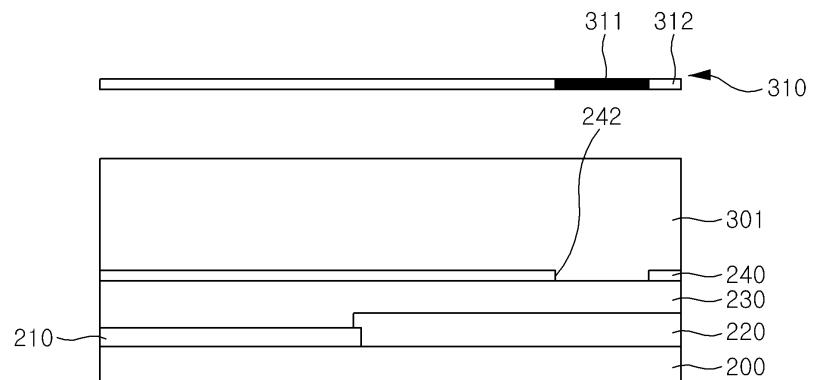

도 8c 및 도 8d를 참조하면, 상기 절개 패턴(241, 242, 243)을 갖는 공통 전극(240) 상에 스페이서용 절연막(301)을 도포하고, 사진 현상 공정을 실시하여 상기 절개 패턴(242)의 일부에 컬럼 스페이서(300)를 형성한다.

이때, 스페이서용 절연막(301)으로 광에 의해 그 특성이 변화되는 감광성의 유기물질을 사용한다. 본 실시예에서는 감광성 투명 수지를 사용하는 것이 바람직하다.

스페이서용 절연막(301)을 절개 패턴(241, 242, 243)이 형성된 공통 전극(240) 상에 도포한 다음, 스페이서 형성용 마스크(310)를 이용한 노광공정을 실시한다. 이때, 상기 스페이서 형성용 마스크(310)는 상기 절개 패턴(242)의 일부와 대응되는 차폐영역(311)을 갖고 나머지 영역은 투과 영역(312)을 갖는 마스크를 사용한다. 이를 이용하여 노광을 실시하게 되면 절개 패턴(242) 상층에 위치한 스페이서용 절연막(301)은 노광되지 않고, 나머지 영역은 노광된다. 이후, 현상 공정을 실시하게 되면 노광된 영역의 스페이서용 절연막(301)은 제거되고 노광되지 않은 영역은 잔류하여 컬럼 스페이서(300)를 형성하게된다. 이후, 소정의 베이킹 공정을 실시하여 컬럼 스페이서(300)를 경화시킨다.

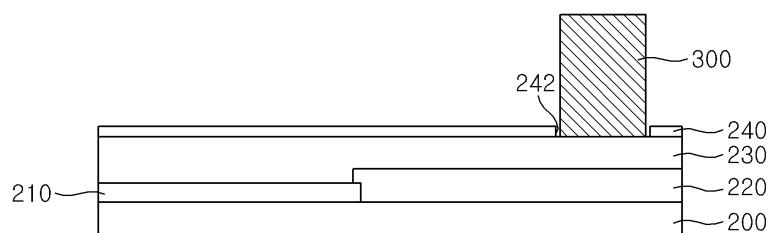

도 8e를 참조하면, 공통 전극(240)의 절개 패턴(241, 242, 243) 내에 컬럼 스페이서(300)가 형성된 칼라 필터 기판(2000)과, 화소 절개 패턴(141, 142, 143)을 갖는 화소 전극(140)이 형성된 박막 트랜지스터 기판(1000)을 가압 밀봉하여 액정 표시 장치를 제작한다.

본 발명은 상술한 설명에 한정되지 않고, 액정 표시 장치의 시야각을 넓이기 위한 다양한 형태의 절개 패턴을 갖는 액정 표시 장치에 적용될 수 있다. 즉, T패턴 형상의 절개부를 갖는 경우와, Z셀 형상의 액정 표시 장치에도 적용될 수 있다.

또한, 상술한 설명에서는 스페이서를 사진 현상 공정을 통해 제작함에 관해 설명하였지만 이에 한정되지 않고, 증착 공정 또는 식각 공정등의 다양한 방법을 통해 상기 컬럼 스페이서를 상기 절개패턴 내측에 형성할 수도 있다.

또한, 본 발명은 상술한 설명과 같이 칼라 필터 기판의 공통 전극의 절개 패턴 내에 컬럼 스페이서가 형성될 뿐만 아니라 박막 트랜지스터 기판의 화소 절개 패턴 상에도 컬럼 스페이서가 형성될 수 있다. 하기에서는 박막 트랜지스터 기판의 화소 절개 패턴 내에 컬럼 스페이서가 형성된 본 발명의 다른 실시예에 따른 액정 표시 장치에 관해 설명한다. 후술되는 설명은 앞서 설명한 실시예와 중복되는 설명은 생략하고, 박막 트랜지스터 기판을 중심으로 설명한다.

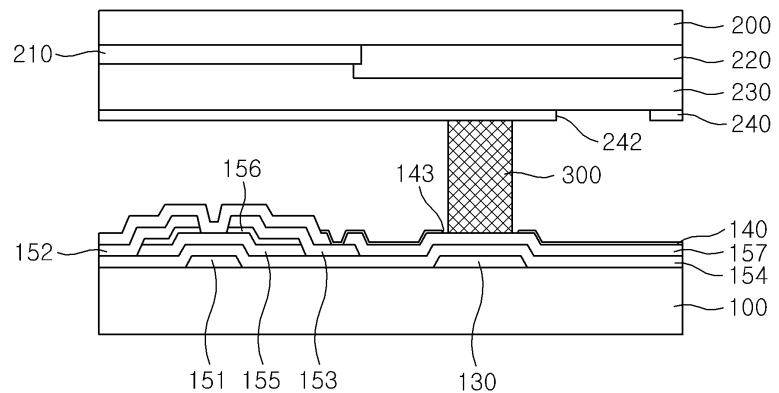

도 9는 본 발명의 다른 실시예에 따른 액정 표시 장치의 단면도이다.

도 9를 참조하면, 투명 절연 기판(100) 상에 박막 트랜지스터를 포함하는 하부 패턴을 형성하고, 그 상부에 절연성 보호막(157)을 형성한다.

이때, 상기 하부 패턴은 상기 박막 트랜지스터와 게이트 라인(미도시) 그리고 소스 라인(미도시) 및 유지 배선(미도시)을 포함하고 이의 형성 방법을 간략히 설명하면 투명 절연 기판(100) 상에 제 1 도전성막을 형성한 다음 감광막 마스크를 이용한 패터닝 공정을 통해 게이트 전극(151), 게이트 라인(110) 및 유지 배선(130)을 형성한다.

먼저 투명 절연기판(100) 상에 CVD법, PVD법 및 스퍼터링법 등을 이용한 증착 방법을 통해 제 1 도전성막을 형성한다. 제 1 도전성 막으로는 Cr, MoW, Cr/Al, Cu, Al(Nd), Mo/Al, Mo/Al(Nd), Cr/Al(Nd) 및 Mo/Al/Mo 중 적어도 어느 하나를 사용하는 것이 바람직하다. 물론 이에 한정되지 않고 앞서 설명한 바와 같이 제 1 도전성막으로 Al, Nd, Ag, Cr, Ti, Ta 및 Mo 중 적어도 어느 하나의 금속 또는 이들을 포함하는 합금으로 형성하되, 단일층 및 다중층으로 형성할 수 있다. 이와 같이 전체 기판 상에 제 1 도전성막을 형성한 후, 감광막을 도포한 다음, 마스크를 이용한 사진 형상 공정을 실시하여 감광막 마스크 패턴을 형성한다. 상기 감광막 마스크 패턴을 식각 마스크로 하는 식각공정을 실시하여 다수의 게이트 라인(110)과 게이트 전극(1510) 그리고, 다수의 유지 배선(130)을 형성하는 것이 바람직하다. 이후, 소정의 스트립 공정을 실시하여 제 1 감광막 마스크 패턴을 제거한다.

이어서, 전체 구조 상에 게이트 절연막(154), 활성층(155) 및 오믹 접촉층(156)을 순차적으로 형성한 다음, 감광막 마스크 패턴(미도시)을 이용한 식각공정을 실시하여 박막 트랜지스터의 활성영역을 형성한다.

여기서, 활성층(155)으로는 비정질 실리콘층을 사용하고, 오믹 접촉층(155)으로는 실리사이드 또는 N형 불순물이 고농도로 도핑된 비정질 실리콘층을 사용한다.

다음으로, 전체 구조상에 제 2 도전성막을 형성한 다음, 이를 감광막 마스크 패턴(미도시)을 이용한 식각공정을 실시하여 소스 및 드레인 전극(152, 153) 및 소스 라인(120)을 형성한다. 이때, 제 2 도전성막으로는 Mo, Al, Cr, Ti 중 적어도 하나의 금속 단일층 또는 다중층을 사용하는 것이 바람직하다. 물론 제 2 도전성막은 제 1 도전성막과 동일한 물질을 사용할 수도 있다.

상술한 바와 같이 박막 트랜지스터를 포함하는 하부 패턴 상에 보호막(157)을 형성하되, 보호막(157)의 일부를 제거하여 드레인 콘택홀을 포함하는 다수의 콘택 홀을 형성할 수 있다.

상기의 보호막(157)으로 질화 실리콘 또는 산화 실리콘 등의 무기 물질로 형성될 수도 있고, 저유전율 유기막으로 형성될 수도 있다. 물론 무기 절연막과 유기막의 이중층으로 형성될 수도 있다.

이어서, 상기 보호막(157) 상에 화소 전극용 도전성막을 형성하고, 이를 패터닝 하여 화소 전극(140)과 다수의 도전성 패드(미도시) 및 콘택(미도시)를 형성한다. 이때, 상기 화소 전극(140)의 일부를 패터닝 하여 화소 절개 패턴(141, 142, 143)도 함께 형성한다.

상기 화소 절개 패턴(141, 142, 143)이 형성된 화소 전극(140) 상에 스페이서용 절연막을 도포하고, 사진 형상 공정을 실시하여 화소 절개 패턴(141, 142, 143) 내측에 스페이서(300)를 형성한다.

이후, 절개 패턴(241, 242, 243)을 갖는 공통전극(240)이 형성된 칼라 필터 기판(2000)과 상기 화소 절개 패턴(141, 142, 143) 내측에 컬럼 스페이서(300)를 갖는 박막 트랜지스터 기판(1000)를 결합 밀봉하고 액정을 주입하여 액정 표시 장치를 제작한다.

### 발명의 효과

상술한 바와 같이, 본 발명은 전극의 절개 패턴 상에 컬럼 스페이서를 형성하여 가압에 의한 컬럼 스페이서의 변형을 방지 할 수 있다.

또한, 가압에 의한 컬럼 스페이서 하부의 전극이 깨져 구동시 블랙 캡 불량이 발생하는 것을 방지할 수 있다.

본 발명을 첨부 도면과 전술된 바람직한 실시예를 참조하여 설명하였으나, 본 발명은 그에 한정되지 않으며, 후술되는 특허청구범위에 의해 한정된다. 따라서, 본 기술분야의 통상의 지식을 가진 자라면 후술되는 특허청구범위의 기술적 사상에서 벗어나지 않는 범위 내에서 본 발명을 다양하게 변형 및 수정할 수 있다.

### 도면의 간단한 설명

도 1은 종래의 다중 도메인 액정 표시 장치의 평면 개념도.

도 2는 도 1의 A-A선에 따라 자른 단면도.

도 3은 종래의 문제를 설명하기 위한 사진.

도 4는 본 발명의 일 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판의 사시도.

도 5는 본 발명의 일 실시예에 따른 액정 표시 장치용 칼라 필터 기판의 사시도.

도 6은 본 발명의 일 실시예에 따른 액정 표시 장치의 사시도.

도 7은 도6의 액정 표시 장치를 B-B 선에 대해 자른 단면도.

도 8a 내지 도 8e는 본 실시예에 따른 액정 표시 장치의 제작 방법을 설명하기 위한 단면도.

도 9는 본 발명의 다른 실시예에 따른 액정 표시 장치의 단면도.

<도면의 주요 부분에 대한 부호의 설명>

10, 110 : 케이트 라인 20, 120 : 소스 라인

40, 140 : 화소 전극 80, 240 : 공통 전극

41, 42, 43, 81, 82, 83, 141, 142, 143, 241, 242, 243 : 절개 패턴

90, 300 : 스페이서

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8a

도면8b

도면8c

도면8d

도면8e

## 도면9

|                |                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 多畴液晶显示器及其所用的基板                                                                       |         |            |

| 公开(公告)号        | <a href="#">KR1020070058181A</a>                                                     | 公开(公告)日 | 2007-06-08 |

| 申请号            | KR1020050116516                                                                      | 申请日     | 2005-12-01 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                             |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                             |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                                             |         |            |

| [标]发明人         | LEE YUN SEOK<br>이윤석<br>SEO DONG JIN<br>서동진<br>CHO WOO SIK<br>조우식                     |         |            |

| 发明人            | 이윤석<br>서동진<br>조우식                                                                    |         |            |

| IPC分类号         | G02F1/1339                                                                           |         |            |

| CPC分类号         | G02F1/1339 G02F1/133512 G02F1/133514 G02F1/1343 G02F1/136286 G02F1/1368 G02F2201/121 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                            |         |            |

### 摘要(译)

本发明涉及多畴液晶显示器及其中使用的基板，提供用于多域液晶显示器的基板和使用该基板的多液晶显示器，包括在具有保护膜的电极的至少一部分中制备的柱间隔物形成在液晶显示器的底层图案上，并在保护膜上形成切口图案，并在切口图案内侧形成。液晶显示器，柱状衬垫，切口图案，电极，保护膜。