**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl.<sup>7</sup>

G02F 1/136

(11) 공개번호 10-2005-0040283

(43) 공개일자 2005년05월03일

(21) 출원번호 10-2003-0075447

(22) 출원일자 2003년10월28일

|          |                                                                                                                                                                                                                                          |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (71) 출원인 | 삼성전자주식회사<br>경기도 수원시 영통구 매탄동 416                                                                                                                                                                                                          |

| (72) 발명자 | 조홍제<br>경기도수원시팔달구영통동주공1차APT107동304호<br>정창오<br>경기도수원시팔달구망포동동수원엘지빌리지201-203<br>이육래<br>충청남도천안시신방동현대향촌아파트304동1408호<br>최동우<br>경기도수원시팔달구영통동청명마을3단지동신아파트311-2002<br>김영선<br>경기도용인시구성면보정리1161번지진산마을삼성5차511-1402<br>강성철<br>경기도용인시상현동금호베스트빌133동1003호 |

| (74) 대리인 | 허성원<br>윤창일                                                                                                                                                                                                                               |

심사청구 : 없음

**(54) 액정표시장치 및 그 제조 방법**

**요약**

본 발명은 액정표시장치 및 그 제조방법에 관한 것으로서, 본 발명의 액정표시장치는 TFT 기판의 가장자리에 금속층과 상기 금속층의 상층에 투명전도층을 갖는 액정표시장치에 있어서, 상기 투명전도층은 상기 금속층의 상면을 노출시키는 개방부를 갖는 것을 특징으로 한다. 이에 의해 그로스 테스트를 수행할 때 패드부와 프로브 펀 사이의 접촉이 안 되는 것을 방지하고 접촉저항을 감소시킬 수 있다.

**대표도**

도 3a

**색인어**

패드부, 그로스 테스트

**명세서**

**도면의 간단한 설명**

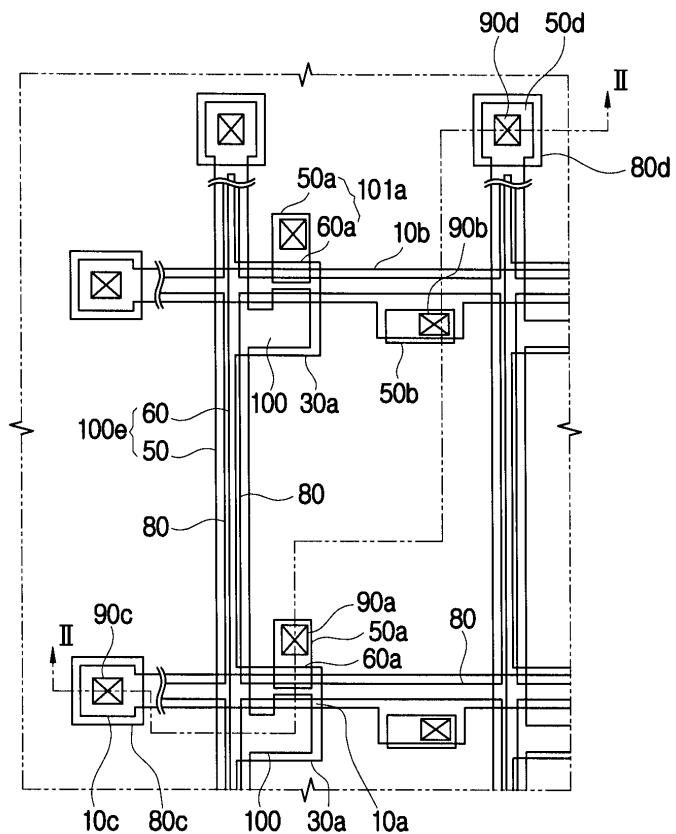

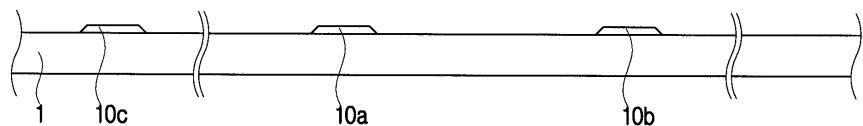

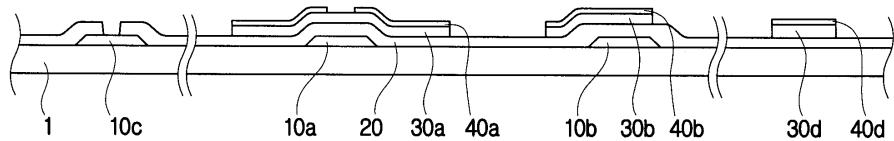

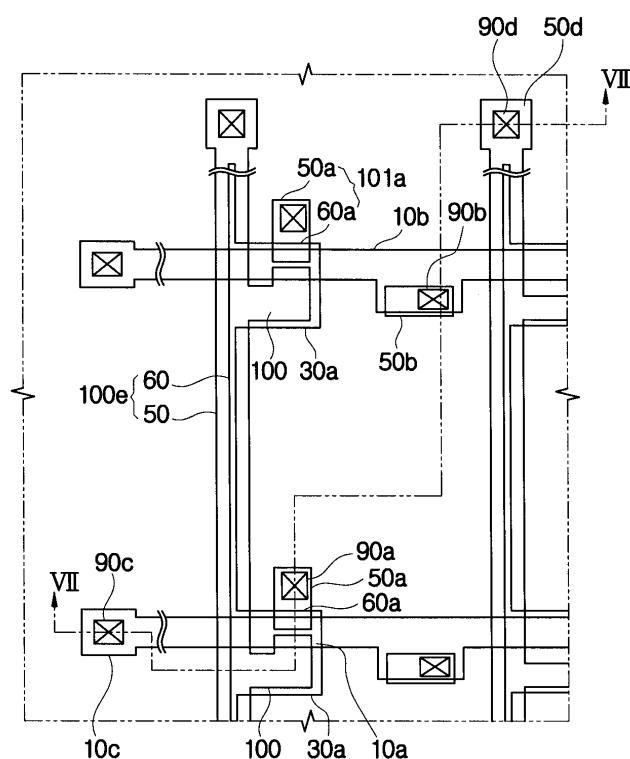

도 1은 본 발명의 실시예에 따른 액정표시장치용 박막 트랜지스터 어레이 기판,

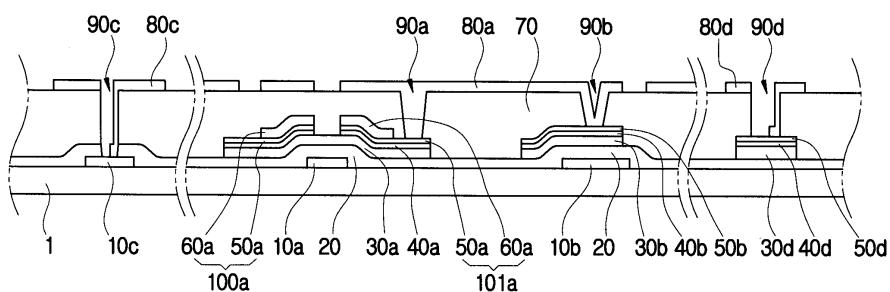

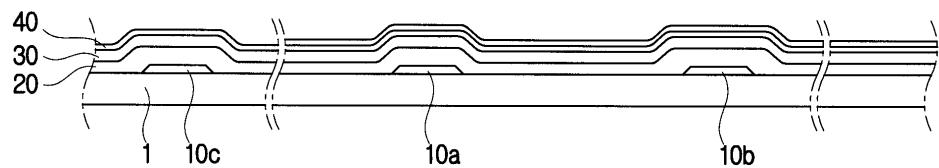

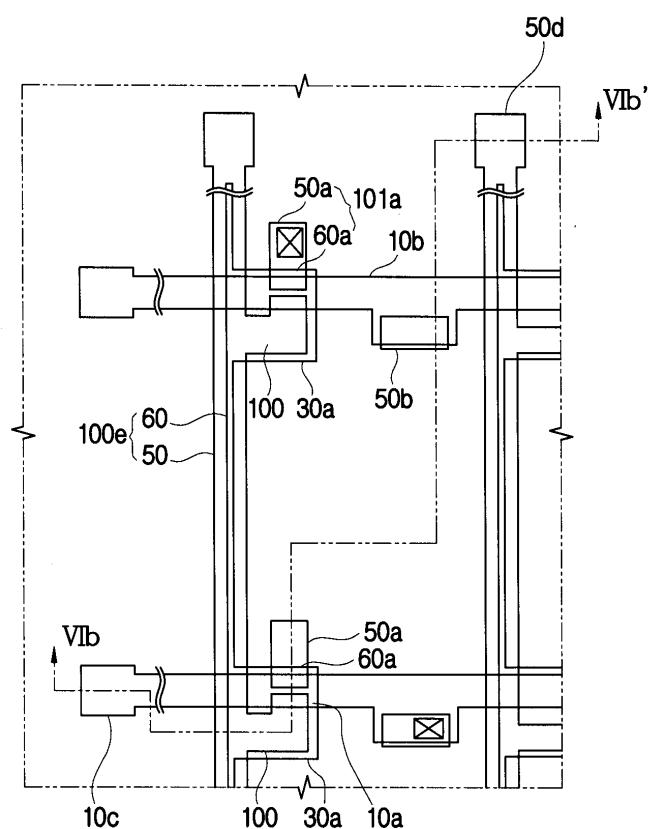

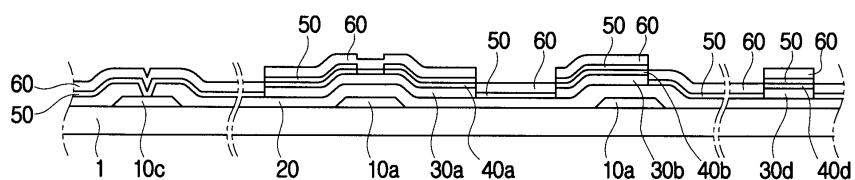

도 2는 도 1에 도시한 박막 트랜지스터 어레이 기판을 II-II' 선을 따라 잘라 도시한 단면도,

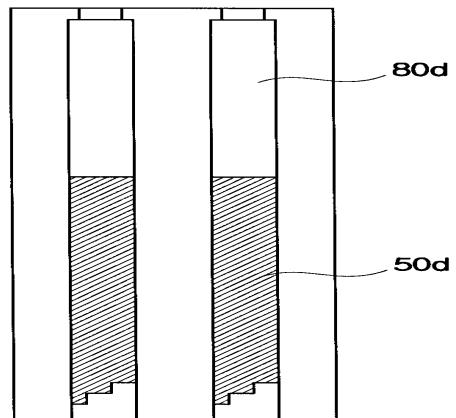

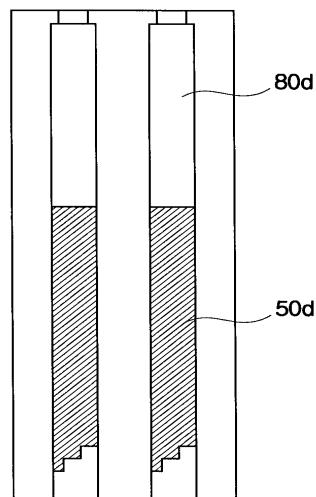

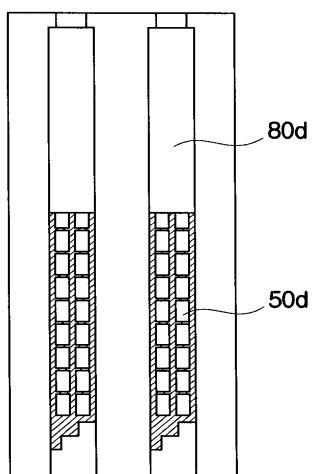

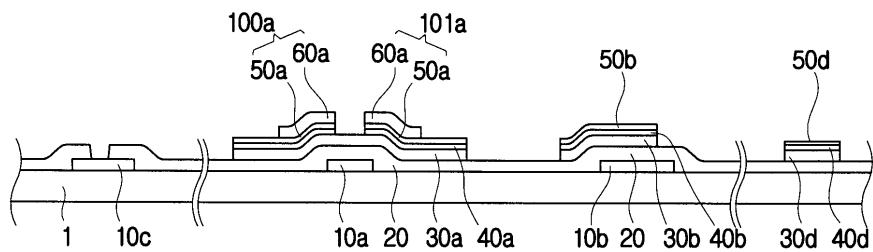

도 3(a)와 도 3(b)는 하부금속층의 상면이 각각 띠 형상 및 격자구조를 갖는 데이터 패드부의 상면도,

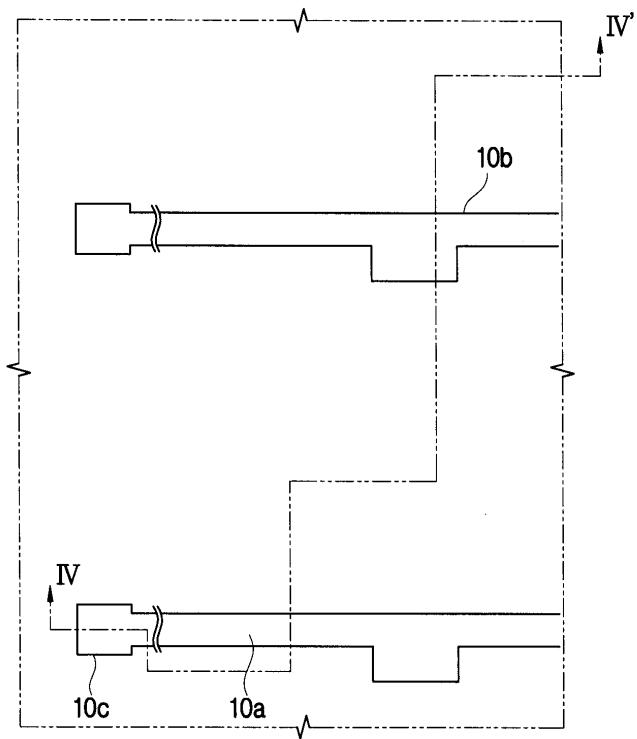

도 4(a)는 각각 테이퍼 구조의 게이트 배선을 형성하는 공정단계를 나타내는 어레이 기판의 평면도,

도 4(b)는 도 4(a)에 도시한 박막 트랜지스터 어레이 기판을 IV-IV' 선을 따라 잘라 도시한 단면도,

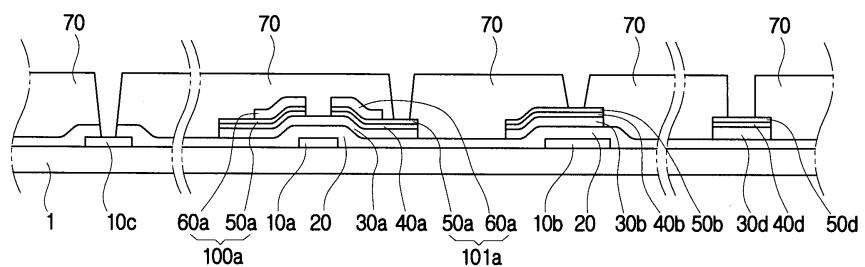

도5(a) 및 도5(b)는 각각 게이트 절연층, 반도체층, 저항성 접촉층을 형성하는 공정단계를 나타내는 단면도, 도6(a)는 각각 데이터 배선을 형성하는 공정단계를 나타내는 박막 트랜지스터 어레이 기판의 평면도, 적층 후의 단면도, 도6(b) 및 도6(c)는 각각 적층 및 식각 후의 도6(a)에 도시된 박막 트랜지스터 어레이 기판을 VI-VI`을 따라 잘라 도시한 단면도, 도7(a)는 각각 보호막을 형성하는 공정단계를 설명하기 위한 기판의 평면도, 도7(b)는 도7(a)에 도시한 박막 트랜지스터 어레이 기판을 VII-VII` 선을 따라 잘라 도시한 단면도이다.

\* 도면의 주요부분에 대한 부호의 설명

1 : 절연기판 10 : 게이트 배선

20 : 절연층 30 : 반도체층 패턴

40 : 저항성 접촉층 50 : 하부막

60 : 상부막 70 : 보호막

80 : 투명전도층 90 : 접촉구멍

100a : 소스전극 101a : 드레인 전극

100e : 데이터선

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정표시장치 및 그 제조방법에 관한 것이다.

액정표시장치는 컴퓨터 모니터 및 TV에 있어서 CRT 브라운관을 대체하면서 가장 널리 사용되고 있는 평판 표시 장치 중 하나이다.

액정표시장치는 전극이 형성되어 있는 두 장의 기판과 그 사이에 삽입되어 있는 액정층 및 컬러필터를 가지며, 전극에 인가된 전압에 의해 액정층의 액정 분자들을 재배열시킴으로써 컬러필터를 투과되는 빛의 양을 조절하는 표시 장치이다.

현재 주로 사용되는 액정표시장치는 기판의 전극에 인가되는 전압을 스위칭하는 박막 트랜지스터를 가지고 있는 능동형 액정 표시 장치이며, 박막 트랜지스터는 두 기판 중 어느 하나에 형성되는 것이 일반적이다.

트랜지스터는 영상신호와 스위칭 신호를 각각 전달하기 위한 데이터 배선과 게이트 배선에 연결되어 있으며, 이러한 배선은 신속하고 안정적인 신호 전달을 위해서 저 저항 금속물질이 사용된다.

이러한 데이터 배선 및 게이트 배선의 끝단에는 외부로부터 신호를 전달하는 구동 IC가 장착되는 패드부가 형성된다.

패드부는 금속층 위에 투명한 도전 물질인 ITO(indium tin oxide) 또는 IZO(indium zinc oxide)의 투명전도층이 적층된 구조를 갖는다. 이러한 투명전도층은 구동 IC를 장착함에 있어서 우수한 접착성을 가지며, 금속층이 공정단계에서 하층으로부터 분리되는 것을 방지하는데 효과적이다.

최근 액정표시장치의 배선으로 낮은 저항의 알루미늄 금속을 사용하면서, 투명전도 물질 중에서도 약산으로 식각이 가능한 IZO가 ITO에 비하여 공정상 보다 유리한 것으로 알려졌다.

그런데 IZO는 화학적으로 안정하지 못한 비정질의 상태이기 때문에 막의 표면에 맹글링 본드(dangling bond)가 형성되고, 상온에 존재하는 수분들과 반응하여 수산화기(-OH)와 같은 물질이 결합하기가 쉽다.

이러한 IZO의 특성은 액정주입 후 FAB, 액정, 컬러필터 불량을 관리하기 위한 그로스 테스트과정에서 프로브 펀에 이물이 부착되는 현상을 발생시키고, 접촉 횟수가 증가 할수록 이물질의 부착을 더욱 심화시켰다.

이로 인하여 패드부와 프로브 핀 사이에 접촉이 잘 안되거나, 접촉저항이 증가하여 전기적인 특성을 확인할 때 제대로 확인할 수 없을 정도로 라인성 얼룩이 생겨나는 현상(이하 "비내림 현상"이라고 한다.)이 발생하였다. 또한 프로브 핀으로부터 트랜지스터로 인가되어야 할 신호가 정상적으로 전달되지 않는 문제가 발생할 수 있었다.

### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 그로스 테스트를 수행할 때 패드부와 프로브 핀 사이의 접촉 불량을 방지하고 및 접촉저항을 개선한 액정표시장치 및 그 제조방법을 제공하는 것이다.

### 발명의 구성 및 작용

상기 목적은, 본 발명에 따라, TFT 기판의 가장자리에 금속층과 상기 금속층의 상층에 투명전도층을 갖는 액정표시장치에 있어서, 상기 투명전도층은 상기 금속층의 상면을 노출시키는 개방부를 갖는 것을 특징으로 하는 액정표시장치에 의해 달성될 수 있다.

여기서 상기 개방부는 상기 금속층의 상면을 띠 형상 또는 격자구조로 노출시키는 것으로 할 수 있다.

그리고 상기 액정표시장치에 있어서 상기 투명전도층은 IZO로 하고, 상기 금속층은 상기 박막 트랜지스터의 소스단자 또는 게이트단자에 각각 연결된 데이터 배선 또는 게이트 배선인 것이 바람직하다.

또한 상기 목적은, 본 발명의 다른 분야에 따라, 액정표시장치의 제조방법에 있어서, 전기전도를 위한 금속층을 형성하는 단계와, 상기 금속층의 상면에 접촉 가능하도록 하는 접촉구멍을 갖는 절연층을 형성하는 단계와, 상기 접촉구멍의 일부에 상기 금속층의 상면이 노출되도록 투명전도층을 형성하는 단계를 포함하는 것을 특징으로 하는 액정표시장치의 제조방법에 의해서도 달성될 수 있다.

여기서, 상기 접촉구멍의 일부에 상기 금속층의 상면이 노출되도록 투명전도층을 형성하는 단계에서 상기 금속층의 상면이 띠 모양 또는 격자모양으로 노출되는 것으로 할 수 있다.

그리고 상기 액정표시장치의 제조방법에 있어서 상기 투명전도층은 IZO로 하고, 상기 금속층은 상기 박막 트랜지스터의 소스단자 또는 게이트단자에 각각 연결된 데이터 배선 또는 게이트 배선인 것이 바람직하다.

도 1은 본 발명의 실시예에 따른 액정표시장치용 박막 트랜지스터 어레이 기판이고, 도 2는 도 1에 도시한 박막 트랜지스터 어레이 기판을 II-II' 선을 따라 잘라 도시한 단면도이다.

도 1의 박막 트랜지스터 어레이 기판은 도2의 단면을 통해 대략 ① 기판, ② 게이트 배선(10), ③ 절연층(20), ④ 반도체층(30), ⑤ 저항성 접촉층(40), ⑥ 하부 금속막(50), ⑦ 상부 금속막(60), ⑧ 보호층(70) 및 ⑨ 투명전도층(80)의 순서로 적층되어 있음을 알 수 있다.

이하, 상기한 적층 순서에 따라 본 발명에 따른 박막 트랜지스터 어레이 기판의 특징을 설명한다.

먼저, 절연기판(1) 위에 낮은 저항을 가지는 은, 은 합금, 알루미늄 또는 알루미늄 합금의 금속 물질로 이루어진 도전막을 포함하는 게이트 배선(10)이 형성되어 있다.

게이트 배선(10)은 그 기능에 따라 게이트선(10b), 게이트 패드(10c) 및 게이트 전극(10a)으로 구분된다.

게이트선(10b)은 박막 트랜지스터의 게이트 단자에 입력되는 스위칭 신호를 전달하는 금속층이며, 게이트 패드(10c)는 게이트선(10b)의 끝부분으로서 외부로부터 상술한 스위칭 신호를 입력받는 금속층이다.

게이트 전극(10a)은 박막 트랜지스터의 게이트 단자의 금속층으로서 게이트선(10b)을 통해서 게이트 패드(10c)에서 입력된 제어신호를 입력받는다. 여기서, 게이트선(10b)은 후술할 화소 전극(80)과 연결된 유지 축전기용 도전체 패턴(50b)과 연속층을 이루면서 화소의 전하 보존 능력을 향상시키는 유지 축전기를 구성한다.

게이트 배선(10)과 기판(110) 위에 질화규소(SiNx) 따위로 이루어진 게이트 절연막(20)이 형성되어 있다.

게이트 전극(10a) 및 유지 축전기의 게이트선(10b)의 상부와, 후술할 데이터 패드의 접촉구멍(90d) 하부의 절연기판(1) 바로 위에 반도체층 패턴(30a, 30b, 30d) 및 저항성 접촉층(40a, 40b, 40d)이 순차적으로 형성되어 있다.

여기서, 반도체층 패턴(30)은 비정질 규소(a-Si) 등의 반도체로 구성된 것이며, 저항성 접촉층(40)은 실리사이드 또는 n형 불순물이 고농도로 도핑된 n+ 수소화 비정질 규소 따위의 물질로 만들어진다.

저항성 접촉층(40a, 40b, 40c) 위에 데이터 배선(50, 60)이 형성된다.

데이터 배선(50, 60)은 구조적으로 하부막(50)과 상부막(60)의 이중구조를 가지며, 기능적으로 데이터선(100e), 소스전극(100a), 드레인 전극(101a), 데이터 축전기용 데이터 패턴(50b) 및 데이터 패드(50d)로 구분된다.

상부막(60)으로 낮은 저항의 금속인 알루미늄(Al) 또는 알루미늄 합금(Al alloy)이 주로 사용되고, 하부막(50)으로는 알루미늄 또는 알루미늄 합금의 확산을 막기 위한 배리어 금속(barrier metal)이 사용된다. 이러한 배리어 금속으로는 몰리브덴(Mo) 또는 몰리브덴-텅스텐(MoW) 합금, 크롬(Cr), 탄탈륨(Ta), 티타늄(Ti) 등이 사용될 수 있다.

데이터선(100e)은 데이터 신호의 전달을 위한 금속층으로서, 도1에 도시된 바와 같이 세로 방향으로 형성되어 있으며, 게이트선(10b)과 교차하여 격자구조의 화소를 형성한다.

소스전극(100a)은 데이터선(100e)의 분지로서 박막트랜지스터의 소스단자의 역할을 수행한다. 드레인 전극(101a)은 소스전극(100a)과 분리되어 게이트 전극(10a)에 중심으로 대칭적으로 형성되고 게이트 전극(10a)의 스위칭 신호에 따라 소스전극(100a)에 인가된 신호를 후술할 화소전극(190)에 전달한다.

데이터 패드(50d)는 데이터선(100e)의 일측의 끝 부분에 형성되어 외부의 구동 IC로부터 화상신호 등을 인가받고 데이터선(100e)을 통해 소스전극(100a)으로 전달한다.

데이터 배선(50,60), 저항성 접촉층(40) 및 반도체층(30)의 패턴은 유사한 구조를 갖고 있다. 즉, 저항성 접촉층(40a,40b,40d)은 데이터 배선(50,60)의 접촉저항을 낮추어 주는 역할을 하기 때문에 각각의 상부에 위치하는 데이터 배선(50,60)의 하부막(50a,50b,50d)과 동일한 형태를 갖고 있다.

데이터 배선(50,60)에서 데이터 패드(50d) 및 데이터 축전기용 패턴(50b)은 하부막(50)으로만 구성되어 있으며, 드레인 전극(101a)은 상부막(60)의 일부가 제거된 형태를 갖는다. 이는 접촉성이 우수한 하부막(50)이 후술할 접촉구멍(90a,90b,90c,90d)을 통해 다른 물질과 직접 접촉되도록 하기 위한 것이다.

데이터 배선(50,60) 및 이들이 형성되지 않은 절연막(20) 상부에 보호막(70)이 형성되어 있다.

보호막(70)은 게이트 절연막(20)과 같은 질화규소를 사용할 수 있으며, 보호막(70)의 상면에 평탄화 특성, 감광성이 우수한 유기물질 또는 저유전율의 유기물질을 코팅하거나 증착한다.

게이트 패드(10c)와 데이터 배선(50,60) 중 적어도 일부에 상부막(60)을 갖지 않는 드레인 전극(101a), 유지 축전기용 데이터 패턴(50b) 및 데이터 패드(50d)에 형성된 보호막(70)은 그 상부에 형성되는 투명전도층(80c,80a,80b,80d)이 하부금속층(10c,50a,50b,50d)에 접촉하기 위한 접촉구멍(90c,90a,90b,90d)을 갖고 있다.

다음으로 보호막(70) 및 접촉구멍(90)의 상부에는 투명전도층(80)이 형성되는데, 투명전도층(80)은 그 기능에 따라 화소전극(80a)과 접촉부(80c,80d)로 구분된다.

화소전극(80a)은 박막트랜지스터의 드레인 전극(101a)과 연결되어 게이트 전극(10a)의 스위칭 신호 및 소스전극(100a)의 데이터 신호에 따라 화상신호를 받고 상판 전극과 함께 전기장을 형성한다. 또한 화소전극(80a)은 접촉구멍(90b)을 통하여 유지 축전기용 도전체 패턴(50b)과도 연결되어 화상신호를 전달한다.

접촉부(80c,80d)는 접촉구멍을 통하여 게이트 전극(10a) 및 데이터 패드와 직접 연결되어 있으며, 외부 구동 IC 및 프로브핀과의 접촉을 보완하고 하부의 금속층을 보호하는 역할을 한다. 이 때, 하부의 금속층(50d)과 접촉하는 투명전도층(80d)의 단면이 불연속된 것을 볼 수 있는데, 불연속부분(이하 "개방부"라고 한다.)에서 하부 금속이 외부에 직접 노출되는 것을 볼 수 있다.

투명전도층(80)은 IZO 또는 ITO 등의 투명한 전도물질로 이루어져 있으며, 배선에 낮은 저항의 알루미늄 또는 그 합금을 사용하는 추세에 따라 약산으로 에칭이 가능한 IZO의 사용이 더 일반화되고 있다. 이외에도 투명한 도전성 폴리머(polymer) 등으로 화소전극(80a)을 형성할 수 있으며 반사형 액정표시장치에서는 불투명한 도전물질의 사용도 가능하다.

이하, 게이트 패드부와 데이터 패드부를 중심으로 본 발명의 실시예를 구체적으로 설명한다.

도2에 도시된 바와 같이, 게이트 패드부는 절연기판(1), 게이트 패드(10c) 및 투명전도층(80c)이 순차적으로 적층된 구조를 갖는다.

한편 데이터 패드부는 절연기판(1), 절연층(20), 반도체층 패턴(30), 저항성 접촉층 패턴(40), 데이터 배선의 하부막(50) 및 투명전도층(80d)이 순차적으로 적층된 구조이다.

도3(a)는 하부금속층(50d)의 상면이 각각 띠 형상 및 격자구조를 갖는 데이터 패드부의 상면도이다. 이 때, 띠 형상을 대신하여 투명전도층(80d)의 개방부가 하부금속층(50d)의 상면이 격자구조를 갖도록 할 수 있으며, 도3(b)는 하부금속층(50d)의 상면이 격자 구조를 갖는 경우를 도시한 것이다.

도3(a)의 패드부는 일부 투명전도층(80)이 제거된 개방부에서 하부막(50)이 상면에 직접 노출되어 있으며 띠 형상을 갖는 것을 볼 수 있다. 한편 도3(b)의 패드부는 투명전도층(80)이 제거된 개방부에서 하부막(50)의 노출형태가 격자구조를 갖는 것을 볼 수 있다.

투명전도층(80)의 재질을 IZO로 하고 블레이드(blade) 방식의 그로스 테스트를 실시한 결과, 도3(a)의 띠 형상의 개방구조가 도3(b)의 격자구조 보다 더 우수한 접촉 성능을 보여주었다.

구체적으로 도3(a)의 띠 형상의 개방구조는 프로브 펈의 미접촉 발생빈도와 패드의 손상이 가장 적었고 비내림 현상이 나타나지 않았다.

한편 도3(b)의 격자구조의 패드부는 기준의 IZO 층만이 노출되는 폐쇄구조에 비하여 상당히 개선된 펈 미접촉 발생빈도를 보였고, 비내림 현상이 미약하게 발생하였다. 약 50회의 테스트 반복 후에 비내림 현상이 증가하였지만, 격자구조의 개방부가 띠구조를 갖는 개방부에 비하여 하부 금속층의 보호에 보다 충실할 수 있는 장점을 가진다.

도3(a) 및 도3(b)에 도시된 테이터 패드부의 구조는 하부 금속층(50d)를 대신하여 게이트 패드(10c)가 노출되는 구조로 게이트 패드부에 동일하게 적용할 수 있음은 물론이다.

이하 도4 내지 도8을 참조하여 본 발명의 실시예에 따른 박막 트랜지스터 어레이 기판의 제조 방법을 상세히 설명한다.

도4(a)와 도4(b)에 도시한 바와 같이, 절연기판(1) 상부에 낮은 저항의 금속인 알루미늄 또는 알루미늄 합금을 적층하고, 마스크를 이용한 사진 식각공정으로 패터닝(patterning)하여 게이트 배선(10)을 테이퍼 구조로 형성한다.

다음으로, 도5(a)에서 볼 수 있는 바와 같이, 절화규소의 절연막(20), 비정질 규소의 반도체층(30), 도핑된 비정질 규소의 저항성 접촉층(40)을 적층한다. 여기서, 게이트 절연막(20)은 절화규소를 250~400[°C]의 온도 범위, 2,000~5,000[°C] 정도의 두께로 적층하여 형성하는 것이 바람직하다.

반도체층 패턴 마스크를 사용하여 사진 식각 공정을 실시하여 도5(b)와 같은 반도체층(30) 및 저항성 접촉층(40)의 패턴을 형성한다. 이 때, 식각은 건식 식각 방법을 사용하고, 노출된 반도체층 패턴(30)의 표면을 안정화시키기 위하여 산소 플라스마를 실시하는 것이 바람직하다.

다음 공정으로, 도6(b)에 도시된 바와 같이, 테이터 배선(50,60)을 형성하기 위한 하부막(50) 및 상부막(60) 금속을 스퍼터링(sputtering)을 통해 적층한다.

이 때, 하부막(50)은 낮은 저항 특성을 갖기 위하여 상부막(60)으로 사용되는 알루미늄의 확산을 방지하고, 접촉특성이 우수한 배리어 금속 중에서 몰리브덴 또는 크롬 등을 약 500[°C] 정도로 적층한다.

상부막(60)은 알루미늄 또는 알루미늄 합금 중 2[wt%]의 네오디뮴(Nd)을 포함하는 Al-Nd 합금의 표적을 150[°C] 정도의 온도에서 스퍼터링(sputtering) 하여 2,500[°C] 정도의 두께로 적층한다.

이어, 도6(a)와 도6(c)에 도시한 바와 같이 테이터 배선(50,60)용 마스크를 이용한 사진 식각 공정으로 상부막(60)을 패터닝(patterning)하고 테이터 배선(50,60)을 형성한다.

여기서, 금속층으로 이루어진 테이터 배선(50,60)은 습식으로 식각하는 것이 일반적이다. 그러나 하부막(50)은 건식으로 식각할 수 있으며, 하부막(50)이 몰리브덴 또는 몰리브덴 합금막인 경우에는 하부막(50)과 상부막(60)을 하나의 식각 조건으로 패터닝 할 수 있다.

테이터 배선(50,60)의 형성에 있어서, 접촉구멍(90)이 형성되는 테이터 패드(50d), 드레인 전극(101a) 및 유지 축전기용 도전체 패턴(50b)의 상면이 식각에 의해 노출되도록 슬릿 마스크를 사용하여 감광막 패턴을 형성할 수도 있다. 그리고 습식으로 식각을 진행하는 경우 채널부의 반도체층(30a)이 식각되는 것을 방지하기 위해서 스토퍼(stopper)막을 채널부에 형성하여 식각할 수도 있다.

다음으로, 보호막(70)을 적층하고 도7에 도시된 바와 같이 건식 식각으로 접촉구멍(90)을 갖도록 보호막(70)을 형성한다. 이 때, 보호막(70)의 상면에 평탄화 특성, 감광성이 우수한 유기물질 또는 저유전율의 유기물질을 코팅 또는 증착할 수 있다.

다음, 마지막으로 도 1 및 2에 도시한 바와 같이, IZO막을 스퍼터링으로 적층하고 마스크를 이용한 패터닝을 실시하여 화소전극(80a) 및 접촉부(80c,80d)를 형성한다. 여기서 IZO막은 접촉저항을 최소로 하기 위해서 250°C 이하의 범위에서 적층하는 것이 바람직하다.

이 때, 접촉부(80c,80d)인 드레인 전극(101a) 및 유지 축전기용 도전체 패턴(50b)의 하부막(50)을 드러내는 접촉 구멍(90)에서 언더컷(undercut)이 발생하지 않아 단선되지 않는다. 또한 IZO막(80)은 낮은 접촉 저항을 가지는 하부막(50)과 충분히 접하고 있어 접촉부(80c,80d)의 접촉 저항을 최소화 할 수 있다.

IZO 막(80)은 접촉구멍에서 도3에 도시된 바와 같이 띠 형태 또는 격자구조의 개방구조를 갖도록 패터닝 하도록 한다. 이에 의해 그로스 테스트를 수행할 때 프로브 펈이 하부막(50)에 직접 접촉이 가능하게 된다.

본 발명의 실시예에서 IZO막(190, 92, 97)을 형성하기 위한 표적(target)은 이데미츠(idemitsu)사의 IDIXO(indium x-metal oxide)라는 상품을 사용하였으며, 표적은 In2O3 및 산화아연(ZnO)를 포함하고 In+ Zn에서 아연(Zn)의 함유량은 15-20[wt%] 범위로 하는 것이 바람직하다.

이상에서 본 발명의 바람직한 실시예에 대하여 상세하게 설명하였지만 본 발명의 권리범위는 이에 한정되는 것은 아니고 다음의 청구범위에서 정의하고 있는 본 발명의 기본 개념을 이용한 당업자의 여러 변형 및 개량 형태 또한 본 발명의 권리범위에 속하는 것이다.

### 발명의 효과

본 발명에 의해 그로스 테스트를 수행할 때 패드부와 프로브 핀 사이의 접촉이 안 되는 것을 방지하고 접촉저항을 감소시킬 수 있다.

### (57) 청구의 범위

#### 청구항 1.

TFT 기판의 가장자리에 금속층과 상기 금속층의 상층에 투명전도층을 갖는 액정표시장치에 있어서,

상기 투명전도층은 상기 금속층의 상면을 노출시키는 개방부를 갖는 것을 특징으로 하는 액정표시장치.

#### 청구항 2.

제1항에 있어서,

상기 개방부는 띠 형상으로 상기 금속층의 상면을 노출시키는 것을 특징으로 하는 액정표시장치.

#### 청구항 3.

제1항에 있어서,

상기 개방부는 상기 금속층의 상면을 격자구조로 노출시키는 것을 특징으로 하는 액정표시장치.

#### 청구항 4.

제1항 내지 제3항에 있어서,

상기 투명전도층은 IZO인 것을 특징으로 하는 액정표시장치.

#### 청구항 5.

제1항 내지 제3항에 있어서,

상기 금속층은 상기 TFT기판의 박막 트랜지스터의 소스단자와 연결된 데이터 배선인 것을 특징으로 하는 액정표시장치.

#### 청구항 6.

제1항 내지 제3항에 있어서,

상기 금속층은 상기 TFT기판의 박막 트랜지스터의 게이트 단자와 연결된 게이트 배선인 것을 특징으로 하는 액정표시장치.

#### 청구항 7.

액정표시장치의 제조방법에 있어서,

전기전도를 위한 금속층을 형성하는 단계와,

상기 금속층의 상면에 접촉 가능하도록 하는 접촉구멍을 갖는 절연층을 형성하는 단계와,

상기 접촉구멍의 일부에 상기 금속층의 상면이 노출되도록 투명전도층을 형성하는 단계를 포함하는 것을 특징으로 하는 액정표시장치의 제조방법.

### 청구항 8.

제7항에 있어서,

상기 접촉구멍의 일부에 상기 금속층의 상면이 노출되도록 투명전도층을 형성하는 단계에서 상기 금속층의 상면이 떠 모양으로 노출되는 것을 특징으로 하는 액정표시장치의 제조방법.

### 청구항 9.

제7항에 있어서,

상기 접촉구멍의 일부에 상기 금속층의 상면이 노출되도록 투명전도층을 형성하는 단계에서 상기 금속층의 상면이 격자구조로 노출되는 것을 특징으로 하는 액정표시장치의 제조방법.

### 청구항 10.

제7항 내지 제9항에 있어서,

상기 투명전도층은 IZO인 것을 특징으로 하는 액정표시장치의 제조방법.

### 청구항 11.

제7항 내지 제9항에 있어서,

상기 금속층은 상기 박막 트랜지스터의 소스단자와 연결된 데이터 배선인 것을 특징으로 하는 액정표시장치의 제조방법.

### 청구항 12.

제7항 내지 제9항에 있어서,

상기 금속층은 상기 박막 트랜지스터의 게이트 단자와 연결된 게이트 배선인 것을 특징으로 하는 액정표시장치의 제조방법.

도면

## 도면1

## 도면2

도면3a

도면3b

도면4a

도면4b

도면5a

도면5b

도면6a

도면6b

도면6c

도면7a

도면7b

|                |                                                                                                                                       |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">KR1020050040283A</a>                                                                                                      | 公开(公告)日 | 2005-05-03 |

| 申请号            | KR1020030075447                                                                                                                       | 申请日     | 2003-10-28 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                                                                              |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                                                                                              |         |            |

| [标]发明人         | CHO HONGJE<br>조홍제<br>JEONG CHANGOH<br>정창오<br>LEE YOUNKRAE<br>이육래<br>CHOI DONGUK<br>최동욱<br>KIM YOUNGSUN<br>김영선<br>KANG SUNGCHUL<br>강성철 |         |            |

| 发明人            | 조홍제<br>정창오<br>이육래<br>최동욱<br>김영선<br>강성철                                                                                                |         |            |

| IPC分类号         | G02F1/136                                                                                                                             |         |            |

| 代理人(译)         | PARK , YOUNG WOO                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                             |         |            |

#### 摘要(译)

本发明涉及液晶显示装置及其制造方法。并且本发明的液晶显示器具有开口，其中透明导电层暴露金属层的上侧，关于在TFT边缘中的金属层的上层中具有透明导电层的液晶显示器。基材和金属层。当用此进行粗略测试时，它防止探针和焊盘部分之间的接触不良并且可以减小恒定电阻。垫部分和粗略测试。