# (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) Int. Cl.

#### **GO2F 1/136** (2006.01)

(21) 출원번호 10-2002-0052660

(22) 출원일자 **2002년09월03일** 심사청구일자 **2007년08월22일**

(65) 공개번호10-2004-0021169(43) 공개일자2004년03월10일

(56) 선행기술조사문헌 JP13059191 A\* KR1020010057663 A\* JP06235927 A\* JP04217322 A\* (45) 공고일자 2008년11월05일

(11) 등록번호 10-0866976 (24) 등록일자 2008년10월29일

(73) 특허권자

#### 엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

#### 황용섭

경기도 수원시 장안구 정자2동 동신아파트 207-804

#### 채기성

인천광역시 연수구 동춘동 한양1차 111동 607호

#### 조규철

경기도 군포시 산본동 1155 가야아파트 512-901

(74) 대리인

특허법인네이트

전체 청구항 수 : 총 8 항

심사관 : 임동재

### (54) 액정표시장치용 어레이기판과 제조방법

\*는 심사관에 의하여 인용된 문헌

#### (57) 요 약

본 발명은 액정표시장치에 관한 것으로 특히, 액정표시장치용 어레이기판과 그 제조방법에 관한 것이다.

본 발명에서 제안하는 제 1 구조는, 게이트 전극일 경우에는 기판과 접촉특성이 양호한 금속(Ti,Ta,Mo,Cr,W,Ni)과 구리의 이중 금속층으로 형성하고, 소스/드레인 전극일 경우에는 하부 오믹콘택층과 구리와의 반응을 막을 수 있는 금속(Ti,Ta,Mo,Cr,W,Ni)의 이중 금속층으로 형성한다.

본 발명에서 제안하는 제 2 구조는 상기 제 1 구조에서 기판의 전면에 절연막으로 보호층을 더욱 형성하는 구조이다.

이때, 게이트 전극일 경우에는 기판과 밀착성이 좋은 금속(Ti,Ta,Mo,Cr,W,Ni)과 구리의 이중금속층으로 형성하고, 소스/드레인 전극일 경우에는 하부 오믹콘택층과 구리와의 반응을 막을 수 있는 금속(Ti,Ta,Ti,Ta,Mo,Cr,W,Ni)의 이중 금속층으로 형성한다.

전술한 바와 같이 구리를 포함한 이중 금속층로 게이트 및 드레인 전극을 형성하면, 공정지연을 방지할 수 있고 박막트랜지스터의 동작 특성을 개선할 수 있어 제품의 수율을 향상할 수 있다.

### 대 표 도 - 도6e

#### 특허청구의 범위

#### 청구항 1

기판 상의 보호층과;

상기 보호층 상에 구성되고, 구리와 제 1 금속 버퍼층의 이중층으로 구성된 게이트 전극과, 게이트 전극과 연결된 게이트 배선과, 게이트 배선에서 연장된 게이트 패드 전극과;

상기 게이트 전극과 게이트 배선과 게이트 패드 전극 상부에 구성된 제 1 절연막과;

상기 게이트 전극 상부의 제 1 절연막 상에 적충되어 구성된 액티브층과 오믹 콘택층과;

상기 오믹 콘택층과 접촉하고, 구리와 제 2 금속 버퍼층의 이중층으로 구성된 소스 및 드레인 전극과 소스전극과 연결된 데이터배선과 데이터 배선에서 연장된 데이터 패드 전극과;

상기 소스전극과 드레인 전극과 데이터 배선이 형성된 기판의 전면에 구성되고, 상기 드레인 전극과, 게이트 패드 전극과 데이터 패드 전극을 각각 노출하는 보호막과;

상기 노출된 드레인 전극과 접촉하는 투명 화소전극과, 게이트 패드 전극과 접촉하는 투명 게이트 패드 전극단 자와, 데이터 패드 전극과 접촉하는 투명 데이터 패드 전극단자;

을 포함하는 액정표시장치용 어레이기판.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

삭제

### 청구항 5

제 1 항에 있어서,

상기 제 2 금속층을 형성하는 물질은 탄탈륨(Ta), 티타늄(Ti),크롬(Cr), 몰리브덴(Mo), 니켈(Ni), 텅스텐(W)으로 구성된 금속그룹중 선택된 하나인 액정표시장치용 어레이기판.

#### 청구항 6

삭제

#### 청구항 7

삭제

#### 청구항 8

삭제

#### 청구항 9

제 1 항에 있어서,

상기 보호층은 질화 실리콘( $SiN_X$ )과 산화 실리콘( $SiO_2$ )을 포함하는 무기절연물질 그룹 중 선택된 하나 또는 벤조 사이클로부텐(BCB)과 아크릴(acryl)계 수지(resin)를 포함한 유기절연물질그룹 중 선택된 하나 또는 이중층으로 구성된 액정표시장치용 어레이기판.

#### 청구항 10

삭제

#### 청구항 11

제 1 항에 있어서,

상기 제 1 금속 버퍼층을 형성하는 물질은 탄탈륨(Ta), 티타늄(Ti), 크롬(Cr), 몰리브덴(Mo), 니켈(Ni), 텅스텐(W)으로 구성된 금속 그룹 중 선택된 하나인 액정표시장치용 어레이기판.

#### 청구항 12

기판 상에 보호층을 형성하는 단계와;

상기 보호층 상에, 구리와 제 1 금속 버퍼층의 이중층으로 구성된 게이트 전극과, 게이트 전극과 연결된 게이트 배선과, 게이트 배선에서 연장된 게이트 패드 전극을 형성하는 단계와;

상기 게이트 전극과 게이트 배선과 게이트 패드 전극 상부에 제 1 절연막을 형성하는 단계와;

상기 게이트 전극 상부의 제 1 절연막 상에 액티브층과 오믹 콘택층을 형성하는 단계와;

상기 오믹 콘택층과 접촉하고, 구리와 제 2 금속 버퍼층의 이중층인 소스 및 드레인 전극과 소스전극과 연결된 데이터배선과 데이터 배선에서 연장된 데이터 패드 전극을 형성하는 단계와;

상기 소스전극과 드레인 전극과 데이터 배선이 형성된 기판의 전면에, 상기 드레인 전극과, 게이트 패드 전극과 데이터 패드 전극을 각각 노출하는 보호막을 형성하는 단계와;

상기 노출된 드레인 전극과 접촉하는 투명 화소전극과, 게이트 패드 전극과 접촉하는 투명 게이트 패드 전극 전극단자와, 데이터 패드 전극과 접촉하는 투명 데이터 패드 전극단자를 형성하는 단계;

를 포함하는 액정표시장치용 어레이기판 제조방법.

#### 청구항 13

삭제

### 청구항 14

삭제

#### 청구항 15

삭제

#### 청구항 16

제 12 항에 있어서,

상기 제 2 버퍼 금속층을 형성하는 물질은 탄탈륨(Ta), 티타늄(Ti),크롬(Cr), 몰리브덴(Mo), 니켈(Ni), 텅스텐 (W)으로 구성된 금속그룹중 선택된 하나로 형성된 액정표시장치용 어레이기판 제조방법.

#### 청구항 17

삭제

#### 청구항 18

삭제

#### 청구항 19

삭제

#### 청구항 20

제 12 항에 있어서,

상기 보호층은 질화 실리콘( $SiN_X$ )과 산화 실리콘( $SiO_2$ )을 포함하는 무기절연물질 그룹 중 선택된 하나 또는 벤조사이클로부텐(BCB)과 아크릴(acryl)계 수지(Rresin)를 포함한 유기절연물질그룹 중 선택된 하나 또는 이중층으로 형성된 액정표시장치용 어레이기판 제조방법.

#### 청구항 21

삭제

#### 청구항 22

제 12 항에 있어서,

상기 제 1 금속 버퍼층을 형성하는 물질은 탄탈륨(Ta), 티타늄(Ti), 크롬(Cr), 몰리브덴(Mo), 니켈(Ni), 텅스텐(W)으로 구성된 금속 그룹 중 선택된 하나로 형성된 액정표시장치용 어레이기판 제조방법.

#### 명 세 서

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <15> 본 발명은 액정표시장치(liquid crystal display device)에 관한 것으로, 구리를 포함한 이중 금속층으로 형성 된 게이트 전극과 소스 및 드레인 전극을 포함하는 액정표시장치용 어레이기판과 그 제조방법에 관한 것이다.

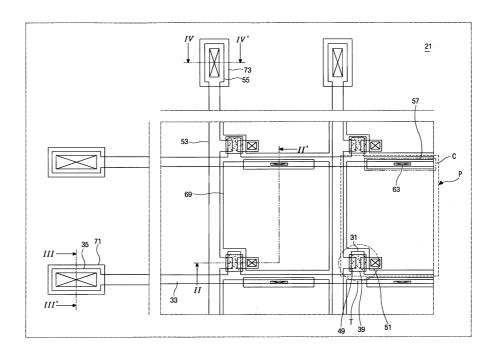

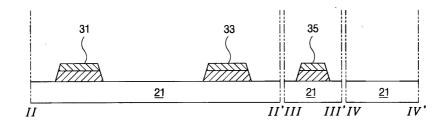

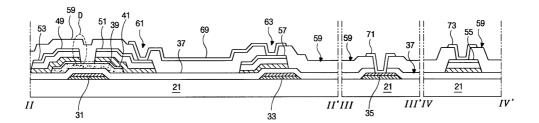

- <16> 도 1은 액정표시장치용 어레이기판의 일부를 도시한 확대평면도이다.

- <17> 기판(21)상에 스위칭 소자인 박막트랜지스터(T)가 매트릭스 형태(matrix type)로 위치하고, 이러한 다수의 박막트랜지스터(T)를 교차하는 게이트배선(33)과 데이터배선(53)이 형성된다.

- <18> 상기 게이트배선(33)의 일 끝단에는 게이트 패드 전극(35)이 형성되어 있고, 상기 게이트 패드 전극(35)은 게이트 배선(33)에 비해 큰 폭음 가지도록 구성된다.

- <19> 상기 데이터배선(53)의 일 끝단에는 데이터 패드 전극(55)이 형성되어 있고, 상기 데이터 패드 전극(55) 또한 데이터배선(53)에 비해 큰 폭을 가지도록 형성된다.

- <20> 상기 게이트 패드 전극(35)과 데이터 패드 전극(55)은 각각 외부의 신호를 직접 인가 받는 수단인 투명한 게이트 패드 전극 전극단자(71)와 데이터 패드 전극단자(73)와 접촉하여 구성된다.

- <21> 이때, 상기 게이트배선(33)과 데이터배선(53)이 교차하여 정의되는 영역을 화소영역(P)이라 한다.

- <22> 상기 게이트배선(33)의 일부 상부에 스토리지 캐패시터(C)가 구성되고, 상기 화소 영역(P)에 구성된 투명한 화소전극(69)과 회로적으로 병렬로 연결된다.

- <23> 상기 박막트랜지스터(T)는 게이트 전극(31)과 소스 전극(49)과 드레인 전극(51)과, 상기 게이트전극(31) 상부에 구성된 액티브층(39)으로 이루어진다.

- <24> 전술한 구성에서, 상기 캐패시터(C)는 게이트 배선(33)의 일부를 제 1 캐패시터 전극으로 하고, 상기 게이트 배선(33)의 일부 상부에 위치하고 상기 소스 및 드레인 전극(49,51)과 동일층 동일물질로 형성되고 상기 화소 전극(69)과 콘택홀(63)을 통해 접촉된 소스-드레인 금속층(57)을 제 2 캐패시터 전극으로 한다.

- <25> 전술한 구성 중, 상기 게이트 전극(31)과 게이트 배선(33)과 게이트 패드 전극(35)은 신호 지연을 방지하기 위해 저 저항 금속인 알루미늄(Al)(또는 알루미늄합금)을 사용하며, 알루미늄(또는 알루미늄합금)의 공정상 단점을 보완하기 위해 일반적으로는 알루미늄(또는 알루미늄합금)에 별도의 금속층을 적층하여 구성한다.

- <26> 상기 드레인 전극(51)과 데이터 배선(53)과 데이터 패드 전극(55)또한, 저항을 낮추기 위해 알루미늄을 사용하

는 경우가 있으며, 이 때에는 알루미늄(또는 알루미늄합금)의 상부와 하부에 별도의 금속층을 더욱 구성하게 된다.

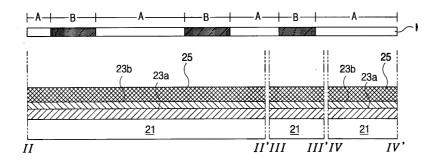

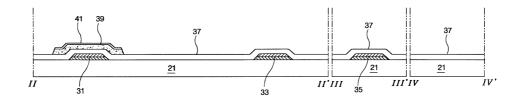

- <27> 이하, 도 2a 내지 2d와 3a 내지 도 3e를 참조하여, 종래에 따른 액정표시장치용 어레이기판의 제조공정을 설명한다.

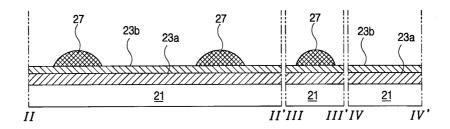

- <28> 먼저, 도 2a에 내지 도 2d는 게이트 전극과 게이트 배선과 게이트 패드 전극을 형성하는 방법을 종래의 공정순 서에 따라 도시한 공정 단면도이다.

- <29> 일반적으로, 게이트 배선과 게이트 전극과 게이트 패드 전극은 알루미늄을 포함하는 이중 금속층으로 형성하며 이와 같이 하는 이유는, 알루미늄(Al)이 저항은 작으나 화학적으로 내식성이 약하고, 후속의 고온 공정에서 힐 락(hillock)형성에 의한 배선 결함문제를 야기하기 때문에 내식성이 강한 몰리브덴(Mo)이나 크롬(Cr)등의 금속 을 적층하는 것이다.

- <30> 이하, 게이트 전극과 게이트 배선과 게이트 패드 전극을 형성하는 공정을 설명한다.

- <31> 도 2a에 도시한 바와 같이, 기판(21) 상에 알루미늄(A1) 또는 알루미늄 합금(A1Nd)을 증착한 제 1 금속층(23a) 과, 제 1 금속층(23a)의 상부에 몰리브덴(Mo)을 증착한 제 2 금속층(23b)을 적층하여 형성한다.

- <32> 연속하여, 상기 제 2 금속층(23b)의 상부에 포토레지스트(photoresist:이하 "PR"이라 칭함)를 도포하여 PR층 (25)을 형성한다.

- <33> 다음으로, 상기 PR층(25)의 상부에 투과부(A)와 차단부(B)로 정의된 마스크(M)를 위치시키고, 마스크(M)의 상부로 빛을 조사하여 하부의 PR층(25)을 노광하는 공정을 진행한다.

- <34> 연속하여, 상기 노광된 PR층(25)을 현상하는 공정을 진행한다.

- <35> 도 2b에 도시한 바와 같이, 현상되고 남은 잔류 PR층(27) 사이로 하부의 제 2 금속층(23b)이 노출된다.

- <36> 이때, 상기 잔류 PR층(27)은 베이크(bake)과정을 거치게 되면서, 반원 형상으로 구성된다.

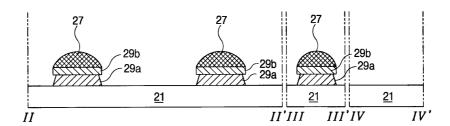

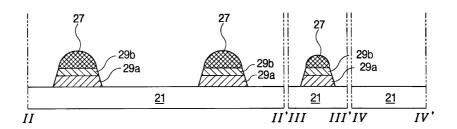

- <37> 도 2c에 도시한 바와 같이, 상기 잔류 PR층(27) 사이로 노출된 제 1 금속층(23a)과 그 하부의 제 2 금속층(23b)을 식각하게 되면, 패턴된 제 1 금속층(29a)인 알루미늄(Al) 또는 알루미늄 합금층은 패턴된 제 2 금속층(29b)인 몰리브덴(Mo)층 보다 빨리 식각되는 특성이 있기 때문에, 제 1 금속층(29a)과 제 2 금속층(29b)은 오버행(overhang)형상이 된다.

- <38> 이와 같은 형상은 다음공정에서 형성되는 절연막(미도시)의 증차 불량의 원인이 되기 때문에 상기 패턴된 제 1 금속층(29a)과 제 2 금속층(29b)의 측면이 연속적으로 테이퍼(taper)지게 구성하는 공정이 더 필요하다.

- <39> 따라서, 도 2d에 도시한 바와 같이, 건식식각 방식으로 잔류 PR층(27)의 양측(평면적으로 둘레임)과 그 하부의 제 1 및 제 2 금속층(29a,29b)을 식각하는 공정을 진행한다. 이때, 잔류 PR층(27)은 그 모양을 그대로 유지하면서 깍이게 된다.

- <40> 이와 같이 하면 앞서 설명한대로, 상기 제 1 금속층(29a)과 제 2 금속층(29b)의 양 측면이 연속적으로 테이퍼진 형상이 된다.

- <41> 상기 건식 식각 공정이 완료되면 잔류 PR층(27)을 제거하는 공정을 진행한다.

- <42> 결과적으로 도 2e에 도시한 바와 같이, 몰리브덴/알루미늄(또는 알루미늄합금)(Mo/AI(AINd))의 이중층으로 게이트 전극(31)과, 게이트 전극(31)에 연결되고 일끝단에 게이트 패드 전극(35)를 포함하는 게이트 배선(33)을 형성할 수 있게 된다.

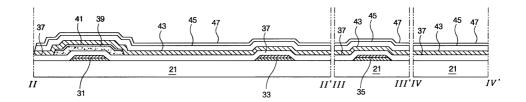

- <43> 이하, 도 3a 내지 도 3e는 상기 도 2a 내지 도 2e에 연속적인 공정이다.

- <44> 도 3a에 도시한 바와 같이, 상기 게이트 전극(31)과 게이트 배선(33)과 게이트 패드전극(35)이 형성된 기판(2 1)의 전면에 질화 실리콘(SiN<sub>x</sub>)과 산화 실리콘(SiO<sub>2</sub>)을 포함하는 무기절연물질 그룹 중 선택된 하나를 증착하여, 제 1 절연막인 게이트 절연막(37)을 형성한다.

- <45> 연속하여, 상기 게이트 전극(31)상부의 게이트 절연막(37)상에 비정질 실리콘(a-Si:H)과 불순물이 포함된 비정 질 실리콘(n+a-Si:H)을 적층하고 패턴하여, 액티브층(39)과 오믹 콘택층(41)을 형성한다.

- <46> 다음으로, 도 3b에 도시한 바와 같이, 상기 오믹 콘택층(41)이 형성된 기판(21)의 전면에, 몰리브덴(Mo)과 알루

- 미늄(A1)과 몰리브덴(Mo)을 차례로 증착하여, 제 3,4,5 금속층(43,45,47)을 적층한다.

- <47> 다음으로, 도 3c에 도시한 바와 같이, 상기 제 3,4,5금속층을 동시에 패턴하여, 몰리브덴/알루미늄/몰리브덴 (Mo/Al/Mo)의 3중 금속층으로 구성되고, 상기 오믹 콘택층(41)과 접촉하면서 서로 이격된 소스 전극(49)과 드레인 전극(51)을 형성하고, 동시에 상기 소스 전극(49)과 연결되고 일 끝단에 데이터 패드(55)를 포함하는 데이터 배선(53)을 형성한다.

- <48> 동시에, 상기 게이트 배선(33)의 일부 상부에 섬 형상의 소스.드레인 금속(57)층을 형성한다.

- <49> 상기 소스 및 드레인 전극(49,51)과 데이터 배선(53)을 몰리브덴(Mo)이나 크롬(Cr)과 같이 저항이 큰 금속을 단일층으로 하여 대면적 기판을 제작하게 되면, 신호 지연에 의해 액정패널의 전면에 대해 동일한 화질을 가지는 화상을 얻을 수 없게 된다.

- <50> 반면, 상기 소스 및 드레인 전극(49,51)과 데이터 배선(53)의 저항이 작을수록 신호의 흐름이 원활하기 때문에 대면적 어레이기판을 제작하는데 적합하다.

- <51> 따라서, 이를 해결하기 위해 전술한 바와 같이, 상기 소스 및 드레인 전극(49,51)과 데이터배선(45)을 저 저항 배선으로 형성하는 것이 필요하다.

- <52> 그런데, 저저항 배선이 알루미늄층의 상부와 하부에 각각 구성된 몰리브덴층중, 상기 하부 몰리브덴 층은 상기 제 2 금속층인 알루미늄 층이 상기 액티브층(39) 또는 오믹 콘택층(41)으로 파고 들어가는 스파이킹(spiking)현상을 방지하기 위해서 형성하고, 상기 상부 몰리브덴 층은 이후 공정에서 형성되는 투명전극과 상기 알루미늄층사이의 콘택 저항을 줄이기 위한 목적으로 형성하는 것이다.

- <53> 이와 같은 이유로, 상기 소스 및 드레인 전극(49.51)과 데이터 배선(53)을 삼층(Mo/A1/Mo)으로 구성하였다.

- <54> 전술한 공정에 연속하여, 상기 소스 전극과 드레인 전극(49,51)사이로 노출된 오믹 콘택층(41)을 식각하여 하부의 액티브층(39)을 노출한다.

- <55> 도 3d에 도시한 바와 같이, 상기 소스 및 드레인 전극(49,51)이 형성된 기판(21)의 전면에 절연물질을 증착하여, 제 2 절연막인 보호막(59)을 형성한다.

- <56> 상기 보호막(59)을 식각하여 드레인 전극(51)의 일부를 노출하는 드레인 콘택홀(61)과, 소스.드레인 금속층의 일부를 노출하는 스토리지 콘택홀(63)과, 상기 게이트 패드 전극(35)을 노출하는 게이트 패드 전극 콘택홀(65)과, 상기 데이터 패드 전극(37)을 노출하는 데이터 패드 콘택홀(67)을 형성한다.

- <57> 도 3e에 도시한 바와 같이, 상기 보호막(59)이 형성된 기판(21)의 전면에 인듐-틴-옥사이드(ITO)와 인듐-징크-옥사이드(IZO)를 포함한 투명 도전성 금속그룹 중 선택된 하나를 증착하고 패턴하여, 상기 드레인 전극(51)과 상기 소스-드레인 금속층(47)과 접촉하는 투명한 화소전극(69)을 형성한다.

- <58> 동시에, 상기 게이트 패드 전극(35)과 접촉하는 게이트 패드 전극단자(71)와 상기 데이터 패드 전극(55)과 접촉하는 데이터 패드 전극단자(73)를 형성한다.

- <59> 전술한 바와 같은 공정으로 종래에 따른 어레이기판을 제작할 수 있다.

- <60> 상기 공정은 5마스크 공정으로 제작될 수 있으나, 상기 게이트 전극과 게이트 배선은 2회의 식각 공정 즉, 습식 식각(wet etching)공정과 건식식각(dry etching)공정을 진행하기 때문에 공정이 지연된다.

- <61> 또한, 종래의 공정 중, 소스 및 드레인 전극(49,51)과 데이터배선(53)과 데이터 패드 전극(55)은 삼층의 금속을 혼산용액으로 일괄 식각하여 형성하게 되는데, 식각시 식각용액에 의해 전지반응(갈바닉)이 발생하게 되며, 이때 몰리브덴(Mo)의 두께가 두꺼울수록 전지반응에 의한 영향을 극복할 수 없다.

- <62> 특히, 전지 반응에 의해 하부 몰리브덴 층이 과식각 되어 상기 호보층을 형성하는 공정 중 알루미늄 층이 주저 앉아 하부의 액티브층과 접촉하게 된다.

- <63> 이때, 상기 알루미늄층과 액티브층이 반응하여 누설전류를 증가시켜 소자의 동작특성을 저하하는 원인이 된다.

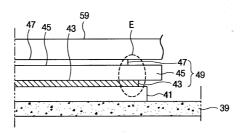

- <64> 이하, 도 4를 참조하여 설명한다. 도 4는 도 3e의 D를 확대한 단면도이다.

- <65> 도시한 바와 같이, 알루미늄층(45)을 사이에 두고 상부와 하부에 구성된 몰리브덴(Mo)이 과식각되는 현상이 발생하게 된다.

- <66> 이와 같은 현상은, 상기 소스 및 드레인전극(49,도 3e의 51)과 데이터 배선(도 3e의 53)과 데이터 패드 전극 (도 3e의 55)이 형성된 기판의 전면에 보호막(55)을 형성하는 과정에서 상기 알루미늄층(45)의 역 테이퍼(E)에 의해 보호막이 제대로 형성되지 않는 경우가 있다.

- <67> 또한, 상기 알루미늄층이 상부에 형성된 보호층(59)에 눌려 하부의 액티브층(39)또는 오믹 콘택층(41)과 접촉하게 된다. 이와 같은 경우에는 상호 확산 작용에 의해 누설전류의 상승으로 인해 소자(박막트랜지스터)의 동작을 저하하는 문제가 있다.

#### 발명이 이루고자 하는 기술적 과제

- <68> 본 발명은 전술한 바와 같은 문제를 해결하기 위한 목적으로 안출된 것으로, 상기 게이트 전극과 소스 및 드레인 전극을 구성할 때, 구리와 버퍼 금속층을 포함하는 이중 금속층으로 구성한다.

- <69> 이때, 상기 게이트 전극으로 구리와 함께 사용되는 버퍼 금속층은 기판과의 밀착성이 좋아야 한다.

- <70> 또한, 상기 소스 및 드레인 전극으로 구리와 함께 사용되는 버퍼 금속층은 하부 오믹 콘택층과 구리와의 반응을 막을 수 있는 금속이면 된다.

- <71> 상기와 같이 구리를 포함한 이중 금속층으로 게이트 및 드레인 전극을 형성하면, 게이트 전극을 형성하는 공정에서 식각 공정을 두 번에 걸쳐 진행할 필요가 없고, 상기 소스 및 드레인 전극을 알루미늄을 포함하는 삼중금속층으로 형성하였을 때 발생하였던 누설전류 문제를 해결할 수 있다.

#### 발명의 구성 및 작용

- <72> 전술한 바와 같은 목적을 달성하기 위한 액정표시장치용 어레이기판은 기판 상에 구성되고, 구리와 제 1 금속 버퍼층의 이중층으로 구성된 게이트 전극과, 게이트 전극과 연결된 게이트 배선과, 게이트 배선에서 연장된 게 이트 패드 전극과; 상기 게이트 전극과 게이트 배선과 게이트 패드 전극 상부에 구성된 제 1 절연막과; 상기 게 이트 전극 상부의 제 1 절연막 상에 적층되어 구성된 액티브층과 오믹 콘택층과; 상기 오믹 콘택층과 접촉하고, 구리와 제 2 금속 버퍼층의 이중층으로 구성된 소스 및 드레인 전극과 소스전극과 연결된 데이터배선과 데이터 배선에서 연장된 데이터 패드 전극과; 소스전극과 드레인 전극과 데이터 배선이 형성된 기판의 전면에 구성되 고, 상기 드레인 전극과, 게이트 패드 전극과 데이터 패드 전극의 일부를 노출하는 보호막과; 상기 노출된 드레 인 전극과 접촉하는 투명 화소전극과, 게이트 패드 전극과 접촉하는 투명 게이트 패드 전극단자와, 데이터 패드 전극과 접촉하는 투명 데이터 패드 전극단자를 포함한다.

- <73> 상기 제 1 금속 버퍼층은 기판과 밀착성이 좋은 물질로 구성한다, 이러한 물질로는 탄탈륨(Ta),티타늄(Ti),크롬(Cr), 몰리브덴(Mo), 니켈(Ni), 텅스텐(W) 등이 있다.

- <74> 상기 제 2 금속 버퍼층은 하부 오믹 콘택층과 구리와의 반응을 막을 수 있는 물질로 구성한다. 이러한 물질로는 탄탈륨(Ta), 티타늄(Ti),크롬(Cr), 몰리브덴(Mo), 니켈(Ni), 텅스텐(W) 등이 있다.

- <75> 상기 게이트 배선의 일부 상부에 상기 소스 및 드레인 전극과 동일층 동일물질로 섬형상의 소스.드레인 금속층을 더욱 구성하며, 소스.드레인 금속층은 상기 보호막을 식각하여 구성한 콘택홀을 통해 상기 화소전극과 접촉하도록 한다.

- <76> 상기 게이트 전극과 게이트배선과 게이트 패드 전극 하부의 기판의 전면에 보호층을 더욱 구성한다.

- <77> 상기 보호층은 질화 실리콘(SiN<sub>x</sub>)과 산화 실리콘(SiO<sub>2</sub>)을 포함하는 무기절연물질 그룹 중 선택된 하나 또는 벤조사이클로부텐(BCB)과 아크릴(acryl)계 수지(resin)를 포함한 유기절연물질그룹 중 선택된 하나 또는 이중층으로 구성한다.

- <78> 상기 보호층을 더욱 구성할 경우에는 제 1 금속 버퍼층은 기판과 밀착성이 좋은 물질이면 되고 이러한 물질로는 탄탈륨(Ta), 티타늄(Ti), 크롬(Cr), 몰리브덴(Mo), 니켈(Ni), 텅스텐(W)등이 있다.

- <79> 본 발명의 특징에 따른 액정표시장치용 어레이기판 제조방법은 기판 상에, 구리와 제 1 금속 버퍼층의 이중층으로 게이트 전극과, 게이트 전극과 연결된 게이트 배선과, 게이트 배선에서 연장된 게이트 패드 전극을 형성하는

단계와; 상기 게이트 전극과 게이트 배선과 게이트 패드 전극 상부에 제 1 절연막을 형성하는 단계와; 상기 게이트 전극 상부의 제 1 절연막 상에 액티브층과 오믹 콘택층을 형성하는 단계와; 상기 오믹 콘택층과 접촉하고, 구리와 제 2 금속 버퍼층의 이중층인 소스 및 드레인 전극과 소스전극과 연결된 데이터배선과 데이터 배선에서 연장된 데이터 패드 전극을 형성하는 단계와; 소스전극과 드레인 전극과 데이터 배선이 형성된 기판의 전면에, 상기 드레인 전극과, 게이트 패드 전극과 데이터 패드 전극의 일부를 노출하는 보호막을 형성하는 단계와; 상기 노출된 드레인 전극과 접촉하는 투명 화소전극과, 게이트 패드 전극과 접촉하는 투명 게이트 패드 전극단자를 형성하는 단계를 포함한다.

- <80> 이하, 첨부한 도면을 참조하여 본 발명에 따른 바람직한 실시예들을 설명한다.

- <81> -- 제 1 실시예 --

- <82> 본 발명의 제 1 실시예는 게이트 전극과 소스 및 드레인 전극을 형성할 때 구리를 포함하는 이중 금속층으로 형성하는 것을 특징으로 한다.

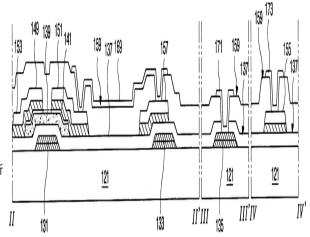

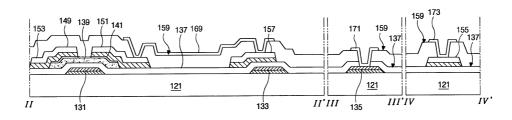

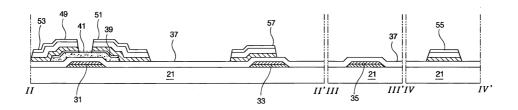

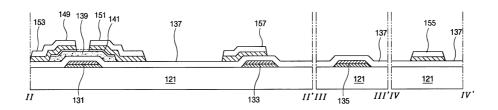

- <83> 이하, 도 5a 내지 도 5d와 도 6a 내지 도 6e를 참조하여, 본 발명에 따른 어레이기판 제조공정을 설명한다.(본 발명의 평면도는 상기 종래의 평면도와 동일함으로 이를 이용하고, 동일한 구성의 도면부호는 종래의 번호에 100번을 더하여 표시한다.)

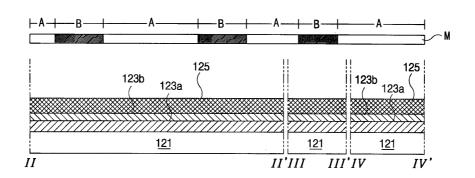

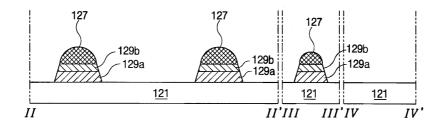

- <84> 도 5a 내지 도 5d는 게이트 전극과 게이트 배선과 게이트 패드 전극을 형성하는 공정을 본 발명의 공정 순서에 따라 도시한 공정 단면도이다.

- <85> 먼저, 기판(121) 상에 몰리브덴(Mo), 크롬(Cr), 텅스텐(W),니켈(Ni),탄탈륨(Ta),티타늄(Ti) 또는 이들의 합금을 포함하는 도전성 금속그룹 중 선택된 하나를 증착하여 제 1 금속층(123a)을 형성하고, 제 1 금속층(123a)의 상 부에 구리(Cu)를 증착한 제 2 금속층(123b)을 적층하여 형성한다.

- <86> 이때, 구리의 하부에 금속층을 더욱 구성하는 이유는 상기 구리가 유리기판과 접촉특성이 좋지 않기 때문에 이를 해결하기 위함이다.

- <87> 연속하여, 상기 제 2 금속층(123b)의 상부에 포토레지스트(photoresist:이하 "PR"이라 칭함)를 도포하여 PR층 (125)을 형성한다.

- <88> 다음으로, 상기 PR층(125)의 상부에 투과부(A)와 차단부(B)로 정의된 마스크(M)를 위치시키고, 마스크(M)의 상부로 빛을 조사하여 하부의 PR층(125)을 노광하는 공정을 진행한다.

- <89> 연속하여, 상기 노광된 PR층(125)을 현상하는 공정을 진행한다.

- <90> 도 5b에 도시한 바와 같이, 현상되고 남은 잔류 PR층(127) 사이로 하부의 제 2 금속층(123b)이 노출된다.

- <91> 이때, 상기 잔류 PR층(123b)은 베이크(bake)과정을 거치게 되면서, 반원 형상으로 구성된다.

- <92> 도 5c에 도시한 바와 같이, 상기 잔류 PR층(127) 사이로 노출된 제 2 금속층(125b)과 그 하부의 제 1 금속층 (125a)을 습식식각 하게 되면, 패턴된 제 1 금속층(129a)과 구리(Cu)층인 제 2 금속층(129b)의 측면이 연속적으로 테이퍼지게 구성된다.

- <93> 연속하여, 상기 잔류 PR층을 제거하고 나면 도 5d에 도시한 바와 같이, 구리/버퍼 금속층(Cu/Ti,Ta,Cr,Mo,W,Ni 중 선택된 하나)의 이중층으로 게이트 전극(131)과, 게이트 전극(131)에 연결되고 일 끝단에 게이트 패드 전극(135)를 포함하는 게이트 배선(133)을 형성할 수 있게 된다.

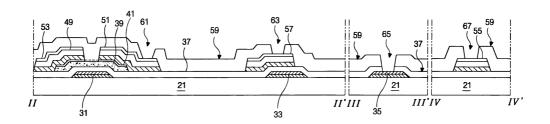

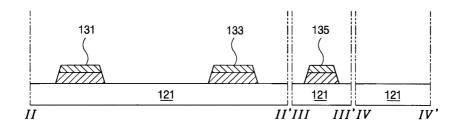

- <94> 상기 게이트 전극과 게이트 배선과 게이트 패드 전극을 형성하는 공정에 이어 이하, 도 6a 내지 도 6e를 참조하여, 본 발명에 따른 액정표시장치용 어레이기판의 공정을 설명한다.

- <95> 삭제

- <96> 도 6a에 도시한 바와 같이, 상기 게이트 전극(131)과 게이트 배선(133)등이 형성된 기판(121)의 전면에 제 1 절 연막인 게이트 절연막(137)을 형성한다.

- <97> 상기 게이트 절연막(137)은 질화 실리콘(SiN<sub>x</sub>)과 산화 실리콘(SiO<sub>2</sub>)을 포함하는 무기절연물질 그룹 중 선택된 하

나를 증착하여 형성한다.

- <98> 다음으로, 상기 게이트 전극(131)상부의 게이트 절연막(137)상에 아일랜드 형태로 액티브층(139)(active laye r)과 오믹 콘택층(141)(ohmic contact layer)을 형성한다.

- <99> 상기 액티브층(139)은 일반적으로 순수한 비정질 실리콘(a-Si:H)으로 형성하고, 상기 오믹 콘택층(141)은 불순물이 포함된 비정질 실리콘(n+a-Si:H)으로 형성한다.

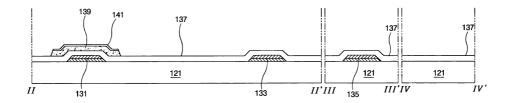

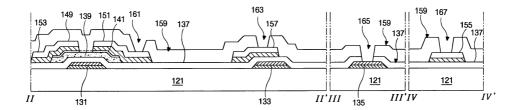

- <100> 다음으로, 도 6b에 도시한 바와 같이, 상기 오믹 콘택층(141)이 형성된 기판(121)의 전면에 탄탈륨(Ta), 티타늄 (Ti), 몰리브덴(Mo), 크롬(Cr), 니켈(Ni)등을 포함하는 도전성 금속 그룹 중 선택된 하나를 증착한 제 1 금속층 (143)을 형성하고, 상기 제 1 금속층(143)의 상부에 구리(Cu)를 증착한 제 2 금속층(145)을 형성한다.

- <101> 이때, 상기 제 1 금속층(143)은 상기 구리층인 제 2 금속층(145)과 반도체층이 직접 접촉하여 상호반응하는 것을 방지 할 수 있다

- <102> 다음으로, 도 6c에 도시한 바와 같이, 상기 제 1 금속층과 제 2 금속층을 습식식각하여, 구리를 포함한 이중 금속층으로 구성된 소스 전극(149)과 이와는 소정간격 이격된 드레인 전극(151)과, 상기 소스 전극(149)과 연결되고 일끝단에 데이터 패드(155)를 포함하는 데이터 배선(153)을 형성한다.

- <103> 동시에, 게이트 배선(133)의 일부 상부에 아일랜드 형상으로 소스-드레인 금속층(157)을 형성한다.

- <104> 연속하여, 상기 소스전극(149)과 드레인 전극(151)사이의 이격된 영역에 사이로 노출된 오믹 콘택층(141)을 식 각하여 하부의 액티브층(139)을 노출한다.

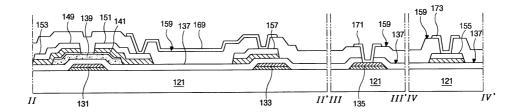

- <105> 다음으로, 도 6d에 도시한 바와 같이, 상기 소스및 드레인 전극(149,151)이 형성된 기판(121)의 전면에 질화 실리콘(SiN<sub>2</sub>)과 산화 실리콘(SiO<sub>X</sub>)을 포함한 무기절연 물질 그룹 중 선택된 하나를 증착하거나, 벤조사이클로부텐(BCB)과 아크릴(acryl)계 수지(resin)를 포함한 유기절연 물질 그룹 중 선택된 하나 또는 이중층을 증착/도포하여 보호막(159)을 형성한다.

- <106> 삭제

- <107> 삭제

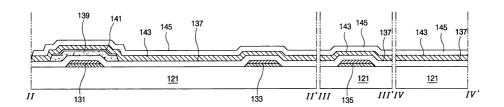

- <108> 상기 보호막(159)을 패터닝하여, 상기 드레인 전극(151)의 일부를 노출하는 드레인 콘택홀(161)과 상기 소스-드레인 금속층(157)을 노출하는 스토리지 콘택홀(163)과 상기 게이트 패드 전극(135)의 일부를 노출하는 게이트 패드 전극 콘택홀(165)과, 상기 데이터 패드 전극(137)을 노출하는 데이터 패드 콘택홀(167)을 형성한다.

- <109> 다음으로, 도 6e에 도시한 바와 같이, 상기 보호막(159) 상에 인듐-틴-옥사이드(ITO)와 인듐-징크-옥사이드 (IZO)를 포함한 투명 도전성 금속 그룹 중 선택된 하나를 증착하여, 상기 드레인 전극(151)과 소스-드레인 금속 충(157)과 접촉하는 화소전극(169)과, 상기 게이트 패드 전극(135)과 접촉하는 게이트 패드 전극단자(171)와, 상기 데이터 패드 전극(137)과 접촉하는 데이터 패드 전극단자(173)를 형성한다.

- <110> 전술한 바와 같은 공정으로 본 발명의 제 1 실시예에 따른 어레이기판을 제작할 수 있다.

- <111> 전술한 바와 같이, 게이트 전극과 소스 및 드레인 전극을 형성할 때, 저 저항특성을 가진 구리를 사용하게 되면, 공정 시간을 단축할 수 있고 소자의 동작 특성을 개선할 수 있다.

- <112> 제 1 실시예는 구리와 금속 버퍼층의 이중 금속층을 사용함으로서 구리의 단점을 보완하였다. 즉, 구리는 유리 기판과의 접촉 특성이 좋지 않고, 상기 오믹 콘택층과 접촉하면 상호 확산에 의한 누설전류 특성이 커지기 때문 에 이를 방지하기 위해 몰리브덴(Mo), 크롬(Cr), 텅스텐(W), 니켈(Ni)등의 금속을 버퍼층으로서 사용하였다.

- <113> -- 제 2 실시예 --

- <114> 삭제

- <115> 본 발명의 제 2 실시예의 특징은 상기 게이트 전극을 형성하기전 기판의 전면에 절연막으로 보호층을 형성하는

것이다.

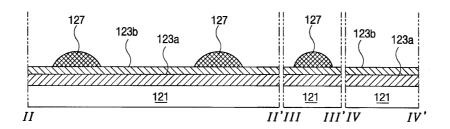

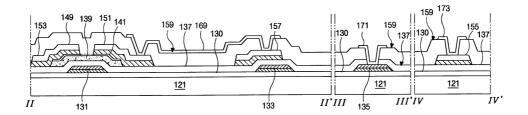

- <116> 도 7을 참조하여 설명한다.

- <117> 도 7은 도 1의 Ⅱ-Ⅲ`,Ⅲ-Ⅲ`,Ⅳ-Ⅳ`를 따라 절단한 본 발명의 제 2 실시예에 따른 액정표시장치용 어레이기판의 단면도이다.

- <118> 도시한 바와 같이, 기판(121)상에 보호층(130)을 형성하고, 상기 보호층(130)의 상부에 구리(Cu)와 버퍼 금속 층(Ti,Ta,W,Cr,Ni,Mo 중 선택된 하나)으로 구성된 이중 금속층인 게이트 전극(131)과, 이에 연결되고 일 끝단에 게이트 패드 전극(135)를 포함하는 게이트 배선(133)을 형성한다.

- <119> 상기 게이트 전극(131)과 게이트 배선(133)을 포함하는 기판(121)의 전면에 게이트 절연막(137)을 형성한다.

- <120> 상기 게이트 전극(131) 상부의 게이트 절연막(137)상에는 액티브층(139)과 오믹 콘택층(141)을 형성하며, 상기 오믹 콘택층(141)과 접촉하고 서로 이격되고 구리(Cu)와 버퍼 금속층(Ti,Ta,W,Cr,Ni,Mo 중 선택된 하나)의 이중 층인 소스 및 드레인 전극(149,151)과, 소스 전극(149)에 연결되면서 일 끝단에는 데이터 패드(155)를 포함하는 데이터 배선(153)을 형성한다.

- <121> 이때, 상기 소스 및 드레인 전극(149,151)과 동일층 동일물질로 상기 게이트 배선(133)의 일부 상부에 섬형상의 소스.드레인 금속층(157)을 형성한다.

- <122> 상기 소스 및 드레인 전극(149,151)이 형성된 기판(121)의 전면에 드레인 전극(151)의 일부를 노출하는 보호막 (159)을 형성한다.

- <123> 상기 보호막(159)의 상부에는 상기 드레인 전극(151)과 접촉하는 화소전극(169)과, 상기 게이트 패드 전극(135)과 접촉하는 게이트 패드 전극 전극단자(171)와, 상기 데이터 패드 전극(155)과 접촉하는 데이터 패드 전극단자(173)를 형성한다.

- <124> 전술한 구성에서, 상기 보호층(130)으로 질화 실리콘(SiN<sub>X</sub>) 또는 산화 실리콘(SiO<sub>2</sub>)을 포함하는 무기절연물질 그룹 중 선택된 하나와, 벤조사이클로부텐(BCB)과 아크릴(acryl)계 수지(resin)를 포함한 유기절연 물질 그룹 중 선택된 하나 또는 이중층을 증착 또는 도포하여 사용한다.

- <125> 보호층(130)으로 인해 게이트 전극(131)으로 구리와 함께 형성되는 금속 버퍼층으로 몰리브덴(Mo), 크롬(Cr), 텅스텐(W), 니켈(Ni) 이외에 티타늄(Ti),탄탄륨(Ta)을 더 사용할 수 있게 된다.

- <126> 즉, 상기 기판(121)상에 보호충(130)을 형성하여 줌으로서, 상기 티타늄(Ti)과 탄탈륨(Ta)을 식각하는 식각액이 기판(121)에 닿지 않게 되기 때문에 이들을 사용할 수 있다.

- <127> 전술한 바와 같은 구성으로 본 발명의 제 2 실시예에 따른 액정표시장치용 어레이기판을 제작할 수 있다.

#### 발명의 효과

- <128> 본 발명에 따라 액정표시장치용 어레이기판을 제작하게되면, 첫째 구리를 포함한 이중 금속층이 동일한 식각액 에 의해 일괄 식각되므로 공정시간을 단축할 수 있는 효과가 있다.

- <129> 둘째, 드레인 전극을 형성하는 금속과 하부의 액티브층과 반응하지 않기 때문에 박막트랜지스터의 동작 특성을 개선할 수 있는 효과가 있다.

- <130> 셋째, 게이트 물질과 소스 및 드레인 물질로 저저항 구리를 사용하였기 때문에 대면적 액정패널을 제작할 수 있는 효과가 있다.

### 도면의 간단한 설명

- <1> 도 1은 액정표시장치용 어레이기판의 일부를 도시한 평면도이고,

- <2> 도 2a 내지 도 2f와 도 3a 내지 도 3e는 도 1의 Ⅱ-Ⅱ'와 Ⅲ-Ⅲ'와 Ⅳ-Ⅳ'를 따라 절단하여, 종래 공정 순서에 따라 도시한 공정 단면도이고,

- <3> 도 4는 도 3e의 D를 확대한 단면도이고,

- <4> 도 5a 내지 도 5d와 도 6a 내지 도 6e는 도 1의 Ⅱ-Ⅱ'와 Ⅲ-Ⅲ'와 Ⅳ-Ⅳ'를 따라 절단하여, 본 발명의 공정 순

서에 따라 도시한 공정 단면도이고,

<5> 도 7은 도 1의 Ⅱ-Ⅱ'와 Ⅲ-Ⅲ'와 Ⅳ-Ⅳ'를 따라 절단한 본 발명의 제 2 실시예에 따른 액정표시장치용 어레이 기판의 단면도이다.

<6> <도면의 주요부분에 대한 부호의 설명>

<7> 121 : 기판 131 : 게이트 전극

<8> 133 : 게이트 배선 135 : 게이트 패드 전극

< 9> 137 : 게이트 절연막 139 : 액티브층

<10> 141 : 오믹 콘택층 149 : 소스 전극

<11> 151 : 드레인 전극 153 : 데이트 배선

<12> 155 : 데이터 패드 전극 157 : 소스.드레인 금속층

<13> 159 : 보호막 169 : 화소 전극

<14> 171 : 게이트 패드 전극단자 173 : 데이터 패드 전극단자.

### 도면

#### 도면1

### 도면2a

### *도면2b*

## 도면2c

### 도면2d

# 도면2e

# 도면3a

# 도면3b

# 도면3c

# 도면3d

# 도면3e

## 도면4

# 도면5a

# 도면5b

## 도면5c

# 도면5d

## 도면6a

## 도면6b

# 도면6c

# 도면6d

# 도면6e

## 도면7

| 专利名称(译)        | 用于液晶显示装置的阵列基板和制造方法                                                                                         |         |            |

|----------------|------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | KR100866976B1                                                                                              | 公开(公告)日 | 2008-11-05 |

| 申请号            | KR1020020052660                                                                                            | 申请日     | 2002-09-03 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                   |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                                  |         |            |

| [标]发明人         | HWANG YONG SUP<br>황용섭<br>CHAE GEE SUNG<br>채기성<br>JO GYOO CHUL<br>조규철                                       |         |            |

| 发明人            | 황용섭<br>채기성<br>조규철                                                                                          |         |            |

| IPC分类号         | G02F1/136 G02F1/1368 G02F1/1362 H01L21/28 H01L21/3205 H01L21/768 H01L23/52 H01L29/423 H01L29/49 H01L29/786 |         |            |

| CPC分类号         | G02F1/136286 G02F2001/13629                                                                                |         |            |

| 其他公开文献         | KR1020040021169A                                                                                           |         |            |

| 外部链接           | Espacenet                                                                                                  |         |            |

|                |                                                                                                            |         |            |

### 摘要(译)

液晶显示器的阵列基板及其制造方法技术领域本发明涉及液晶显示器,更具体地,涉及用于液晶显示器的阵列基板及其制造方法。 本发明所提出的第一种结构,当栅电极,所述基板和所述接触性能和良好的金属(钛,钽,钼,铬,钨,镍)和形成双金属层,铜时的源/漏电极Lt; RTI ID = 0.0欧姆接触层和铜并且由金属的双金属层(Ti,Ta,Mo,Cr,W,Ni)形成。 本发明所提出的第二个结构具有这样的结构,进一步形成具有在所述第一结构的衬底的整个表面上的绝缘膜的保护层。 在栅电极的情况下,金属的双金属层(Ti,Ta,Mo,Cr,W或Ni)(Ti,Ta,Ta,Mo,Cr,W和Ni)可以防止下欧姆接触层和铜之间的反应。 如上所述,当栅极和漏极由包括铜的双金属层形成时,可以防止工艺延迟并改善薄膜晶体管的操作特性,从而提高产品产量有。