**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl. (11) 공개번호 10-2006-0033100

*G02F 1/1337* (2006.01) (43) 공개일자 2006년04월19일

(21) 출원번호 10-2004-0082045

(22) 출원일자 2004년10월14일

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 한혜리

경기도 의왕시 삼동 삼풍 빌라트 602호

문승환

경기 용인시 상현동 현대6차아파트 205-1504(만현마을 2단지)

(74) 대리인 박영우

심사청구 : 없음

---

**(54) 액정표시장치**

---

**요약**

오동작을 방지할 수 있는 액정표시장치가 개시된다. 액정표시장치는 어레이 기판, 어레이 기판과 대향하는 대향 기판 및 어레이 기판과 대향 기판과의 사이에 개재된 액정층을 포함한다. 어레이 기판은 기판, 화소 어레이, 구동회로 및 배향막으로 이루어진다. 기판은 표시영역과 상기 표시영역에 인접하는 주변영역을 구비하고, 화소 어레이는 표시영역에 대응하여 기판 상에 구비된다. 구동회로는 주변영역에 대응하여 기판 상에 구비되어 화소 어레이를 구동하고, 배향막은 화소 어레이와 구동회로를 커버한다. 따라서, 구동회로의 오동작을 방지할 수 있다.

**대표도**

도 2

**명세서**

**도면의 간단한 설명**

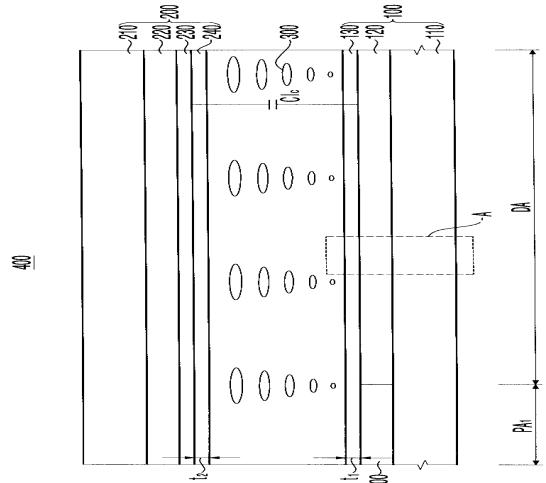

도 1은 본 발명의 일 실시예에 따른 액정표시장치의 평면도이다.

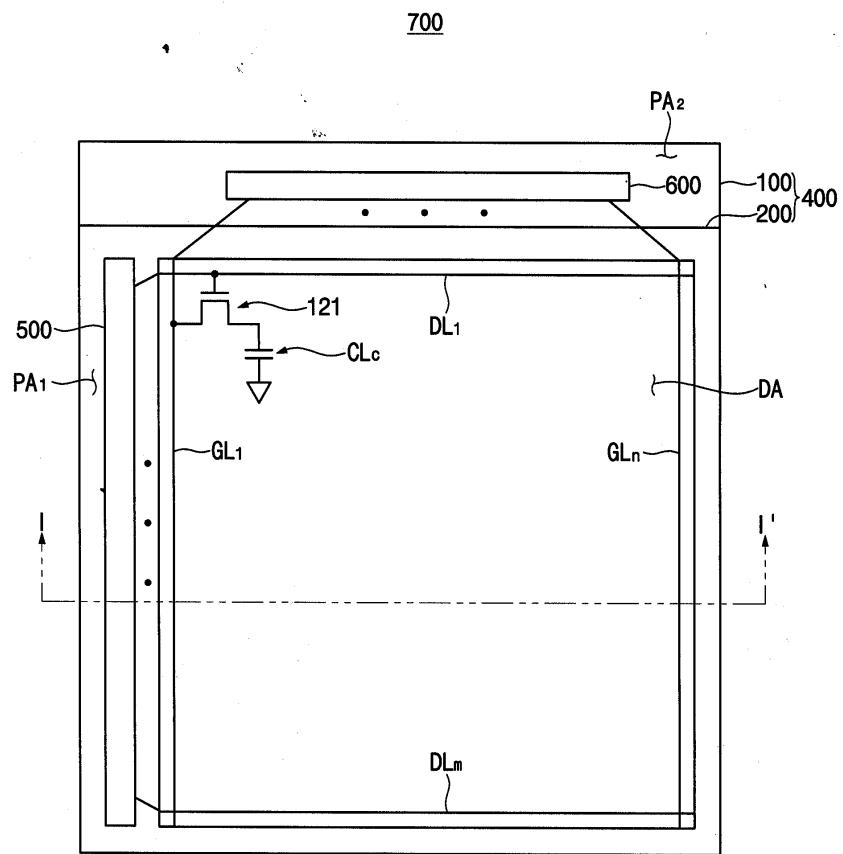

도 2는 도 1에 도시된 절단선 I - I`에 따른 단면도이다.

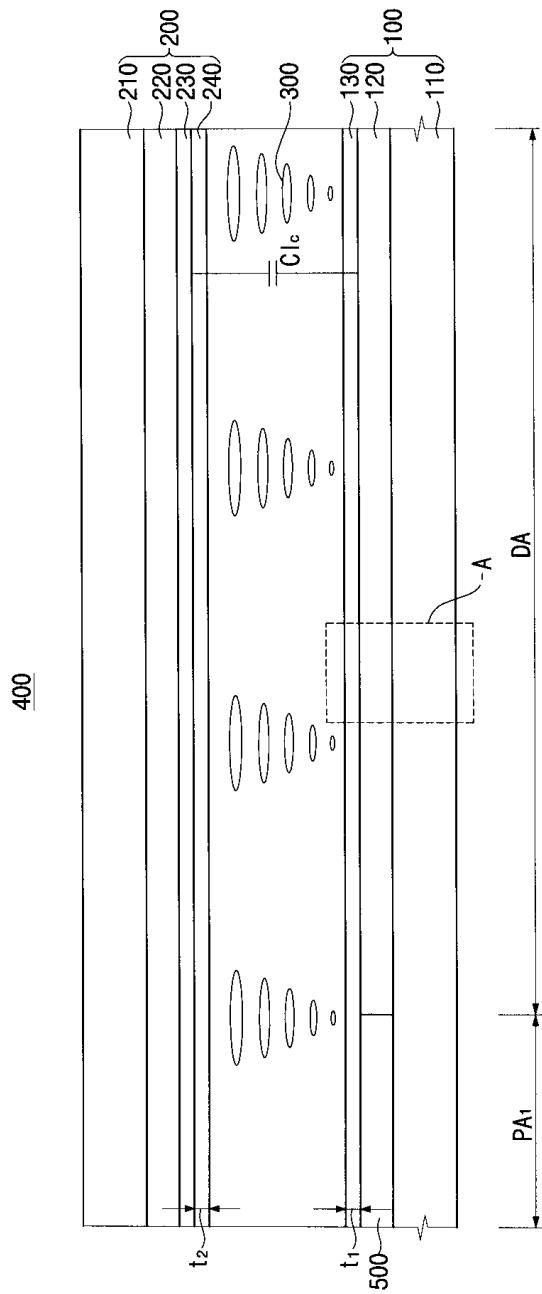

도 3은 도 1에 도시된 게이트 구동회로의 블록도이다.

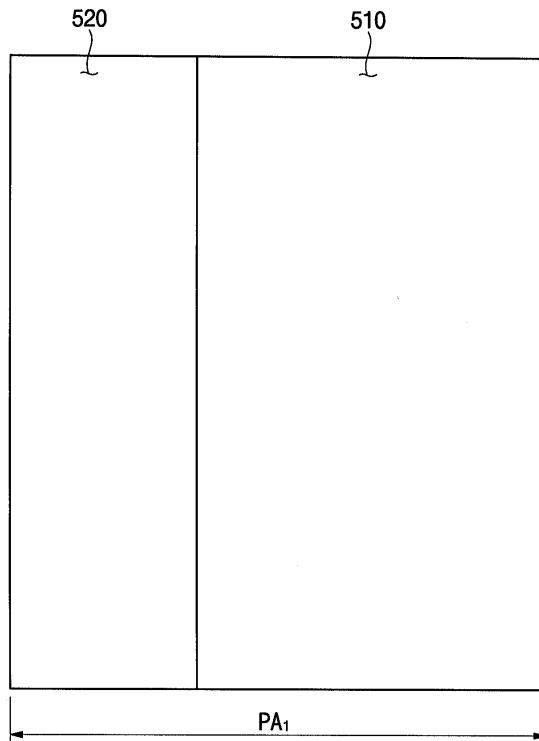

도 4는 도 1에 도시된 A 부분의 확대 단면도이다.

\*도면의 주요 부분에 대한 부호의 설명\*

100 : 어레이 기판 130 : 제1 배향막

120 : 화소 어레이 230 : 공통전극

200 : 대향 기판 240 : 제2 배향막

300 : 액정층 400 : 액정표시패널

500 : 게이트 구동회로 600 : 데이터 구동회로

700 : 액정표시장치

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정표시장치에 관한 것으로, 더욱 상세하게는 오동작을 방지할 수 있는 액정표시장치에 관한 것이다.

일반적으로, 액정표시장치는 다수의 게이트 라인과 다수의 데이터 라인이 구비된 액정표시패널, 다수의 게이트 라인에 게이트 신호를 출력하는 게이트 구동회로 및 다수의 데이터 라인에 데이터 신호를 출력하는 데이터 구동회로로 이루어진다.

게이트 구동회로 및 데이터 구동회로는 칩 형태로 이루어져 액정표시패널에 실장된다. 그러나, 최근에는 액정표시장치의 전체적인 사이즈를 감소시키면서 생산성을 증대시키기 위하여 게이트 구동회로를 액정표시패널에 내장하는 구조가 개발되고 있다.

액정표시패널은 다수의 게이트 라인과 다수의 데이터 라인이 구비된 하부기판, 하부기판과 마주하는 상부기판 및 하부기판과 상부기판과의 사이에 개재된 액정층을 포함한다.

게이트 구동회로가 액정표시패널의 하부기판에 내장되는 구조에서, 게이트 구동회로와 상부기판에 형성된 공통전극과의 사이에서 기생 커패시턴스가 발생한다. 이러한 기생 커패시턴스는 게이트 구동회로의 오동작을 유발한다.

#### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명의 목적은 오동작을 방지하기 위한 액정표시장치를 제공하는 것이다.

#### 발명의 구성 및 작용

본 발명의 일 특징에 따른 액정표시장치는 어레이 기판, 액정층 및 대향 기판을 포함한다.

상기 어레이 기판은 제1 기판, 화소 어레이, 구동회로 및 제1 배향막으로 이루어진다.

상기 제1 기판은 표시영역과 상기 표시영역에 인접하는 주변영역을 구비하고, 상기 화소 어레이는 상기 표시영역에 대응하여 상기 제1 기판 상에 구비된다. 상기 구동회로는 상기 주변영역에 대응하여 상기 제1 기판 상에 구비되어 상기 화소 어레이를 구동하고, 상기 제1 배향막은 상기 화소 어레이와 상기 구동회로를 커버한다.

상기 액정층은 상기 제1 배향막 상에 구비되고, 상기 대향 기판은 상기 액정층 상에 구비된 제2 배향막과 상기 제2 배향막 상에 구비되어 상기 제1 기판과 마주하는 제2 기판으로 이루어진다.

이러한 액정표시장치에 따르면, 상기 어레이 기판에 구비되는 상기 제1 배향막이 상기 구동회로를 전체적으로 커버하도록 상기 주변영역까지 형성됨으로써, 상기 구동회로의 오동작을 방지할 수 있다.

이하, 첨부한 도면들을 참조하여 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다.

도 1은 본 발명의 일 실시예에 따른 액정표시장치의 평면도이고, 도 2는 도 1에 도시된 절단선 I - I'에 따른 단면도이다.

도 1 및 도 2를 참조하면, 본 발명의 일 실시예에 따른 액정표시장치(400)는 영상을 표시하는 액정표시패널(400), 상기 액정표시패널(400)에 구비되어 상기 액정표시패널(400)에 게이트 신호를 출력하는 게이트 구동회로(500) 및 데이터 신호를 출력하는 데이터 구동회로(600)를 포함한다.

상기 액정표시패널(400)은 어레이 기판(100), 상기 어레이 기판(100)과 마주하는 대향 기판(200) 및 상기 어레이 기판(100)과 상기 대향기판(200)과의 사이에 개재된 액정층(300)을 포함한다.

상기 액정표시패널(400)은 상기 영상을 표시하는 표시영역(DA), 상기 표시영역(DA)을 감싸는 제1 주변영역(PA1) 및 상기 제1 주변영역(PA1)의 외측에 형성된 제2 주변영역(PA2)으로 이루어진다.

상기 표시영역(DA)에 대응하여 상기 어레이 기판(100)의 제1 기판(110)에는 화소 어레이(120)가 구비되고, 상기 제1 주변영역(PA1)에 대응하여 상기 제1 기판 상에는 상기 게이트 구동회로(500)가 구비된다. 상기 화소 어레이(120)는 제1 내지 제n 게이트 라인(GL1 ~ GLn), 제1 내지 제m 데이터 라인(DL1 ~ DLm), 다수의 박막 트랜지스터(Tr), 보호막(미도시) 및 화소전극(미도시)을 포함한다.

상기 제1 내지 제n 게이트 라인(GL1 ~ GLn)은 상기 제1 내지 제m 데이터 라인(DL1 ~ DLm)과 서로 직교한다. 도 1에 도시된 상기 박막 트랜지스터(Tr)의 게이트 전극은 상기 제1 게이트 라인(GL1)과 전기적으로 연결되고, 상기 제1 박막 트랜지스터(Tr)의 소오스 전극은 상기 제1 데이터 라인(DL1)과 전기적으로 연결되며, 상기 제1 박막 트랜지스터(Tr)의 드레인 전극은 상기 화소전극과 연결된다.

상기 다수의 박막 트랜지스터(Tr), 보호막(미도시) 및 화소전극(미도시)에 대해서는 이후 도 4를 참조하여 구체적으로 설명하기로 한다.

한편, 상기 제2 주변영역(PA2)에서 상기 어레이 기판(100)은 상기 대향기판(200)보다 길게 연장되어, 상기 제2 주변영역(PA2)에 대응하여 상기 제1 기판(110) 상에는 칩 형태로 이루어진 상기 데이터 구동회로(600)가 실장된다.

상기 데이터 구동회로(600)는 상기 표시영역(DA)에 형성된 상기 제1 내지 제n 데이터 라인(DL1 ~ DLm)과 전기적으로 연결된다. 따라서, 상기 데이터 구동회로(600)로부터 출력된 상기 데이터 신호는 상기 제1 내지 제m 데이터 라인(DL1 ~ DLm)으로 인가된다.

상기 제1 주변영역(PA1)에는 상기 게이트 구동회로(500)가 상기 다수의 박막 트랜지스터(Tr)와 동일한 공정을 통해 동일한 시간 상에서 형성된다.

상기 게이트 구동회로(500)는 상기 표시영역(DA)에 형성된 상기 제1 내지 제n 게이트 라인(GL1 ~ GLn)과 전기적으로 연결된다. 따라서, 상기 게이트 구동회로(500)로부터 출력된 상기 게이트 신호는 상기 제1 내지 제n 게이트 라인(GL1 ~ GLn)으로 인가된다.

상기 화소 어레이(120)와 상기 게이트 구동회로(500)가 구비된 상기 제1 기판(110) 상에는 상기 화소 어레이(120)와 상기 게이트 구동회로(500)를 커버하는 제1 배향막(130)이 형성된다. 상기 제1 배향막(130)에는 상기 액정층(300)에 구비된 다수의 액정분자를 소정의 방향으로 배열시키기 위한 제1 배향홈(미도시)이 형성된다.

본 발명의 일 예로, 상기 제1 배향막(130)은 절연성을 갖는 폴리 이미드(Poly Imide; PI)계 물질로 이루어진다. 또한, 상기 제1 배향막(130)의 제1 두께(t1)는 500 ~ 1500Å로 이루어진다.

상기 제1 배향막(130)은 상기 게이트 구동회로(500)를 전체적으로 커버하여 상기 표시패널(400)의 외부로부터의 습기나 이물이 상기 게이트 구동회로(500)로 유입되는 것을 차단한다.

한편, 상기 대향기판(200)은 제2 기판(210), 컬러필터층(220), 공통전극(230) 및 제2 배향막(240)을 포함한다. 상기 컬러필터층(220)은 레드, 그린 및 블루 색화소로 이루어져 상기 제2 기판(210) 상에 형성되고, 상기 공통전극(230)은 투명성 도전 물질로 이루어져 상기 컬러필터층(220) 상에 균일한 두께로 적층된다. 따라서, 상기 공통전극(230), 상기 액정층(300) 및 상기 화소전극에 의해서 액정 커패시터(Cl<sub>c</sub>)가 형성된다.

상기 제2 배향막(240)은 상기 액정층(300)에 구비된 다수의 액정분자를 소정의 방향으로 배열시키기 위한 제2 배향홈(미도시)이 형성된다. 일반적으로, 상기 다수의 액정분자는 상기 공통전극(230)과 상기 화소전극에 의해서 소정의 각도로 틸트되는 트위스트 네마틱 액정분자로 이루어진다. 따라서, 상기 제1 배향홈과 상기 제2 배향홈은 서로 직교하도록 형성된다.

본 발명의 일 예로, 상기 제2 배향막(240)은 절연성을 갖는 상기 PI계 물질로 이루어진다. 또한, 상기 제2 배향막(240)의 제2 두께(t<sub>2</sub>)는 500 ~ 1500Å로 이루어진다.

이와 같이, 상기 제1 배향막(130)은 상기 어레이 기판(100)에 형성된 상기 게이트 구동회로(500)를 커버하고, 상기 제2 배향막(240)은 상기 대향 기판(200)에 형성된 상기 공통전극(230)을 커버한다. 따라서, 상기 게이트 구동회로(500)와 상기 공통전극(230)과의 사이에서 생성되는 기생 커패시턴스가 감소될 수 있다.

도 3은 도 1에 도시된 게이트 구동회로의 블록도이다.

도 3을 참조하면, 게이트 구동회로(500)는 쉬프트 레지스터(510)와 배선부(520)로 이루어지고, 상기 게이트 구동회로(500)는 어레이 기판(100, 도 1에 도시됨)의 제1 주변영역(PA1)에 형성된다.

상기 쉬프트 레지스터(510)는 제1 내지 제n 게이트 라인(GL<sub>1</sub> ~ GL<sub>n</sub>, 도 1에 도시됨)에 전기적으로 연결되고, 상기 제1 내지 제n 게이트 라인(GL<sub>1</sub> ~ GL<sub>n</sub>)에 게이트 신호를 순차적으로 출력한다.

상기 배선부(520)는 상기 쉬프트 레지스터(510)를 구동하기 위한 각종 신호를 외부로부터 입력받아 상기 쉬프트 레지스터(510)로 제공하는 다수의 신호배선(미도시)으로 이루어진다. 도면에 도시하지는 않았지만, 상기 배선부(520)를 통해 상기 쉬프트 레지스터(510)로 제공되는 신호는 개시신호, 클럭신호 및 구동전압으로 이루어질 수 있다.

도 2에 도시된 제1 배향막(130)은 상기 게이트 구동회로(500)의 상기 쉬프트 레지스터(510)와 배선부(520)를 전체적으로 커버한다. 따라서, 외부로부터 유입된 습기 또는 이물에 의해서 상기 다수의 신호배선이 부식되거나 상기 쉬프트 레지스터(510)에 형성된 구동 트랜지스터(미도시)가 오동작하는 것을 방지할 수 있다.

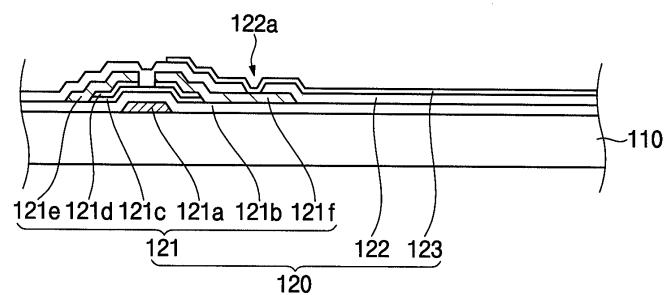

도 4는 도 1에 도시된 A 부분의 확대 단면도이다.

도 4를 참조하면, 어레이 기판(100)에 형성된 화소 어레이(120)는 박막 트랜지스터(121), 보호막(122) 및 화소전극(123)을 포함한다.

상기 박막 트랜지스터(121)는 제1 기판(110) 상에 형성된 게이트 전극(121a), 상기 게이트 전극(121a)을 커버하는 게이트 절연막(121b), 상기 게이트 전극(121a)과 오버랩되도록 상기 게이트 절연막(121b) 상에 순차적으로 형성된 액티브층(121c) 및 상기 액티브층(121c) 상에 형성된 오믹 콘택층(121d)을 포함한다.

또한, 상기 박막 트랜지스터(121)는 서로 소정의 간격으로 이격되도록 상기 오믹 콘택층(121d) 상에 형성된 소오스 전극(121e) 및 드레인 전극(121f)을 포함한다.

상기 보호막(122)은 상기 제1 기판(110) 상에 형성되어 상기 박막 트랜지스터(121)를 커버한다. 상기 보호막(122)에는 상기 박막 트랜지스터(121)의 드레인 전극(121f)을 노출시키기 위한 콘택홀(122a)이 형성된다.

상기 화소전극(123)은 투명성 도전 물질로 이루어져 상기 보호막(122) 상에 형성된다. 또한, 상기 화소전극(123)은 상기 콘택홀(122a)을 통해 상기 드레인 전극(121f)과 전기적으로 연결된다.

### 발명의 효과

이와 같은 액정표시장치에 따르면, 상기 어레이 기판에 구비되는 상기 제1 배향막이 상기 구동회로를 전체적으로 커버하도록 상기 표시영역으로부터 상기 제1 주변영역으로까지 연장하여 형성된다.

따라서, 상기 액정표시패널의 외부로부터 유입된 습기나 이물에 의해서 상기 게이트 구동회로가 부식되는 것을 방지할 수 있다.

또한, 상기 제1 배향막은 절연성을 갖는 물질로 이루어져 상기 게이트 구동회로와 상기 공통전극과의 사이에 형성되는 기생 커패시턴스를 감소시킬 수 있다. 그 결과, 상기 게이트 구동회로의 오동작을 방지할 수 있다.

이상 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

#### (57) 청구의 범위

##### 청구항 1.

표시영역과 상기 표시영역에 인접하는 주변영역을 갖는 제1 기판, 상기 표시영역에 대응하여 상기 제1 기판 상에 구비된 화소 어레이, 상기 주변영역에 대응하여 상기 제1 기판 상에 구비되고 상기 화소 어레이를 구동하는 구동회로 및 상기 화소 어레이와 상기 구동회로를 커버하는 제1 배향막을 포함하는 어레이 기판;

상기 제1 배향막 상에 구비된 액정층; 및

상기 액정층 상에 구비된 제2 배향막 및 상기 제2 배향막 상에 구비되어 상기 제1 기판과 마주하는 제2 기판을 포함하는 대향 기판을 포함하는 것을 특징으로 하는 액정표시장치.

##### 청구항 2.

제1항에 있어서, 상기 제1 배향막은 상기 구동회로를 전체적으로 커버하는 것을 특징으로 하는 액정표시장치.

##### 청구항 3.

제1항에 있어서, 상기 제1 배향막은 500 ~ 1500Å의 두께를 갖는 것을 특징으로 하는 액정표시장치.

##### 청구항 4.

제1항에 있어서, 상기 화소 어레이는,

다수의 박막 트랜지스터;

상기 박막 트랜지스터를 커버하고, 상기 박막 트랜지스터의 드레인 전극을 노출시키는 콘택홀이 형성된 보호막; 및

상기 보호막 상에 구비되고 상기 드레인 전극을 통해 상기 박막 트랜지스터와 전기적으로 연결된 화소전극을 포함하는 것을 특징으로 하는 액정표시장치.

##### 청구항 5.

제1항에 있어서, 상기 대향기판은,

상기 제2 배향막 상에 구비된 공통전극; 및

다수의 색화소로 이루어져 상기 공통전극과 상기 제2 기판과의 사이에 개재된 컬러필터층을 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 6.

제5항에 있어서, 상기 공통전극의 하부에 구비된 상기 제2 배향막은 상기 공통전극을 전체적으로 커버하고,

상기 제2 배향막은 500 ~ 1500Å의 두께를 갖는 것을 특징으로 하는 액정표시장치.

도면

도면1

도면2

도면3

500

도면4

|                |                                             |         |            |

|----------------|---------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                       |         |            |

| 公开(公告)号        | <a href="#">KR1020060033100A</a>            | 公开(公告)日 | 2006-04-19 |

| 申请号            | KR1020040082045                             | 申请日     | 2004-10-14 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                    |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                    |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                    |         |            |

| [标]发明人         | HAN HYERHEE<br>한혜리<br>MOON SEUNGHWAN<br>문승환 |         |            |

| 发明人            | 한혜리<br>문승환                                  |         |            |

| IPC分类号         | G02F1/1337                                  |         |            |

| CPC分类号         | G02F1/133711 G02F1/133723                   |         |            |

| 代理人(译)         | PARK , YOUNG WOO                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                   |         |            |

## 摘要(译)

公开了一种能够防止故障的液晶显示器。液晶显示器包括阵列面板，阵列面板，面对的相对板，以及允许阵列面板和相对板之间的液晶层。阵列面板包括基板，像素阵列和驱动电路，以及配向层。基板包括显示区域和与显示区域相邻的外围区域。像素阵列对应于显示区域，并且基板配备在基板上。它对应于外围区域，驱动电路配备在基板上，驱动电路驱动像素阵列。对准层覆盖像素阵列和驱动电路。因此，可以防止驱动电路的故障。