# (19)대한민국특허청(KR) (12) 공개특허공보(A)

(51) . Int. Cl. G02F 1/1343 (2006.01) G02F 1/136 (2006.01)

(11) 공개번호

10-2006-0131020

(43) 공개일자

2006년12월20일

(21) 출원번호

10-2005-0050847

(22) 출원일자

2005년06월14일

심사청구일자

없음

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

이준우

경기 안양시 동안구 관양2동 인덕원 삼성아파트 112동 204호

하은희

서울 서초구 양재1동 90번지 신영체르니아파트 814호

김희섭

경기 화성시 태안읍 반월리 865-1번지 신영통 현대아파트 110동304호

이창훈

경기 용인시 기흥읍 서천리 705번지 예현마을 현대홈타운 104동1205호

(74) 대리인

유미특허법인

전체 청구항 수 : 총 16 항

## (54) 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치

#### (57) 요약

본 발명에 따른 박막 트랜지스터 표시판은 기판, 기판 위에 형성되어 있는 복수의 게이트선, 기판 위에 형성되어 있으며 투명한 도전체로 이루어진 복수의 공통 전극, 게이트선 및 공통 전극 위에 형성되어 있는 게이트 절연막, 게이트 절연막 위에 형성되어 있는 반도체층, 반도체층 위에 형성되어 있으며, 소스 전극을 포함하는 데이터선 및 소스 전극과 마주하고 있는 드레인 전극, 그리고 드레인 전극과 연결되어 있으며 공통 전극과 중첩하고 있는 복수의 화소 전극을 포함하고, 공통 전극은 복수개의 절개부를 가지는 것이 바람직하다. 본 발명에 따른 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치는 하나의 기판에 형성된 공통 전극 위에 화소 전극을 중첩되게 배치함으로써, 시야각을 넓힐 수 있고, 구동 전압을 낮출수 있으며, 개구율을 크게 할 수 있다. 또한, 공통 전극에 절개부를 형성하고, 절개부의 크기를 조절함으로써 화소 전극과 공통 전극이 중첩되는 부분의 면적을 변경하여 유지 축전기의 유지 용량을 용이하게 조절할 수 있다.

#### 대표도

도 1

#### 특허청구의 범위

## 청구항 1.

기판,

상기 기판 위에 형성되어 있는 복수의 게이트선,

상기 기판 위에 형성되어 있으며 투명한 도전체로 이루어진 복수의 공통 전극,

상기 게이트선 및 공통 전극 위에 형성되어 있는 게이트 절연막,

상기 게이트 절연막 위에 형성되어 있는 반도체층,

상기 반도체층 위에 형성되어 있으며, 소스 전극을 포함하는 데이터선 및 상기 소스 전극과 마주하고 있는 드레인 전극, 그리고

상기 드레인 전극과 연결되어 있으며 상기 공통 전극과 중첩하고 있는 복수의 화소 전극

을 포함하고,

상기 공통 전극은 복수개의 절개부를 가지는 박막 트랜지스터 표시판.

## 청구항 2.

제1항에서,

상기 복수개의 절개부는 선 형상, 사각 형상, 원형 형상, 사선 형상, 마름모 형상 또는 육각 형상 중에서 선택된 어느 하나인 박막 트랜지스터 표시판.

### 청구항 3.

제1항에서,

상기 공통 전극은 상기 화소 전극 사이에서 연속적인 면으로 이루어져 있는 박막 트랜지스터 표시판.

#### 청구항 4.

제1항에서,

상기 화소 전극과 상기 공통 전극은 일부 중첩되어 유지 축전기를 이루는 박막 트랜지스터 표시판.

## 청구항 5.

제1항에서,

상기 화소 전극은 데이터선과 평행한 방향으로 복수개의 가지가 선형으로 뻗어있으며, 상기 공통 전극의 절개부는 상기 화소 전극에 대응하는 위치에 형성되어 있는 박막 트랜지스터 표시판.

### 청구항 6.

제1 기판, 상기 제1 기판 위에 형성되어 있는 복수의 게이트선, 상기 제1 기판 위에 형성되어 있으며 투명한 도전체로 이루어진 복수의 공통 전극, 상기 게이트선 및 공통 전극 위에 형성되어 있는 게이트 절연막, 상기 게이트 절연막 위에 형성되어 있는 반도체층, 상기 반도체층 위에 형성되어 있으며, 소스 전극을 포함하는 데이터선 및 상기 소스 전극과 마주하고 있는 드레인 전극, 그리고 상기 드레인 전극과 연결되어 있으며 상기 공통 전극과 중첩하고 있는 복수의 화소 전극을 포함하고, 상기 공통 전극은 복수개의 절개부를 가지는 박막 트랜지스터 표시판.

상기 제2 기판과 대향하고 있는 제2 기판, 상기 제2 기판 위에 형성되어 있는 색필터를 포함하는 색필터 표시판,

상기 박막 트랜지스터 표시판 및 색필터 표시판 사이에 주입되어 있는 액정층

을 포함하는 액정 표시 장치.

#### 청구항 7.

제6항에서.

상기 복수개의 절개부는 선 형상, 사각 형상, 원형 형상, 사선 형상, 마름모 형상 또는 육각 형상 중에서 선택된 어느 하나인 액정 표시 장치.

#### 청구항 8.

제6항에서.

상기 공통 전극은 상기 화소 전극 사이에서 연속적인 면으로 이루어져 있는 액정 표시 장치.

## 청구항 9.

제6항에서,

상기 화소 전극과 상기 공통 전극은 일부 중첩되어 유지 축전기를 이루는 박막 트랜지스터 표시판.

### 청구항 10.

제6항에서,

상기 화소 전극은 상기 데이터선과 평행한 방향으로 복수개의 가지가 선형으로 뻗어있으며, 상기 공통 전극의 절개부는 상기 화소 전극에 대응하는 위치에 형성되어 있는 박막 트랜지스터 표시판.

## 청구항 11.

제6항에서,

하나의 화소는 적어도 하나의 상기 화소 전극과 공통 전극으로 이루어지며, 상기 공통 전극은 인접한 화소의 공통 전극과 연결되어 있는 액정 표시 장치.

#### 청구항 12.

제6항에서.

상기 공통 전극 및 화소 전극이 중첩되는 부분에 대응하는 액정층의 일부가 화상 표시 영역의 일부가 되는 액정 표시 장치.

### 청구항 13.

제6항에서.

상기 화상 표시 영역의 액정 분자들은 비틀림각 및 경사각을 가지는 액정 표시 장치.

## 청구항 14.

제6항에서.

상기 공통 전극 및 화소 전극 사이에 발생하는 전기장은 포물선 모양의 전기력선이며, 상기 전기력선은 상기 공통 전극 또는 화소 전극 위에서 수직 및 수평 성분을 가지는 액정 표시 장치.

## 청구항 15.

제10항에서.

서로 이웃하는 상기 공통 전극의 절개부 사이의 간격은 상기 선형의 화소 전극의 폭보다 큰 액정 표시 장치.

#### 청구항 16.

제6항에서,

상기 제1 및 제2 기판의 바깥면에 각각 부착되어 있는 편광판을 더 포함하는 액정 표시 장치.

#### 명세서

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치에 관한 것이다.

일반적으로 액정 표시 장치는 양 기판 또는 한 기판의 내면에 전극을 가지고 있으며, 광학적 스위칭 매개체로서 두 전극 사이에 액정 물질층을 둔 표시 장치로서, 양 전극에 전위차를 주면 그 전위차로 인하여 액정 분자들이 재배열되고, 재배열된 액정 분자들이 빛을 산란시키거나 빛의 투과 특성을 변화시킴으로써 화상을 표시한다.

종래의 액정 표시 장치의 한 예로서, 아래 위 두 기판의 내면에 각각 형성되어 있는 위 전극과 아래 전극 사이에 네마틱 액정 물질이 삽입되어 있으며, 액정 분자들은 기판에 평행하게 비틀려 배향되어 있는 미국 특허 제5,576,861호에 개시된 비틀린 네마틱 액정 표시 장치를 들 수 있다. 이 액정 표시 장치에서는 아래 위 전극에 전압을 인가하여 전위차를 주면 양 기

판에 수직한 전기장이 형성되고, 액정 분자의 장축을 전기장의 방향과 평행하게 배열시키려는 토크(torque)(이 토크의 크기는 전기장의 세기에 의존함), 즉 유전율 이방성으로 인한 토크와 러빙 등의 배향 처리를 통하여 발생하며 액정 분자의 장축 방향을 특정한 방향을 향하도록 배열시키려는 탄성 토크가 평형을 이루도록 액정 분자들이 재배열된다.

종래의 액정 표시 장치의 또 다른 예로는, 한쪽 기판 위에 줄 모양의 두 전극을 서로 평행하게 배치하고 그 사이에 액정 물질층을 두며, 액정 분자들은 기판에 평행하게 배향한 미국 특허 제5,598,285호에 개시되어 있는 액정 표시 장치를 들 수 있다. 이 액정 표시 장치에서는 전극 사이에 전위차를 주어, 본질적으로 기판에 평행하고 두 전극에 수직한 방향으로 전기장을 형성하고, 액정 물질의 유전율 이방성으로 인한 토크와 배향 처리로 인한 탄성 토크가 평형을 이루도록 액정 분자들이 재배열한다.

이러한 종래의 액정 표시 장치는 각각 문제점을 가지고 있다.

비틀린 네마틱형 액정 표시 장치의 가장 큰 문제점은 시야각이 좁다는 것이다. 이 액정 표시 장치에서는 표시 장치를 바라보는 사람의 눈의 방향과 표시 장치의 표면에 수직인 방향과 이루는 각이 커질수록, 액정 분자들의 장축 방향과 단축 방향의 굴절률 차이인 복굴절성(△n)과 액정층의 두께(d)의 곱, 즉 △n·d 값이 커지고, 이에 따라 대비비가 급격히 저하된다. 그 뿐 아니라, 밝기가 뒤바뀌는 계조 반전의 현상도 나타난다. 따라서 시야각이 매우 좁고, 그 시야각보다 큰 각도로 표시장치를 바라보는 경우 정면에서 보는 화상에 비하여 화질이 급격히 나빠진다.

시야각을 보상하기 위하여, 앞에서 언급한 미국 특허 제5,576,861호에서와 같이, 위상차 보상판 등을 이용하여 시야각을 넓히는 방법이 제시되고 있으나, 부가적인 부분인 보상판을 부착하는 부가적인 공정이 필요하기 때문에 비용이 높아지고 공정이 늘어날 뿐 아니라, 보상판을 사용하더라도 시야각의 한계는 여전히 남아 있다.

두 번째 장치에서는 두 전극 사이의 영역에 위치하는 전기장이 두 전극으로부터 멀어질수록 작아지기 때문에, 노멀리 블랙모드(normally black mode)에서 빛을 통과시키기 위한 최소의 전압(문턱 전압)이 높을 뿐 아니라 빛을 최대한 통과시키는 전압(포화 전압) 또한 높아서 전체적으로 소비 전력이 커지는 문제점이 있다. 또한 모든 전극이 하나의 기판에 형성되어 있을 뿐 아니라, 충분한 정전 용량을 확보하기 위하여 화소 전극과 공통 전극이 절연막을 사이에 두고 중첩되는 부분을 두어야 하므로 빛이 통과하는 개구율이 작아지는 문제점이 있다.

#### 발명이 이루고자 하는 기술적 과제

본 발명의 기술적 과제는 넓은 시야각을 확보하고, 낮은 전압으로 액정을 구동하여 소비 전력을 낮추며, 개구율을 크게 하는 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치를 제공하는 것이다.

또한, 본 발명의 다른 기술적 과제는 유지 축전기의 유지 용량을 용이하게 조절할 수 있는 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치를 제공하는 것이다.

#### 발명의 구성

본 발명에 따른 박막 트랜지스터 표시판은 기판, 상기 기판 위에 형성되어 있는 복수의 게이트선, 상기 기판 위에 형성되어 있으며 투명한 도전체로 이루어진 복수의 공통 전극, 상기 게이트선 및 공통 전극 위에 형성되어 있는 게이트 절연막, 상기 게이트 절연막 위에 형성되어 있는 반도체층, 상기 반도체층 위에 형성되어 있으며, 소스 전극을 포함하는 데이터선 및 상기 소스 전극과 마주하고 있는 드레인 전극, 그리고 상기 드레인 전극과 연결되어 있으며 상기 공통 전극과 중첩하고 있는 복수의 화소 전극을 포함하고, 상기 공통 전극은 복수개의 절개부를 가지는 것이 바람직하다.

또한, 상기 복수개의 절개부는 선 형상, 사각 형상, 원형 형상, 사선 형상, 마름모 형상 또는 육각 형상 중에서 선택된 어느 하나인 것이 바람직하다.

또한, 상기 공통 전극은 상기 화소 전극 사이에서 연속적인 면으로 이루어져 있는 것이 바람직하다.

또한, 상기 화소 전극과 상기 공통 전극은 일부 중첩되어 유지 축전기를 이루는 것이 바람직하다.

또한, 상기 화소 전극은 데이터선과 평행한 방향으로 복수개의 가지가 선형으로 뻗어있으며, 상기 공통 전극의 절개부는 상기 화소 전극에 대응하는 위치에 형성되어 있는 것이 바람직하다. 또한, 본 발명에 따른 액정 표시 장치는 제1 기판, 상기 제1 기판 위에 형성되어 있는 복수의 게이트선, 상기 제1 기판 위에 형성되어 있으며 투명한 도전체로 이루어진 복수의 공통 전극, 상기 게이트선 및 공통 전극 위에 형성되어 있는 게이트 절연막, 상기 게이트 절연막 위에 형성되어 있는 반도체층, 상기 반도체층 위에 형성되어 있으며, 소스 전극을 포함하는 데이터선 및 상기 소스 전극과 마주하고 있는 드레인 전극, 그리고 상기 드레인 전극과 연결되어 있으며 상기 공통 전극과 중첩하고 있는 복수의 화소 전극을 포함하고, 상기 공통 전극은 복수개의 절개부를 가지는 박막 트랜지스터 표시판, 상기 제2 기판과 대향하고 있는 제2 기판, 상기 제2 기판 위에 형성되어 있는 색필터를 포함하는 색필터 표시판, 상기 박막 트랜지스터 표시판 및 색필터 표시판 사이에 주입되어 있는 액정층을 포함하는 것이 바람직하다.

또한, 상기 복수개의 절개부는 선 형상, 사각 형상, 원형 형상, 사선 형상, 마름모 형상 또는 육각 형상 중에서 선택된 어느 하나인 것이 바람직하다.

또한, 상기 공통 전극은 상기 화소 전극 사이에서 연속적인 면으로 이루어져 있는 것이 바람직하다.

또한, 상기 화소 전극과 상기 공통 전극은 일부 중첩되어 유지 축전기를 이루는 것이 바람직하다.

또한, 상기 화소 전극은 상기 데이터선과 평행한 방향으로 복수개의 가지가 선형으로 뻗어있으며, 상기 공통 전극의 절개 부는 상기 화소 전극에 대응하는 위치에 형성되어 있는 것이 바람직하다.

또한, 하나의 화소는 적어도 하나의 상기 화소 전극과 공통 전극으로 이루어지며, 상기 공통 전극은 인접한 화소의 공통 전극과 연결되어 있는 것이 바람직하다.

또한, 상기 공통 전극 및 화소 전극이 중첩되는 부분에 대응하는 액정층의 일부가 화상 표시 영역의 일부가 되는 것이 바람 직하다.

또한, 상기 화상 표시 영역의 액정 분자들은 비틀림각 및 경사각을 가지는 것이 바람직하다.

또한, 상기 공통 전극 및 화소 전극 사이에 발생하는 전기장은 포물선 모양의 전기력선이며, 상기 전기력선은 상기 공통 전극 또는 화소 전극 위에서 수직 및 수평 성분을 가지며, 서로 이웃하는 상기 공통 전극의 절개부 사이의 간격은 상기 선형의 화소 전극의 폭보다 큰 것이 바람직하다.

또한, 상기 제1 및 제2 기판의 바깥면에 각각 부착되어 있는 편광판을 더 포함하는 것이 바람직하다.

그러면, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 본 발명의 실시예에 대하여 첨부한 도면을 참고로 하여 상세히 설명한다. 그러나 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명 하는 실시예에 한정되지 않는다.

도면에서 여러 층 및 영역을 명확하게 표현하기 위하여 두께를 확대하여 나타내었다. 명세서 전체를 통하여 유사한 부분에 대해서는 동일한 도면 부호를 붙였다. 층, 막, 영역, 판 등의 부분이 다른 부분 "위에" 있다고 할 때, 이는 다른 부분 "바로 위에" 있는 경우뿐 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다. 반대로 어떤 부분이 다른 부분 "바로 위에" 있다고 할 때에는 중간에 다른 부분이 없는 것을 뜻한다.

이제 본 발명의 실시예에 따른 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치에 대하여 도면을 참고로 하여 상세하게 설명한다.

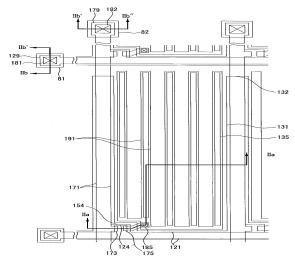

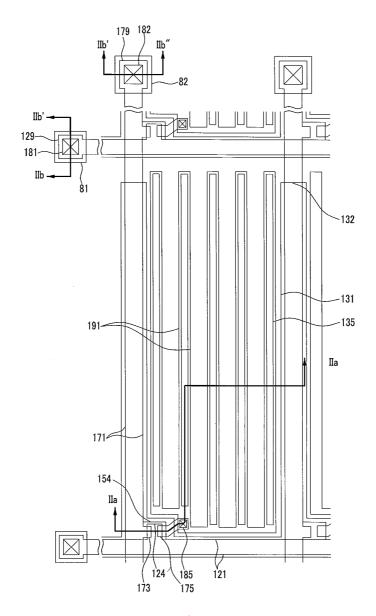

먼저, 도 1, 도 2a 및 도 2b를 참고로 하여 본 발명의 바람직한 한 실시예에 따른 박막 트랜지스터 표시판에 대하여 상세히 설명한다.

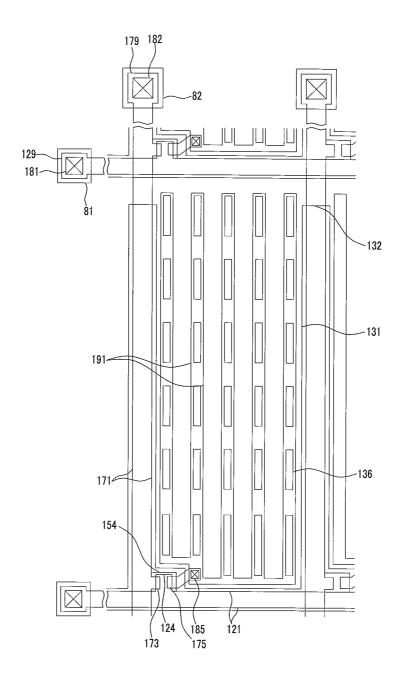

도 1은 본 발명의 한 실시예에 따른 액정 표시 장치용 박막 트랜지스터 표시판의 배치도이고, 도 2a는 도 1의 박막 트랜지스터 표시판을 IIa-IIa 선을 따라 잘라 도시한 단면도이고, 도 2b는 도 1의 박막 트랜지스터 표시판을 IIb-IIb' 선 및 IIb'-IIb' 선을 따라 잘라 도시한 단면도이다.

투명한 유리 또는 플라스틱 따위로 만들어진 절연 기판(110) 위에 복수의 게이트선(gate line)(121) 및 공통 전극 (common electrode)(131)이 형성되어 있다.

게이트선(121)은 게이트 신호를 전달하며 주로 가로 방향으로 뻗어 있다. 각 게이트선(121)은 위로 돌출한 복수의 게이트 전극(gate electrode)(124)과 다른 층 또는 외부 구동 회로와의 접속을 위하여 면적이 넓은 끝 부분(129)을 포함한다.

게이트 신호를 생성하는 게이트 구동 회로(도시하지 않음)는 집적 회로 칩의 형태로 기판(110) 위에 부착되는 가요성 인쇄 회로막(flexible printed circuit film)(도시하지 않음) 위에 장착되거나, 기판(110) 위에 직접 장착될 수 있고, 또는 기판 (110)에 집적될 수 있다. 게이트 구동 회로가 기판(110) 위에 집적되어 있는 경우 게이트선(121)이 연장되어 이와 직접 연결될 수 있다.

공통 전극(131)은 공통 전압(common voltage)을 인가 받으며 게이트선(121) 사이의 공간을 거의 채우며 배치되어 있다. 공통 전극(131)은 가로 방향으로 길게 뻗어 있으며 공통 전극(131)의 밑면의 일부(132)는 오목한 모양으로 길게 파여져 있다. 그리고, 공통 전극(131)은 세로 방향으로 긴 절개부(135)를 복수개 가지며, 복수개의 절개부(135)는 서로 동일한 간 격을 유지하며 형성되어 있다.

게이트선(121)은 알루미늄(Al)이나 알루미늄 합금 등 알루미늄 계열 금속,은(Ag)이나 은 합금 등 은 계열 금속,구리(Cu)나 구리 합금 등 구리 계열 금속,몰리브덴(Mo)이나 몰리브덴 합금 등 몰리브덴 계열 금속,크롬(Cr), 탄탈륨(Ta) 및 티타늄(Ti) 따위로 만들어질 수 있다. 그러나 이들은 물리적 성질이 다른 두 개의 도전막(도시하지 않음)을 포함하는 다중막 구조를 가질 수도 있다.이 중 한 도전막은 신호 지연이나 전압 강하를 줄일 수 있도록 비저항(resistivity)이 낮은 금속,예를 들면 알루미늄 계열 금속,은 계열 금속,구리 계열 금속 등으로 만들어진다.이와는 달리,다른 도전막은 다른 물질,특히 ITO(indium tin oxide) 및 IZO(indium zinc oxide)와의 물리적,화학적,전기적 접촉 특성이 우수한 물질,이를테면 몰리브덴 계열 금속,크롬,탄탈륨,티타늄 등으로 만들어진다.이러한 조합의 좋은 예로는 크롬 하부막과 알루미늄(합금)상부막 및 알루미늄(합금)하부막과 몰리브덴(합금)상부막을 들 수 있다.그러나 게이트선(121)은 이외에도 여러 가지 다양한 금속 또는 도전체로 만들어질 수 있다.

공통 전극(131)은 ITO(indium tin oxide) 또는 IZO(indium zinc oxide) 등의 투명한 도전 물질로 만들어질 수 있다.

게이트선(121) 및 공통 전극(131)의 측면은 기판(110) 면에 대하여 경사져 있으며 그 경사각은 약 30도 내지 약 80도인 것이 바람직하다.

게이트선(121) 및 공통 전극(131) 위에는 질화규소(SiNx) 또는 산화규소(SiOx) 따위로 만들어진 게이트 절연막(gate insulating layer)(140)이 형성되어 있다. 게이트 절연막(140)은 게이트선(121) 및 공통 전극(131)이 서로 단락되는 것을 방지하고, 이들 위에 형성되는 다른 도전성 박막과의 절연을 도모한다.

게이트 절연막(140) 위에는 수소화 비정질 규소(hydrogenated amorphous silicon)(비정질 규소는 약칭 a-Si로 씀) 또는 다결정 규소(polysilicon) 등으로 만들어진 복수의 선형 반도체(151)가 형성되어 있다. 선형 반도체(151)는 주로 세로 방향으로 뻗어 있으며, 게이트 전극(124)을 향하여 뻗어 나온 복수의 돌출부(projection)(154)를 포함한다.

반도체(151) 위에는 복수의 선형 및 섬형 저항성 접촉 부재(ohmic contact)(161, 165)가 형성되어 있다. 저항성 접촉 부재(161, 165)는 인 따위의 n형 불순물이 고농도로 도핑되어 있는 n+ 수소화 비정질 규소 따위의 물질로 만들어지거나 실리사이드(silicide)로 만들어질 수 있다. 선형 저항성 접촉 부재(161)는 복수의 돌출부(163)를 가지고 있으며, 이 돌출부(163)와 섬형 저항성 접촉 부재(165)는 쌍을 이루어 반도체(151)의 돌출부(154) 위에 배치되어 있다.

반도체(151)와 저항성 접촉 부재(161, 165)의 측면 역시 기판(110) 면에 대하여 경사져 있으며 경사각은 30도 내지 80도 정도이다.

저항성 접촉 부재(161, 165) 위에는 복수의 데이터선(data line)(171)과 복수의 드레인 전극(drain electrode)(175)이 형성되어 있다.

데이터선(171)은 데이터 신호를 전달하며 주로 세로 방향으로 뻗어 게이트선(121)과 교차한다. 각 데이터선(171)은 게이트 전극(124)을 향하여 뻗은 복수의 소스 전극(source electrode)(173)과 다른 층 또는 외부 구동 회로와의 접속을 위하여 면적이 넓은 끝 부분(179)을 포함한다. 데이터 신호를 생성하는 데이터 구동 회로(도시하지 않음)는 기판(110) 위에 부착되는 가요성 인쇄 회로막(도시하지 않음) 위에 장착되거나, 기판(110) 위에 직접 장착되거나, 기판(110)에 집적될 수 있다. 데이터 구동 회로가 기판(110) 위에 집적되어 있는 경우, 데이터선(171)이 연장되어 이와 직접 연결될 수 있다.

드레인 전극(175)은 데이터선(171)과 분리되어 있고 게이트 전극(124)을 중심으로 소스 전극(173)과 마주 본다.

하나의 게이트 전극(124), 하나의 소스 전극(173) 및 하나의 드레인 전극(175)은 반도체(151)의 돌출부(154)와 함께 하나의 박막 트랜지스터(thin film transistor, TFT)를 이루며, 박막 트랜지스터의 채널(channel)은 소스 전극(173)과 드레인 전극(175) 사이의 돌출부(154)에 형성된다.

데이터선(171) 및 드레인 전극(175)은 몰리브덴, 크롬, 탄탈륨 및 티타늄 등 내화성 금속(refractory metal) 또는 이들의합금으로 만들어지는 것이 바람직하며, 내화성 금속막(도시하지 않음)과 저저항 도전막(도시하지 않음)을 포함하는 다중막 구조를 가질 수 있다. 다중막 구조의 예로는 크롬 또는 몰리브덴 (합금) 하부막과 알루미늄 (합금) 상부막의 이중막, 몰리브덴 (합금) 하부막과 알루미늄 (합금) 중간막과 몰리브덴 (합금) 상부막의 삼중막을 들 수 있다. 그러나 데이터선(171) 및 드레인 전극(175)은 이외에도 여러 가지 다양한 금속 또는 도전체로 만들어질 수 있다.

저항성 접촉 부재(161, 165)는 그 아래의 반도체(151)와 그 위의 데이터선(171) 및 드레인 전극(175) 사이에만 존재하며 이들 사이의 접촉 저항을 낮추어 준다. 반도체(151)는 데이터선(171), 드레인 전극(175) 및 그 아래의 저항성 접촉 부재 (161, 165)와 실질적으로 동일한 평면 모양이다. 그러나 반도체(151)에는 소스 전극(173)과 드레인 전극(175) 사이를 비롯하여 데이터선(171) 및 드레인 전극(175)으로 가리지 않고 노출된 부분이 있다.

데이터선(171), 드레인 전극(175) 및 노출된 반도체(151) 부분 위에는 보호막(passivation layer)(180)이 형성되어 있다. 보호막(180)은 무기 절연물로 만들어지며, 무기 절연물의 예로는 질화규소와 산화규소를 들 수 있다. 그러나 보호막(180)은 유기막의 우수한 절연 특성을 살리면서도 노출된 반도체(151) 부분에 해가 가지 않도록 하부 무기막과 상부 유기막의 이중막 구조를 가질 수 있다.

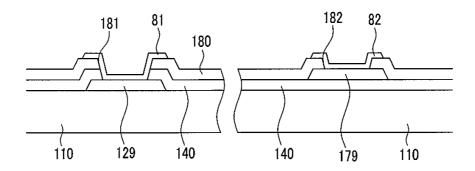

보호막(180)에는 데이터선(171)의 끝 부분(179)과 드레인 전극(175)을 각각 드러내는 복수의 접촉 구멍(contact hole) (182, 185)이 형성되어 있으며, 보호막(180)과 게이트 절연막(140)에는 게이트선(121)의 끝 부분(129)을 드러내는 복수의 접촉 구멍(181)이 형성되어 있다.

보호막(180) 위에는 복수의 화소 전극(pixel electrode)(191) 및 복수의 접촉 보조 부재(contact assistant)(81, 82)가 형성되어 있다. 이들은 ITO(indium tin oxide) 또는 IZO(indium zinc oxide) 등의 투명한 도전 물질로 만들어질 수 있다.

화소 전극(191)은 주로 세로 방향으로 뻗어 공통 전극(131)과 중첩한다. 이 때, 화소 전극(191)의 하단은 서로 연결되어 있다. 화소 전극(191)은 데이터선(171)과 평행한 방향으로 복수개의 가지가 선형으로 뻗어있다. 공통 전극(131)이 데이터선(171)과 중첩되는 부분은 기생용량이 발생하여 화상 신호를 지연시키므로 공통 전극(131) 중에서 데이터선(171)과 중첩되는 부분은 제거하고 일부(132)만을 남겨두어 인접하는 공통 전극(131)을 서로 연결한다.

화소 전극(191)은 공통 전극(131)의 절개부(135)에 대응하는 위치에 형성되며, 화소 전극(191)의 가장자리는 공통 전극(131)의 가장자리와 중첩되어 있다. 따라서, 화소 전극(191)과 공통 전극(131)은 유지 축전기를 이루어 박막 트랜지스터가 턴 오프된 후에도 인가된 전압을 유지한다. 이러한 공통 전극(131)의 절개부(135)의 크기를 조절함으로써 화소 전극(191)과 공통 전극(131)이 중첩되는 부분(X, Y)의 면적을 변경하여 유지 축전기의 유지 용량을 조절할 수 있다.

화소 전극(191)은 접촉 구멍(185)을 통하여 드레인 전극(175)과 물리적·전기적으로 연결되어 있으며, 드레인 전극(175)으로부터 데이터 전압을 인가 받는다. 데이터 전압이 인가된 화소 전극(191)은 공통 전압을 인가 받는 공통 전극(131)과함께 전기장을 생성함으로써 두 전극(191, 131) 위에 위치하는 액정층(도시하지 않음)의 액정 분자의 방향을 결정한다. 이와 같이 결정된 액정 분자의 방향에 따라 액정층을 통과하는 빛의 편광이 달라진다.

접촉 보조 부재(81, 82)는 각각 접촉 구멍(181, 182)을 통하여 게이트선(121)의 끝 부분(129) 및 데이터선(171)의 끝 부분(179)과 연결된다. 접촉 보조 부재(81, 82)는 게이트선(121)의 끝 부분(129) 및 데이터선(171)의 끝 부분(179)과 외부 장치와의 접착성을 보완하고 이들을 보호한다.

이하에서 본 발명의 한 실시예에 따른 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치에 의해 액정 표시 장치가 동작하는 방법에 대해 상세히 설명한다.

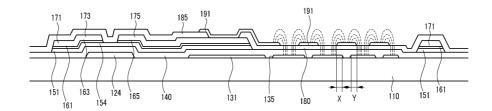

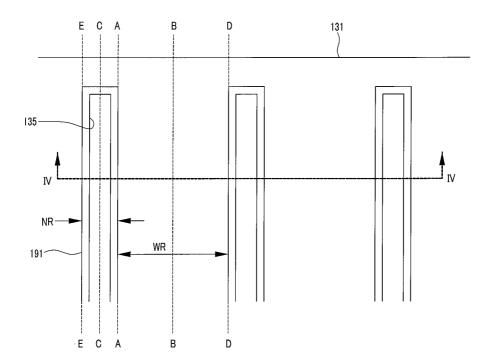

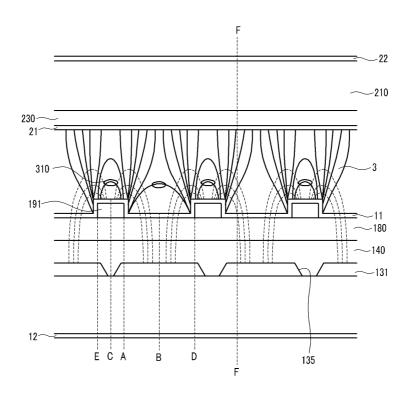

도 3은 본 발명의 한 실시예에 따른 박막 트랜지스터 표시판의 전극을 나타내는 배치도이고, 도 4는 도 3에서 IV-IV 선을 잘라 도시한 액정 표시 장치의 단면도로서, 상부 기판 및 하부 기판 사이의 등전위선 및 전기력선을 함께 도시한 도면이다.

도 3 및 도 4에 도시한 바와 같이, 하부 기판(110) 위에는 면형의 공통 전극(131)이 형성되어 있으며, 공통 전극(131) 위에는 게이트 절연막(140) 및 보호막(180)이 덮여 있고, 보호막(180) 위에는 폭이 좁은 다수의 화소 전극(191)이 세로 방향으로 서로 평행하게 형성되어 있다. 화소 전극(191)의 폭은 화소 전극(191)사이의 간격보다 작다. 화소 전극(191) 위에는 폴리이미드(polyimide) 따위의 물질로 만들어진 배향막(alignment layer)(11)이 도포되어 있으며 이들은 수평 배향막일수 있다. 하부 기판(110)의 바깥 면에는 편광판(12)이 부착되어 있다.

상부 기판(210) 위에는 색필터(230)가 형성되어 있으며, 색필터(230) 위에는 폴리이미드 따위의 물질로 만들어진 배향막(21)이 도포되어 있으며 이들은 수평 배향막일 수 있다. 상부 기판(210)의 바깥 면에는 편광판(22)이 부착되어 있다.

그리고, 두 기판(110, 211)의 배향막(11, 21) 사이에는 양의 유전율 이방성을 가지는 액정층(3)이 주입되어 있다. 따라서, 액정층(3)의 액정 분자는 전기장이 없는 상태에서 그 장축이 화소 전극(191)의 방향과 평행하도록 배향되어 있으며, 전압이 인가된 경우에는 그 장축이 화소 전극(191)의 방향과 수직하도록 배향되며 이에 따라 액정층을 통과하는 빛의 편광이달라진다.

이러한 액정 표시 장치는 하부 기판(110)의 하부에 위치하는 조명부(backlight unit)(도시하지 않음)로부터 발생한 빛의 투과율을 조절하여 표시 동작을 할 수도 있지만, 반사형 액정 표시 장치의 경우에는 아래 편광판(12)은 필요하지 않다. 반사형 액정 표시 장치의 경우에는 화소 전극(191)과 공통 전극(131) 모두를 불투명하고 반사율이 높은 알루미늄(AI) 등의 물질로 만드는 것이 바람직하다.

도 4에 도시한 바와 같이, 이러한 액정 표시 장치의 공통 전극(131) 및 화소 전극(191)에 전압을 인가하여 전위차를 주면 전기장이 생성된다. 도 4에 실선으로 도시한 것은 등전위선이며, 점선으로 도시한 것은 전기력선이다.

전기장의 형태는 화소 전극(191) 위의 좁은 영역(NR)의 세로 방향 중앙선(C)(실제로는 면에 해당함) 및 화소 전극(191) 사이의 넓은 영역(WR)의 세로 방향 중앙선(B)(실제로는 면에 해당함)에 대하여 대칭이다. 좁은 영역(NR)의 중앙선(C)으로부터 넓은 영역(WR)의 중앙선(B)까지의 영역에는 좁은 영역(NR)과 넓은 영역(WR)의 경계선(A)(실제로는 면에 해당함)에 정점을 두고 있는 반타원 모양 또는 포물선 모양(이하에서는 편의상 반타원 모양인 것으로 설명한다)의 전기력선 형태를 가지는 전기장이 생성된다. 전기력선의 접선은 좁은 영역(NR)과 넓은 영역(WR)의 경계선(A) 상에서 기판(10)에 대하여 거의 평행하고, 좁은 영역(NR) 및 넓은 영역(WR)의 중앙 위치에서는 기판(10)에 대하여 거의 수직이 된다. 또한, 타원의 중심 및 세로 방향 정점은 좁은 영역(NR)과 넓은 영역(WR)의 경계선(A) 상에 위치하고, 가로 방향의 두 정점은 각각 넓은 영역(WR) 및 좁은 영역(NR)에 위치한다. 이때, 좁은 영역(NR)에 위치하는 가로 방향 정점은 넓은 영역(WR)에 위치하는 가로 방향 정점에 비하여 타원의 중심으로부터의 거리가 짧기 때문에 타원은 경계선(A)에 대하여 대칭을 이루지 않는다. 또한, 전기력선의 밀도가 위치에 따라 달라지고 전기장의 세기도 이에 비례하여 달라진다. 따라서, 좁은 영역(NR)과 넓은 영역(WR) 사이의 경계선(A-A) 상에서 전기장의 세기가 가장 크고, 좁은 영역(NR) 및 넓은 영역(WR)의 중앙선(C-C, B-B)으로 갈수록, 그리고 상부 기판(210)으로 갈수록 작아진다.

그러면, 이러한 전기장에 의하여 액정 분자가 재배열된 상태를 기판에 수평인 성분과 이에 수직인 성분으로 나누어 살펴본다. 먼저, 초기 상태를 설명한다.

두 배향막(11, 21)은 러빙 또는 자외선 조사법으로 배향 처리되어, 액정 분자들이 모두 한 방향으로 배열하되 기판(110, 210)에 대하여 약간의 선경사각을 가지지만 거의 수평이 되고, 기판(110, 210)에 평행한 면상에서 볼 때 화소 전극(191) 방향 및 이에 수직인 방향에 대하여 일정 각을 이루도록 배열되어 있다. 편광판(12, 22)의 편광축은 서로 직교하도록 배치하며, 하부 편광판(12)의 편광축은 러빙 방향과 거의 일치한다.

다음, 화소 전극(191) 및 공통 전극(131)에 각각 전압을 인가하되, 화소 전극(191)에 높은 전압을 인가한다. 이 때 액정 분자의 배열은 전기장에 의한 힘(전기장의 방향과 세기에 의존)과 배향 처리로 인하여 발생하는 탄성 복원력이 평형을 이룸으로써 결정된다.

이러한 액정 분자의 재배열 상태를 기판에 평행한 성분과 수직인 성분으로 나누어 살펴본다. 설명의 편의상 기판에 수직인 방향을 z축, 기판과 평행하고 화소 전극(191) 방향에 수직인 방향을 x축, 화소 전극(191)의 방향에 평행한 방향을 y축으로 정한다. 즉, 도 3에서 왼쪽에서 오른쪽을 향하는 방향을 x축, 화소 전극(191)을 따라 아래에서 위로 향하는 방향을 y축, 도 4에서 하부 기판(110)에서 상부 기판(210)을 향하는 방향을 z축으로 정한다.

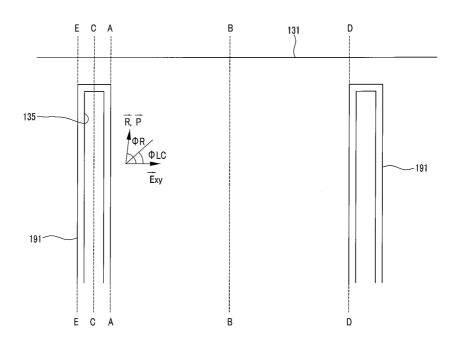

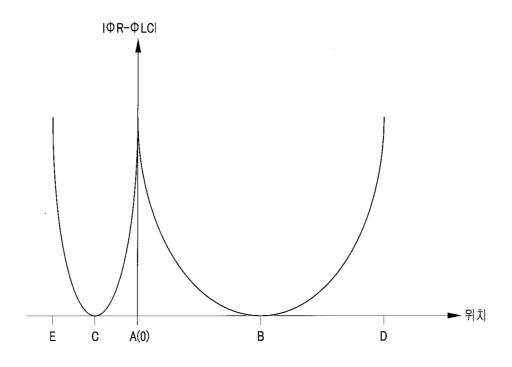

먼저, 액정 분자(310)의 비틀림각, 즉, x축 또는 초기 배열 방향에 대하여 액정 분자의 장축이 기판에 평행한 면(xy 평면) 위에서 이루는 각의 변화를 도 5, 도 6 및 도 7을 참고로 설명한다.

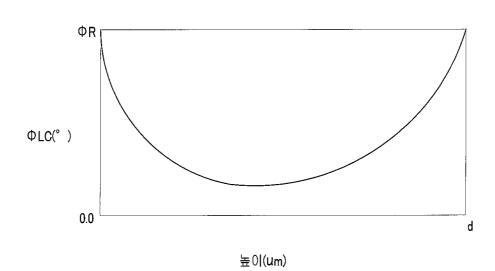

도 5는 본 발명의 한 실시예에서 액정 분자들의 비틀림각 변화를 설명하기 위한 도면이고, 도 6은 본 발명의 한 실시예에서 기판에 수평이고 화소 전극에 수직인 선에 대한 액정 분자들의 비틀림각 변화를 도시한 그래프이고, 도 7은 본 발명의 한 실시예에서 기판에 수직인 선에 대한 액정 분자들의 비틀림각 변화를 도시한 그래프이다.

도 5에 도시한 바와 같이, 러빙 방향은 벡터  $\overrightarrow{R}$ 로, 전기장의 x-y 평면 성분은 벡터  $\overrightarrow{E}_{xy}$ 로, 아래 편광판(12)의 광축은 벡터  $\overrightarrow{P}$ 로 나타내었으며, 러빙 방향이 x축과 이루는 각은  $\Psi$ R로, 액정 분자의 장축이 x축과 이루는 각을  $\Psi$ LC로 나타내었다. 그 런데 여기에서 아래 편광판(12)의 광축은 러빙 방향과 일치하므로 아래 편광판(12)의 광축이 x축과 이루는 각  $\Psi$ P= $\Psi$ R이다.

전기장의 x-y 평면 성분( $\overrightarrow{E}_{xy}$ )의 방향은 경계선(A)으로부터 넓은 영역(WR)의 중앙선(B)에 이르기까지는 양의 x 방향이고, 넓은 영역(WR)의 중앙선(B)으로부터 다음 경계선(D)까지는 음의 x 방향이다. 전기장 성분의 세기는 경계선(A, D) 상에서 가장 크고 중앙선(B-B) 쪽으로 갈수록 작아져 중앙선(B-B) 상에서는 0이 된다.

배향 처리에 의한 탄성적 복원력의 크기는 xy 평면 상에서는 위치에 관계없이 일정하다. 액정 분자들은 이러한 두 가지 힘이 평형을 이루도록 배열하여야 하므로, 도 6에 도시한 바와 같이, 경계선(A, D)에서는 액정 분자의 장축 방향이 전기장 성분( $\overrightarrow{E}_{xy}$ )에 대하여 거의 평행하고 러빙 방향에 대해서는 큰 각도를 가지지만, 영역(NR, WR)의 중심선(C, B)으로 갈수록 액정 분자의 장축이 러빙 방향에 대하여 이루는 각( $|\Psi R-\Psi LC|$ )이 작아지고, 중심선(B, C)에서는 액정 분자의 장축과 러빙 방향이 동일해진다. 아래 편광판(20)의 광축은 러빙 방향과 평행하므로, 아래 편광판(20)의 광축과 액정 분자의 장축이 이루는 각도도 이와 동일한 분포를 가지며, 이 값은 빛의 투과율과 밀접한 관련이 있다.

좁은 영역(NR)과 넓은 영역(WR)의 폭의 비를 변화시켜 다양한 형태의 전기장을 만들어 낼 수 있다. 화소 전극(191)을 투명한 물질로 만드는 경우에는 좁은 영역(NR) 또한 표시 영역으로 사용할 수 있으나, 불투명 전극으로 하는 경우에는 화소전극(191) 위의 좁은 영역(NR)을 표시 영역으로 사용할 수 없다.

한편, 전기장의 xy 평면 성분( $\overrightarrow{E}_{xy}$ )은 아래 배향막(11)으로부터 위 배향막(21)에 이르기까지, 즉 z축을 따라가며 점점 작아지며, 배향에 의한 탄성적 복원력은 배향막(11, 21)의 표면에서 가장 크고, 두 배향막(11, 21) 사이 액정층의 중앙으로 갈수록 점점 작아진다.

도 7은 z축을 따라가며 액정 분자의 장축 방향이 x축과 이루는 비틀림각을 도시한 도면으로서, 두 배향막 사이의 간격, 즉셀 간격이 d인 경우이다. 여기에서 가로축은 아래 배향막(11)으로부터의 높이를 뜻하고, 세로축은 비틀림각을 나타낸다.

도 7에 도시한 바와 같이, 비틀림각은 배향막(11, 21)의 표면에서는 배향력에 의한 힘이 강하기 때문에 크고, 액정층의 중앙으로 갈수록 작아져 전기장의 방향에 가깝게 되는 것을 알 수 있으며, 배향막(11, 21) 바로 위에서는 액정 분자의 장축이러빙 방향과 동일한 방향으로 배열한다. 여기에서 인접한 액정 분자의 비틀림각의 차이를 비틀림(twist)이라고 하면, 도 7에서 비틀림은 곡선의 기울기에 해당되고, 이는 배향막(11, 21)의 표면에서는 크고 액정층의 중앙으로 갈수록 작아진다.

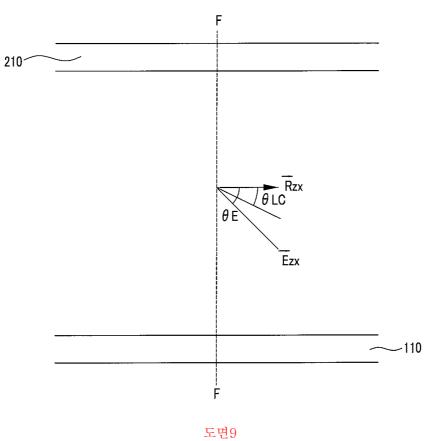

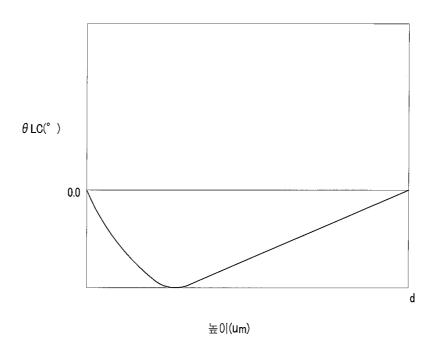

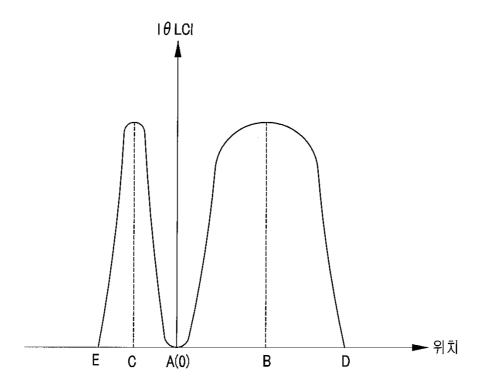

액정 분자의 경사각, 즉, x축 또는 초기 배열 방향에 대하여 액정 분자의 장축이 기판에 수직인 면(zx 평면) 위에서 이루는 각의 변화를 도 8, 도 9 및 도 10을 참고로 설명한다.

도 8은 본 발명의 한 실시예에서 액정 분자들의 경사각 변화를 설명하기 위한 도면이고, 도 9는 본 발명의 한 실시예에서 기판에 수직인 선에 대한 액정 분자들의 경사각 변화를 도시한 그래프이고, 도 10은 본 발명의 한 실시예에서 기판에 수평이고 화소 전극에 수직인 선에 대한 액정 분자들의 경사각 변화를 도시한 그래프이다.

도 8에서는 편의상 기판(110, 210)만을 도시한 것이며, 도 5에서 도시한 러빙 방향을 나타내는 벡터  $\overrightarrow{R}$ 의 zx 평면에 대한 성분을 벡터  $\overrightarrow{R}$ =zx로, 전기장의 zx 평면 성분은 벡터  $\overrightarrow{E}_{zx}$ 로 나타내었으며, 전기장의 zx 평면 성분  $\overrightarrow{E}_{zx}$ 가 x축과 이루는 각은  $\Theta$ E로, 액정 분자의 장축이 x축과 이루는 경사각을  $\Theta$ LC로 나타내었다. 그런데, 여기에서 벡터  $\overrightarrow{R}$ 은 xy 평면상에 존재하므로(선경사각은 무시)  $\overrightarrow{R}_{zx}$ 는 x 방향이 된다.

전기장의 zx 평면 성분( $\overrightarrow{E}_{zx}$ )의 크기는 아래 기판(10)에서 위 기판(11)으로 갈수록 작아지고, 각도  $\Theta$ E 또한 아래 기판(10)에서 위 기판(11)으로 갈수록 작아진다.

앞서 설명한 것처럼 배향 처리에 의한 탄성적 복원력의 크기는 두 기판(10, 11)의 표면에서 가장 크고, 액정층의 중앙으로 갈수록 작아진다.

액정 분자들은 이러한 두 가지 힘이 평형을 이루도록 배열하여야 한다. 도 9에 나타낸 것처럼, 하부 기판(110) 표면에서는 배향력이 강하므로 액정 분자들이 x축과 평행하게 배열하지만, 위로 올라갈수록 전기장에 의한 힘이 상대적으로 커지므로 경사각( $\Theta$ LC)의 크기가 어느 정도 지점까지는 계속해서 증가하다가 다시 감소하여 위 기판(11) 표면에서는 다시 x축과 평행하게 배열한다. 이때, 곡선의 정점은 아래 기판(10)에 가까운 위치에서 나타난다.

한편, 전기장의 zx 평면 성분(  $\overline{E}_{zx}$ )이 x축에 대하여 이루는 각  $\theta$ E는 경계선(A, D) 상에서는  $\theta$ 0에 가깝고 중앙선(B-B) 쪽으로 갈수록 커지며, 전기장의  $\theta$ 2x 평면 성분(  $\overline{E}_{zx}$ )의 크기는 경계선(A, D) 상에서 가장 크고 중앙선(B-B) 쪽으로 갈수록 작아진다.

배향 처리에 의한 탄성적 복원력의 크기는 x 축 상에서는 위치에 관계없이 일정하다.

따라서, 도 10에 도시한 바와 같이, 경계선(A, D)에서는 액정 분자의 경사각이 거의 0에 가깝지만 중심선(C, B)으로 갈수록 커져 전기장의 zx 평면 성분( $\overline{E}_{zx}$ )이 x축과 이루는 각( $\Theta$ E)과 유사한 분포를 가진다. 그러나,  $\Theta$ E보다는 완만하게 변화한다.

이와 같이 공통 전극 및 화소 전극(131, 191)에 전압이 인가되면 액정 분자들은 비틀림각 및 경사각을 가지며 재배열하는데, 그 비틀림각 및 경사각의 변화로 인하여 빛의 투과율이 변화한다. 경계선(A, D) 상에서는 z축을 따라 볼 때 경사각의 변화는 거의 없지만 비틀림각의 변화는 크다. 반면에, 중앙선(B, C) 상에서는 z축을 따라 볼 때 비틀림각의 변화는 거의 없지만 경사각은 약간 변화한다. 따라서, 경계선(A, D)과 중앙선(B, C) 사이의 영역에서는 비틀림각과 경사각이 모두 변화하는 영역이 된다. 결국, 위치에 따른 투과율 곡선은 전기력선의 형태와 유사한 형태가 된다.

한편, 공통 전극의 절개부는 본 발명의 한 실시예에 도시한 바와 같은 긴 선 형태뿐만 아니라 복수개의 작은 사각 형상, 원 형 형상, 사선 형상, 마름모 형상 또는 육각 형상 등이 가능하다.

도 11은 본 발명의 다른 실시예에 따른 액정 표시 장치용 박막 트랜지스터 표시판의 배치도로서, 복수개의 작은 직사각형 으로 절개부를 형성한 경우의 배치도이다.

도 11에 도시한 바와 같이, 본 발명의 다른 실시예에 따른 액정 표시 장치용 박막 트랜지스터 표시판은 절연 기판(110) 위에 복수의 게이트선(gate line)(121) 및 공통 전극(common electrode)(131)이 형성되어 있다. 게이트선(121)은 게이트 신호를 전달하며 주로 가로 방향으로 뻗어 있다. 각 게이트선(121)은 위로 돌출한 복수의 게이트 전극(gate electrode) (124)과 다른 층 또는 외부 구동 회로와의 접속을 위하여 면적이 넓은 끝 부분(129)을 포함한다.

공통 전극(131)은 공통 전압(common voltage)을 인가 받으며 게이트선(121) 사이의 공간을 거의 채우며 배치되어 있다. 공통 전극(131)은 가로 방향으로 길게 뻗어 있으며 공통 전극(131)의 밑면의 일부(132)는 오목한 모양으로 길게 파여져 있다. 그리고, 공통 전극(131)은 직사각형의 절개부(136)를 복수 개 가지며, 복수개의 절개부(136)는 서로 소정 간격을 유지하며 형성되어 있다.

게이트선(121) 및 공통 전극(131)의 측면은 기판(110) 면에 대하여 경사져 있으며 그 경사각은 약 30도 내지 약 80도인 것이 바람직하다.

게이트선(121) 및 공통 전극(131) 위에는 질화규소(SiNx) 또는 산화규소(SiOx) 따위로 만들어진 게이트 절연막(gate insulating layer)(140)이 형성되어 있다. 게이트 절연막(140)은 게이트선(121) 및 공통 전극(131)이 서로 단락되는 것을 방지하고, 이들 위에 형성되는 다른 도전성 박막과의 절연을 도모한다.

게이트 절연막(140) 위에는 수소화 비정질 규소(hydrogenated amorphous silicon)(비정질 규소는 약칭 a-Si로 씀) 또는 다결정 규소(polysilicon) 등으로 만들어진 복수의 선형 반도체(151)가 형성되어 있다. 선형 반도체(151)는 주로 세로 방향으로 뻗어 있으며, 게이트 전극(124)을 향하여 뻗어 나온 복수의 돌출부(projection)(154)를 포함한다.

반도체(151) 위에는 복수의 선형 및 섬형 저항성 접촉 부재(ohmic contact)(161, 165)가 형성되어 있다. 저항성 접촉 부재(161, 165)는 인 따위의 n형 불순물이 고농도로 도핑되어 있는 n+ 수소화 비정질 규소 따위의 물질로 만들어지거나 실리사이드(silicide)로 만들어질 수 있다. 선형 저항성 접촉 부재(161)는 복수의 돌출부(163)를 가지고 있으며, 이 돌출부(163)와 섬형 저항성 접촉 부재(165)는 쌍을 이루어 반도체(151)의 돌출부(154) 위에 배치되어 있다.

반도체(151)와 저항성 접촉 부재(161, 165)의 측면 역시 기판(110) 면에 대하여 경사져 있으며 경사각은 30도 내지 80도 정도이다.

저항성 접촉 부재(161, 165) 위에는 복수의 데이터선(data line)(171)과 복수의 드레인 전극(drain electrode)(175)이 형성되어 있다.

데이터선(171)은 데이터 신호를 전달하며 주로 세로 방향으로 뻗어 게이트선(121)과 교차한다. 각 데이터선(171)은 게이트 전극(124)을 향하여 뻗은 복수의 소스 전극(source electrode)(173)과 다른 층 또는 외부 구동 회로와의 접속을 위하여 면적이 넓은 끝 부분(179)을 포함한다. 데이터 신호를 생성하는 데이터 구동 회로(도시하지 않음)는 기판(110) 위에 부착되는 가요성 인쇄 회로막(도시하지 않음) 위에 장착되거나, 기판(110) 위에 직접 장착되거나, 기판(110)에 집적될 수 있다. 데이터 구동 회로가 기판(110) 위에 집적되어 있는 경우, 데이터선(171)이 연장되어 이와 직접 연결될 수 있다.

드레인 전극(175)은 데이터선(171)과 분리되어 있고 게이트 전극(124)을 중심으로 소스 전극(173)과 마주 본다.

하나의 게이트 전극(124), 하나의 소스 전극(173) 및 하나의 드레인 전극(175)은 반도체(151)의 돌출부(154)와 함께 하나의 박막 트랜지스터(thin film transistor, TFT)를 이루며, 박막 트랜지스터의 채널(channel)은 소스 전극(173)과 드레인 전극(175) 사이의 돌출부(154)에 형성된다.

저항성 접촉 부재(161, 165)는 그 아래의 반도체(151)와 그 위의 데이터선(171) 및 드레인 전극(175) 사이에만 존재하며 이들 사이의 접촉 저항을 낮추어 준다. 반도체(151)는 데이터선(171), 드레인 전극(175) 및 그 아래의 저항성 접촉 부재 (161, 165)와 실질적으로 동일한 평면 모양이다. 그러나 반도체(151)에는 소스 전극(173)과 드레인 전극(175) 사이를 비롯하여 데이터선(171) 및 드레인 전극(175)으로 가리지 않고 노출된 부분이 있다.

데이터선(171), 드레인 전극(175) 및 노출된 반도체(151) 부분 위에는 보호막(passivation layer)(180)이 형성되어 있다. 보호막(180)은 무기 절연물로 만들어지며, 무기 절연물의 예로는 질화규소와 산화규소를 들 수 있다. 그러나 보호막(180) 은 유기막의 우수한 절연 특성을 살리면서도 노출된 반도체(151) 부분에 해가 가지 않도록 하부 무기막과 상부 유기막의 이중막 구조를 가질 수 있다.

보호막(180)에는 데이터선(171)의 끝 부분(179)과 드레인 전극(175)을 각각 드러내는 복수의 접촉 구멍(contact hole) (182, 185)이 형성되어 있으며, 보호막(180)과 게이트 절연막(140)에는 게이트선(121)의 끝 부분(129)을 드러내는 복수의 접촉 구멍(181)이 형성되어 있다.

보호막(180) 위에는 복수의 화소 전극(pixel electrode)(191) 및 복수의 접촉 보조 부재(contact assistant)(81, 82)가 형성되어 있다. 이들은 ITO(indium tin oxide) 또는 IZO(indium zinc oxide) 등의 투명한 도전 물질로 만들어질 수 있다.

화소 전극(191)은 주로 세로 방향으로 뻗어 공통 전극(131)과 중첩한다. 이 때, 화소 전극(191)의 하단은 서로 연결되어 있다. 화소 전극(191)은 데이터선(171)과 평행한 방향으로 복수개의 가지가 선형으로 뻗어있다.

공통 전극(131)이 데이터선(171)과 중첩되는 부분은 기생용량이 발생하여 화상 신호를 지연시키므로 공통 전극(131) 중에서 데이터선(171)과 중첩되는 부분은 제거하고 일부(132)만을 남겨두어 인접하는 공통 전극(131)을 서로 연결한다.

화소 전극(191)은 공통 전극(131)의 절개부(136)에 대응하는 위치에 형성되며, 화소 전극(191)의 가장자리는 공통 전극(131)의 가장자리와 중첩되어 있다. 따라서, 화소 전극(191)과 공통 전극(131)은 유지 축전기를 이루어 박막 트랜지스터가 턴 오프된 후에도 인가된 전압을 유지한다. 이러한 공통 전극(131)의 절개부(136)의 크기를 조절함으로써 화소 전극(191)과 공통 전극(131)이 중첩되는 부분(X, Y)의 면적을 변경하여 유지 축전기의 유지 용량을 조절할 수 있다.

화소 전극(191)은 접촉 구멍(185)을 통하여 드레인 전극(175)과 물리적·전기적으로 연결되어 있으며, 드레인 전극(175)으로부터 데이터 전압을 인가 받는다. 데이터 전압이 인가된 화소 전극(191)은 공통 전압을 인가 받는 공통 전극(131)과 함께 전기장을 생성함으로써 두 전극(191, 131) 위에 위치하는 액정층(도시하지 않음)의 액정 분자의 방향을 결정한다. 이와 같이 결정된 액정 분자의 방향에 따라 액정층을 통과하는 빛의 편광이 달라진다.

접촉 보조 부재(81, 82)는 각각 접촉 구멍(181, 182)을 통하여 게이트선(121)의 끝 부분(129) 및 데이터선(171)의 끝 부분(179)과 연결된다. 접촉 보조 부재(81, 82)는 게이트선(121)의 끝 부분(129) 및 데이터선(171)의 끝 부분(179)과 외부 장치와의 접착성을 보완하고 이들을 보호한다.

### 발명의 효과

본 발명에 따른 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치는 하나의 기판에 형성된 공통 전극 위에 화소 전극을 중첩되게 배치함으로써, 시야각을 넓힐 수 있고, 구동 전압을 낮출 수 있으며, 개구율을 크게 할 수 있다.

또한, 공통 전극에 절개부를 형성하고, 절개부의 크기를 조절함으로써 화소 전극과 공통 전극이 중첩되는 부분의 면적을 변경하여 유지 축전기의 유지 용량을 용이하게 조절할 수 있다.

이상에서 본 발명의 바람직한 실시예에 대하여 상세하게 설명하였지만, 당해 기술 분야에서 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시예가 가능하다는 점을 이해할 수 있을 것이다. 따라서, 본 발명의 권리 범위는 이에한정되는 것은 아니고 다음의 청구범위에서 정의하고 있는 본 발명의 기본 개념을 이용한 당업자의 여러 변형 및 개량 형태 또한 본 발명의 권리범위에 속하는 것이다.

#### 도면의 간단한 설명

도 1은 본 발명의 한 실시예에 따른 액정 표시 장치용 박막 트랜지스터 표시판의 배치도이고, 도 2a는 도 1의 박막 트랜지스터 표시판을 IIa-IIa 선을 따라 잘라 도시한 단면도이고, 도 2b는 도 1의 박막 트랜지스터 표시판을 IIb-IIb' 선 및 IIb'-IIb' 선을 따라 잘라 도시한 단면도이다.

도 3은 본 발명의 한 실시예에 따른 박막 트랜지스터 표시판의 전극을 나타내는 배치도이고,

도 4는 도 3에서 IV-IV 선을 잘라 도시한 액정 표시 장치의 단면도로서, 상부 기판 및 하부 기판사이의 등전위선 및 전기력선을 함께 도시한 도면이고,

도 5는 본 발명의 한 실시예에서 액정 분자들의 비틀림각 변화를 설명하기 위한 도면이고,

도 6은 본 발명의 한 실시예에서 기판에 수평이고 화소 전극에 수직인 선에 대한 액정 분자들의 비틀림각 변화를 도시한 그래프이고,

도 7은 본 발명의 한 실시예에서 기판에 수직인 선에 대한 액정 분자들의 비틀림각 변화를 도시한 그래프이고,

도 8은 본 발명의 한 실시예에서 액정 분자들의 경사각 변화를 설명하기 위한 도면이고,

도 9는 본 발명의 한 실시예에서 기판에 수직인 선에 대한 액정 분자들의 경사각 변화를 도시한 그래프이고,

도 10은 본 발명의 한 실시예에서 기판에 수평이고 화소 전극에 수직인 선에 대한 액정 분자들의 경사각 변화를 도시한 그래프이고,

도 11은 본 발명의 다른 실시예에 따른 액정 표시 장치용 박막 트랜지스터 표시판의 배치도이다.

<도면의 주요부분에 대한 부호의 설명>

110: 기판 121, 129: 게이트선

124: 게이트 전극 131: 공통 전극

140: 게이트 절연막 151, 154: 반도체

161, 165: 저항성 접촉 부재 171, 179: 데이터선

173: 소스 전극 175: 드레인 전극

180: 보호막 181, 182, 185: 접촉 구멍

190: 화소 전극 81, 82: 접촉 보조 부재

도면2a

## 도면2b

도면4

도면5

도면10

| 专利名称(译)        | 薄膜晶体管显示面板和包括其的                                                                          | 液晶显示装置  |            |  |

|----------------|-----------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | KR1020060131020A                                                                        | 公开(公告)日 | 2006-12-20 |  |

| 申请号            | KR1020050050847                                                                         | 申请日     | 2005-06-14 |  |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                |         |            |  |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                                |         |            |  |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                                                |         |            |  |

| [标]发明人         | LEE JUN WOO<br>이준우<br>HAN EUN HEE<br>한은희<br>KIM HEE SEOP<br>김희섭<br>LEE CHANG HUN<br>이창훈 |         |            |  |

| 发明人            | 이준우<br>한은희<br>김희섭<br>이창훈                                                                |         |            |  |

| IPC分类号         | G02F1/1343 G02F1/136                                                                    |         |            |  |

| CPC分类号         | G02F1/134309 G02F1/133528 G02F1/134363 G02F1/13439 G02F2001/134318                      |         |            |  |

| 外部链接           | Espacenet                                                                               |         |            |  |

## 摘要(译)

根据本发明的薄膜晶体管基板可以由基板形成,多条栅极线形成在基板上,并且导体在基板上形成时是透明的。根据本发明的薄膜晶体管基板和包括该薄膜晶体管基板的液晶显示器将所述像素电极复制地布置在所形成的公共电极上的一个基板上。以这种方式,可以扩大视角。可以降低驱动电压。并且孔径比可以很多。此外,切口部分形成在公共电极上。通过控制切口部分的尺寸,改变了像素电极和公共电极重叠的部分的面积,并且可以容易地控制维护电容器的存储电容。液晶显示器,PLS,公共电极,存储电容,图案。