US 20120154702A1

### (19) United States

# (12) Patent Application Publication Kim et al.

## (10) Pub. No.: US 2012/0154702 A1

(43) **Pub. Date: Jun. 21, 2012**

#### (54) LIQUID CRYSTAL DISPLAY

(76) Inventors: **Hee-Seob Kim**, Hwaseong-gun

(KR); Joon-Hak Oh, Seoul (KR); Doo-Hwan You, Suwon-si (KR); Young-Chol Yang, Kunpo-si (KR)

*9* 1

(22) Filed: Feb. 28, 2012

Appl. No.:

#### Related U.S. Application Data

13/407,339

(63) Continuation of application No. 12/949,920, filed on Nov. 19, 2010, now Pat. No. 8,125,599, which is a continuation of application No. 12/369,260, filed on Feb. 11, 2009, now Pat. No. 7,852,442, which is a continuation of application No. 11/566,496, filed on Dec. 4, 2006, now Pat. No. 7,495,735, which is a continuation of application No. 10/866,536, filed on Jun. 10, 2004, now Pat. No. 7,158,201.

#### (30) Foreign Application Priority Data

Jun. 10, 2003 (KR) ...... 2003-0037090

#### **Publication Classification**

(51) **Int. Cl.**

**G02F 1/136** (2006.01)

(52) U.S. Cl. ...... 349/42

(57) ABSTRACT

A thin film transistor array panel is provided, which includes: a substrate; a plurality of first signal lines formed on the substrate; a plurality of second signal lines intersecting the first signal lines to define pixel areas; first and second pixel electrodes disposed substantially in a pixel area and having different areas; a plurality of thin film transistors connected to the first and the second signal lines and at least one of the first and the second pixel electrodes; a coupling electrode overlapping the second pixel electrode; and a tilt direction defining member for determining tilt directions of liquid crystal molecules formed on the substrate.

FIG.1

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6

FIG.7

FIG.8

FIG.9

FIG.10

FIG.11

FIG.12

FIG.13

#### LIQUID CRYSTAL DISPLAY

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a Continuation of U.S. application Ser. No. 12/949,920 filed on Nov. 19, 2010, which is a Continuation of U.S. application Ser. No. 12/369,260 filed on Feb. 11, 2009, which is a continuation of U.S. patent application Ser. No. 11/566,496 filed Dec. 4, 2006, now U.S. Pat. No. 7,495,735 which is a continuation of Ser. No. 10/866,536 filed Jun. 10, 2004, now U.S. Pat. No. 7,158,201 which claims priority to Korean Application No. 2003-37090 filed Jun. 10, 2003, the entireties of which are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

[0002] (a) Field of the Invention

[0003] The present invention relates to a liquid crystal display.

[0004] (b) Description of the Related Art

[0005] A liquid crystal display (LCD) is one of the most widely used flat panel displays. An LCD includes two panels provided with field-generating electrodes such as pixel electrodes and a common electrode and a liquid crystal (LC) layer interposed therebetween. The LCD displays images by applying voltages to the field-generating electrodes to generate an electric field in the LC layer, which determines orientations of LC molecules in the LC layer to adjust polarization of incident light.

[0006] Among the LCDs, a vertical alignment (VA) mode LCD, which aligns LC molecules such that the long axes of the LC molecules are perpendicular to the panels in absence of electric field, is spotlighted because of its high contrast ratio and wide viewing angle.

[0007] The wide viewing angle of the VA mode LCD can be realized by cutouts in the field-generating electrodes and protrusions on the field-generating electrodes. Since the cutouts and the protrusions can determine the tilt directions of the LC molecules, the tilt directions can be distributed into several directions by using the cutouts and the protrusions such that the viewing angle is widened.

[0008] However, the VA mode LCD has relatively poor lateral visibility compared with front visibility.

#### SUMMARY OF THE INVENTION

[0009] A thin film transistor array panel is provided, which includes: a substrate; a plurality of first signal lines formed on the substrate; a plurality of second signal lines intersecting the first signal lines to define pixel areas; first and second pixel electrodes disposed substantially in a pixel area and having different areas; a plurality of thin film transistors connected to the first and the second signal lines and at least one of the first and the second pixel electrodes; a coupling electrode overlapping the second pixel electrode; and a tilt direction defining member for determining tilt directions of liquid crystal molecules formed on the substrate.

[0010] A liquid crystal display is provided, which includes: a thin film transistor array panel, a common electrode panel, a first tilt direction defining member formed on the thin film transistor array panel, and a second tilt direction defining member determining tilt directions of liquid crystal molecules along with the first tilt direction defining member formed on the common electrode panel. The thin film tran-

sistor array panel includes: a plurality of first signal lines; a plurality of second signal lines intersecting the first signal lines to define pixel areas; first and second pixel electrodes disposed substantially in a pixel area and having different areas; a plurality of thin film transistors connected to the first and the second signal lines and at least one of the first and the second pixel electrodes; and a coupling electrode overlapping the second pixel electrode. The common electrode panel includes a common electrode for generating an electric field along with the first and the second pixel electrodes;

[0011] The first and the second tilt direction defining members may include cutouts formed in the pixel electrodes and the common electrode.

[0012] The liquid crystal display is provided, which includes: a first substrate; a plurality of first signal lines formed on the first substrate; a plurality of second signal lines intersecting the first signal lines to define pixel areas; first and second pixel electrodes disposed substantially in a pixel area; a plurality of thin film transistors connected to the first and the second signal lines and at least one of the first and the second pixel electrodes; a coupling electrode overlapping the second pixel electrode; a second substrate facing the first substrate; a common electrode formed on the second substrate; a first tilt direction defining member formed on the thin film transistor array panel; and a second tilt direction defining member determining tilt directions of liquid crystal molecules along with the first tilt direction defining member formed on the common electrode panel, wherein a ratio of a voltage difference between the first pixel electrode and the common electrode and a voltage difference between the second pixel electrode and the common electrode is in a range between about 0.5 - 0.95

[0013] The tilt direction determining member may include a cutout of one of the first and the second pixel electrodes.

[0014] The coupling electrode may be connected to a drain electrode of one of the thin film transistors.

[0015] The first and the second pixel electrodes may have edges facing each other and forming a gap and the gap includes oblique portions making an angle of about 45 degrees with the gate lines.

[0016] The thin film transistor array panel may further include a third signal line intersecting the second signal lines and supplied with a reference voltage, wherein the first and the second pixel electrodes are capacitively coupled to each other through the coupling electrode, and the thin film transistors comprise a first transistor connected to one of the first signal lines, one of the second signal lines, and the first pixel electrode and a second transistor connected to one of the first signal lines, the third signal line, and the second pixel electrode.

[0017] The thin film transistor array panel may further include an insulating layer disposed between the first and the second pixel electrodes and the first and the second transistors and having a first contact hole for connecting the second pixel electrode to the second transistor.

[0018] The thin film transistor array panel may further include an insulating layer disposed between the first and the second pixel electrodes and the first and the second transistors, wherein the first pixel electrode is connected to the first transistor or overlaps a drain electrode of the first transistor.

[0019] The first pixel electrode may have an area larger than the second pixel electrode.

[0020] The first pixel electrode may have an area once to six times an area of the second pixel electrode.

[0021] The thin film transistor array panel may further include a third pixel electrode capacitively coupled to the first pixel electrode.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0022] The present invention will become more apparent by describing embodiments thereof in detail with reference to the accompanying drawings in which:

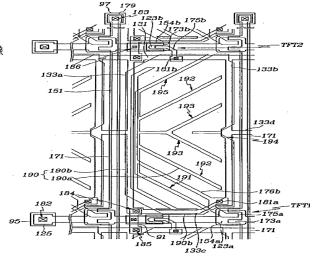

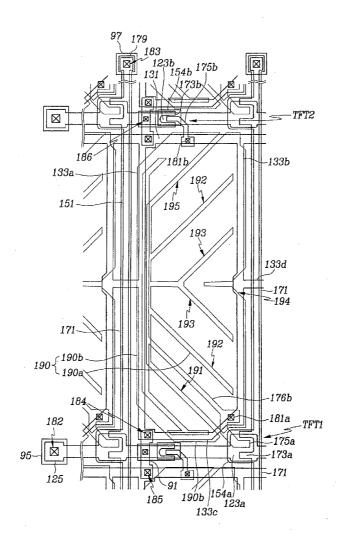

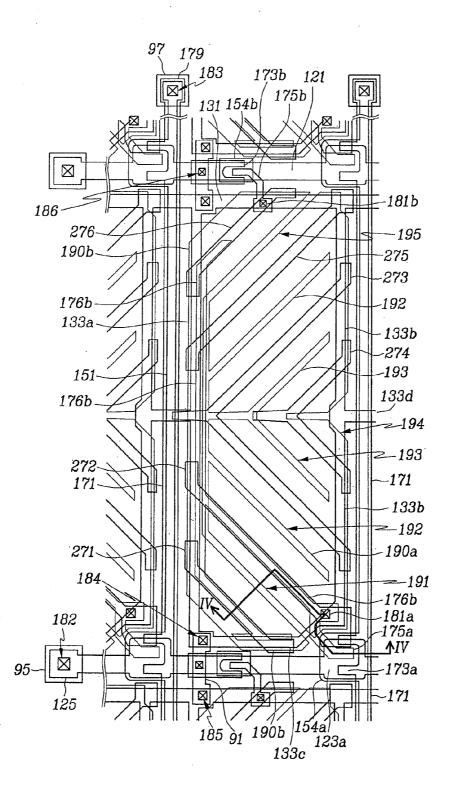

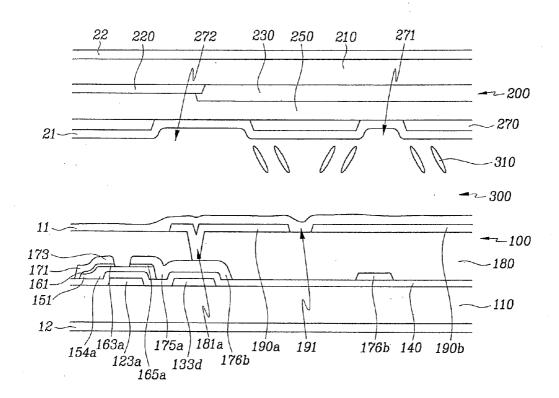

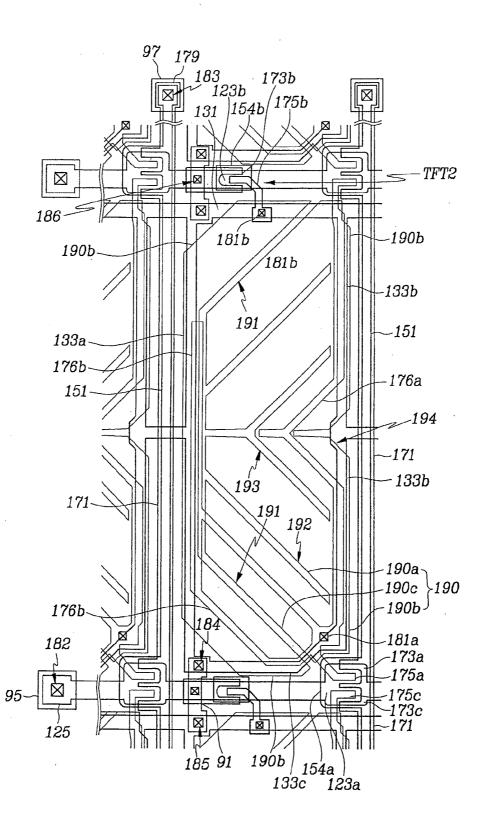

[0023] FIG. 1 is a layout view of a TFT array panel of an LCD according to an embodiment of the present invention; [0024] FIG. 2 is a layout view of a common electrode panel of an LCD according to an embodiment of the present invention:

[0025] FIG. 3 is a layout view of an LCD including the TFT array panel shown in FIG. 1 and the common electrode panel shown in FIG. 2;

$\begin{tabular}{ll} [0026] & FIG.~4~is~a~sectional~view~of~the~LCD~shown~in~FIG. \\ 4~taken~along~the~line~V-V'; \end{tabular}$

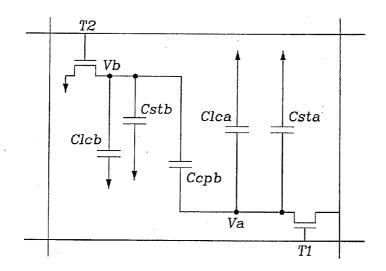

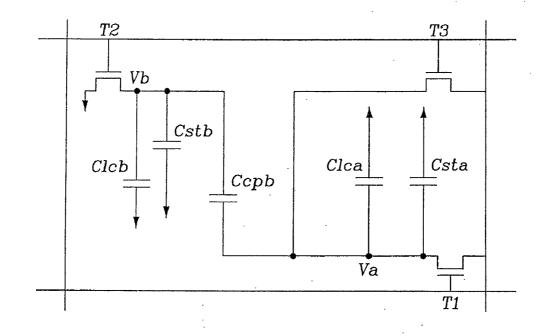

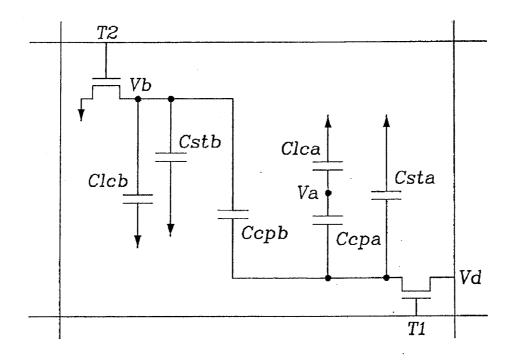

[0027] FIG. 5 is an equivalent circuit of the LCD shown in FIGS. 1-4;

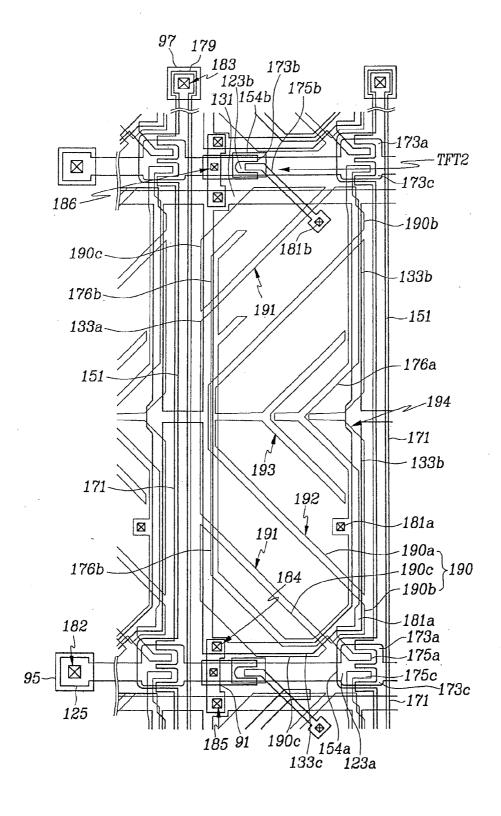

[0028] FIG. 6 is a layout view of a TFT array panel for an LCD according to another embodiment of the present inventions.

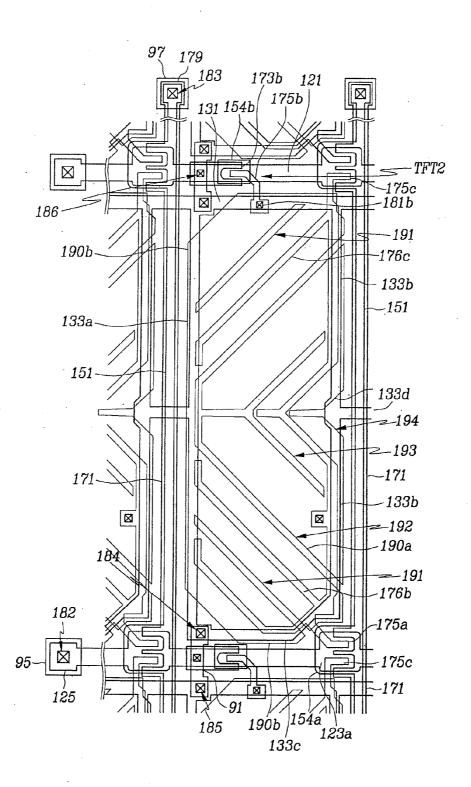

[0029] FIG. 7 is an equivalent circuit diagram of an LCD including the TFT array panel shown in FIG. 6;

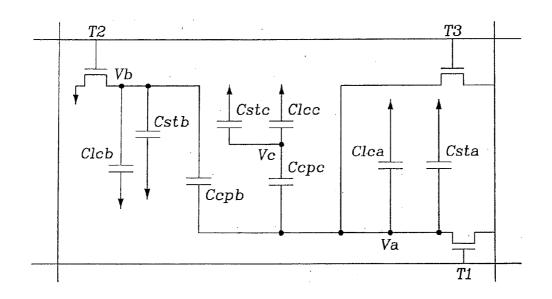

[0030] FIG. 8 is a layout view of a TFT array panel for an LCD according to another embodiment of the present invention:

[0031] FIG. 9 is an equivalent circuit diagram of an LCD including the TFT array panel shown in FIG. 8;

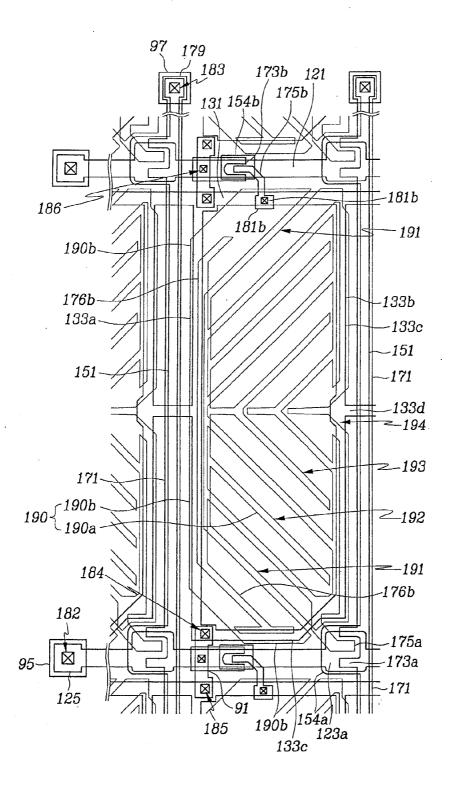

[0032] FIG. 10 is a layout view of a TFT array panel for an LCD according to another embodiment of the present invention:

[0033] FIG. 11 is an equivalent circuit diagram of an LCD including the TFT array panel shown in FIG. 10; and

[0034] FIGS. 12 and 13 are layout views of TFT array panels for an LCD according to another embodiment of the present invention.

#### DETAILED DESCRIPTION OF EMBODIMENTS

[0035] The present invention now will be described more fully hereinafter with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. The present invention may, however, be embodied in many different forms and should not be construed as limited to the embodiments set forth herein.

[0036] In the drawings, the thickness of layers, films and regions are exaggerated for clarity. Like numerals refer to like elements throughout. It will be understood that when an element such as a layer, film, region or substrate is referred to as being "on" another element, it can be directly on the other element or intervening elements may also be present. In contrast, when an element is referred to as being "directly on" another element, there are no intervening elements present.

[0037] Now, liquid crystal displays and thin film transistor (TFT) array panels for LCDs according to embodiments of the present invention will be described with reference to the accompanying drawings.

[0038] An LCD according to an embodiment of the present invention will be described in detail with reference to FIGS. 1-5.

[0039] FIG. 1 is a layout view of a TFT array panel of an LCD according to an embodiment of the present invention,

FIG. 2 is a layout view of a common electrode panel of an LCD according to an embodiment of the present invention, FIG. 3 is a layout view of an LCD including the TFT array panel shown in FIG. 1 and the common electrode panel shown in FIG. 2, and FIG. 4 is a sectional view of the LCD shown in FIG. 4 taken along the line V-V'.

[0040] An LCD according to an embodiment of the present invention includes a TFT array panel 100, a common electrode panel 200, and a LC layer 300 interposed between the panels 100 and 200 and containing a plurality of LC molecules 310 aligned substantially vertical to surfaces of the panels 100 and 200.

[0041] The TFT array panel 100 is now described in detail with reference FIGS. 1, 3 and 4.

[0042] A plurality of gate lines 121 and a plurality of storage electrode lines 131 are formed on an insulating substrate 110 such as transparent glass.

[0043] The gate lines 121 extend substantially in a transverse direction and are separated from each other and transmit gate signals. Each gate line 121 includes a plurality of first and second gate electrodes 123a and 123b and an end portion 125 having a large area for connection with an external driving circuit. The first gate electrode 123a has a width wider than other portions of the gate line 121.

[0044] Each storage electrode line 131 extends substantially in the transverse direction and includes a plurality of ring-shaped branches 133a-133c and a plurality of branch connections 133d connected between adjacent branches 133a-133c. Each branch set includes a pair of first and second storage electrodes 133a and 133b extending in a longitudinal direction and a third storage electrodes 133c connected to ends of the first and the second storage electrodes 133a and 133b and extending in the transverse direction and in an oblique direction. The storage electrode lines 131 are supplied with a predetermined voltage such as a common voltage, which is applied to a common electrode 270 on the common electrode panel 200 of the LCD. The third storage electrodes 133c may be connected to each other.

[0045] The gate lines 121 and the storage electrode lines 131 is preferably made of Al containing metal such as Al and Al alloy, Ag containing metal such as Ag and Ag alloy, Cu containing metal such as Cu and Cu alloy, Mo containing metal such as Mo and Mo alloy, Cr, Ti or Ta. The gate lines 121 and the storage electrode lines 131 may have a multilayered structure including two films having different physical characteristics, a lower film (not shown) and an upper film (not shown). The upper film is preferably made of low resistivity metal including Al containing metal such as Al and Al alloy for reducing signal delay or voltage drop in the gate lines 121 and the storage electrode lines 131. On the other hand, the lower film is preferably made of material such as Cr, Mo and Mo alloy, which has good contact characteristics with other materials such as indium tin oxide (ITO) or indium zinc oxide (IZO). However, the gate lines 121 and the storage electrode lines 131 may be made of other various metals or conductive materials.

[0046] In addition, the lateral sides of the gate lines 121 and the storage electrode lines 131 are inclined relative to a surface of the substrate, and the inclination angle thereof ranges about 20-80 degrees.

[0047] A gate insulating layer 140 preferably made of silicon nitride (SiNx) is formed on the gate lines 121 and the storage electrode lines 131.

[0048] A plurality of semiconductor stripes 151 and a plurality of semiconductor islands 154b preferably made of hydrogenated amorphous silicon (abbreviated to "a-Si") or polysilicon are formed on the gate insulating layer 140. Each semiconductor stripe 151 extends substantially in the longitudinal direction and has a plurality of projections 154a branched out toward the first gate electrodes 123a. The semiconductor islands 154b are disposed on the second gate electrodes 123b.

[0049] A plurality of ohmic contact stripes and islands 161 and 165a as well as a plurality of ohmic contact islands (not shown), which are preferably made of silicide or n+ hydrogenated a-Si heavily doped with n type impurity such as phosphorous, are formed on the semiconductor stripes 151 as well as on the semiconductor islands 154b. Each ohmic contact stripe 161 has a plurality of projections 163, and the projections 163 and the ohmic contact islands 165 are located in pairs on the projections 154a of the semiconductor stripes 151. The ohmic contact islands on the semiconductor islands 154b are also located in pairs.

[0050] The lateral sides of the semiconductor stripes 151 and the ohmic contacts 161 and 165 are inclined relative to a surface of the substrate, and the inclination angles thereof are preferably in a range between about 30-80 degrees.

[0051] A plurality of data lines 171 including a plurality of first source electrodes 173*a* and a plurality of first drain electrodes 175*a* as well as a plurality of second source electrodes 173*b* and a plurality of second drain electrodes 175*b* are formed on the ohmic contacts 161 and 165 and the gate insulating layer 140 as well as on the semiconductor islands 154*b*

[0052] The data lines 171 for transmitting data voltages extend substantially in the longitudinal direction and intersect the gate lines 121, the storage electrode lines 131, and the branch connections 133d. Each data line 171 is disposed between adjacent branches 133a-133c and it includes an end portion 179 having a large area for contact with another layer or an external device. A plurality of branches of each data line 171, which project toward the first drain electrodes 175a, form the first source electrodes 173a. The second source electrodes 173b and the second drain electrodes 175b are disposed on the second gate electrodes 123b. Each of the first/second drain electrodes 175a/175b extends upward/ downward from an end portion and includes an expansion having a large area for contact with another layer and each of the first/second source electrodes 173a/173b is curved to partly enclose an end portion of the first/second drain electrode 175a/175b.

[0053] A first gate electrode 123a, a first source electrode 173a, and a first drain electrode 175a along with a projection 154a of a semiconductor stripe 151 form a first TFT having a channel formed in the projection 154a disposed between the first source electrode 173a and the first drain electrode 175a. Similarly, a second gate electrode 123b, a second source electrode 173b, and a second drain electrode 175b along with a semiconductor island 154b form a second TFT having a channel formed in the semiconductor island 154b disposed between the second source electrode 173b and the second drain electrode 175b.

[0054] In the meantime, each of the first drain electrodes 175a extends to form a coupling electrode 176b and the coupling electrode 176b includes a longitudinal portion partly overlapping a first storage electrode 133a, three oblique portions connected to the longitudinal portion and

extending parallel to each other, and a transverse portion connected to one of the three oblique portions and partly overlapping the third storage electrode 133c. The oblique portions of the coupling electrode 176b make an angle of about 45 degrees with the gate lines 121. Two of the oblique portions are connected to respective ends of the longitudinal portion and approximately making a right angle and remaining one of the oblique portions are connected to an intermediate point of the longitudinal portion and to the expansion of the first drain electrode 175b.

[0055] The data lines 171, the drain electrodes 175a and 175b, and the second source electrodes 173b are preferably made of refractory metal such as Cr, Mo containing metal, Ti and Ti, or Al containing metal and they may also have a multilayered structure including a lower film (not shown) preferably made of refractory metal and an upper film (not shown) located thereon and preferably made of low resistivity material.

[0056] Like the gate lines 121 and the storage electrode lines 131, the data lines 171, the drain electrodes 175a and 175b, and the second source electrodes 173b have tapered lateral sides, and the inclination angles thereof range about 30-80 degrees.

[0057] The ohmic contacts 161 and 165 are interposed only between the underlying semiconductor stripes 151 and the overlying data lines 171, the overlying drain electrodes 175a and 175b, and the second source electrodes 173b thereon and reduce the contact resistance therebetween. The semiconductor stripes and islands 151 and 154b include a plurality of exposed portions, which are not covered with the data lines 171, the drain electrodes 175a and 175b, and the second source electrodes 173b, such as portions located between the source electrodes 173a and 173b and the drain electrodes 175a and 175b.

[0058] A passivation layer 180 is formed on the data lines 171, the drain electrodes 175a and 175b, the second source electrodes, and the exposed portions of the semiconductor stripes 151. The passivation layer 180 is preferably made of photosensitive organic material having a good flatness characteristic, low dielectric insulating material having dielectric constant lower than 4.0 such as a-Si:C:O and a-Si:O:F formed by plasma enhanced chemical vapor deposition (PECVD), or inorganic material such as silicon nitride. The passivation layer 180 may include a lower film of inorganic insulator and an upper film of organic insulator.

[0059] The passivation layer 180 has a plurality of contact holes 181a, 181b, 183 and 186 exposing the expansions of the first and the second drain electrodes 175a and 175b, the end portions 179 of the data lines 171, and the second source electrodes 173b, respectively. The passivation layer 180 and the gate insulating layer 140 have a plurality of contact holes 182, 183 and 184 exposing the end portions 125 of the gate lines 121, end portions of the first storage electrodes 133a, and portions of the storage electrodes 131 near the end portions of the first storage electrodes 133a, respectively.

[0060] A plurality of pairs of first and second pixel electrodes 190a and 190b, a plurality of contact assistants 95 and 97, and a plurality of storage connections 91, which are preferably made of a transparent conductor such as ITO and IZO or a reflective conductor such as Al, are formed on the passivation layer 180.

[0061] The storage connections 91 cross over the gate lines 121 and the second source electrodes 173b and they are connected to the exposed projection of the end portions of the

first storage electrodes 133a and the exposed portions of the storage electrode lines 131 respectively through the contact holes 184 and 185 opposite each other with respect to the gate lines 121. In addition, the storage connections 91 are connected to the second source electrodes 173b through the contact holes 186. The storage electrode lines 131 including the storage electrodes 133a and 133b along with the storage connections 91 and the second source 173b may be used for repairing defects in the gate lines 121, the data lines 171, or the TFTs. The electrical connection between the gate lines 121 and the storage electrode lines 131 for repairing the gate lines 121 is obtained by illuminating the cross points of the gate lines 121 and the storage connections 91 by a laser beam to electrically connect the gate lines 121 to the storage connections 91. In this case, the second source electrodes 173b enhance the electrical connection between the gate lines 121 and the storage connections 91.

[0062] The first/second pixel electrodes 190a/190b are physically and electrically connected to the first/second drain electrodes 175a/175b through the contact holes 181a/181b such that the first/second pixel electrodes 190a/190b receive the data/common voltages from the first/second drain electrodes 175a/175b. In addition, the second pixel electrodes 190b overlap the coupling electrodes 176b.

[0063] The pixel electrodes 190a and 190b supplied with the data voltages generate electric fields in cooperation with the common electrode 270, which reorient liquid crystal molecules 310 in the liquid crystal layer 300.

[0064] A pixel electrode 190a/190b and the common electrode 270 form a liquid crystal capacitor, which stores applied voltages after turn-off of the TFT. An additional capacitor called a "storage capacitor," which is connected in parallel to the liquid crystal capacitor, is provided for enhancing the voltage storing capacity. The storage capacitors are implemented by overlapping the pixel electrodes 190a and 190b with the storage electrode lines 131 including the storage electrodes 133a, 133b and 133c.

[0065] A pair of first and second pixel electrodes 190a and 190b engage with each other interposing a gap 191 and their outer boundary has substantially a shape of rectangle with chamfered left corners. The first pixel electrode 190a has a shape of a rotated equilateral trapezoid having a left edge disposed near a longitudinal portion of a coupling electrode 176b, a right edge disposed near a second storage electrode 133b, and a pair of upper and lower oblique edges extending substantially parallel to the oblique portions of the coupling electrode 176b and thereby making an angle of about 45 degrees with the gate lines 121. The second pixel electrode 190b includes a pair of trapezoidal portions facing the oblique edges of the first pixel electrode 190a and a longitudinal portion facing the left edge of the first pixel electrode 190a. Accordingly, the gap 191 has a pair of oblique upper and lower portions having a substantially uniform width and making an angle of about 45 degrees with the gate lines 121 and a longitudinal portion having a substantially uniform width.

[0066] The first pixel electrode 190a has upper and lower cutouts 192 and a pair of middle cutouts 193 and 194, which partition the first pixel electrode 190a into a plurality of partitions. The upper and the lower cutouts 192 are disposed at upper and lower halves of the pixel electrode 190, respectively, and the middle cutouts 193 and 194 are located between the upper cutout 92 and the lower cutout 92. The gap 191 and the cutouts 192 and 194 substantially have inversion

symmetry with respect to an imaginary transverse center line bisecting the upper and the lower halves of the first pixel electrode **190***a*.

[0067] The upper cutout 192 extends substantially parallel to the upper oblique portion of the gap 191 and substantially perpendicular to the lower cutout 192, which extends substantially parallel to the upper oblique portion of the gap 191. The upper and the lower cutouts 192 extend approximately from the left edge of the first pixel electrode 190a approximately to the right edge of the first pixel electrode 190a.

[0068] The middle cutout 193 includes a transverse portion extending approximately from the left edge of the first pixel electrode 190a along the transverse center line of the pixel electrode 190 and a pair of oblique portions extending from the transverse portion to the right edge of the first pixel electrode 190a and extending substantially parallel to the upper cutout 192 and the lower cutout 192, respectively. The middle cutout 194 extends along the transverse center line of the first pixel electrode 190a and has an inlet from the right edge of the pixel electrode 190, which has a pair of oblique edges substantially parallel to the upper cutout 192 and the lower cutout 192, respectively.

[0069] Accordingly, the upper half of the first pixel electrode 190a is also partitioned into three upper partitions by the upper cutout 192 and the middle cutout 193, and the lower half of the first pixel electrode 190a is partitioned into three lower partitions by the lower cutout 192 and the middle cutout 193. The number of partitions or the number of the cutouts is varied depending on the design factors such as the size of pixels, the ratio of the transverse edges and the longitudinal edges of the first and second pixel electrodes 190a and 190b, the type and characteristics of the liquid crystal layer 300, and so on. For descriptive convenience, the gap 191 is also referred to as a cutout.

[0070] In the meantime, the storage electrode lines 131 may further include a plurality of branches (not shown) overlapping the cutouts 191-194.

[0071] The contact assistants 95 and 97 are connected to the end portions 125 of the gate lines 121 and the end portions 179 of the data lines 171 through the contact holes 182 and 183, respectively. The contact assistants 95 and 97 protect the end portions 125 and 179 and complement the adhesiveness of the end portions 125 and 179 and external devices.

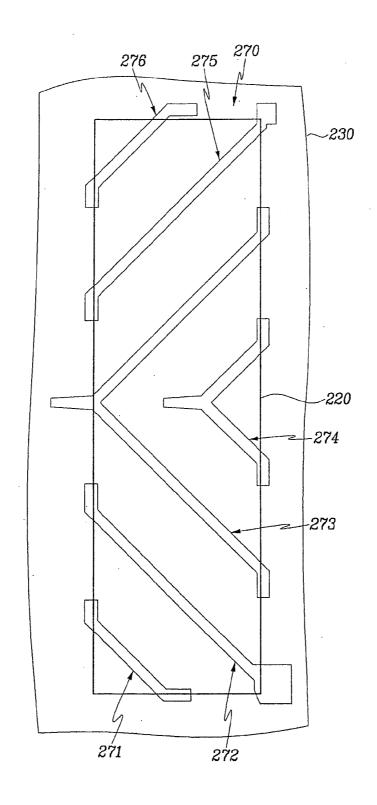

[0072] The description of the common electrode panel 200 follows with reference to FIGS. 2-4.

[0073] A light blocking member 220 called a black matrix for preventing light leakage is formed on an insulating substrate 210 such as transparent glass. The light blocking member 220 may include a plurality of openings that face the pixel electrodes 190 and it may have substantially the same shape as the pixel electrodes 190.

[0074] A plurality of color filters 230 are formed on the substrate 210 and they are disposed substantially in the areas enclosed by the light blocking member 220. The color filters 230 may extend substantially along the longitudinal direction along the pixel electrodes 190. The color filters 230 may represent one of the primary colors such as red, green and blue colors.

[0075] An overcoat 250 for preventing the color filters 230 from being exposed and for providing a flat surface is formed on the color filters 230 and the light blocking member 220.

[0076] A common electrode 270 preferably made of transparent conductive material such as ITO and IZO is formed on the overcoat 250.

[0077] The common electrode 270 has a plurality of sets of cutouts 271-276.

[0078] A set of cutouts 271-276 face a pair of first and second pixel electrodes 190a and 190b and include a plurality of lower and upper cutouts 271 and 272 and 275 and 276 and middle cutouts 273 and 274. Each of the cutouts 271-276 is disposed between adjacent cutouts 191-194 of the first pixel electrode 190a, or between the cutout 191 and a chamfered edge of the second pixel electrode 190b. In addition, each of the cutouts 271-276 has at least an oblique portion extending parallel to the upper cutout 192 or the lower cutout 192 of the first pixel electrode 190a, and the distances between adjacent two of the cutouts 271-276 and 191-194, the oblique portions thereof, and the chamfered edges of the second pixel electrode 190b, which are parallel to each other, are substantially the same. The cutouts 271-276 substantially have inversion symmetry with respect to an imaginary transverse center line of the first pixel electrode 190a. The oblique portions of the cutouts 271, 272 and 276 overlap the oblique portions of the coupling electrodes 176b that prevents light leakage near the cutouts 271, 272 and 276.

[0079] Each of the cutouts 271 and 276 has an oblique portion extending approximately from a left edge of the pixel electrode 190 approximately to an upper or lower edge of the pixel electrode 190 and transverse and longitudinal portions extending from respective ends of the oblique portion along edges of the pixel electrode 190, overlapping the edges of the pixel electrode 190, and making obtuse angles with the oblique portion.

[0080] Each of the cutouts 272 and 275 has an oblique portion, a longitudinal portion connected to an end of the oblique portion, and an expansion connected to the other end of the oblique portion. The oblique portion extends approximately from the left edge of the pixel electrode 190 approximately to upper right or lower right corner of the pixel electrode 190. The longitudinal portion extends from the end of the oblique portion along the left edge of the pixel electrode 190, overlaps the left edge of the pixel electrode 190, and makes an obtuse angle with the oblique portion. The expansion covers the respective corner of the pixel electrode 190.

[0081] The cutout 273 has a pair of oblique portions extending approximately from the center of the left edge of the pixel electrode 190 to the right edge of the pixel electrode 190, a transverse portion extending from a meeting point of the oblique portions to the left, and a pair of longitudinal portions extending from the respective oblique portions along the right edge of the pixel electrode 190, overlapping the right edge of the pixel electrode 190, and making an obtuse angle with the respective oblique portions. The cutout 274 has a transverse portion extending along the transverse center line of the pixel electrode 190, a pair of oblique portions extending from the transverse portion approximately to the right edge of the pixel electrode 190 and making obtuse angles with the transverse portion, and a pair of longitudinal portions extending from the respective oblique portions along the right edge of the pixel electrode 190, overlapping the right edge of the pixel electrode 190, and making an obtuse angle with the respective oblique portions.

[0082] The number of the cutouts 271-276 may be varied depending on the design factors, and the light blocking member 220 may also overlap the cutouts 271-276 to block the light leakage through the cutouts 271-276.

[0083] In the meantime, the cutouts 271-276 may expose portions of the color filters 230 if there is no overcoat 250, and the exposed portions of the color filters 230 may contaminate the LC layer 300.

[0084] Alignment layers 11 and 21 for aligning the LC molecules 310 are coated on inner surfaces of the panels 100 and 200, and crossed polarizers 12 and 22 are provided on outer surfaces of the panels 100 and 200, respectively, such that a transmissive axis of one of the polarizers 12 and 22 is parallel to the transverse direction. One of the polarizers may be omitted when the LCD is a reflective LCD.

[0085] The LC layer  $300\,\mathrm{has}$  negative dielectric anisotropy and the LC molecules 310 in the LC layer 300 are aligned such that their long axes are substantially vertical to the surfaces of the panels in absence of electric field.

[0086] The LCD shown in FIGS. 1-4 is represented as an equivalent circuit shown in FIG. 5.

[0087] Referring to FIG. 5, the LCD includes a plurality of gate lines, a plurality of data lines, and a plurality of pixels and each pixel includes a pair of first and second subpixels and a coupling capacitor Ccpb. Each subpixel includes a first/second LC capacitor Clca/Clcb, a first/second storage electrode Csta/Cstb, and a first/second TFT T1/T2. The first/second LC capacitor Clca/Clcb is formed of a first/second pixel electrode 190a/190b, a common electrode 270, and a region of a LC layer 300 disposed on the first/second pixel electrode 190a/ 190b. The first/second storage capacitor Csta/Cstb is formed of the first/second pixel electrode 190a/190b, a storage electrode line 131, and insulator(s) 140 and 180 interposed therebetween. The first TFT T1 is connected to a gate line, a data line supplied with data voltages, and the capacitor Clca and Csta, while the second TFT T2 is connected to a gate line previous to the gate line connected to the TFT T1, a storage electrode line supplied with a common voltage, and the capacitors Clcb and Cstb. The coupling capacitor Ccpb is formed of a coupling electrode 176b, the second pixel electrode 190b, and an insulator 140 interposed therebetween, and connected between output terminals of the TFTs T1 and T2.

[0088] Now, a behavior of a pixel is described in detail.

When the previous gate line connected to the second TFT T2 is supplied with a gate-on voltage, the second TFT T2 turns on to transmit the common voltage to the second pixel electrode 190b, which in turn is refreshed by the common voltage. When the previous gate line is supplied with a gateoff voltage, the second pixel electrode  $190\bar{b}$  becomes floating. When the current gate line connected to the first TFT T1 is supplied with a gate-on voltage, the first TFT T1 turns on to transmit a data voltage to the first pixel electrode 190a. Since the second pixel electrode 190b is floating and capacitively coupled to the first pixel electrode 190a through the coupling capacitor Ccpb, the voltage of the second pixel electrode 190b is changed the capacitive coupling. The capacitive coupling makes the magnitude of the voltage of the second pixel electrode 190b higher than that of the first pixel electrode 190a, which will be described in detail.

[0090] The voltage across the first LC capacitor Clca is denoted by Va(=Vd1), and the voltage across the second LC capacitor Clcb is denoted by Vb. The voltage distribution law results in:

$Vb \approx 1/(C_1+2C_2) \times [(2-C_3/C_2) \times (C_1+C_2) \times Vd1],$

where C<sub>1</sub>=Clca+Csta, C<sub>2</sub>=Ccpb, and C<sub>3</sub>=Clcb+Cstb, and capacitances of the capacitors Clea, Csta, Clcb, Cstb, and

Ccpb are denoted by the same characters as those of the capacitors Clca, Csta, Clcb, Cstb, and Ccpb. Parasitic capacitances between terminals of the TFTs T1 and T2 are neglected since it is trivial.

[0091] The voltage Vb can be controlled such that the voltage Vb approaches the voltage Va but always higher than the voltage Va by adjusting the capacitances capacitors Clca, Csta, Clcb, Cstb, and Ccpb. In particular, the ratio of the voltages Va and Vb can be effectively controlled by adjusting the capacitance Ccpb. The capacitance Ccpb can be adjusted by varying the overlapping area or the distance between the coupling electrode 176b and the second pixel electrode 190b. For example, the overlapping area can be varied by changing the width of the coupling electrode 176b and the distance can be varied by placing the coupling electrode 176b in the same layer as the gate lines 121.

[0092] The non-zero voltages across the LC capacitors Clca and Clcb generate electric fields substantially perpendicular to the surfaces of the panels 100 and 200 and the LC molecules 310 tend to change their orientations in response to the electric field such that their long axes are perpendicular to the field directions. Since the field strength in the first LC capacitor Clca is different from that in the second LC capacitor Clcb, the LC molecules 310 in the first and the second LC capacitors Clca and Clcb experience different tilting forces to have different tilt angles. Accordingly, the lateral visibility is improved.

[0093] According to experiments, the lateral visibility of LCDs according to this embodiment represented by 1–(gradient of lateral gamma curve)/(gradient of front gamma curve) was measured to be about 0.22-0.35 that is excellent. In addition, the aperture ratio of the LCDs was almost equal to that of LCDs having a pixel electrode per a pixel.

[0094] The area of the first pixel electrode 190a is preferably larger than that of the second pixel electrode 190b, but it is preferably smaller than about six times the area of the second pixel electrode 190b. In the LCD shown in FIGS. 1-4, the area of the first pixel electrode 190a is about five times the area of the second pixel electrode 190b. In addition, the ratio of the voltages Va and Vb is preferably in a range between about 0.50 and about 0.95.

[0095] In the meantime, a set of the cutouts 191-194 and 271-276 divides a pair of first and second pixel electrodes 190a and 190b into a plurality of subareas and each subarea has two major edges as shown in FIG. 3. The cutouts 191-194 and 271-276 control the tilt directions of the LC molecules 310 in the LC layer 300. This will be described in detail.

[0096] The cutouts 191-194 and 271-276 of the first electrodes 190a and 270 and the edges of the second pixel electrodes 190 distort the electric fields to have a horizontal component. The horizontal components of the electric fields are perpendicular to the edges of the cutouts 191-194 and 271-276 and the edges of the pixel electrodes 190.

[0097] Accordingly, the tilt directions of the LC molecules 310 on the subareas are different and thus the viewing angle is enlarged.

[0098] At least one of the cutouts 191-194 and 271-276 can be substituted with protrusions or depressions, and the shapes and the arrangements of the cutouts 191-194 and 271-276 may be modified.

[0099] Furthermore, and the shape and the position of the coupling electrode 176b may be modified, which will be described in detail.

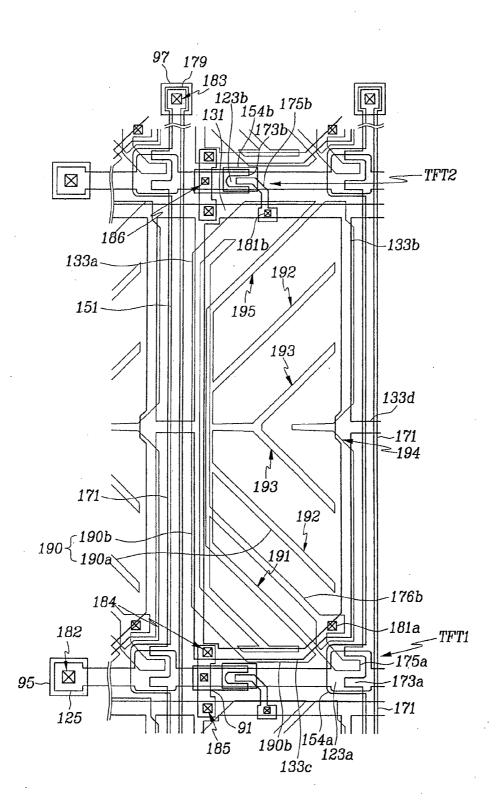

[0100] An LCD according to another embodiment of the present invention will be described in detail with reference to FIGS. 6 and 7.

[0101] FIG. 6 is a layout view of a TFT array panel for an LCD according to another embodiment of the present invention, and FIG. 7 is an equivalent circuit diagram of an LCD including the TFT array panel shown in FIG. 6.

[0102] An LCD according to this embodiment includes a TFT array panel shown in FIG. 6, the common electrode panel 200 shown in FIG. 2, and the LC layer 310 shown in FIG. 4, and layered structures of the panels according to this embodiment are almost the same as that shown in FIG. 4.

[0103] Regarding the TFT array panel, a plurality of gate lines 121 including a plurality of first and second gate electrodes 123a and 123b and end portions 125 and a plurality of storage electrode lines 131 including a plurality of first to third storage electrodes 133a-133c and branch connections 133d are formed on a substrate 110, and a gate insulating layer 140, a plurality of semiconductor stripes 151 including a plurality of projections 154a and a plurality of semiconductor islands 154b, and a plurality of ohmic contact stripes 161including a plurality of projections 163 and a plurality of ohmic contact islands 165 are sequentially formed thereon. A plurality of data lines 171 including a plurality of first source electrodes 173a and end portions 179, and a plurality of first and second drain electrodes 175a and 175b are formed on the ohmic contacts 161 and 165, and a passivation layer 180 is formed thereon. A plurality of contact holes 181a-186 are provided at the passivation layer 180 and the gate insulating layer 140. A plurality of sets of first and second pixel electrodes 190a and 190b having a plurality of cutouts 191-194, a plurality of contact assistants 95 and 97, and a plurality of storage connections 91 are formed on the passivation layer

[0104] Regarding the common electrode panel 200, a light blocking member 220, a plurality of color filters 230, an overcoat 250, and a common electrode 270 having a plurality of cutouts 271-276 are formed on an insulating substrate 210 as shown in FIGS. 2 and 4.

[0105] Different from the LCD shown in FIGS. 1-5, a pair of first and second pixel electrodes 190a and 190b according to this embodiment are divided along a cutout 192 rather than a cutout 191 and a pixel of the LCD according to this embodiment includes first to third TFTs T1-T3. Like the LCD shown in FIGS. 1-5, the first TFT T1 is connected to a gate line, a data line supplied with data voltages, and a first LC capacitor Clca and a first storage capacitor Csta, while the second TFT T2 is connected to a gate line previous to the gate line connected to the TFT T1, a storage electrode line supplied with a common voltage, and a second LC capacitor Clcb and a second storage capacitor Cstb. The third TFT T3 is connected to the previous gate line, the data line, and the capacitors Clcb and Cstb.

[0106] Referring to FIG. 6, the first TFT T1 includes a first gate electrode 123a, a first source electrode 173a, and a first drain electrode 175a, while the third TFT T3 includes a first gate electrode 123a connected to the previous gate line, a first source electrode 173a, and a third drain electrode 175c. The second TFT T2 includes a second gate electrode 123b, a second source electrode 173b, and a second drain electrode 175b.

[0107] The first and the third drain electrodes 175a and 175 extend along a second storage electrode 133b and then they are curved along a cutout 274 to meet each other. The first drain electrode 175a has a pair of branches that form a cou-

pling electrode 176b and overlap the cutouts 271 and 272. The third drain electrode 175d has a branch that forms a coupling electrode 176c and overlaps the cutout 275.

[0108] In operation, when the previous gate line connected to the second and the third TFTs T2 and T3 is supplied with a gate-on voltage, the second TFT T2 turns on to transmit the common voltage to the second pixel electrode 190b and the third TFT T3 also turns on to transmit a data voltage for a previous pixel to the first pixel electrode 190a. Then, the coupling capacitor Ccpb stores the voltage difference between the previous data voltage and the common voltage. When the current gate line connected to the first TFT T1 is supplied with a gate-on voltage, the first TFT T1 turns on to transmit a data voltage for a current pixel to the first pixel electrode 190a. Since the second pixel electrode 190b is floating and capacitively coupled to the first pixel electrode 190a through the coupling capacitor Ccpb, the voltage of the second pixel electrode 190b is changed by the capacitive coupling.

[0109] Many of the above-described features of the LCD shown in FIGS. 1-5 may be appropriate to the LCD shown in FIGS. 6 and 7.

[0110] An LCD according to another embodiment of the present invention will be described in detail with reference to FIGS. 8 and 9.

[0111] FIG. 8 is a layout view of a TFT array panel for an LCD according to another embodiment of the present invention, and FIG. 9 is an equivalent circuit diagram of an LCD including the TFT array panel shown in FIG. 8.

[0112] An LCD according to this embodiment includes a TFT array panel shown in FIG. 8, the common electrode panel 200 shown in FIG. 2, and the LC layer 310 shown in FIG. 4, and layered structures of the panels according to this embodiment are almost the same as that shown in FIG. 4.

[0113] Regarding the TFT array panel that is similar to that shown in FIG. 6, a plurality of gate lines 121 including a plurality of first and second gate electrodes 123a and 123b and end portions 125 and a plurality of storage electrode lines 131 including a plurality of first to third storage electrodes 133a-133c and branch connections 133d are formed on a substrate 110, and a gate insulating layer 140, a plurality of semiconductor stripes 151 including a plurality of projections 154a and a plurality of semiconductor islands 154b, and a plurality of ohmic contact stripes 161 including a plurality of projections 163 and a plurality of ohmic contact islands 165 are sequentially formed thereon. A plurality of data lines 171 including a plurality of first source electrodes 173a and end portions 179, and a plurality of first and second drain electrodes 175a and 175b are formed on the ohmic contacts 161 and 165, and a passivation layer 180 is formed thereon. A plurality of contact holes 181a-186 are provided at the passivation layer 180 and the gate insulating layer 140. A plurality of sets of pixel electrodes 190a-190c having a plurality of cutouts 191-194, a plurality of contact assistants 95 and 97, and a plurality of storage connections 91 are formed on the passivation layer 180.

[0114] Regarding the common electrode panel 200, a light blocking member 220, a plurality of color filters 230, an overcoat 250, and a common electrode 270 having a plurality of cutouts 271-276 are formed on an insulating substrate 210 as shown in FIGS. 2 and 4.

[0115] Different from the LCD shown in FIGS. 6 and 7, a set of pixel electrodes 190a-190c include first, second and a pair of third pixel electrodes 190a-190c forming first to third

LC capacitors Clca, Clcb and Clcb and first to third storage capacitors Csta, Cstb and Cstc. The first and the second pixel electrodes 190a and 190b are divided along a cutout 192, while the second and the third pixel electrodes 190b and 190c are divided along a cutout 191. The third electrodes 190c are floating.

[0116] In addition, the first drain electrode 175a has a branch that form a coupling electrode 176b and includes a transverse portion overlapping a third storage electrode 133c, an oblique portion connected to the transverse portion and overlapping a cutout 271, a longitudinal portion overlapping a storage electrode 13a, and a pair of oblique portions partly overlapping cutouts 275 and 276. Accordingly, the coupling electrode 176b overlaps the second and the third pixel electrodes 190b and 190c to form coupling capacitors Ccpb and Ccpc. The third drain electrode 175d has no branch.

[0117] In operation, when the previous gate line connected to the second and the third TFTs T2 and T3 is supplied with a gate-on voltage, the second TFT T2 turns on to transmit the common voltage to the second pixel electrode 190b and the third TFT T3 also turns on to transmit a data voltage for a previous pixel to the first pixel electrode 190a. When the current gate line connected to the first TFT T1 is supplied with a gate-on voltage, the first TFT T1 turns on to transmit a data voltage for a current pixel to the first pixel electrode 190a. Since the second and the third pixel electrodes 190b and 190care floating and capacitively coupled to the first pixel electrode 190a through the coupling capacitor Ccpb, the voltages of the second and the third pixel electrodes 190b and 190c are changed by the capacitive coupling. The capacitive coupling makes the magnitude of the voltage of the second pixel electrode 190b higher than that of the first pixel electrode 190a, and it makes the magnitude of the voltage of the third pixel electrode 190c lower than that of the first pixel electrode 190a, which will be described in detail.

[0118] The voltage across the first LC capacitor Clca is denoted by Va, and the voltage across the third LC capacitor Clcc is denoted by Vc. The voltage distribution law results in:

Vb≈Va×[(Ccpc/(Ccpc+Clcc)]<Va,

where capacitances of the capacitors Clcpc and Clcc are denoted by the same characters as those of the capacitors Clcpc and Clcc. The ratio of the voltages Va and Vc can be effectively controlled by adjusting the capacitance Ccpc. The capacitance Ccpc can be adjusted by varying the overlapping area or the distance between the coupling electrode **176***b* and the third pixel electrode **190***c*. In the LCD shown in FIGS. **1-4**, the area of the first to the third pixel electrode **190***a* has a proportion relation 1:1.37:0.44.

[0119] Many of the above-described features of the LCD shown in FIGS. 1-7 may be appropriate to the LCD shown in FIGS. 8 and 9.

[0120] An LCD according to another embodiment of the present invention will be described in detail with reference to FIGS. 10 and 11.

[0121] FIG. 10 is a layout view of a TFT array panel for an LCD according to another embodiment of the present invention, and FIG. 11 is an equivalent circuit diagram of an LCD including the TFT array panel shown in FIG. 10.

[0122] An LCD according to this embodiment includes a TFT array panel shown in FIG. 10, the common electrode panel 200 shown in FIG. 2, and the LC layer 310 shown in FIG. 4, and layered structures of the panels according to this embodiment are almost the same as that shown in FIG. 4.

[0123] Regarding the TFT array panel, a plurality of gate lines 121 including a plurality of first and second gate electrodes 123a and 123b and end portions 125 and a plurality of storage electrode lines 131 including a plurality of first to third storage electrodes 133a-133c and branch connections 133d are formed on a substrate 110, and a gate insulating layer 140, a plurality of semiconductor stripes 151 including a plurality of projections 154a and a plurality of semiconductor islands 154b, and a plurality of ohmic contact stripes 161 including a plurality of projections 163 and a plurality of ohmic contact islands 165 are sequentially formed thereon. A plurality of data lines 171 including a plurality of first source electrodes 173a and end portions 179, and a plurality of first and second drain electrodes 175a and 175b are formed on the ohmic contacts 161 and 165, and a passivation layer 180 is formed thereon. A plurality of contact holes 181a and 182-186 are provided at the passivation layer 180 and the gate insulating layer 140. A plurality of sets of first and second pixel electrodes 190a and 190b having a plurality of cutouts 191-194, a plurality of contact assistants 95 and 97, and a plurality of storage connections 91 are formed on the passivation layer 180.

[0124] Regarding the common electrode panel 200, a light blocking member 220, a plurality of color filters 230, an overcoat 250, and a common electrode 270 having a plurality of cutouts 271-276 are formed on an insulating substrate 210 as shown in FIGS. 2 and 4.

[0125] Different from the LCD shown in FIGS. 1-5, the second pixel electrodes 190b according to this embodiment are floating and there is no contact hole exposing the first drain electrode 175a. In addition, the coupling electrodes 176a overlap all the cutouts 271-276 and almost all the storage electrodes 133a-133c. Accordingly, the coupling electrode 176b overlaps the first and the second pixel electrodes 190a and 190b to form coupling capacitors Cepa and Ccpb. The capacitive coupling makes the magnitude of the magnitude of the voltage of the second pixel electrode 190c lower than that of the first pixel electrode 190a.

[0126] Many of the above-described features of the LCD shown in FIGS. 1-5 may be appropriate to the LCD shown in FIGS. 10 and 11.

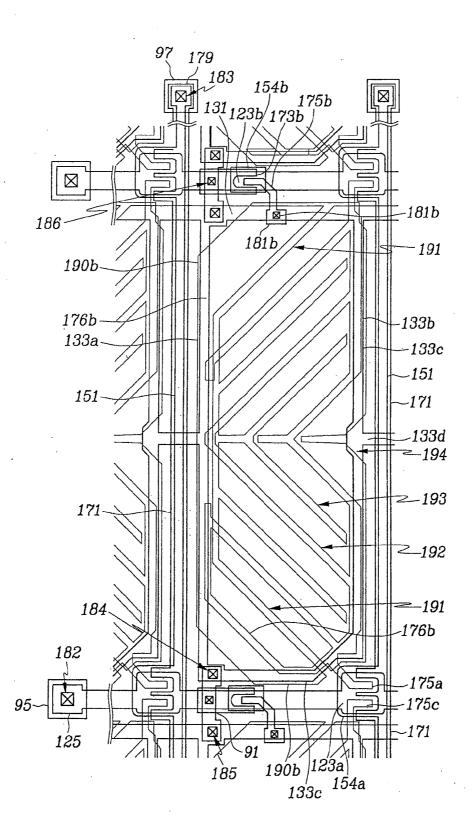

[0127] An LCD according to another embodiment of the present invention will be described in detail with reference to FIGS. 12 and 13.

[0128] FIGS. 12 and 13 are layout views of TFT array panels for an LCD according to another embodiment of the present invention.

[0129] Each LCD according to these embodiments includes a TFT array panel shown in FIG. 12 or 13, the common electrode panel 200 shown in FIG. 2, and the LC layer 310 shown in FIG. 4, and layered structures of the panels according to this embodiment are almost the same as that shown in FIG. 4.

[0130] Regarding the TFT array panel, a plurality of gate lines 121 including a plurality of first and second gate electrodes 123a and 123b and end portions 125 and a plurality of storage electrode lines 131 including a plurality of first to third storage electrodes 133a-133c and branch connections 133d are formed on a substrate 110, and a gate insulating layer 140, a plurality of semiconductor stripes 151 including a plurality of projections 154a and a plurality of semiconductor islands 154b, and a plurality of ohmic contact stripes 161 including a plurality of projections 163 and a plurality of ohmic contact islands 165 are sequentially formed thereon. A

plurality of data lines 171 including a plurality of first source electrodes 173a and end portions 179, and a plurality of first and second drain electrodes 175a and 175b are formed on the ohmic contacts 161 and 165, and a passivation layer 180 is formed thereon. A plurality of contact holes 181a-186 are provided at the passivation layer 180 and the gate insulating layer 140. A plurality of sets of first and second pixel electrodes 190a and 190b having a plurality of cutouts 191-194, a plurality of contact assistants 95 and 97, and a plurality of storage connections 91 are formed on the passivation layer 180. The areal ratio of the first and the second pixel electrodes 190a and 190b is about 5:1.

[0131] Regarding the common electrode panel 200, a light blocking member 220, a plurality of color filters 230, an overcoat 250, and a common electrode 270 having a plurality of cutouts 271-276 are formed on an insulating substrate 210 as shown in FIGS. 2 and 4.

[0132] The LCD shown in FIG. 12 has a similar layout to the LCD shown in FIG. 6. However, a pair of first and second pixel electrodes 190a and 190b are divided along a cutout 191 rather than a cutout 192. In addition, a coupling electrode 176b extending from the first drain electrode 175a has a transverse portion overlapping the third storage electrode, oblique portions overlapping the cutouts 271 and 272, and a longitudinal portion overlapping the first storage electrode 133a.

[0133] The LCD shown in FIG. 13 has a similar layout as the LCD shown in FIG. 10. However, a coupling electrode 176b extending from the drain electrode 175a and 175b has less overlapping portions than that shown in FIG. 10. For example, a longitudinal portion overlapping the first storage electrode 133a is shorter than that shown in FIG. 10.

[0134] Many of the above-described features of the LCD shown in FIGS. 1-5,6 and 10 may be appropriate to the LCD shown in FIGS. 12 and 13.

[0135] While the present invention has been described in detail with reference to the preferred embodiments, those skilled in the art will appreciate that various modifications and substitutions can be made thereto without departing from the spirit and scope of the present invention as set forth in the appended claims.

What is claimed is:

- 1. A liquid crystal display comprising:

- a first substrate;

- a plurality of first signal lines formed on the first substrate; a plurality of second signal lines intersecting the first signal lines:

- a first pixel electrode and a second pixel electrode;

- a first thin film transistor connected to the first pixel electrode:

- a second thin film transistor connected to the second pixel electrode:

- a second substrate facing the first substrate; and

- a liquid crystal layer interposed between the first and second substrates and including liquid crystal molecules,

- wherein the liquid crystal molecules are oriented by a plurality of tilt direction defining members when an electric field is applied to the first pixel electrode or the second pixel electrode, and

- wherein the oriented directions of the liquid crystal molecules are inclined with respect to the first signal lines or the second signal lines and are different.

\* \* \* \* \*

| 专利名称(译)        | 液晶显示器                                                              |         |            |

|----------------|--------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | US20120154702A1                                                    | 公开(公告)日 | 2012-06-21 |

| 申请号            | US13/407339                                                        | 申请日     | 2012-02-28 |

| [标]申请(专利权)人(译) | 基姆熙燮<br>吴浚HAK<br>你斗焕<br>杨YOUNG CHOL                                |         |            |

| 申请(专利权)人(译)    | 金喜善SEOB<br>吴浚-HAK<br>游斗焕<br>杨YOUNG-CHOL                            |         |            |

| 当前申请(专利权)人(译)  | 三星DISPLAY CO., LTD.                                                |         |            |

| [标]发明人         | KIM HEE SEOB OH JOON HAK YOU DOO HWAN YANG YOUNG CHOL              |         |            |

| 发明人            | KIM, HEE-SEOB<br>OH, JOON-HAK<br>YOU, DOO-HWAN<br>YANG, YOUNG-CHOL |         |            |

| IPC分类号         | G02F1/136 G02F1/1337 G02F1/1333 G02F1/1343 G02F1/1368 G02F1/139    |         |            |

| CPC分类号         | G02F1/133707 G02F1/1393 G02F1/134336                               |         |            |

| 优先权            | 1020030037090 2003-06-10 KR                                        |         |            |

| 外部链接           | Espacenet USPTO                                                    |         |            |

| L+>            |                                                                    | 97      | 179        |

#### 摘要(译)

提供一种薄膜晶体管阵列面板,包括:基板;多个第一信号线形成在基板上;多条第二信号线,与第一信号线交叉,以限定像素区域;第一和第二像素电极基本上设置在像素区域中并具有不同的区域;多个薄膜晶体管,连接到第一和第二信号线以及第一和第二像素电极中的至少一个;耦合电极与第二像素电极重叠;和倾斜方向限定构件,用于确定在基板上形成的液晶分子的倾斜方向。