#### US007843533B2

US 7,843,533 B2

Nov. 30, 2010

## (12) United States Patent

Noguchi et al.

#### (54) LIQUID CRYSTAL DISPLAY WITH TRANSMISSION AND REFLECTION REGIONS

(75) Inventors: Noboru Noguchi, Tenri (JP); Hisashi

Nagata, Yokohama (JP); Toshihiro

Matsumoto, Nara (JP); Kazuhiko

Tsuda, Ikoma-gun (JP); Makoto Kanbe,

Sakurai (JP); Akihiko Kojima, Tenri

(JP)

(73) Assignee: Sharp Kabushiki Kaisha, Osaka (JP)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 1177 days.

(21) Appl. No.: 11/353,952

(22) Filed: Feb. 15, 2006

(65) **Prior Publication Data**

US 2006/0125755 A1 Jun. 15, 2006

#### Related U.S. Application Data

(63) Continuation of application No. 10/244,820, filed on Sep. 17, 2002, now Pat. No. 7,084,849.

#### (30) Foreign Application Priority Data

| Sep. 18, 2001 | (JP) | <br>2001-283001 |

|---------------|------|-----------------|

| Feb. 25, 2002 | (JP) | <br>2002-048244 |

| Sep. 6, 2002  | (JP) | <br>2002-261514 |

(51) **Int. Cl.** *G02F 1/1335* (2006.01) *G02F 1/1343* (2006.01)

See application file for complete search history.

### (56) References Cited

(10) Patent No.:

(45) Date of Patent:

#### U.S. PATENT DOCUMENTS

4,605,977 A

8/1986 Matthews

4,853,810 A

8/1989 Pohl et al.

5,438,342 A

8/1995 Yamaguchi

(Continued)

#### FOREIGN PATENT DOCUMENTS

JP 4-223428 A 8/1992

(Continued)

#### OTHER PUBLICATIONS

U.S. Appl. No. 10/244,820, filed Sep. 17, 2002.

(Continued)

Primary Examiner—David Nelms

Assistant Examiner—Nathanael R Briggs

(74) Attorney, Agent, or Firm—Nixon & Vanderhye P.C.

#### (57) ABSTRACT

A liquid crystal display device includes: pixel electrodes arranged in columns and rows, each including a reflective electrode region; scanning lines; and signal lines. The device sequentially supplies a scanning signal voltage to one of the scanning lines after another to select one group of pixel electrodes, connected to the same one of the scanning lines, after another, and then supplies display signal voltages to the selected group of pixel electrodes by way of the signal lines, thereby displaying an image thereon. The pixel electrodes are arranged such that the polarity of a voltage to be applied to a liquid crystal layer is inverted for every predetermined number of pixel electrodes in each of the rows and in each of the columns. The display signal voltage to be supplied to each pixel electrode is updated at a frequency of 45 Hz or less.

#### 12 Claims, 22 Drawing Sheets

# US 7,843,533 B2 Page 2

|              | U.S. 1 | PATENT  | DOCUMENTS             | JP<br>JP | 2000-305110 A<br>2002-14321 A | 11/2000<br>1/2002                     |

|--------------|--------|---------|-----------------------|----------|-------------------------------|---------------------------------------|

| 5,764,324    | l A    | 6/1998  | Lu et al.             | KR       | 2000-0001129                  | 1/2000                                |

| 5,991,883    | 3 A    | 11/1999 | Atkinson              | KR       | 2001-0025955                  | 4/2001                                |

| 6,195,140    | B1*    | 2/2001  | Kubo et al 349/44     | 1111     | 2001 0023933                  | 72001                                 |

| 6,429,842    | 2 B1   | 8/2002  | Shin et al.           |          | OTHER BILL                    | DI ICATIONS                           |

| 6,452,654    | 1 B2*  | 9/2002  | Kubo et al 349/114    |          | OTHER PU                      | BLICATIONS                            |

| 6,683,666    | 5 B1*  | 1/2004  | Jang et al 349/113    | IIS Ar   | nd No. 09/856 926 filed       | Apr. 28, 20002 entitled "Display      |

| 2002/0033918 | 3 A1*  | 3/2002  | Shigeno et al 349/114 |          |                               | e and Electronic Device Mounting      |

| 2002/0051104 | 1 A1   | 5/2002  | Kurata                | Same".   | nionou or briving sum         | o and Brothomic Boyles Mountaing      |

| F            | OREIG  | N PATE  | NT DOCUMENTS          | Korean   | Office Action issued on C     | Oct. 4, 2005 (w/English translation). |

| JP           | 05-134 | 1629    | 5/1993                | * cited  | by examiner                   |                                       |

FIG.3A

FIG.5

FIG.6

FIG.9

FIG. 10A

*FIG.10B*

FIG.12

FIG.13

Potential Difference B IT0 [(512) Al (524) Potential Difference A FIG.15ITO (522)

Potential at ITO Electrode ≠ Potential at AL Electrode

Potential Difference A ≠ Potential Difference B

FIG.16

Nov. 30, 2010

FIG. 19B

FIG. 194

FIG.20

FIG.21

*FIG.22*

#### LIQUID CRYSTAL DISPLAY WITH TRANSMISSION AND REFLECTION REGIONS

This application is a Continuation of application Ser. No. 5 10/244,820, filed Sep. 17, 2002, now U.S. Pat. No. 7,084,849 the entire content of which is hereby incorporated herein by reference in this application.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a liquid crystal display device, and more particularly relates to a liquid crystal display device that can display an image of quality with its power 15 dissipation reduced by utilizing reflected light.

#### 2. Description of the Related Art

As various types of portable electronic appliances, including cell phones and personal digital assistants (PDAs), have become more and more popularized, liquid crystal display 20 devices, which are often built in these appliances, are increasingly required to reduce their power dissipation. Meanwhile, the amount of information to be displayed on the liquid crystal display devices has also been on the rise. Thus, the liquid crystal display devices also have to further improve the quality of an image to be displayed thereon.

To provide a liquid crystal display device that can display an image of quality with its power dissipation reduced, the present inventors carried out an intensive research on a method of driving a TFT liquid crystal display device of the reflection type at a decreased frequency. As a result of experiments, the present inventors discovered and confirmed that if the image on the display is refreshed at a decreased rate, then a flicker (or variation in brightness) is produced and cannot be eliminated even by adjusting the so-called "counter voltage shift". Hereinafter, the relationship between the flicker and the counter voltage shift will be described.

difficult by adjust electron by the counter of experiments to flicker in the counter voltage and cannot be eliminated even by adjusting the so-called "counter voltage shift". Hereinafter, the relationship between the flicker and the counter voltage shift will be described.

In a TFT liquid crystal display device, a feedthrough phenomenon occurs in the voltage being applied to pixel electrodes due to the parasitic capacitance formed by its TFTs and 40 the switching operations of the TFTs. Accordingly, to compensate for such a feedthrough voltage, an offset voltage, which has its amplitude defined in accordance with the feedthrough voltage, is applied to a counter electrode that is disposed so as to face the pixel electrodes by way of a liquid 45 crystal layer.

However, if the feedthrough voltage is not equal to the offset voltage (the difference between the feedthrough and offset voltages is sometimes called a "counter voltage shift"), then the effective voltage to be applied to the liquid crystal 50 layer changes every time the polarity of the voltage is inverted. As a result, the observer senses that voltage variation as a flicker.

Even for a normal liquid crystal display device to be driven at a refresh rate of 60 Hz, various countermeasures are taken 55 to make such a flicker as insensible as possible. Examples of those countermeasures include a so-called "gate line inversion" (which is also called a "1H inversion") technique, by which the polarity of the applied voltage is inverted on a gate line basis. However, the counter voltage shift might sometimes be too great to be eliminated by any of those countermeasures. In that case, the flicker might be sensed just like a moving striped pattern.

The present inventors carried out experiments on a reflective liquid crystal display device having pixel pitches of 60  $^{65}$   $\mu$ m×RGB×180  $\mu$ m to find a counter voltage shift value at which no flicker was perceivable in a half-tone display state.

2

Consequently, the present inventors discovered and confirmed that where the observer was watching the image on the display carefully, a counter voltage shift of about 250 mV resulted in a quite perceivable flicker even when the device was driven by the gate line inversion technique.

If the liquid crystal display device is driven at a decreased frequency to reduce its power dissipation, that flicker resulting from the counter voltage shift gets even more noticeable. For example, if the device is driven at 5 Hz, even a counter voltage shift of as small as 30 mV makes the line-by-line difference in brightness between the gate lines easily perceivable. What is worse, the refresh period (i.e., vertical scanning period) is as long as 200 ms. Accordingly, in that case, the observer can clearly see with his or her own eyes how bright and dark lines are alternated on a vertical scanning period basis. Thus, such a liquid crystal display device is far from being a commercially viable product.

That counter voltage shift of about 30 mV is so small as to be easily created due to any of a number of inevitably occurring variations that include: a variation in thickness of the liquid crystal layer during the manufacturing process; a small variation in temperature of the liquid crystal layer according to the operating environment; and degradation in electrical or physical properties of the liquid crystal material or alignment film material with time. Nevertheless, when a huge number of liquid crystal display devices should be produced, it is very difficult to reduce the counter voltage shift to less than 30 mV by adjusting the offset voltage to be applied to the counter electrode. A counter voltage shift that can be compensated for by the currently available technique is at least about 100 mV.

The present inventors discovered and confirmed via experiments that when the refresh rate is about 45 Hz or less, the flicker is too much noticeable to be eliminated by any of the currently available counter voltage shift adjustment techniques.

The results of our experiments also revealed that the flicker is perceivable particularly easily in a reflective/transmissive liquid crystal display device (which will be herein referred to as a "dual-mode liquid crystal display device") in which each pixel thereof includes a reflective portion for conducting a display operation in a reflection mode and a transmissive portion for conducting a display operation in a transmission mode. In the dual-mode liquid crystal display device, the flicker also becomes particularly noticeable when the refresh rate is as low as about 45 Hz or less. However, in the device of this type, the flicker is perceivable even more easily than a reflective or transmissive device. Accordingly, some countermeasure must always be taken for the dual-mode device, not just when the device is driven at a decreased frequency.

#### SUMMARY OF THE INVENTION

In order to overcome the problems described above, an object of the present invention is to provide a liquid crystal display device that produces a hardly perceivable flicker even when the device is driven with its power dissipation reduced.

A more specific object of the present invention is to provide a liquid crystal display device that can display an image of quality thereon almost without allowing the observer to perceive any flicker even when driven at a low frequency of 45 Hz or less.

A liquid crystal display device according to a preferred embodiment of the present invention preferably includes pixel electrodes, scanning lines, signal lines, switching elements, a liquid crystal layer, and at least one counter electrode. The pixel electrodes are preferably arranged in columns and rows and each of the pixel electrodes preferably

includes a reflective electrode region. The scanning lines preferably extend in a row direction, while the signal lines preferably extend in a column direction. Each of the switching elements is preferably provided for an associated one of the pixel electrodes and is preferably connected to the associated pixel electrode, an associated one of the scanning lines and an associated one of the signal lines. The at least one counter electrode preferably faces the pixel electrodes by way of the liquid crystal layer. The liquid crystal display device preferably supplies sequentially a scanning signal voltage to one of the scanning lines after another to select one group of pixel electrodes, which are connected to the same one of the scanning lines, after another from the pixel electrodes, and then supplies display signal voltages to the selected group of pixel electrodes by way of the signal lines, thereby displaying 15 an image thereon. The pixel electrodes are preferably arranged in such a manner that the polarity of a voltage to be applied to the liquid crystal layer is inverted for every predetermined number of pixel electrodes in each of the rows and in each of the columns. The display signal voltage to be 20 supplied to each of the pixel electrodes is preferably updated at a frequency of 45 Hz or less.

In one preferred embodiment of the present invention, the switching elements that are connected to one of the scanning lines preferably include: a first group of switching elements, 25 which are connected to the pixel electrodes belonging to one of two rows that are adjacent to the scanning line; and a second group of switching elements, which are connected to the pixel electrodes belonging to the other adjacent row. The first and second groups of switching elements are preferably arranged along the scanning line such that every predetermined number of switching elements of the first group are followed by every predetermined number of switching elements of the second group. The polarity of the voltage to be applied to the liquid crystal layer is preferably inverted for every group of pixel electrodes that are connected to their associated predetermined number of signal lines.

In an alternative preferred embodiment, the switching elements that are connected to one of the signal lines preferably include: a first group of switching elements, which are connected to the pixel electrodes belonging to one of two columns that are adjacent to the signal line; and a second group of switching elements, which are connected to the pixel electrodes belonging to the other adjacent column. The first and second groups of switching elements are preferably arranged 45 along the signal line such that every predetermined number of switching elements of the first group are followed by every predetermined number of switching elements of the second group. The polarity of the voltage to be applied to the liquid crystal layer is preferably inverted for every group of pixel 50 electrodes that are connected to their associated predetermined number of scanning lines.

In another preferred embodiment of the present invention, each of the pixel electrodes is preferably a reflective electrode. In that case, the pixel electrodes preferably have mutually congruent planar shapes and are preferably arranged so as to overlap with each other substantially entirely when translated in the row direction or in the column direction.

In still another preferred embodiment, each of the pixel electrodes preferably includes the reflective electrode region 60 and a transmissive electrode region.

In this particular preferred embodiment, a shift width of geometric centers of mass of the transmissive electrode regions of the pixel electrodes as measured in the row direction or in the column direction is preferably half or less of the 65 pitch of the pixel electrodes as measured in the row direction or in the column direction.

4

More specifically, the transmissive electrode regions of the pixel electrodes preferably have mutually congruent planar shapes and are preferably arranged so as to overlap with each other substantially entirely when translated in the row direction or in the column direction.

In yet another preferred embodiment, the switching elements that are connected to one of the scanning lines preferably include: a first group of switching elements, which are connected to the pixel electrodes belonging to one of the rows that is adjacent to, and located over, the scanning line; and a second group of switching elements, which are connected to the pixel electrodes belonging to one of the rows that is adjacent to, and located under, the scanning line. The first and second groups of switching elements are preferably arranged along the scanning line such that every predetermined number of switching elements of the first group are followed by every predetermined number of switching elements of the second group. A distance from each of the switching elements of the first group to a geometric center of mass of the transmissive electrode region of the pixel electrode that is connected to the switching element of the first group is preferably different from a distance from each of the switching elements of the second group to a geometric center of mass of the transmissive electrode region of the pixel electrode that is connected to the switching element of the second group.

In yet another preferred embodiment, each of the pixel electrodes preferably includes only one transmissive electrode region that is surrounded with the reflective electrode region.

In yet another preferred embodiment, a storage capacitor is preferably formed below the reflective electrode region.

In yet another preferred embodiment, the pixel electrodes preferably define multiple pixels, respectively. Each of the pixels preferably includes a reflective portion that is defined by the reflective electrode region and a transmissive portion that is defined by the transmissive electrode region. An electrode potential difference created between the electrodes of the reflective portion is preferably approximately equal to an electrode potential difference created between the electrodes of the transmissive portion.

In this particular preferred embodiment, the reflective electrode region preferably includes: a reflective conductive layer; and a transparent conductive layer, which is provided on one surface of the reflective conductive layer so as to face the liquid crystal layer.

More specifically, the transparent conductive layer is preferably amorphous.

Preferably, a difference in work function between the transparent conductive layer and the transmissive electrode region is preferably within 0.3 eV.

More particularly, the transmissive electrode region is preferably made of an ITO layer, the reflective conductive layer preferably includes an Al layer, and the transparent conductive layer is preferably made of an oxide layer mainly composed of indium oxide and zinc oxide.

In yet another preferred embodiment, the transparent conductive layer preferably has a thickness of 1 nm to 20 nm.

In yet another preferred embodiment, the pixel electrodes preferably define multiple pixels, respectively. Each of the pixels preferably includes a reflective portion that is defined by the reflective electrode region and a transmissive portion that is defined by the transmissive electrode region. To substantially compensate for a difference between an electrode potential difference created in the reflective portion and an electrode potential difference created in the transmissive portion, alternating current signal voltages having mutually different center levels are preferably applied to respective por-

tions of the liquid crystal layer that correspond to the reflective portion and the transmissive portion.

In this particular preferred embodiment, the at least one counter electrode preferably includes: a first counter electrode that faces the reflective electrode regions of the pixel 5 electrodes; and a second counter electrode that faces the transmissive electrode regions of the pixel electrodes. The first and second counter electrodes are preferably electrically isolated from each other.

Specifically, each of the first and second counter electrodes 10 is preferably formed in the shape of a comb that has a plurality of branches extending in the row direction.

More specifically, counter signal voltages to be applied to the first and second counter electrodes are preferably alternating current signal voltages that have the same polarity, the 15 same period and the same amplitude but have mutually different center levels.

In yet another preferred embodiment, the reflective portion preferably includes: a reflective portion liquid crystal capacitor, which is defined by the reflective electrode regions, the 20 first counter electrode, and portions of the liquid crystal layer located between the reflective electrode regions and the first counter electrode; and a first storage capacitor, which is electrically connected in parallel to the reflective portion liquid crystal capacitor. The transmissive portion preferably 25 includes: a transmissive portion liquid crystal capacitor, which is defined by the transmissive electrode regions, the second counter electrode, and portions of the liquid crystal layer located between the transmissive electrode regions and the second counter electrode; and a second storage capacitor, 30 which is electrically connected in parallel to the transmissive portion liquid crystal capacitor. The alternating current signal voltage that is applied to the first counter electrode is preferably also applied to a first storage capacitor counter electrode that the first storage capacitor includes. The alternating cur- 35 rent signal voltage that is applied to the second counter electrode is preferably also applied to a second storage capacitor counter electrode that the second storage capacitor includes.

A liquid crystal display device according to another preincludes pixel electrodes, scanning lines, signal lines, switching elements, a liquid crystal layer and at least one counter electrode. The pixel electrodes are preferably arranged in columns and rows. Each of the pixel electrodes preferably includes a reflective electrode region and a transmissive elec- 45 trode region. The scanning lines preferably extend in a row direction, while the signal lines preferably extend in a column direction. Each of the switching elements is preferably provided for an associated one of the pixel electrodes and is preferably connected to the associated pixel electrode, an 50 associated one of the scanning lines and an associated one of the signal lines. The at least one counter electrode preferably faces the pixel electrodes by way of the liquid crystal layer. The liquid crystal display device preferably sequentially supplies a scanning signal voltage to one of the scanning lines 55 after another to select one group of pixel electrodes, which are connected to the same one of the scanning lines, after another from the pixel electrodes, and then preferably supplies display signal voltages to the selected group of pixel electrodes by way of the signal lines, thereby displaying an image 60 thereon. The pixel electrodes are preferably arranged in such a manner that the polarity of a voltage to be applied to the liquid crystal layer is inverted for every predetermined number of pixel electrodes in each of the rows and in each of the columns. A shift width of geometric centers of mass of the 65 transmissive electrode regions of the pixel electrodes as measured in the row direction or in the column direction is pref-

erably half or less of the pitch of the pixel electrodes as measured in the row direction or in the column direction.

In one preferred embodiment of the present invention, the switching elements that are connected to one of the scanning lines preferably include: a first group of switching elements, which are connected to the pixel electrodes belonging to one of two rows that are adjacent to the scanning line; and a second group of switching elements, which are connected to the pixel electrodes belonging to the other adjacent row. The first and second groups of switching elements are preferably arranged along the scanning line such that every predetermined number of switching elements of the first group are followed by every predetermined number of switching elements of the second group. The polarity of the voltage to be applied to the liquid crystal layer is preferably inverted for every group of pixel electrodes that are connected to their associated predetermined number of signal lines.

In another preferred embodiment of the present invention, the switching elements that are connected to one of the signal lines preferably include: a first group of switching elements, which are connected to the pixel electrodes belonging to one of two columns that are adjacent to the signal line; and a second group of switching elements, which are connected to the pixel electrodes belonging to the other adjacent column. The first and second groups of switching elements are preferably arranged along the signal line such that every predetermined number of switching elements of the first group are followed by every predetermined number of switching elements of the second group. The polarity of the voltage to be applied to the liquid crystal layer is preferably inverted for every group of pixel electrodes that are connected to their associated predetermined number of scanning lines.

In still another preferred embodiment of the present invention, the transmissive electrode regions of the pixel electrodes preferably have mutually congruent planar shapes and are preferably arranged so as to overlap with each other substantially entirely when translated in the row direction or in the column direction.

In yet another preferred embodiment, the switching eleferred embodiment of the present invention preferably 40 ments that are connected to one of the scanning lines preferably include: a first group of switching elements, which are connected to the pixel electrodes belonging to one of the rows that is adjacent to, and located over, the scanning line; and a second group of switching elements, which are connected to the pixel electrodes belonging to one of the rows that is adjacent to, and located under, the scanning line. The first and second groups of switching elements are preferably arranged along the scanning line such that every predetermined number of switching elements of the first group are followed by every predetermined number of switching elements of the second group. A distance from each of the switching elements of the first group to a geometric center of mass of the transmissive electrode region of the pixel electrode that is connected to the switching element of the first group is preferably different from a distance from each of the switching elements of the second group to a geometric center of mass of the transmissive electrode region of the pixel electrode that is connected to the switching element of the second group.

In yet another preferred embodiment, each of the pixel electrodes may include only one transmissive electrode region that is surrounded with the reflective electrode region.

In yet another preferred embodiment, a storage capacitor may be formed below the reflective electrode region.

In yet another preferred embodiment, the pixel electrodes preferably define multiple pixels, respectively. Each of the pixels preferably includes a reflective portion that is defined by the reflective electrode region and a transmissive portion

that is defined by the transmissive electrode region. An electrode potential difference created between the electrodes of the reflective portion is preferably approximately equal to an electrode potential difference created between the electrodes of the transmissive portion.

In this particular preferred embodiment, the reflective electrode region preferably includes: a reflective conductive layer; and a transparent conductive layer, which is provided on one surface of the reflective conductive layer so as to face the liquid crystal layer.

Specifically, the transparent conductive layer is preferably amorphous.

More specifically, a difference in work function between the transparent conductive layer and the transmissive electrode region is preferably within 0.3 eV.

In a specific preferred embodiment of the present invention, the transmissive electrode region is preferably made of an ITO layer, the reflective conductive layer preferably includes an Al layer, and the transparent conductive layer is preferably made of an oxide layer mainly composed of 20 indium oxide and zinc oxide.

In a specific preferred embodiment, the transparent conductive layer preferably has a thickness of 1 nm to 20 nm.

In yet another preferred embodiment, the pixel electrodes preferably define multiple pixels, respectively. Each of the 25 pixels preferably includes a reflective portion that is defined by the reflective electrode region and a transmissive portion that is defined by the transmissive electrode region. To substantially compensate for a difference between an electrode potential difference created in the reflective portion and an 30 electrode potential difference created in the transmissive portion, alternating current signal voltages having mutually different center levels are preferably applied to respective portions of the liquid crystal layer that correspond to the reflective portion and the transmissive portion.

In this particular preferred embodiment, the at least one counter electrode preferably includes: a first counter electrode that faces the reflective electrode regions of the pixel electrodes; and a second counter electrode that faces the first and second counter electrodes are preferably electrically isolated from each other.

Specifically, each of the first and second counter electrodes is preferably formed in the shape of a comb that has a plurality of branches extending in the row direction.

More particularly, counter signal voltages to be applied to the first and second counter electrodes are preferably alternating current signal voltages that have the same polarity, the same period and the same amplitude but have mutually different center levels.

In yet another preferred embodiment, the reflective portion preferably includes: a reflective portion liquid crystal capacitor, which is defined by the reflective electrode regions, the first counter electrode, and portions of the liquid crystal layer located between the reflective electrode regions and the first 55 counter electrode; and a first storage capacitor, which is electrically connected in parallel to the reflective portion liquid crystal capacitor. The transmissive portion preferably includes: a transmissive portion liquid crystal capacitor, which is defined by the transmissive electrode regions, the 60 second counter electrode, and portions of the liquid crystal layer located between the transmissive electrode regions and the second counter electrode; and a second storage capacitor, which is electrically connected in parallel to the transmissive portion liquid crystal capacitor. The alternating current signal 65 voltage that is applied to the first counter electrode is also preferably applied to a first storage capacitor counter elec-

trode that the first storage capacitor includes. The alternating current signal voltage that is applied to the second counter electrode is also preferably applied to a second storage capacitor counter electrode that the second storage capacitor

A liquid crystal display device according to still another preferred embodiment of the present invention preferably includes pixel electrodes, a liquid crystal layer and at least one counter electrode. Each of the pixel electrodes preferably includes a reflective electrode region and a transmissive electrode region. The at least one counter electrode preferably faces the pixel electrodes by way of the liquid crystal layer. The pixel electrodes preferably define multiple pixels, respectively. Each of the pixels preferably includes a reflective portion that is defined by the reflective electrode region and a transmissive portion that is defined by the transmissive electrode region. An electrode potential difference created between the electrodes of the reflective portion is preferably approximately equal to an electrode potential difference created between the electrodes of the transmissive portion.

In one preferred embodiment of the present invention, the reflective electrode region preferably includes: a reflective conductive layer; and a transparent conductive layer, which is provided on one surface of the reflective conductive layer so as to face the liquid crystal layer.

In this particular preferred embodiment, the transparent conductive layer is preferably amorphous.

Specifically, a difference in work function between the transparent conductive layer and the transmissive electrode region is preferably within 0.3 eV.

In a specific preferred embodiment, the transmissive electrode region is preferably made of an ITO layer, the reflective conductive layer preferably includes an Al layer and the transparent conductive layer is preferably made of an oxide layer 35 mainly composed of indium oxide and zinc oxide.

In a specific preferred embodiment, the transparent conductive layer preferably has a thickness of 1 nm to 20 nm.

In another preferred embodiment, in order to substantially compensate for a difference between an electrode potential transmissive electrode regions of the pixel electrodes. The 40 difference created in the reflective portion and an electrode potential difference created in the transmissive portion, alternating current signal voltages having mutually different center levels are preferably applied to respective portions of the liquid crystal layer that correspond to the reflective portion and the transmissive portion.

> In this particular preferred embodiment, the at least one counter electrode preferably includes: a first counter electrode that faces the reflective electrode regions of the pixel electrodes; and a second counter electrode that faces the transmissive electrode regions of the pixel electrodes. The first and second counter electrodes are preferably electrically isolated from each other.

> Specifically, each of the first and second counter electrodes is preferably formed in the shape of a comb that has a plurality of branches extending in the row direction.

> More specifically, counter signal voltages to be applied to the first and second counter electrodes are preferably alternating current signal voltages that have the same polarity, the same period and the same amplitude but have mutually different center levels.

In yet another preferred embodiment, the reflective portion preferably includes: a reflective portion liquid crystal capacitor, which is defined by the reflective electrode regions, the first counter electrode, and portions of the liquid crystal layer located between the reflective electrode regions and the first counter electrode; and a first storage capacitor, which is electrically connected in parallel to the reflective portion liquid

crystal capacitor. The transmissive portion preferably includes: a transmissive portion liquid crystal capacitor, which is defined by the transmissive electrode regions, the second counter electrode, and portions of the liquid crystal layer located between the transmissive electrode regions and the second counter electrode; and a second storage capacitor, which is electrically connected in parallel to the transmissive portion liquid crystal capacitor. The alternating current signal voltage that is applied to the first counter electrode is preferably also applied to a first storage capacitor counter electrode that the first storage capacitor includes. The alternating current signal voltage that is applied to the second counter electrode is preferably also applied to a second storage capacitor counter electrode that the second storage capacitor includes.

Other features, elements, processes, steps, characteristics 15 and advantages of the present invention will become more apparent from the following detailed description of preferred embodiments of the present invention with reference to the attached drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

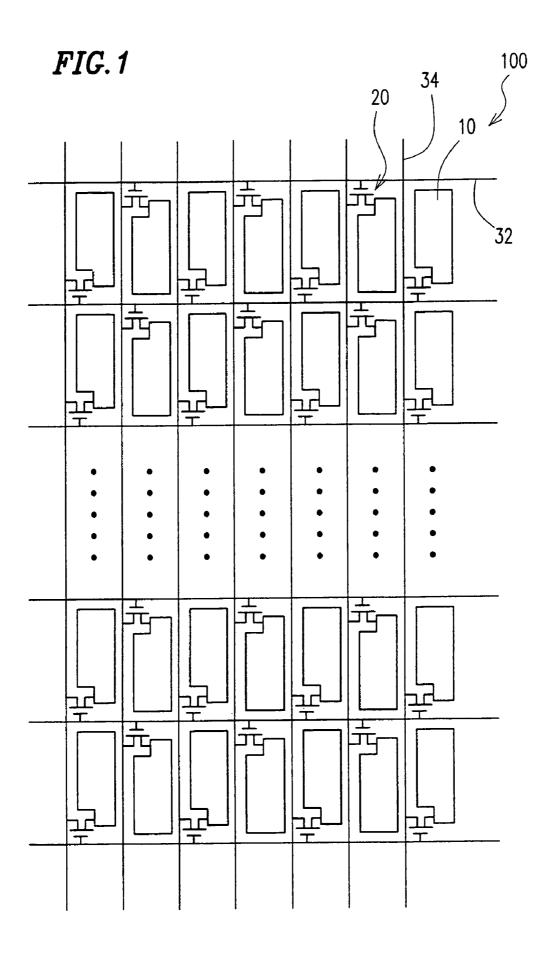

FIG. 1 is a plan view schematically illustrating a layout for a reflective liquid crystal display device 100 according to a first specific preferred embodiment of the present invention. 25

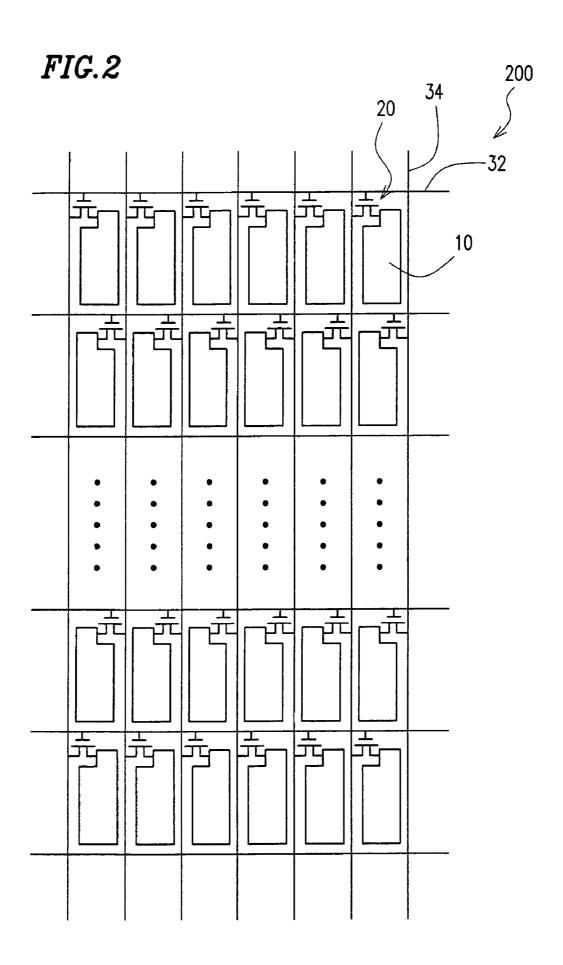

FIG. 2 is a plan view schematically illustrating a layout for another reflective liquid crystal display device 200 according to the first preferred embodiment.

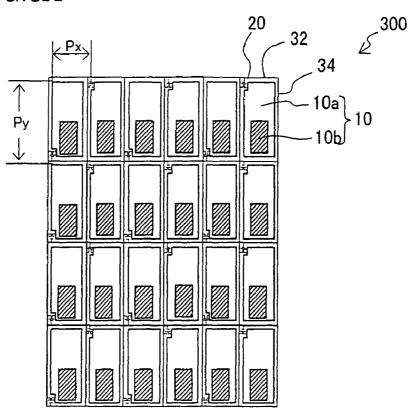

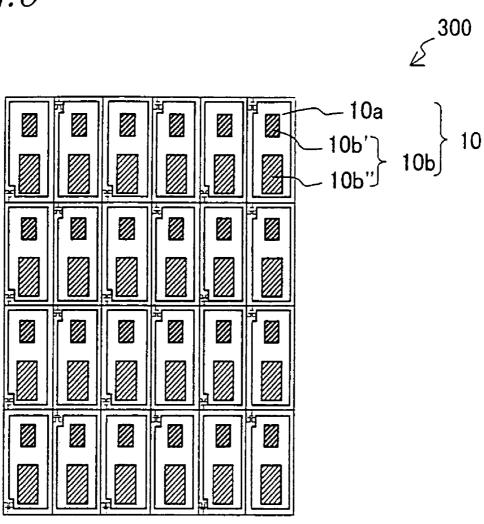

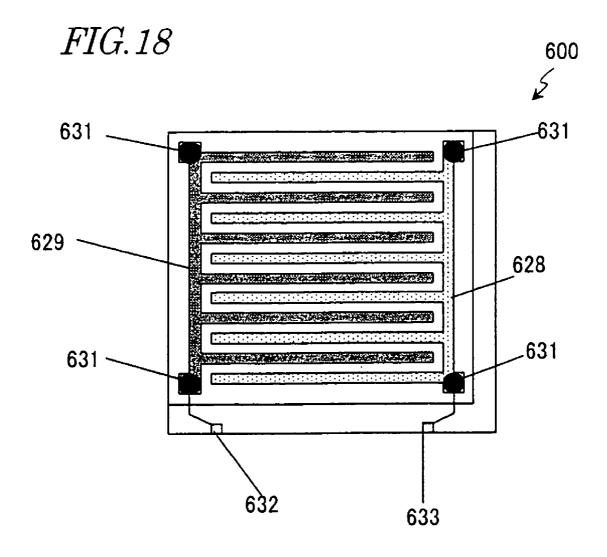

FIG. 3A is a plan view illustrating an exemplary arrangement of pixel electrodes in a dual-mode liquid crystal display <sup>30</sup> device according to the first preferred embodiment.

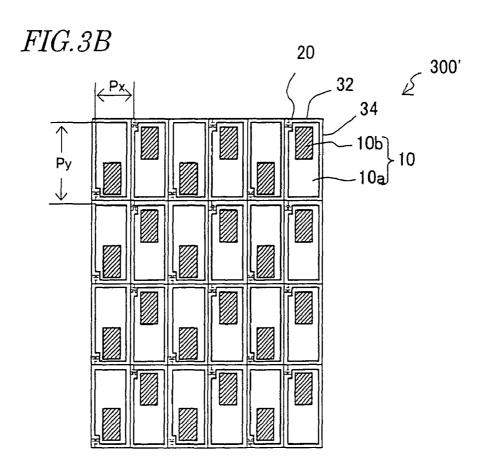

FIG. **3**B is a plan view illustrating an exemplary arrangement of pixel electrodes in a dual-mode liquid crystal display device according to a comparative example.

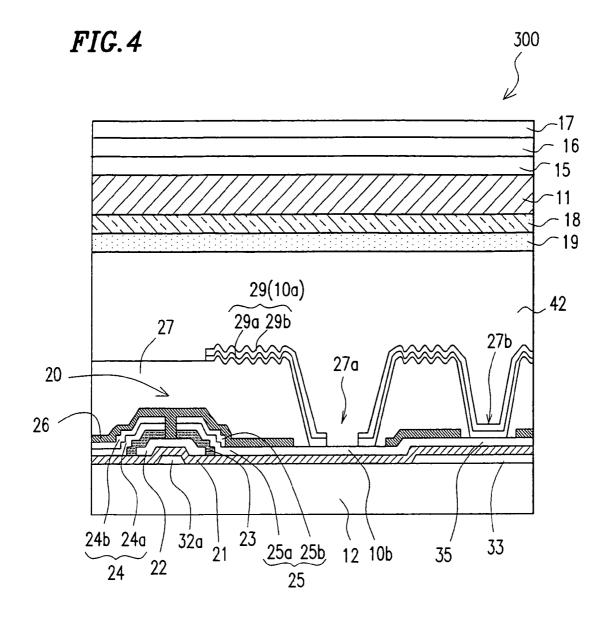

FIG. 4 is a cross-sectional view schematically illustrating a  $\,^{35}$  dual-mode liquid crystal display device 300 according to the first preferred embodiment.

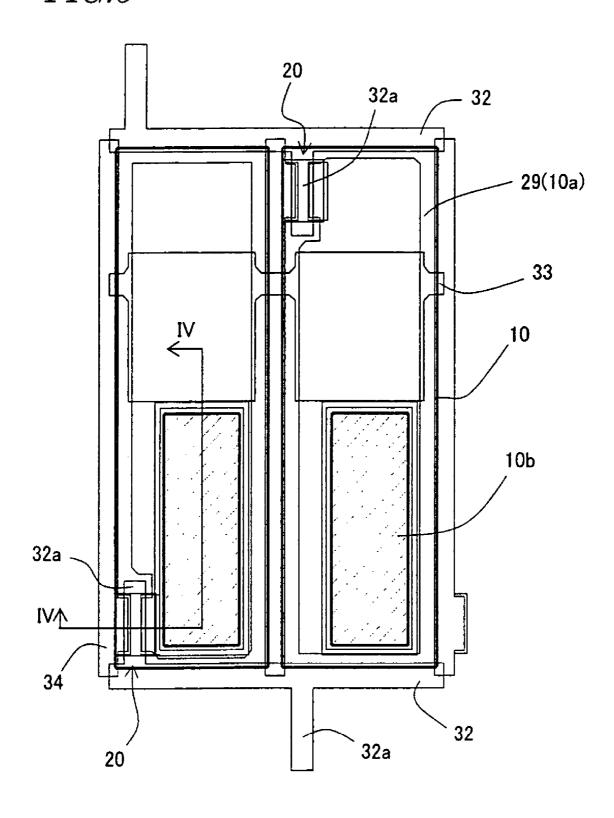

$\overline{\mathrm{FIG}}$ . 5 is a plan view schematically illustrating the dual-mode liquid crystal display device 300 of the first preferred embodiment.

FIG. 6 is a plan view illustrating another exemplary arrangement of pixel electrodes in the dual-mode liquid crystal display device of the first preferred embodiment.

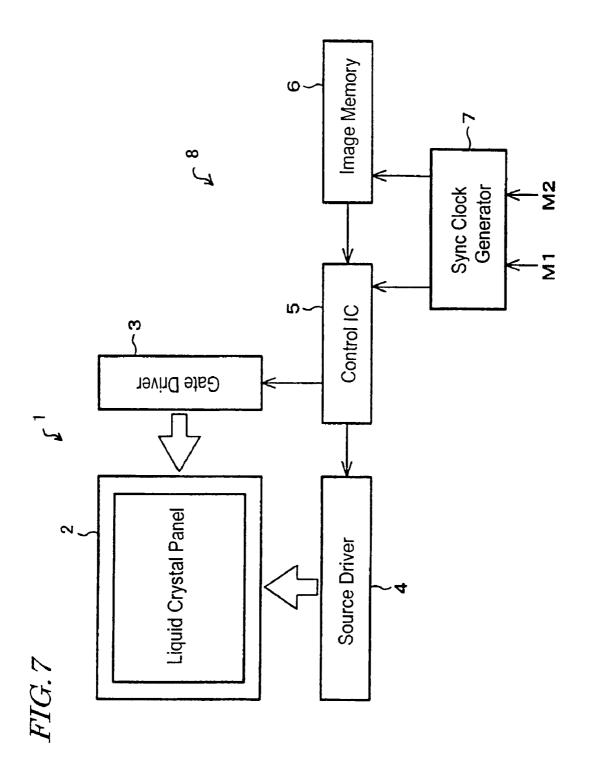

FIG. 7 is a block diagram showing a system configuration for a liquid crystal display device 1 according to the first preferred embodiment.

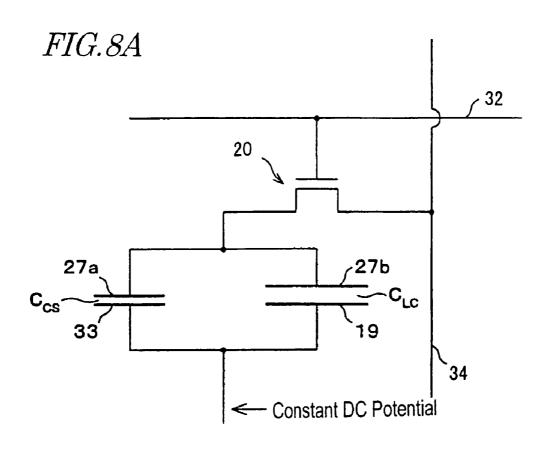

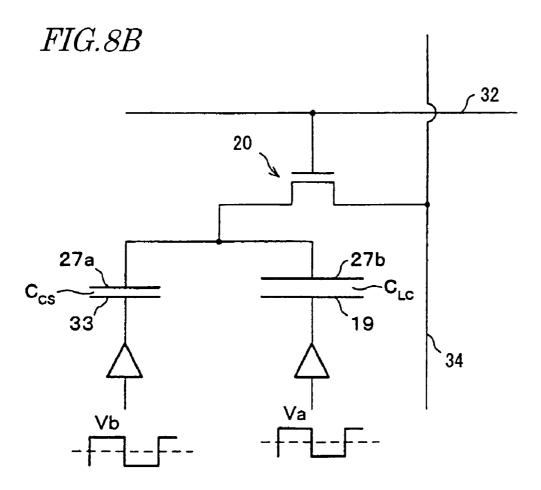

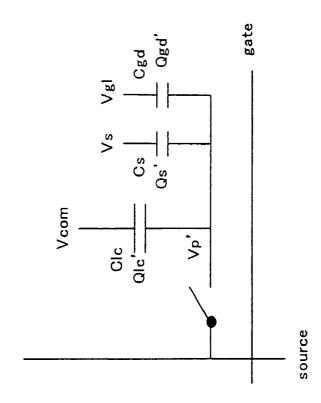

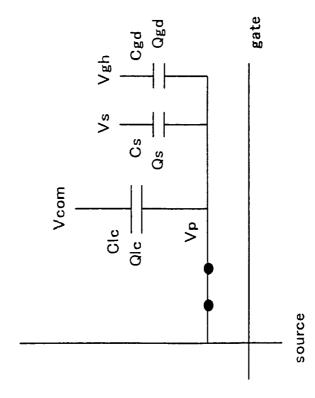

FIGS. 8A and 8B each show an equivalent circuit of one pixel of a liquid crystal panel that includes a storage capacitor  $C_{CS}$ .

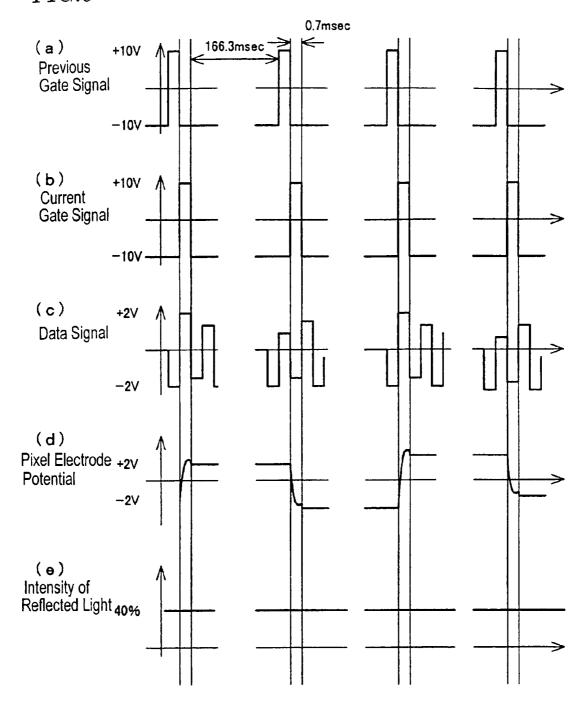

FIG. 9 shows patterns (a), (b), (c), (d) and (e), which show the waveform of a gate signal, the waveform of another gate signal, the waveform of a data signal, the potential level at a pixel electrode and the intensity of reflected light, respectively, in a situation where the liquid crystal display device of the first preferred embodiment is driven at a low frequency.

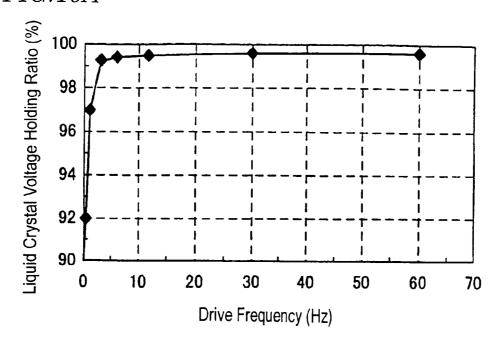

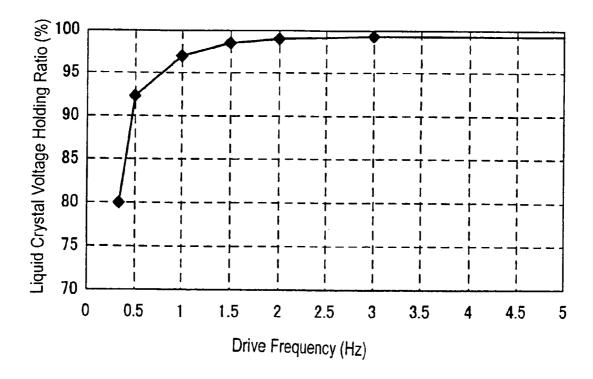

FIGS. 10A and 10B are graphs showing the dependence of the liquid crystal voltage holding ratio Hr on the drive frequency (or refresh rate).

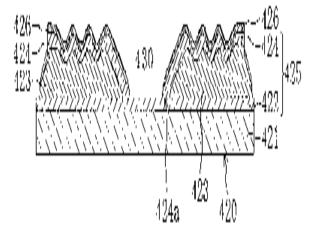

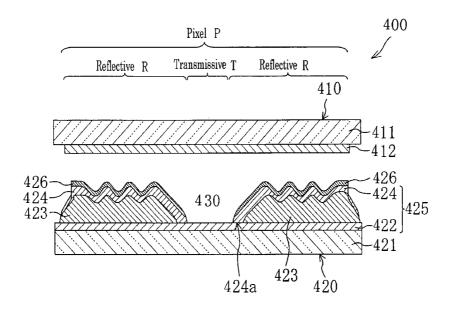

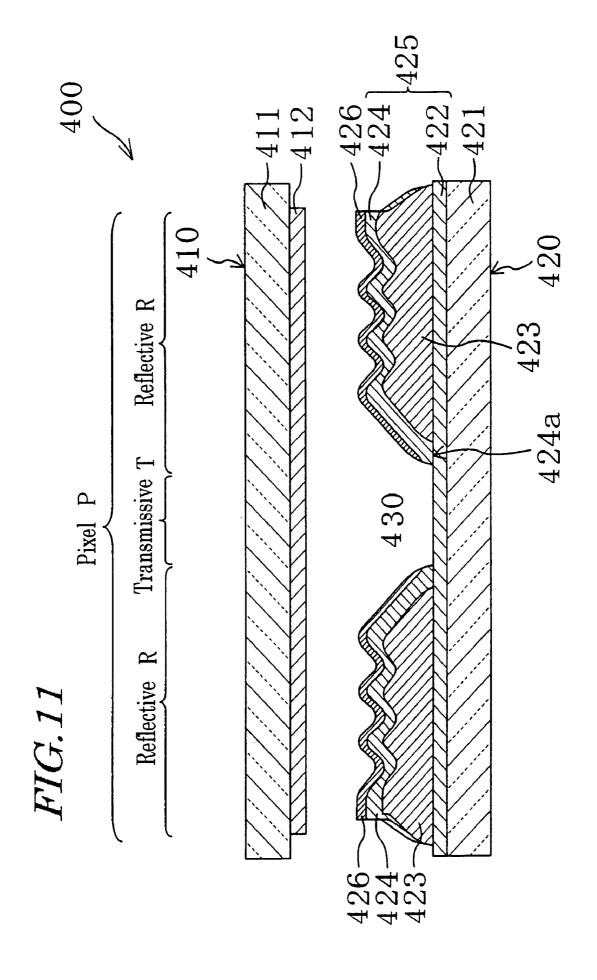

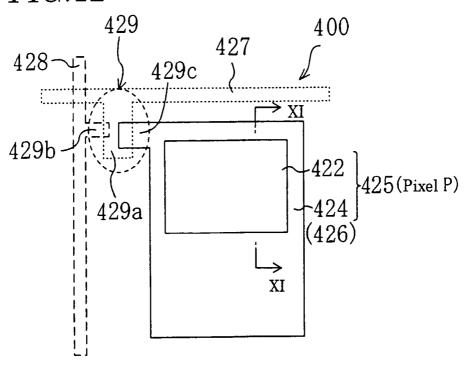

FIG. 11 is a cross-sectional view schematically illustrating  $_{60}$  the structure of a dual-mode liquid crystal display device 400 according to a second specific preferred embodiment of the present invention as viewed on a plane XI-XI shown in FIG.  $^{12}$

FIG. 12 is a plan view schematically illustrating the struc- 65 ture of one pixel of the dual-mode liquid crystal display device 400 according to the second preferred embodiment.

10

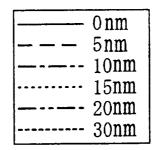

FIG. 13 is a graph showing the relationships between the wavelength of light and the reflectance for various thicknesses of an amorphous transparent conductive film.

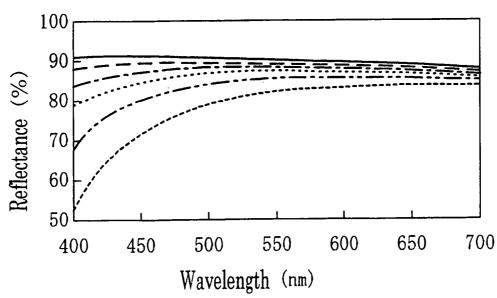

FIG. **14** is a cross-sectional view illustrating the structure of one pixel of a conventional dual-mode liquid crystal display device.

FIG. 15 shows an electrode potential difference created between the electrodes of a transmissive portion and an electrode potential difference created between the electrodes of a reflective portion.

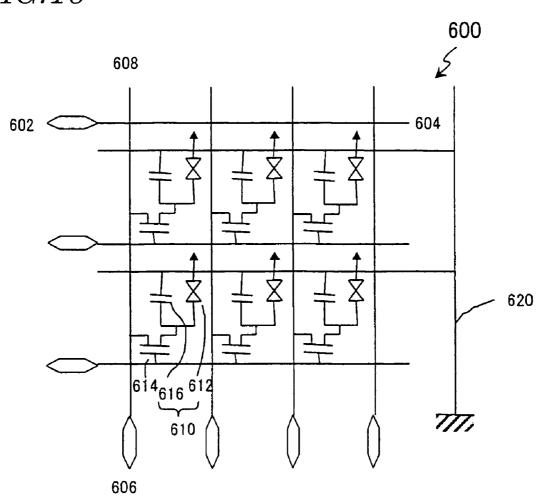

FIG. 16 schematically shows the arrangement of a liquid crystal display device 600 according to a third specific preferred embodiment of the present invention.

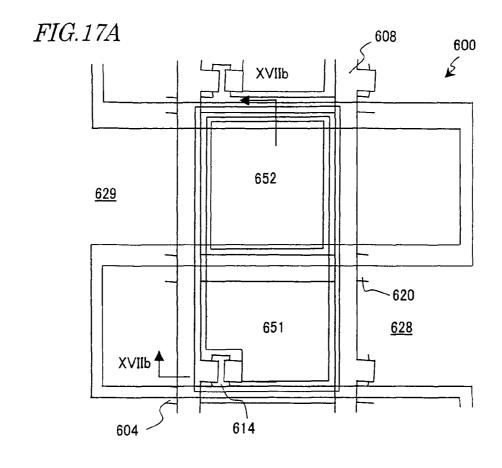

FIGS. 17A and 17B are respectively a plan view and a cross-sectional view, taken along the line XVIIb-XVIIb shown in FIG. 17A, schematically illustrating the structure of one pixel of the liquid crystal display device 600 according to the third preferred embodiment.

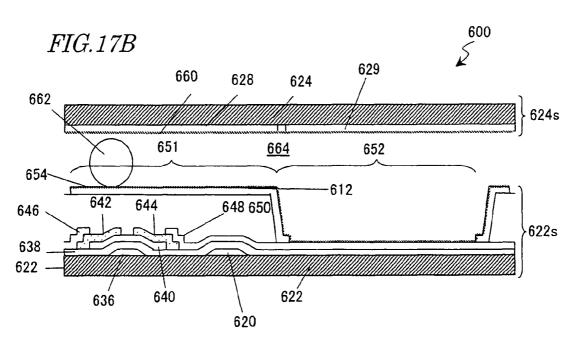

FIG. 18 is a plan view schematically illustrating the configuration of a counter electrode of the liquid crystal display device 600 according to the third preferred embodiment.

FIGS. 19A and 19B each show an equivalent circuit of one pixel of the liquid crystal display device 600 according to the third preferred embodiment in which the TFT is in ON state and in the OFF state, respectively.

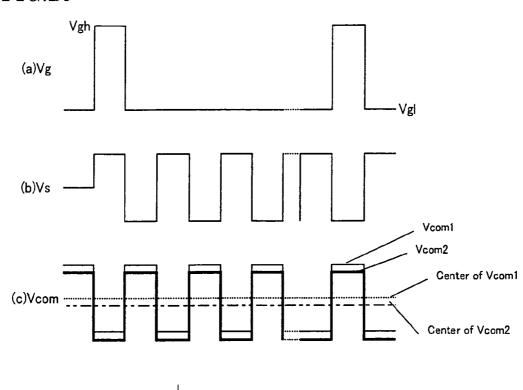

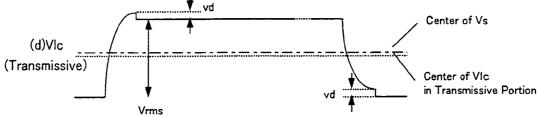

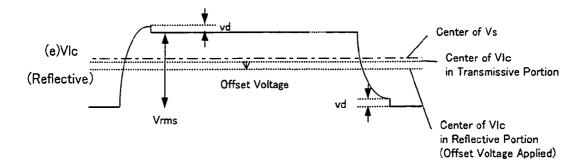

FIG. 20 shows the respective waveforms of signals (a) through (e) for use to drive the liquid crystal display device 600 according to the third preferred embodiment.

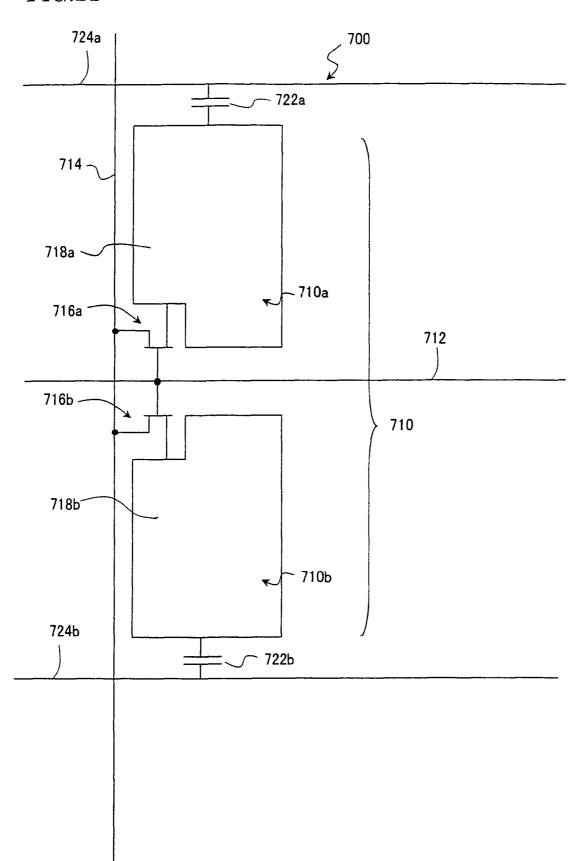

FIG. 21 schematically shows the structure of one pixel of another liquid crystal display device 700 according to the third preferred embodiment.

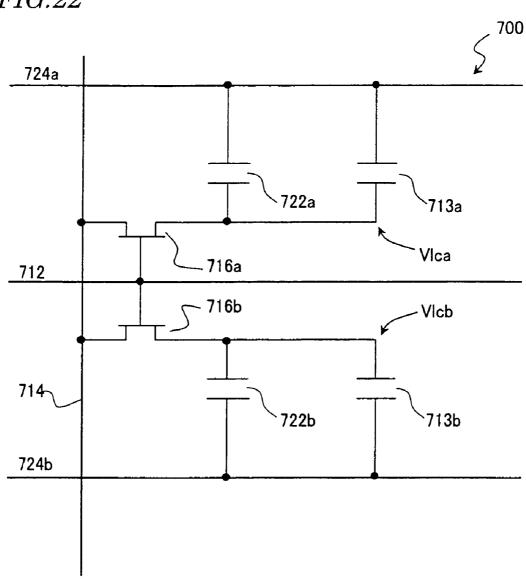

FIG. 22 schematically shows an equivalent circuit of one pixel of the liquid crystal display device 700 shown in FIG. 21.

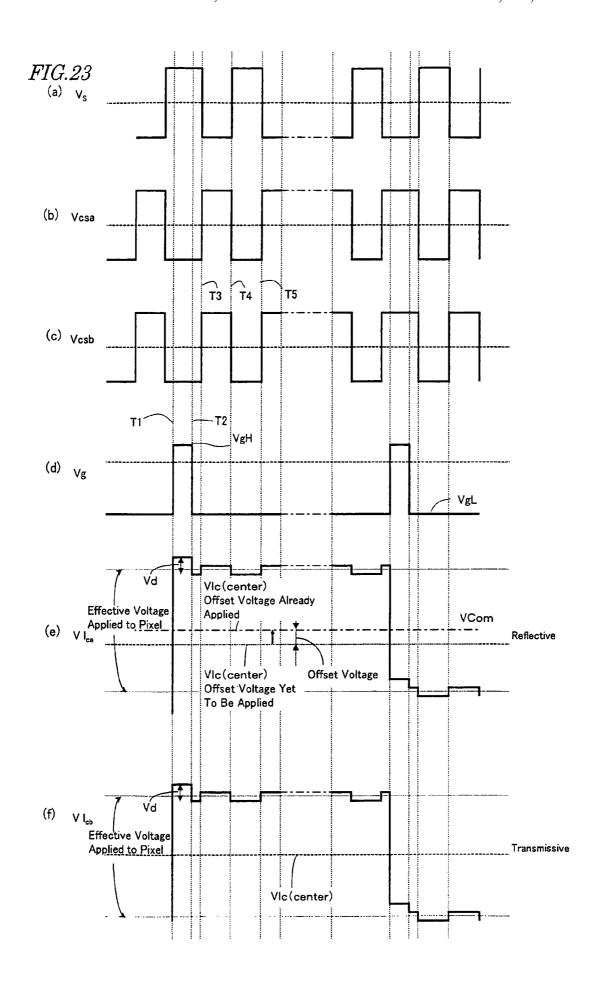

FIG. 23 schematically shows the waveforms and timings of respective voltages for use to drive the liquid crystal display device 700.

## DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

Hereinafter, preferred embodiments of a liquid crystal display device according to the present invention will be described with reference to the accompanying drawings. A liquid crystal display device according to a preferred embodiment of the present invention is a display device that can conduct a display operation by utilizing at least reflected light. That is to say, the present invention is applicable not only to a normal reflective liquid crystal display device but also to a so-called "semi-transmissive" or "reflective/transmissive (i.e., dual-mode)" liquid crystal display device, in which each pixel electrode thereof includes a reflective electrode region and a transmissive electrode region.

It should be noted that the pixel electrode does not herein always have a single electrode layer but may have a plurality of electrode layers, which are provided for each pixel and to which a display signal voltage is applied. That is to say, as in the dual-mode liquid crystal display device to be described later, the reflective electrode region may be made of a reflective electrode layer and the transmissive electrode region may be made of a transparent electrode layer. Alternatively, the reflective electrode region may be a combination of a transparent electrode and a reflective film. As another alternative, the pixel electrode may also be formed by providing a hole (i.e., a transmissive portion) for a single metal film, i.e., an electrode that is made of a semi-transmissive conductive film.

In this configuration, no electrode layer exists in the transmissive portion of the metal film. However, if the hole is sufficiently small, then an electric field that is applied from the metal film (i.e., electrode layer) surrounding the hole is intense enough. Then, the voltage to be applied to the liquid 5 crystal layer is hardly affected by the hole of the metal film. Accordingly, the pixel electrode made of such a metal film is also herein regarded as having a reflective electrode region and a transmissive electrode region (corresponding to the hole).

Unlike a reflective liquid crystal display device, a liquid crystal display device including the transmissive electrode regions and the reflective electrode regions can advantageously display an image of quality even in an environment in which the ambient light is relatively dark. In addition, if its backlight is selectively turned ON or OFF according to the operating environment, the device can also conduct a display operation in the transmission mode.

#### Embodiment 1

Hereinafter, the pixel arrangement of a liquid crystal display device, which produces a hardly perceivable flicker even when driven at as low a frequency as 45 Hz or less, for example, and a method of driving such a device will be <sup>25</sup> described.

First, the structure of a reflective liquid crystal display device 100 according to a first specific preferred embodiment of the present invention will be described with reference to FIG. 1. The reflective liquid crystal display device 100 includes a low frequency driver (not shown), a preferred embodiment of which will be described later.

As shown in FIG. 1, the reflective liquid crystal display device 100 includes reflective pixel electrodes 10 (which will be herein simply referred to as "reflective electrodes") that are arranged in columns and rows (i.e., in a matrix fashion), gate bus lines 32 extending in the row direction, source bus lines 34 extending in the column direction, and TFTs 20, each of which is provided for an associated one of the reflective electrodes 10. That is to say, each reflective electrode 10 is connected to one of the gate bus lines 32 and one of the source bus lines 34 by way of its associated TFT 20.

This liquid crystal display device 100 sequentially supplies a gate signal voltage to one of the gate bus lines 32 after another, thereby selecting one group of reflective electrodes 10, which are connected to the same gate bus line 32, after another. Then, the liquid crystal display device 100 supplies display signal voltages to the selected group of reflective electrodes 10 by way of the source bus lines 34, thereby displaying an image thereon. That is to say, this liquid crystal display device 100 is driven by a line sequential technique.

A period in which each of the gate bus lines is selected will be herein referred to as a "horizontal scanning period" and a period of time it takes to scan a predetermined number of gate 55 bus lines over the entire display screen will be herein referred to as a "vertical scanning period". Where all of the gate bus lines are scanned on a frame-by-frame basis (i.e., when the refresh rate is 60 Hz), one frame period corresponds to one vertical scanning period. On the other hand, where one frame 60 is divided into multiple fields so that the gate bus lines are scanned on a field-by-field basis, one field period that it takes to scan all of the gate bus lines belonging to one field corresponds to one vertical scanning period. In the liquid crystal display device according to this preferred embodiment of the 65 present invention, the display signal voltage to be supplied to each of the pixel electrodes is updated at a frequency of 45 Hz

12

or less. That is to say, the liquid crystal display device 100 is driven at a low frequency so that one vertical scanning period becomes  $\frac{1}{45}$  second or less.

Also, in each of the rows and in each of the columns, the pixel electrodes are arranged so that the polarity of the voltage to be applied to the liquid crystal layer is inverted for every predetermined number of pixel electrodes. That is to say, the liquid crystal display device is driven by a so-called "dot inversion technique". In the illustrative preferred embodiment to be described below, the liquid crystal display device is supposed to be driven by inverting the polarity for every pixel (i.e., the predetermined number of pixel electrodes is one). Alternatively, the polarity may also be inverted for every group of three consecutive pixels representing the three primary colors of red (R), green (G) and blue (B) (i.e., the predetermined number of pixel electrodes is three).

To drive the reflective liquid crystal display device 100 by

the dot inversion technique, the reflective electrodes 10 are

arranged in a hound's-tooth check pattern with respect to the

TFTs 20 as shown in FIG. 1. That is to say, the TFTs 20 that

are connected to each single gate bus line 32 include a first

group of TFTs 20 that are connected to the reflective electrodes 10 belonging to one of the two adjacent rows (e.g., the

upper row) and a second group of TFTs 20 that are connected

to the reflective electrodes 10 belonging to the other adjacent

row (e.g., the lower row). And the first and second groups of

TFTs 20 are arranged along the gate bus line 32 such that

every predetermined number of TFTs 20 of the first group are

followed by every predetermined number of TFTs 20 of the

second group.

In such an arrangement, if the polarity of the display signal voltages to be applied to all of the source bus lines 34 is inverted every time one gate bus line 32 is selected and if the polarity of the display signal voltages to be applied to the same reflective electrodes 10 in the next vertical scanning period is inverted, the liquid crystal display device 100 can be driven by the dot inversion technique. That is to say, by combining the hound's-tooth check arrangement of the TFTs 20 with the gate line inversion driving technique, the dot inversion drive is substantially realized. In this manner, the liquid crystal display device 100 of this preferred embodiment can be driven by the dot inversion technique by utilizing the conventional circuit configuration that is designed to realize gate line inversion drive.

For the sake of simplicity, it is herein supposed to be the "polarity of the display signal voltages to be applied to the source bus lines 34" that should be inverted. Strictly speaking, though, it is the "polarity of the voltage to be applied to the liquid crystal layer" to be driven by the "pixel electrodes 10 connected to the source bus lines 34" that is actually inverted. In other words, it is the "polarity of the potential at the pixel electrodes with respect to the potential at the counter electrode" that should be inverted. In the same way, the "display signal voltages to be applied to the pixel electrodes 10" will also be used as an equivalent to the "voltage to be applied to the liquid crystal layer".

The following Table 1 shows counter voltage shift values at which no flicker was perceivable to the human eyes for the liquid crystal display device 100 of the first preferred embodiment with the hound's-tooth check TFT arrangement and a liquid crystal display device with the conventional TFT arrangement that were displaying images in half tones:

TABLE 1

| Refresh<br>Rate<br>(Hz) | Vertical<br>Scanning<br>Period<br>(msec) | Counter voltage<br>Shift value<br>(±mV or less)<br>in conventional<br>arrangement | Counter voltage<br>Shift value<br>(±mV or less)<br>in hound's tooth<br>arrangement |

|-------------------------|------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 70.0                    | 14.3                                     | 256                                                                               | 527                                                                                |

| 17.5                    | 57.1                                     | 85                                                                                | 123                                                                                |

| 10.0                    | 100.0                                    | 66                                                                                | 111                                                                                |

| 6.4                     | 157.1                                    | 37                                                                                | 144                                                                                |

| 5.0                     | 200.0                                    | 28                                                                                | 146                                                                                |

| 3.7                     | 271.4                                    | 30                                                                                | 169                                                                                |

where the pixel pitches were  $60 \, \mu m \times RGB \times 180 \, \mu m$  in both of these devices.

As shown in Table 1, even when the liquid crystal display device with the conventional arrangement was driven at a refresh rate of 70 Hz, a counter voltage shift of about 250 mV produced a perceivable flicker. Also, when the refresh rate was decreased to about 5 Hz, even a counter voltage shift of as small as about 30 mV made the line-by-line difference in brightness quite perceivable. What is worse, the refresh period (i.e., the vertical scanning period) was as long as about 200 ms in that case. As a result, the observer could clearly see with his or her own eyes how bright and dark lines were alternated every vertical scanning period.

In contrast, when the image on the liquid crystal display device 100 with the hound's-tooth arrangement was refreshed at a rate of 5 Hz, for example, a counter voltage shift of greater than 150 mV resulted in a perceivable flicker. Even so, that flicker did not form a striped pattern because the polarities of voltages being applied to vertically or horizontally adjacent pixels were different from each other. For that 35 reason, the flicker was just felt like slight unevenness over the screen or periodic recurrence of barely perceivable difference in brightness. In this manner, when the refresh rate was decreased to as low as 5 Hz, the counter voltage shift value that might affect the display quality was approximately 150 mV, which does fall within an easily adjustable range even when the devices should be mass-produced. Thus, by adjusting the offset voltage, those defects can be substantially eliminated from the image displayed.

As described above, by combining the hound's-tooth 45 check TFT arrangement with the gate line inversion driving technique, even a liquid crystal display device being driven at a low frequency can also display an image of quality with its power dissipation reduced and without allowing the observer to perceive any flicker.

The liquid crystal display device 100 of the preferred embodiment described above is driven by the gate line inversion technique with the TFTs 20 arranged in a hound's-tooth check pattern along the gate bus lines 32. Alternatively, even when driven by a source line inversion technique with the 55 TFTs 20 arranged in a hound's-tooth check pattern along the source bus lines 34, the liquid crystal display device 200 can also be driven substantially by the dot inversion technique as shown in FIG. 2. Specifically, in the liquid crystal display device 200 shown in FIG. 2, the TFTs 20 that are connected to 60 one source bus line 34 include a first group of TFTs 20 that are connected to the reflective electrodes 10 belonging to one of the two adjacent columns (e.g., the left-hand-side column) and a second group of TFTs 20 that are connected to the reflective electrodes 10 belonging to the other adjacent column (e.g., the right-hand-side column). And the first and second groups of TFTs 20 are arranged along the source bus

14

line 34 such that every predetermined number of TFTs 20 of the first group are followed by every predetermined number of TFTs 20 of the second group.

In such an arrangement, if the polarity of the display signal voltage to be applied to one source bus line 34 is opposite to that of the display signal voltage to be applied to its adjacent source bus lines 34 in every vertical scanning period and if the polarities of the display signal voltages to be applied to the respective source bus lines 34 are inverted in the next vertical scanning period, the liquid crystal display device 200 can also be driven by the dot inversion technique. That is to say, by combining the hound's-tooth check arrangement of the TFTs 20 with the source line inversion driving technique, the dot inversion drive is substantially realized. In this manner, the liquid crystal display device 200 of this preferred embodiment can be driven by the dot inversion technique by utilizing the conventional circuit configuration that is designed to realize source line inversion driving.

It should be noted, however, that in the source line inversion driving technique, the counter electrode is driven with a direct current. Accordingly, the amplitude of the drive voltage to be applied to the liquid crystal layer should be defined by the amplitudes of the display signal voltages that are supplied from the source bus lines 34. Thus, compared to the gate line inversion driving technique in which the difference between the voltage applied to the counter electrode and the display signal voltages applied to the source bus lines 34 defines the amplitude of the drive voltage to be applied to the liquid crystal layer, the amplitude of the display signal voltages should be increased. That is to say, a driver circuit for the source driver should have a higher breakdown voltage, and the source line inversion driving technique dissipates greater power than the gate line inversion driving technique. For that reason, the gate line inversion driving technique is preferred to the source line inversion driving technique.

As described above, by combining the hound's-tooth check TFT arrangement with the gate or source line inversion driving technique, even a liquid crystal display device being driven at a low frequency can also display an image of quality without allowing the observer to perceive any flicker.

However, if the hound's-tooth check arrangement is formed with the positional relationship between each reflective electrode (or pixel electrode) 10 and its associated TFT 20 maintained as shown in FIG. 1 or 2, then two adjacent reflective electrodes 10 will face mutually different directions. For example, in the illustrative arrangement shown in FIG. 1, one of two horizontally adjacent reflective electrodes 10 is disposed by rotating the other to 180 degrees. On the other hand, in the illustrative arrangement shown in FIG. 2, one of two vertically adjacent reflective electrodes 10 is disposed by mirror-reflecting the other about the source bus line 34 as a reflection axis. Accordingly, unless the reflective electrodes 10 are arranged symmetrically via the 180 degree rotation or mirror reflection as shown in FIG. 1 or 2, the arrangement of the reflective electrodes 10 will be an irregular one as the TFTs 20 are arranged in the hound's-tooth check pattern. In that case, the irregular arrangement of the reflective electrodes 10 (or pixels) might be perceived as a zigzag line. Such a zigzag line is particularly noticeable when the refresh rate is 45 Hz or less.

To avoid such an unwanted situation, the reflective electrodes 10 having mutually congruent planar shapes should be arranged substantially straight both in the column and row directions. That is to say, all of the reflective electrodes 10 preferably have mutually congruent planar shapes and are preferably arranged so as to overlap with each other substantially entirely when translated either in the column direction

or in the row direction. Also, even if the reflective electrodes 10 themselves are not arranged in a completely straight line, at least the geometric centers of mass of the reflective electrodes 10 should be arranged substantially in a straight line both in the column and row directions. Then, the zigzag line 5 will be hardly perceivable.

In the liquid crystal display devices 100 and 200 shown in FIGS. 1 and 2, each of the reflective electrodes 10 has a partially notched rectangular planar shape so as not to cover its associated TFT 20. Alternatively, each reflective electrode 10 may also be a rectangular electrode that does cover its TFT 20. In that case, even if the liquid crystal display device 100 or 200 is driven at a low frequency of 45 Hz or less, the zigzag line will be invisible.

In the preferred embodiments described above, the present invention is applied to a reflective liquid crystal display device. However, the present invention is equally applicable to a semi-transmissive liquid crystal display device including semi-transmissive pixel electrodes 10, which are made of a semi-transmissive conductive film (e.g., an Al film having a number of pinholes), and similar effects are also achievable in that case.

#### Dual-Mode Liquid Crystal Display Device

Hereinafter, a preferred arrangement of pixel electrodes 10 to be combined with the hound's-tooth check TFT arrangement will be described for a reflective/transmissive liquid crystal display device (which will be herein referred to as a "dual-mode liquid crystal display device"). In the dual-mode 30 liquid crystal display device to be described below, each pixel electrode includes a reflective electrode region and a transmissive electrode region. Also, each pixel includes: a reflective portion in which a display operation is conducted in a reflection mode by utilizing the light that has been reflected 35 from the reflective electrode region; and a transmissive portion in which a display operation is conducted in a transmission mode by utilizing the light that has been transmitted through the transmissive electrode region. In a semi-transmissive liquid crystal display device of which the pixel elec- 40 trodes are made of a metal film with pinholes, the light that has been transmitted through the pinholes and the light that has been reflected from the metal film are not perceived separately. In contrast, in the dual-mode liquid crystal display device, the light that has been transmitted through the trans- 45 missive portion and the light that has been reflected from the reflective portion are perceivable separately.

FIG. 3A illustrates a dual-mode liquid crystal display device 300 according to a preferred embodiment of the present invention. In the liquid crystal display device 300, the 50 TFTs 20 are arranged in the hound's-tooth check pattern with respect to the gate bus lines 32. Thus, just like the liquid crystal display device 100 shown in FIG. 1, dot inversion driving is substantially realized for the liquid crystal display device 300 by the gate line inversion driving technique. In the 55 dual-mode liquid crystal display device 300, each pixel electrode 10 includes a reflective electrode region 10a and a transmissive electrode region 10b. The transmissive electrode regions 10b have mutually congruent planar shapes and are arranged so as to overlap with each other substantially 60 entirely when translated in the row direction (at a pitch Px) or in the column direction (at a pitch Py). That is to say, the transmissive electrode regions 10b are arranged in a straight line both in the column and row directions.

FIG. 3B illustrates a liquid crystal display device 300' that 65 is laid out by a conventional or normal design process so as to have a hound's-tooth check TFT arrangement. As shown in

16

FIG. 3B, the positional relationship between each TFT 20 and its associated pixel electrode 10 is maintained. However, in the liquid crystal display device 300', the transmissive electrode regions 10b are arranged irregularly in the row direction, and a shift between the centers of mass of two horizontally adjacent transmissive electrode regions 10b is approximately Py/2, which is greater than the pitch Px in the row direction. Thus, while a display operation is conducted in the transmission mode, the irregular arrangement of the transmissive electrode regions 10b is perceived as a zigzag line. Also, in the example illustrated in FIG. 3B, each pixel electrode 10 includes only one transmissive electrode region 10b that is surrounded with the reflective electrode region 10a. Accordingly, the irregular shift of the geometric centers of mass of the transmissive electrode regions 10b causes an irregular shift of the geometric centers of mass of the reflective electrode regions 10a. For that reason, even while a display operation is conducted in the reflection mode, a zigzag line is also perceivable.

In contrast, in the liquid crystal display device 300 shown in FIG. 3A, the transmissive electrode regions 10b are arranged in a straight line in the row direction. Thus, even while a display operation is conducted in the transmission mode, no zigzag line is perceived. It should be noted that the transmissive electrode regions 10b do not have to be arranged in a straight line as shown in FIG. 3A. This is because as long as the shift width of the centers of mass of the transmissive electrode regions 10b as measured in the column direction is half or less of the pitch thereof in the row direction, the zigzag line is still hardly perceivable. Naturally, though, the transmissive electrode regions 10b are preferably arranged so that the geometric centers of mass thereof are aligned, and more preferably, the transmissive electrode regions 10b having mutually congruent planar shapes are arranged in a straight line as described above.

In a dual-mode liquid crystal display device (particularly in a liquid crystal display device in which only one transmissive electrode region  $\mathbf{10}b$  is surrounded with the reflective electrode region  $\mathbf{10}a$  in each pixel electrode  $\mathbf{10}$ ), the arrangement of the transmissive electrode regions  $\mathbf{10}b$  easily affects the quality of the image displayed. Thus, it is particularly preferable that the transmissive electrode regions  $\mathbf{10}b$  satisfy the relationship described above. Naturally, the reflective electrode regions  $\mathbf{10}a$  also preferably satisfy the relationship described above.

The phenomenon that the irregular arrangement of the transmissive electrode regions 10b and/or the reflective electrode regions 10a is perceived as a zigzag line is particularly noticeable when the liquid crystal display device is driven at as low a frequency as 45 Hz or less. However, even if the liquid crystal display device is driven at a frequency of 60 Hz or more, the quality of the image displayed is also degraded by the zigzag line. Accordingly, the effects described above are achievable not just for a liquid crystal display device that is driven at a low frequency but also for a dual-mode liquid crystal display device with a hound's-tooth check TFT arrangement as well. Also, as in the liquid crystal display device 100 described above, even if the liquid crystal display device 300 is driven at a low frequency, the device 300 still can display an image of quality almost without allowing the observer to perceive any flicker.

Next, the structure of the dual-mode liquid crystal display device 300 will be described in further detail with reference to FIGS. 4 and 5. FIG. 4 is a cross-sectional view schematically illustrating the dual-mode liquid crystal display device 300. FIG. 5 is a plan view thereof. The cross section illustrated in FIG. 4 is taken along the line IV-IV shown in FIG. 5.

As shown in FIG. 4, the liquid crystal display device 300 includes two insulating substrates (e.g., glass substrates) 11 and 12 and a liquid crystal layer 42 sandwiched between the substrates 11 and 12.

On one surface of the insulating substrate 11 that is 5 opposed to the liquid crystal layer 42, a color filter layer 18 and a counter electrode (or common electrode) 19 are stacked in this order. On the upper surface of the insulating substrate 11, a phase plate 15, a polarizer 16 and an antireflective film 17 are formed in this order to control the incoming light. The 10 antireflective film 17 may be omitted. Furthermore, on the innermost surface of the insulating substrate 11 that is closest to the liquid crystal layer 42, an alignment film (not shown) is provided. Although not shown specifically in FIG. 4, another phase plate, another polarizer and a backlight are provided on 15 the outer surface of the insulating substrate 12.

On the surface of the insulating substrate 12 that is opposed to the liquid crystal layer 42, TFTs 20, gate bus lines 32, source bus lines 34 and pixel electrodes 10 are formed as shown in FIG. 5. Each of the pixel electrodes 10 is connected 20 to one of the gate bus lines 32 and one of the source bus lines 34 by way of one of the TFTs 20. The pixel electrode 10 includes a reflective electrode region 10a and a transmissive electrode region 10b.

As shown in FIG. 4, each of the TFTs 20 includes: a gate 25 electrode 32a, which is formed as a portion of the gate bus line 32; a gate insulating film 21, which is formed so as to cover the gate electrode 32a; a semiconductor layer (e.g., an amorphous silicon layer) 22, which is formed on the gate insulating film 21; and source/drain electrodes 24 and 25, which are 30 formed over these members. A contact layer 23 is formed between the semiconductor layer 22 and the source/drain electrodes 24 and 25. The source electrode 24 has a two-layer structure consisting of an ITO layer 24a and a Ta layer 24b, which form integral parts of the source bus line 34. In the 35 same way, the drain electrode 25 also has a two-layer structure consisting of an ITO layer 25a and a Ta layer 25b. An extended portion of the ITO layer 25a defines the transmissive electrode region 10b and a storage capacitor electrode 35.

Another insulating film (e.g., an SiN film) 26 and an inter- 40 level dielectric film (e.g., photosensitive resin film) 27 are formed so as to cover the TFT 20. A finely embossed pattern is formed on a portion of the surface of the interlevel dielectric film 27. A reflective electrode 29 (corresponding to the reflective electrode region 10a) on the interlevel dielectric film 27 has a surface shape that reflects the unevenness on the surface of the interlevel dielectric film 27 and diffuses and reflects the incoming light adequately. This reflective electrode 29 has a two-layer structure in which an Al film 29b is deposited on a Mo film **29***a*. The reflective electrode **29** is electrically in 50 contact with the ITO layer 25a at an opening 27a and a contact hole 27b, which are formed through the insulating film 26 and the interlevel dielectric film 27. A portion of the ITO layer 25a inside the opening 27a, in which no reflective electrode 29 exists, functions as the transmissive electrode region 10b.

As shown in FIG. 5, the TFTs 20 connected to an arbitrary one of the gate bus lines 32 include: a first group of TFTs 20 connected to the pixel electrodes 10 belonging to a row that is adjacent to, and located over, the gate bus line 32; and a second group of TFTs 20 connected to the pixel electrodes 10 60 belonging to a row that is adjacent to, and located under, the gate bus line 32. The first and second groups of TFTs 20 are alternately arranged along the gate bus line 32. Accordingly, the TFTs 20 and the pixel electrodes 10 are arranged such that a distance from a TFT 20 to the geometric center of mass of 65 the transmissive electrode region 10b of its associated pixel electrode 10 is alternated with a different distance from an

18

adjacent TFT **20** to the geometric center of mass of the transmissive electrode region **10***b* of its associated pixel electrode **10**. In such a layout, the transmissive electrode regions **10***b* can be regularly arranged in the row direction so as to satisfy the conditions described above.

A display operation is conducted in the reflection mode in a portion of the liquid crystal layer 42 that is located between the reflective electrode 29 (i.e., the reflective electrode region 10a) and the counter electrode 19. On the other hand, a display operation is conducted in the transmission mode in another portion of the liquid crystal layer 42 that is located between the transmissive electrode region 10b and the counter electrode 19. That portion of the liquid crystal layer 42 corresponding to the transmissive portion (or transmissive region), in which the display operation is conducted in the transmission mode, is thicker than that portion of the liquid crystal layer 42 corresponding to the reflective portion (or reflective region), in which the display operation is conducted in the reflection mode. The difference in thickness between these two portions of the liquid crystal layer 42 is approximately equal to the thickness of the interlevel dielectric film 27. By utilizing such a structure, the display operation can be optimized both in the transmission and reflection modes. The portion of the liquid crystal layer 42 corresponding to the transmissive portion is preferably twice thicker than the portion of the liquid crystal layer 42 corresponding to the reflective portion.

The liquid crystal display device 30 includes: a liquid crystal capacitor  $C_{LC}$  that is formed by the pixel electrodes 10, the counter electrode 19 and portions of the liquid crystal layer 42 located between these electrodes 10 and 19; and a storage capacitor  $C_{CS}$ , which is electrically connected in parallel to the liquid crystal capacitor  $C_{LC}$ . The storage capacitor  $C_{CS}$  is formed by a storage capacitor line 33 (which is formed in the same process step with the gate bus line 32), the gate insulating film 21 and a portion of the ITO layer 25a (i.e., storage capacitor electrode 35). As shown in FIG. 4, that portion of the ITO layer 25a faces the storage capacitor line 33 with the gate insulating film 21 interposed between them. To prevent the pixel aperture ratio from decreasing substantially, the storage capacitor  $C_{CS}$  is preferably formed below the reflective electrode 29.

In addition, by forming the storage capacitor, the counter voltage shift can be reduced and the flicker can be further decreased. To minimize the flicker by forming a storage capacitor with a great capacitance value, the storage capacitor  $C_{CS}$  preferably has a relatively great capacitance value. In this preferred embodiment, to realize a voltage holding ratio (or retentivity) of 99% in a situation where the area of the reflective electrode region 10a accounts for 60% of each pixel electrode 10 and a refresh rate is 5 Hz, the storage capacitor  $C_{CS}$  has a capacitance value of 0.96 pF. The ratio of this storage capacitance value  $C_{CS}$  to the liquid crystal capacitance value  $C_{LC}$  of 0.48 pF is 2.00. For the same reasons, the storage capacitor  $C_{CS}$  is also preferably provided for the liquid crystal display device 100 or 200 described above.

In the dual-mode liquid crystal display device 300 according to the preferred embodiment described above, the TFTs 20 are arranged in the hound's-tooth check pattern with respect to the gate bus lines 32. Alternatively, as in the liquid crystal display device 200 described above, the TFTs 20 may also be arranged in the hound's-tooth check pattern with respect to the source bus lines 34. Also, in a dual-mode liquid crystal display device in general, the pixel electrodes do not have to be arranged as in the preferred embodiment described above. For example, as shown in FIG. 6, the transmissive electrode region 10b of each pixel electrode 10 may be

divided into two transmissive electrode regions 10b' and 10b''. As another alternative, the transmissive electrode region 10b may also be divided into three or more. In any of those alternative preferred embodiments, however, the transmissive electrode regions 10b', 10b'' and so on preferably satisfy the conditions described above as a whole. More preferably, the transmissive electrode regions 10b', 10b'' and so on are arranged so that each of the transmissive electrode regions 10b', 10b'' and so on satisfies the conditions described above.

Furthermore, in the dual-mode liquid crystal display device 300, the structures and materials of the respective members thereof are not limited to those exemplified above, but any known structure or material may be used instead. Furthermore, the switching element does not have to be the 15 TFT 20 but may also be an FET or any other three-terminal element. Also, the dual-mode liquid crystal display device 300 may be fabricated by a known process (see Japanese Laid-Open Publication No. 2000-305110, for example).

#### Low-Frequency Driver

Hereinafter, a circuit to be preferably used to drive the liquid crystal display device at a low frequency will be described.

FIG. 7 is a block diagram illustrating an exemplary liquid crystal display device 1 according to the first preferred embodiment of the present invention. The liquid crystal display device 1 is a representative of the liquid crystal display devices 100, 200 and 300 described above.

As shown in FIG. 7, the liquid crystal display device 1 includes a liquid crystal panel 2 and a low-frequency driver 8. The liquid crystal panel 2 may have the configuration of the liquid crystal display device 100, 200 or 300 described above. The low-frequency driver 8 includes a gate driver 3, a source 3 driver 4, a control IC 5, an image memory 6 and a sync clock generator 7.

The gate driver 3 is provided as a gate signal driver to output gate signals, having respective voltage levels representing selected and non-selected periods, to the gate bus 40 lines 32 of the liquid crystal panel 2. The source driver 4 is provided as a data signal driver to supply image data to the respective pixel electrodes on the selected gate bus line 32 by way of the respective source bus lines 34 of the liquid crystal panel 2. The source driver 4 outputs the image data as display 45 (or data) signals by an alternating current driving technique. The control IC 5 receives the image data, which is stored in the image memory 6 that is built in a computer, for example, and outputs a gate start pulse signal GSP and a gate clock signal GCK to the gate driver 3 and RGB gray-scale data, a 50 source start pulse signal SP and a source clock signal SCK to the source driver 4, respectively.

The sync clock generator 7 is provided as a means for setting the frequency. Specifically, the clock generator 7 generates and outputs sync clock pulses to the control IC 5 and 55 the image memory 6 to make the control IC 5 read the image data from the image memory 6 and output the gate start pulse signal GSP, gate clock signal GCK, source start pulse signal SP and source clock signal SCK in response to the clock pulses. In this preferred embodiment, the sync clock generator 7 sets the frequency of the sync clock pulses so that the frequencies of the respective signals are equalized with the refresh frequency of the image on the liquid crystal panel 2. The frequency of the gate start pulse signal GSP is equal to the refresh frequency. The sync clock generator 7 can set at least 65 one refresh rate equal to 30 Hz or less and can also define multiple refresh rates including 30 Hz.

20