### US008203520B2

## (12) United States Patent

### Shimoshikiryoh

### (54) LIQUID CRYSTAL DISPLAY

(75) Inventor: **Fumikazu Shimoshikiryoh**, Matsusaka

(JP)

(73) Assignee: Sharp Kabushiki Kaisha, Osaka-shi

(JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 986 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 12/216,974

(22) Filed: Jul. 14, 2008

(65) Prior Publication Data

US 2009/0046048 A1 Feb. 19, 2009

### Related U.S. Application Data

(63) Continuation of application No. 11/002,424, filed on Dec. 3, 2004, now Pat. No. 7,429,981.

### (30) Foreign Application Priority Data

| Dec. 5, 2003  | (JP) | <br>2003-408046 |

|---------------|------|-----------------|

| Aug. 30, 2004 | (JP) | <br>2004-250982 |

(51) Int. Cl. *G09G 3/36*

(2006.01)

(56) References Cited

### U.S. PATENT DOCUMENTS

4,345,249 A 8/1982 Togashi

(10) Patent No.: US 8,203,520 B2 (45) Date of Patent: \*Jun. 19, 2012

| 5,576,863    | A    | 11/1996 | Aoki et al.    |             |

|--------------|------|---------|----------------|-------------|

| 5,923,310    | A    | 7/1999  | Kim            |             |

| 7,429,981    | B2 * | 9/2008  | Shimoshikiryoh | <br>345/204 |

| 2001/0006410 | A1   | 7/2001  | Yamada et al.  |             |

| 2001/0024257 | A1   | 9/2001  | Kubo et al.    |             |

| 2002/0047822 | A1   | 4/2002  | Senda et al.   |             |

| 2002/0097362 | A1   | 7/2002  | Yamada et al.  |             |

| 2002/0118153 | A1   | 8/2002  | Kimura         |             |

| 2002/0149552 | A1   | 10/2002 | Fish et al.    |             |

| 2002/0154076 | A1   | 10/2002 | Greene et al.  |             |

| 2002/0167477 | Al   | 11/2002 | Tsutsui et al. |             |

|              |      | (Con    | tinued)        |             |

### FOREIGN PATENT DOCUMENTS

| EP | 1113312  | 7/2001   |

|----|----------|----------|

| JP | 6-14154  | 2/1994   |

| JP | 63-21907 | 11/1994  |

|    | (Co.     | ntinued) |

### OTHER PUBLICATIONS

European Search Report for corresponding European Patent Application dated Sep. 12, 2007.

Primary Examiner — Kimnhung Nguyen (74) Attorney, Agent, or Firm — Harness, Dickey & Pierce, P.L.C.

### (57) ABSTRACT

A liquid crystal display includes a plurality of pixels each of which has a liquid crystal layer and a plurality of electrodes for applying a voltage to the liquid crystal layer and which are arranged in a matrix of rows and columns. Each of the plurality of pixels has a first sub-pixel and a second sub-pixel which can apply mutually different voltages to the liquid crystal layer, where the first sub-pixel has a higher brightness than the second sub-pixel in certain gradations.

### 26 Claims, 115 Drawing Sheets

## US 8,203,520 B2

Page 2

| U.S.                               | PATENT DOC                 | CUMENTS     |           | FOREIGN PATI | ENT DOCUMENTS |

|------------------------------------|----------------------------|-------------|-----------|--------------|---------------|

| 2003/0016202 A1                    | 1/2003 Edwa                | ards et al. | JP        | 6-332009     | 12/1994       |

| 2003/0146893 A1                    | 8/2003 Sawa                | abe         | JP        | 10-186330    | 7/1998        |

| 2003/0179172 A1                    | 9/2003 Miya                |             | JP        | 10-268349    | 10/1998       |

| 2003/0179323 A1                    | 9/2003 Abile               |             | JP        | 10-274783    | 10/1998       |

| 2003/0227429 A1                    | 12/2003 Shim               |             | JP        | 11-242225    | 9/1999        |

| 2004/0008172 A1                    | 1/2004 Naka                |             | JP        | 2002-55343   | 2/2002        |

| 2004/0012551 A1<br>2004/0183767 A1 | 1/2004 Ishii<br>9/2004 Koo |             | * cited b | y examiner   |               |

FIG.1

18s

- 11a

*FIG.7*

FIG.9

*FIG.11*

FIG.12

*FIG.13*

FIG.14

FIG.15

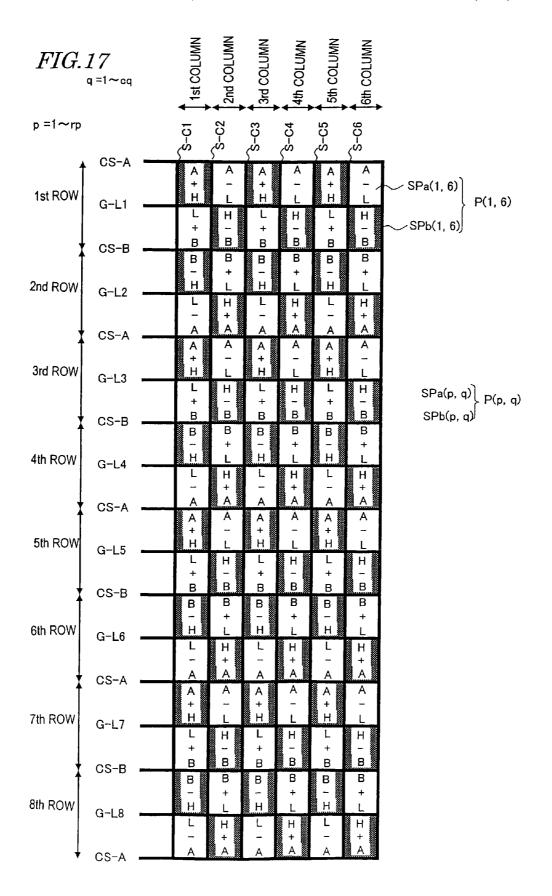

| FIG. 18          | ţ           | 2nd COLUMN                            | 4th COLUMN<br>5th COLUMN | eth COLUMN                            |                                 |

|------------------|-------------|---------------------------------------|--------------------------|---------------------------------------|---------------------------------|

| p =1 <b>~</b> rp | S-C1        | `\$-c2<br>`\$-c3                      | S-C5                     | °-C6                                  |                                 |

| 1st ROW G-       | - A - A + L | A A A                                 |                          | A<br>-                                | Pa(1, 6) P(1, 6)                |

| cs               | B<br>-      | - +<br>B B<br>B B<br>+ -              | - +<br>B B<br>B          | B +                                   | Pb(1, 6)J                       |

| 2nd ROW G-       | L2 L        | L H<br>H L<br>+ -                     | L H L + - A A            | L<br>H<br>+<br>A                      |                                 |

| 3rd ROW G-I      | A -         | A A + - H H                           | A A + - L H              | A<br>+<br>L                           |                                 |

| cs               | -В В        | + -<br>B B<br>B B                     | + -<br>B B               | H<br>+<br>B<br>B                      | SPa(p, q) $P(p, q)$ $SPb(p, q)$ |

| 4th ROW G-I      |             | - + H H L - +                         | - + H L - +              | H                                     |                                 |

| 5th ROW G-I      | A<br>+      | A A A A A A A A A A A A A A A A A A A | A A A + L H              | A A - L H                             |                                 |

| cs-              | +           | B B B                                 | - + B<br>B B B           | B<br>B<br>+                           |                                 |

| 6th ROW G-L      | -<br>-      | L H<br>H L<br>+ -                     | H L + -                  | <u>L</u><br>Н<br>+                    |                                 |

| 7th ROW G-L      | A<br>-      | A A A + - H H H L                     | A A A + - L H L          | A A A A A A A A A A A A A A A A A A A |                                 |

| cs-              | -<br>-      | B B B                                 | H                        | H<br>+<br>B<br>B                      |                                 |

| 8th ROW G-L      | ₩ ⊔ 🕷       | L H<br>H L<br>- +                     | L H<br>H L<br>- +        | L<br>H<br>-                           |                                 |

| ↓ cs-            | Α Α         | АА                                    | А А                      | А                                     |                                 |

S\_m+1 4 + -SBL\_m -||-->|-≠ 4 TFTB\_n, m\_ ComLC— ComLC GBL\_n+3 GBL\_n+2 GBL\_n+1 ∫ 유기

FIG. 22-1

FIG. 22-2

FIG. 23A-1

## FIG. 23A-2

# FIG. 23A-3

FIG. 23B-1

FIG. 23B-2

# FIG. 23B-3

FIG. 24A-1

FIG. 24A-2

FIG. 24B-1

|       |              | ,            | m<br><del>  → →</del> | m+1          | m+2          | m+3          | m+4          | m+5                     | l |

|-------|--------------|--------------|-----------------------|--------------|--------------|--------------|--------------|-------------------------|---|

| •     | A            |              | b<br>R1               | d<br>R1      | b<br>R1      | d<br>R1<br>+ | b<br>R1      | d<br>R1<br>+            |   |

| n     | В            |              | -<br>R2<br>d          | +<br>R2<br>b | -<br>R2<br>d | +<br>R2<br>b | -<br>R2<br>d | +<br>R2<br>b            |   |

| m 1.4 | Α            |              | b<br>R2<br>+          | d<br>R2<br>- | b<br>R2<br>+ | d<br>R2<br>- | b R2 + 1     | d<br>R2<br>-            |   |

| n+1 B | +<br>R1<br>d | - R1         | +<br>R1<br>d          | - R1 b       | +<br>R1<br>d | - R1         |              |                         |   |

| n+2   | A            |              | b<br>R1               | d<br>R1<br>+ | b<br>R1      | d<br>R1<br>+ | b<br>R1      | d<br>R1<br>+            |   |

| В     | -<br>R2<br>d | + R2 b       | -<br>R2<br>d          | + R2 b       | R2<br>d      | +<br>R2<br>b |              |                         |   |

| n+3   | Α            |              | b<br>R2<br>+          | d<br>R2<br>- | b<br>R2<br>+ | d<br>R2<br>- | b<br>R2<br>+ | d<br>R2<br>-            |   |

| В     |              | +<br>R1<br>d | - R1                  | +<br>R1<br>d | - R1         | +<br>R1<br>d | -<br>R1<br>b | b: Bright<br>—— d: Dark |   |

|       |              |              |                       |              |              |              |              |                         |   |

FIG. 24B-2

FIG. 25A

FIRST APPROXIMATION CIRCUIT OF CS BUSLINE LOAD IMPEDANCE: CR LOW PASS FILTER

Amounts of changes in pixel electrode

Amounts of changes in pixel electrode

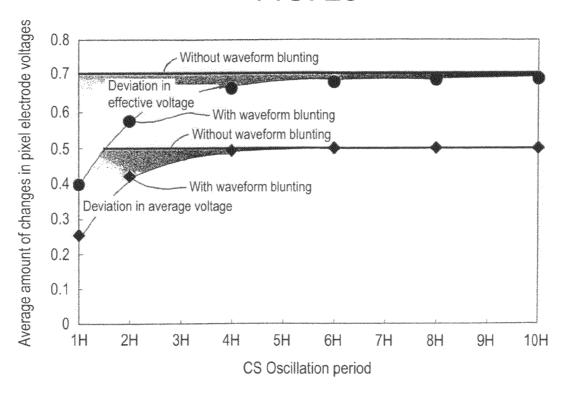

Amounts of changes in pixel electrode voltages caused by voltage oscillation of CS buslines (Time constant in the presence of CS waveform blunting: 0.2H)

Amounts of changes in pixel electrode voltages caused by voltage oscillation of CS buslines (Time constant in the sresence of CS waveform blunting: 0.2H)

Amounts of changes in pixel electrode voltages caused by voltage oscillation of CS buslines (Time constant in the presence of CS waveform blunting: 0.2H)

Amounts of changes in pixel electrode voltages caused by voltage oscillation of CS buslines (Time constant in the presence of CS waveform blunting: 0.2H)

Amounts of changes in pixel electrode voltages caused by voltage oscillation of CS buslines (Time constant in the presence of CS waveform blunting: 0.2H)

FIG. 28

**--|**-**--|**-**→**|----1 **--|---|-**4 ۲ ナイナ GBL\_n+4

FIG. 29-2

FIG. 30A-1

FIG. 30A-2

FIG. 30A-3

FIG. 30B-1

FIG. 30B-2

FIG. 30B-3

FIG. 31A-1

FIG. 31A-2

FIG. 31B-1

FIG. 31B-2

4 + 4 2-csBL ∠csBL <-ssel S\_m+1 -SBL\_m TFTB\_n, m\_\_\_\_ ComLC— CSVtypeB1 CCSVtypeB2 GBL\_n+2 GBL\_n+3 GBL\_n+1 튑

FIG. 32-1

\$\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarrow\rightarro <del>-)|-</del> **₩** 4 4 ---<del>)|</del> \$H 4H **→**|-**→ →**+ **→** 4 4 \$H \$H 1 **→ → --|**|-**--|**|-**→**|-<del>-}|-</del> **⊣⊢** <del>- |</del> GBL\_n+5

FIG. 32-2

FIG. 33A-1

FIG. 33A-2

FIG. 33A-3

FIG. 33B-1

FIG. 33B-2

FIG. 33B-3

FIG. 34A-1

FIG. 34A-2

FIG. 34B-1

FIG. 34B-2

|     |   | ! | m            | m+1          | m+2          | m+3          | m+4          | m+5          | <b>.</b>  |

|-----|---|---|--------------|--------------|--------------|--------------|--------------|--------------|-----------|

|     |   |   |              |              |              |              |              |              |           |

| n+4 | Α |   | b<br>B1      | d<br>B1<br>+ | b<br>B1      | d<br>B1<br>+ | b<br>B1      | d<br>B1<br>+ |           |

|     | В |   | B2<br>d      | + B2 b       | -<br>B2<br>d | +<br>B2<br>b | -<br>B2<br>d | +<br>B2<br>b |           |

| n+5 | Α |   | b B1 +       | d<br>B1<br>- | b<br>B1<br>+ | d<br>B1<br>- | b<br>B1<br>+ | d<br>B1<br>- |           |

|     | В |   | +<br>B2<br>d | -<br>B2<br>b | +<br>B2<br>d | - B2 b       | +<br>B2<br>d | -<br>B2<br>b |           |

| n+6 | Α |   | B1 -         | d<br>B1<br>+ | b<br>B1      | d<br>B1<br>+ | b<br>B1      | d<br>B1<br>+ |           |

|     | В |   | -<br>B2<br>d | +<br>B2<br>b | -<br>B2<br>d | +<br>B2<br>b | B2<br>d      | +<br>B2<br>b |           |

| n+7 | Α |   | b B1 +       | d<br>B1<br>- | b<br>B1<br>+ | d<br>B1<br>- | b<br>B1<br>+ | d<br>B1<br>- |           |

|     | В |   | +<br>B2<br>d | -<br>B2<br>b | +<br>B2<br>d | B2<br>b      | +            | -<br>B2<br>b | b: Bright |

| •   | I | 7 |              |              |              |              |              |              | u. Dalk   |

FIG. 36A-1

FIG. 36A-2

FIG. 36B-1

FIG. 36B-2

CSV typeM1a CSV typeM2a CSV typeM3a CSV typeM4a FIG. 37-1 SBL\_m+2 ₩ -1 SBL\_m+1 4 1h 44 1 SBL\_m CSBL\_n+2B,n+3A CSBL\_n+1B,n+2A CSBL\_nB,n+1A CSBL\_n-1B,nA CSV typeM4a CSV typeM3a CSV typeM2a CSV typeM1a GBL\_n

+ 1 1 ---+ HH + 1 --FIG. 37-2 —Ih ≠¥ 4 1 4 **→** --|---|-**₽→ →**|-4 ₩ Ц 4 CSBL\_n+3B,n+4A CSBL\_n+4B,n+5A CSBL\_n+5B,n+6A CSBL\_n+6B,n+7A CSBL\_n+7B,n+8A

7 4 1 1 1 FIG. 37-3 <del>}</del>⊢ **₩** 46 <del>}</del> 4 1 44 나 나 1 1 4 CSBL\_n+12B, CSBL\_n+10B, CSBL\_n+11B, CSBL\_n+8B, n+9A CSBL\_n+9B, GBL\_n+10 GBL\_n+12 GBL\_n+9 GBL\_n+11

FIG. 38-1 VCSVtypeM3a ¬ VCSVtypeM4a \_ VCSVtypeM1a \_ VCSVtypeM2a

FIG. 38-2

FIG. 38-3

CSV typeM1b CSV typeM2b CSV typeM3b CSV typeM4b CSV typeM5b CSV typeM6b 1 FIG. 39-1 28F\_m+2 2BF\_m+1 **₩** 44 1 +  $m_{J8S}$ n+3A CSV typeM6b CSV typeM5b CSV typeM4b CSV typeM3b CSV typeM2b CSV typeM1b GBL\_n+1 GBL

FIG. 39-2 **₩** <del>}</del> 1 + ₩ -CSBL\_n+6B, n+7A CSBL\_n+7B, n+8A CSBL\_n+4B, CSBL\_n+5B, GBL\_n+7

1 1 1 H-11 1  $CSBL_n+12B$ n+13A

FIG. 39-3

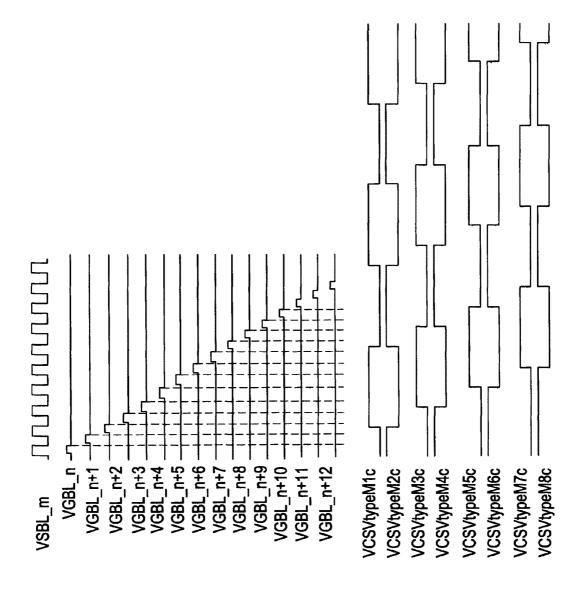

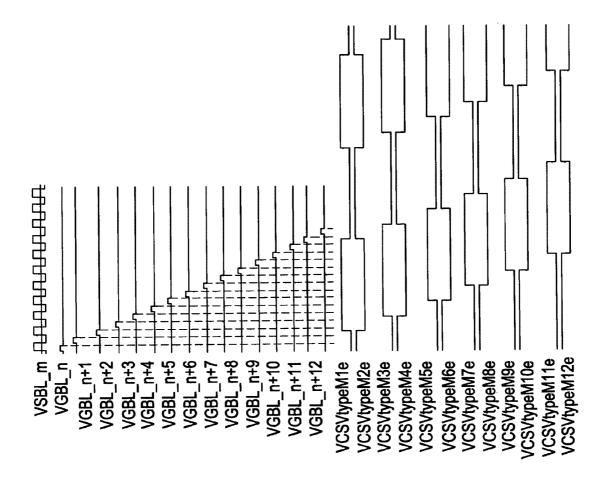

FIG. 40-1 VCSVtypeM5b ☐ VCSVtypeM6b ☐ VCSVtypeM3b \_ VCSVtypeM4b \_ VCSVtypeM1b **VCSVtypeM2b** VGBL\_n VGBL\_n+1 VGBL\_n+3 VGBL\_n+5 VGBL\_n+5 VGBL\_n+6 VGBL\_n+6 VGBL\_n+9 VGBL\_n+9 VGBL\_n+10 VGBL\_n+11

FIG. 40-2

FIG. 40-3

2BF m+5 中 FIG. 41-1 SBL\_m+1 W\_188 CSBL\_(n+3) B, (n+4)A CSBL\_(n-1) B, (n)A CSBL\_(n+1) CSBL\_(n) B, (n+1)A CSV typeM8b CSV typeM7b CSV typeM6b CSV typeM5b CSV typeM4b CSV typeM3b CSV typeM2b CSV typeM1b GBL\_n+3 GBL\_n+2 GBL\_n+1

FIG. 41-2 CSBL\_(n+9) B, (n+10)A GBL\_n+5 GBL\_n+6

**>** 4 4 44 4 1 ح FIG. 41-3 45 4 46 北 HE HH CSBL\_(n+12) CSBL\_(n+15) **CSBL\_(n+13)** CSBL\_(n+11) (n+15)A B, (n+14)A B, (n+16)A B, (n+11)A B, (n+12)A B, (n+13)A GBL\_n+10 GBL\_n+12 GBL\_n+11 GBL\_n

4 44 4 44 FIG. 41-4 4 44 4 4 CSBL\_(n+18) B, (n+19)A CSBL\_(n+19) B, (n+20)A CSBL\_(n+17) B,(n+18)A CSBL\_(n+21) B, (n+22)A B, (n+21)A GBL\_n+5 GBL\_n+8 GBL\_n+4 GBL\_n+7 GBL\_n+3 GBL\_n+6

FIG. 41-5

| بك        | - <del>(</del> + + + + + + + + + + + + + + + + + + +                                                                              | - <del>*</del> * |                                                                               | - * * * *      | -<br>+<br>+<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | 1<br>1<br>1<br>1                       | -11<br>                   |   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------|---|

| یک        | <del>\</del> |                  |                                                                               |                | ~£<br>→<br>→<br>- £                                                                              |                                        |                           |   |

| ید        | -4<br>-4<br>-4<br>-4<br>-4<br>-4<br>-4<br>-4<br>-4<br>-4<br>-4<br>-4<br>-4<br>-                                                   |                  | <del>,</del> <del>,</del> <del>,</del> <del>,</del> <del>,</del> <del>,</del> | - <del> </del> | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-      | —————————————————————————————————————— | -#-<br>+#-                |   |

| <u>بر</u> | 4<br>+ +<br>+ +                                                                                                                   | _!\<br>^#<br>}   | ر<br>بر بر<br>آ                                                               |                | <b>*</b> ₹ ₹                                                                                     | ~- h<br>^- k<br>}-                     | -K                        |   |

|           | CSBL_(n+22)<br>B, (n+23)A                                                                                                         |                  | CSBL_(n+23)<br>B, (n+24)A                                                     |                | CSBL_(n+24)<br>B, (n+25)A                                                                        |                                        | CSBL_(n+25)<br>B, (n+26)A |   |

| 4444      |                                                                                                                                   |                  |                                                                               |                |                                                                                                  |                                        |                           |   |

| ととととと     |                                                                                                                                   |                  |                                                                               |                |                                                                                                  |                                        |                           |   |

| GBL_n+9   |                                                                                                                                   | GBL_n+10         |                                                                               | GBL_n+11       |                                                                                                  | GBL_n+12                               |                           | _ |

FIG. 42-1

FIG. 42-2

FIG. 42-3

2BL\_m+2 28F\_m+1 FIG. 43-1 4 4 1 aBL\_m CSBL\_(n-1) B, (n)A B, (n+4)A B, (n+1)A CSV typeM10b CSV typeM9b CSV typeM8b CSV typeM7b CSV typeM6b CSV typeM5b CSV typeM4b CSV typeM3b CSV typeM2b CSV typeM1b GBL\_n+3 GBL\_n+2

4 4 45 FIG. 43-2 4 ₩ Ц 46 CSBL\_(n+8) B, (n+9)A CSBL\_(n+6) B, (n+7)A B, (n+10)A CSBL\_(n+ B, (n+5)A B, (n+8)A GBL\_n+9 GBL\_n+7 GBL\_n+5 GBL\_n+6 GBL\_n+8

마 4 4 4 ₽H-45 4 4 FIG. 43-3 4 4 4 4 HH 7 CSBL\_(n+15) B, (n+16)A CSBL\_(n+12) CSBL\_(n+13) B, (n+14)A B, (n+15)A B, (n+13)A B, (n+12)A GBL\_n+12 GBL n+11 GBL\_n+2 GBL\_n+1

₩ |-4 FIG. 43-4 3 4 4 44 1 CSBL\_(n+18) B, (n+19)A CSBL\_(n+20) B, (n+21)A CSBL\_(n+21) B, (n+20)A B, (n+22)A B, (n+18)A GBL\_n+5 GBL\_n+6 GBL\_n+4 GBL n+3 GBL\_n+8 GBL\_n+7

4 ---FIG. 43-5 7 4 1 1 --B, (n+24)A

FIG. 44-1

FIG. 44-2

FIG. 44-3

SBL\_m+2 285\_m+1 1 4 1 + SBL\_m CSBL\_(n+2) B, (n+3)A CSBL\_(n+3) B, (n+4)A CSBL\_(n+1) B, (n+2)A FIG. 45-1 CSBL\_(n-1) B, (n)A CSBL\_(n) B, (n+1)A CSV typeM12b CSV typeM11b CSV typeM10b CSV typeM9b CSV typeM8b CSV typeM7b CSV typeM6b CSV typeM5b CSV typeM4b CSV typeM3b CSV typeM2b CSV typeM1b GBL\_n+3 GBL\_n+2 GBL\_n+1

1 44 4 136 44 ST. 44 HH HH 节 4 4 北 1 4 1 1 FIG. 45-2 CSBL\_(n+5) B, (n+6)A CSBL\_(n+8) B, (n+9)A CSBL\_(n+9) B, (n+10)A CSBL\_(n+4) B, (n+5)A CSBL\_(n+6) (n+8)AB, (n+7)A GBL\_n+5 GBL\_n+6 GBL\_n+7 GBL\_n+8 GBL\_n+9

44 1 44 44 HH 1 HH 7 1 HH 1 45 45 4 4 4 4 CSBL\_(n+12) B, (n+13)A FIG. 45-3 CSBL\_(n+11) B, (n+12)A CSBL\_(n+13) CSBL\_(n+14) CSBL\_(n+15) (n+15)AB, (n+16)A B, (n+14)A GBL\_n+10 ~~~~~~~ GBL\_n+11 GBL\_n+12 GBL\_n+2 GBL\_n+1

H 1 1 46 + 1 H+ 4 4 4 1 1 CSBL\_(n+20) B, (n+21)A FIG. 45-4 CSBL\_(n+18) CSBL\_(n+16) CSBL\_(n+17) CSBL\_(n+19) CSBL\_(n+21 B, (n+20)A B, (n+22)A B, (n+19)A B, (n+18)A GBL\_n+6 GBL\_n+5 GBL\_n+8 GBL\_n+7 GBL\_n+4

₩ 4 4 1 FIG. 45-5 GBL\_n+11

FIG. 46-1

FIG. 46-2

FIG. 46-3

CSV typeM1f CSV typeM2f CSV typeM3f CSV typeM4f FIG. 47-1 SBL\_m+2 + 1 + SBL\_m+1 <del>}</del> → ⊢ H-1 HH HH m\_182 CSBL\_n+2B,n+3A CSBL\_n+1B,n+2A CSV typeM4f CSV typeM3f CSV typeM2f CSV typeM1f

1 + FIG. 47-2 4 **₩** 1 4 11 4 CSBL\_n+6B,n+7A CSBL\_n+7B,n+8A CSBL\_n+3B,n+4A CSBL\_n+4B,n+5A CSBL\_n+5B,n+6A

)+ + + 7 الر براج <del>)</del>|-/ 46 4 **→** 44 H-11-4 **→** + 46 CSBL\_n+8B,n+9A CSBL\_n+12B, n+13A CSBL\_n+11B, n+12A CSBL\_n+10B, CSBL\_n+9B, n+10A GBL\_n+8 トトトト GBL\_n+10 GBL\_n+9

FIG. 48-1 VCSVtypeM3f 1 **VCSVtypeM2f** VCSVtypeM1f

FIG. 48-2

FIG. 48-3

CSV typeM1g CSV typeM2g CSV typeM3g CSV typeM4g CSV typeM5g CSV typeM6g **→** <del>||-</del> 4 1 4 4 46 )|-/ FIG. 49-1 2BF\_m+2 **→** 4 4 46 1 2Br\_m+1 1h <del>}</del> → 4 4 4 1 CSBL\_n+2B, n+3A M\_J8S CSBL\_n+1B, CSBL\_nB, CSV typeM6g CSV typeM5g CSV typeM4g CSV typeM3g CSV typeM2g CSV typeM1g GBL\_n+2

₩ |-|-FIG. 49-2 H )|-46 4 ₩ -4 4 H-4H n+8A GBL\_n+3 トイト GBL\_n+5

Jun. 19, 2012

FIG. 49-3

| CBL_n+8 ケイケイケー | <u>بع</u>              |   | <b>しししししし</b> |

|----------------|------------------------|---|---------------|

| GBL_n+9        | SBL_n+8B,              |   |               |

| 01+10          |                        |   |               |

|                |                        |   |               |

| GBL_n+11       | —  -<br> -  -<br> -  - |   |               |

|                | <b>-1</b>              |   |               |

| GBL_n+12       | — <u>†</u>             | į |               |

|                |                        |   |               |

VSBL\_m f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>|-f<sup>-</sup>| VCSVtypeM5g VCSVtypeM6g VCSVtypeM1g VCSVtypeM2g VCSVtypeM3g VCSVtypeM4g VGBL\_n+1

VGBL\_n+3

VGBL\_n+4

VGBL\_n+5

VGBL\_n+6

VGBL\_n+7

VGBL\_n+8

VGBL\_n+9

VGBL\_n+11

VGBL\_n+11

VGBL\_n+11

VGBL\_n+11

VGBL\_n+11

FIG. 50-2

FIG. 50-3

## LIOUID CRYSTAL DISPLAY

### PRIORITY STATEMENT

This application is a continuation of application Ser. No. 511/002,424 filed on Dec. 3, 2004 now U.S. Pat. No. 7,429, 981, and from which priority is claimed under 35 U.S.C. §120. This application also claims priority from Japanese Patent Application Nos. 2003-408046 filed on Dec. 5, 2003 and 2004-250982 filed on Aug. 30, 2004, in the Japan Intellectual Property Office under U.S.C. §119. The entire contents of each of the above-identified applications are incorporated herein by reference.

## BACKGROUND OF THE INVENTION

### 1. Field of the Invention

The present invention relates to a structure and/or drive method which can reduce viewing angle dependence of ry characteristics in a liquid crystal display.

## 2. Description of the Related Art

Liquid crystal displays are flat-panel displays which have excellent features including high resolution, small thickness, light weight, and low power consumption. Their market size 25 has expanded recently with improvements in display performance and production capacity as well as improvements in price competitiveness against other types of display device.

Twisted nematic (TN) liquid crystal displays which have conventionally been in common use have liquid crystal molecules with positive dielectric anisotropy placed between upper and lower substrates in such a way that their long axis are oriented approximately parallel to substrate surfaces and twisted 90 degrees along the thickness of a liquid crystal layer. When a voltage is applied to the liquid crystal layer, the 35 liquid crystal molecules rise parallel to the electric field, releasing the twisted alignment. The TN liquid crystal display controls transmitted light quantity using changes in rotary polarization resulting from the orientation changes of the liquid crystal molecules caused by voltage.

The TN liquid crystal display allows wide manufacturing margins and high productivity. On the other hand, it has problems with display performance, especially with viewing angle characteristics. Specifically, when the display surface of the TN liquid crystal display is viewed obliquely, the 45 display contrast ratio lowers considerably. Consequently, even if an image clearly presents a plurality of grayscales from black to white when viewed from the front, brightness differences between grayscales appear very unclear when the image is viewed obliquely. Besides, the phenomenon (socalled grayscale reversal) that a portion which appears dark when viewed from the front appears brighter when viewed obliquely also presents a problem.

To improve the viewing angle characteristics of the TN liquid crystal display, some liquid crystal displays have been 55 developed recently, including an in-plane switching (IPS) liquid crystal display described in Japanese Patent Publication No. 63-21907, a multi-domain vertically aligned (MVA) liquid crystal display described in Japanese Laid-Open Patent Publication No. 11-242225, an Axial Symmetric Micro-cell (ASM) display described in Japanese Laid-Open Patent Publication No. 10-186330, and a liquid crystal display described in Japanese Laid-Open Patent Publication No. 2002-55343.

Liquid crystal displays employing any of the novel modes described above (wide viewing angle modes) solve the concrete problems with viewing angle characteristics. Specifically they are free of the problems that the display contrast 2

ratio lowers considerably or display grayscales are reversed when the display surface of the TN liquid crystal display is viewed obliquely.

Under circumstances, where display quality of liquid crystal displays continues to be improved, a new problem with viewing angle characteristics have surfaced, namely, viewing angle dependence of  $\gamma$  characteristics, meaning that  $\gamma$  characteristics differ between when the display is viewed from the front and when the display is viewed obliquely. This presents a problem, especially when displaying images such as photographs or displaying television broadcasts and the like.

The viewing angle dependence of γ characteristics is more prominent in MVA mode and ASM mode than in IPS mode. On the other hand, it is more difficult to produce IPS panels which provide a high contrast ratio when viewed from the front with high productivity than MVA or ASM panels. Thus, it is desired to reduce the viewing angle dependence of γ characteristics in MVA mode or ASM mode.

The present invention has been made in view of the above points. Its main object is to provide a liquid crystal display with reduced viewing angle dependence of  $\gamma$  characteristics.

#### SUMMARY OF THE INVENTION

To achieve the above object, a first aspect of the present invention provides a liquid crystal display used in normally black mode, comprising a plurality of pixels each of which has a liquid crystal layer and a plurality of electrodes for applying voltage to the liquid crystal layer, wherein: each of the plurality of pixels comprises a first sub-pixel and a second sub-pixel which can apply mutually different voltages to their respective liquid crystal layers; and when each of the plurality of pixels displays a grayscale gk which satisfies 0≦gk≦gn, where gk and gn are integers not less than zero and a larger value of gk corresponds to higher brightness, relationships  $\Delta V12$  (gk)>0 volts and  $\Delta V12$  (gk) $\geq \Delta V12$  (gk+1) are satisfied at least in a range  $0 \le gk \le n-1$  if it is assumed that  $\Delta V12$ (gk)=V1 (gk)-V2 (gk), where V1 (gk) and V2 (gk) are rootmean-square voltages applied to the liquid crystal layers of the first sub-pixel and the second sub-pixel, respectively. Incidentally, the "pixel" herein represents the minimum unit of display on the liquid crystal display and in the case of color display, it corresponds to "a picture element (or dot)" which displays an individual color (typically, R, G or B).

The liquid crystal display may be configured such that: each of the plurality of pixels comprises a third sub-pixel which can apply a voltage different from those of the first sub-pixel and the second sub-pixel to its liquid crystal layer; and when each of the plurality of pixels displays a grayscale gk and  $\Delta V13$  (gk)=V1 (gk)-V3 (gk), a relationship 0 volts< $\Delta V13$  (gk)< $\Delta V12$  (gk) is satisfied if the root-mean-square voltage applied to the liquid crystal layer of the third sub-pixel is V3 (gk).

Preferably, the root-mean-square voltages applied to the liquid crystal layers satisfy a relationship  $\Delta V12$  (gk) $\geq \Delta V12$  (gk+1) at least in a range  $0 \leq gk \leq n-1$ .

Preferably, relationships  $\Delta V12$  (gk) $\cong \Delta V12$  (gk+1) and  $\Delta V13$  (gk) $\cong \Delta V13$  (gk+1) are satisfied at least in a range  $0 < gk \le n-1$  when each pixel has a third sub-pixel.

In a preferred embodiment, the first sub-pixel and the second sub-pixel each comprise: a liquid crystal capacitor formed by a counter electrode and a sub-pixel electrode opposing the counter electrode via the liquid crystal layer, and a storage capacitor formed by a storage capacitor electrode connected electrically to the sub-pixel electrode, an insulating layer, and a storage capacitor counter electrode opposing the storage capacitor electrode via the insulating layer; and

the counter electrode is a single electrode shared by the first sub-pixel and the second sub-pixel, and the storage capacitor counter electrodes of the first sub-pixel and the second sub-pixel are electrically independent of each other. Typically, the counter electrode is provided on a counter substrate (sometimes referred to as a "common electrode"), but in IPS mode, it is provided on the same substrate as the sub-pixel electrode. Incidentally, "the counter electrode opposing a sub-pixel electrode via the liquid crystal layer" need not necessarily oppose the sub-pixel electrode across the thickness of the liquid crystal layer. In an IPS liquid crystal display, it is placed within the liquid crystal layer in opposing relation to the sub-pixel electrode across the liquid crystal layer.

In a preferred embodiment, the liquid crystal display comprises two switching elements provided for the first sub-pixel and the second sub-pixel, respectively, wherein the two switching elements are turned on and off by scan line signal voltages supplied to a common scan line; display signal voltages are applied to the respective sub-pixel electrodes and 20 storage capacitor electrodes of the first sub-pixel and the second sub-pixel from a common signal line when the two switching elements are on; voltages of the respective storage capacitor counter electrodes of the first sub-pixel and the second sub-pixel change after the two switching elements are 25 turned off; and the amounts of change defined by the direction and magnitude of the change differ between the first sub-pixel and the second sub-pixel. The amounts of change in the storage capacitor counter electrodes are defined here not only in terms of magnitude (absolute value), but also in terms of 30 direction. For example, the amounts of change in the voltages of the storage capacitor counter electrodes of the first subpixel and the second sub-pixel may be equal in absolute value and differ in sign. In short, if voltage rises in one of the storage capacitor counter electrodes and falls in the other storage 35 capacitor counter electrode after the switching element is turned off, the absolute values of the changes may be equal.

Preferably, the liquid crystal layer is a vertically aligned liquid crystal layer and contains nematic liquid crystal material with negative dielectric anisotropy.

Preferably, the liquid crystal layers of the first sub-pixel and the second sub-pixel each contain four domains which are approximately 90 degrees apart in azimuth direction in which their liquid crystal molecules incline when a voltage is applied.

Preferably, the first sub-pixel and the second sub-pixel are placed on opposite sides of the common signal line; the first sub-pixel and the second sub-pixel each have, on the counter electrode side, a plurality of ribs protruding towards the liquid crystal layer and the plurality of ribs include a first rib extending in a first direction and a second rib extending in a second direction approximately orthogonal to the first direction; and the first rib and the second rib are placed symmetrically with respect to a center line parallel to the common scan line in each of the first sub-pixel and the second sub-pixel and the second rib in one of the first and second sub-pixels is symmetrical with respect to the arrangement of the first rib and the second rib in the other sub-pixel.

Preferably, the center line parallel to the common scan line 60 in each of the first sub-pixel and the second sub-pixel is placed at an interval equal to approximately one half of an array pitch of the scan lines in both the first sub-pixel and the second sub-pixel.

Preferably, the area of the first sub-pixel is equal to or 65 smaller than the area of the second sub-pixel. When each of the plurality of pixels has three or more sub-pixels, preferably

4

the area of the sub-pixel to which the highest root-meansquare voltage is applied is not larger than the areas of the other sub-pixels.

In a liquid crystal display according to another aspect of the present invention: direction of the electric field applied to the liquid crystal layers in the plurality of pixels is reversed every vertical scanning period; and when displaying an intermediate grayscale, the direction of the electric field is reversed periodically in the row direction in the case of pixels in an arbitrary row and it is reversed every pixel in the column direction in the case of pixels in an arbitrary column.

According to one embodiment, the direction of the electric field is reversed every pixel in the row direction in the case of pixels in an arbitrary row.

According to one embodiment, the direction of the electric field is reversed every two pixels in the row direction in the case of pixels in an arbitrary row.

A liquid crystal display according to one embodiment, operates in normally black mode; wherein the at least two sub-pixels include two sub-pixels SPa (p, q) and SPb (p, q); and when each of the plurality of pixels displays a grayscale gk which satisfies  $0 \le gk \le gn$ , where gk and gn are integers not less than zero and a larger value of gk corresponds to higher brightness, relationships  $\Delta V12$  (gk)>0 volts and  $\Delta V12$  (gk) $\ge \Delta V12$  (gk+1) are satisfied at least in a range  $0 < gk \le n-1$  if it is assumed that  $\Delta V12$  (gk)=V1 (gk)-V2 (gk), where V1 (gk) and V2 (gk) are root-mean-square voltages applied to the liquid crystal layers of the first sub-pixel and the second sub-pixel, respectively.

According to one embodiment, a relationship  $\Delta V12$  (gk)  $\geq \Delta V12$  (gk+1) is satisfied at least in a range  $0 < gk \leq n-1$ .

According to one embodiment, SPa (p, q) and SPb (p, q) each comprise: a liquid crystal capacitor formed by a counter electrode and a sub-pixel electrode opposing the counter electrode via the liquid crystal layer, and a storage capacitor formed by a storage capacitor electrode connected electrically to the sub-pixel electrode, an insulating layer, and a storage capacitor counter electrode opposing the storage capacitor electrode via the insulating layer; and the counter electrode is a single electrode shared by SPa (p, q) and SPb (p, q), and the storage capacitor counter electrodes of SPa (p, q) and SPb (p, q) are electrically independent of each other.

According to one embodiment, the liquid crystal display 45 comprises two switching elements provided for SPa (p, q) and SPb (p, q), respectively, wherein the two switching elements are turned on and off by scan line signal voltages supplied to a common scan line; display signal voltages are applied to the respective sub-pixel electrodes and storage capacitor electrodes of SPa (p, q) and SPb (p, q) from a common signal line when the two switching elements are on; voltages of the respective storage capacitor counter electrodes of SPa (p, q) and SPb (p, q) change after the two switching elements are turned off; and the amounts of change defined by the direction and magnitude of the change differ between SPa (p, q) and SPb (p, q). Specifically, when the two switching elements are on, voltages are applied to the respective storage capacitor counter electrodes of VSpa (on) and VSpb (on) such that when the two switching elements are turned off, potentials of the respective storage capacitor counter electrodes will change, for example, from VSpa (on) and VSpb (on) to VSpa (off) and VSpb (off), respectively, and that the respective amounts of change "VSpa (off)-VSpa (on)" and "VSpb (off)-VSpb (on)" will be mutually different.

According to one embodiment, the changes in the voltages of the storage capacitor counter electrodes of SPa (p, q) and SPb (p, q), are equal in amount and opposite in direction.

According to one embodiment, the voltages of the storage capacitor counter electrodes of SPa (p, q) and SPb (p, q) are oscillating voltages 180 degrees out of phase with each other. The oscillating voltages may be rectangular waves, sine waves, or triangular waves.

According to one embodiment, the oscillating voltages of the storage capacitor counter electrodes of SPa (p, q) and SPb (p, q) each have a period approximately equal to one horizontal scanning period.

the storage capacitor counter electrodes of SPa (p, q) and SPb (p, q) each have a period shorter than one horizontal scanning period.

According to one embodiment, the oscillating voltages of the storage capacitor counter electrodes of SPa (p, q) and SPb (p, q) are approximately equal within any horizontal scanning period if averaged over the period.

According to one embodiment, the period of the oscillation is one-half of one horizontal scanning period.

According to one embodiment, the oscillating voltages are rectangular waves with a duty ratio of 1:1.

According to one embodiment, SPa (p, q) and SPb (p, q) have different areas, of which the smaller area belongs to SPa (p, q) or SPb (p, q) whichever has a larger root-mean-square 25 voltage applied to its liquid crystal layer.

According to one embodiment, the area of SPa (p, q) and area of SPb (p, q) are practically equal.

A third aspect of the present invention provides a liquid crystal display, comprising a plurality of pixels each of which 30 has a liquid crystal layer and a plurality of electrodes for applying a voltage to the liquid crystal layer and which are arranged in a matrix of rows and columns, wherein: each of the plurality of pixels has a first sub-pixel and a second sub-pixel which can apply mutually different voltages to the 35 liquid crystal layer, where the first sub-pixel has a higher brightness than the second sub-pixel in certain gradations; the first sub-pixel and the second sub-pixel each comprise: a liquid crystal capacitor formed by a counter electrode and a sub-pixel electrode opposing the counter electrode via the 40 liquid crystal layer, and a storage capacitor formed by a storage capacitor electrode connected electrically to the subpixel electrode, an insulating layer, and a storage capacitor counter electrode opposing the storage capacitor electrode via the insulating layer; the counter electrode is a single 45 electrode shared by the first sub-pixel and the second subpixel, and the storage capacitor counter electrodes of the first sub-pixel and the second sub-pixel are electrically independent of each other; and the storage capacitor counter electrode of the first sub-pixel in any of the plurality of pixels and the 50 storage capacitor counter electrode of the second sub-pixel of a pixel adjacent to any of the pixels in the column direction are electrically independent of each other.

According to one embodiment, the first sub-pixel in the any of the pixels is arranged in such a way as to be adjacent to the 55 second sub-pixel of the pixel adjacent to the any of the pixels in the column direction.

According to one embodiment, in each of the plurality of pixels, the first sub-pixel is arranged in such a way as to be adjacent to the second sub-pixel in the column direction.

According to one embodiment, the liquid crystal display comprises a plurality of storage capacitor trunks electrically independent of each other, wherein each of the storage capacitor trunks is electrically connected to any of the storage capacitor counter electrodes of the first sub-pixel and the 65 second sub-pixel in the plurality of pixels via a storage capacitor line.

According to one embodiment, the number of the storage capacitor trunks electrically independent of each other among a plurality of the storage capacitor trunks is L, storage capacitor counter voltage supplied by each of the storage capacitor trunks is oscillating voltage, and the period of oscillation is L times a horizontal scanning period.

According to one embodiment, the plurality of storage capacitor trunks electrically independent of each other are an even number of storage capacitor trunks grouped into pairs of According to one embodiment, the oscillating voltages of 10 storage capacitor trunks which supply storage capacitor counter voltages whose oscillations are 180 degrees out of phase with each other.

> According to one embodiment, the number of storage capacitor trunks electrically independent of each other is larger than 8 times the quotient obtained by dividing one horizontal scanning period by a CR time constant which approximates maximum load impedance of the storage capacitor line.

> According to one embodiment, the number of storage capacitor trunks electrically independent of each other is larger than 8 times the quotient obtained by dividing one horizontal scanning period by a CR time constant which approximates maximum load impedance of the storage capacitor line and is an even number.

> According to one embodiment, the plurality of storage capacitor trunks include a first storage capacitor trunk and a second storage capacitor trunk electrically independent of each other; and if the storage capacitor line connected to the storage capacitor counter electrode of the first sub-pixel of the pixel located at the intersection of an arbitrary column and a given row n among rows formed by the plurality of pixels is designated as CSBL\_A\_n, if the storage capacitor line connected to the storage capacitor counter electrode of the second sub-pixel is designated as CSBL\_B\_n, and if k a natural number (including 0): CSBL\_A\_n+k is connected to the first storage capacitor trunk, and CSBL\_B\_n+k is connected to the second storage capacitor trunk.

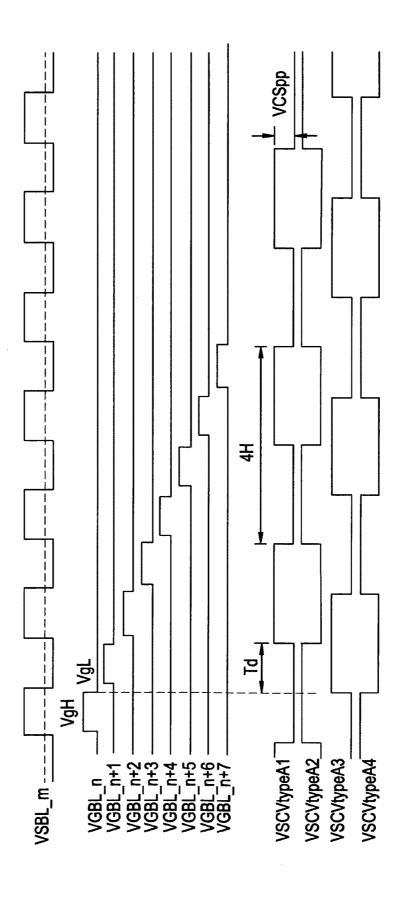

> According to one embodiment, the periods of oscillation of first and second storage capacitor counter voltages supplied, respectively, by the first and second storage capacitor trunks are both twice the horizontal scanning period.

> According to one embodiment, the second storage capacitor counter voltage lags the first storage capacitor counter voltage by a phase difference of one horizontal scanning

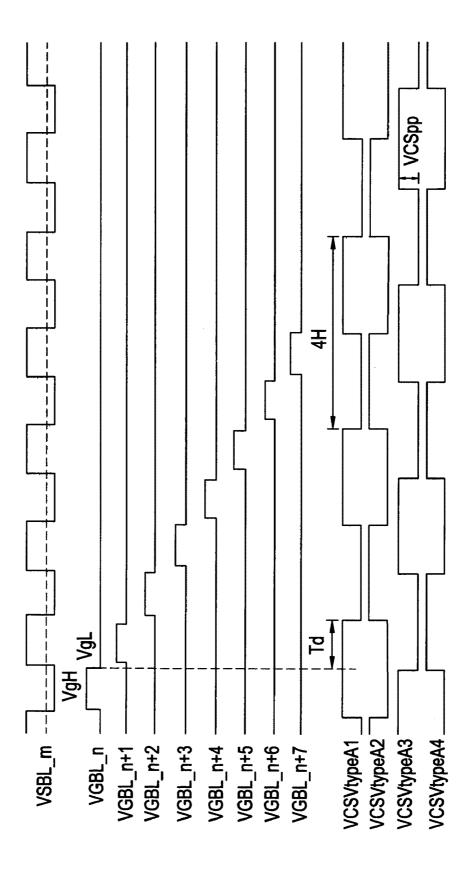

> According to one embodiment, the liquid crystal display comprises two switching elements provided for the first subpixel and the second sub-pixel, respectively, wherein the two switching elements are turned on and off by scan line signal voltages supplied to a common scan line, display signal voltages are applied to the respective sub-pixel electrodes and storage capacitor electrodes of the first sub-pixel and the second sub-pixel from a common signal line when the two switching elements are on, and voltages of the respective storage capacitor counter electrodes of the first sub-pixel and the second sub-pixel change after the two switching elements are turned off; and if Td denotes the time required for the first storage capacitor counter voltage to change for the first time after the two switching elements are turned off, Td is larger than 0 horizontal scanning period and smaller than one horizontal scanning period.

> According to one embodiment, the Td is approximately equal to 0.5 times the horizontal scanning period.

> According to one embodiment, the plurality of storage capacitor trunks include a first storage capacitor trunk, second storage capacitor trunk, third storage capacitor trunk, and fourth storage capacitor trunk electrically independent of

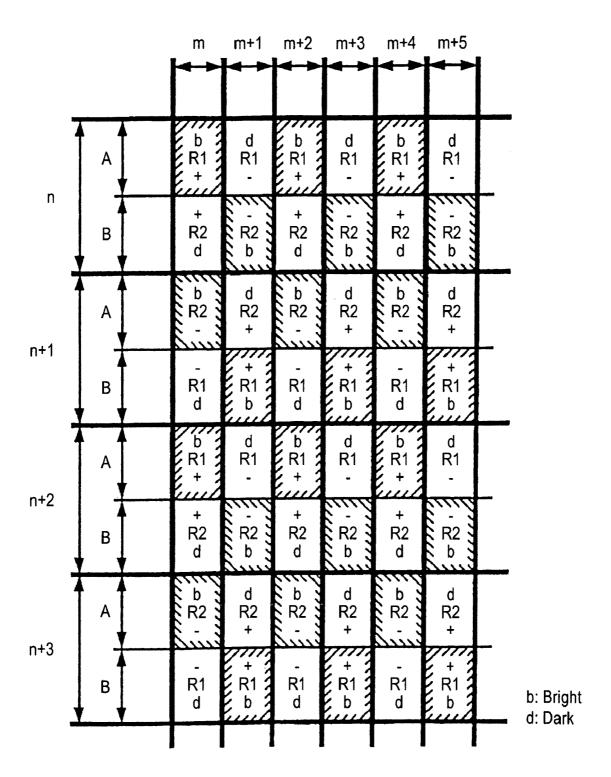

each other; and if the storage capacitor line connected to the storage capacitor counter electrode of the first sub-pixel of the pixel located at the intersection of an arbitrary column and a given row n among rows formed by the plurality of pixels is designated as CSBL\_A\_n, if the storage capacitor line connected to the storage capacitor counter electrode of the second sub-pixel is designated as CSBL\_B\_n, and if k is a natural number (including 0): CSBL\_A\_n+4\*k and CSBL\_B\_n+2+4\*k are connected to the first storage capacitor trunk, CSBL\_B\_n+4\*k and CSBL\_A\_n+2+4\*k are connected to the second storage capacitor trunk, CSBL\_A\_n+1+4\*k and CSBL\_B\_n+3+4\*k are connected to the third storage capacitor trunk, and CSBL\_B\_n+1+4\*k and CSBL\_A\_n+3+4\*k are connected to the fourth storage capacitor trunk.

According to one embodiment, the periods of oscillation of first to fourth storage capacitor counter voltages supplied, respectively, by the first to fourth storage capacitor trunks are all 4 times the horizontal scanning period.

According to one embodiment, the second storage capacitor counter voltage lags the first storage capacitor counter voltage by a phase difference of two horizontal scanning periods, the third storage capacitor counter voltage lags the first storage capacitor counter voltage by a phase difference of three horizontal scanning periods, and the fourth storage 25 capacitor counter voltage lags the first storage capacitor counter voltage by a phase difference of one horizontal scanning period.

According to one embodiment, the liquid crystal display comprises two switching elements provided for the first sub- 30 pixel and the second sub-pixel, respectively, wherein the two switching elements are turned on and off by scan line signal voltages supplied to a common scan line, display signal voltages are applied to the respective sub-pixel electrodes and storage capacitor electrodes of the first sub-pixel and the 35 second sub-pixel from a common signal line when the two switching elements are on, and voltages of the respective storage capacitor counter electrodes of the first sub-pixel and the second sub-pixel change after the two switching elements are turned off; and if Td denotes the time required for the first  $\,$  40  $\,$ storage capacitor counter voltage to change for the first time after the two switching elements are turned off, Td is larger than 0 horizontal scanning period and smaller than two horizontal scanning periods.

According to one embodiment, the Td is approximately 45 equal to one horizontal scanning period.

According to one embodiment, the plurality of storage capacitor trunks include a first storage capacitor trunk, second storage capacitor trunk, third storage capacitor trunk, fourth storage capacitor trunk, fifth storage capacitor trunk, and 50 sixth storage capacitor trunk electrically independent of each other; and if the storage capacitor line connected to the storage capacitor counter electrode of the first sub-pixel of the pixel located at the intersection of an arbitrary column and a given row n among rows formed by the plurality of pixels 55 arranged in a row-and-column matrix is designated as CSBL\_A\_n, if the storage capacitor line connected to the storage capacitor counter electrode of the second sub-pixel is designated as CSBL\_B\_n, and if k is a natural number (including 0): CSBL\_A\_n+3\*k is connected to the first storage 60 capacitor trunk, CSBL\_B\_n+3\*k is connected to the second storage capacitor trunk, CSBL\_A\_n+1+3\*k is connected to the third storage capacitor trunk, CSBL\_B\_n+1+3\*k is connected to the fourth storage capacitor trunk, CSBL\_A\_n+2+ 3\*k is connected to the fifth storage capacitor trunk, and 65 CSBL\_B\_n+2+3\*k is connected to the sixth storage capacitor trunk.

8

According to one embodiment, the periods of oscillation of first to sixth storage capacitor counter voltages supplied, respectively, by the first to sixth storage capacitor trunks are all 6 times the horizontal scanning period.

According to one embodiment, the plurality of storage capacitor trunks include a first storage capacitor trunk, second storage capacitor trunk, third storage capacitor trunk, fourth storage capacitor trunk, fifth storage capacitor trunk, sixth storage capacitor trunk, ..., (L-3)-th storage capacitor trunk, (L-2)-th storage capacitor trunk, (L-1)-th storage capacitor trunk, and L-th storage capacitor trunk for a total of L storage capacitor trunks electrically independent of each other; and when ½ of the number L of the electrically independent storage capacitor trunks is an odd number, i.e., when L=2, 6, 10, ..., or the like, if the storage capacitor line connected to the storage capacitor counter electrode of the first sub-pixel of the pixel located at the intersection of an arbitrary column and a given row n among rows formed by the plurality of pixels is designated as CSBL\_A\_n, if the storage capacitor line connected to the storage capacitor counter electrode of the second sub-pixel is designated as CSBL\_B\_n, and if k is a natural number (including 0): CSBL\_A\_n+(L/2)\*k is connected to the first storage capacitor trunk, CSBL\_B\_n+(L/2)\*k is connected to the second storage capacitor trunk, CSBL\_A\_n+1+ (L/2)\*k is connected to the third storage capacitor trunk, CSBL\_B\_n+1+(L/2)\*k is connected to the fourth storage capacitor trunk, CSBL\_A\_n+2+(L/2)\*k is connected to the fifth storage capacitor trunk, CSBL\_B\_n+2+(L/2)\*k is connected to the sixth storage capacitor trunk, CSBL\_A\_n+(L/ 2)-2+(L/2)\*k is connected to the (L-3)-th storage capacitor trunk, CSBL\_B\_n+(L/2)-2+(L/2)\*k is connected to the (L-2)-th storage capacitor trunk,  $CSBL_A_n+(L/2)-1+$ (L/2)\*k is connected to the (L-1)-th storage capacitor trunk, and CSBL\_B\_n+(L/2)-1+(L/2)\*k is connected to the L-th storage capacitor trunk.

According to one embodiment, the periods of oscillation of first to L-th storage capacitor counter voltages supplied, respectively, by the first to L-th storage capacitor trunks are all L times the horizontal scanning period.

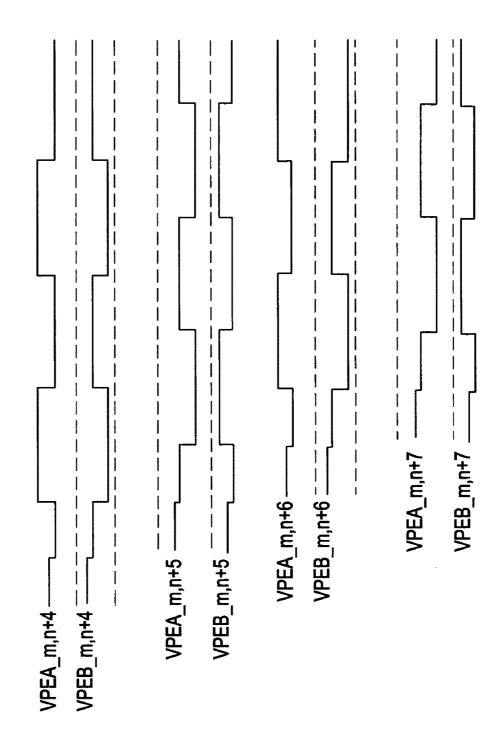

According to one embodiment, the plurality of storage capacitor trunks include a first storage capacitor trunk, second storage capacitor trunk, third storage capacitor trunk, fourth storage capacitor trunk, fifth storage capacitor trunk, sixth storage capacitor trunk, seventh storage capacitor trunk, and eighth storage capacitor trunk electrically independent of each other; and if the storage capacitor line connected to the storage capacitor counter electrode of the first sub-pixel of the pixel located at the intersection of an arbitrary column and a given row n among rows formed by the plurality of pixels is designated as CSBL\_A\_n, if the storage capacitor line connected to the storage capacitor counter electrode of the second sub-pixel is designated as CSBL B n, and if k is a natural number (including 0): CSBL\_A\_n+8\*k and CSBL\_B\_n+4+ 8\*k are connected to the first storage capacitor trunk, CSBL\_B\_n+8\*k and CSBL\_A\_n+4+8\*k are connected to the second storage capacitor trunk, CSBL\_A\_n+1+8\*k and CSBL\_B\_n+5+8\*k are connected to the third storage capacitor trunk, CSBL\_B\_n+1+8\*k and CSBL\_A\_n+5+8\*k are connected to the fourth storage capacitor trunk, CSBL\_A\_n+ 2+8\*k and CSBL\_B\_n+6+8\*k are connected to the fifth storage capacitor trunk, CSBL B n+2+8\*k and CSBL A n+6+ 8\*k are connected to the sixth storage capacitor trunk, CSBL\_A\_n+3+8\*k and CSBL\_B\_n+7+8\*k are connected to the seventh storage capacitor trunk, and CSBL\_B\_n+3+8\*k and CSBL\_A\_n+7+8\*k are connected to the eighth storage capacitor trunk.

According to one embodiment, the periods of oscillation of first to eighth storage capacitor counter voltages supplied, respectively, by the first to eighth storage capacitor trunks are all 8 times the horizontal scanning period.

According to one embodiment, the plurality of storage 5 capacitor trunks include a first storage capacitor trunk, second storage capacitor trunk, third storage capacitor trunk, fourth storage capacitor trunk, fifth storage capacitor trunk, sixth storage capacitor trunk, seventh storage capacitor trunk, eighth storage capacitor trunk ..., (L-3)-th storage capacitor 10 trunk, (L-2)-th storage capacitor trunk, (L-1)-th storage capacitor trunk, and L-th storage capacitor trunk for a total of L storage capacitor trunks electrically independent of each other; and when ½ of the number L of the electrically independent storage capacitor trunks is an even number, i.e., when L=4, 8, 12, . . . , or the like, if the storage capacitor line connected to the storage capacitor counter electrode of the first sub-pixel of the pixel located at the intersection of an arbitrary column and a given row n among rows formed by the plurality of pixels arranged in a row-and-column matrix is designated as CSBL\_A\_n, if the storage capacitor line connected to the storage capacitor counter electrode of the second sub-pixel is designated as CSBL\_B\_n, and if k is a natural number (including 0): CSBL\_A\_n+L\*k and CSBL\_B\_n+(L/ 2)+L\*k are connected to the first storage capacitor trunk, CSBL\_B\_n+L\*k and CSBL\_A\_n+(L/2)+L\*k are connected <sup>25</sup> trunks satisfy relationships: to the second storage capacitor trunk, CSBL\_A\_n+1+L\*k and CSBL B n+(L/2)+1+L\*k are connected to the third storage capacitor trunk, CSBL\_B\_n+1+L\*k and CSBL\_A\_n+(L/ 2)+1+L\*k are connected to the fourth storage capacitor trunk,  $CSBL_A_n+2+L*k$  and  $CSBL_B_n+(L/2)+2+L*k$  are con- 30 nected to the fifth storage capacitor trunk, CSBL\_B\_n+2+ L\*k and  $CSBL\_A\_n+(L/2)+2+L*k$  are connected to the sixth capacitor trunk, CSBL\_A\_n+3+L\*k  $CSBL_B_n+(L/2)+3+L*k$  are connected to the seventh storage capacitor trunk, CSBL\_B\_n+3+L\*k and CSBL\_A\_n+(L/ 2)+3+L\*k are connected to the eighth storage capacitor trunk,  $CSBL_A_n+(L/2)-2+L*k$  and  $CSBL_B_n+L-2+L*k$  are connected to the (L-3)-th storage capacitor trunk;  $CSBL_B_n+(L/2)-2+L*k$  and  $CSBL_A_n+L-2+L*k$  are connected to the (L-2)-th storage capacitor trunk,  $CSBL_A_n+(L/2)-1+L*k$  and  $CSBL_B_n+L-1+L*k$  are connected to the (L-1)-th storage capacitor trunk, and  $CSBL_B_n+(L/2)-1+L*k$  and  $CSBL_A_n+L-1+L$  k are connected to the L-th storage capacitor trunk.

According to one embodiment, the periods of oscillation of first to L-th storage capacitor counter voltages supplied,  $^{\rm 45}$  respectively, by the first to L-th storage capacitor trunks are all L times the horizontal scanning period.

A fourth aspect of the present invention provides a liquid crystal display, comprising a plurality of pixels each of which has a liquid crystal layer and a plurality of electrodes for 50 applying a voltage to the liquid crystal layer and which are arranged in a matrix of rows and columns, wherein: each of the plurality of pixels has a first sub-pixel and a second sub-pixel which can apply mutually different voltages to the liquid crystal layer, where the first sub-pixel has a higher brightness than the second sub-pixel in certain gradations; the first sub-pixel and the second sub-pixel each comprise: a liquid crystal capacitor formed by a counter electrode and a sub-pixel electrode opposing the counter electrode via the liquid crystal layer, and a storage capacitor formed by a storage capacitor electrode connected electrically to the subpixel electrode, an insulating layer, and a storage capacitor counter electrode opposing the storage capacitor electrode via the insulating layer; the counter electrode is a single electrode shared by the first sub-pixel and the second subpixel, and the storage capacitor counter electrodes of the first 65 sub-pixel and the second sub-pixel are electrically independent of each other; the liquid crystal display further comprises

a plurality of storage capacitor trunks electrically independent of each other, each of storage capacitor trunks being electrically connected to any of the storage capacitor counter electrodes of the first sub-pixel and the second sub-pixel in the plurality of pixels via a storage capacitor line, the storage capacitor counter electrode of the first sub-pixel of one of two adjacent pixels in the column direction is connected to a storage capacitor line electrically equivalent to the storage capacitor counter electrode of the second sub-pixel of the other; and the number of the storage capacitor trunks electrically independent of each other among a plurality of storage capacitor trunks is L or more (L is an even number), storage capacitor counter voltage supplied by each of the storage capacitor trunks is oscillating voltage, and the period of oscillation is 2\*K\*L (K is a positive integer) times a horizontal scanning period.

According to one embodiment, if the storage capacitor line connected to the storage capacitor counter electrode of the first sub-pixel of the pixel located at the intersection of an arbitrary column and a given row n among rows formed by the plurality of pixels arranged in a row-and-column matrix is designated as CSBL\_(n) A and the storage capacitor line connected to the storage capacitor counter electrode of the second sub-pixel is designated as CSBL\_(n)B, CS buslines connected to the L electrically independent storage capacitor trunks satisfy relationships:

```

CSBL_{(p+2*(1-1))B,(p+2*(1-1)+1)A}

CSBL_{(p+2*(2-1))}B, (p+2*(2-1)+1)A,

CSBL_{(p+2*(3-1))}B, (p+2*(3-1)+1)A,

CSBL_{-}(p+2*(K-1))B,(p+2*(K-1))+1)A and

CSBL_{p+2*(1-1)+K*L+1}B,(p+2*(1-1))+K*L+2)A,

CSBL\_(p+2*(2-1)+K*L+1)B, (p+2*(2-1))+K*L+2)A,

CSBL_{p+2*(3-1)+K*L+1)B,(p+2*(3-1))+K*L+2)A,

CSBL\_(p+2*(K-1)+K*L+1)B, (p+2*(3-1)+L+2)A;

CSBL_{-}(p+2*(1-1)+1)B, (p+2*(1-1)+2)A,

CSBL_{(p+2*(2-1)+1)}B, (p+2*(2-1)+2)A,

CSBL_{-}(p+2*(3-1)+1)B, (p+2*(3-1)+2)A,

CSBL (p+2*(K-1)+1)B, (p+2*(K-1)+2)A

CSBL\_(p+2*(1-1)+K*L)B, (p+2*(1-1)+K*L+1)A,

CSBL (p+2*(2-1)+K*L)B, (p+2*(2-1)+K*L+1)A,

CSBL\_(p+2*(3-1)+K*L)B, (p+2*(3-1)+K*L+1)A,

CSBL_{p+2*(K-1)+K*L}B, (p+2*(K-1)+K*L+1)A,

```

where p=1, 3, 5, or the like, or p=0, 2, 4, or the like.

According to one embodiment, K is 1 or 2, and L is any of 6, 10, and 12

According to one embodiment, preferably the storage capacitor line is placed between two adjacent pixels in the column direction.

According to one embodiment, the liquid crystal display comprises: two switching elements provided for the first subpixel and the second sub-pixel, respectively; and a scan line commonly connected to the two switching elements, wherein the common scan line is placed between the first sub-pixel and the second sub-pixel.

According to one embodiment, the plurality of storage capacitor trunks are an even number of storage capacitor trunks grouped into pairs of storage capacitor trunks which supply storage capacitor counter voltages whose oscillations are 180 degrees out of phase with each other.

According to one embodiment, in any two adjacent pixels in the column direction, the storage capacitor counter electrode of the first sub-pixel of one pixel and the storage capacitor counter electrode of the second sub-pixel of the other pixel are connected to a common storage capacitor line.

According to one embodiment, duty ratios of the storage capacitor counter voltages are all 1:1.

According to one embodiment, the first sub-pixel in the any 25 of the pixels is arranged in such a way as to be adjacent to the second sub-pixel of the pixel adjacent to the any of the pixels in the column direction and in each of the plurality of pixels, the first sub-pixel is arranged in such a way as to be adjacent to the second sub-pixel in the column direction.

According to one embodiment, the first sub-pixel and the second sub-pixel are approximately equal in area.

According to one embodiment, the second sub-pixel is larger in area than the first sub-pixel.

The first aspect of the present invention can reduce the  $^{35}$  viewing angle dependence of  $\gamma$  characteristics in a liquid crystal display. In particular, it can achieve extremely high display quality by improving  $\gamma$  characteristics of liquid crystal displays with a wide viewing angle such as MAV or ASV liquid crystal displays.

The second aspect of the present invention can reduce flickering on a liquid crystal display driven by alternating current. By combining the first and second aspects of the present invention, it is possible to provide a liquid crystal display with reduced flickering, improved viewing angle 45 characteristics of γ characteristics, and high quality display.

The third aspect of the present invention can increase the periods of oscillation of the voltages (oscillating voltages) applied to the storage capacitor counter electrodes in the liquid crystal display according to the second aspect. Thus, it is possible to provide a liquid crystal display which is suitable for improving viewing angle characteristics of a large or high-resolution liquid crystal display by dividing one pixel into two or more sub-pixels and illuminating the sub-pixels at different brightness levels.

The fourth aspect of the present invention can supply oscillating voltages to the sub-pixels of adjacent pixels in the column direction using common storage capacitor lines (CS buslines) in addition to being able to increase the periods of oscillation of the voltages (oscillating voltages) applied to the 60 storage capacitor counter electrodes as is the case with the third aspect. Consequently, the storage capacitor lines can also serve as black matrices (BM) if placed between pixels adjacent to each other in the column direction. Thus, the fourth aspect, which can omit the black matrices that need to 65 be provided separately in the case of the liquid crystal display according to the third aspect as well as reduce the number of

12

CS buslines compared to the third aspect, has the advantage of being able to increase the aperture ratio of pixels.

### BRIEF DESCRIPTION OF THE DRAWINGS

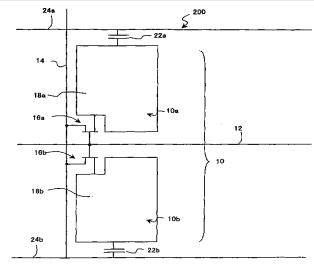

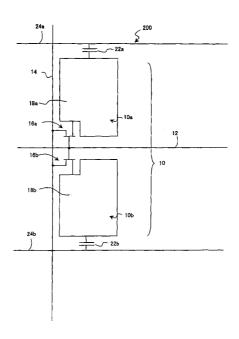

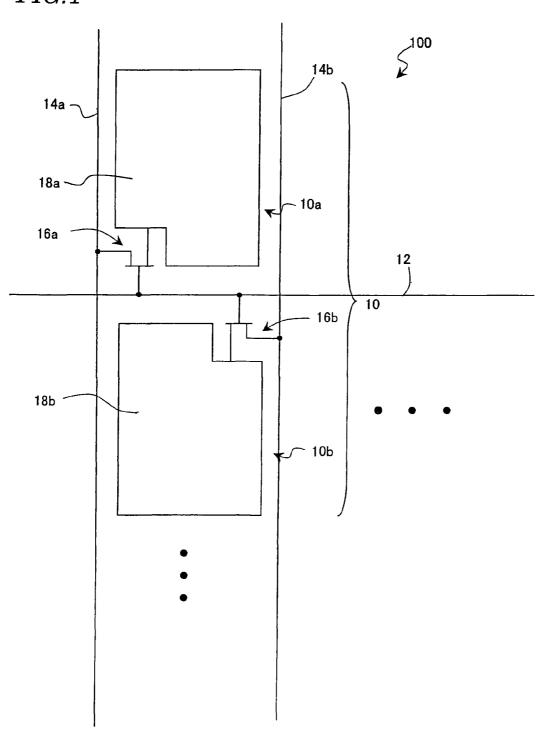

FIG. 1 is a diagram schematically showing a pixel configuration of a liquid crystal display 100 according to an embodiment in a first aspect of the present invention.

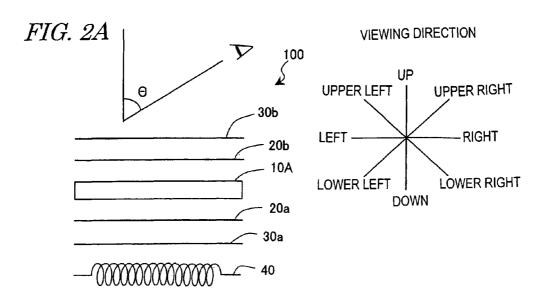

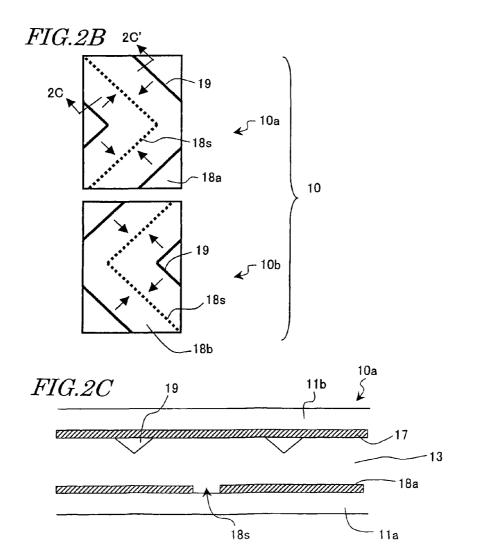

FIGS. 2A to 2C are schematic diagrams showing a structure of a liquid crystal display according to the embodiment of the present invention.

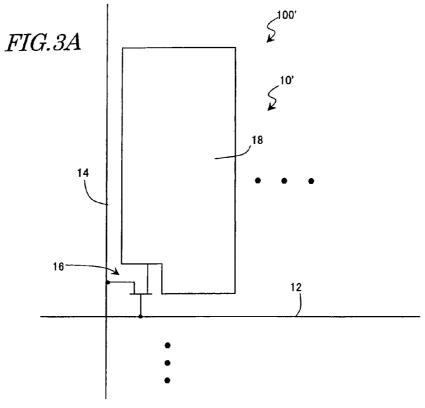

FIGS. 3A to 3C are diagrams schematically showing a structure of a conventional liquid crystal display 100'.

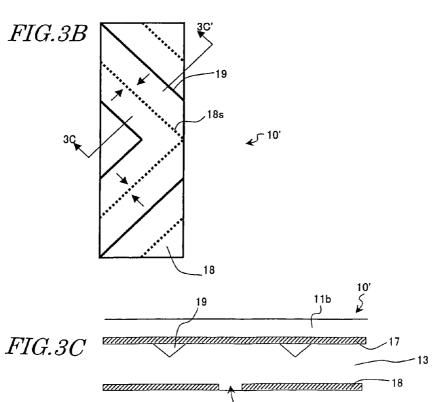

FIGS. 4A to 4C are diagrams illustrating display characteristics of an MVA liquid crystal display, where FIG. 4A is a graph showing dependence of transmittance on applied voltage, FIG. 4B is a diagram showing transmittances in FIG. 4A after being normalized with respect to transmittance in white mode, and FIG. 4C is a diagram showing γ characteristics.

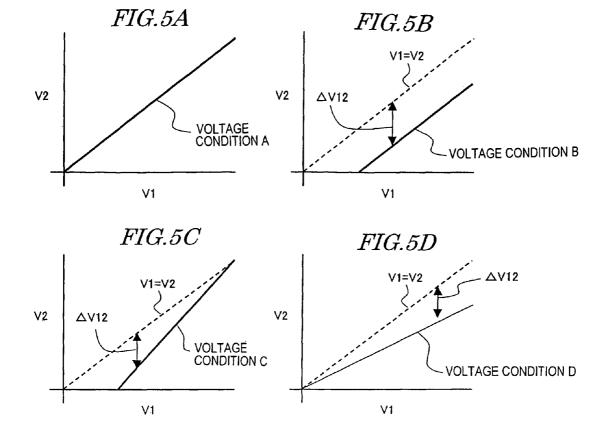

FIGS. 5A to 5D are diagrams showing conditions A to D, respectively, of voltages to be applied to liquid crystal layers of sub-pixels obtained by dividing pixels.

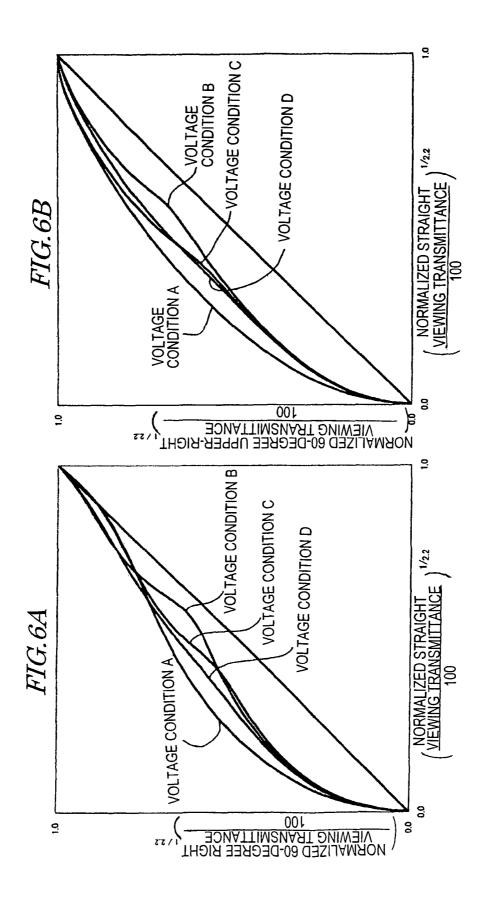

FIGS. **6**A to **6**B are graphs showing  $\gamma$  characteristics obtained under voltage conditions A to D, shown in FIG. **5**, where FIG. **6**A shows right side 60-degree viewing  $\gamma$  characteristics and FIG. **6**B shows upper-right side 60-degree viewing  $\gamma$  characteristics.

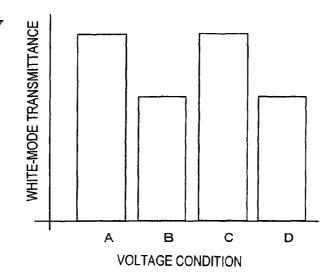

FIG. 7 is a graph showing white-mode transmittance (frontal viewing) obtained under voltage conditions A to D.

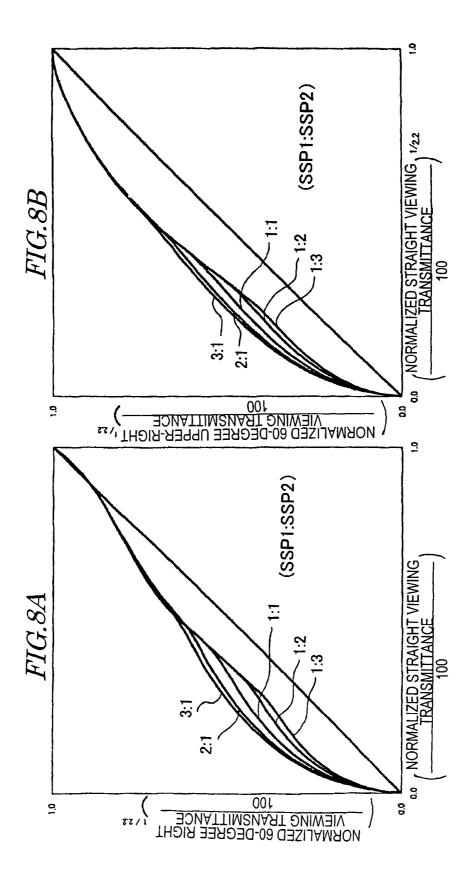

FIGS. 8A to 8B are graphs illustrating effects of area ratios between sub-pixels on  $\gamma$  characteristics under voltage condition C according to the embodiment of the present invention, where FIG. 8A shows right side 60-degree viewing  $\gamma$  characteristics and FIG. 6B shows upper-right side 60-degree viewing  $\gamma$  characteristics.

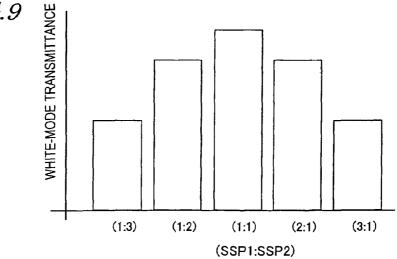

FIG. 9 is a diagram showing relationship between white-mode transmittance (frontal viewing) and sub-pixel area ratios under voltage condition C according to the embodiment of the present invention.

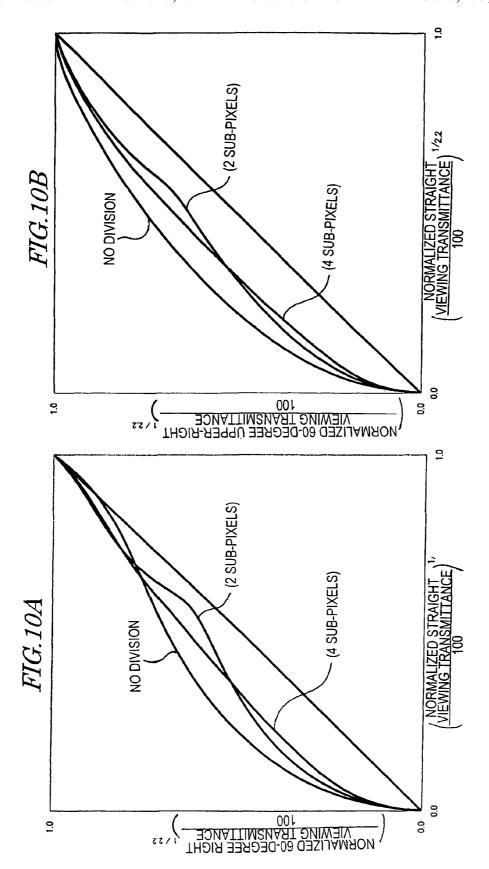

FIGS. 10A to 10B are diagrams illustrating effects of subpixel counts on  $\gamma$  characteristics under voltage condition B according to the embodiment of the present invention, where FIG. 10A shows right side 60-degree viewing  $\gamma$  characteristics and FIG. 10B shows upper-right side 60-degree viewing  $\gamma$  characteristics.

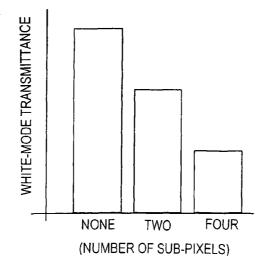

FIG. 11 is a diagram showing relationship between white-mode transmittance (frontal viewing) and sub-pixel counts under voltage condition B according to the embodiment of the present invention.

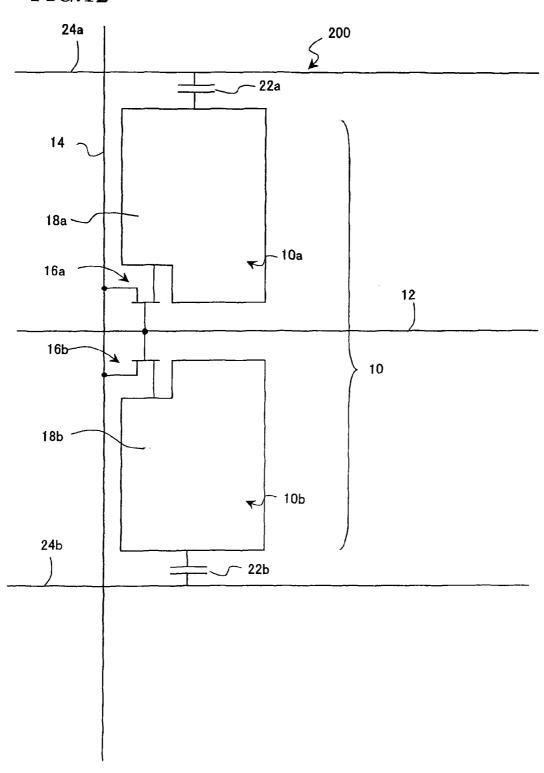

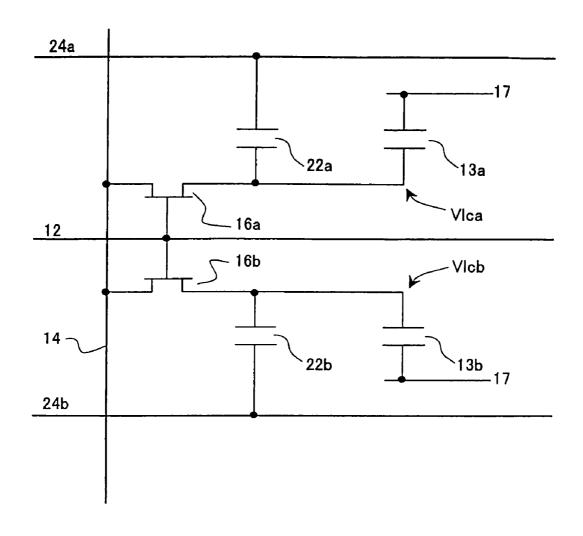

FIG. 12 is a schematic diagram showing a pixel structure of a liquid crystal display 200 according to another embodiment of the present invention.

FIG. 13 is a diagram showing an equivalent circuit for a pixel of the liquid crystal display 200.

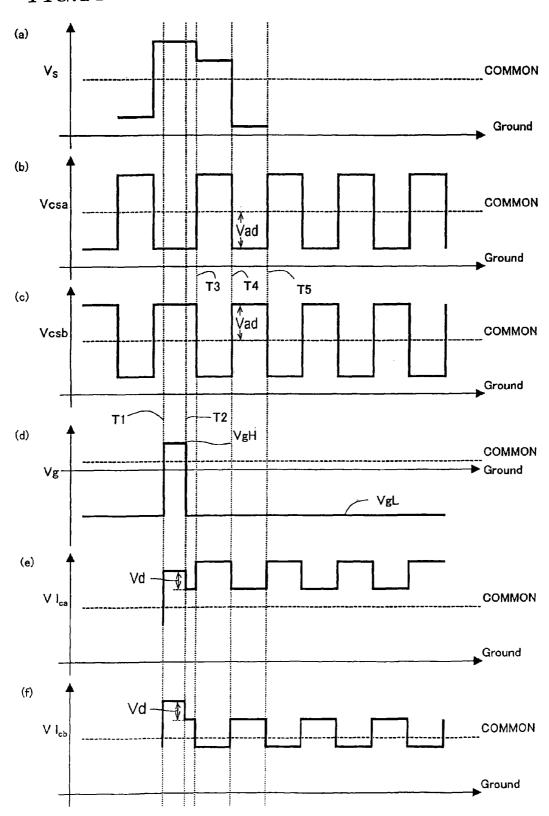

FIG. 14 is a diagram showing various voltage waveforms (a)-(f) for driving the liquid crystal display 200.

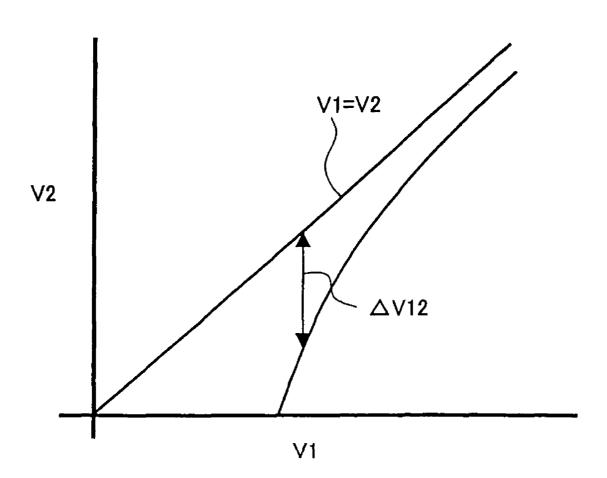

FIG. 15 is a diagram showing relationship between voltages applied to liquid crystal layers of sub-pixels in the liquid crystal display 200.

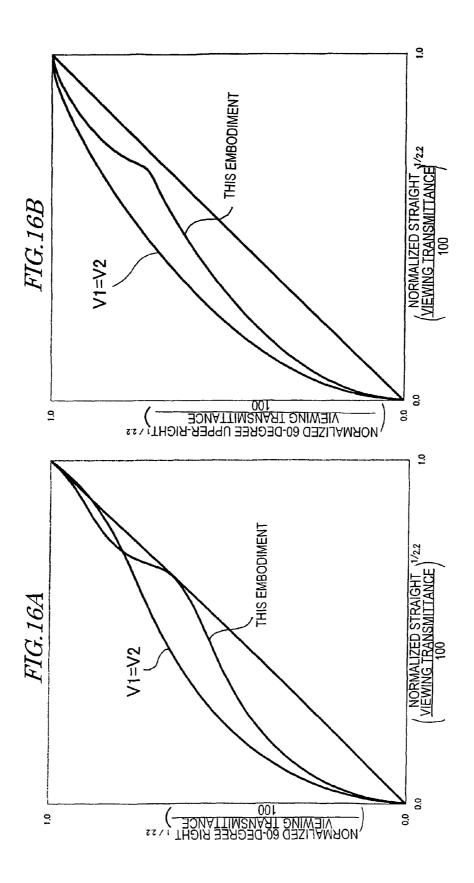

FIGS. 16A to 16B are diagrams showing  $\gamma$  characteristics of the liquid crystal display 200, where FIG. 16A shows right side 60-degree viewing  $\gamma$  characteristics and FIG. 16B shows upper-right side 60-degree viewing  $\gamma$  characteristics.

FIG. 17 is a diagram schematically showing a pixel arrangement of a liquid crystal display according to a second aspect of the present invention.

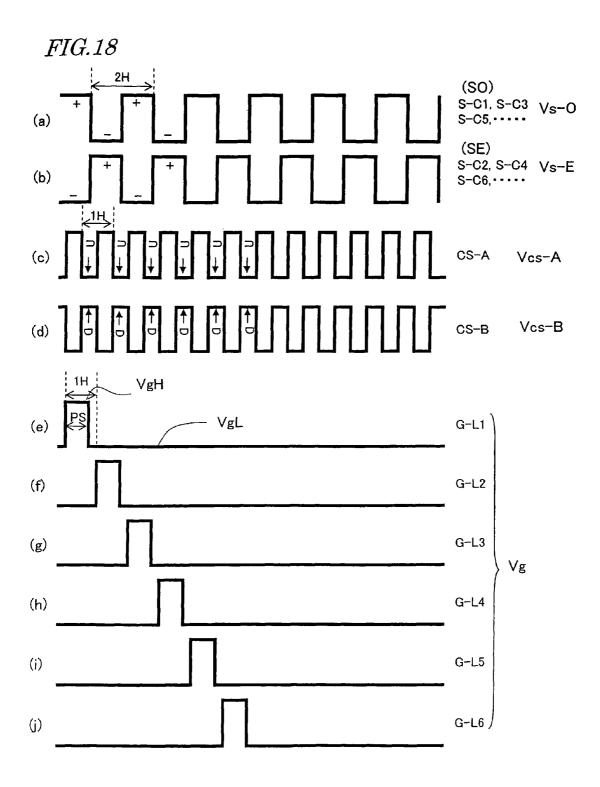

FIG. **18** is a diagram showing waveforms (a)-(j) of various voltages (signals) for driving the liquid crystal display which has the configuration shown in FIG. **17**.

FIG. **19** is a diagram schematically showing a pixel arrangement of a liquid crystal display according to another <sup>5</sup> embodiment of the present invention.

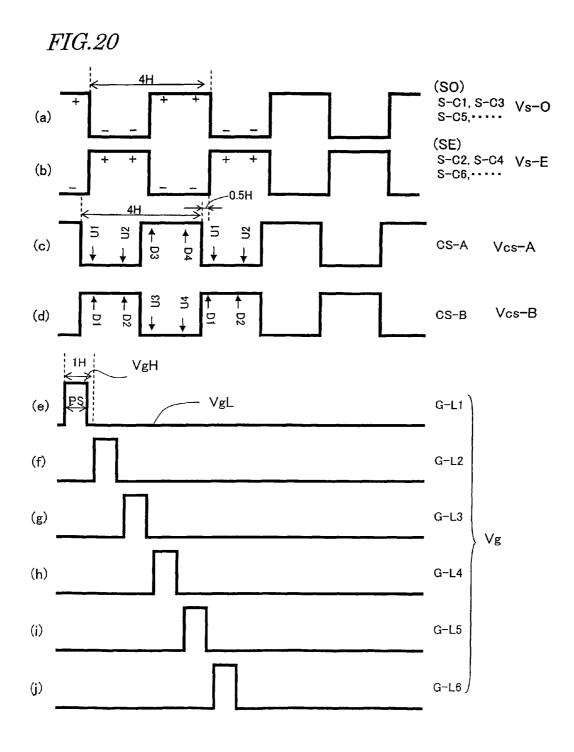

FIG. 20 is a diagram showing waveforms (a)-(j) of various voltages (signals) for driving the liquid crystal display which has the configuration shown in FIG. 19.

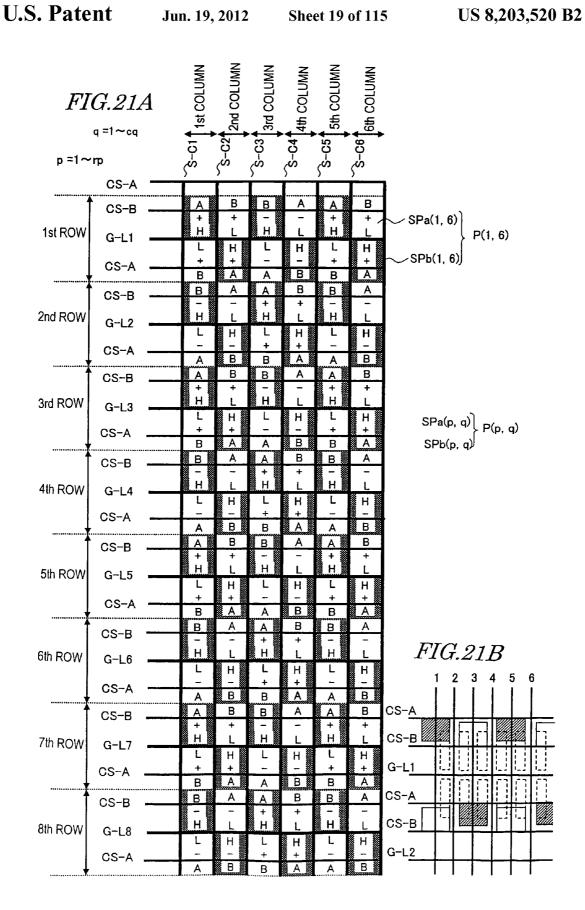

FIG. 21A is a diagram schematically showing a pixel arrangement of a liquid crystal display according to another embodiment of the present invention and FIG. 21B is a diagram schematically showing an arrangement of its storage capacitor lines and storage capacitor electrodes.

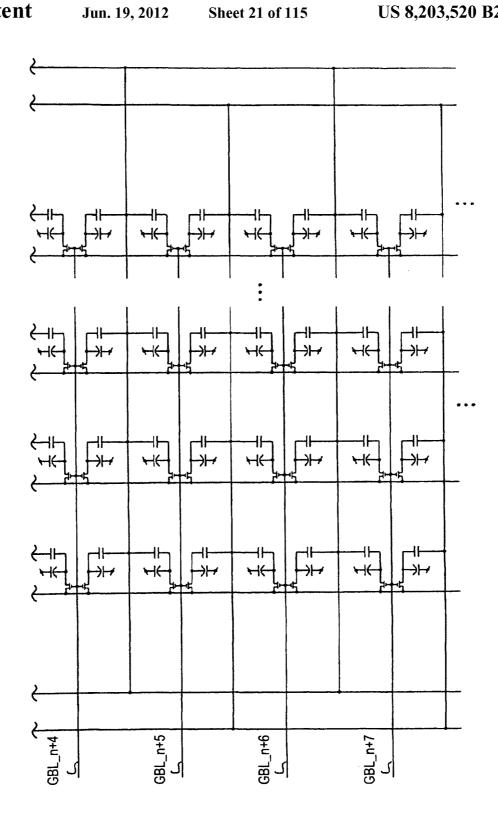

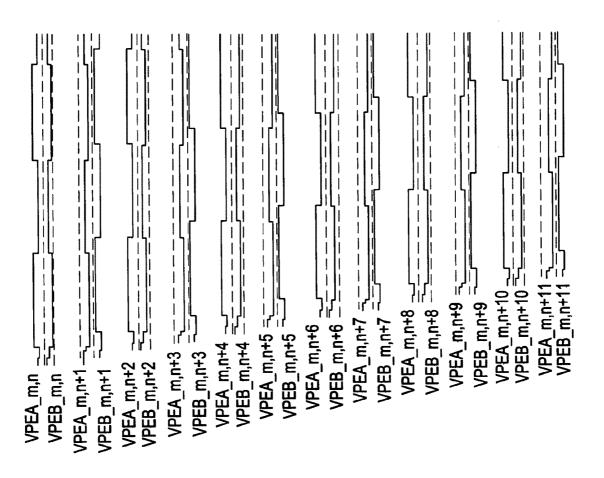

FIGS. 22-1 to 22-2 are an equivalent circuit diagram of a certain area of a liquid crystal display according to a second aspect of the present invention.

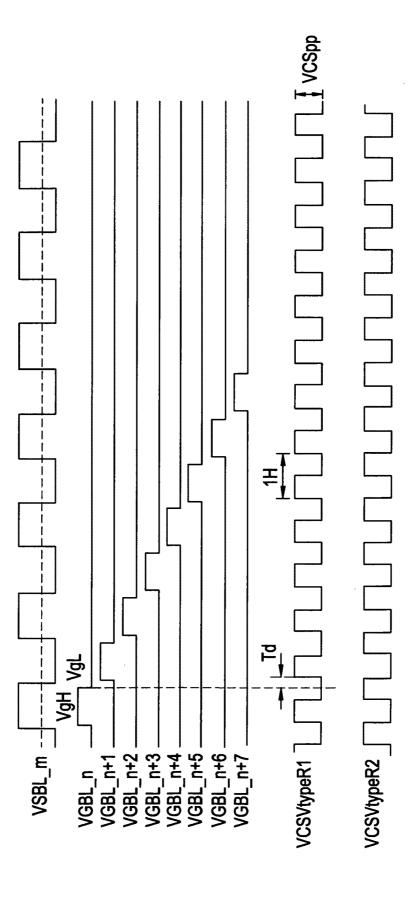

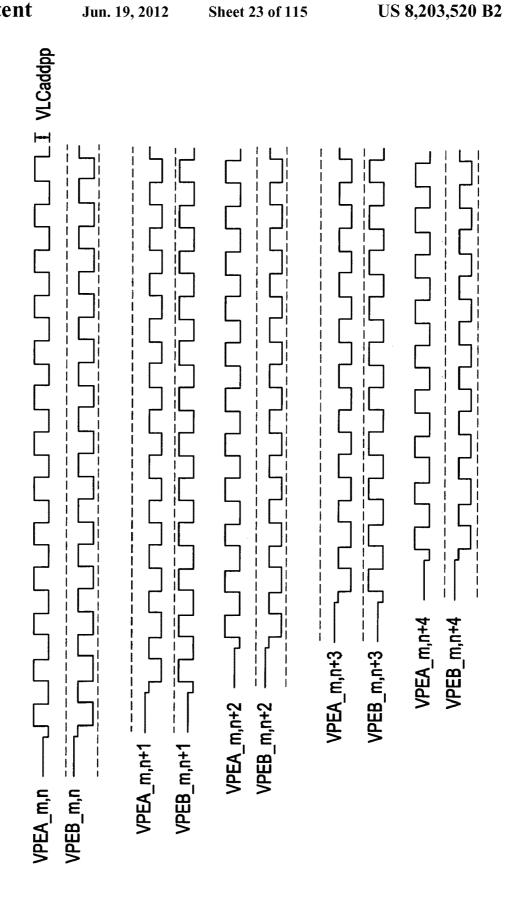

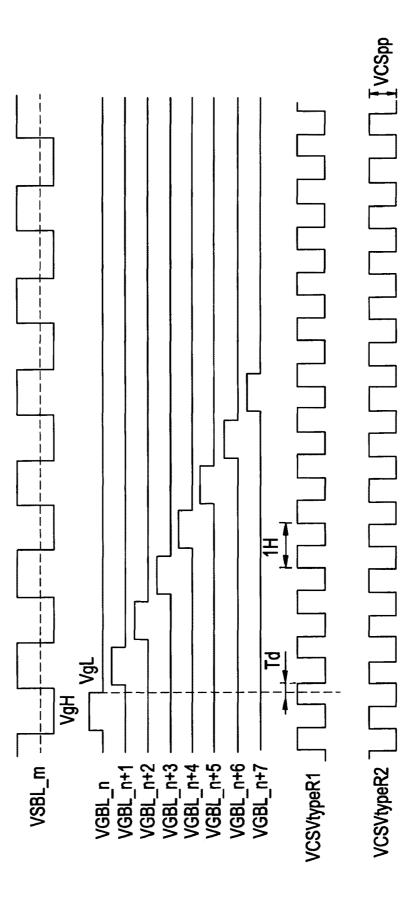

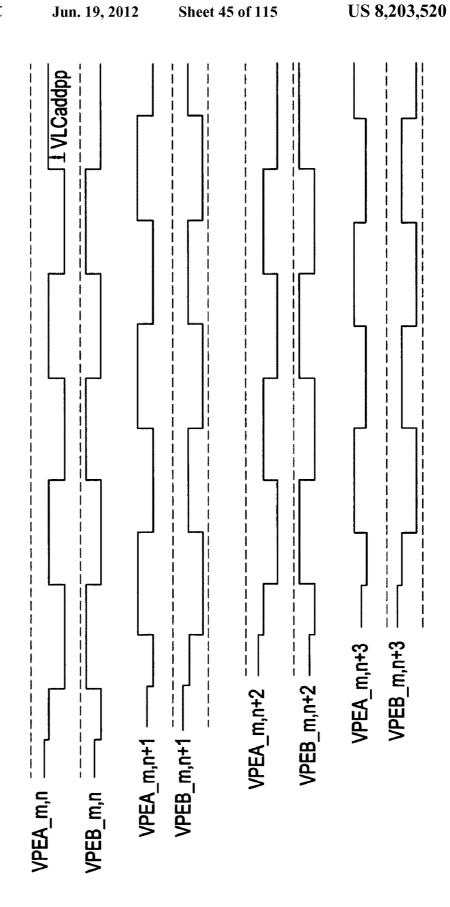

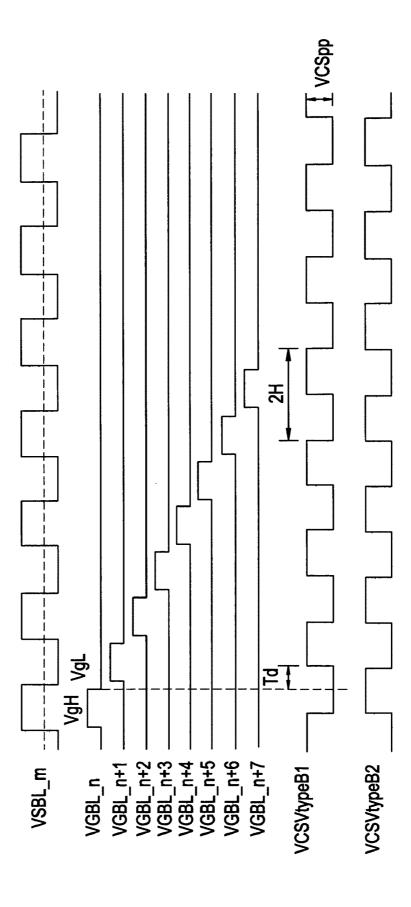

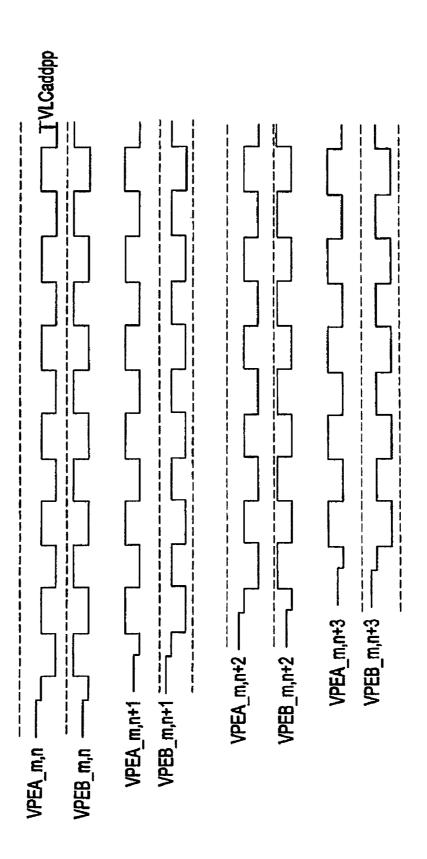

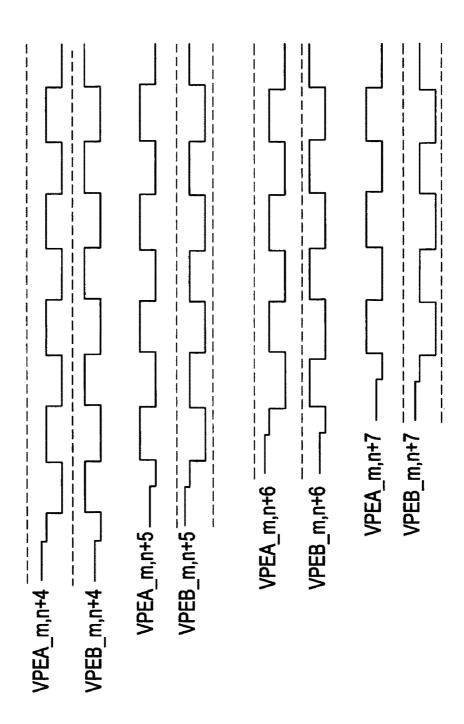

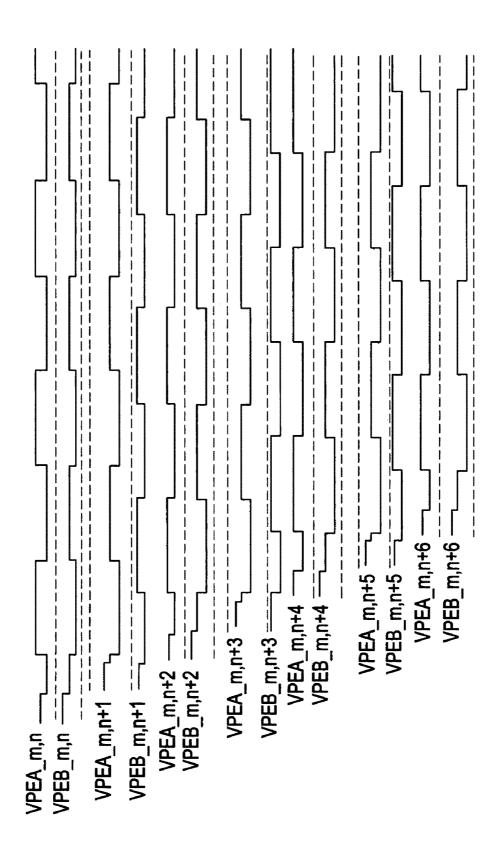

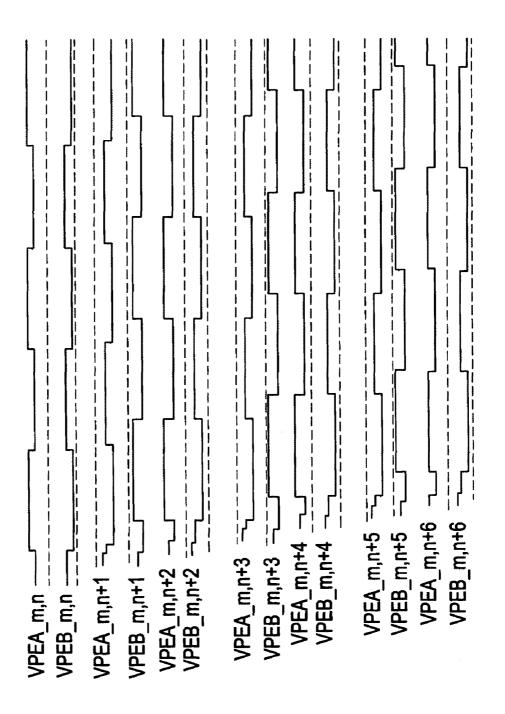

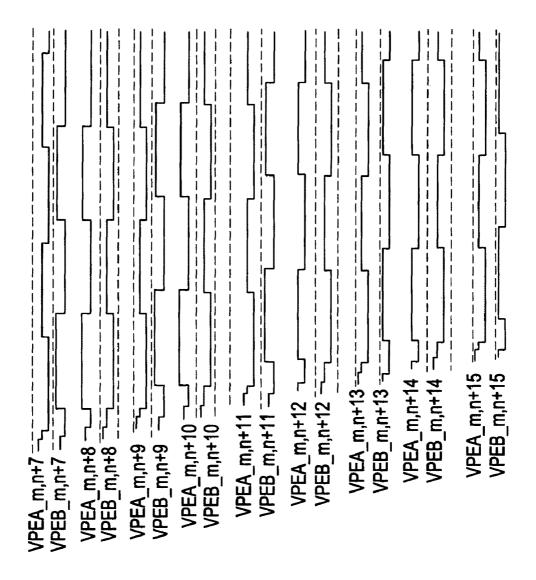

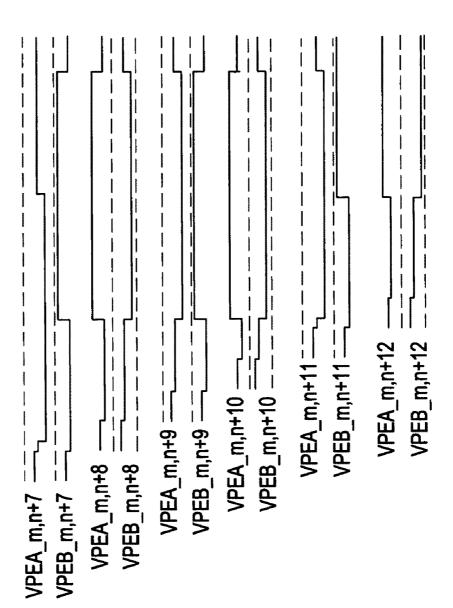

FIGS. **23**A-**1** to **23**A-**3** are a diagram showing periods and phases of oscillation of oscillating voltages supplied to CS <sub>20</sub> buslines in terms of voltage waveforms of gate buslines as well as showing voltages of sub-pixel electrodes in the liquid crystal display shown in FIG. **22**.

FIGS. 23B-1 to 23B-3 are a diagram showing periods and phases of oscillation of oscillating voltages supplied to the CS <sup>25</sup> buslines in terms of voltage waveforms of gate buslines as well as showing voltages of sub-pixel electrodes in the liquid crystal display shown in FIG. 22 (voltages applied to liquid crystal layers have polarity opposite to that in FIG. 23A).

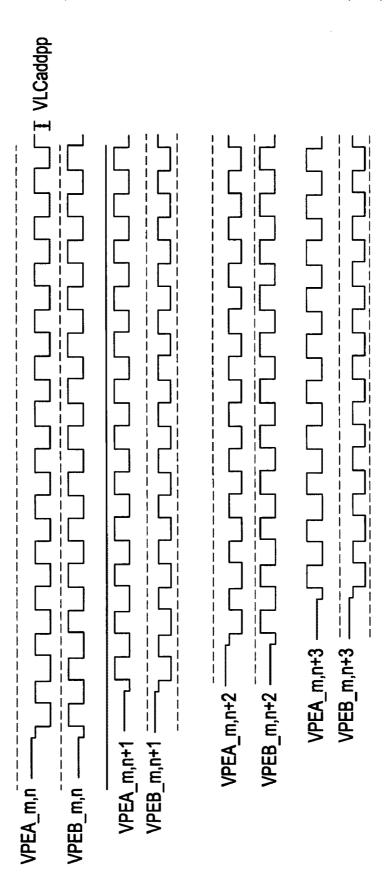

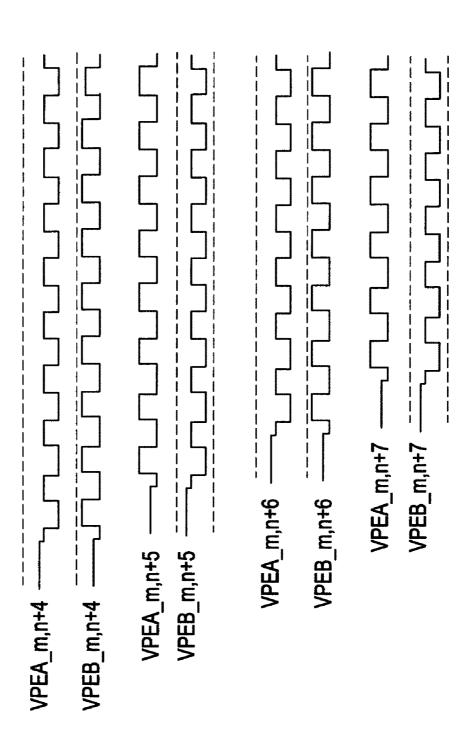

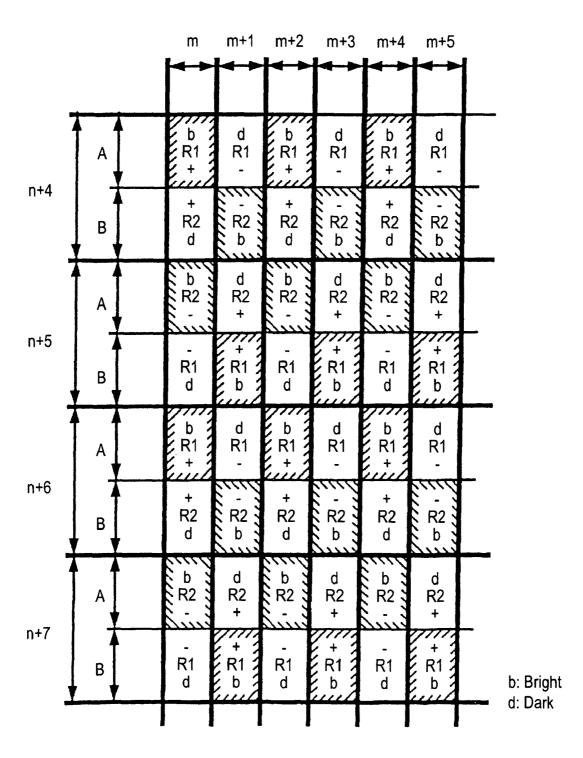

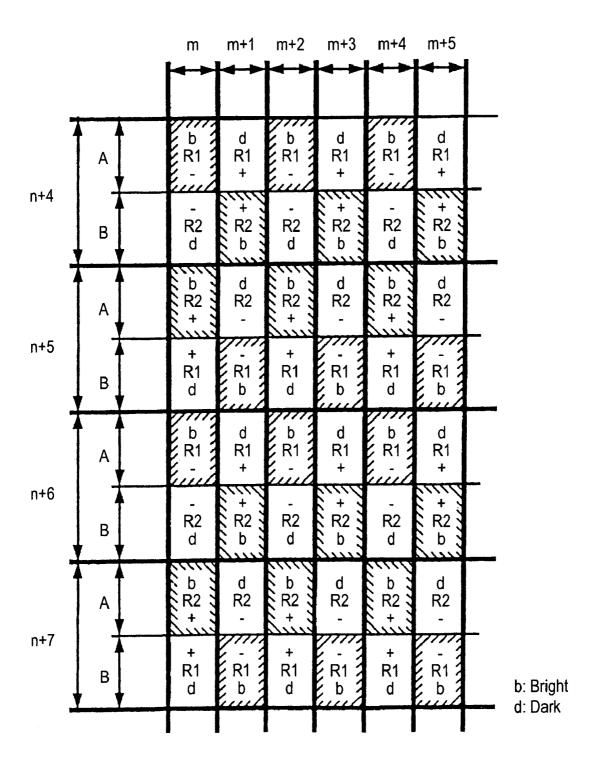

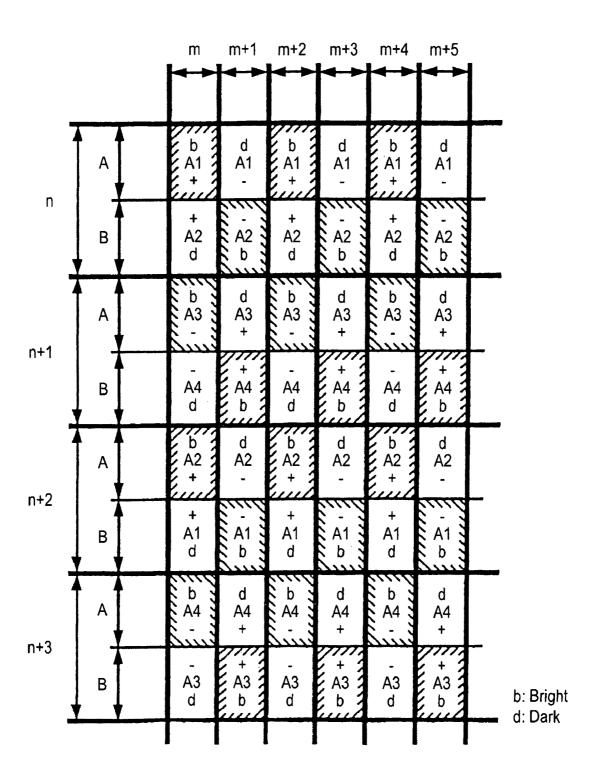

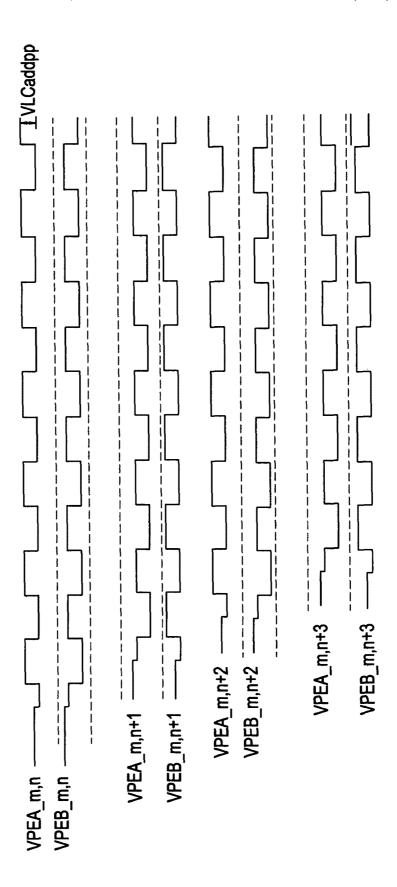

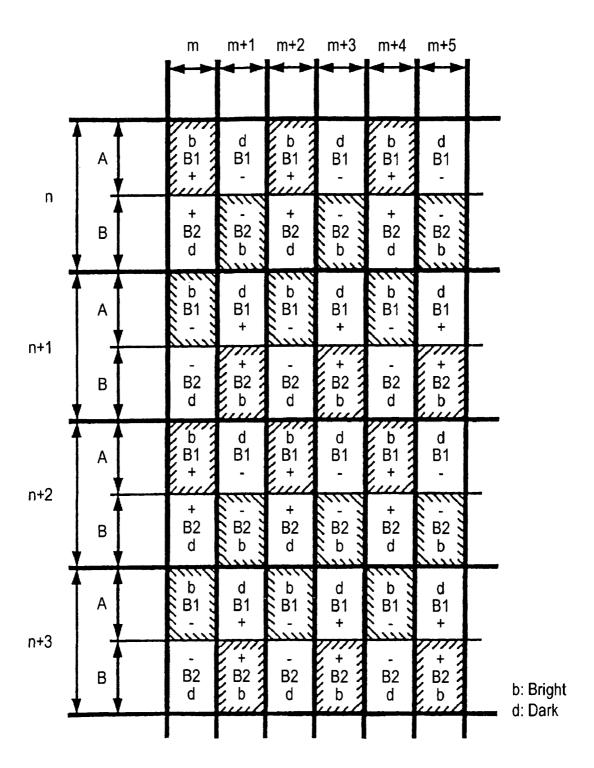

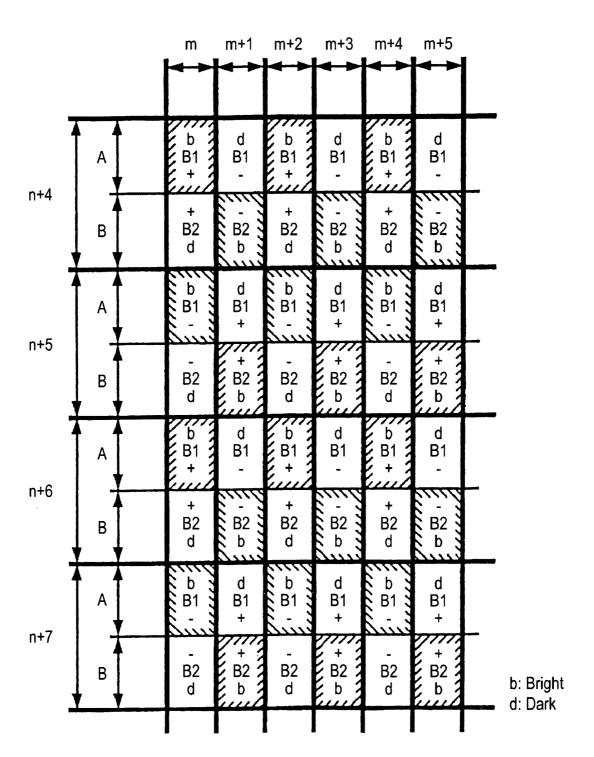

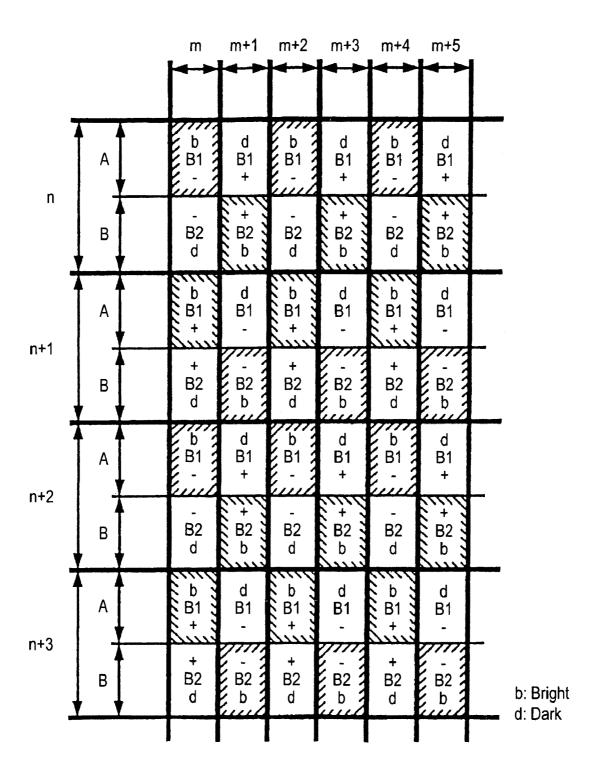

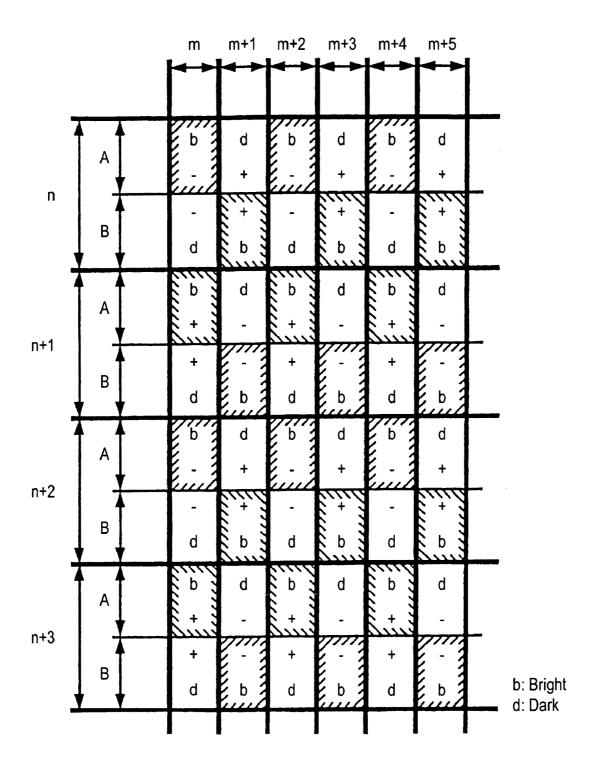

FIGS. 24A-1 to 24A-2 are a schematic diagram showing driving states of the liquid crystal display shown in FIG. 22 (where the voltages in FIG. 23A are used).

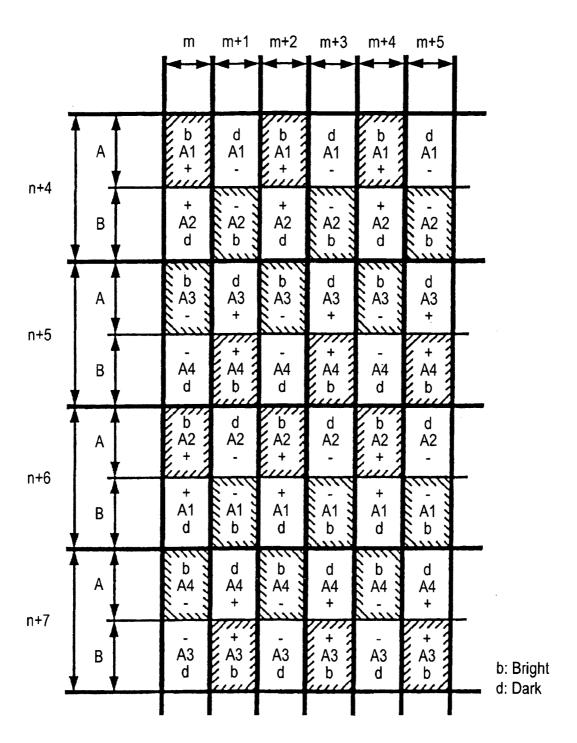

FIGS. **24**B-**1** and **24**B-**2** are a schematic diagram showing driving states of the liquid crystal display shown in FIG. **22** (where the voltages in FIG. **23**B are used).

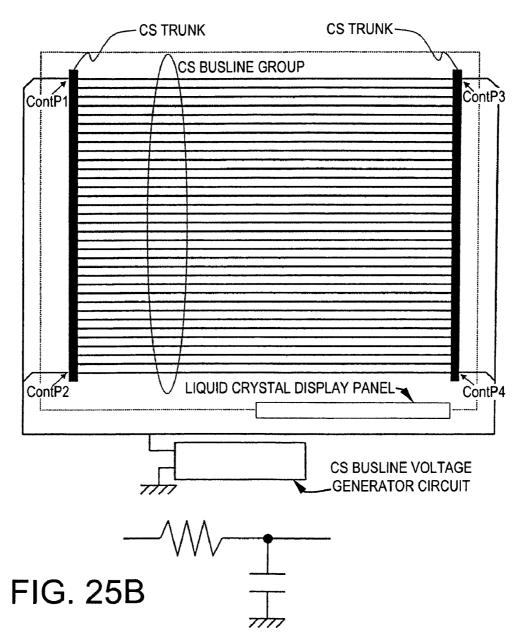

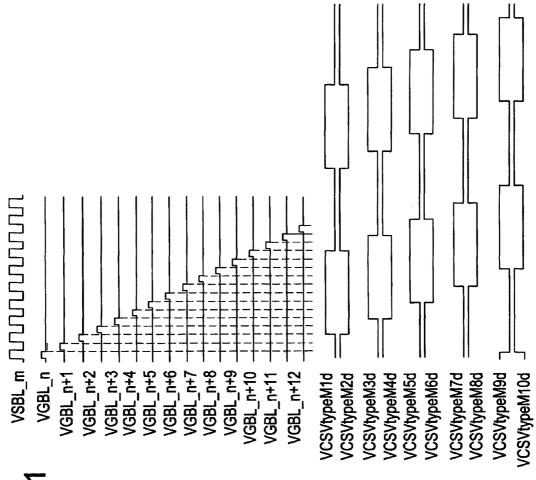

FIG. 25A is a diagram schematically showing a configuration used to supply oscillating voltages to CS buslines in a liquid crystal display according to an embodiment of the second aspect of the present invention and 25B is a diagram 40 schematically showing an equivalent circuit which approximates electrical load impedance of the liquid crystal display.

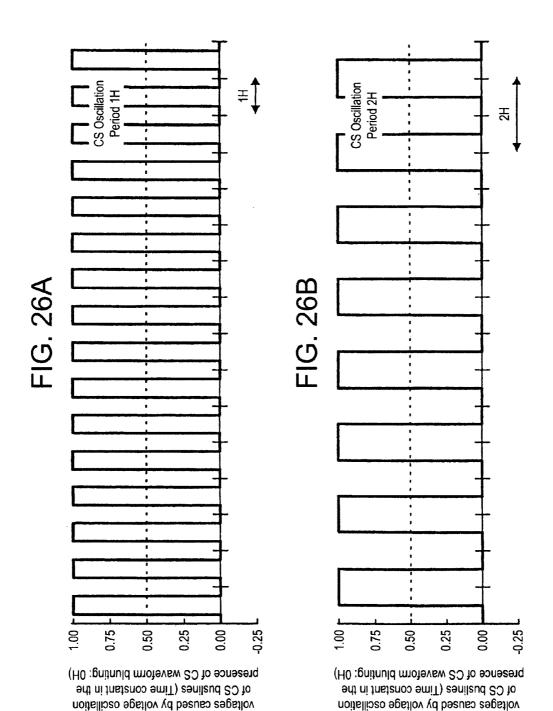

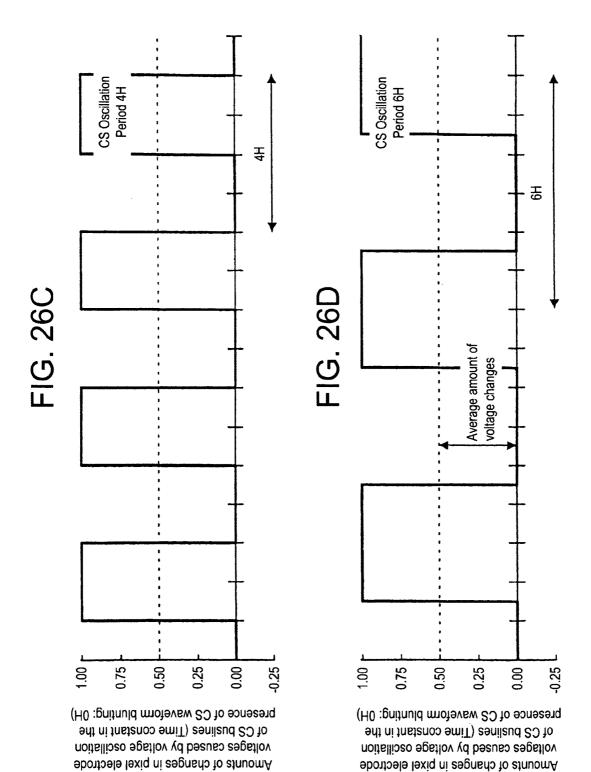

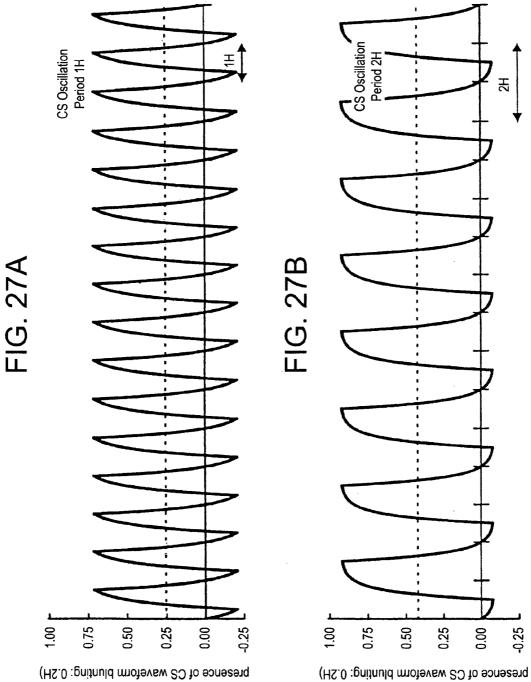

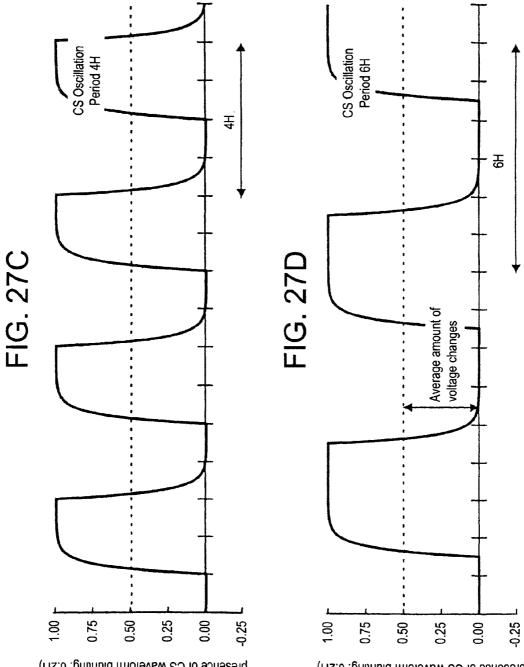

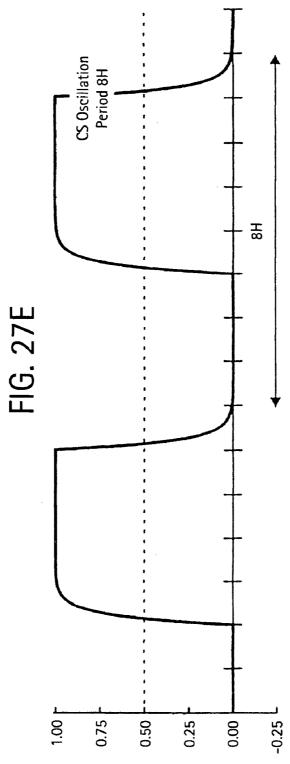

FIGS. **26**A-**26**D are a diagram schematically showing oscillating voltage waveforms (a) to (e) of sub-pixel electrodes without CS voltage waveform blunting.

FIGS. 27A to 27E are a diagram schematically showing oscillating voltage waveforms (a) to (e) of sub-pixel electrodes with waveform blunting corresponding to a CR time constant of "0.2H".

FIG. **28** is a graph showing relationship of the average 50 value and effective value of oscillating voltages calculated based on the waveforms in FIGS. **26** and **27** vs. the oscillation period of CS busline voltages.

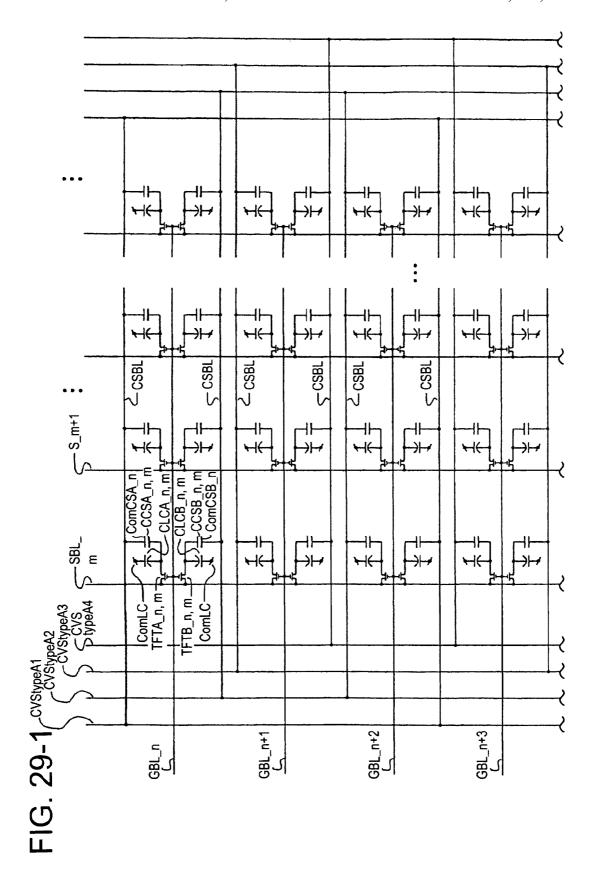

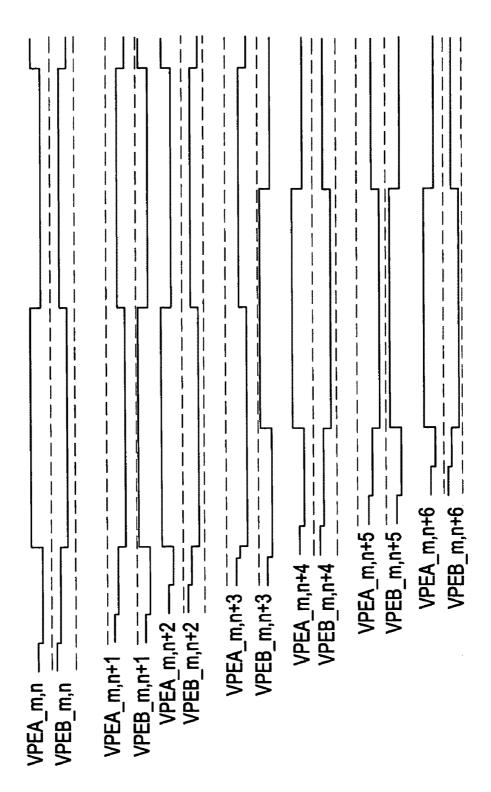

FIGS. 29-1 to 29-2 are a diagram schematically showing an equivalent circuit of a liquid crystal display according to an 55 embodiment of a third aspect of the present invention.

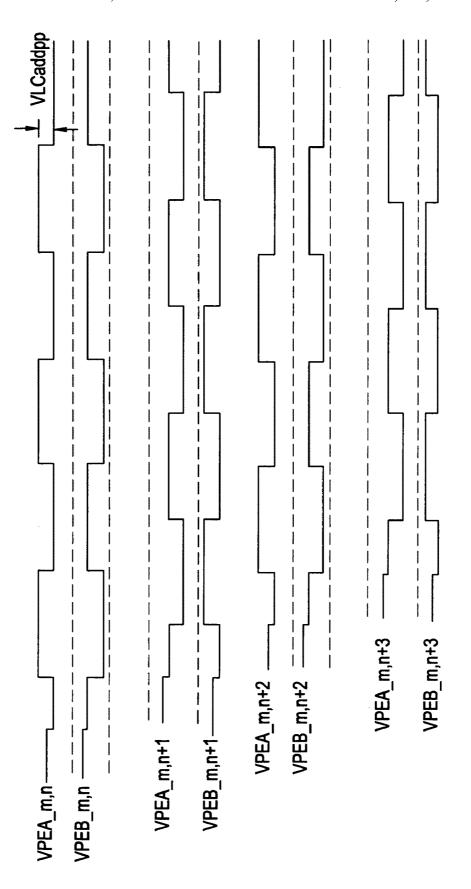

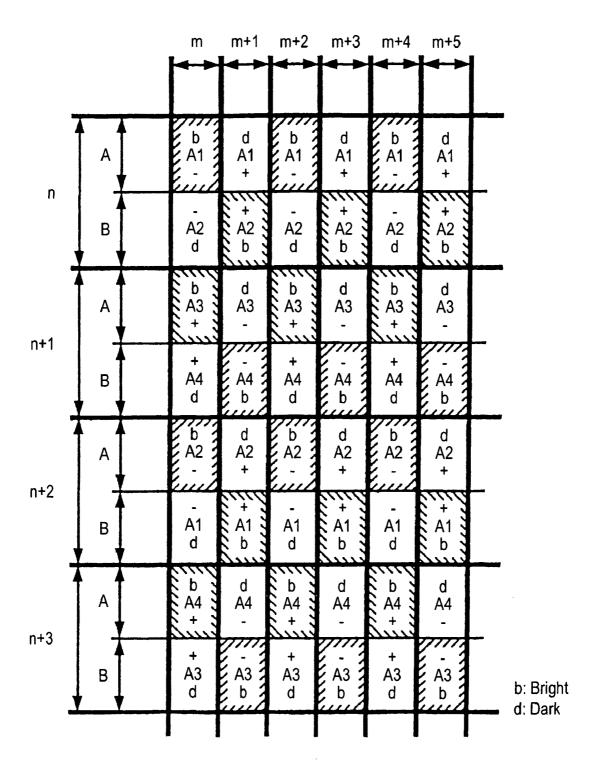

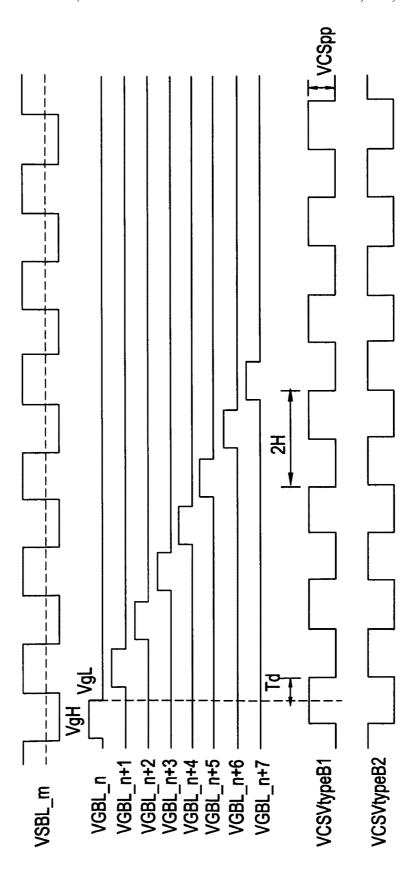

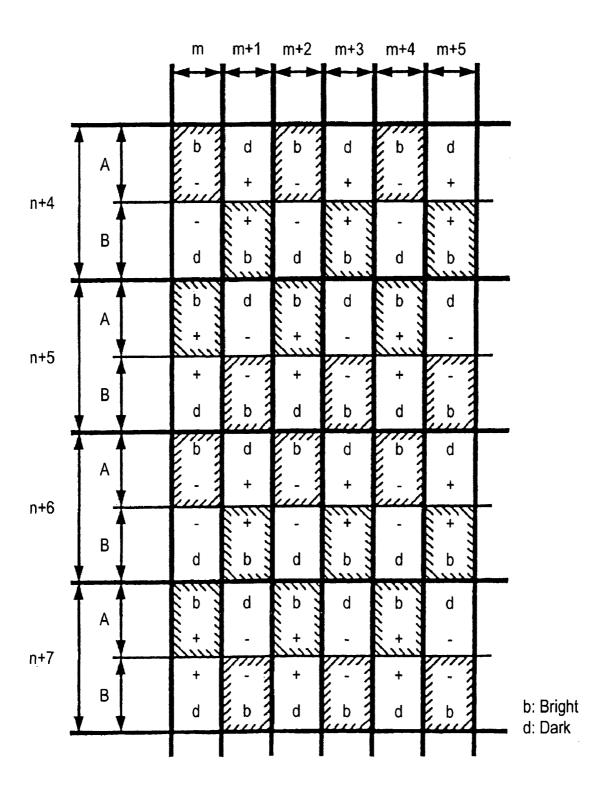

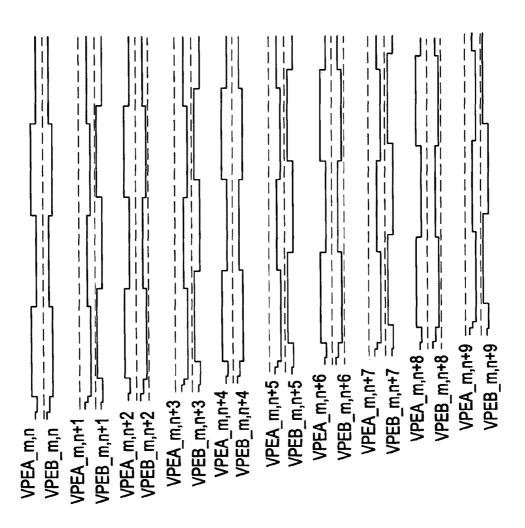

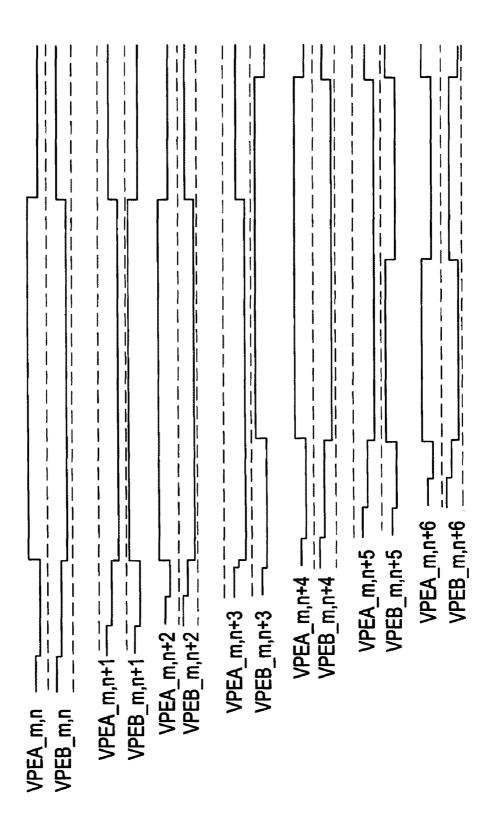

FIGS. **30**A-**1** to **30**A-**3** are a diagram showing periods and phases of oscillation of oscillating voltage supplied to the CS buslines in terms of voltage waveforms of gate buslines as well as showing voltages of sub-pixel electrodes in the liquid 60 crystal display shown in FIG. **29**.

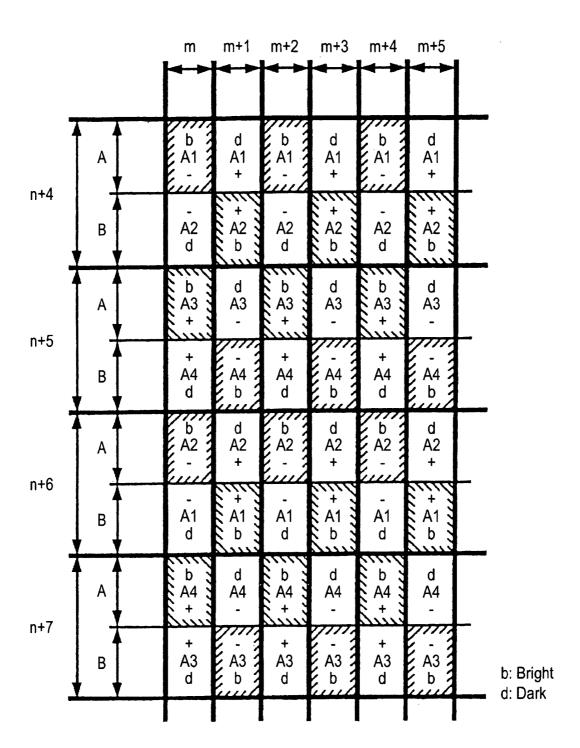

FIGS. 30B-1 to 30B-3 are a diagram showing periods and phases of oscillation of oscillating voltage supplied to the CS buslines in terms of voltage waveforms of the gate buslines as well as showing voltages of sub-pixel electrodes in the liquid 65 crystal display shown in FIG. 29 (voltages applied to liquid crystal layers have polarity opposite to that in FIG. 30A).

14

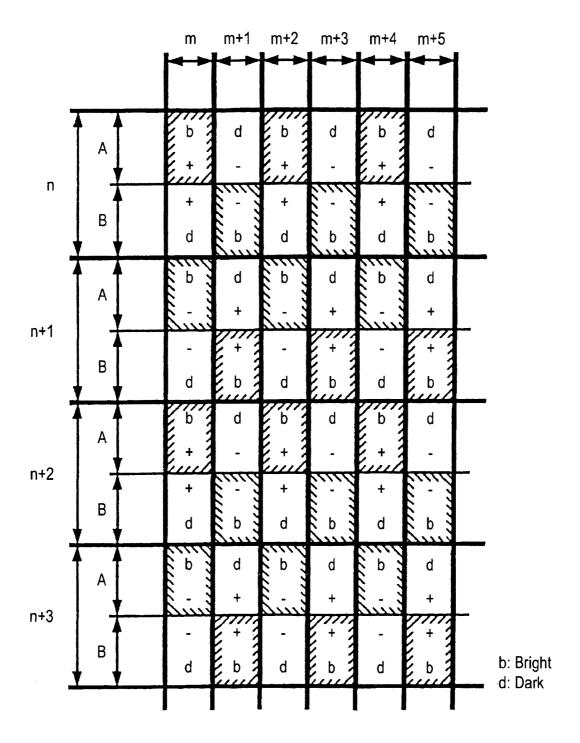

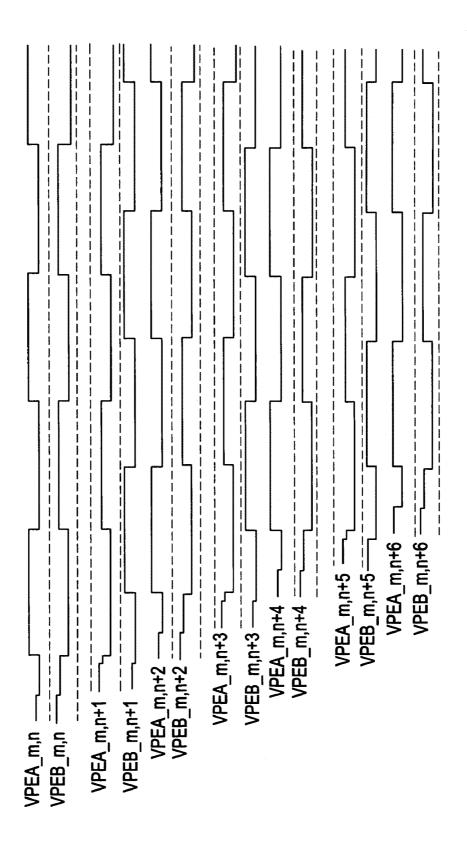

FIGS. **31**A-**1** to **31**A-**2** are a diagram showing driving states of the liquid crystal display shown in FIG. **29** (where the voltages in FIG. **30**A are used).

FIGS. 31B-1 to 31B-2 are a diagram showing driving states of the liquid crystal display shown in FIG. 29 (where the voltages in FIG. 30B are used).

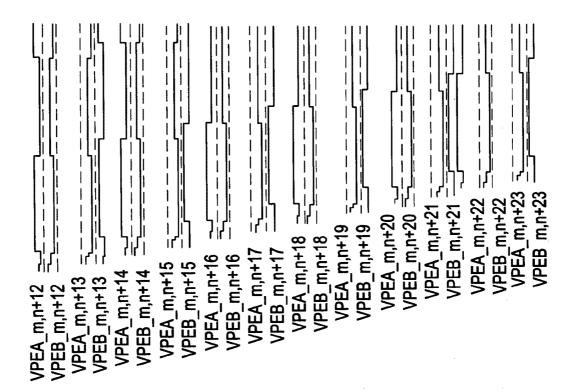

FIGS. 32-1 to 32-2 are a diagram schematically showing an equivalent circuit of a liquid crystal display according to another embodiment of the third aspect of the present invention

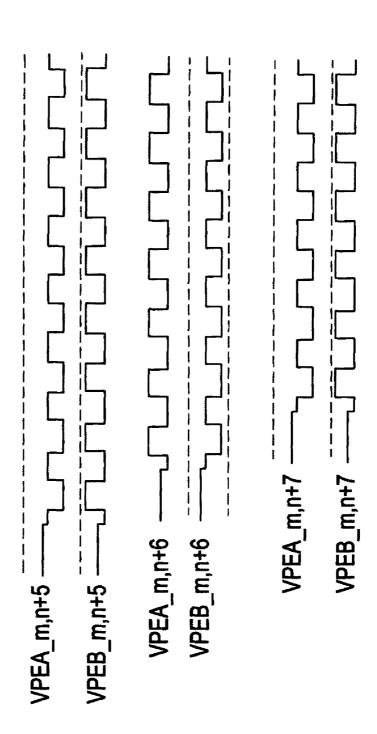

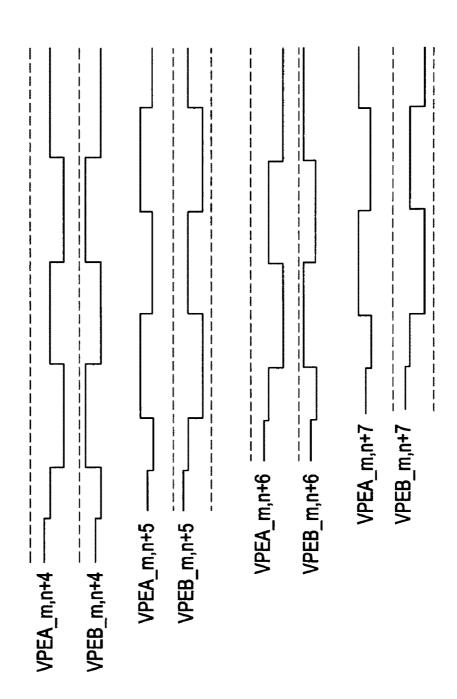

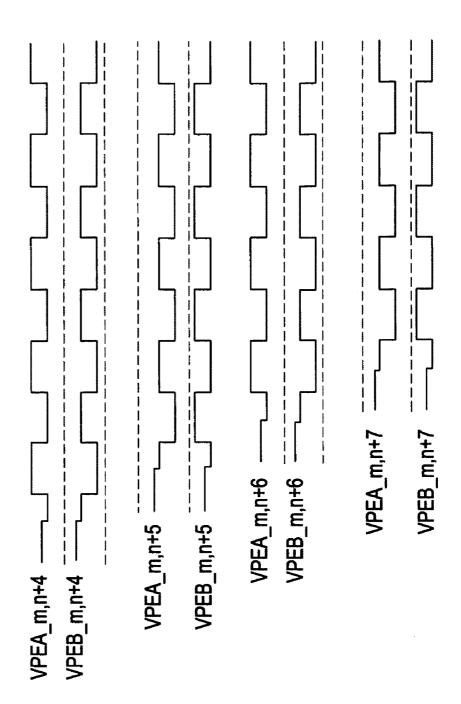

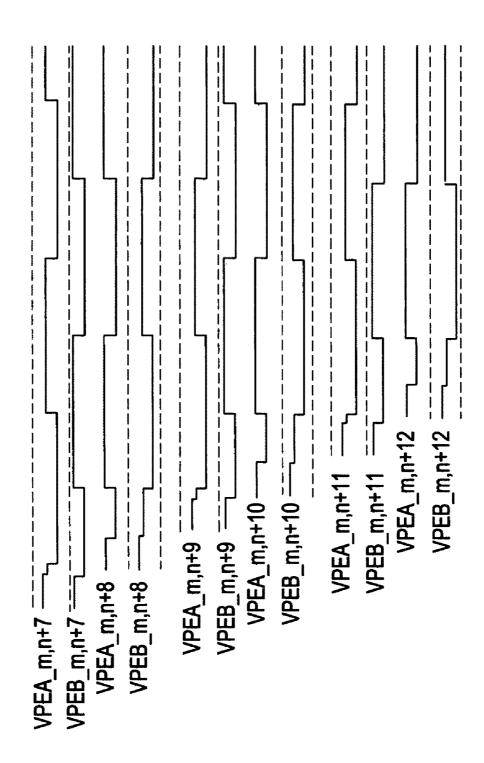

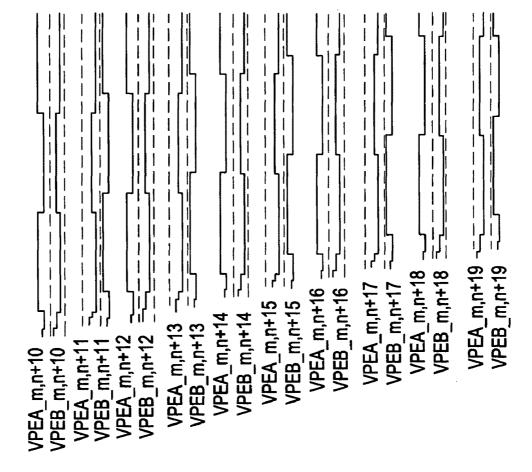

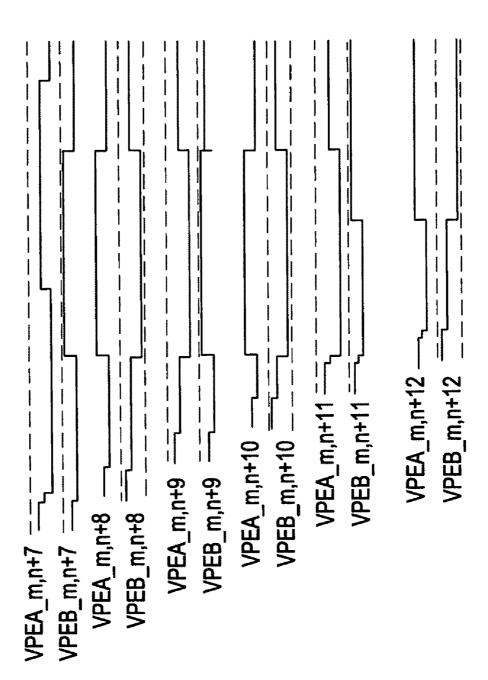

FIGS. **33**A-**1** to **33**A-**3** are a diagram showing periods and phases of oscillation of oscillating voltage supplied to the CS buslines in terms of voltage waveforms of gate buslines as well as showing voltages of sub-pixel electrodes in the liquid crystal display shown in FIG. **32**.

FIGS. **33**B-**1** to **33**B-**3** are a diagram showing periods and phases of oscillation of oscillating voltage supplied to the CS buslines in terms of voltage waveforms of the gate buslines as well as showing voltages of sub-pixel electrodes in the liquid crystal display shown in FIG. **32** (voltages applied to liquid crystal layers have polarity opposite to that in FIG. **33**A).

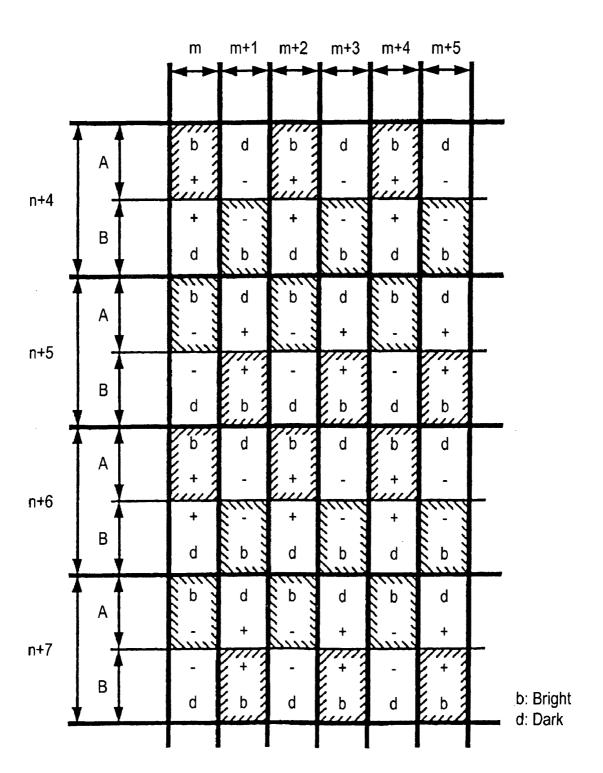

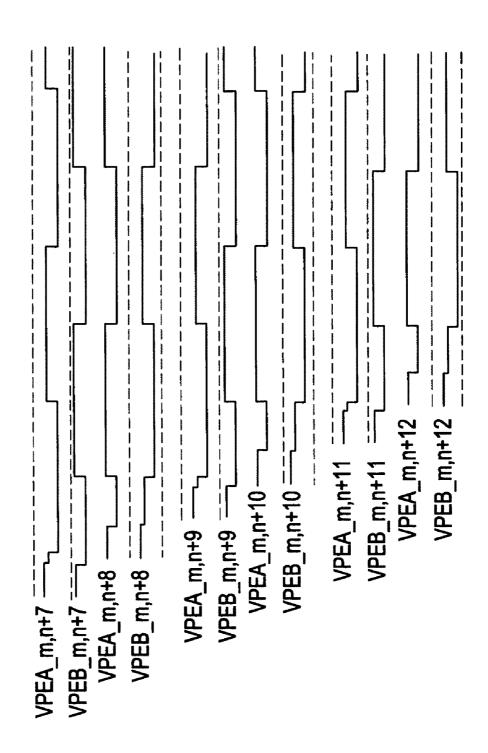

FIGS. **34**A-**1** to **34**A-**2** are a diagram showing driving states of the liquid crystal display shown in FIG. **32** (where the voltages in FIG. **33**A are used).

FIGS. 34B-1 to 34B-2 are a diagram showing driving states of the liquid crystal display shown in FIG. 32 (where the voltages in FIG. 33B are used).

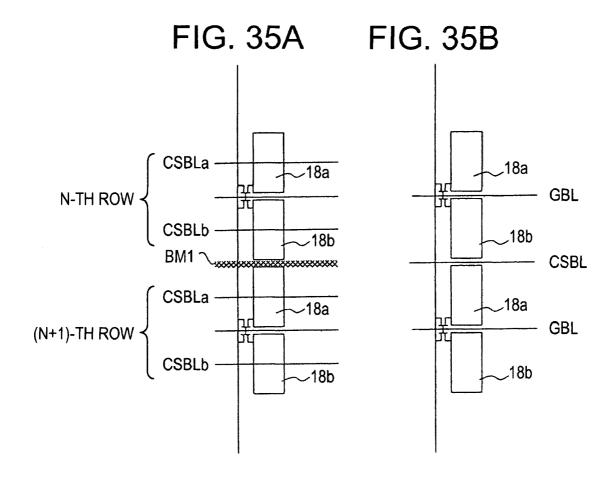

FIG. 35A is a schematic diagram showing a layout example of CS buslines and an inter-pixel black matrix in the liquid crystal display according to an embodiment of the third aspect of the present invention and 35B is a schematic diagram showing a layout example of CS buslines which also serve as an inter-pixel black matrix in a liquid crystal display according to an embodiment of a fourth aspect of the present invention.