(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-168706

(P2019-168706A)

(43) 公開日 令和1年10月3日(2019.10.3)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2H193       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 612J        |

| <b>G09G 3/34</b> (2006.01)  | G09G 3/34 | J           |

| <b>G03B 21/14</b> (2006.01) | G09G 3/20 | 612U        |

| <b>G03B 21/00</b> (2006.01) | G09G 3/20 | 5C006       |

|                             |           | 5C080       |

|                             |           | 641E        |

審査請求 有 請求項の数 6 O L (全 25 頁) 最終頁に続く

|            |                                   |          |                                    |

|------------|-----------------------------------|----------|------------------------------------|

| (21) 出願番号  | 特願2019-92736 (P2019-92736)        | (71) 出願人 | 308036402<br>株式会社 JVCケンウッド         |

| (22) 出願日   | 令和1年5月16日 (2019.5.16)             |          | 神奈川県横浜市神奈川区守屋町3丁目12<br>番地          |

| (62) 分割の表示 | 特願2015-94023 (P2015-94023)<br>の分割 | (72) 発明者 | 中島 伸基<br>神奈川県横浜市神奈川区守屋町3丁目12<br>番地 |

| 原出願日       | 平成27年5月1日 (2015.5.1)              | (72) 発明者 | 相崎 隆嗣<br>神奈川県横浜市神奈川区守屋町3丁目12<br>番地 |

F ターム (参考) 2H193 ZD25 ZD27 ZD29 ZF13 ZG48

ZG60 ZR02

2K203 FA24 FA62 GA40 GA44 GA45

GA52 GA59 GA60 GB45 GB62

GB69 HB05 MA06

最終頁に続く

(54) 【発明の名称】光源駆動装置、光源駆動方法および表示装置

## (57) 【要約】

【課題】液晶表示素子をデジタル駆動方式により駆動する場合の表示品質を向上させる。

【解決手段】映像信号のフレームを分割した分割周期を作成する。表示素子は、階調毎に予め割り当てられた分割周期に応じて映像信号に従い画素毎にオンおよびオフが制御される。表示素子に光を照射させる光源の光量を、黒表示を除く最も低い階調に対応する第1の分割周期での第1の光量を、第1の分割周期以外の第2分割周期の第2の光量より低い光量にするとともに、黒表示を除く全ての階調に第1の光量を含むように制御する。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

映像信号のフレーム周期を分割した分割周期を作成する分割周期作成部と、

階調毎に予め割り当てられた前記分割周期に応じて前記映像信号に従い画素毎にオンおよびオフが制御される表示素子に対して光を照射する光源を駆動する光源制御部とを備え、

前記光源制御部は、

黒表示を除く最も低い階調に対応する第1の分割周期での第1の光量を、該第1の分割周期以外の第2の分割周期の第2の光量より低い光量にするとともに、黒表示を除く全ての階調に前記第1の光量を含むように制御することを特徴とする光源駆動装置。

10

**【請求項 2】**

前記光源制御部は、

前記光源の光量を、前記第2の分割周期のうち前記第1の分割周期から連続する1以上の分割周期でさらに前記第1の光量に制御することを特徴とする請求項1に記載の光源駆動装置。

**【請求項 3】**

映像信号のフレーム周期を分割した分割周期を作成する分割周期作成ステップと、

階調毎に予め割り当てられた前記分割周期に応じて前記映像信号に従い画素毎にオンおよびオフが制御される表示素子に対して光を照射する光源を駆動する光源制御ステップとを備え、

20

前記光源制御ステップは、

黒表示を除く最も低い階調に対応する第1の分割周期と、該第1の分割周期以外の第2の分割周期とのうち、少なくとも該第1の分割周期での第1の光量を、該第2の分割周期の第2の光量より低い光量にするとともに、黒表示を除く全ての階調に前記第1の光量を含むように制御することを特徴とする光源駆動方法。

**【請求項 4】**

光源と、

前記光源から射出された光を映像信号に応じて変調させる表示素子と、

30

前記映像信号のフレーム周期を分割した分割周期を作成する分割周期作成部と、

階調毎に予め割り当てられた前記分割周期に応じて前記映像信号に従い前記表示素子の画素毎のオンおよびオフを制御する駆動部と、

前記光源を駆動する光源制御部と

を備え、

前記光源制御部は、

黒表示を除く最も低い階調に対応する第1の分割周期と、該第1の分割周期以外の第2の分割周期とのうち、少なくとも該第1の分割周期での第1の光量を、該第2の分割周期の第2の光量より低い光量にするとともに、黒表示を除く全ての階調に前記第1の光量を含むように制御することを特徴とする表示装置。

40

**【請求項 5】**

前記光源制御部は、

前記光源の光量を、前記第2の分割周期のうち前記第1の分割周期から連続する1以上の分割周期でさらに前記第1の光量に制御することを特徴とする請求項4に記載の表示装置。

**【請求項 6】**

前記駆動部は、

前記画素のオンおよびオフを、前記階調毎に、前記画素のブロック単位でさらに制御する

50

ことを特徴とする請求項 4 または請求項 5 に記載の表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光源駆動装置、光源駆動方法および表示装置に関する。

【背景技術】

【0002】

液晶表示装置に用いられる液晶表示素子を駆動する駆動方式として、アナログ駆動方式とディジタル駆動方式とが知られている。アナログ駆動方式は、画素に印加される電圧値を連続的なアナログ値とした駆動方式である。ディジタル駆動方式は、画素に印加する電圧の大きさを 2 値とし、画像の輝度（階調）に対応して、印加電圧の時間幅を変えることにより、液晶の画素に印加する実効電圧値を制御する駆動方式である。ディジタル駆動方式は、画素に印加される情報が「0」および「1」の何れかであるため、ノイズなどの外部要因による影響を受け難いという特徴がある。

10

【0003】

ディジタル駆動方式において、映像信号の 1 フレームを時分割制御して中間階調を得る技術が知られている。例えば、特許文献 1 には、映像信号の 1 フレーム周期を等分割して複数のサブフレームを形成し、表示する映像信号の階調に対応して適宜サブフレームを選択して表示を行い、人の視覚積分効果を利用して中間階調を表現する技術が開示されている。

20

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開 2013 - 092548 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、人の階調に対する反応はリニアではなく、より低い階調（より暗い画像）においてより敏感に反応することが知られている。一方、上述した、サブフレームを用いた階調制御による駆動方式は、各階調での照度は、その階調で選択したサブフレームの照度を加算したものになる。液晶の、電圧印加時間と透過率との関係はリニアではなく、人の階調に対する反応と似たものとなるが、階調が低い領域においてズレが大きくなり、視覚的に違和感のある画像となってしまうという問題点があった。

30

【0006】

本発明は、上記に鑑みてなされたものであって、液晶表示素子をディジタル駆動方式により駆動する場合の表示品質を向上させることを目的とする。

【課題を解決するための手段】

【0007】

上述した課題を解決し、目的を達成するために、本発明は、映像信号のフレーム周期を分割した分割周期を作成する分割周期作成部と、階調毎に予め割り当てられた分割周期に応じて映像信号に従い画素毎にオンおよびオフが制御される表示素子に対して光を照射する光源を駆動する光源制御部とを備え、光源制御部は、黒表示を除く最も低い階調に対応する第 1 の分割周期での第 1 の光量を、第 1 の分割周期以外の第 2 の分割周期の第 2 の光量より低い光量にするとともに、黒表示を除く全ての階調に第 1 の光量を含むように制御することを特徴とする。

40

【発明の効果】

【0008】

本発明によれば、液晶表示素子をディジタル駆動方式により駆動する場合の表示品質を向上させることが可能となるという効果を奏する。

【図面の簡単な説明】

50

## 【0009】

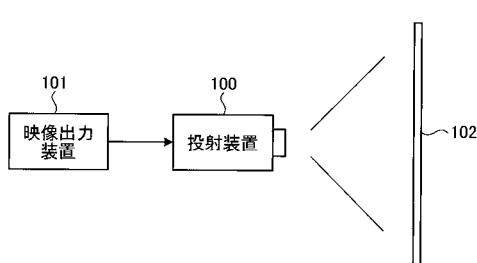

【図1】図1は、各実施形態に適用可能な表示システムの一例の構成を示す図である。

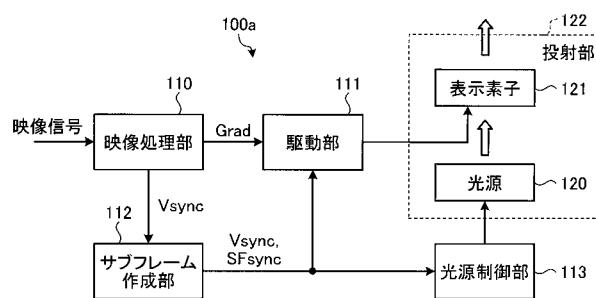

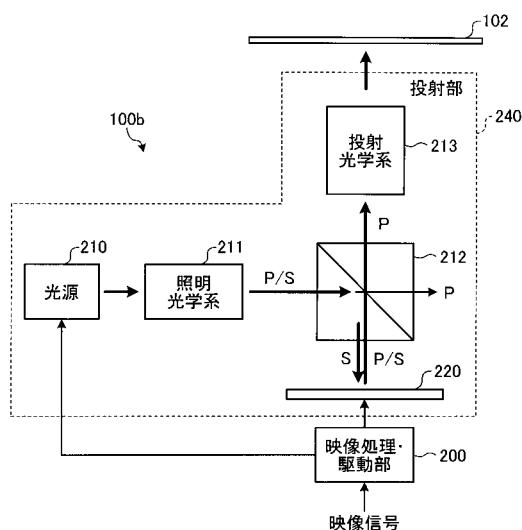

【図2】図2は、第1の実施形態に係る投射装置の一例の構成を概略的に示すブロック図である。

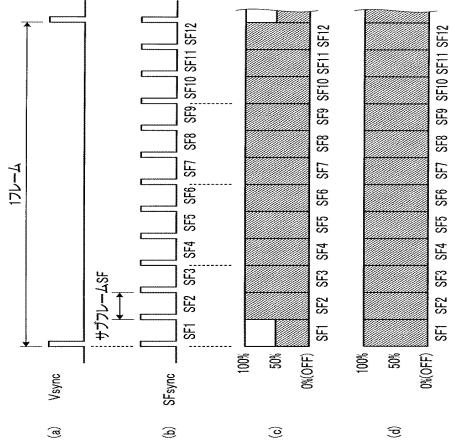

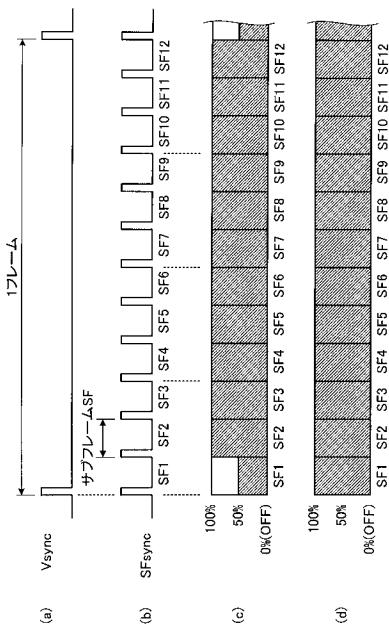

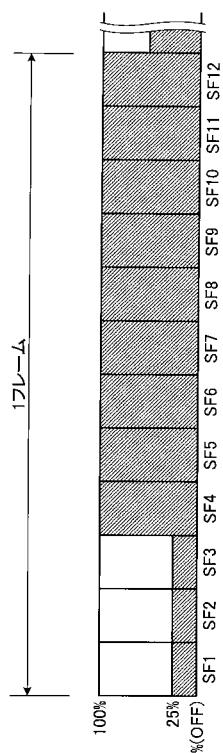

【図3】図3は、第1の実施形態に係る、階調値とサブフレームと画素のオン／オフ制御との関係の例を示す図である。

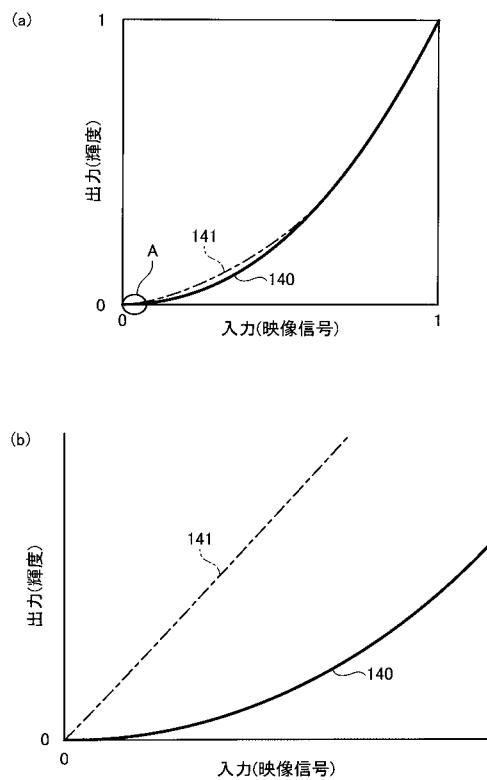

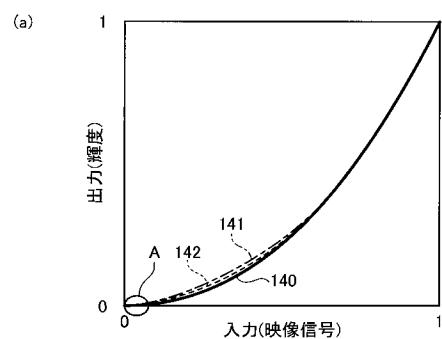

【図4】図4は、 $\gamma = 2.2$ のガンマ曲線と投射部の入出力特性の例とを比較して示す図である。

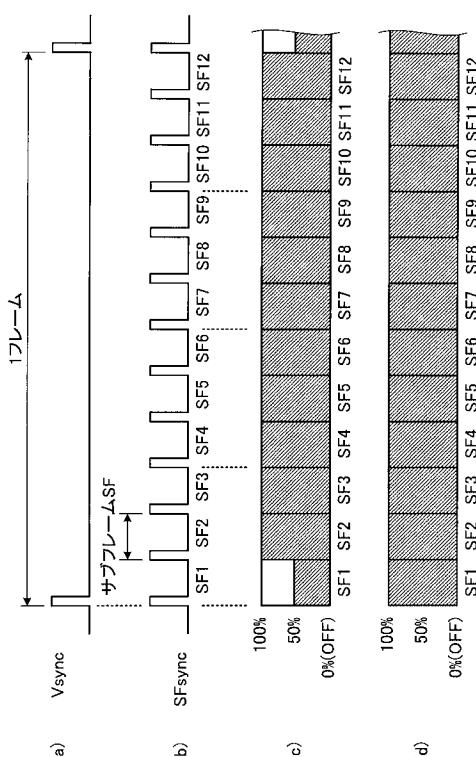

【図5】図5は、第1の実施形態に係る光源制御を説明するためのタイムチャートである。

【図6】図6は、表示素子の各画素の例を示す図である。

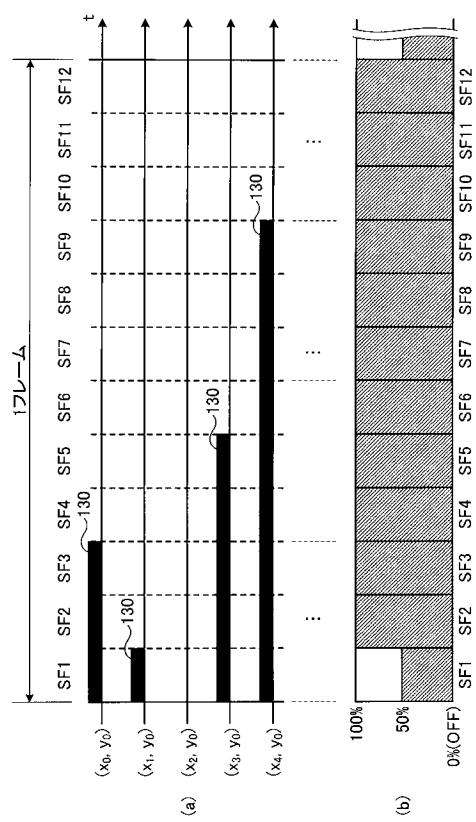

【図7】図7は、第1の実施形態に係る、表示素子における各画素のオン／オフ制御と、光源の光量制御との関係の例を示す図である。

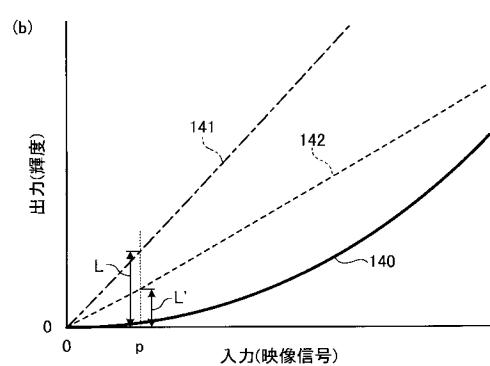

【図8】図8は、第1の実施形態に係る光源制御を行った場合の効果について説明するための図である。

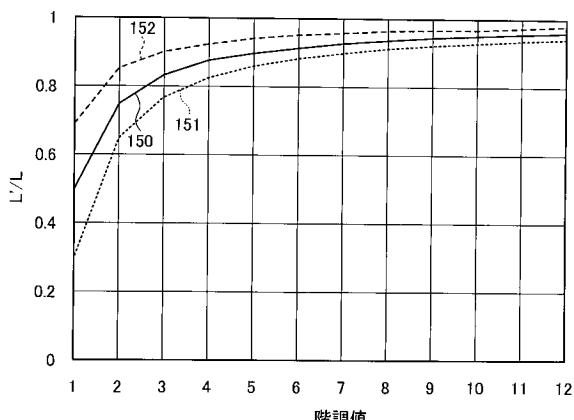

【図9】図9は、第1の実施形態に係る、最小分解能の階調値n毎の変化の例を示す図である。

【図10】図10は、第1の実施形態の変形例に係る光源の制御の例を示す図である。

【図11】図11は、第2の実施形態に係る投射装置の一例の構成を示す図である。

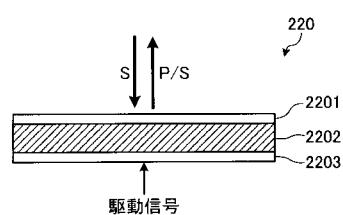

【図12】図12は、表示素子の構成例を、光の入射方向と平行な方向の断面により示す図である。

【図13】図13は、表示素子の特性の例を示す図である。

【図14】図14は、第2の実施形態に係る映像処理・駆動部および画素電極部の構成の例を示すブロック図である。

【図15】図15は、第2の実施形態に係る画素回路の一例の構成を示すブロック図である。

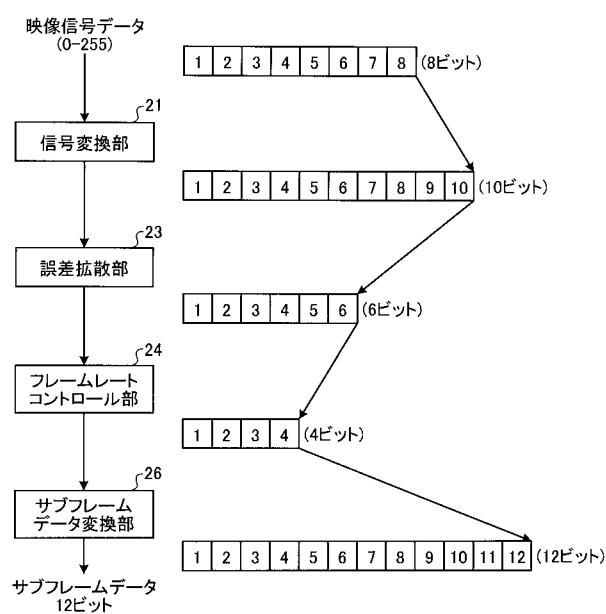

【図16】図16は、第2の実施形態に係る、信号変換部、誤差拡散部、フレームレートコントロール部およびサブフレームデータ作成部における処理の流れを説明するための図である。

【図17】図17は、第2の実施形態に係るフレームレートコントロールテーブルの例を示す。

【図18】図18は、第2の実施形態に適用可能な駆動階調テーブルの例を示す図である。

【図19】図19は、第2の実施形態に係る制御の例を示すタイムチャートである。

## 【発明を実施するための形態】

## 【0010】

以下に添付図面を参照して、光源駆動装置、表示装置および光源駆動方法の好適な実施形態を詳細に説明する。係る実施形態に示す具体的な数値および外観構成などは、本発明の理解を容易とするための例示にすぎず、特に断る場合を除き、本発明を限定するものではない。なお、本発明に直接関係のない要素は詳細な説明および図示を省略している。

## 【0011】

図1は、各実施形態に適用可能な表示システムの一例の構成を示す。図1において、表示装置としての投射装置100は、光源および表示素子を備える。投射装置100は、光源から射出された光を、映像出力装置101から供給された映像信号に基づき表示素子により変調して、映像信号に応じた投射光として出射する。投射装置100から出射された投射光は、スクリーンなどの被投射媒体102に投射され、被投射媒体102上に、映像信号に応じた投射映像として表示される。

## 【0012】

## (第1の実施形態)

第1の実施形態に係る投射装置について説明する。図2は、第1の実施形態に係る投射

10

20

30

40

50

装置の一例の構成を概略的に示す。図2において、図1の投射装置100に対応する投射装置100aは、映像処理部110と、駆動部111と、後述する分割周期を作成する分割周期作成部としてのサブフレーム作成部112と、光源制御部113と、投射部122とを備える。また、投射部122は、光源120と表示素子121とを含む。ここで、サブフレーム作成部112と光源制御部113とによる構成を、光源駆動装置と呼ぶ。

#### 【0013】

映像処理部110に対して映像信号が入力される。ここで、映像信号は、所定のフレーム周期（例えば60フレーム/秒）でフレーム画像が更新される動画像を表示するためのデジタル方式の映像信号であるものとする。これに限らず、アナログ方式の映像信号を例えば映像処理部110においてデジタル方式の映像信号に変換してもよい。また、説明のため、映像信号は、画素毎に、階調値「0」～階調値「12」の13階調を表現可能であるものとする。ここで、階調値「0」および階調値「12」は、それぞれ黒表示および白表示に対応し、階調値「1」～階調値「11」は、階調値に応じた明るさの中間調表示に対応する。

10

#### 【0014】

映像処理部110は、入力された映像信号から、フレームの先頭を示すフレーム同期信号Vsyncと、画素毎の階調情報Gradとを抽出する。階調情報Gradは、画素の階調値（輝度値）を含む。映像処理部110は、抽出した階調情報Gradを駆動部111に供給する。また、映像処理部110は、抽出したフレーム同期信号Vsyncをサブフレーム作成部112に供給する。

20

#### 【0015】

サブフレーム作成部112は、映像処理部110から供給されたフレーム同期信号Vsyncから、1フレーム周期を分割した分割周期を作成する。サブフレーム作成部112は、例えば、1フレーム周期を、映像信号の階調数に対応する分割数で分割し、分割周期を作成する。この分割周期を、以下、サブフレームと呼ぶ。

20

#### 【0016】

映像信号が13階調を表現可能であるこの例では、サブフレーム作成部112は、1フレーム周期を階調数より1少ない12のサブフレームSF1、SF2、…、SF12に分割する。これは、詳細は後述するが、階調値「0」または階調値「12」では、1フレーム周期内において画素のオフ状態またはオン状態が維持されるためである。

30

#### 【0017】

サブフレーム作成部112は、例えば、分割した各サブフレームSF1、SF2、…、SF12のタイミングを示すサブフレーム同期信号SFsyncを生成し、生成したサブフレーム同期信号SFsyncを、フレーム同期信号Vsyncと共に出力する。サブフレーム作成部112から出力されたフレーム同期信号Vsyncおよびサブフレーム同期信号SFsyncは、それぞれ駆動部111および光源制御部113に供給される。

#### 【0018】

光源制御部113は、光源120の発光を制御するための光源制御信号を、サブフレーム作成部112から供給されたフレーム同期信号Vsyncおよびサブフレーム同期信号SFsyncに基づき生成する。光源120は、例えば半導体レーザであって、光源制御部113から供給された光源制御信号に従いレーザ光の発光が制御される。例えば、光源120は、光源制御信号に従い、少なくとも、射出するレーザ光の強度（明るさ）が制御される。また、光源120は、光源制御信号に従い、発光タイミングが、少なくとも上述のサブフレーム単位で制御可能とされている。光源制御部113による光源120の発光制御の詳細については、後述する。

40

#### 【0019】

なお、光源120は、光源制御信号に従い発光強度が制御可能で、且つ、発光タイミングがサブフレーム単位で制御可能であれば、他の種類の光源であってもよい。例えば、光源としてLED(Light Emitting Diode)を用いてもよいし、UHP(Ultra High Performance)ランプを用いることも可能である。

50

## 【0020】

一方、駆動部111は、映像処理部110から供給された画素毎の階調情報Gradと、サブフレーム作成部112から供給されたフレーム同期信号Vsyncおよびサブフレーム同期信号SFSyncとに基づき、表示素子121を駆動するための駆動信号を生成する。駆動信号は、表示素子121に供給される。

## 【0021】

表示素子121は、画素がマトリクス状に配置され、駆動部111から供給された、映像信号に基づく駆動信号に従い、光源120から入射された光を画素毎に変調して射出する。第1の実施形態では、表示素子121として、液晶の特性を用いた液晶表示素子を用いる。液晶表示素子は、画素毎の画素電極と、各画素に共通する共通電極との間に液晶を挟み込み、画素電極により映像信号に応じて画素毎に電圧を印加することで特定の偏光方向の光に対する液晶の透過率を変化させ、映像の表示を行う。10

## 【0022】

第1の実施形態では、表示素子121として、反射型の液晶表示素子を用いる。反射型の液晶表示素子では、照射された光は、入射面から液晶層を通過して反射面に照射され、反射面で反射されて再び液晶層を通過して入射面から外部に射出される。反射型の液晶表示素子は、入射された光の偏光状態を変化させて射出するため、偏光ビームスプリッタなどを用いて入射光と出射光を偏光分離する。

## 【0023】

投射装置100aにおいて、光源120および表示素子121とを含んで、投射部122が構成される。被投射媒体102に投射される投射映像は、この投射部122に含まれる光源120の特性と表示素子121の特性とを統合した特性を備えることになる。以降、これら光源120の特性と表示素子121の特性とを統合した特性を、投射部122の特性とする。また、表示素子121に入力される駆動信号を、投射部122に対する入力とし、光源120の光が表示素子121を介して射出された光を、投射部122の出力とする。20

## 【0024】

次に、第1の実施形態に係るデジタル駆動方式について、より具体的に説明する。第1の実施形態では、駆動部111は、デジタル駆動方式により表示素子121を駆動する。第1の実施形態に係るデジタル駆動方式では、駆動部111は、画素をオン状態と、オフ状態との2状態で制御する。なお、オン状態は、例えば液晶の透過率が最も高い状態であって、液晶に白色の光を入射した場合に略白の表示（白表示）となる状態である。また、オフ状態は、例えば液晶の透過率が最も低い状態であって、液晶に白色の光を入射した場合に略黒の表示（黒表示）となる状態である。また、駆動部111は、ある画素について、1フレーム周期内のサブフレームのうち、当該画素の階調値に応じた数のサブフレームにおいてオン状態に制御し、それ以外のサブフレームにおいてオフ状態に制御することで、当該画素において階調を表現する。30

## 【0025】

図3は、第1の実施形態に係る、階調値とサブフレームと画素のオン／オフ制御との関係の例を示す。図3において、各列は、左から右に向けてサブフレームSF1、SF2、…、SF12とされている。これらのうち、サブフレームSF1がフレーム周期の先頭のサブフレーム、サブフレームSF12がフレーム周期の後端のサブフレームとする。また、図3において、各行は、上から下に向けて階調値が0から1ずつ増加する。階調値「0」が最も低い（暗い）階調であり、階調値「12」が最も高い（明るい）階調である。40

## 【0026】

第1の実施形態では、駆動部111は、画素の階調値に応じた数のサブフレームを、フレーム周期の先頭から順に選択し、選択したサブフレームにおいて、当該画素をオン状態に制御する。図3において、斜線を付して示す値「1」のセルは、画素をオン状態に制御することを示し、値「0」のセルは、画素をオフ状態に制御することを示す。50

## 【0027】

例えば、ある画素の階調値が「3」である場合、駆動部111は、フレーム周期の先頭のサブフレームSF1から3つのサブフレーム（サブフレームSF1、SF2およびSF3）を選択する。そして、駆動部111は、選択したサブフレームにおいて、当該画素をオン状態に制御する。また、駆動部111は、その他の9個のサブフレーム（サブフレームSF4～SF12）では、当該画素をオフ状態に制御する。

#### 【0028】

また例えば、ある画素の階調値が「12」である場合、駆動部111は、フレーム周期の先頭のサブフレームSF1から12個のサブフレーム（サブフレームSF1～SF12）を選択する。そして、駆動部111は、選択したサブフレームにおいて、当該画素をオン状態に制御する。この場合には、オフ状態に制御するサブフレームは存在しない。

10

#### 【0029】

さらに例えば、ある画素の階調値が「0」である場合、駆動部111は、1フレーム周期内の全てのサブフレーム（サブフレームSF1～SF12）で当該画素をオフ状態に制御する。この場合には、オン状態に制御するサブフレームは存在しない。

#### 【0030】

このように、第1の実施形態では、オンおよびオフ制御を行うサブフレームが、階調毎に予め割り当てられる。また、階調値「0」では、フレーム周期内で画素のオフ状態が維持され、階調値「12」では、フレーム周期内で画素のオン状態が維持される。このように、階調値「0」および階調値「12」の階調は、フレーム周期内の全てのサブフレームをオフ状態およびオン状態に制御することで実現できるため、1フレーム周期内のサブフレーム数は、12で足りる。

20

#### 【0031】

ここで、投射部122の特性について説明する。一般的に、ディスプレイの入出力特性はリニアではなく、入力に対して出力が下に凸の曲線で表される。したがって、映像信号の処理も、この入出力特性に従い行われる。ディスプレイの入出力特性を示す曲線としては、一般的には、例えばガンマ値 = 2.2 のガンマ曲線が用いられる。ガンマ曲線は、入力値を  $V_{IN}$ 、出力値を  $V_{OUT}$ としたときに、 $V_{OUT} = V_{IN}^{\gamma}$  により示される。

#### 【0032】

入出力特性がガンマ値 のディスプレイに対して、例えばガンマ値 1 / のガンマ曲線に従い補正された映像信号を供給することで、リニアな階調表現を得ることができる。例えば、映像出力装置101から出力される映像信号は、一般的には、リニアな階調特性に対し、ガンマ値 1 / 0.455 のガンマ曲線に基づき補正された階調特性を持つ。

30

#### 【0033】

液晶を用いた表示素子121を備える投射部122の特性も、入出力特性はリニアではなく、ディスプレイの入出力特性と同様の、入力に対して出力が下に凸の曲線で表される。例えば、投射部122の入力は、映像信号の階調値に対応する。第1の実施形態では、図3を用いて説明したように、階調値は、液晶層への電圧印加時間に対応する。また、投射部122の出力は、光源120の光量と液晶の透過率とに基づくものとなる。より詳細には、投射部122の出力は、光源120から光が表示素子121を介して被投射媒体102に投射された場合の、被投射媒体102上の輝度に対応する。

40

#### 【0034】

図4は、 $\gamma = 2.2$  のガンマ曲線に従った入出力特性を基準の特性として、この基準特性と投射部122の入出力特性の例とを比較して示す。図4(a)において、横軸に入力すなわち映像信号を、最大値を1に正規化して示す。上述の例では、入力は、値「1」が階調値「12」に対応する。また、図4(a)において、縦軸に出力すなわち輝度を、それぞれ最大値を1に正規化して示している。なお、輝度は、上述した、光源120から光が表示素子121を介して被投射媒体102に投射された場合の、被投射媒体102上の輝度であるものとする。さらに、図4(a)の例では、光源120の光量は、一定に制御されているものとする。

#### 【0035】

50

図4(b)は、図4(a)において範囲Aで示した部分を拡大した例である。図4(a)および図4(b)において、特性線140が基準特性( $\gamma = 2.2$ のガンマ曲線に従った特性)を、特性線141が表示素子121の入出力特性を、それぞれ示す。

#### 【0036】

図4(a)に示されるように、例えば入力値0.5(階調値「7」以上)といった高い入力値の範囲では、特性線140と特性線141とが略一致し、投射部122の入出力特性が基準特性と略等しいと見做すことができる。

#### 【0037】

一方、例えば入力値<0.5(階調値「6」以下)といった低い入力値の範囲では、特性線140と特性線141とが重ならず、投射部122の入出力特性が基準特性に対して高い出力(輝度)側にずれている。図4(a)の最も低い入力値を含む範囲Aにおいても、図4(b)に示されるように、投射部122の入出力特性が基準特性に対して高い出力(輝度)側にずれている。

10

#### 【0038】

この特性線141に従った入出力特性により投射部122を駆動すると、高い階調値の範囲、すなわち、特性線141と特性線140とが略一致する範囲での入力値の映像信号による映像の表示については、略意図した通りの表示が得られると考えられる。一方、低い階調値の範囲、すなわち、特性線141が特性線140に対して高出力側にずれている範囲での入力値の映像信号による映像の表示については、意図した映像よりも明るく表示されることになる。これは、映像信号の映像における暗い映像領域の表示品質の低下の要因となり得る。

20

#### 【0039】

そこで、第1の実施形態では、1フレーム周期内で光源120の光量を制御することで、投射部122の入出力特性を例えば基準特性に近付ける。より詳細には、第1の実施形態では、光源120の光量をサブフレーム単位で制御し、光源120の光量を、各サブフレームSF1～SF12に含まれる、黒表示(階調値「0」)を除く最も低い階調に対応する第1のサブフレームでの第1の光量が、第1のサブフレーム以外の第2サブフレームの第2の光量より低い光量になるように制御する。

30

#### 【0040】

図5のタイムチャートを用いて、第1の実施形態に係る光源制御について、より具体的に説明する。図5において、右方向に向けて時間が進行する。図5(a)は、フレーム周期を表すフレーム同期信号Vsyncの例を示す。信号の立ち上がりエッジから、次の立ち上がりエッジまでを、1フレーム周期とする。

30

#### 【0041】

図5(b)は、サブフレーム周期を表すサブフレーム同期信号SFsyncの例を示す。フレーム同期信号Vsyncと同様に、サブフレーム同期信号SFsyncも、信号の立ち上がりエッジから、次の立ち上がりエッジまでを、1サブフレーム周期とする。図5(b)の例では、上述の図3に対応し、1フレーム周期を時間軸方向に12のサブフレームSF1～SF12に分割している。

40

#### 【0042】

図5(d)は、既存技術による光源120の光量制御の例を示す。既存技術においては、図5(d)に斜線を付して示しているように、全てのサブフレームSF1～SF12において、光源120の光量を均一な光量に制御していた。このときの各サブフレームSF1～SF12における光源120の光量を、100%の光量とする。上述した図4の特性線141は、この既存技術に対応するものである。

#### 【0043】

図5(c)は、第1の実施形態に係る光源120の光量制御の例を示す。第1の実施形態では、光源制御部113は、フレーム周期の先頭のサブフレームSF1において光源120の光量を例えば50%の低減比率で低減させる制御を行い、その他のサブフレームSF2～SF12では、光源120の光量を100%の光量に制御する。サブフレームSF

50

1は、上述の図3に示したように、黒表示（階調値「0」）を除く最も低い階調において画素がオン制御されるサブフレームである。したがって、このサブフレームSF1では、階調値「0」の階調を除く各階調で共通して画素がオン制御される。

#### 【0044】

図6および図7を用いて、第1の実施形態に係る投射部122の制御について、より具体的に説明する。図6は、表示素子121の各画素の例を示す。ここでは、説明のため、表示素子121が5画素×5画素を含むものとし、各画素を座標( $x_n, y_n$ )で示している。図6の各マス内の数値は、映像信号に従った各画素の階調値の例を示す。

#### 【0045】

図7は、第1の実施形態に係る、表示素子121における各画素のオン／オフ制御と、光源120の光量制御との関係の例を示す。なお、図7において、右方向に向けて時間の進行を示している。

#### 【0046】

図7(a)は、図6の例において、座標( $x_0, y_0$ )~( $x_4, y_0$ )の5個の画素について、オン状態に制御されるオン区間130を示している。図6を参照し、駆動部112は、画素( $x_0, y_0$ )に対し、階調値の「3」に対してサブフレームSF1~SF3をオン区間130とし、画素( $x_1, y_0$ )に対し、階調値の「1」に対してサブフレームSF1のみをオン区間130としている。また、駆動部112は、画素( $x_2, y_0$ )に対し、階調値が「0」であるので、オン区間130を設けない。さらに、駆動部112は、画素( $x_3, y_0$ )および画素( $x_4, y_0$ )に対し、それぞれ階調値が「5」および「9」であるため、それサブフレームSF1~SF5、ならびに、サブフレームSF1~SF9をオン区間130としている。

#### 【0047】

図7(b)は、光源120の光量制御の例を示す。この例では、図5(c)と同様に、光源制御部113は、光源120を、サブフレームSF1において光量を50%の低減比率で低減させる制御を行い、他のサブフレームSF2~SF12において100%の光量に制御している。そのため、各画素( $x_0, y_0$ )、( $x_1, y_0$ )、( $x_3, y_0$ )および( $x_4, y_0$ )は、サブフレームSF1において50%の輝度(光量)となる。そして、各画素( $x_0, y_0$ )、( $x_3, y_0$ )および( $x_4, y_0$ )は、サブフレームSF2以降において、100%の輝度(光量)となる。

#### 【0048】

したがって、黒表示の画素( $x_2, y_0$ )を除く各画素( $x_0, y_0$ )、( $x_1, y_0$ )、( $x_3, y_0$ )および( $x_4, y_0$ )は、図5(d)で示した、光源120の光量を全サブフレームSF1~SF12で均一な光量に制御した場合と比較して、サブフレームSF1で光量を低減比率50%で低減させた分、輝度(光量)が下がっていることになる。

#### 【0049】

例えば、光源120の光量が100%の場合の輝度を「1」として正規化し、各画素において、各サブフレームにおける光源120の光量が単純加算されるものとする。この場合、第1の実施形態に係る光源制御によれば、各画素( $x_0, y_0$ )、( $x_1, y_0$ )、( $x_3, y_0$ )および( $x_4, y_0$ )の輝度(光量)は、それぞれ「2.5」、「0.5」、「4.5」および「8.5」となる。これに対して、各サブフレームSF1~SF12における光源の光量を均一とする既存技術の場合は、各画素( $x_0, y_0$ )、( $x_1, y_0$ )、( $x_3, y_0$ )および( $x_4, y_0$ )の輝度(光量)は、それぞれ「3」、「1」、「5」および「9」となる。

#### 【0050】

各画素の輝度(光量)を、第1の実施形態による光量制御を行った場合と、既存技術とで比較すると、黒表示を除き、階調が低いほど両者の比が大きくなることが分かる。

#### 【0051】

図8を用いて、第1の実施形態に係る光源制御を行った場合の効果について説明する。なお、図8において、上述した図4と共に部分には同一の符号を付して、詳細な説明を省略する。図8(a)および図8(b)は、上述した図4(a)および図4(b)に対

10

20

30

40

50

して、第1の実施形態に係る光源制御を行った場合の投射部122の入出力特性の例を示す特性線142を追加したものである。

#### 【0052】

図8の例では、光源120の光量を、サブフレームSF1で50%、他のサブフレームSF2～SF12でそれぞれ100%に制御している。このように制御することで、例えば入力値<0.5(階調値「6」以下)といった低い入力値の範囲において、第1の実施形態に係る特性線142は、既存技術による特性線141と比較して、より特性線140すなわち基準特性に近付いていることが分かる。一方、入力値0.5(階調値「7」以上)といった高い入力値の範囲では、既存技術と同様に、特性線142は特性線と略一致している。

10

#### 【0053】

したがって、第1の実施形態に係る光源制御を行うことで、低い階調の範囲での入力値の映像信号による映像の表示が、既存技術に対してより意図した映像に近付き、既存技術に対して表示品質を向上させることができる。

#### 【0054】

出力値の最小分解能は、単位入力値における出力値によって表すことができる。図8(b)に示されるように、ある入力値pにおける、既存技術における最小分解能Lと、第1の実施形態に係る光量制御を行った場合の最小分解能L'について考える。この場合、サブフレームSF1の光量aを「0 a 1」とし、他のサブフレームSF2～SF12の光量bを「1」とした場合、最小分解能L'は、 $L' = a \times L$ とすることができる。

20

#### 【0055】

ここで、「0 a / b 1」とした場合、階調値nにおける最小分解能L'(n)は、下記の式(1)により表される。なお、式(1)において、n>0である。また、サブフレームSFの順番を示す値nは、階調値に対応する。

#### 【数1】

$$L'(n) = \frac{b \times n - (b - a)}{b \times n} \times L(n) \quad \cdots (1)$$

#### 【0056】

図9は、第1の実施形態に係る、式(1)に従い計算した最小分解能の、階調値n毎の変化の例を示す。図9において、縦軸は、第1の実施形態に係る最小分解能L'、既存技術による最小分解能Lとの比 $L'/L$ を示し、横軸は、階調値nを示す。また、特性線150は「a=0.5、b=1」の場合の例、特性線151は「a=0.3、b=1」の場合の例、特性線152は「a=0.7、b=1」の場合の例をそれぞれ示す。

30

#### 【0057】

図9に示されるように、階調値nが大きくなる程、比 $L'/L$ の値が「1」に近付き、階調値nが小さくなる程、比 $L'/L$ の値が小さくなる。また、階調値nが一定値以下(例えば階調値「4」～「5」以下)では、階調値nに対する比 $L'/L$ の値の変化の度合いが大きくなる。したがって、階調値nの値が一定値以下の範囲、例えば「1 n 4～5」の範囲において最小分解能がより小さくなり、暗い映像領域における表示品質を向上させることができる。

40

#### 【0058】

また、特性線150、151および152に示されるように、値a/bによって比 $L'/L$ の変化の度合いが異なる。したがって、光源制御部113において、例えば光量bを「1」に固定とし、光量aを0 a 1の間で調整することで、より適切な制御を行うことが可能である。例えば、光源120や表示素子121の特性に応じて値aを変更することが考えられる。

#### 【0059】

(第1の実施形態の变形例)

次に、第1の実施形態の变形例について説明する。上述した第1の実施形態では、フレ

50

ーム周期を分割したサブフレーム S F 1 ~ S F 1 2 のうち、黒表示（階調値「0」）を除く最も低い階調値に対応する1つのサブフレーム S F 1 のみにおいて光源 1 2 0 の光量を低減させる制御を行っていた。これに対して、第1の実施形態の変形例では、複数のサブフレーム S F において光源 1 2 0 の光量を低減させる。

#### 【0060】

図10は、第1の実施形態の変形例に係る光源 1 2 0 の制御の例を示す。図10の例では、光源制御部 1 1 3 は、フレーム周期を分割したサブフレーム S F 1 ~ S F 1 2 のうち、黒表示を除く最も低い階調値に対応するサブフレーム S F 1 と、このサブフレーム S F 1 に時間的に連続するサブフレーム S F 2 および S F 3 の3つのサブフレーム S F において、光源 1 2 0 の光量を低減させる制御を行う。10

#### 【0061】

各サブフレーム S F 1 ~ S F 3 における光量の低減度合いは、投射部 1 2 2 の入出力特性が基準特性に近付くように決める。図10の例では、各サブフレーム S F 1 ~ S F 3 において、光源 1 2 0 の光量を低減比率 25% で均一に低減させて制御しているが、これはこの例に限定されない。例えば、光源 1 2 0 の光量の低減比率は 25% に限られない。また例えば、光源 1 2 0 の光量を、各サブフレーム S F 1 ~ S F 3 において異なる低減比率で低減させてもよい。

#### 【0062】

さらに、上述では、サブフレーム作成部 1 1 2 は、フレーム周期を等分割して各サブフレーム S F を作成しているが、これはこの例に限定されない。すなわち、サブフレーム作成部 1 1 2 は、各サブフレーム S F の長さを異ならせててもよい。20

#### 【0063】

##### (第2の実施形態)

次に、第2の実施形態について説明する。図11は、第2の実施形態に係る、図1の投射装置 1 0 0 に対応する投射装置 1 0 0 b の一例の構成を示す。投射装置 1 0 0 b は、映像処理・駆動部 2 0 0 と、投射部 2 4 0 とを含む。また、投射部 2 4 0 は、光源 2 1 0 と、照明光学系 2 1 1 と、光分離器 2 1 2 と、投射光学系 2 1 3 と、表示素子 2 2 0 とを含む。

#### 【0064】

映像処理・駆動部 2 0 0 は、例えば映像出力装置 1 0 1 から供給された映像信号に基づき、光源 2 1 0 を制御するための光源制御信号と、表示素子 2 2 0 を駆動するための駆動信号とを生成する。30

#### 【0065】

光源 2 1 0 は、図2の光源 1 2 0 に対応し、例えば半導体レーザが用いられる。光源 2 1 0 から射出された光は、照明光学系 2 1 1 を介して光分離器 2 1 2 に入射される。照明光学系 2 1 1 から光分離器 2 1 2 に入射される光は、P 偏光と S 偏光とを含む光である。

#### 【0066】

光分離器 2 1 2 は、光に含まれる P 偏光と S 偏光とを分離する偏光分離面を含み、偏光分離面において P 偏光を透過させ、S 偏光を反射させる。光分離器 2 1 2 としては、偏光ビームスプリッタを用いることができる。照明光学系 2 1 1 から光分離器 2 1 2 に入射された光は、偏光分離面で P 偏光と S 偏光とに分離され、P 偏光は、偏光分離面を透過し、S 偏光は、偏光分離面で反射されて表示素子 2 2 0 に照射される。40

#### 【0067】

表示素子 2 2 0 は、図2の表示素子 1 2 1 に対応し、例えば反射型液晶表示素子である。図12は、表示素子 2 2 0 の構成例を、光の入射方向と平行な方向の断面により示す。表示素子 2 2 0 は、対向電極 2 2 0 1 と、画素電極および画素電極を駆動する画素回路を含む画素電極部 2 2 0 3 と、液晶層 2 2 0 2 とを備え、対向電極 2 2 0 1 と、画素電極部 2 2 0 3 の画素電極とで液晶層 2 2 0 2 を挟んで構成される。表示素子 2 2 0 は、画素回路に供給される駆動信号に応じて、画素電極と対向電極 2 2 0 1 との間の液晶層 2 2 0 2 に電圧を印加するようになっている。50

## 【0068】

表示素子220に入射されたS偏光は、対向電極2201から液晶層2202を介して画素電極部2203に入射され、画素電極部2203で反射されて再び液晶層2202および対向電極2201を介して、表示素子220から射出される。このとき、液晶層2202は、駆動信号に応じて対向電極2201と画素電極部2203の画素電極と間に印加される電圧に応じて、入射および反射されるS偏光を変調する。対向電極2201に入射したS偏光は、画素電極部2203で反射して対向電極2201から射出するまでの過程で変調を受け、P偏光とS偏光からなる光として対向電極2201から射出される。

## 【0069】

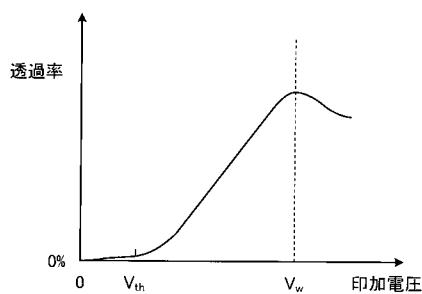

図13は、表示素子220の特性の例を示す。図13において、横軸は、画素電極と対向電極2201とにより液晶層2202に印加される印加電圧を示す。縦軸は、液晶層2202の透過率を示す。表示素子220から射出される光の強度は、この透過率に応じたものとなる。液晶層2202の透過率は、印加電圧が0Vで略0%であり、オフ状態となっている。透過率は、印加電圧を上げていくと徐々に上昇し、閾値電圧 $V_{th}$ を超えると、急激な上昇となる。透過率は、飽和電圧 $V_w$ で飽和する。この飽和電圧 $V_w$ が白レベル電圧である。表示素子220は、例えば0Vから飽和電圧 $V_w$ の間の透過率を用いて表示を行う。

## 【0070】

図12に戻り、表示素子220から射出されたP偏光およびS偏光を含む光は、光分離器212に入射され、偏光分離面においてS偏光が反射され、P偏光が透過される。透過されたP偏光は、光分離器212から射出されて投射光学系213に入射され、投射光として投射装置100bから射出される。投射装置110bから射出された投射光は、被投射媒体102に投射され、被投射媒体102上に投射映像が表示される。

## 【0071】

なお、第2の実施形態においても、投射部240の入出力特性は、上述した第1の実施形態における投射部122の入出力特性と同様に、図4の特性線141で示されるような、基準特性に対して低階調の範囲で高輝度側にずれた特性を有するものとする。

## 【0072】

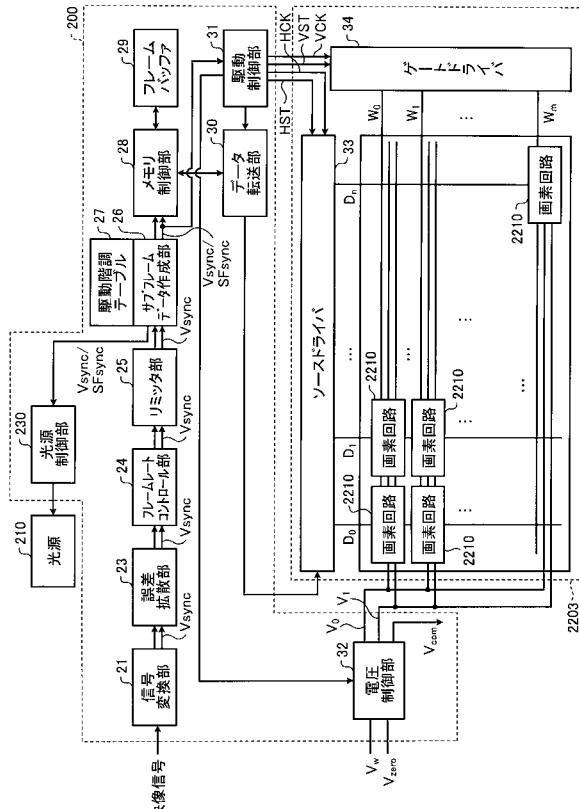

図14は、第2の実施形態に係る投射装置100bに含まれる映像処理・駆動部200および画素電極部2203の構成の例を示す。この第2の実施形態に係る投射装置100bは、上述した第1の実施形態に係る投射装置100aと同様に、映像信号のフレーム周期を分割して分割周期すなわちサブフレームSFを作成し、映像信号の画素毎に、画素の階調値に応じた数のサブフレームSFにおいてオン状態に制御することで階調を表現する、デジタル駆動方式が適用される。以下では、上述の第1の実施形態と同様に、階調が階調値「0」～「12」の13階調で表現され、フレーム周期を階調数より1少ない12の分割周期に等分割して、12のサブフレームSF1～SF12を作成するものとする。

## 【0073】

図14において、映像処理・駆動部200は、信号変換部21と、誤差拡散部23と、フレームレートコントロール部24と、リミッタ部25と、サブフレームデータ作成部26と、駆動階調テーブル27と、メモリ制御部28と、フレームバッファ29と、データ転送部30と、駆動制御部31と、電圧制御部32と、光源制御部230とを含む。

## 【0074】

また、画素電極部2203は、ソースドライバ33と、ゲートドライバ34と、各画素回路2210、2210、…とを含む。なお、ソースドライバ33およびゲートドライバ34は、画素電極部2203の外部に設けてよい。

## 【0075】

画素電極部2203において、各画素回路2210、2210、…は、マトリクス状に配列され、列方向に列データ線 $D_0$ 、 $D_1$ 、…、 $D_n$ によりそれぞれ接続され、行方向に行選択線 $W_0$ 、 $W_1$ 、…、 $W_m$ によりそれぞれ接続される。列データ線 $D_0$ 、 $D_1$ 、…、 $D_n$ は、ソースドライバ33にそれぞれ接続される。また、行選択線 $W_0$ 、 $W_1$ 、…、 $W_m$ は、ゲー

10

20

30

40

50

トドライバ34にそれぞれ接続される。

#### 【0076】

メモリ制御部28は、後述するサブフレームデータ作成部26からフレーム同期信号Vsyncと、サブフレーム同期信号SFSyncとが供給される。また、メモリ制御部28は、サブフレームデータ作成部26で作成された各サブフレームSFのサブフレームデータ(後述する)を、サブフレーム同期信号SFSyncに従い、サブフレームSF毎に分割されたフレームバッファ29に格納する。フレームバッファ29は、2つのフレームバッファを含むダブルバッファの構造になっており、メモリ制御部28は、一方のフレームバッファに映像信号データを格納している間、他方のフレームバッファからサブフレームデータを読み出すことができる。

10

#### 【0077】

駆動制御部31は、サブフレームデータ作成部26からフレーム同期信号Vsyncおよびサブフレーム同期信号SFSyncが供給され、サブフレームSF毎の処理のタイミングなどを制御する。駆動制御部31は、これら同期信号に基づき、データ転送部30への転送指示と、ソースドライバ33およびゲートドライバ34の制御とを行う。より具体的には、駆動制御部31は、フレーム同期信号Vsyncおよびサブフレーム同期信号SFSyncに基づき、垂直スタート信号VSTおよび垂直シフトクロック信号VCKと、水平スタート信号HSTおよび水平シフトクロック信号HCKとを生成する。

20

#### 【0078】

垂直スタート信号VSTおよび水平スタート信号HSTは、それぞれサブフレームSF先頭のタイミングと、ライン先頭のタイミングとを指定する。垂直シフトクロック信号VCKは、行選択線W<sub>0</sub>、W<sub>1</sub>、…、W<sub>m</sub>を指定する。また、水平シフトクロック信号HCKは、列データ線D<sub>0</sub>、D<sub>1</sub>、…、D<sub>n</sub>に対応した指定を行なう。垂直スタート信号VSTおよび垂直シフトクロック信号VCKは、ゲートドライバ34に供給される。また、水平スタート信号HSTおよび水平シフトクロック信号HCKは、ソースドライバ33に供給される。

30

#### 【0079】

データ転送部30は、駆動制御部31の制御に従い、メモリ制御部28に対して、指定したサブフレームSFのサブフレームデータをフレームバッファ29から読み出すように指示する。データ転送部30は、メモリ制御部28から、フレームバッファ29から読み出したサブフレームデータを受け取り、受け取ったサブフレームデータを、駆動制御部31の制御に従い例えればライン単位でソースドライバ33へと転送する。

30

#### 【0080】

ソースドライバ33は、1ライン分のサブフレームデータをデータ転送部30より受け取る毎に、対応する画素回路2210、2210、…に対して、列データ線D<sub>0</sub>、D<sub>1</sub>、…、D<sub>n</sub>を用いて同時に転送する。また、ゲートドライバ34は、行選択線W<sub>0</sub>、W<sub>1</sub>、…、W<sub>m</sub>のうち、駆動制御部31から供給された垂直スタート信号VSTおよび垂直シフトクロック信号VCKにより指定された行の行選択線をアクティブにする。これにより、指定された行の全ての列の画素回路2210に、画素毎のサブフレームデータが転送される。

40

#### 【0081】

駆動制御部31は、さらに、フレーム同期信号Vsyncおよびサブフレーム同期信号SFSyncに基づき、電圧タイミング信号を生成する。電圧タイミング信号は、電圧制御部32供給される。また、電圧制御部32に対して、電圧値が0Vのゼロ電圧V<sub>zero</sub>と、飽和電圧V<sub>w</sub>とが供給される。電圧制御部32は、電圧タイミング信号に示されるタイミングで、各画素回路2210、2210、…に対して、ゼロ電圧V<sub>zero</sub>および飽和電圧V<sub>w</sub>に基づく電圧を、プランギング電圧である電圧V<sub>0</sub>と、駆動電圧である電圧V<sub>1</sub>として供給する。また、電圧制御部32は、対向電極2201に供給するための共通電圧V<sub>com</sub>を出力する。なお、プランギング電圧および駆動電圧は、それぞれ、画素をオフ状態およびオン状態に制御する電圧に対応する。

#### 【0082】

50

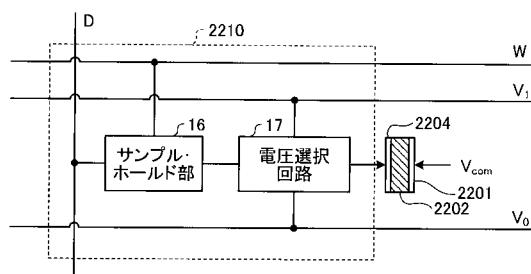

図15は、第2の実施形態に係る画素回路2210の一例の構成を示す。画素回路2210は、サンプル・ホールド部16と電圧選択回路17とを備え、電圧選択回路17の出力が、画素電極2204に供給される。なお、画素電極2204に液晶層2202を挟んで対向する対向電極2201に対して、共通電圧 $V_{com}$ が供給される。サンプル・ホールド部16は、S R A M(Static Random Access Memory)構造のフリップフロップよりなる。サンプル・ホールド部16は、列データ線Dと行選択線Wとから信号が入力され、出力は、電圧選択回路17に供給される。電圧選択回路17は、電圧制御部32から電圧 $V_0$ および電圧 $V_1$ が供給される。

#### 【0083】

次に、映像処理・駆動部200の動作について説明する。ディジタル方式の映像信号が信号変換部21に供給される。信号変換部21は、供給された映像信号からフレーム同期信号 $V_{sync}$ を抽出すると共に、当該映像信号を所定のビット数の映像信号データに変換して出力する。信号変換部21は、抽出したフレーム同期信号 $V_{sync}$ を誤差拡散部23、フレームレートコントロール部24、リミッタ部25およびサブフレームデータ作成部26にそれぞれ供給する。

#### 【0084】

また、信号変換部21から出力された映像信号データは、誤差拡散部23、フレームレートコントロール部24およびリミッタ部25によりそれぞれ所定の信号処理を施されてサブフレームデータ作成部26に供給される。

#### 【0085】

図16を用いて、第2の実施形態に係る、信号変換部21、誤差拡散部23、フレームレートコントロール部24およびサブフレームデータ作成部26における処理の流れを説明する。ここでは、信号変換部21に入力される映像信号がビット数が8ビットの映像信号データであるものとして説明する。

#### 【0086】

信号変換部21は、入力されたNビットの映像信号データを、よりビット数が大きい( $M + F + D$ )ビットのビット数を持つデータに変換する。ここで、値MはサブフレームSF数を2進数で表したときのビット数、値Dは誤差拡散部23により補間されるビット数、値Fはフレームレートコントロール部24により補間されるビット数を表している。なお値N、値M、値Fおよび値Dは、それぞれ1以上の整数である。図16の例では、値N=8、値D=4、値F=2、値M=4とされている。

#### 【0087】

信号変換部21は、例えばルックアップテーブルを用いてビット数の変換処理を行う。ここで、上述したように、一般的に、ディスプレイは、ガンマ値=2.2のガンマ曲線に従った入出力特性を持っている。そのため、映像出力装置101から出力される映像信号は、一般的には、ディスプレイで表示した際にリニアな階調表現が得られるように、ディスプレイのガンマ値の逆数のガンマ値によるガンマ曲線で補正された信号となっている。

#### 【0088】

信号変換部21は、投射部240の入出力特性を基準特性、すなわちガンマ値=2.2のガンマ曲線の特性に近付けるように予め調整されたルックアップテーブルを用いて、入力された映像信号データの変換を行う。この変換処理を、キャリブレーションと呼ぶ。このとき、信号変換部21は、ルックアップテーブルにより、Nビットの映像信号データを、( $M + F + D$ )ビットの映像信号データに変換して出力する。値N=8、値D=4、値F=2、値M=4であるこの例では、信号変換部21は、8ビットの映像信号データを、10ビットの映像信号データに変換して出力することになる。

#### 【0089】

信号変換部21において( $M + F + D$ )ビットに変換された映像信号データは、誤差拡散部23により下位Dビットの情報を周辺画素に拡散することによって、( $M + F$ )ビットのデータに変換される。値N=8、値D=4、値F=2、値M=4であるこの例では、

10

20

30

40

50

誤差拡散部 23 は、信号変換部 21 から出力された 10 ビットの映像信号データに対して、画素毎に、下位 4 ビットの情報を周辺画素に拡散し上位 6 ビットのデータに量子化する。

#### 【 0 0 9 0 】

誤差拡散法とは、表示すべき映像信号と実表示値との誤差（表示誤差）を周辺の画素に拡散することで階調不足を補う方法である。第 2 の実施形態においては、表示すべき映像信号の下位 4 ビットを表示誤差とし、注目画素の右隣の画素に表示誤差の 7 / 16 を、左下の画素に表示誤差の 3 / 16 を、直下の画素に表示誤差の 5 / 16 を、右下の画素に表示誤差の 1 / 16 を、それぞれ加える。この処理を、例えば 1 フレームの映像内の左から右に向けて画素毎に行い、この処理をさらに 1 フレームの映像内の上から下に向けてライン毎に行う。10

#### 【 0 0 9 1 】

誤差拡散部 23 の動作について、より詳細に説明する。注目画素は、上述のように誤差を拡散すると共に、直前の注目画素により拡散された誤差が加算される。誤差拡散部 23 は、入力された 10 ビットの映像信号データの注目画素に対して、先ず、直前の注目画素により拡散された誤差を誤差バッファから読み出して加算する。誤差拡散部 23 は、誤差バッファの値が加算された 10 ビットの注目画素を、上位の 6 ビットと下位の 4 ビットとに分割する。

#### 【 0 0 9 2 】

分割された下位の 4 ビットの値は、（下位 4 ビット、表示誤差）とするとき、次のようになる。20

( 0 0 0 0 , 0 )

( 0 0 0 1 , + 1 )

( 0 0 1 0 , + 2 )

( 0 0 1 1 , + 3 )

( 0 1 0 0 , + 4 )

( 0 1 0 1 , + 5 )

( 0 1 1 0 , + 6 )

( 0 1 1 1 , + 7 )

( 1 0 0 0 , - 7 )

( 1 0 0 1 , - 6 )

( 1 0 1 0 , - 5 )

( 1 0 1 1 , - 4 )

( 1 1 0 0 , - 3 )

( 1 1 0 1 , - 2 )

( 1 1 1 0 , - 1 )

( 1 1 1 1 , 0 )

#### 【 0 0 9 3 】

分割された下位の 4 ビットの値に対応する表示誤差は、誤差バッファへと加算され記憶される。また、分割された下位の 4 ビットの値に対して閾値比較を行ない、値が 2 進数表記で「1000」より大きい場合、上位 6 ビットの値に「1」が加算される。そして、上位の 6 ビットのデータが誤差拡散部 23 から出力される。40

#### 【 0 0 9 4 】

誤差拡散部 23 にて (M + F) ビットに変換された映像信号データは、フレームレートコントロール部 24 に入力される。フレームレートコントロール部 24 は、表示素子 220 の 1 画素の表示に対して m (m は 2 以上の整数) フレームを 1 周期として、その周期の n (n は m > n > 0 の整数) フレームではオン表示を行ない、残りの (m - n) フレームではオフ表示を行うことにより疑似的に階調を表示させるフレームコントロール処理を行う。

#### 【 0 0 9 5 】

10

20

30

40

50

換言すれば、フレームレートコントロール処理は、画面の書き換えと網膜の残像効果とを利用して中間階調を擬似的に作り出す処理である。例えば、ある画素を1フレーム毎に階調値「0」と階調値「1」とで交互に書き換えることにより、人間の目には、その画素が階調値「0」と階調値「1」の中間の階調値を持つ画素に見えることになる。そして、このような階調値「0」と階調値「1」との交互の書き換えを、例えば4フレームを1セットとして制御することによって、階調値「0」と階調値「1」との間に3段階の階調を擬似的に表現できるようになる。

#### 【0096】

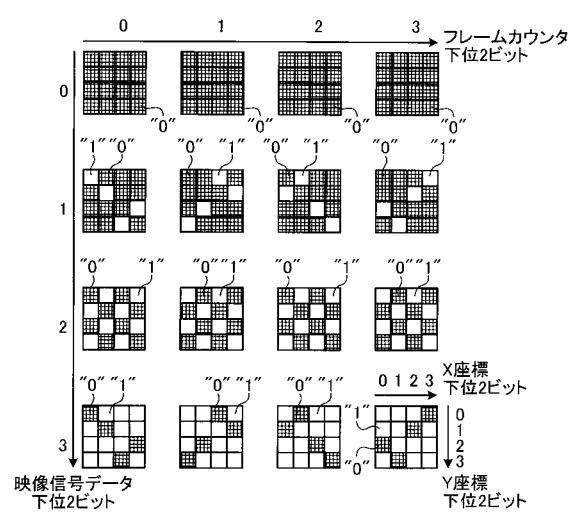

フレームレートコントロール部24は、図17に示されるフレームレートコントロールテーブルを備える。フレームレートコントロール部24は、さらに、例えばフレーム同期信号Vsyncに基づきフレームをカウントするフレームカウンタを備える。図17の例では、フレームレートコントロールテーブルは、それぞれのマスにおいて値「0」または「1」が指定される $4 \times 4$ のマトリクス（小マトリクスと呼ぶ）が、さらに $4 \times 4$ のマトリクス状（大マトリクスと呼ぶ）に配置されてなる。

10

#### 【0097】

大マトリクスの各列は、フレームカウンタのカウンタ値における下位2ビットの値で指定される。また、大マトリクスの各行は、フレームレートコントロール部24に入力される6ビットの映像信号データにおける下位2ビットの値で指定される。また、各小マトリクスの各列および各行は、画素の表示エリア内での位置情報、すなわち、画素の座標に基づき指定される。より具体的には、各小マトリクスの各列は、画素のX座標の下位2ビットの値で指定され、各行は、画素のY座標の下位2ビットの値で指定される。

20

#### 【0098】

フレームレートコントロール部24では、供給された(M+F)ビットの映像信号データの下位Fビットの値と、画素の位置情報およびフレームのカウント情報とから、フレームレートコントロールテーブル内の位置を特定し、その位置での値（値「0」または値「1」）を上位Mビットに加える。これにより、(M+F)ビットの映像信号データを、Mビットのデータに変換する。

20

#### 【0099】

値F=2、値M=4のこの例では、誤差拡散部23により出力された6ビットの映像信号データは、フレームレートコントロール部24に入力される。フレームレートコントロール部24は、この映像信号データの下位2ビットの情報と、表示エリアでの位置情報と、フレームカウンタ情報とより、フレームレートコントロールテーブルから値「0」または値「1」を取得し、取得した値を、入力された映像信号データの6ビットから分離された上位4ビットの値に加算する。

30

#### 【0100】

より具体的には、フレームレートコントロール部24は、入力された6ビットの映像信号データ（画素データ）を、上位の4ビットのデータと下位の2ビットのデータとに分割する。フレームレートコントロール部24は、分割して得た下位2ビットのデータと、当該画素の表示エリアでのX座標の下位2ビットおよびY座標の下位2ビットと、フレームカウンタのカウント値の下位2ビットとの合計8ビットの値を用いて、図17のフレームレートコントロールテーブルの大マトリクスおよび小マトリクスにおける位置を特定し、特定された位置により指定される値「0」または値「1」を取得する。フレームレートコントロール部24は、取得した値「0」または値「1」を、入力された映像信号データから分離した上位4ビットのデータに加算して、4ビットの映像信号データとして出力する。

40

#### 【0101】

このように、フレームレートコントロール部24により、画素のオン／オフが、画素のブロック単位で、階調毎に制御される。これにより、連続する2つの階調の間に、擬似的にさらに階調を表現することができる。

#### 【0102】

50

図14を参照し、フレームレートコントロール部24から出力された4ビットの映像信号データは、リミッタ部25に供給される。リミッタ部25は、供給された映像信号データの階調値の最大値を「12」に制限する。リミッタ部25で階調値の最大値が「12」に制限された映像信号データは、サブフレームデータ作成部26に供給される。サブフレームデータ作成部26は、駆動階調テーブル27を用いて、供給された映像信号データを12ビットのデータに変換する。

#### 【0103】

また、サブフレームデータ作成部26は、供給されたフレーム同期信号Vsyncに基づきサブフレーム同期信号SFSyncを生成する。サブフレームデータ作成部26は、フレーム同期信号Vsyncおよびサブフレーム同期信号SFSyncを、メモリ制御部28および駆動制御部31に供給すると共に、光源制御部230に供給する。

10

#### 【0104】

図18は、第2の実施形態に適用可能な駆動階調テーブル27の例を示す。図18において、上述した図3と同様に、各列は、左から右に向けてサブフレームSF1、SF2、…、SF12とされている。これらのうち、サブフレームSF1がフレーム周期の先頭のサブフレーム、サブフレームSF12がフレーム周期の後端のサブフレームとする。また、図18において、各行は、上から下に向けて階調値が0から12ずつ増加する。階調値「0」が最も低い（暗い）階調であり、階調値「12」が最も高い（明るい）階調である。

#### 【0105】

第2の実施形態では、上述の図3の第1の実施形態の例とは逆に、画素の階調値に応じた数のサブフレームを、フレーム周期の後端から順に選択し、選択したサブフレームにおいて、当該画素をオン状態に制御する。図18において、斜線を付して示す値「1」のセルは、画素をオン状態に制御することを示し、値「0」のセルは、画素をオフ状態に制御することを示す。駆動階調テーブル27は、このように、画素のオン／オフ制御を示す値が、各サブフレームSF1～SF12と階調値とに関連付けられて格納される。

20

#### 【0106】

このように、第2の実施形態においても、上述の第1の実施形態と同様に、オンおよびオフ制御を行うサブフレームが、階調毎に予め割り当てられる。

#### 【0107】

サブフレームデータ作成部26は、映像信号データに従い駆動階調テーブル27を参照し、サブフレームSF毎に、各画素のデータを値「0」または値「1」のデータ（以下、0／1データと呼ぶ）に変換し、サブフレームデータを作成する。

30

#### 【0108】

例えば、上述した図6を参照し、それぞれ階調値が「3」、「1」、「0」、「5」および「9」である座標 $(x_0, y_0) \sim (x_4, y_0)$ の各画素は、サブフレームSF1において、値「0」、「0」、「0」、「0」および「0」の各0／1データに変換され、サブフレームSF1のサブフレームデータとされる。各画素は、サブフレームSF4で、それぞれ値「0」、「0」、「0」、「0」および「1」の各0／1データに変換され、サブフレームSF4のサブフレームデータとされる。また、サブフレームSF12において、それぞれ値「1」、「1」、「0」、「1」および「1」の各0／1データに変換され、サブフレームSF12のサブフレームデータとされる。

40

#### 【0109】

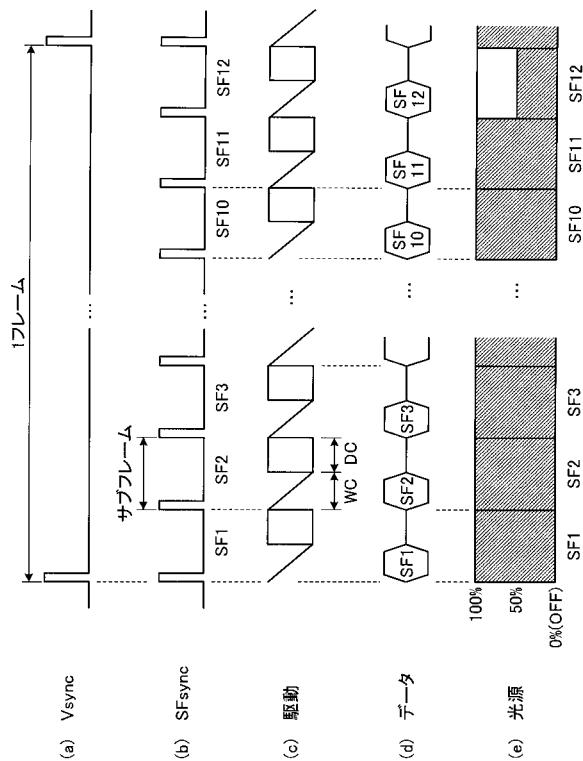

図19は、第2の実施形態に係る制御の例を示すタイムチャートである。図19のタイムチャートは、上述した図5のタイムチャートと対応するもので、表示素子220に関する駆動タイミングと、光源210の駆動タイミングとが含まれている。図19(a)および図19(b)は、それぞれフレーム同期信号Vsyncおよびサブフレーム同期信号SFSyncの例を示す。図19(b)の例では、上述の図18に対応し、1フレーム周期を階調数より1少ない12のサブフレームSF1～SF12に分割している。

#### 【0110】

図19(c)は、表示素子210の駆動タイミングの例を示し、図19(d)は、映像

信号データの画素電極部 2203への転送タイミングの例を示す。また、図19(e)は、光源210の光量制御の例を示す。

#### 【0111】

図19(c)において、期間WCは、画素電極部2203に含まれる全ての画素回路2210にサブフレームSF毎の映像信号データを転送するデータ転送期間を示す。期間DCは、画素回路2210を駆動する際の駆動期間を示す。1つのサブフレームSFに期間WCおよび期間DCが配置される。期間WCは、サブフレームSFの開始タイミングに対応して開始され、期間WCの終了後、期間DCが開始される。期間DCは、サブフレームSFの終了タイミングに対応して終了される。

10

1フレーム周期内で、時間軸方向に先頭からサブフレームSF1、SF2、…、SF11、SF12の順番で、フレームバッファ29から各サブフレームSF1、SF2、…、SF11、SF12のサブフレームデータが読み出されて、期間WCにおいて各画素回路2210に転送される。転送されたサブフレームデータは、各画素回路2210のサンプル・ホールド部16にそれぞれ保持される。

#### 【0112】

一例として、データ転送部30は、駆動制御部31の制御に従い、サブフレームデータをライン単位でソースドライバ33に転送する。ソースドライバ33は、駆動制御部31の制御に従い、転送されたサブフレームデータを、例えば、各データ線D<sub>0</sub>、D<sub>1</sub>、…、D<sub>n</sub>にそれぞれ対応するレジスタに画素毎に書き込み保持する。ここで画素毎に保持されるデータは、画素の階調値が駆動階調テーブル27に基づき変換された値「0」または値「1」の0/1データとなる。

20

#### 【0113】

また、ゲートドライバ34は、駆動制御部31の制御に従い、サブフレームデータのライン単位での転送タイミングに対応して行選択線W<sub>0</sub>、W<sub>1</sub>、…、W<sub>m</sub>を順次選択する。これにより、ソースドライバ33に保持された各画素の0/1データが、行選択線W<sub>0</sub>、W<sub>1</sub>、…、W<sub>m</sub>により選択された各画素回路2210のサンプル・ホールド部16に取得され保持される。これにより、期間WC内で、画素電極部2203に含まれる全ての画素回路2210において、サンプル・ホールド部16に画素の0/1データが保持される。

30

#### 【0114】

期間DCでは、画素電極部2203に含まれる全ての画素回路2210が駆動される。図15を参照して、画素回路2210の駆動制御について説明する。各画素回路2210に0/1データを転送する期間WCでは、サンプル・ホールド部16に保持される0/1データの値に関わらず、画素をプランギング状態とする必要がある。そのため、電圧制御部32は、駆動制御部31の制御に従い、期間WCでは、電圧V<sub>0</sub>と、電圧V<sub>1</sub>と、共通電圧V<sub>com</sub>とを同電位（例えば接地電位）に設定する。

#### 【0115】

期間WCが終了すると、駆動期間である期間DCが開始される。電圧制御部32は、駆動制御部31の制御により、期間DCを等分割した期間DC#1およびDC#2それぞれで、各画素回路2210を駆動する。電圧制御部32は、期間DC#1では、電圧V<sub>1</sub>が飽和電圧V<sub>w</sub>に、電圧V<sub>0</sub>および共通電圧V<sub>com</sub>を接地電位に、それぞれ設定する。また、電圧制御部32は、期間DC#2では、期間DC#1とは逆に、電圧V<sub>1</sub>を接地電位に、電圧V<sub>0</sub>および共通電圧V<sub>com</sub>を飽和電圧V<sub>w</sub>に設定する。

40

#### 【0116】

画素回路2210において、サンプル・ホールド部16に保持される0/1データが値「0」の場合、電圧選択回路17は、電圧V<sub>0</sub>を画素電極2204に印加する電圧として選択する。期間DC#1では、画素電極2204の電圧V<sub>pe</sub>と対向電極2201に印加される共通電圧V<sub>com</sub>は、それぞれ接地電位となる。したがって、液晶層2202に印加される電圧は、0[V]となり、液晶層2202の駆動状態がプランギング状態（オフ状態）となる。

50

## 【0118】

画素回路 2210において、サンプル・ホールド部 16に保持される0/1データが値「1」の場合、電圧選択回路 17は、電圧  $V_1$ を画素電極 2204に印加する電圧として選択する。期間 DC #1では、画素電極 2204の電圧  $V_{pe}$ が飽和電圧  $V_w$ 、対向電極 2201に印加される共通電圧  $V_{com}$ は接地電位となる。したがって、液晶層 2202に印加される電圧は、対向電極 2201の電位を基準として、正の飽和電圧  $V_w$ となり、液晶層 2202が駆動状態（オン状態）となる。また、期間 DC #2では、画素電極 2204の電圧  $V_{pe}$ が接地電位、対向電極 2201に印加される共通電圧  $V_{com}$ が飽和電圧  $V_w$ （飽和電圧 +  $V_w$ ）となり、液晶層 2202に印加される電圧は、対向電極 2201の電位を基準として、負の飽和電圧  $V_w$ （飽和電圧 -  $V_w$ ）となり、液晶層 2202が駆動状態（オン状態）となる。

10

## 【0119】

液晶層 2202に絶対値が等しく正負が異なる電圧（飽和電圧 +  $V_w$ および -  $V_w$ ）を同じ期間印加することにより、長時間平均して液晶層 2202に印加する電圧が0[V]となり、焼き付きを防止することができる。

## 【0120】

図19の説明に戻り、図19(e)は、光源制御部 230による光源 210の光量制御の例を示す。図18を用いて説明したように、第2の実施形態では、サブフレーム SF 12が黒表示（階調値「0」）を除く最も低い階調において画素がオン制御されるサブフレームとなっており、このサブフレーム SF 12では、階調値「0」の階調を除く各階調で共通して画素が駆動状態（オン制御）とされる。そのため、光源制御部 230は、サブフレームデータ作成部 26から供給されるフレーム同期信号  $V_{sync}$ およびサブフレーム同期信号  $SF_{sync}$ に従い、フレーム周期の後端のサブフレーム SF 12において光源 210の光量を例えば50%の低減比率で低減させる制御を行い、他のサブフレーム SF 1 ~ SF 11では、光源 210の光量を100%の光量に制御している。

20

## 【0121】

このように、フレーム周期の後端側で光源 210の光量を低減させる光源制御を行っても、上述した第1の実施形態と同様に、低い階調の範囲での入力値の映像信号による映像の表示が、既存技術に対してより意図した映像に近付き、既存技術に対して表示品質向上させることができる。

30

## 【符号の説明】

## 【0122】

- 16 サンプル・ホールド部

- 17 電圧選択回路

- 21 信号変換部

- 23 誤差拡散部

- 24 フレームレートコントロール部

- 26 サブフレームデータ作成部

- 27 駆動階調テーブル

- 28 メモリ制御部

- 29 フレームバッファ

- 30 データ転送部

- 31 駆動制御部

- 32 電圧制御部

- 33 ソースドライバ

- 34 ゲートドライバ

- 100, 100a, 100b 投射装置

- 101 映像出力装置

- 102 被投射媒体

- 110 映像処理部

40

50

|   |   |   |               |

|---|---|---|---------------|

| 1 | 1 | 1 | 駆動部           |

| 1 | 1 | 2 | サブフレーム作成部     |

| 1 | 1 | 3 | , 2 3 0 光源制御部 |

| 1 | 2 | 0 | , 2 1 0 光源    |

| 1 | 2 | 1 | , 2 2 0 表示素子  |

| 1 | 2 | 2 | , 2 4 0 投射部   |

| 2 | 0 | 0 | 映像処理・駆動部      |

| 2 | 2 | 0 | 1 対向電極        |

| 2 | 2 | 0 | 2 液晶層         |

| 2 | 2 | 0 | 3 画素電極部       |

| 2 | 2 | 0 | 4 画素電極        |

| 2 | 2 | 1 | 0 画素回路        |

10

【 义 1 】

【 図 2 】

( 3 )

【図4】

【図5】

【図6】

|                | x <sub>0</sub> | x <sub>1</sub> | x <sub>2</sub> | x <sub>3</sub> | x <sub>4</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|

| y <sub>0</sub> | 3              | 1              | 0              | 5              | 9              |

| y <sub>1</sub> | 1              | 2              | 4              | 6              | 10             |

| y <sub>2</sub> | 1              | 2              | 5              | 6              | 10             |

| y <sub>3</sub> | 2              | 3              | 8              | 5              | 9              |

| y <sub>4</sub> | 2              | 4              | 9              | 4              | 8              |

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【 図 1 3 】

【図14】

〔 15 〕

【 16 】

【図17】

【図18】

| SF | SF1 | SF2 | SF3 | SF4 | SF5 | SF6 | SF7 | SF8 | SF9 | SF10 | SF11 | SF12 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0    |

| 1  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 1    |

| 2  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 3  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 4  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 5  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 6  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 7  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 8  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 9  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 10 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 11 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1    | 1    |

| 12 | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1    | 1    | 1    |

【図19】

---

フロントページの続き

|                         |               |            |

|-------------------------|---------------|------------|

| (51) Int.CI.            | F I           | テーマコード(参考) |

| G 0 2 F 1/133 (2006.01) | G 0 3 B 21/14 | A          |

|                         | G 0 3 B 21/00 | E          |

|                         | G 0 2 F 1/133 | 5 3 5      |

F ターム(参考) 5C006 AA13 AA14 AF01 AF07 AF13 AF44 AF45 BB15 BB28 BB29

BC16

5C080 AA10 BB05 EE19 EE28 EE29 FF11 GG12 JJ01 JJ02 JJ04

JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 光源驱动装置，光源驱动方法及显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2019168706A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2019-10-03 |

| 申请号            | JP2019092736                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2019-05-16 |

| [标]申请(专利权)人(译) | JVC 建伍株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | JVC建伍公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 中島伸基<br>相崎隆嗣                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 中島 伸基<br>相崎 隆嗣                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G09G3/34 G03B21/14 G03B21/00 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F1分类号          | G09G3/36 G09G3/20.612.J G09G3/34.J G09G3/20.612.U G09G3/20.641.E G03B21/14.A G03B21/00.E G02F1/133.535                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F-Term分类号      | 2H193/ZD25 2H193/ZD27 2H193/ZD29 2H193/ZF13 2H193/ZG48 2H193/ZG60 2H193/ZR02 2K203 /FA24 2K203/FA62 2K203/GA40 2K203/GA44 2K203/GA45 2K203/GA52 2K203/GA59 2K203/GA60 2K203/GB45 2K203/GB62 2K203/GB69 2K203/HB05 2K203/MA06 5C006/AA13 5C006/AA14 5C006 /AF01 5C006/AF07 5C006/AF13 5C006/AF44 5C006/AF45 5C006/BB15 5C006/BB28 5C006/BB29 5C006/BC16 5C080/AA10 5C080/BB05 5C080/EE19 5C080/EE28 5C080/EE29 5C080/FF11 5C080 /GG12 5C080/JJ01 5C080/JJ02 5C080/JJ04 5C080/JJ05 5C080/JJ06 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

### 摘要(译)

解决方案：创建一个通过分割视频信号帧而获得的分割周期。根据视频信号，根据预先分配给每个灰度的划分周期，针对每个像素控制显示元件的ON / OFF。控制用于使显示元件照射光的光源的光量，以使得与除黑色显示之外的与最低灰度对应的第一划分时段处的第一光量为小于a的光量。在除第一除法周期以外的第二除法周期中第二光量，并且除黑色显示外，所有渐变中均包含第一光量。选定的图：图5