(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-21159

(P2017-21159A)

(43) 公開日 平成29年1月26日(2017.1.26)

| (51) Int.Cl.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>G09G 3/36 (2006.01)</b>   | G09G 3/36   | 2H088       |

| <b>G02F 1/1368 (2006.01)</b> | G02F 1/1368 | 2H192       |

| <b>G09G 3/20 (2006.01)</b>   | G09G 3/20   | 624B        |

| <b>G02F 1/13 (2006.01)</b>   | G09G 3/20   | 611A        |

| <b>G11C 11/412 (2006.01)</b> | G09G 3/20   | 621H        |

審査請求 未請求 請求項の数 9 O L (全 16 頁) 最終頁に続く

|           |                              |            |                                                                                                               |

|-----------|------------------------------|------------|---------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2015-138183 (P2015-138183) | (71) 出願人   | 000001960<br>シチズン時計株式会社<br>東京都西東京市田無町六丁目1番12号                                                                 |

| (22) 出願日  | 平成27年7月9日 (2015.7.9)         | (74) 代理人   | 100104190<br>弁理士 酒井 昭徳                                                                                        |

|           |                              | (72) 発明者   | 永田 洋一<br>東京都西東京市田無町六丁目1番12号<br>シチズンホールディングス株式会社内                                                              |

|           |                              | F ターム (参考) | 2H088 EA22 HA06 HA08 MA20<br>2H192 AA24 CB23 CB24 CB26 FB02<br>GD61<br>5B015 HH01 HH03 JJ03 KA09 KA13<br>KB65 |

最終頁に続く

## (54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】 1画素あたりの面積の増加を抑えつつ、消費電力の低減を図ること。

【解決手段】 画素回路 110 は、表示の画素ごとに設けられた CMOS 型の SRAM セルである。また、画素回路 110 は、負荷抵抗回路部 131 と記憶回路部 132 との間に保護用の MOS トランジスタ 117, 118 を有する。記憶回路部 132 には、負荷抵抗回路部 131 および保護用の MOS トランジスタ 117, 118 より高電圧への耐性が低いトランジスタが用いられる。

【選択図】 図 1

## 【特許請求の範囲】

## 【請求項 1】

表示の画素ごとに設けられた CMOS (Complementary Metal Oxide Semiconductor) 型の SRAM (Static Random Access Memory) セルであって、

負荷抵抗回路部と記憶回路部との間に保護用の MOS トランジスタを有し、

前記記憶回路部のトランジスタに、前記負荷抵抗回路部のトランジスタおよび前記保護用の MOS トランジスタより高電圧への耐性が低いトランジスタを用いた SRAM セルと、

前記 SRAM セルのそれぞれにおける前記負荷抵抗回路部と前記保護用の MOS トランジスタとの間から出力される信号に基づく液晶表示を行う液晶表示部と、

を備えることを特徴とする液晶表示装置。

## 【請求項 2】

前記負荷抵抗回路部に P 型 MOS トランジスタを用い、前記記憶回路部に N 型 MOS トランジスタを用いる

ことを特徴とする請求項 1 に記載の液晶表示装置。

## 【請求項 3】

前記負荷抵抗回路部に N 型 MOS トランジスタを用い、前記記憶回路部に P 型 MOS トランジスタを用いる

ことを特徴とする請求項 1 に記載の液晶表示装置。

## 【請求項 4】

前記負荷抵抗回路部に負荷抵抗を用い、前記記憶回路部に N 型 MOS トランジスタを用いる

ことを特徴とする請求項 1 に記載の液晶表示装置。

## 【請求項 5】

前記負荷抵抗回路部に負荷抵抗を用い、前記記憶回路部に P 型 MOS トランジスタを用いる

ことを特徴とする請求項 1 に記載の液晶表示装置。

## 【請求項 6】

前記負荷抵抗回路部には最大で第 1 電圧の電圧が印加され、

前記保護用の MOS トランジスタは、前記記憶回路部に印加される最大の電圧を前記第 1 電圧より低い第 2 電圧に制限する、

ことを特徴とする請求項 1 ~ 5 のいずれか一つに記載の液晶表示装置。

## 【請求項 7】

前記 SRAM セルのレプリカ回路と、

前記記憶回路部に対応する前記レプリカ回路のトランジスタと、前記保護用の MOS トランジスタに対応する前記レプリカ回路のトランジスタと、の間の最大の電圧が前記第 2 電圧に近づくように、前記保護用の MOS トランジスタに対応する前記レプリカ回路のトランジスタのゲート電圧を調整し、前記 SRAM セルにおける前記保護用の MOS トランジスタのゲートに、前記保護用の MOS トランジスタに対応する前記レプリカ回路のトランジスタのゲート電圧と同じ電圧を印加する調整回路と、

を備えることを特徴とする請求項 6 に記載の液晶表示装置。

## 【請求項 8】

前記レプリカ回路および前記調整回路は、前記 SRAM セルのうちの複数の SRAM セルにおいて共有されることを特徴とする請求項 7 に記載の液晶表示装置。

## 【請求項 9】

前記負荷抵抗回路部に印加される最大の電圧を、前記液晶表示を行う期間においては前記第 1 電圧に制御し、前記 SRAM セルへの信号の転送期間においては前記第 1 電圧より低い第 3 電圧に制御する制御回路を備えることを特徴とする請求項 6 ~ 8 のいずれか一つに記載の液晶表示装置。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置に関する。

**【背景技術】****【0002】**

従来、LCOS (Liquid Crystal On Silicon) などの空間光変調器によって変調した信号光を光情報記録媒体に照射してホログラムを形成することで情報信号を記録するホログラフィックメモリが知られている。空間光変調器には、たとえば液晶セルを用いた液晶表示装置が用いられる。液晶表示装置において、液晶セルの駆動にはある程度の高電圧を要するため、液晶セルを駆動する画素回路には、高電圧の駆動信号を液晶セルへ出力可能な構成が求められる。

**【0003】**

また、FLC (Ferroelectric Liquid Crystal : 強誘電性液晶) は反転電流が多く、DRAM (Dynamic Random Access Memory) では画素データを保持できないため、液晶表示装置には、メモリセルとしてたとえばSRAM (Static Random Access Memory) セルが用いられる。また、画素回路にSRAMを用いた液晶表示装置において、水平ドライバにレベルシフタを設け、ビット線や画素を高電圧で動作させる構成が知られている(たとえば、下記特許文献1参照。)。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2014-215496号公報(図1)

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、上述した従来技術では、たとえば画素回路のSRAMの全体を高電圧で動作させるため、画素回路のSRAMの各トランジスタに高耐圧素子を用いることになり、1画素あたりの面積が増加するという問題がある。また、たとえばビット線の電圧振幅が大きくなるため、ビット線の充放電により消費電力が大きくなるという問題がある。

**【0006】**

本発明は、上述した従来技術による問題点を解消するため、1画素あたりの面積の増加を抑えつつ、消費電力の低減を図ることができる液晶表示装置を提供することを目的とする。

**【課題を解決するための手段】****【0007】**

上述した課題を解決し、目的を達成するため、本発明にかかる液晶表示装置は、表示の画素ごとに設けられたCMOS (Complementary Metal Oxide Semiconductor) 型のSRAM (Static Random Access Memory) セルであって、負荷抵抗回路部と記憶回路部との間に保護用のMOSトランジスタを有し、前記記憶回路部のトランジスタに、前記負荷抵抗回路部のトランジスタおよび前記保護用のMOSトランジスタより高電圧への耐性が低いトランジスタを用いたSRAMセルと、前記SRAMセルのそれぞれにおける前記負荷抵抗回路部と前記保護用のMOSトランジスタとの間から出力される信号に基づく液晶表示を行う液晶表示部と、を備える。

**【0008】**

これにより、液晶表示に要する高電圧の信号を液晶表示部に出力しつつ、SRAMにおける記憶回路部に印加される最大電圧を低くし、SRAMにおける記憶回路部に小型の素子を用いることが可能になる。

10

20

30

40

50

## 【発明の効果】

## 【0009】

本発明の一側面によれば、1画素あたりの面積の増加を抑えつつ、消費電力の低減を図ることができるという効果を奏する。

## 【図面の簡単な説明】

## 【0010】

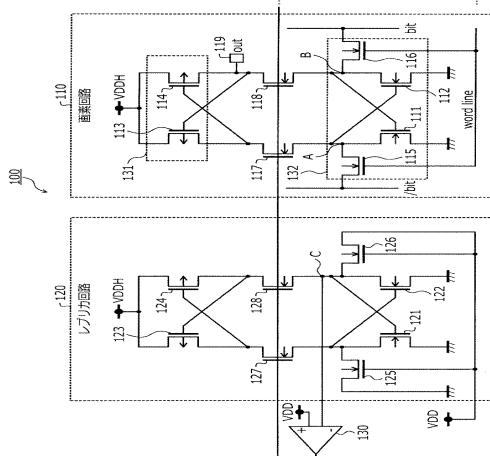

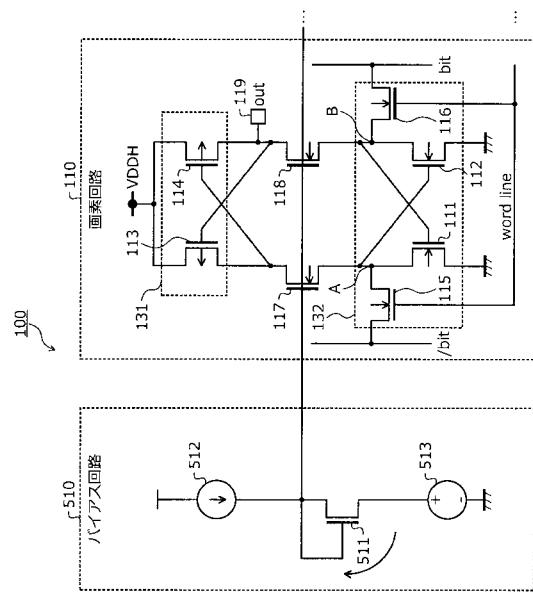

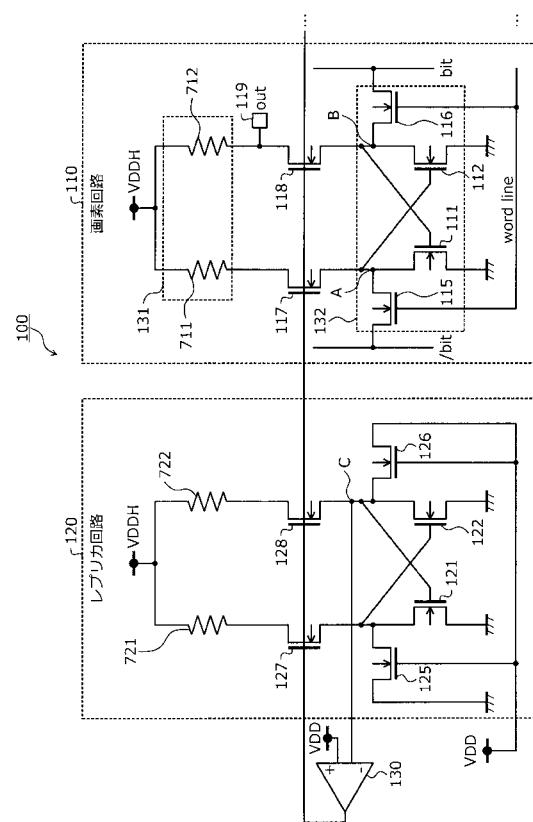

【図1】図1は、実施の形態にかかる液晶駆動回路の一例を示す図である。

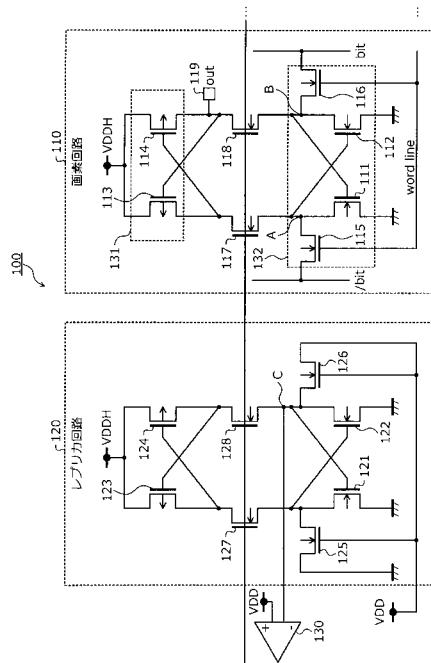

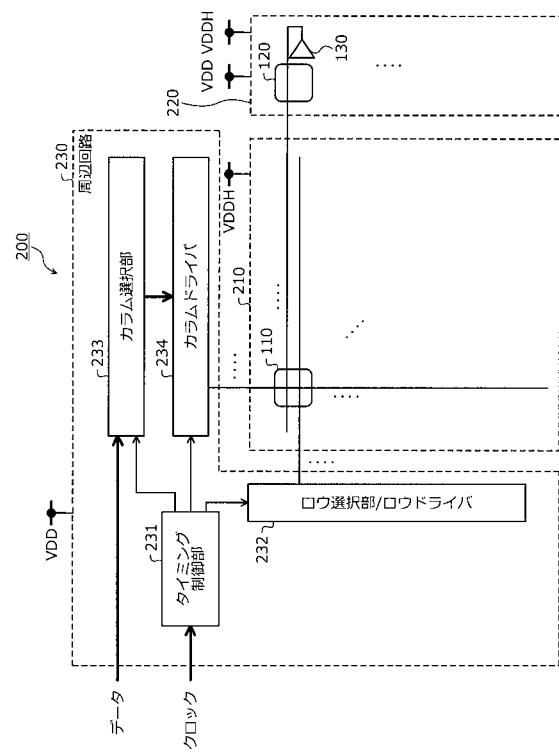

【図2】図2は、実施の形態にかかる液晶駆動回路を適用した液晶表示装置の一例を示す図である。

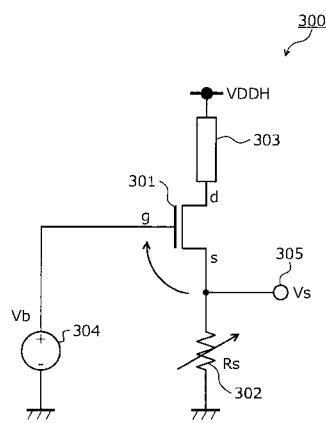

【図3】図3は、実施の形態にかかる画素回路を模したゲート接地の回路の一例を示す図である。

10

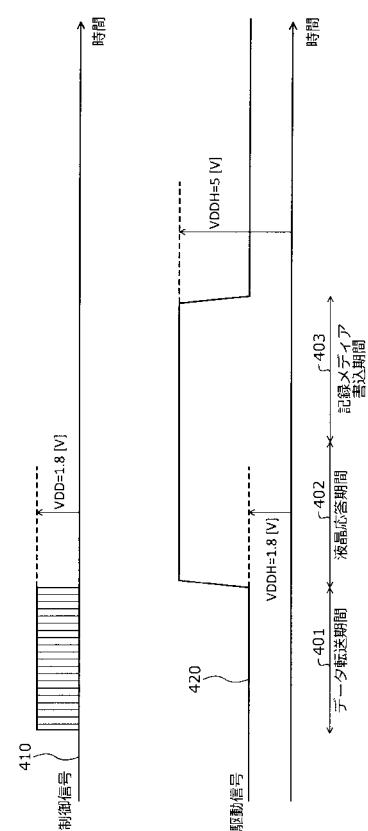

【図4】図4は、実施の形態にかかる駆動信号の電圧の制御の一例を示す図である。

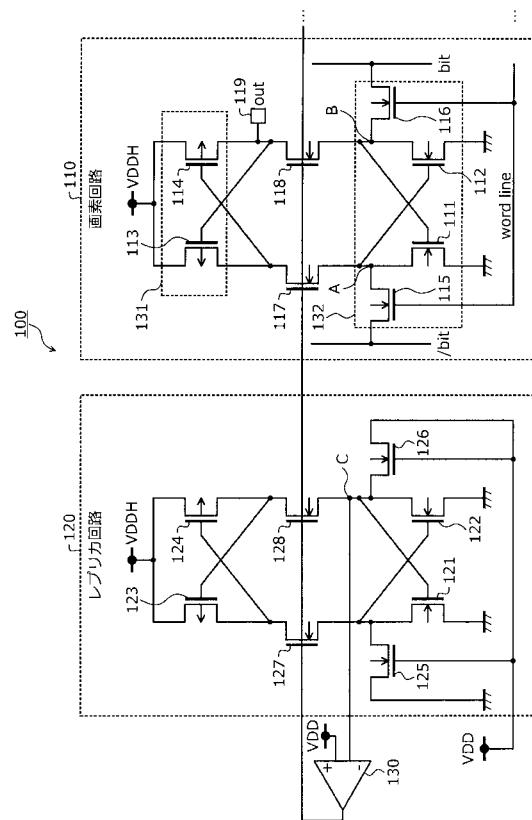

【図5】図5は、実施の形態にかかる液晶駆動回路の他の構成例1を示す図である。

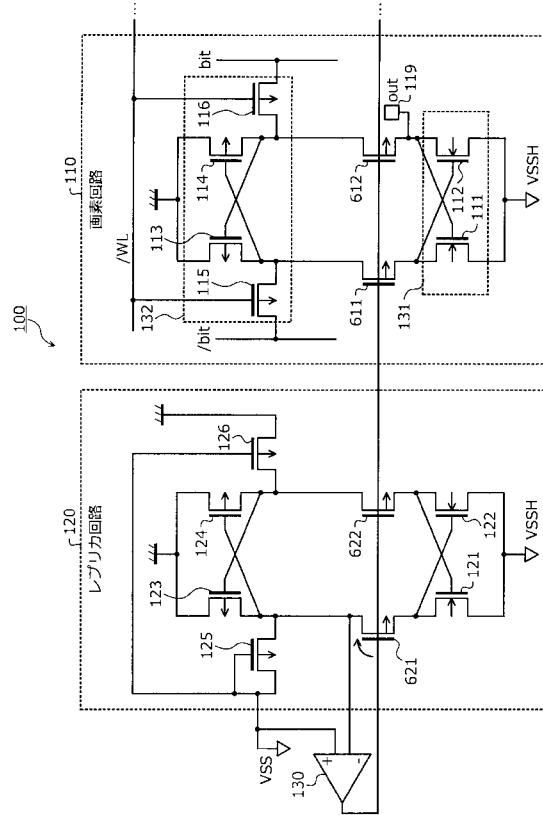

【図6】図6は、実施の形態にかかる液晶駆動回路の他の構成例2を示す図である。

【図7】図7は、実施の形態にかかる液晶駆動回路の他の構成例3を示す図である。

## 【発明を実施するための形態】

## 【0011】

以下に図面を参照して、本発明にかかる液晶表示装置の実施の形態を詳細に説明する。

## 【0012】

## (実施の形態)

20

## (実施の形態にかかる液晶駆動回路)

図1は、実施の形態にかかる液晶駆動回路の一例を示す図である。図1に示すように、実施の形態にかかる液晶駆動回路100は、複数の画素回路110と、レプリカ回路120と、差動アンプ130と、を備える。液晶駆動回路100は、液晶セルを用いた液晶表示部(たとえば図2に示す液晶表示部210)を駆動することにより液晶表示部に画像を表示させる回路である。

## 【0013】

画素回路110は、液晶駆動回路100によって駆動する液晶表示部の画素ごとに設けられた、液晶表示部の画素を駆動する回路である。図1においては画素ごとに設けられた画素回路110のうちの1つの画素回路110について説明するが、画素ごとに設けられた画素回路110のうちの他の画素回路110についても同様である。

30

## 【0014】

画素回路110は、8個のトランジスタ(MOSトランジスタ111～118)を備える。画素回路110においては、6個のMOSトランジスタ(MOSトランジスタ111～116)によってCMOS(Complementary Metal Oxide Semiconductor:相補型金属酸化膜半導体)型のSRAMセルが構成される。このようなSRAMは、たとえば完全CMOS型のSRAMセルや、フルCMOS型のSRAMと呼ばれる場合もある。MOSトランジスタ111, 112, 115, 116はN型MOSトランジスタである。MOSトランジスタ113, 114はP型MOSトランジスタである。

40

## 【0015】

画素回路110においては、MOSトランジスタ111, 113によって第1のインバータが構成される。また、画素回路110においては、MOSトランジスタ112, 114によって第2のインバータが構成される。そして、第1のインバータの入力と第2のインバータの出力とを接続し、第1のインバータの出力と第2のインバータの入力とを接続することによってSRAMセルが構成される。

## 【0016】

SRAMセルにおいて、駆動トランジスタとしてのMOSトランジスタ111, 112と、負荷トランジスタとしてのMOSトランジスタ113, 114と、によってフリップフロップが構成される。また、SRAMセルにおいて、MOSトランジスタ115, 11

50

6は選択用トランジスタとして用いられる。

【0017】

また、MOSトランジスタ113, 114は、負荷トランジスタとして動作することにより、SRAMセルにおいて電源と記憶回路部132との間の負荷として機能する負荷抵抗回路部131を構成する。また、MOSトランジスタ111, 112, 115, 116は、MOSトランジスタ111, 112が駆動トランジスタとして動作し、MOSトランジスタ115, 116が選択用トランジスタとして動作することにより、SRAMセルにおいて情報を記憶する記憶回路部132を構成する。

【0018】

ラッチノードAは、MOSトランジスタ111, 113によって構成される第1のインバータの出力であり、MOSトランジスタ112, 114によって構成される第2のインバータの入力である。ラッチノードBは、MOSトランジスタ112, 114によって構成される第2のインバータの出力であり、MOSトランジスタ111, 113によって構成される第1のインバータの入力である。

【0019】

対になったビット線(bit)および反転ビット線(/bit)は、互いに逆の論理状態(たとえば“H”および“L”)となる各ビット線である。“H”は、“L”よりも高い電圧である。“L”は、“H”よりも低い電圧である。たとえば“H”および“L”は互いに極性が異なる各信号である。

【0020】

ラッチノードBが“H”的場合にはラッチノードAに“L”が出力される。これにより、MOSトランジスタ112, 114によって構成される第2のインバータはラッチノードBを元の“H”に保つ。一方、ラッチノードBが“L”的場合にはラッチノードAに“H”が出力される。これにより、MOSトランジスタ112, 114によって構成される第2のインバータはラッチノードBを元の“L”に保つ。

【0021】

画素回路110に“H”を書き込むには、ワード線(word line)を“H”にしてMOSトランジスタ115, 116のゲートを開いた状態(オンにした状態)でビット線(bit)を“H”にする。これにより、反転ビット線(/bit)は“L”となり、ラッチノードAは“L”、ラッチノードBは“H”となる。

【0022】

逆に、画素回路110に“L”を書き込むには、ワード線を“H”にしてMOSトランジスタ115, 116のゲートを開いた状態でビット線(bit)を“L”にする。これにより、反転ビット線(/bit)は“H”となり、ラッチノードAは“H”、ラッチノードBは“L”となる。

【0023】

画素回路110に値を書き込んだ後は、ワード線を“L”にしてMOSトランジスタ115, 116のゲートを閉じた状態(オフにした状態)とすることにより、書き込まれた値がフリップフロップにより安定して保持される。

【0024】

また特に、画素回路110は、保護用のMOSトランジスタ117, 118(シールド素子)を備える。MOSトランジスタ117は、MOSトランジスタ111とMOSトランジスタ113との間に設けられている。MOSトランジスタ118は、MOSトランジスタ112とMOSトランジスタ114との間に設けられている。MOSトランジスタ117, 118の各ゲートは差動アンプ130の出力に接続されている。図1に示す例ではMOSトランジスタ117, 118はN型MOSである。

【0025】

出力端子119(out)は、MOSトランジスタ114のドレインとMOSトランジスタ118のソースとの間に設けられている。画素回路110に書き込まれた値は、駆動信号として、出力端子119から液晶表示部の画素へ出力される。この駆動信号の電圧は

10

20

30

40

50

、MOSトランジスタ113, 114のソースに接続された電圧源の電圧VDDHとなる。電圧VDDHは、液晶表示部における液晶駆動に要する電圧である。

【0026】

このように、実施の形態にかかる液晶駆動回路100においては、SRAMセルを構成するP型MOSトランジスタ(MOSトランジスタ113, 114)とN型MOSトランジスタ(MOSトランジスタ111, 112, 115, 116)との間に保護用のトランジスタ(MOSトランジスタ117, 118)が設けられる。

【0027】

そして、P型MOSトランジスタ(MOSトランジスタ113, 114)および保護用のトランジスタ(MOSトランジスタ117, 118)には、高電圧への耐性(劣化あるいは破壊耐性)が比較的高いトランジスタを用いる。また、N型MOSトランジスタ(MOSトランジスタ111, 112, 115, 116)には、高電圧への耐性(破壊耐性)がP型MOSトランジスタ(MOSトランジスタ113, 114)および保護用のトランジスタ(MOSトランジスタ117, 118)より低いトランジスタを用いる。トランジスタの高電圧への耐性については、例としてはゲート酸化膜厚やウェルなどの濃度といった素子構造そのものや、ゲートの幅などの設計によって調整可能である。

10

【0028】

たとえば、MOSトランジスタ113, 114, 117, 118は、出力端子119から出力される駆動信号の最大の電圧VDDHに十分に耐えられる高耐圧素子とする。これにより、駆動信号の最大の電圧VDDHによるMOSトランジスタ113, 114, 117, 118の破壊を回避しつつ、出力端子119から出力される駆動信号は、電圧VDDHとGND(0[V])との間をスイングする高電圧の信号とすることができる。

20

【0029】

一方、MOSトランジスタ111, 112, 115, 116は、出力端子119から出力される駆動信号の最大の電圧VDDHに十分に耐えられない標準耐圧素子とする。これにより、MOSトランジスタ111, 112, 115, 116は、MOSトランジスタ113, 114, 117, 118よりも小型の素子によって実現することが可能になる。このため、たとえばMOSトランジスタ111~118の全てに高耐圧素子を用いる場合に比べて高耐圧素子の数を少なくし、画素回路110を小型化することができる。

30

【0030】

また、MOSトランジスタ117, 118をシールド素子として設けることにより、P型のMOSトランジスタ113, 114には最大でVDDH(第1電圧)の電流が流れるようにしつつ、N型のMOSトランジスタ111, 112, 115, 116に印加される最大の電圧をVDDHより低いVDD(第2電圧)に制限することができる。たとえば画素回路110が“H”をラッチしても、ラッチノードA, Bを電圧VDDHよりも低い電圧VDDに抑え、MOSトランジスタ111, 112, 115, 116の破壊を回避することができる。

【0031】

したがって、出力端子119に接続された液晶表示部の画素を高電圧(VDDH)で駆動しつつ、MOSトランジスタ111, 112, 115, 116を小型化することが可能になる。このため、複数の画素回路110のそれぞれを小型化し、液晶駆動回路100を小型化することができる。

40

【0032】

また、液晶駆動回路100のビット線やワード線へ入力される制御信号の最大の電圧を、電圧VDDHより低い電圧VDDとすることが可能になる。これにより、液晶駆動回路100のビット線やワード線へ制御信号を転送する周辺回路(たとえば図2に示す周辺回路230)の電源に、液晶表示部の駆動に要する電圧VDDHより低い電圧VDDの電源を用いることができる。このため、液晶駆動回路100のビット線やワード線へ制御信号を転送する周辺回路における消費電力を低減することができる。

50

【0033】

このように、液晶駆動回路 100 によれば、液晶表示に要する高電圧の駆動信号を液晶表示部に出力しつつ、CMOS型のSRAMにおけるN型のMOSトランジスタ 111, 112, 115, 116 に印加される最大電圧を低くし、MOSトランジスタ 111, 112, 115, 116 に小型の素子を用いることが可能になる。このため、1画素あたりの面積の増加を抑えつつ、消費電力の低減を図ることができる。

【0034】

レプリカ回路 120 および差動アンプ 130 は、MOSトランジスタ 117, 118 の各ゲート電圧を制御するバイアス回路として動作する。レプリカ回路 120 は、画素回路 110 のレプリカ回路である。差動アンプ 130 は、レプリカ回路 120 を用いて画素回路 110 のMOSトランジスタ 117, 118 のゲート電圧を調整する調整回路である。

10

【0035】

具体的には、レプリカ回路 120 は、CMOS型のSRAMセルを構成するMOSトランジスタ 121~128 を備える。MOSトランジスタ 121~128 は、それぞれ画素回路 110 のMOSトランジスタ 111~118 に対応し、それぞれMOSトランジスタ 111~118 と同じ電気的特性を有する。

【0036】

また、MOSトランジスタ 125, 126 の各ゲートには、電圧 VDDH より低い電圧 VDD の電源が接続されている。また、MOSトランジスタ 121~128 によって構成されるSRAMセルにおけるビット線 (bit) に対応する位置には電圧 VDD の電源が接続されている。また、MOSトランジスタ 121~128 によって構成されるSRAMセルにおける反転ビット線 (/bit) に対応する位置は接地されている。すなわち、MOSトランジスタ 121~128 によって構成されるSRAMセルは、画素回路 110 のSRAMに“H”を書き込む状態を模したレプリカ回路となっている。

20

【0037】

差動アンプ 130 は、レプリカ回路 120 のMOSトランジスタ 127, 128 と、画素回路 110 のMOSトランジスタ 117, 118 と、の各ゲート電圧を調整する。具体的には、差動アンプ 130 は、レプリカ回路 120 のラッチノード C の電圧と、電圧 VDD と、の差分を示す電圧を出力する。レプリカ回路 120 のラッチノード C は、画素回路 110 のラッチノード B に対応するノードである。差動アンプ 130 からの出力は、レプリカ回路 120 のMOSトランジスタ 127, 128 と、画素回路 110 のMOSトランジスタ 117, 118 と、の各ゲートへ入力される。

30

【0038】

これにより、レプリカ回路 120 のラッチノード C の電圧と、電圧 VDD と、が等しくなるようにレプリカ回路 120 のMOSトランジスタ 127, 128 が制御される。また、画素回路 110 において“H”をラッチする場合にラッチノード B が電圧 VDD となるように、画素回路 110 のMOSトランジスタ 117, 118 が制御される。

40

【0039】

したがって、複数の画素回路 110 におけるSRAMセルの製造誤差（たとえばウエハ間やロット間のばらつき）や電源電圧の変動による、ラッチノード A, B 等における電圧の誤差や変動を抑えることができる。このため、液晶駆動回路 100 を安定して動作させることができる。

40

【0040】

このように、差動アンプ 130 は、レプリカ回路 120 のMOSトランジスタ 121, 122, 125, 126 と、レプリカ回路 120 のMOSトランジスタ 127, 128 と、の間の最大の電圧（ラッチノード C の電圧）が VDD に近づくようにMOSトランジスタ 127, 128 のゲート電圧を調整する。また、差動アンプ 130 は、MOSトランジスタ 117, 118 のゲート電圧を、MOSトランジスタ 127, 128 のゲート電圧と同じゲート電圧に調整する。これにより、画素回路 110 におけるラッチノード B の最大の電圧を電圧 VDD に精度よく制御し、液晶駆動回路 100 の動作の安定化を図ることができる。

50

## 【0041】

また、レプリカ回路120および差動アンプ130は、液晶駆動回路100の画素回路110のうちの複数の画素回路110において共有される。すなわち、1組のレプリカ回路120および差動アンプ130は、複数の画素回路110のMOSトランジスタ117, 118のゲート電圧を制御する。

## 【0042】

たとえば、液晶駆動回路100の全ての画素回路110に対して1組のレプリカ回路120および差動アンプ130が設けられる。または、液晶駆動回路100の画素回路110を複数のグループに分け、グループごとにレプリカ回路120および差動アンプ130が設けられてもよい。これにより、レプリカ回路120および差動アンプ130を設けることによる装置の大型化や消費電力の増加を抑えることができる。10

## 【0043】

(実施の形態にかかる液晶駆動回路を適用した液晶表示装置)

図2は、実施の形態にかかる液晶駆動回路を適用した液晶表示装置の一例を示す図である。図1に示した液晶駆動回路100は、たとえば図2に示す液晶表示装置200に適用することができる。図2に示すように、液晶表示装置200は、液晶表示部210と、バイアス回路220と、周辺回路230と、を備える。

## 【0044】

液晶表示部210は、たとえば、複数の信号線および複数の走査線を有し、複数の信号線および複数の走査線の交差に対応してマトリクス状に画素が配置された液晶表示部である。また、液晶表示部210は、複数の信号線および複数の走査線へ入力された各信号に応じた画像をマトリクス状の各画素により表示する。20

## 【0045】

液晶表示部210においては、各画素を駆動する回路として、図1に示した画素回路110がマトリクス状に設けられている。液晶表示部210に含まれる画素回路110のそれぞれは、液晶表示装置200における液晶表示部の各画素を駆動する。

## 【0046】

たとえば、液晶表示部210には、LCD等の液晶パネルを用いることができる。たとえば、液晶表示部210における列方向のカラム(Column)ラインが信号線であり、液晶表示部210における行方向のロウ(Row)ラインが走査線である。30

## 【0047】

バイアス回路220においては、液晶表示部210のロウ(行)ごとに、そのロウに設けられた複数の画素回路110と接続するようにレプリカ回路120および差動アンプ130が設けられている。たとえば、液晶表示部210の第n行目における複数の画素回路110のMOSトランジスタ117, 118の各ゲートには、バイアス回路220における第nのレプリカ回路120および第nの差動アンプ130が接続される。

## 【0048】

ただし、画素回路110とレプリカ回路120および差動アンプ130との関係はこれに限らず、たとえばバイアス回路220にはレプリカ回路120および差動アンプ130を1組だけ設け、そのレプリカ回路120および差動アンプ130に液晶表示部210の全ての画素回路110を接続してもよい。また、液晶表示部210のカラム(列)ごとにレプリカ回路120および差動アンプ130を設けてもよい。40

## 【0049】

周辺回路230には、液晶表示部210に画像を表示させるためのデータおよびクロックが入力される。たとえば、周辺回路230は、タイミング制御部231と、ロウ選択部/ロウドライバ232と、カラム選択部233と、カラムドライバ234と、を備える。

## 【0050】

タイミング制御部231は、周辺回路230へ入力されたクロックに基づいて、ロウ選択部/ロウドライバ232、カラム選択部233およびカラムドライバ234における各動作タイミングを制御する。50

## 【0051】

ロウ選択部 / ロウドライバ 232 は、タイミング制御部 231 からの制御に基づいて、液晶表示部 210 の行 (Row) ごとに設けられた走査線のいずれかに信号を入力することにより、液晶表示部 210 における書き換え対象の行を設定する。

## 【0052】

カラム選択部 233 は、周辺回路 230 へ入力されたデータに基づいて、液晶表示部 210 の列 (Column) ごとに設けられた信号線へ入力する各データ信号をカラムドライバ 234 へ出力する。カラムドライバ 234 は、カラム選択部 233 から出力された各データ信号を、液晶表示部 210 の列ごとに設けられた信号線へ入力する。これにより、液晶表示部 210 に対して各列の書き換えが指示される。このとき、実際に書き換えられる液晶表示部 210 の画素は、ロウ選択部 / ロウドライバ 232 によって書き換え対象として設定された行における各列の画素である。

10

## 【0053】

液晶表示部 210 には、各画素の液晶駆動に要する電圧 VDDH が供給される。バイアス回路 220 には、電圧 VDDH と、電圧 VDDH より低く、たとえば図 1 に示した MOS トランジスタ 111, 112, 115, 116 を破壊しない程度の電圧 VDD と、が供給される。周辺回路 230 には電圧 VDD が供給される。

## 【0054】

図 2 に示した液晶表示装置 200 は、液晶表示部 210 を用いて画像を表示する液晶表示装置であるが、液晶表示部 210 を用いて光を空間変調する空間光変調装置としての側面を有する。たとえば、画像を光情報記録媒体に照射してホログラムを形成することで情報を記録するホログラフィックメモリにおいて、光を空間変調することによって画像を生成する空間光変調装置として液晶表示装置 200 を用いることができる。ただし、液晶表示装置 200 は、ホログラフィックメモリに限らず、たとえばプロジェクタや電子式ビューファインダ等にも適用可能である。

20

## 【0055】

(実施の形態にかかる画素回路を模したゲート接地の回路)

図 3 は、実施の形態にかかる画素回路を模したゲート接地の回路の一例を示す図である。図 3 において、MOS トランジスタ 117, 118 によって MOS トランジスタ 111, 112, 115, 116 が高電圧からシールドされる原理について説明する。図 3 に示す模擬回路 300 は、図 1 に示した液晶駆動回路 100 における 1 個の画素回路 110 およびレプリカ回路 120 を模したゲート接地の回路である。模擬回路 300 は、トランジスタ 301 と、可変抵抗 302 と、負荷 303 と、電圧源 304 と、を備える。

30

## 【0056】

トランジスタ 301 は、図 1 に示した MOS トランジスタ 117, 118 (シールド素子) に対応する。トランジスタ 301 のソース (s) に接続された可変抵抗 302 (Rs) は、図 1 に示した MOS トランジスタ 111, 112 に対応する。可変抵抗 302 の抵抗値 Rs (トランジスタ 301 のソース抵抗) の変化は、図 1 に示した画素回路 110 がラッチする信号の変化に対応する。トランジスタ 301 のドレイン (d) に接続された負荷 303 は、図 1 に示した MOS トランジスタ 113, 114 に対応する。

40

## 【0057】

トランジスタ 301 のゲート (g) に接続された直流の電圧源 304 (Vb) は、図 1 に示したレプリカ回路 120 および差動アンプ 130 からなるバイアス回路に対応する。ノード 305 は、トランジスタ 301 のソースと可変抵抗 302 との間に接続されたノードであり、図 1 に示したラッチノード A, B (メモリセルの入出力部) に対応する。

## 【0058】

このように、トランジスタ 301 のゲート電圧を電圧源 304 によって電圧 Vb に固定し、トランジスタ 301 のソース抵抗を可変抵抗 302 によって変化させる場合について説明する。

## 【0059】

50

ソース抵抗  $R_s$  が高い場合は、トランジスタ 301 におけるゲートとソースとの間の電圧がトランジスタ 301 のしきい値電圧  $V_{TH}$  と同じ程度になるまではトランジスタ 301 に電流が流れる。このため、ノード 305 における電圧  $V_s$  は、 $V_s = V_b - V_{TH}$  となる。ソース抵抗  $R_s$  が低い場合は、トランジスタ 301 におけるゲートとソースとの間の電圧が上がり導通する。このため、ノード 305 における電圧  $V_s$  は、 $V_s = 0$  となる。

#### 【0060】

すなわち、電圧源 304 からの電圧  $V_b$  を適切に設定することにより、ノード 305 における電圧  $V_s$  の変化幅を制限することができる。電圧源 304 からの電圧  $V_b$  は、図 1 に示した画素回路 110 においては、MOS トランジスタ 117, 118 のしきい値電圧を  $V_{TH}$  とすると、 $V_b = V_{DD} + V_{TH}$  となる。

10

#### 【0061】

たとえば、図 1 に示した画素回路 110 においては、トランジスタ 301 に相当するシールド素子として MOS トランジスタ 117, 118 が SRAM の P 型 MOS (MOS トランジスタ 113, 114) と N 型 MOS (MOS トランジスタ 111, 112, 115, 116) との間に挿入されている。これにより、画素回路 110 の低電圧系 (たとえば MOS トランジスタ 111, 112, 115, 116) における電圧は、 $0 \sim V_{DD} [V]$  の間で変動する。このため、画素回路 110 のラッチ機能は維持しつつ、画素回路 110 の低電圧系を高電圧から保護することができる。

#### 【0062】

また、MOS トランジスタ 117, 118 のソース側は、低電圧 SRAM の機能を有するため、低電圧系の周辺回路と直結することが可能になる。たとえば、画素回路 110 は、画素回路 110 を制御する周辺回路 (たとえば図 2 に示した周辺回路 230) と、レベル変換回路などを介さずに直接接続することが可能になる。このため、たとえば図 2 に示した液晶表示装置 200 の小型化を図ることができる。また、消費電力の増加を抑えることができる。

20

#### 【0063】

また、MOS トランジスタ 117, 118 のドレイン側の出力端子 119 は高電圧 ( $0 \sim V_{DDH} [V]$ ) を出力可能になるため、たとえば出力端子 119 と表示画素との間にレベル変換回路などを設けなくても、表示画素を直接駆動することができる。このため、たとえば図 2 に示した液晶表示装置 200 の小型化を図ることができる。また、消費電力の増加を抑えることができる。

30

#### 【0064】

(実施の形態にかかる駆動信号の電圧の制御)

図 4 は、実施の形態にかかる駆動信号の電圧の制御の一例を示す図である。ここでは図 2 に示した液晶表示装置 200 をホログラフィックメモリに適用する場合について説明する。図 4 において、横軸は時間を示す。

30

#### 【0065】

制御信号 410 は、図 2 に示した周辺回路 230 から液晶表示部 210 へ入力される制御信号である。制御信号 410 の最大の電圧は、電圧  $V_{DDH}$  より低い電圧  $V_{DD}$  (一例としては  $1.8 [V]$ ) である。駆動信号 420 は、図 1 に示した出力端子 119 から表示画素へ印加される駆動信号である。駆動信号 420 の最大の電圧は  $V_{DDH}$  (一例としては  $5 [V]$ ) である。

40

#### 【0066】

また、図 4 に示すように、駆動信号 420 の最大の電圧を可変としてもよい。データ転送期間 401 は、図 2 に示した周辺回路 230 から液晶表示部 210 の複数の画素回路 110 へデータが転送される期間、すなわち SRAM におけるデータの書き換え期間である。液晶応答期間 402 は、複数の画素回路 110 から読み出された各値に応じて表示画素の液晶が応答する期間である。記録メディア書き込期間 403 は、表示画素により表示された情報がホログラフィックメモリの記録メディアに書き込まれる期間である。

#### 【0067】

50

液晶表示装置 200 をホログラフィックメモリに適用する場合は、データ転送期間 401、液晶応答期間 402、記録メディア書込期間 403 が周期的に繰り返される。このとき、液晶表示装置 200 は、図 4 に示すように、駆動信号 420 の最大の電圧 VDDH を、液晶応答期間 402 および記録メディア書込期間 403 においては表示画素の駆動に要する電圧（一例としては 5 [V]）としつつ、データ転送期間 401 においては表示画素の駆動に要する電圧より低い電圧（一例としては 1.8 [V]）としてもよい。

#### 【0068】

これにより、データ転送時には駆動信号 420 の最大の電圧 VDDH を周辺回路の電源電圧 VDD と同じ程度の電圧まで下げ、データ転送後に駆動信号 420 の最大の電圧 VDDH を表示画素の駆動に要する電圧に戻すことができる。これにより、データ転送時の貫通電流を抑制し、液晶表示装置 200 の消費電力を低減することができる。

10

#### 【0069】

なお、駆動信号 420 の電圧 VDDH を可変とする場合においても、差動アンプ 130 へ入力される電圧 VDDH は一定の電圧（一例としては 5 [V]）としてもよい。これにより、動作の安定化を図ることができる。

#### 【0070】

このように、P 型の MOS トランジスタ 113, 114 に印加される最大の電圧 VDDH を、画素回路 110 から読み出された信号に基づく液晶表示を行う期間（液晶応答期間 402 および記録メディア書込期間 403）においては電圧 VDD より高い第 1 電圧（一例としては 5 [V]）に制御し、画素回路 110 への信号の転送期間（データ転送期間 401）においては第 1 電圧より低い第 3 電圧（一例としては 1.8 [V]）に制御する制御回路を液晶表示装置 200 に設けてもよい。

20

#### 【0071】

これにより、画素回路 110 へのデータ転送時の貫通電流を抑制し、液晶表示装置 200 の消費電力を低減することができる。P 型の MOS トランジスタ 113, 114 に印加される最大の電圧 VDDH を制御する制御回路は、たとえば図 2 に示した周辺回路 230 に設けることができる。

#### 【0072】

図 4 において、駆動信号 420 の電圧 VDDH を可変とする場合について説明したが、駆動信号 420 の電圧 VDDH を一定（一例としては 5 [V]）としてもよい。この場合も、周辺回路における消費電力を低減することができる。

30

#### 【0073】

（実施の形態にかかる液晶駆動回路の他の構成例）

図 5 は、実施の形態にかかる液晶駆動回路の他の構成例 1 を示す図である。図 5 において、図 1 に示した部分と同様の部分については同一の符号を付して説明を省略する。図 1 においてはレプリカ回路 120 および差動アンプ 130 を用いて画素回路 110 の MOS トランジスタ 117, 118 のゲート電圧を制御する構成について説明したが、このような構成に限らない。

#### 【0074】

たとえば、図 5 に示すように、液晶駆動回路 100 は、図 1 に示したレプリカ回路 120 および差動アンプ 130 に代えてバイアス回路 510 を備えていてもよい。バイアス回路 510 は、トランジスタ 511 と、直流の定電流源 512 と、直流の電圧源 513 と、を備えている。

40

#### 【0075】

トランジスタ 511 は、定電流源 512 と電圧源 513 との間に設けられた MOS トランジスタである。トランジスタ 511 のゲートは、定電流源 512 と、画素回路 110 の MOS トランジスタ 117, 118 の各ゲートと、に接続されている。これにより、MOS トランジスタ 117, 118 の各ゲートに一定のゲート電圧を供給することができる。

#### 【0076】

図 5 に示した構成においても、図 1 に示した構成と同様に、1 画素あたりの面積の増加

50

を抑えつつ、消費電力の低減を図ることができる。また、図5に示した構成において、図4に示したように、駆動電圧の最大の電圧を可変としてもよい。

#### 【0077】

図6は、実施の形態にかかる液晶駆動回路の他の構成例2を示す図である。この例は、たとえば液晶駆動回路をN型シリコン基板上に構成したものに相当する。図6において、図1に示した部分と機能的に同様の部分については同一の符号を付して説明を省略する。図6に示す構成においては、画素回路110は、MOSトランジスタ111, 112の側が電源(VSSH)に接続され、MOSトランジスタ113, 114の側が接地されている。この場合は、保護用のMOSトランジスタとして図1に示したN型のMOSトランジスタ117, 118に代えてP型のMOSトランジスタ611, 612を設けた構成とする。また、保護用のMOSトランジスタ611はMOSトランジスタ111とMOSトランジスタ113, 115との間に接続され、保護用のMOSトランジスタ612はMOSトランジスタ112とMOSトランジスタ114, 116との間に接続される。

10

#### 【0078】

また、レプリカ回路120においても、保護用のMOSトランジスタとして図1に示したN型のMOSトランジスタ127, 128に代えてP型のMOSトランジスタ621, 622を設けた構成とする。また、保護用のMOSトランジスタ621はMOSトランジスタ121とMOSトランジスタ123, 125との間に接続され、保護用のMOSトランジスタ622はMOSトランジスタ122とMOSトランジスタ124, 126との間に接続される。

20

#### 【0079】

また、画素回路110の出力端子119は、MOSトランジスタ112とMOSトランジスタ612との間に設けられる。また、MOSトランジスタ115, 116の各ゲートにはワード線の反転信号(/WL)が入力される。

#### 【0080】

図6に示した構成においても、図1に示した構成と同様に、1画素あたりの面積の増加を抑えつつ消費電力の低減を図るとともに、動作の安定化を図ることができる。また、図6に示した構成において、図5に示したように、レプリカ回路120および差動アンプ130に代えてバイアス回路510(図5参照)を設けた構成としてもよい。また、図6に示した構成において、図4に示したように、駆動電圧の最大の電圧を可変としてもよい。

30

#### 【0081】

図7は、実施の形態にかかる液晶駆動回路の他の構成例3を示す図である。図7において、図1に示した部分と同様の部分については同一の符号を付して説明を省略する。図7に示すように、画素回路110は、図1に示した負荷抵抗回路部131において、MOSトランジスタ113, 114に代えて負荷抵抗711, 712を設けることにより、抵抗負荷型のSRAMセルとしてもよい。この場合は、レプリカ回路120においても、MOSトランジスタ123, 124に代えて負荷抵抗721, 722を設けた構成とする。

#### 【0082】

図7に示した構成においても、図1に示した構成と同様に、1画素あたりの面積の増加を抑えつつ消費電力の低減を図るとともに、動作の安定化を図ることができる。また、図7に示した構成において、図4に示したように、駆動電圧の最大の電圧を可変としてもよい。また、図7に示した構成において、図5に示したように、レプリカ回路120および差動アンプ130に代えてバイアス回路510(図5参照)を設けた構成としてもよい。

40

#### 【0083】

また、図7に示した構成において、図6に示したように、MOSトランジスタ111, 112の側が電源(VSSH)に接続され、負荷抵抗711, 712の側が接地された構成としてもよい。この場合は、保護用のMOSトランジスタとしてN型のMOSトランジスタ117, 118に代えてP型のMOSトランジスタ611, 612を設け、保護用のトランジスタとしてMOSトランジスタ127, 128に代えてP型のMOSトランジスタ621, 622を設けた構成とする。

50

## 【0084】

以上説明したように、液晶表示装置によれば、1画素あたりの面積の増加を抑えつつ、消費電力の低減を図ることができる。

## 【産業上の利用可能性】

## 【0085】

以上のように、本発明にかかる液晶表示装置は、L C O Sなどの液晶パネルを用いて画像を表示する液晶表示装置に有用であり、特に、画像を光情報記録媒体に照射してホログラムを形成することで情報を記録するホログラフィックメモリに適している。

## 【符号の説明】

## 【0086】

10

100 液晶駆動回路

110 画素回路

111 ~ 118 , 121 ~ 128 , 611 , 612 , 621 , 622 MOSトランジスタ

119 出力端子

120 レプリカ回路

130 差動アンプ

131 負荷抵抗回路部

132 記憶回路部

200 液晶表示装置

20

210 液晶表示部

220 , 510 バイアス回路

230 周辺回路

231 タイミング制御部

232 ロウ選択部 / ロウドライバ

233 カラム選択部

234 カラムドライバ

300 模擬回路

301 , 511 トランジスタ

30

302 可変抵抗

303 負荷

304 , 513 電圧源

305 ノード

401 データ転送期間

402 液晶応答期間

403 記録メディア書き込期間

410 制御信号

420 駆動信号

512 定電流源

711 , 712 , 721 , 722 負荷抵抗

40

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【 図 5 】

〔 囮 6 〕

【図7】

## フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

|         |       |       |

|---------|-------|-------|

| G 0 2 F | 1/13  | 5 0 5 |

| G 1 1 C | 11/40 | 3 0 1 |

F ターム(参考) 5C006 AC15 BA12 BB16 BB28 BF04 BF06 BF25 BF27 BF33 FA20

FA26 FA41 FA46 FA47

5C080 AA10 BB05 DD05 DD19 DD22 DD26 FF11 JJ02 JJ03 JJ04

KK02 KK43

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2017021159A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2017-01-26 |

| 申请号            | JP2015138183                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2015-07-09 |

| [标]申请(专利权)人(译) | 西铁城控股株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 西铁城钟表有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 永田洋一                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 永田 洋一                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/36 G02F1/1368 G09G3/20 G02F1/13 G11C11/412                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/36 G02F1/1368 G09G3/20.624.B G09G3/20.611.A G09G3/20.621.H G02F1/13.505 G11C11/40.301 G11C11/412                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H088/EA22 2H088/HA06 2H088/HA08 2H088/MA20 2H192/AA24 2H192/CB23 2H192/CB24 2H192/CB26 2H192/FB02 2H192/GD61 5B015/HH01 5B015/HH03 5B015/JJ03 5B015/KA09 5B015/KA13 5B015/KB65 5C006/AC15 5C006/BA12 5C006/BB16 5C006/BB28 5C006/BF04 5C006/BF06 5C006/BF25 5C006/BF27 5C006/BF33 5C006/FA20 5C006/FA26 5C006/FA41 5C006/FA46 5C006/FA47 5C080/AA10 5C080/BB05 5C080/DD05 5C080/DD19 5C080/DD22 5C080/DD26 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/KK02 5C080/KK43 |         |            |

| 代理人(译)         | 酒井 昭德                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

### 摘要(译)

本发明的一个目的是在抑制每像素面积增加的同时降低功耗。像素电路(110)是为每个显示像素提供的CMOS型SRAM单元。另外，像素电路110包括在负载电阻电路单元131和存储器电路单元132之间的保护MOS晶体管117和118。对于存储电路单元132，使用具有比负载电阻电路单元131和保护MOS晶体管117和118低的高电压的晶体管。[选图]图1