(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-191162

(P2014-191162A)

(43) 公開日 平成26年10月6日(2014.10.6)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36  | 2 H 1 9 3   |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 5 C 0 0 6   |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20  | 5 C 0 8 0   |

|                             | GO2F 1/133 | 5 7 5       |

|                             | GO2F 1/133 | 5 5 0       |

審査請求 未請求 請求項の数 10 O L (全 22 頁)

|           |                            |            |                                                                                                                                                                                               |

|-----------|----------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2013-66097 (P2013-66097) | (71) 出願人   | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号                                                                                                                                                 |

| (22) 出願日  | 平成25年3月27日 (2013.3.27)     | (74) 代理人   | 110000752<br>特許業務法人朝日特許事務所                                                                                                                                                                    |

|           |                            | (72) 発明者   | 山▲崎▼ 哲朗<br>長野県諏訪市大和3丁目3番5号 セイコ<br>ーエプソン株式会社内                                                                                                                                                  |

|           |                            | F ターム (参考) | 2H193 ZA04 ZA07 ZB02 ZB03 ZB05<br>ZC16 ZC25 ZD02 ZD25 ZD30<br>ZF01 ZF17 ZF21 ZF32 ZF33<br>ZF35 ZF45 ZH23 ZH40 ZH52<br>ZQ11 ZR04<br>5C006 AA14 AA22 AC21 AF13 BB16<br>BC12 BF03 BF04 BF26 EC11 |

|           |                            |            | 最終頁に続く                                                                                                                                                                                        |

(54) 【発明の名称】駆動装置、液晶表示装置、電子機器および駆動方法

## (57) 【要約】

【課題】サブフィールド駆動方式において配向不良を低減する。

【解決手段】駆動装置は、複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号から変換されたサブフィールドコードに応じて、複数のサブフィールドの各々について第1電圧であるオン電圧またはオフ電圧を、画素に印加する印加手段を有する。印加手段は、複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、オン電圧を第1電圧から第2電圧に変更し、第2電圧は、画素における基準電位との電位差が第1電圧よりも小さく、少なくとも一のサブフィールドにおいてオン電圧が第2電圧に変更された場合のフレームにおける画素の階調が、当該少なくとも一のサブフィールドにおいて当該オン電圧が第1電圧のままであった場合の当該フレームにおける当該画素の階調と同一範囲にある。

【選択図】図11

**【特許請求の範囲】****【請求項 1】**

複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号から変換されたサブフィールドコードに応じて、前記複数のサブフィールドの各々について第1電圧であるオン電圧またはオフ電圧を、画素に印加する印加手段

を有し、

前記印加手段は、前記複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、前記オン電圧を前記第1電圧から第2電圧に変更し、

前記第2電圧は、前記画素における基準電位との電位差が前記第1電圧よりも小さく、

前記少なくとも一のサブフィールドにおいて前記オン電圧が前記第2電圧に変更された場合の前記フレームにおける前記画素の階調が、当該少なくとも一のサブフィールドにおいて当該オン電圧が前記第1電圧のままであった場合の当該フレームにおける当該画素の階調と同一範囲にある

ことを特徴とする駆動装置。

**【請求項 2】**

前記印加手段は、前記フレームの最初のサブフィールドにおいて、前記オン電圧を前記第2電圧に変更する

ことを特徴とする請求項1に記載の駆動装置。

**【請求項 3】**

前記印加手段は、前記複数のサブフィールドのうち、前記サブフィールドコードが最初にオン電圧を示すサブフィールドにおいて、前記オン電圧を前記第2電圧に変更する

ことを特徴とする請求項1に記載の駆動装置。

**【請求項 4】**

前記フレームは、2以上の異なる時間長のサブフィールドにより各々が構成される複数のフィールドに区分され、

前記印加手段は、前記複数のフィールドの各々の最初のサブフィールドにおいて、前記オン電圧を前記第2電圧に変更する

ことを特徴とする請求項1に記載の駆動装置。

**【請求項 5】**

前記フレームは、2以上の異なる時間長のサブフィールドにより各々が構成される複数のフィールドに区分され、

前記印加手段は、前記複数のフィールドの各々の、前記サブフィールドコードが最初にオン電圧を示すサブフィールドにおいて、前記オン電圧を前記第2電圧に変更する

ことを特徴とする請求項1に記載の駆動装置。

**【請求項 6】**

前記画素が液晶を含み、

前記印加手段は、前記画素において前記第2電圧が連續して印加される時間が、前記液晶の応答時間より短くなるように前記第2電圧を印加する

ことを特徴とする請求項1ないし5のいずれか一項に記載の駆動装置。

**【請求項 7】**

複数の画素を有する電気光学パネルと、

複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号から変換されたサブフィールドコードに応じて、前記複数のサブフィールドの各々について第1電圧であるオン電圧またはオフ電圧を、前記複数の画素に印加する印加手段

を有し、

前記印加手段は、前記複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、前記オン電圧を前記第1電圧から第2電圧に変更し、

前記第2電圧は、前記画素における基準電位との電位差が前記第1電圧よりも小さく、

前記少なくとも一のサブフィールドにおいて前記オン電圧が前記第2電圧に変更された場合の前記フレームにおける前記画素の階調が、当該少なくとも一のサブフィールドにお

いて当該オン電圧が前記第1電圧のままであった場合の当該フレームにおける当該画素の階調と同一範囲にある

ことを特徴とする電気光学装置。

**【請求項8】**

請求項7に記載の電気光学装置を有する電子機器。

**【請求項9】**

複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号から変換されたサブフィールドコードに応じて、前記複数のサブフィールドの各々について第1電圧であるオン電圧またはオフ電圧を、画素に印加するステップと、

前記複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、前記オン電圧を前記第1電圧から第2電圧に変更するステップと

を有し

前記第2電圧は、前記画素における基準電位との電位差が前記第1電圧よりも小さく、前記少なくとも一のサブフィールドにおいて前記オン電圧が前記第2電圧に変更された場合の前記フレームにおける前記画素の階調が、当該少なくとも一のサブフィールドにおいて当該オン電圧が前記第1電圧のままであった場合の当該フレームにおける当該画素の階調と同一範囲にある

ことを特徴とする電気光学装置の駆動方法。

**【請求項10】**

複数の画素を有する液晶パネルと、

複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号から変換されたサブフィールドコードに応じて、前記複数のサブフィールドの各々について第1電圧であるオン電圧またはオフ電圧を、前記複数の画素に印加する印加手段とを有し、

前記印加手段は、前記複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、前記オン電圧を前記第1電圧から第2電圧に変更し、

前記第2電圧は、前記第2電圧を印加した際の液晶素子の透過率と第1電圧を印加した際の透過率とが同じとなる電圧で、且つ、前記透過率に到達する時間が、第1電圧を印加した際よりも長くなる電圧である

ことを特徴とする液晶表示装置。

20

30

40

50

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、サブフィールド駆動方式を用いた表示装置における配向不良を低減する技術に関する。

**【背景技術】**

**【0002】**

液晶素子等の電気光学素子における階調制御方法として、電気光学素子に印加される電圧を変調する電圧変調方式の他、電気光学素子に一定電圧が印加される時間を変調する、いわゆるサブフィールド駆動方式が知られている（特許文献1）。サブフィールド駆動方式において、1フレームは複数のサブフィールドに分割される。複数のサブフィールドのうち電圧を印加するサブフィールド（オンするサブフィールド）と電圧を印加しないサブフィールド（オフするサブフィールド）との組み合わせにより、電気光学素子の階調が制御される。

**【0003】**

特許文献1は、液晶の応答特性を考慮に入れた正確な階調表示をするため、あらかじめ実測した応答特性に基づいて、各サブフィールドの時間長および電圧値を決定することを開示している。

**【先行技術文献】**

**【特許文献】**

**【0004】**

【特許文献1】特開2001-100709号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

電気光学素子において、電圧無印加（オフ）の状態から急に高い電圧を印加すると、一時的な配向不良を起こす場合がある。この配向不良により、電気光学素子の階調が意図したものと異なってしまう場合があるという問題があった。

これに対し本発明は、サブフィールド駆動方式において配向不良を低減する技術を提供する。

10

**【課題を解決するための手段】****【0006】**

本発明は、複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号から変換されたサブフィールドコードに応じて、前記複数のサブフィールドの各々について第1電圧であるオン電圧またはオフ電圧を、画素に印加する印加手段を有し、前記印加手段は、前記複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、前記オン電圧を前記第1電圧から第2電圧に変更し、前記第2電圧は、前記画素における基準電位との電位差が前記第1電圧よりも小さく、前記少なくとも一のサブフィールドにおいて前記オン電圧が前記第2電圧に変更された場合の前記フレームにおける前記画素の階調が、当該少なくとも一のサブフィールドにおいて当該オン電圧が前記第1電圧のままであった場合の当該フレームにおける当該画素の階調と同一範囲にあることを特徴とする駆動装置を提供する。

20

この駆動装置によれば、サブフィールド駆動方式において配向不良を低減することができる。

**【0007】**

前記印加手段は、前記フレームの最初のサブフィールドにおいて、前記オン電圧を前記第2電圧に変更してもよい。

この駆動装置によれば、フレームの最初のサブフィールドの電圧印加に起因する配向不良を低減することができる。

**【0008】**

30

前記印加手段は、前記複数のサブフィールドのうち、前記サブフィールドコードが最初にオン電圧を示すサブフィールドにおいて、前記オン電圧を前記第2電圧に変更してもよい。

この駆動装置によれば、サブフィールドコードによらず、最初にオン電圧が印加されるサブフィールドに起因する配向不良を低減することができる。

**【0009】**

前記フレームは、2以上の異なる時間長のサブフィールドにより各々が構成される複数のフィールドに区分され、前記印加手段は、前記複数のフィールドの各々の最初のサブフィールドにおいて、前記オン電圧を前記第2電圧に変更してもよい。

40

この駆動装置によれば、各フィールドの最初のサブフィールドの電圧印加に起因する配向不良を低減することができる。

**【0010】**

前記フレームは、2以上の異なる時間長のサブフィールドにより各々が構成される複数のフィールドに区分され、前記印加手段は、前記複数のフィールドの各々の、前記サブフィールドコードが最初にオン電圧を示すサブフィールドにおいて、前記オン電圧を前記第2電圧に変更してもよい。

この駆動装置によれば、サブフィールドコードによらず、各フィールドで最初にオン電圧が印加されるサブフィールドに起因する配向不良を低減することができる。

**【0011】**

前記画素が液晶を含み、前記印加手段は、前記画素において前記第2電圧が連続して印

50

加される時間が、前記液晶の応答時間より短くなるように前記第2電圧を印加してもよい。

この駆動装置によれば、階調への影響を抑制しつつ、サブフィールド駆動方式において配向不良を低減することができる。

#### 【0012】

また、本発明は、複数の画素を有する電気光学パネルと、複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号から変換されたサブフィールドコードに応じて、前記複数のサブフィールドの各々について第1電圧であるオン電圧またはオフ電圧を、前記複数の画素に印加する印加手段を有し、前記印加手段は、前記複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、前記オン電圧を前記第1電圧から第2電圧に変更し、前記第2電圧は、前記画素における基準電位との電位差が前記第1電圧よりも小さく、前記少なくとも一のサブフィールドにおいて前記オン電圧が前記第2電圧に変更された場合の前記フレームにおける前記画素の階調が、当該少なくとも一のサブフィールドにおいて当該オン電圧が前記第1電圧のままであった場合の当該フレームにおける当該画素の階調と同一範囲にあることを特徴とする電気光学装置を提供する。10

この電気光学装置によれば、サブフィールド駆動方式において配向不良を低減することができる。

#### 【0013】

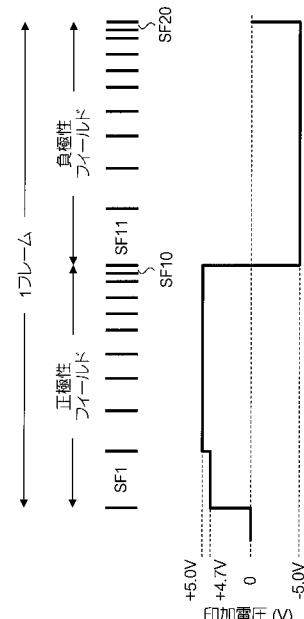

さらに、本発明は、上記の電気光学装置を有する電子機器を提供する。

この電子機器によれば、サブフィールド駆動方式において配向不良を低減することができる。20

#### 【0014】

さらに、本発明は、複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号から変換されたサブフィールドコードに応じて、前記複数のサブフィールドの各々について第1電圧であるオン電圧またはオフ電圧を、画素に印加するステップと、前記複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、前記オン電圧を前記第1電圧から第2電圧に変更するステップとを有し、前記第2電圧は、前記画素における基準電位との電位差が前記第1電圧よりも小さく、前記少なくとも一のサブフィールドにおいて前記オン電圧が前記第2電圧に変更された場合の前記フレームにおける前記画素の階調が、当該少なくとも一のサブフィールドにおいて当該オン電圧が前記第1電圧のままであった場合の当該フレームにおける当該画素の階調と同一範囲にあることを特徴とする電気光学装置の駆動方法を提供する。30

この駆動方法によれば、サブフィールド駆動方式において配向不良を低減することができる。

#### 【0015】

さらに、本発明は、複数の画素を有する液晶パネルと、複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号から変換されたサブフィールドコードに応じて、前記複数のサブフィールドの各々について第1電圧であるオン電圧またはオフ電圧を、前記複数の画素に印加する印加手段とを有し、前記印加手段は、前記複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、前記オン電圧を前記第1電圧から第2電圧に変更し、前記第2電圧は、前記第2電圧を印加した際の液晶素子の透過率と第1電圧を印加した際の透過率とが同じとなる電圧で、且つ、前記透過率に到達する時間が、第1電圧を印加した際よりも長くなる電圧であることを特徴とする液晶表示装置を提供する。40

この液晶表示装置によれば、サブフィールド駆動方式において配向不良を低減することができる。

#### 【図面の簡単な説明】

#### 【0016】

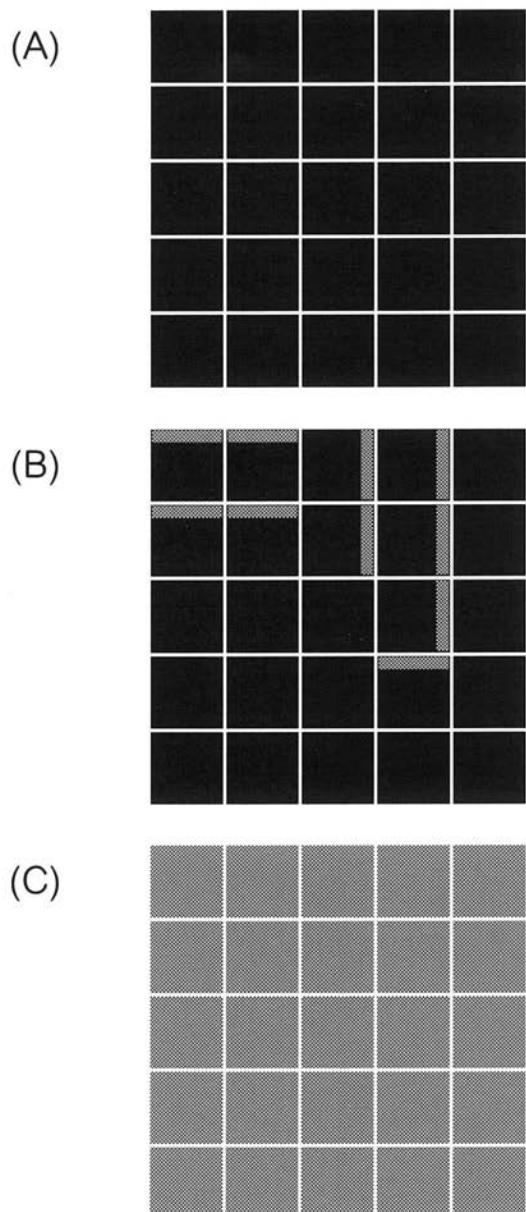

【図1】液晶素子において発生する配向不良を例示する図。

【図2】第1実施形態に係る電子機器1000の構成を示す図。50

- 【図3】電気光学装置1の構成を示す図。

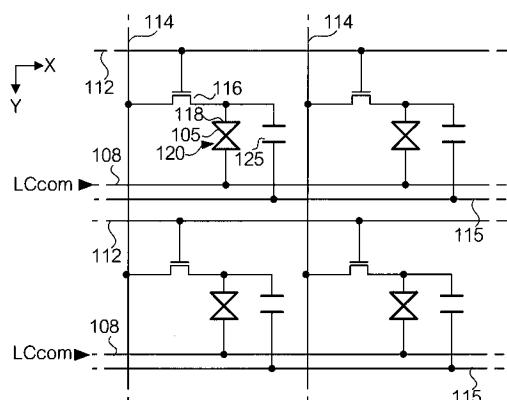

- 【図4】画素111の等価回路を示す図。

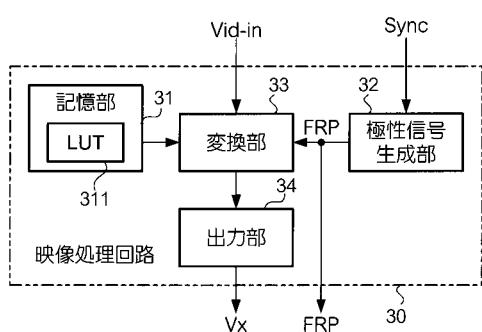

- 【図5】映像処理回路30の構成を示す図。

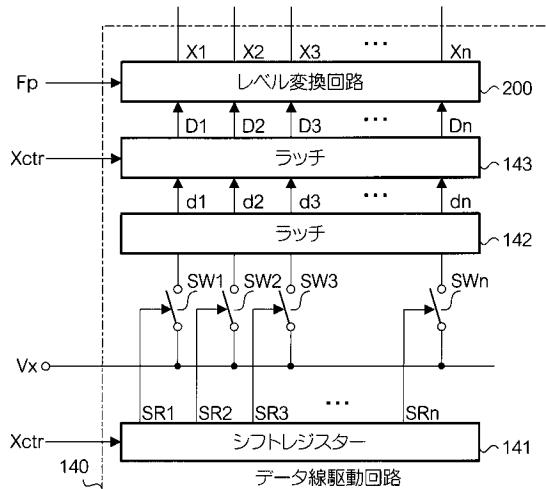

- 【図6】データ線駆動回路140の詳細を示す図。

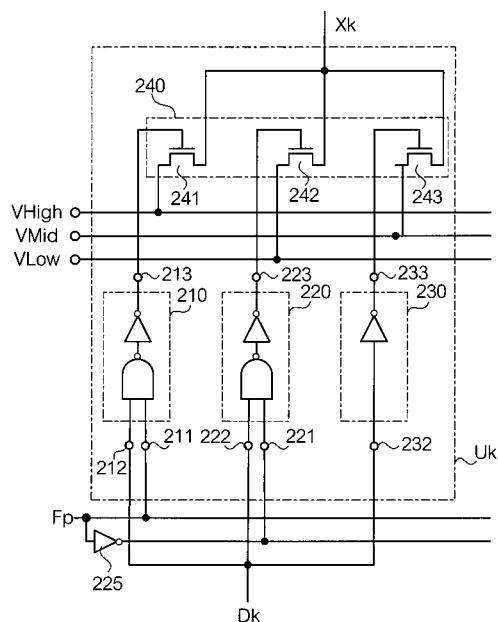

- 【図7】レベル変換回路200の構成を例示する図。

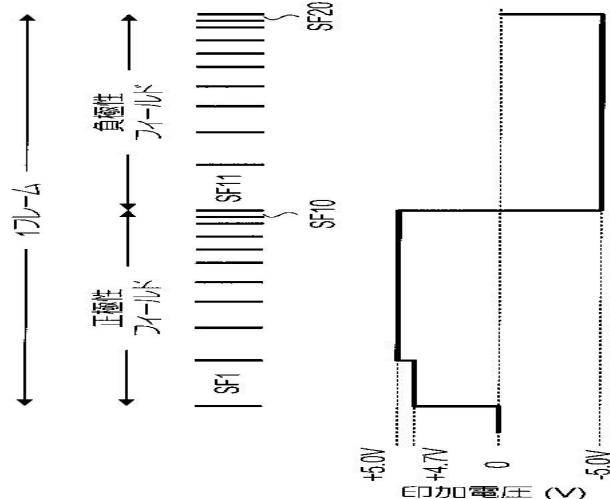

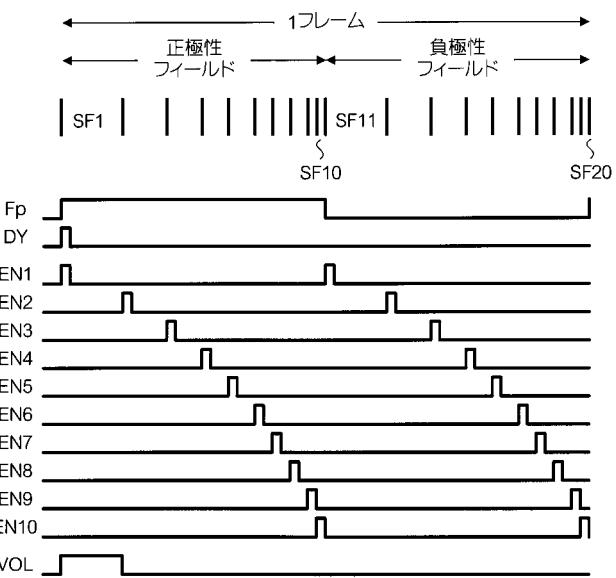

- 【図8】サブフィールド駆動を説明するタイミングチャート。

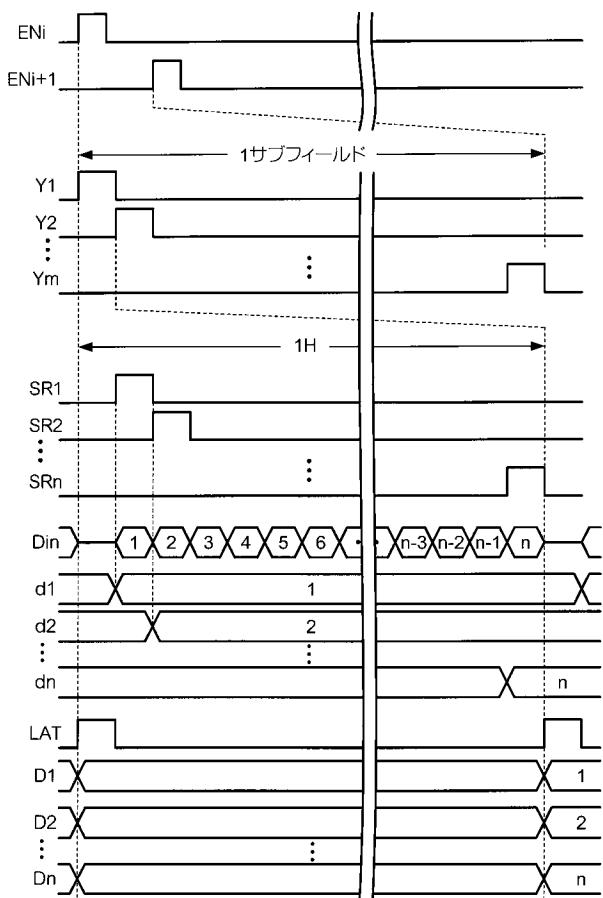

- 【図9】各サブフィールドにおける動作を示すタイミングチャート。

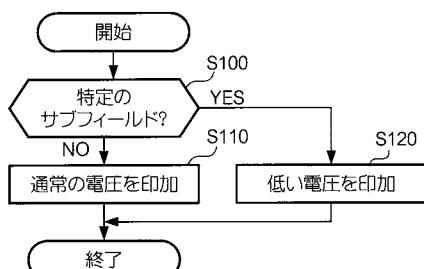

- 【図10】電気光学装置1の動作を示すフローチャート。

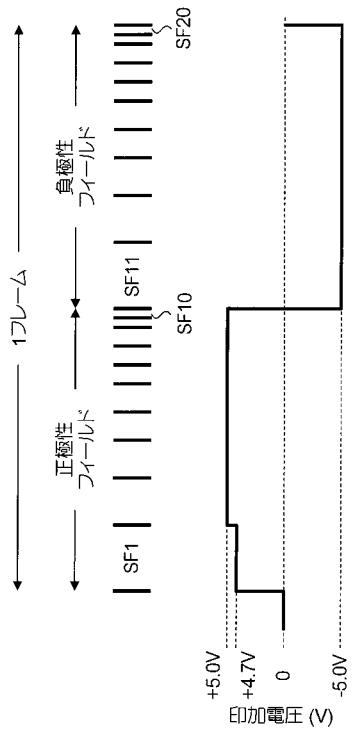

- 【図11】第1実施形態において液晶素子120に印加される電圧を例示する図。

- 【図12】変形例1において液晶素子120に印加される電圧を例示する図。

- 【図13】変形例2において液晶素子120に印加される電圧を例示する図。

- 【図14】第2実施形態に係る電気光学装置1の構成を示す図。

- 【図15】第2実施形態に係るレベル変換回路200の構成を示す図。

- 【図16】第2実施形態において液晶素子120に印加される電圧を例示する図。

【発明を実施するための形態】

【0017】

1. 概要

実施形態に係る装置の構成および動作の説明に先立ち、サブフィールド駆動方式を用いた液晶表示装置の問題点について説明する。液晶素子は、電圧印加により液晶分子の配向を制御することにより光学状態特性（透過率または反射率）を制御するものである。電圧印加により配向が変化する方向を規制するため、電圧無印加の状態における液晶分子の傾きの方向および角度を所定の範囲に制御する技術が知られている。電圧無印加の状態における液晶分子に与えられた傾きをプレチルトという。液晶素子に対し、電圧無印加の状態から急に高い電圧を印加すると、プレチルトで規制した方向に液晶分子が動かず、一時的な配向不良が起こる場合がある。

【0018】

図1は、液晶素子において発生する配向不良を例示する図である。図1は、ノーマリープラックの液晶素子において、電圧無印加（オフ電圧）の状態（図1（A））からオン電圧（飽和電圧）を印加した場合における液晶素子の光学状態を示している。図1（B）は電圧印加開始から1.5ミリ秒後の光学状態を、図1（C）は電圧印加開始から7.5ミリ秒後の光学状態を、それぞれ示している。この配向不良は一時的なものであるので、いわゆる電圧変調方式のように、ある程度長い時間（例えば1フレーム）同じ電圧が印加され続ければ解消する。この例では、電圧印加開始から1.5ミリ秒後の時点で不均一に配向不良が発生しているが（図1（B））、電圧印加開始から7.5ミリ秒が経過した時点では配向不良は解消されほぼ所望の光学状態になっている。しかし、サブフィールド駆動方式においては、一定の高い電圧のオン／オフが繰り返されるため、一時的な配向不良が継続的に発生し、液晶素子の階調が意図したものと異なってしまう場合がある。また、この配向不良は、書き換え前の液晶分子の状態や温度など種々の要因に影響され、制御が困難である。したがって、配向不良を考慮して各サブフィールドにおけるオン／オフの組み合わせ（サブフィールドコード）を作成することはできない。

【0019】

この問題に対処するため、プレチルトやギャップ（後述）を調整することにより、配向の規制力を高める技術がある。しかし、配向の規制力を高めるためにプレチルトやギャップを調整すると、コントラストや透過率が低下するという表示背反が起こる場合がある。本発明は、サブフィールド駆動方式において電圧無印加の状態から電圧を印加するときに、規定のオン電圧より低い電圧を印加することにより、配向不良を抑制する。

【0020】

2. 第1実施形態

2-1. 構成

図2は、本発明の第1実施形態に係る電子機器1000の構成を示す図である。この例

10

20

30

40

50

で、電子機器 1000 は、入力された映像信号 V i d - i n に応じた映像をスクリーンに投射するプロジェクターである。電子機器 1000 は、電気光学装置 1、光源 2、制御部 3、および投射部 4 を有する。電子機器 1000 において、光源 2 から照射された光を電気光学装置 1 が変調し、さらにこれを投射部 4 がスクリーンに投射する。

#### 【 0 0 2 1 】

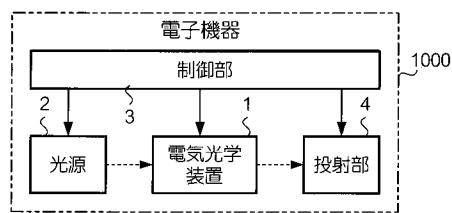

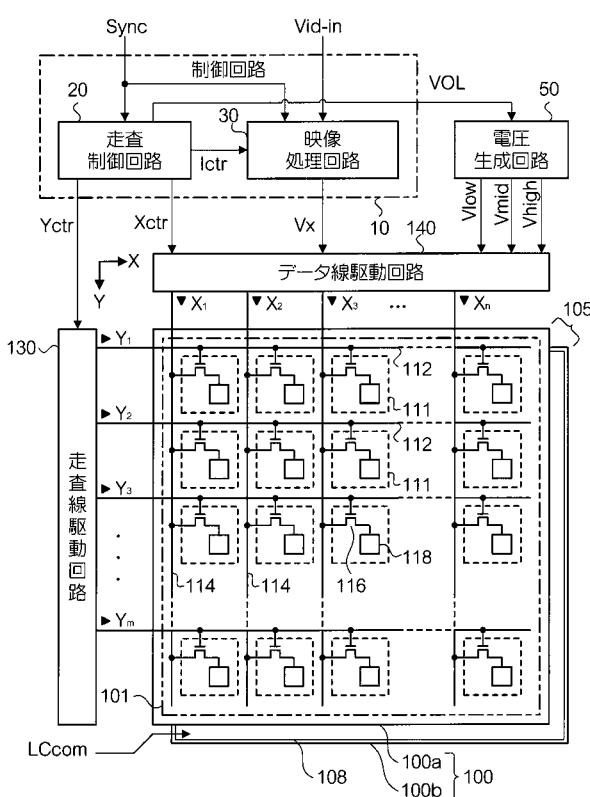

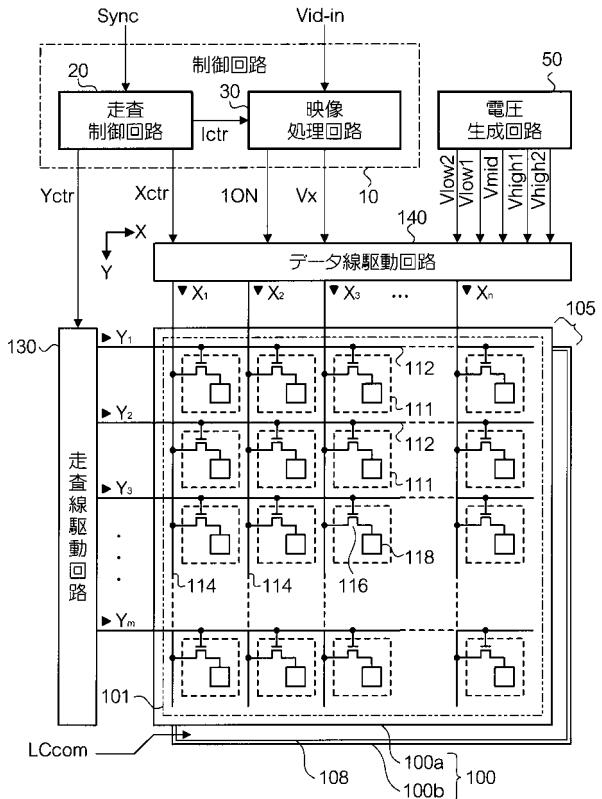

図 3 は、電気光学装置 1 の構成を示す図である。電気光学装置 1 は、光変調器であり、液晶パネル 100、走査線駆動回路 130、およびデータ線駆動回路 140 を 3 組と、制御回路 10 と、電圧生成回路 50 とを有する。各組は、それぞれ、色成分 R (赤)、色成分 G (緑)、および色成分 B (青) に対応している。ここでは、図面が煩雑になるのを避けるため、1 組の液晶パネル 100、走査線駆動回路 130、およびデータ線駆動回路 140 のみを図示している。10

#### 【 0 0 2 2 】

液晶パネル 100 は、供給される信号に応じて画像を表示する装置である。液晶パネル 100 は、m 行 n 列のマトリクス状に配置された画素 111 を有する。画素 111 は、走査線駆動回路 130 及びデータ線駆動回路 140 から供給される信号に応じた光学状態を示す。液晶パネル 100 は、複数の画素 111 の光学状態を制御することにより画像を表示する。

#### 【 0 0 2 3 】

液晶パネル 100 は、素子基板 100a と、対向基板 100b と、液晶 105 とを有する。素子基板 100a と対向基板 100b とは、一定の間隙を保って貼り合わせられている。この間隙 (ギャップ) に、液晶 105 が挟まれている。20

#### 【 0 0 2 4 】

素子基板 100a は、対向基板 100b との対向面において、m 行の走査線 112 および n 列のデータ線 114 を有する。走査線 112 は X (横) 方向に沿って、データ線 114 は Y (縦) 方向に沿って、それぞれ設けられており、互いに絶縁されている。一の走査線 112 を他の走査線 112 と区別するときは、図において上から順に第 1、第 2、第 3、...、第 (m - 1)、および第 m 行の走査線 112 という。同様に、一のデータ線 114 を他のデータ線 114 と区別するときは、図において左から順に第 1、第 2、第 3、...、第 (n - 1)、第 n 列のデータ線 114 という。画素 111 は、X 軸および Y 軸に垂直な位置にある視点からみたときに、走査線 112 およびデータ線 114 の交差に対応して設けられている。30

#### 【 0 0 2 5 】

図 4 は、画素 111 の等価回路を示す図である。画素 111 は、TFT116 と、液晶素子 120 と、保持容量 125 とを有する。液晶素子 120 は、画素電極 118 と、液晶 105 と、コモン電極 108 とを有する。画素電極 118 は、画素 111 每に個別に設けられた電極である。コモン電極 108 は、すべての画素 111 に共通の電極である。画素電極 118 は素子基板 100a に、コモン電極 108 は対向基板 100b に、それぞれ設けられている。液晶 105 は、画素電極 118 およびコモン電極 108 に挟まれている。コモン電極 108 には、コモン電圧 L C c o m が印加される。

#### 【 0 0 2 6 】

TFT116 は、画素電極 118 への電圧の印加を制御するスイッチング素子の一例であり、この例では、n チャネル型の電界効果トランジスターである。TFT116 は、画素 111 每に個別に設けられている。第 i 行第 j 列の TFT116 のゲートは第 i 行の走査線 112 に、ソースは第 j 列のデータ線 114 に、ドレインは画素電極 118 に、それぞれ接続されている。保持容量 125 は、一端が画素電極 118 に、他端が容量線 115 に、それぞれ接続されている。容量線 115 には、時間的に一定の電圧が印加される。40

#### 【 0 0 2 7 】

第 i 行の走査線 112 に H (High) レベルの電圧 (以下「選択電圧」という) が印加されると、第 i 行第 j 列の TFT116 はオン状態となり、ソースとドレインが導通する。このとき、第 j 列のデータ線 114 に、第 i 行第 j 列の画素 111 の階調値 (データ) に

10

20

30

40

50

応じた電圧（以下「データ電圧」という）が印加されると、データ電圧は、TFT116を介して第i行第j列の画素電極118に印加される。

#### 【0028】

その後、第i行の走査線112にL（Low）レベルの電圧（以下「非選択電圧」という）が印加されると、TFT116はオフ状態になり、ソースとドレインは高インピーダンス状態となる。TFT116がオン状態のとき画素電極118に印加された電圧は、液晶素子120の容量性および保持容量125によって、TFT116がオフ状態になった後も保持される。

#### 【0029】

液晶素子120には、データ電圧とコモン電圧との電位差に相当する電圧が印加される。液晶105の分子配向状態は、液晶素子120に印加される電圧に応じて変化する。画素111の光学状態は、液晶105の分子配向状態に応じて変化する。例えば、液晶パネル100が透過型のパネルである場合、変化する光学状態は透過率である。

10

#### 【0030】

再び図3を参照する。走査線駆動回路130は、m本の走査線112の中から一の走査線112を順次排他的に選択する（すなわち走査線112を走査する）回路である。具体的には、走査線駆動回路130は、制御信号Yctrに従って、第i行の走査線112に、走査信号Yiを供給する。この例で、走査信号Yiは、選択される走査線112に対しては選択電圧となり、選択されない走査線112に対しては非選択電圧となる信号である。

20

#### 【0031】

データ線駆動回路140は、n本のデータ線114にデータ電圧を示す信号（以下「データ信号」という）を出力する回路である。具体的には、データ線駆動回路140は、映像処理回路30から供給されるデータ信号Vxを、制御信号Xctrに従ってサンプリングし、第1～第n列のデータ線114にデータ信号X1～Xnとして出力する。なお、本説明において電圧については、液晶素子120の印加電圧を除き、特に明記しない限り図示省略した接地電位を基準（ゼロV）として表す。

20

#### 【0032】

液晶パネル100に表示される画像は、所定の周期で書き換えられる。以下、この書き換えの周期を「フレーム」という。例えば、画像が60Hzで書き換えられる場合、1フレームは約16.7 msecである。走査線駆動回路130が1フレームに1回、m本の走査線112を走査し、データ線駆動回路140がデータ信号を出力することにより、液晶パネル100に表示される画像が書き換えられる。

30

#### 【0033】

この例で、液晶パネル100の駆動にはサブフィールド駆動方式が用いられる。サブフィールド駆動方式において、1フレームはさらに複数の期間に分割される。この分割された期間をサブフィールドという。各サブフィールドにおいて液晶素子120に印加される電圧の絶対値は、オン電圧（例えば5V）およびオフ電圧（例えばゼロV）の2値のいずれかである。複数のサブフィールドは、オン電圧の極性が正極性となる期間（以下「正極性フィールド」という）およびオン電圧の極性が負極性となる期間（以下「負極性フィールド」という）に分けられる。

40

#### 【0034】

制御回路10は、上位装置から供給される映像信号Vid-inおよび同期信号Syncに応じて走査線駆動回路130およびデータ線駆動回路140を制御する信号を出力する。映像信号Vid-inは、液晶パネル100における各画素の階調値をそれぞれ指定するデジタル信号である。映像信号Vid-inは、同期信号Syncと同期して供給される。同期信号は、垂直走査信号、水平走査信号およびドットクロック信号（いずれも図示省略）を含んでいる。この例で、映像信号Vid-inの周波数は60Hzである。すなわち、映像信号Vid-inにより示される画像は、16.67ミリ秒毎に書き換えられる。

50

## 【0035】

なお、映像信号  $V_{id-in}$  は直接的には階調値を指定するものであるが、階調値に応じて液晶素子に印加される電圧（以下「印加電圧」という）が定まるので、映像信号  $V_{id-in}$  は液晶素子の印加電圧を指定するものといえる。

## 【0036】

制御回路 10 は、走査制御回路 20 と映像処理回路 30 とを有する。走査制御回路 20 は、制御信号  $X_{ctr}$ 、制御信号  $Y_{ctr}$ 、制御信号  $I_{ctr}$  等、各種の制御信号を生成して、同期信号  $Sync$  に同期して各部を制御する。映像処理回路 30 は、デジタルの映像信号  $V_{id-in}$  を処理して、各色成分毎にデータ信号  $V_x$  を出力する。

## 【0037】

10

図 5 は、映像処理回路 30 の構成を示す図である。映像処理回路 30 は、記憶部 31 と、極性信号生成部 32 と、変換部 33 と、出力部 34 とを有する。記憶部 31 は、LUT (Look Up Table) を記憶している。LUT 311 は、映像信号  $V_{id-in}$  により示される階調値をサブフィールドコードに変換する際に用いられる。サブフィールドコードは、各階調について、複数のサブフィールドの各々においてオン電圧（第 1 階調、例えば白に対応する電圧）およびオフ電圧（第 2 階調、例えば黒に対応する電圧）のどちらを印加すべきであるかを示す情報である。

## 【0038】

20

極性信号生成部 32 は極性信号  $F_R P$  を生成する。極性信号  $F_R P$  は、今が正極性フィールドおよび負極性フィールドのどちらであるかを示す信号である。この例で、極性信号生成部 32 は外部から入力される同期信号  $Sync$  から極性信号  $F_R P$  を生成する。極性信号生成部 32 は生成した極性信号  $F_R P$  を、変換部 33 および他の装置（例えばデータ線駆動回路 140）に出力する。

## 【0039】

30

変換部 33 は、映像信号  $V_{id-in}$  により示される階調値を、サブフィールドコードに変換する。この例で、変換部 33 は、時間比および現在が正極性フィールドであるか負極性フィールドであるかに応じて、階調値をサブフィールドコードに変換する。すなわち、変換部 33 は、映像信号  $V_{id-in}$  に加え、時間比を示す時間比信号  $PNR$  および極性信号  $F_R P$  を用いて、階調値をサブフィールドコードに変換する。出力部 34 は、サブフィールドコードを示すデータ信号  $V_x$  を出力する。データ線駆動回路 140 は、データ信号  $V_x$  に応じた電圧をデータ線 114 に印加する。なお、本実施形態においてはサブフィールド駆動方式が用いられるので、データ線 114 に印加される電圧の絶対値は、オン電圧およびオフ電圧の 2 値のいずれかである。

## 【0040】

40

図 6 は、データ線駆動回路 140 の詳細を示す図である。データ線駆動回路 140 は、データ信号  $X_1$ 、 $X_2$ 、 $X_3$ 、…、 $X_n$  をデータ線 114 に供給する回路である。データ線駆動回路 140 は、シフトレジスター 141、データ供給線  $V_x$ 、スイッチ  $SW_1 \sim SW_n$ 、ラッチ 142、ラッチ 143 およびレベル変換回路 200 を有している。この例で、データ線駆動回路 140 は、いわゆる SOG (System On Glass) 技術を用いて、素子基板 100a 上に形成されている。

## 【0041】

シフトレジスター 141 は、制御回路 10 からの信号に従って、サンプリングパルス  $SR_1$ 、 $SR_2$ 、 $SR_3$ 、…、 $SR_n$  を順次生成する。データ供給線  $V_x$  は、スイッチ  $SW$  を介してラッチ 142 に接続されている。スイッチ  $SW$  の制御入力端子には、サンプリングパルス  $SR$  が供給される。この構成により、サンプリングパルス  $SR_1$ 、 $SR_2$ 、 $SR_3$ 、…、 $SR_n$  に各々同期して、画像データ信号  $V_x$  がラッチ 142 に供給される。ラッチ 142 は、スイッチ  $SW$  を介して入力される画像データ信号  $V_x$  をラッチし、点順次の画像データ  $d_1 \sim d_n$  を得る。ラッチ 142 により得られた画像データ  $d_1 \sim d_n$  は、ラッチ 143 に入力される。ラッチ 143 は、画像データ  $d_1 \sim d_n$  をラッチし、線順次の画像データ  $D_1 \sim D_n$  を得る。レベル変換回路 200 は、画像データ「1」に対応する 2

50

つの電圧（V High および V Low）と、画像データ「0」に対応する電圧（V Mid）との合計3つの電圧の中から、画像データD1～Dnおよび極性信号Fpに基づいて選択した電圧の信号を、データ信号X1～Xnとしてデータ線114に供給する。

#### 【0042】

図7は、レベル変換回路200の構成を例示する図である。図3においては、k番目のデータ線にデータ信号Xkを出力するための変換ユニットUkが示されている。kは1～nを満たす整数である。変換ユニットUkは、データ信号Dkおよび極性信号Fpに応じて、電圧V High、V Mid、およびV Lowのいずれかを選択する3値セレクターである。レベル変換回路200はn個の変換ユニットを有しており、各変換ユニットは同じ構成を有している。ここでは変換ユニットUkを例として説明する。レベル変換回路200は、制御部210、制御部220および制御部230の3つの制御部、並びに選択部240を有する。制御部210は、電圧V Highを選択するタイミングを制御する。制御部220は、電圧V Lowを選択するタイミングを制御する。制御部230は、電圧V Midを選択するタイミングを制御する。選択部240は、制御部210、制御部220および制御部230からの信号に応じて、電圧V High、V LowおよびV Midのいずれかの電圧をデータ線114に印加する。

10

#### 【0043】

制御部210は、入力端子211、入力端子212および出力端子213を有する。入力端子211には、極性信号Fpが入力される。入力端子212には、画像データ信号Vxが入力される。制御部210は、極性信号Fpおよび画像データ信号Vxを用いた論理演算を行う回路を有する。第1の論理演算は、極性信号Fpが示す値および画像データ信号Vxが示す値の否定論理積（NAND）を含む。この例で、第1の論理演算は、FpとVxの否定論理積およびこの否定論理積の結果の否定（NOT）から構成される。出力端子213は、第1の論理演算の結果を出力する。

20

#### 【0044】

制御部220は、入力端子221、入力端子222および出力端子223を有する。入力端子221と極性信号Fpの信号線との間にはNOT回路250が設けられている。入力端子221には、極性信号Fpの反転信号が入力される。入力端子222には、画像データ信号Vxが入力される。制御部220は、極性信号Fpの反転信号および画像データ信号Vxを用いた論理演算（以下「第2の論理演算」という）を行う回路を有する。第2の論理演算は、反転信号が示す値および画像データ信号Vxが示す値の否定論理積を含む。この例で、第2の論理演算は、Fpの反転信号とVxの否定論理積（NAND）およびこの否定論理積の結果の否定（NOT）から構成される。出力端子223は、第2の論理演算の結果を出力する。

30

#### 【0045】

制御部230は、入力端子232および出力端子233を有する。入力端子232には、画像データ信号Vxが入力される。制御部220は、画像データ信号Vxを用いた論理演算（以下「第3の論理演算」という）を行う回路を有する。第3の論理演算は、画像データ信号Vxが示す値の否定を含む。この例で、第3の論理演算は、Vxの否定（NOT）から構成される。出力端子233は、第3の論理演算の結果を出力する。

40

#### 【0046】

選択部240は、TFT241、TFT242およびTFT243の3つのスイッチング素子を有する。この例で、TFT241、TFT242およびTFT243は、単一の伝導型のチャネル（ここではnチャネル）を有する電界効果トランジスターであり、ソース端子、ドレイン端子およびゲート端子を有する。TFT241のソース端子は、電圧V High（例えば12.0V）が印加される電圧線に接続されている。TFT241のドレイン端子は、データ線114に接続されている。TFT241のゲート端子は、出力端子213に接続されている。TFT241は、出力端子213からHレベルの信号が入力されたときにオン状態となり、データ線114に電圧V Highを印加する。この例で、出力端子213からHレベルの信号が出力されるのは、第1の論理演算の結果が真のとき

50

、すなわち、第1の論理演算における否定論理積の結果が偽のときである。TFT242のソース端子は、電圧VLow（例えば2.0V）が印加される電圧線に接続されている。TFT242のドレイン端子は、データ線114に接続されている。TFT242のゲート端子は、出力端子223に接続されている。TFT242は、出力端子223からHレベルの信号が入力されたときにオン状態となり、データ線114に電圧VLowを印加する。この例で、出力端子223からHレベルの信号が出力されるのは、第2の論理演算の結果が真のとき、すなわち、第2の論理演算における否定論理積の結果が偽のときである。TFT243のソース端子は、電圧VMid（例えば7V）が印加される電圧線に接続されている。TFT243のドレイン端子は、データ線114に接続されている。TFT243のゲート端子は、出力端子233に接続されている。TFT243は、出力端子233からHレベルの信号が入力されたときにオン状態となり、データ線114に電圧VMidを印加する。この例で、出力端子233からHレベルの信号が出力されるのは、第3の論理演算の結果が真のとき、すなわち、第3の論理演算における否定の結果が真のときである。

10

20

30

**【0047】**

再び図3を参照する。電圧生成回路50は、データ線駆動回路140に対し電源電圧を供給する。具体的には、電圧生成回路50は、電圧VHigh、電圧VMid、および電圧VLowの3種類の電圧を提供する。これら3種類の電圧値の大小関係は、VHigh > VMid > VLowである。電圧VHighは、正極性のオン電圧に相当する電圧である。電圧VMidは、オフ電圧に相当する電圧である。電圧VLowは、負極性のオン電圧に相当する電圧である。この例で、電圧VMidは、コモン電圧LCcommonと等しい固定電圧である。すなわち、液晶素子120に印加される電圧は、VHigh（例えば12.0V）とVMid（例えば7V）との電位差に相当する電圧（例えば5V）、VLow（例えば2.0V）とVMid（例えば7V）との電位差に相当する電圧（例えば-5V）、またはゼロVのいずれかである。なお、この例で、電圧VHighおよび電圧VLowは、制御回路10の制御により変動する。通常時はVHigh = V1、VLow = V3であるが、特定のサブフィールドにおいては、VHigh = V2、VLow = V4である。以下の例においては、V1 = 12.0V、V2 = 11.7V、V3 = 2.0V、V4 = 2.3V、VMid = 7.0Vである。

40

**【0048】**

ここで、データ線駆動回路140は、複数のサブフィールドから構成されるフレームに区分された映像を示す映像信号Vid-inから変換されたサブフィールドコードに応じて、複数のサブフィールドの各々についてオン電圧またはオフ電圧を、画素111に印加する印加手段を有する駆動装置の一例である。この印加手段は、複数のサブフィールドのうち少なくとも一のサブフィールドにおいて、オン電圧を第1電圧から第2電圧に変更する。第2電圧は、画素111に印加される電圧が第1電圧よりも小さい。

50

**【0049】**

第2電圧を第1電圧よりどれだけ小さくするか、すなわち、電圧生成回路50において生成される電圧値は、液晶素子120の特性に応じて決められる。配向不良を低減する観点からは第2電圧は小さい方が好ましい。しかし、第2電圧を小さくしすぎると、所望の階調を表現できなくなるという問題がある。そこで、第2電圧は、少なくとも一のサブフィールドにおいてオン電圧が第2電圧に変更された場合のそのフレームにおける画素111の階調が、そのサブフィールドにおいてオン電圧が第1電圧のままであった場合のそのフレームにおける画素111の階調と同一範囲にあるように決定される。または、第2電圧は、第2電圧を印加した際の液晶素子120の透過率と第1電圧を印加した際の透過率とが同じとなる電圧で、且つ、前記透過率に到達する時間が、第1電圧を印加した際よりも長くなる電圧としてもよい。

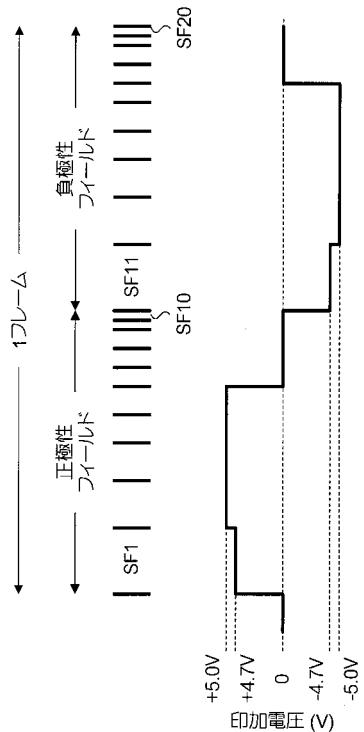

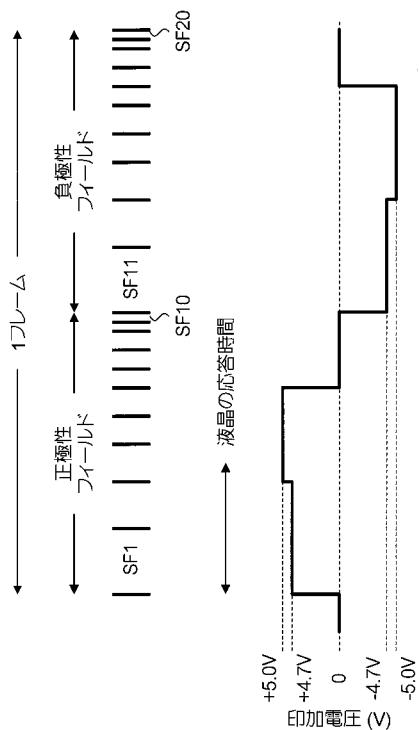

**【0050】**

2 - 2 . 動作

図8は、サブフィールド駆動を説明するタイミングチャートである。この例では、1フ

50

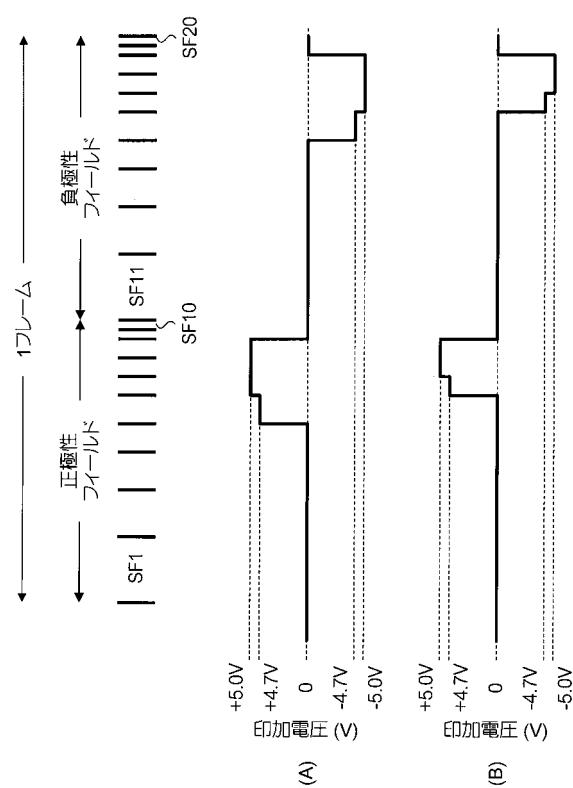

レームは 20 サブフィールドに分割される。以下の説明において k 番目のサブフィールドを SF k と表す。例えば、1 番目のサブフィールドは SF 1 と表す。SF 1 ~ SF 10 においては正極性の電圧が印加され、SF 11 ~ SF 20 においては負極性の電圧が印加される。すなわち、1 フレームは、正極性電圧が印加される正極性フィールドおよび負極性電圧が印加される負極性フィールドの 2 つのフィールドに区分される。この例では、前半 10 サブフィールドが正極性フィールドに含まれ、後半 10 サブフィールドが負極性フィールドに含まれる。なお、図 8 およびこれ以降の図においては、図面が煩雑になるのを防ぐため、SF 1、SF 10、SF 11、および SF 20 のみ符号付で図示している。

#### 【0051】

この例で、正極性フィールドおよび負極性フィールドの各々に含まれるサブフィールドは、2 以上の異なる時間長を有する。時間長の組み合わせは、正極性フィールドと負極性フィールドとで共通である。例えば、SF 1 と SF 11 の時間長は同じである。

#### 【0052】

垂直同期信号 DY は、フレームの始期を示す信号である。この例で、垂直同期信号 DY が L レベルから H レベルに立ち上がったタイミングがフレームの始期を示している。スタート信号 EN 1 ~ EN 10 は、それぞれ、SF 1 ~ SF 10 ( および SF 11 ~ SF 20 ) の始期を示す信号である。この例で、スタート信号 EN k が L レベルから H レベルに立ち上がったタイミングがサブフィールドの始期を示している。信号 VOL は、オン電圧を通常のオン電圧 ( 例えは 5.0V ) から、低いオン電圧 ( 例えは 4.7V ) に変更する時間を示している。この例で、信号 VOL が H レベルの期間は、オン電圧が第 2 電圧に変更される。

#### 【0053】

図 9 は、各サブフィールドにおける動作を示すタイミングチャートである。走査線駆動回路 130 は、制御信号 Yctr に基づいて走査信号 Y1、Y2、Y3、...、Ym を生成する。各走査信号が H レベルになる期間 ( アクティブ期間 ) は 1 水平走査期間 ( 1H ) である。アクティブ期間が順次隣りの走査線 112 にずれていく。これにより、走査線 112 が 1 本ずつ順次選択される。m 本の走査線 112 を順次選択するのに要する時間を 1 フィールドという。

#### 【0054】

データ線駆動回路 140 において、シフトレジスター 141 は、制御信号 Xctr に基づいてサンプリングパルス SR1、SR2、SR3、...、SRn を生成する。スイッチ SW1 ~ SWn は、それぞれ、サンプリングパルス SR1 ~ SRn に基づいて画像データ信号 Vx をサンプリングする。ラッチ 142 は、サンプリング結果をラッチする。すなわち、ラッチ 142 は、サンプリングパルス SRk が H レベルであるときの画像データ Vx の値を、画像データ dk としてラッチする。画像データ Vx は n 本のデータ線 114 に対応するデータを含んでいるが、ラッチ 142 により、画像データ Vx は点順次の画像データ d1 ~ dn に分解される。ラッチ 143 は水平走査期間の開始時点で画像データ d1 ~ dn をラッチし、線順次の画像データ D1 ~ Dn を得る。

#### 【0055】

制御回路 10 から供給される極性信号 Fp は、所定の周波数 ( 例えは 60Hz ) で H レベルから L レベルに変化する信号である。いま、画像データ Dk の値が「1」 ( H レベル ) であった場合を考える。極性信号 Fp が H レベルの間は、出力端子 213 から H レベルの信号が出力され、出力端子 223 および出力端子 233 から L レベルの信号が出力される。これらの信号を受けて、TFT241 がオン状態となり、TFT242 および TFT243 はオフ状態となる。これらのスイッチング動作により、k 番目のデータ線 114 には、電圧 VHIGH が印加される。一方、極性信号 Fp が L レベルの間は、出力端子 223 から H レベルの信号が出力され、出力端子 213 および出力端子 233 から L レベルの信号が出力される。これらの信号を受けて、TFT242 がオン状態となり、TFT241 および TFT243 はオフ状態となる。これらのスイッチング動作により、k 番目のデータ線 114 には、電圧 VOL が印加される。すなわち、画像データ Dk の値が「1」

10

20

30

40

50

である場合は、極性信号 F p に応じて極性の異なる電圧がデータ線 114 に印加される。

#### 【0056】

次に、画像データ D k の値が「0」(L レベル) であった場合を考える。この場合は、極性信号 F p の値によらず、出力端子 233 から H レベルの信号が出力され、出力端子 213 および出力端子 223 から L レベルの信号が出力される。これらの信号を受けて、TFT243 がオン状態となり、TFT241 および TFT242 はオフ状態となる。これらのスイッチング動作により、k 番目のデータ線 114 には、電圧 V Mid が印加される。

#### 【0057】

図 10 は、電気光学装置 1 の動作を示すフローチャートである。図 10 の処理は、サブフィールド毎に行われる。図 10 のフローに先立ち、映像処理回路 30 の変換部 33 は、記憶部 31 に記憶されている LUT311 を参照して、入力映像信号 Vid-in により示される階調値を対応するサブフィールドコードに変換する。

10

#### 【0058】

ステップ S100において、映像処理回路 30 は、現サブフィールドが特定のサブフィールドであるか判断する。特定のサブフィールドはあらかじめ決められており、映像処理回路 30 の記憶部 31 には、特定のサブフィールドを特定するための情報が記憶されている。特定のサブフィールドは、例えば、各フレームの最初のサブフィールド、すなわち SF1 である。現サブフィールドが特定のサブフィールドであると判断された場合 (S100 : YES)、映像処理回路 30 は、処理をステップ S120 に移行する。現サブフィールドが特定のサブフィールドでないと判断された場合 (S100 : NO)、映像処理回路 30 は、処理をステップ S110 に移行する。

20

#### 【0059】

ステップ S110において、走査制御回路 20 は、データ電圧として通常の電圧（例えば、オン電圧が 5.0V になる電圧）が印加されるように、電圧生成回路 50 を制御する。具体的には、映像処理回路 30 は、L レベルの信号 VOL を電圧生成回路 50 に出力する。L レベルの信号 VOL が入力されている間、電圧生成回路 50 は、電圧 VHigh および電圧 VLow として通常の電圧に相当する電圧 V1（例えば 12.0V）および電圧 V3（例えば 2.0V）をそれぞれ出力する。現サブフィールドのサブフィールドコードがオンの場合、データ線駆動回路 140 は、正極性フィールドにおいては電圧 VHigh（この場合、電圧 V1）を、負極性フィールドにおいては電圧 VLow（この場合、電圧 V3）を、対応するデータ線 114 に印加する。現サブフィールドのサブフィールドコードがオフの場合、データ線駆動回路 140 は、電圧 VMid を、対応するデータ線 114 に印加する。

30

#### 【0060】

ステップ S120において、走査制御回路 20 は、データ電圧として低い電圧（例えば、オン電圧が 4.7V になる電圧）が印加されるように、電圧生成回路 50 を制御する。具体的には、映像処理回路 30 は、H レベルの信号 VOL を電圧生成回路 50 に出力する。H レベルの信号 VOL が入力されている間、電圧生成回路 50 は、電圧 VHigh および電圧 VLow として低い電圧に相当する電圧 V2（例えば 11.7V）および電圧 V4（例えば 2.3V）をそれぞれ出力する。電圧 V1 ~ V4 の関係は、V1 > V2 > V4 > V3 である。現サブフィールドのサブフィールドコードがオンの場合、データ線駆動回路 140 は、正極性フィールドにおいては電圧 VHigh（この場合、電圧 V2）を、負極性フィールドにおいては電圧 VLow（この場合、電圧 V4）を、対応するデータ線 114 に印加する。現サブフィールドのサブフィールドコードがオフの場合、データ線駆動回路 140 は、電圧 VMid を、対応するデータ線 114 に印加する。

40

#### 【0061】

図 11 は、第 1 実施形態において液晶素子 120 に印加される電圧を例示する図である。図 11 下段の図において、横軸は時間を、縦軸は液晶素子 120 に印加される電圧を示している。サブフィールドコードは、すべてのサブフィールドでオンである。液晶素子 1

50

20に印加される電圧の絶対値は、SF1で4.7Vであり、それ以外のサブフィールドでは5.0Vである。このように、本実施形態によれば、電圧無印加の状態から急に高い電圧が印加されることが抑制される。したがって、配向不良の発生を低減することができる。

#### 【0062】

##### 2-3. 変形例

###### 2-3-1. 変形例1

図12は、変形例1において液晶素子120に印加される電圧を例示する図である。ステップS100における「特定のサブフィールド」は実施形態で説明したものに限定されない。変形例1において、特定のサブフィールドは、正極性フィールドおよび負極性フィールドのそれぞれの最初のサブフィールド、すなわちSF1およびSF11である。この例で、サブフィールドコードは、「1111100000」である。なお「1」はオンを示し、「0」はオフを示す。異なる時間長(異なる重み)のサブフィールドが用いられる場合、時間長の短い(重みの軽い)サブフィールドほど、オフになる可能性が高い。図12のように時間長の短いサブフィールドがフィールドの後半に偏っている場合、フィールドが切り替わったときに配向不良が発生する可能性がある。変形例1によれば、各フィールドで電圧無印加の状態から急に高い電圧が印加されることが抑制される。したがって、配向不良の発生を低減することができる。なお、1フレームに含まれるフィールド(ブロック)の数は2つに限定されない。例えば、1フレームが4つのフィールドに分割されるサブフィールドのパターンが用いられてもよい。

#### 【0063】

##### 2-3-2. 変形例2

図13は、変形例2において液晶素子120に印加される電圧を例示する図である。変形例2において、特定のサブフィールドは、各フィールドの始期から液晶の応答時間未満のサブフィールドである。例えば、液晶の応答時間が、フレームの始期からSF3の途中までに相当する時間であった場合、SF1およびSF2、並びに対応するSF11およびSF12が、特定のサブフィールドである。変形例2によれば、低い電圧が連続して印加される時間は液晶の応答時間より短い。したがって、配向不良の発生を低減しつつ、所望の階調とのずれを低減することができる。

#### 【0064】

##### 3. 第2実施形態

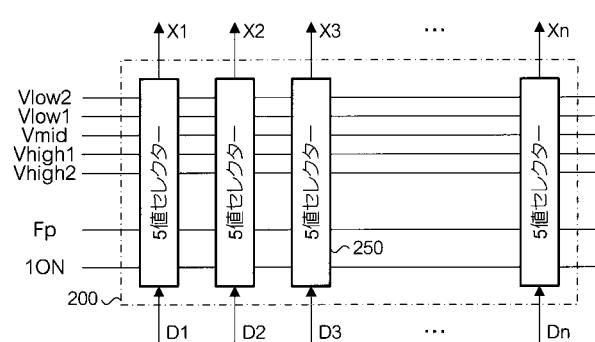

図14は、第2実施形態に係る電気光学装置1の構成を示す図である。以下、第1実施形態と共に通する事項についてはその説明を省略する。第1実施形態においては、低いオン電圧が印加されるサブフィールドは、サブフィールドコードによらず固定されていた。すなわち、ステップS100における「特定のサブフィールド」のサブフィールドコードがオフであった場合、その後のサブフィールドにおいて、急に高い電圧が印加されてしまう場合があった。第2実施形態は、この問題に対処する。

#### 【0065】

第2実施形態において、電圧生成回路50は、VHigh1、VHigh2、VMid、VLow1、およびVLow2の5種類の電圧を供給する。第2実施形態において電圧生成回路50は制御回路10からの制御を受けず、VHigh1、VHigh2、VMid、VLow1、およびVLow2はすべて固定電圧である。これら5種類の電圧値の大小関係は、VHigh1 > VHigh2 > VMid > VLlow2 > VLlow1である。電圧VHigh1は、正極性の通常のオン電圧に相当する電圧である。電圧VLlow2は、負極性の通常のオン電圧に相当する電圧である。電圧VHigh2は、正極性の低いオン電圧に相当する電圧である。電圧VLlow1は、負極性の低いオン電圧に相当する電圧である。電圧VMidは、オフ電圧に相当する電圧である。電圧VMidは、コモン電圧LCcommonと等しい。この例では、VHigh1 = 12.0V、VHigh2 = 11.7V、VMid = 7.0V、VLlow2 = 2.3V、およびVLlow1 = 2.0Vである。

#### 【0066】

10

20

30

40

50

第2実施形態において、映像処理回路は、データ線駆動回路140に対して制御信号1ONを出力する。制御信号1ONは、制御の単位期間（フレームまたはフィールド）においてサブフィールドコードが最初にオンになるサブフィールドを示す信号である。具体的には、制御信号1ONがHレベルのときは、現サブフィールドが最初にオンになるサブフィールドであることを示し、Lレベルのときは現サブフィールドが最初にオンになるサブフィールドでないことを示す。

#### 【0067】

図15は、第2実施形態に係るレベル変換回路200の構成を示す図である。詳細な回路構成は省略するが、レベル変換回路200は、n個の5値セレクター260を有する。

5値セレクター260は、データ線114に対応して設けられている。k番目のデータ線114に対応する5値セレクター260は、極性信号Fp、制御信号1ON、およびデータ信号Dkに応じて、電圧VHigh1、VHigh2、VMid、VLow1、およびVLow2の中から一の電圧を選択し、選択された電圧を出力する。具体的には、データ信号DkがLレベル（オフ）の場合、5値セレクター260は、電圧VMidを選択する。データ信号DkがHレベル（オン）であり極性信号FpがHレベル（正極性）である場合において、制御信号1ONがLレベル（最初にオンになるサブフィールドでない）のときは電圧VHigh1を選択し、制御信号1ONがHレベル（最初にオンになるサブフィールドである）のときは電圧VHigh2を選択する。データ信号DkがHレベル（オン）であり極性信号FpがLレベル（負極性）である場合において、制御信号1ONがLレベル（最初にオンになるサブフィールドでない）のときは電圧VLow1を選択し、制御信号1ONがHレベル（最初にオンになるサブフィールドである）のときは電圧VLow2を選択する。

#### 【0068】

図16は、第2実施形態において液晶素子120に印加される電圧を例示する図である。

図16(A)は最初にオンになるサブフィールドがSF5である例を、図16(B)は最初にオンになるサブフィールドがSF6である例を、それぞれ示している。どのようなサブフィールドコードが与えられても、最初にオンになるサブフィールドにおいて低いオン電圧が印加される。このように、本実施形態によれば、電圧無印加の状態から急に高い電圧が印加されることが抑制される。したがって、配向不良の発生を低減することができる。なお、図16では、各フィールドにおいて最初にオンになるサブフィールドで低いオン電圧が印加される例を説明したが、各フレームにおいて最初にオンになるサブフィールドのみ低いオン電圧が印加されてもよい。

#### 【0069】

##### 4. 変形例

本発明は上述の実施形態に限定されるものではなく、種々の変形実施が可能である。以下、変形例をいくつか説明する。以下の変形例のうち2つ以上のものが組み合わせて用いられてもよい。

#### 【0070】

第1実施形態および第2実施形態においては、対象となるサブフィールド期間のすべてにおいて通常よりも低いオン電圧を印加する例を説明した。この変形例においては、印加されるオン電圧は変化せず（上記の例では5.0V）、対象となるサブフィールド期間の一部においてオフ電圧を印加し、対象となるサブフィールド期間の実効値として、低いオン電圧が印加されるようにしてもよい。例えば、2ミリ秒の時間長を有するサブフィールドに対して120マイクロ秒の間、オフ電圧を印加すれば、実効値として印加されるオン電圧は4.7Vになる。この場合において、オフ電圧を印加する期間は、不連続な複数の期間に分割されてもよい。例えば、オフ電圧を印加する期間は、液晶がほとんど応答しない時間、具体的には、SF1～SF11の中で最も短いサブフィールドよりも短い時間長の期間であってもよい。このようにオフ期間を分割することにより、階調表現に与える影響を低減することができる。

#### 【0071】

10

20

30

40

50

第1実施形態の変形例として説明した変形例が、第2実施形態に対して適用されてもよい。

#### 【0072】

液晶表示装置1等のハードウェアの構成は実施形態で説明したものに限定されない。例えば、極性信号は、画像処理回路30とは別の装置により生成されてもよい。別の例で、データ線駆動回路140の具体的構成は実施形態で説明したものと違う構成であってもよい。

また、実施形態では複数のサブフィールドは、時間長が異なるサブフィールドを含んでいたが、すべて時間長が同一であってもよい。さらに、1フレームを構成するサブフィールドの数は実施形態で説明したものに限定されず、これより多くても少なくともよい。

10

#### 【0073】

液晶表示装置1を用いた電子機器1000は、実施形態で例示したプロジェクターの他にも、テレビジョンや、ビューファインダー型・モニタ直視型のビデオテープレコーダー、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、デジタルスチルカメラ、携帯電話機、タッチパネルを備えた機器等などが挙げられる。

#### 【0074】

液晶105は、VA液晶に限定されない。TN液晶等、VA液晶以外の液晶が用いられてもよい。また、液晶105は、ノーマリー・ホワイトモードの液晶であってもよい。また、液晶以外の電気光学素子が用いられてもよい。

20

電気光学装置としては、実施形態で例示した液晶表示装置の他にも、EPD(マイクロカプセル型電気泳動ディスプレイ)やECD(エレクトロクロミックディスプレイ)等が挙げられる。

実施形態で説明したパラメーター(例えば、階調数、フレーム周波数、画素数、サブフィールド数など)および信号の極性やレベルはあくまで例示であり、本発明はこれに限定されない。

#### 【符号の説明】

#### 【0075】

1…電気光学装置、2…光源、3…制御部、4…投射部、10…制御回路、20…走査制御回路、30…画像処理回路、31…記憶部、32…極性信号生成部、33…変換部、34…出力部、50…電圧生成回路、100…液晶パネル、105…液晶、108…コモン電極、111…画素、112…走査線、114…データ線、115…容量線、116…TFT、118…画素電極、120…液晶素子、125…保持容量、130…走査線駆動回路、140…データ線駆動回路、141…シフトレジスター、142…ラッチ、143…ラッチ、200…レベル変換回路、210…制御部、211…入力端子、212…入力端子、213…出力端子、220…制御部、221…入力端子、222…入力端子、223…出力端子、230…制御部、232…入力端子、233…出力端子、240…選択部、241…TFT、242…TFT、243…TFT、250…NOT回路、260…5値セレクター、311…LUT、100…電子機器

30

【図2】

【 図 3 】

( 4 )

( 5 )

( 6 )

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図1】

---

フロントページの続き

F ターム(参考) 5C080 AA10 AA13 BB05 CC03 DD01 FF11 JJ02 JJ04 JJ07 KK08

KK23 KK43 KK47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 驱动装置，液晶显示装置，电子装置和驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2014191162A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2014-10-06 |

| 申请号            | JP2013066097                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2013-03-27 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 山崎哲朗                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 山崎哲郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/36 G09G3/20.641.E G09G3/20.623.C G02F1/133.575 G02F1/133.550                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZA07 2H193/ZB02 2H193/ZB03 2H193/ZB05 2H193/ZC16 2H193/ZC25 2H193/ZD02 2H193/ZD25 2H193/ZD30 2H193/ZF01 2H193/ZF17 2H193/ZF21 2H193/ZF32 2H193/ZF33 2H193/ZF35 2H193/ZF45 2H193/ZH23 2H193/ZH40 2H193/ZH52 2H193/ZQ11 2H193/ZR04 5C006/AA14 5C006/AA22 5C006/AC21 5C006/AF13 5C006/BB16 5C006/BC12 5C006/BF03 5C006/BF04 5C006/BF26 5C006/EC11 5C080/AA10 5C080/AA13 5C080/BB05 5C080/CC03 5C080/DD01 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/JJ07 5C080/KK08 5C080/KK23 5C080/KK43 5C080/KK47 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

## 摘要(译)

解决问题：为了减少子场驱动系统中的对准故障。解决方案：一种驱动装置具有施加装置，该施加装置根据从视频信号转换而来的子场代码对多个子场中的每个施加第一电压或第二电压。视频被分成帧以由多个子场构成。施加装置在多个子场中的至少一个子场中将导通电压从第一电压改变为第二电压，并且在第二电压中，像素中与参考电势的电势差小于第一电压的电势差，并且当在至少一个子场中将导通电压改变为第二电压时，帧中的像素的灰度与在至少在一个子场中将导通电压保持为第一电压时的帧中的像素的灰度处于相同范围内。一个子字段。