### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2014-2392 (P2014-2392A)

(43) 公開日 平成26年1月9日(2014.1.9)

| (51) Int.Cl. |        |           | FΙ   |        |        |    | テーマコート    | : (参考) |

|--------------|--------|-----------|------|--------|--------|----|-----------|--------|

| G02F         | 1/1343 | (2006.01) | GO2F | 1/1343 |        |    | 2H092     |        |

| GO2F         | 1/1368 | (2006.01) | GO2F | 1/1368 |        |    | 2H192     |        |

| G09F         | 9/30   | (2006.01) | GO9F | 9/30   | 338    |    | 3 K 1 O 7 |        |

| HO1L         | 51/50  | (2006.01) | GO9F | 9/30   | 349A   |    | 5CO94     |        |

| H05B         | 33/12  | (2006.01) | HO5B | 33/14  | A      |    |           |        |

|              |        |           | 審査請求 | さ有 講   | 求項の数 6 | ΟL | (全 73 頁)  | 最終頁に続く |

(21) 出願番号 特願2013-147426 (P2013-147426) (22) 出願日 平成25年7月16日 (2013.7.16) (62) 分割の表示 特願2013-115012 (P2013-115012) の分割 原出願日 平成19年4月5日(2007.4.5) 特願2006-105618 (P2006-105618) (31) 優先権主張番号 (32) 優先日 平成18年4月6日(2006.4.6)

(33) 優先権主張国 日本国(JP) (71) 出願人 000153878

株式会社半導体エネルギー研究所 神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内 Fターム(参考) 2H092 GA14 GA17 GA50 GA59 GA60

JA26 JA46 JB42 HA03 JA25 JB57 JB58 KA08 KB26 MA08 MA10 MA14 MA17 NA27 PA06 PA08 2H192 AA24 BB02 BB12 BB53 **BB54** CB02 CB05 CB13 EA42 FB02 FB22 FB33 HA43 HA47

最終頁に続く

## (54) 【発明の名称】表示装置

#### (57)【要約】 (修正有)

【課題】製造工程数やマスク数が少なく、製造コストが 低い液晶表示装置、電子機器、及び液晶表示装置の製造 方法を提供する。

【解決手段】基板100の上方に形成された第1の電極 102cと、第1の電極の上方に形成された絶縁膜と、 絶縁膜の上方に形成された第2の電極108と、第2の 電極の上方に配置された液晶110と、基板の上方に形 成されたトランジスタとを有し、第2の電極は、開口を 有し、第1の電極は、シリコンを含む半導体膜を有し、 トランジスタは、シリコンを含む半導体膜を有し、第1 の電極が有する半導体膜は、トランジスタが有する半導 体膜と同時に成膜する。

## 【選択図】図7

#### 【特許請求の範囲】

### 【請求項1】

基板上のトランジスタと、

前記トランジスタ上の赤色のカラーフィルタと、

前記カラーフィルタ上に配置され、かつ前記トランジスタと電気的に接続された画素電極と、を有し、

前記トランジスタは、酸化物半導体層を有することを特徴とする表示装置。

【発明の詳細な説明】

## 【技術分野】

### [0001]

本発明は、半導体装置及び液晶表示装置、並びにそれらを用いた電子機器に関する。特に、基板に概略平行な電界を生じさせて、液晶分子を制御する半導体装置及び液晶表示装置、並びにそれらを用いた電気機器に関する。

### 【背景技術】

### [0002]

液晶表示装置の技術開発方針の一つに、視野角を広くすることがある。広い視野角を実現する技術として、基板に概略平行な電界を生じさせて、基板と平行な面内で液晶分子を動かして、階調を制御する方式が用いられている。このような方式として、IPS(In- Plane switching)とFFS(Fringe‐ field switching)がある。これらの方式は、液晶の下方にスリット(開口パターン)を有する第1の電極(例えば各画素別に電圧が制御される画素電極)を配置し、さらに第1の電極の下方に第2の電極(例えば全画素に共通の電圧が供給される共通電極)を配置するものである。画素電極と共通電極との間に電界が加わり、液晶が制御される。このようなレイアウトを取ることにより、液晶には基板と平行方向の電界が加わるため、その電界を用いて液晶分子を制御できる。つまり、基板と平行に配向している液晶分子(いわゆるホモジニアス配向)を、基板と平行な方向で制御できるため、視野角が広くなる。

#### [0003]

従来は、共通電極及び画素電極の双方を、ITO(インジウム錫酸化物)で形成していた(例えば特許文献1参照)

【先行技術文献】

#### 【特許文献】

[0004]

【 特 許 文 献 1 】 特 開 2 0 0 0 - 8 9 2 5 5 号 公 報 ( 図 5 及 び 第 1 4 段 落 )

## 【発明の概要】

【発明が解決しようとする課題】

### [0005]

上記したように、第1の電極(例えば画素電極)の下方に第2の電極(例えば共通電極)を配置する構造とした場合、従来は共通電極と画素電極の双方をITOで形成していた。このため、製造工程数やマスク数が多くなり、製造コストが高くなっていた。

本発明は上記のような事情を考慮してなされたものであり、その目的は、広い視野角を有しており、かつ従来と比べて製造工程数やマスク数が少なく、製造コストが低い液晶表示装置、電子機器、及び液晶表示装置の製造方法を提供することにある。

【課題を解決するための手段】

### [0006]

上記課題を解決するため、本発明に係る液晶表示装置は、基板の上方に形成された第1の電極と、第1の電極の上方に形成された絶縁膜と、絶縁膜の上方に形成された第2の電極と、第2の電極の上方に配置された液晶を有し、第2の電極は、開口パターンを有し、第1の電極は、シリコンを含む半導体膜を具備する。

#### [0007]

本発明に係る半導体装置は、基板の上方に形成された第1の電極と、第1の電極の上方

10

20

30

40

に形成された絶縁膜と、絶縁膜の上方に形成された第2の電極を有し、第2の電極は、開口を有し、第1の電極は、シリコンを含む半導体膜を具備する。

## [0008]

本発明に係る液晶表示装置は、基板の上方に形成された第1の電極と、第1の電極の上方に形成された絶縁膜と、絶縁膜の上方に形成された第2の電極と、第2の電極の上方に配置された液晶と、基板の上方に形成されたトランジスタとを有し、第2の電極は、開口を有し、第1の電極は、シリコンを含む半導体膜を有し、トランジスタは、シリコンを含む半導体膜を有し、第1の電極が有する半導体膜は、トランジスタが有する半導体膜と同時に成膜することを特徴とする。

#### [0009]

本発明に係る半導体装置は、基板の上方に形成された第1の電極と、第1の電極の上方に形成された絶縁膜と、絶縁膜の上方に形成された第2の電極と、基板の上方に形成されたトランジスタとを有し、第2の電極は、開口パターンを有し、第1の電極は、シリコンを含む半導体膜を有し、トランジスタは、シリコンを含む半導体膜を有し、第1の電極が有する前記半導体膜は、トランジスタが有する半導体膜と同時に成膜することを特徴とする。

### [0010]

この液晶表示装置および半導体装置によれば、第1の電極は、トランジスタが有する半導体膜と同時に成膜される。成膜後、同時にエッチングされて、同時にパターニングされる。したがって、同一の材料を含むこととなる。また、n型不純物やp型不純物も、同時に導入される場合がある。その場合は、不純物の濃度も概ね等しい部分を有することとなる。ただし、トランジスタは、不純物を導入される部分と、僅かに不純物を導入される部分と、ほとんど不純物が導入されない部分などを有している。第1の電極は、トランジスタが有する半導体膜において、不純物が導入される部分と概ね同じ状態となっている場合が多い。このように、トランジスタと同時に第1の電極を形成することが出来る。そのため、追加で工程が増えることなく、第1の電極を形成することが出来る。また、広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を提供することができる。

## [0011]

なお、開口には、スリット等の閉じられた開口のみではなく、例えば櫛歯形状の電極における櫛歯部分の相互間のスペース等、導電体パターンの相互間に位置していて該導電体パターンが形成されていないスペースを含むものとする。以下、同様である。

#### [0012]

なお、上記した液晶表示装置、半導体装置において、第1の電極と第2の電極の間に位置する層間絶縁膜を具備し、第1の開口以外の、第2の電極と第1の電極とが相互に重なっている部分において、第1の電極、層間絶縁膜、及び第2の電極は容量素子として機能させることが出来る。この場合、保持容量を大きくすることができる。従って、前記トランジスタがオフになったとき、画素電極の電位は保持されやすくなる。

### [0013]

本発明に係る液晶表示装置は、基板の上方に形成された第1の電極と、第1の電極の上方に形成された絶縁膜と、絶縁膜の上方に形成された第2の電極と、第2の電極の上方に配置された液晶と、基板の上方に形成されたトランジスタとを有し、第2の電極は、開口有し、第1の電極は、シリコンを含む半導体膜を有し、トランジスタは、シリコンを含む半導体膜を有し、第1の電極が有する半導体膜は、トランジスタが有する半導体膜と同時に成膜され、第1の電極が有する半導体膜と、トランジスタが有する半導体膜とは、同じ導電型の不純物を含むことを特徴とする。

#### [0014]

本発明に係る半導体装置は、基板の上方に形成された第1の電極と、第1の電極の上方に形成された絶縁膜と、絶縁膜の上方に形成された第2の電極と、基板の上方に形成されたトランジスタとを有し、第2の電極は、開口パターンを有し、第1の電極は、シリコン

10

20

30

40

20

30

40

50

を含む半導体膜を有し、トランジスタは、シリコンを含む半導体膜を有し、第1の電極が有する半導体膜は、トランジスタが有する半導体膜と同時に成膜され、第1の電極が有する半導体膜と、トランジスタが有する半導体膜とは、同じ導電型の不純物を含むことを特徴とする。

[0015]

このように、第1の電極と、トランジスタとが、同じ導電型の不純物( n 型や p 型など )を有することにより、レイアウトを効率的に行うことができ、開口率が向上する。

[0016]

本発明に係る液晶表示装置は、基板の上方に形成されたトランジスタを有し、トランジスタは、半導体膜を有し、半導体膜の一部は、第1の電極を構成し、第1の電極の上方に形成された絶縁膜と、絶縁膜の上方に形成された第2の電極と、第2の電極の上方に配置された液晶とを有し、第2の電極は、開口を具備する。

[0017]

本発明に係る半導体装置は、基板の上方に形成されたトランジスタを有し、トランジスタは、半導体膜を有し、半導体膜の一部は、第1の電極を構成し、第1の電極の上方に形成された絶縁膜と、絶縁膜の上方に形成された第2の電極とを有し、第2の電極は、開口を具備する。

[0018]

このように、第1の電極と、トランジスタの有する半導体膜とが、同じアイランド(島)に形成されていることにより、レイアウトを効率的に行うことができ、開口率が向上する。

[0019]

本発明に係る液晶表示装置は、上記構成において、第1の電極は画素電極であり、第2 の電極は共通電極であることを特徴とする。

[0020]

本発明に係る半導体装置は、上記構成において、第1の電極は画素電極であり、第2の電極は共通電極であることを特徴とする。

[0021]

本発明に係る液晶表示装置は、上記構成において、第1の電極は共通電極であり、第2の電極は画素電極であることを特徴とする。

[0022]

本発明に係る半導体装置は、上記構成において、第1の電極は共通電極であり、第2の電極は画素電極であることを特徴とする。

[0023]

本発明に係る液晶表示装置は、上記構成において、第1の電極と第2の電極との間の電界によって、液晶の配向を制御することを特徴とする。

[0024]

20

30

40

50

なぜなら、ゲートソース間電圧の絶対値を大きくできるため、スイッチとして動作しやすいからである。なお、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。CMOS型のスイッチにすると、スイッチを介して出力する電圧(つまり入力電圧)が、出力電圧に対して、高かったり、低かったりして、状況が変化する場合においても、適切に動作を行うことが出来る。なお、本発明におけるスイッチとしては、例えば、画素電極を制御するTFTや、駆動回路部に用いるスイッチ素子等が挙げられるが、これ以外の部分においても、電流の流れを制御する必要がある部分であれば、スイッチを用いることができる。

## [0025]

なお、本発明において、「接続されている」、とは、「電気的に接続されている」場合と「直接接続されている」場合とを含むものとする。ここで、「電気的に接続されている」場合」とは、所定の接続関係に加え、その間に電気的な接続を可能とする他の素子(例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど)が配置されていてもよい状態を言うものとする。また、「直接接続されている」とは、「電気的に接続されている」のなかでも、特に、電気的な接続を可能とする他の素子を間に介さずに接続されていて、直接接続されている」とは、「電気的に接続されている」場合において、所定の接続関係の間に他の素子を含まないものを特に指すこととする。なお、「直接接続されている」と同様の意味を指すものとして「直接的に接続されている」を用いることがある。

## [0026]

なお、表示素子や表示装置や発光装置は、様々な形態を用いることや、様々な素子を有 することが出来る。例えば、EL素子(有機EL素子、無機EL素子又は有機物及び無機 物を含むEL素子)、電子放出素子、液晶素子、電子インク、グレーティングライトバル ブ(GLV)、プラズマディスプレイ(PDP)、デジタルマイクロミラーデバイス(D M D )、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用に よりコントラストが変化する表示媒体を適用することができる。なお、EL素子を用いた 表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールド エミッションディスプレイ(FED)やSED方式平面型ディスプレイ(SED:Sur face-conduction Electron-emitter Disply) など、液晶素子を用いた表示装置としては液晶ディスプレイ、透過型液晶ディスプレイ、 半 透 過 型 液 晶 デ ィ ス プ レ イ 、 反 射 型 液 晶 デ ィ ス プ レ イ 、 電 子 イ ン ク を 用 い た 表 示 装 置 と し ては電子ペーパーがある。液晶素子以外に対する本発明の適用方法としては、例えば、シ リコンを含む電極をEL素子等の電極として用いることが挙げられる。これにより、低コ ストにEL素子等の素子を作製することができる。この場合、電極は開口パターンを有し ていても良いし、有さなくても良い。有機EL素子に本発明のシリコンを含む電極を用い るのであれば、電極間に有機化合物を含む層を挟む構成であることが好ましいが、これに 限られない。一方で、無機EL素子に本発明のシリコンを含む電極を用いるのであれば、 電極間に無機化合物を含む層を挟む構成であっても良いし、電極上に無機化合物を含む層 を形成する構成であっても良い。無機EL素子においては交流駆動が可能なためである。 この場合、第1の電極と第2の電極とにより形成される横方向電界を用いて発光させるこ とができる。この様な構成を用いることで、光が射出する側に、電極等の光を減衰させる 構造を設けずとも良いため、EL表示装置の輝度が向上し、また、EL素子の劣化が低減 することにつながる。

# [ 0 0 2 7 ]

なお、本発明において、トランジスタは、様々な形態のトランジスタを適用させることが出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ(TFT)、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、ZnO、a.InGaZnOなどの化合物半導体を用いたトランジスタ、有機半導体やカーボンナノチューブを用いたトランジ

20

30

40

50

スタ、その他のトランジスタを適用することができる。また、トランジスタが配置されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。従って例えば、単結晶基板、SOI基板、ガラス基板、プラスチック基板、紙基板、セロファン基板、石材基板などに配置することが出来る。また、ある基板でトランジスタを形成し、その後、別の基板にトランジスタを移動させて、別の基板上に配置するようにしてもよい。

#### [0028]

なお、すでに述べたように、本発明におけるトランジスタは、様々なタイプを用いるこ とができ、様々な基板上に形成させることができる。したがって、回路の全てが、ガラス 基板上に形成されていてもよいし、プラスチック基板に形成されていてもよいし、単結晶 基板に形成されていてもよいし、SOI基板上に形成されていてもよいし、どのような基 板上に形成されていてもよい。回路の全てが基板上に形成されていることにより、部品点 数 を 減 ら し て コ ス ト を 低 減 さ せ る こ と や 、 回 路 部 品 と の 接 続 点 数 を 減 ら し て 信 頼 性 を 向 上 させることができる。あるいは、回路の一部が、ある基板に形成されており、回路の別の 一部が、別の基板に形成されていてもよい。つまり、回路の全てが同じ基板上に形成され ていなくてもよい。例えば、回路の一部は、ガラス基板上にトランジスタを用いて形成し 、回路の別の一部は、単結晶基板上に形成し、そのICチップをCOG(Chip G1ass)で接続してガラス基板上に配置してもよい。あるいは、そのICチップを TAB(Tape Auto Bonding)やプリント基板を用いてガラス基板と接 続してもよい。このように、回路の一部が同じ基板上に形成されていることにより、部品 点数を減らしてコストを低減させることや、回路部品との接続点数を減らして信頼性を向 上させることができる。また、駆動電圧が高い部分や駆動周波数が高い部分は、消費電力 が大きくなってしまうので、そのような部分は同じ基板に形成しないようにすれば、消費 電力の増加を防ぐことができる。

### [ 0 0 2 9 ]

なお、トランジスタの構成は、様々な形態をとることができ、特定の構成に限定されな い。例えば、ゲート本数が2本以上になっているマルチゲート構造を用いてもよい。マル チゲート構造にすることにより、オフ電流を低減させることや、トランジスタの耐圧を向 上させて信頼性を良くすることや、飽和領域で動作する時に、ドレイン・ソース間電圧が 変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることがで きる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上 下にゲート電極が配置されている構造にすることで、チャネル形成領域が増えることによ り電流値を大きくすることや、空乏層ができやすくなることによりS値を小さくすること ができる。また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネル の下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆 スタガ構造でもよいし、チャネル形成領域が複数の領域に分かれていてもよいし、並列に 接続されていてもよいし、直列に接続されていてもよい。また、チャネル(もしくはその 一部)にソース電極やドレイン電極が重なっていてもよい。チャネル(もしくはその一部 )にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に 電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域があっ てもよい。LDD領域を設けることにより、オフ電流を低減させることや、トランジスタ の耐圧を向上させて信頼性を良くすることや、飽和領域で動作する時に、ドレイン・ソー ス間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にす ることができる。

# [0030]

なお、本発明においては、一画素とは、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、R(赤)G(緑)B(青)の色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。なお、色要素は、三色に限定されず、それ以上でもよく、

例えば、RGBW(Wは白)や、RGBに、イエロー、シアン、マゼンダを追加したものなどがある。また、別の例としては、1つの色要素について、複数の領域を用いて明るさを制御する場合は、その領域一つ分を一画素とする。よって、一例としては、面積階調を行う場合、一つの色要素につき、明るさを制御する領域が複数あり、その全体で階調を表現するわけであるが、明るさを制御する領域の一つ分を一画素とする。よって、その場合は、一つの色要素は、複数の画素で構成されることとなる。また、その場合、画素によって、表示に寄与する領域の大きさが異なっている場合がある。また、一つの色要素につき複数ある、明るさを制御する領域において、つまり、一つの色要素を構成する複数の画素において、各々に供給する信号を僅かに異ならせるようにして、視野角を広げるようにしてもよい。

10

なお、一画素(三色分)と記載する場合は、RとGとBの三画素分を一画素と考える場合であるとする。一画素(一色分)と記載する場合は、一つの色要素につき、複数の画素がある場合、それらをまとめて一画素と考える場合であるとする。

### [0031]

なお、本発明において、画素は、マトリクス状に配置(配列)されている場合を含んでいる。ここで、画素がマトリクスに配置(配列)されているとは、縦縞と横縞を組み合わせたいわゆる格子状にストライプ配置されている場合を含んでいる。そして、三色の色要素(例えばRGB)でフルカラー表示を行う場合に、三つの色要素がいわゆるデルタ配置されている場合も含むものとする。さらに、ベイヤー配置されている場合も含んでいる。なお、色要素は、三色に限定されず、それ以上でもよく、例えば、RGBW(Wは白)や、RGBに、イエロー、シアン、マゼンダを追加したものなどがある。また、色要素毎にその発光領域の大きさが異なっていてもよい。

20

### [0032]

トランジスタとは、それぞれ、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル形成領域を有する。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、本発明においては、ソース及びドレインとして機能する領域を、それぞれ第1端子、第2端子と表記する。

[0033]

30

なお、ゲートとは、ゲート電極とゲート配線(ゲート線またはゲート信号線等とも言う)とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極とは、チャネル形成領域やLDD(Lightly Doped Drain)領域などを形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部分の導電膜のことを言う。ゲート配線とは、各画素のゲート電極の間を接続するためや、ゲート電極と別の配線とを接続するための配線のことを言う。

## [0034]

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分も存在する。そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線とオーバーラップしてチャネル形成領域がある場合、その領域はゲート配線として機能しているが、ゲート電極としても機能していることになる。よって、そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

40

### [0035]

また、ゲート電極と同じ材料で形成され、ゲート電極とつながっている領域も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線とつながっている領域も、ゲート配線と呼んでも良い。このような領域は、厳密な意味では、チャネル形成領域とオーバーラップしていなかったり、別のゲート電極と接続させる機能を有してなかったりする場合がある。しかし、製造コスト、工程の削減、レイアウトの簡略化な

どの関係で、ゲート電極やゲート配線と同じ材料で形成され、ゲート電極やゲート配線と つながっている領域がある。よって、そのような領域もゲート電極やゲート配線と呼んで も良い。

#### [0036]

また、例えば、マルチゲートのトランジスタにおいて、1つのトランジスタのゲート電極と、別のトランジスタのゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような領域は、ゲート電極とゲート電極とを接続させるための領域であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1つのトランジスタであると見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極やゲート配線と同じ材料で形成され、それらとつながって配置されているものは、ゲート電極やゲート配線と呼んでも良い。また、例えば、ゲート電極とゲート配線とを接続している部分の導電膜も、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い

[0037]

なお、ゲート端子とは、ゲート電極の領域や、ゲート電極と電気的に接続されている領域について、その一部分のことを言う。

### [0038]

なお、ソースとは、ソース領域とソース電極とソース配線(ソース線またはソース信号線等とも言う)とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、p型不純物(ボロンやガリウムなど)やn型不純物(リンやヒ素など)が多く含まれる半導体領域のことを言う。従って、少しだけp型不純物やn型不純物が含まれる領域、いわゆる、LDD(Lightly Doped Drain)領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各画素のソース電極の間を接続するためや、ソース電極と別の配線とを接続するための配線のことを言う。

[0039]

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分も存在する。そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているソース配線とオーバーラップしてソース領域がある場合、その領域はソース配線として機能しているが、ソース電極としても機能していることになる。よって、そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

[0040]

また、ソース電極と同じ材料で形成され、ソース電極とつながっている領域や、ソース電極とソース電極とを接続する部分も、ソース電極と呼んでも良い。また、ソース領域とオーバーラップしている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線とつながっている領域も、ソース配線と呼んでも良い。このような領域は、厳密な意味では、別のソース電極と接続させる機能を有していなかったりする場合がある。しかし、製造コスト、工程の削減、又はレイアウトの簡略化などの関係で、ソース電極やソース配線と同じ材料で形成され、ソース電極やソース配線とつながっている領域がある。よって、そのような領域もソース電極やソース配線と呼んでも良い。

[ 0 0 4 1 ]

また、 例えば、ソース電極とソース配線とを接続している部分の導電膜も、ソース電極 と呼んでも良いし、ソース配線と呼んでも良い。

### [0042]

なお、ソース端子とは、ソース電極の領域や、ソース電極や、ソース電極と電気的に接続されている領域について、その一部分のことを言う。

[0043]

20

10

30

なお、ドレインについては、ソースと同様である。

### [0044]

なお、本発明において、半導体装置とは半導体素子(トランジスタやダイオードなど) を含む回路を有する装置をいう。また、半導体特性を利用することで機能しうる装置全般 でもよい。また、表示装置とは、表示素子(液晶素子や発光素子など)を有する装置のこ とを言う。なお、基板上に液晶素子やEL素子などの表示素子を含む複数の画素やそれら の画素を駆動させる周辺駆動回路が形成された表示パネル本体のことでもよい。さらに、 フレキシブルプリントサーキット(FPC)やプリント配線基盤(PWB)が取り付けら れたものも含んでもよい。また、発光装置とは、特にEL素子やFEDで用いる素子など の自発光型の表示素子を有している表示装置をいう。液晶表示装置とは、液晶素子を有し ている表示装置をいう。

[0045]

なお、本発明において、「ある物」の上に形成されている、あるいは、「ある物」上に 形成されている、というように、「ある物」の上に、あるいは、「ある物」上に、という 記載については、「ある物」の上に直接接していることに限定されない。直接接してはい ない場合、つまり、間に別のものが挟まっている場合も含むものとする。従って例えば、 層Aの上に(もしくは層A上に)、層Bが形成されている、という場合は、層Aの上に直 接接して層Bが形成されている場合と、層Aの上に直接接して別の層(例えば層Cや層D など)が形成されていて、その上に直接接して層Bが形成されている場合とを含むものと する。また、「ある物」の上方に、という記載についても同様であり、ある物の上に直接 接していることに限定されず、間に別のものが挟まっている場合も含むものとする。従っ て例えば、層Aの上方に、層Bが形成されている、という場合は、層Aの上に直接接して 層Bが形成されている場合と、層Aの上に直接接して別の層(例えば層Cや層Dなど)が 形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。な お、「ある物」の下に、あるいは、「ある物」の下方に、の場合についても、同様であり 、直接接している場合と、接していない場合とを含むこととする。ここで特に指定しない 場合には、基板の一方の面を「上」方向とし、基板の他方の面を「下」方向とする。つま り、作製段階において、層Aの「上」に層Bを形成した構成を有している場合、その完成 物の天地を逆転したとしても、層Aの「上」に層Bが形成された構成と言うことができる 。すなわち、「上」または「下」といった方向の持つ意味は、「ある物」に対して、対象 物がそのどちら側に形成されるのかを示すに留まり、一般的な「上」および「下」の持つ 意味である「重力に対する方向」を言うものではない。もちろん、「左」、「右」といっ た、その他の方向についても同様である。なお、特に指定する場合にはこれに限られず、 重力の方向を基準としても良いし、その他の基準を用いても良い。

### 【発明の効果】

### [0046]

本 発 明 に よ れ ば 、 ト ラ ン ジ ス タ の 有 す る 半 導 体 膜 と 液 晶 を 駆 動 す る 第 1 の 電 極 と を 同 一 工程で形成することができる。その結果、第1の電極を、マスク数(レチクル数)や製造 工程数を増やすことなく製造することが出来る。

[0047]

従って、広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を 提供することができる。

【図面の簡単な説明】

[ 0 0 4 8 ]

- 【図1】本発明に係る液晶表示装置の構成を示した図。

- 【 図 2 】 本 発 明 に 係 る 液 晶 表 示 装 置 の 構 成 を 示 し た 図 。

- 【図4】本発明に係る液晶表示装置の構成を示した図。

- 【 図 5 】 本 発 明 に 係 る 液 晶 表 示 装 置 の 構 成 を 示 し た 図 。

- 【図6】本発明に係る液晶表示装置の構成を示した図。

10

20

30

40

- 【図3】本発明に係る液晶表示装置の構成を示した図。

20

30

40

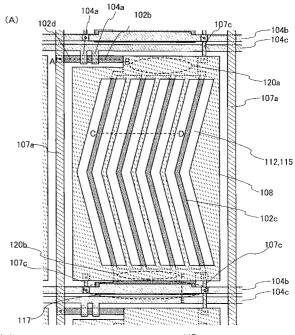

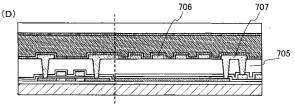

- 【図7】(A)は第1の実施形態に係る液晶表示装置の構成を説明する為の平面図、(B)は(A)のA-B断面図及びC-D断面図。

- 【図8】図7(B)の別の構成を示した図。

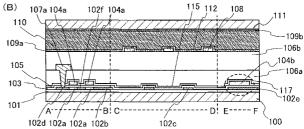

- 【図9】(A)は第2の実施形態に係る液晶表示装置の構成を説明する為の平面図、(B

- ) は ( A ) の A B 断面図及び C D 断面図。

- 【図10】(A)は第3の実施形態に係る液晶表示装置の構成を説明する為の平面図、(

- B)は(A)のA-B断面図、C-D断面図、及びE-F断面図。

- 【図11】(A)は第4の実施形態に係る液晶表示装置の構成を説明する為の平面図、(

- B)は(A)のA-B断面図及びC-D断面図。

- 【図12】(A)は第5の実施形態に係る液晶表示装置の構成を説明する為の平面図、(

- B) は(A) の A B 断面図及び C D 断面図。

- 【図13】(A)は第6の実施形態に係る液晶表示装置の構成を説明する為の平面図、(

- B)は(A)のA-B断面図、C-D断面図、及びE-F断面図。

- 【図14】(A)は第7の実施形態に係る液晶表示装置の構成を説明する為の平面図、(

- B)は(A)のA B断面図、C-D断面図、及びE-F断面図。

- 【図15】(A)は第8の実施形態に係る液晶表示装置の構成を説明する為の平面図、(

- B)は(A)のA B断面図、C-D断面図、及びE-F断面図。

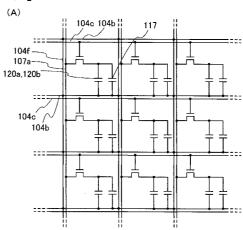

- 【図16】(A)は第9の実施形態に係る液晶表示装置の回路図、(B)は第10の実施形態に係る液晶表示装置の構成の回路図。

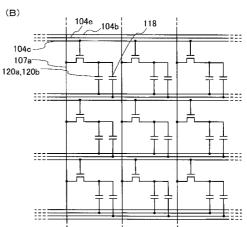

- 【図17】(A)は第11の実施形態に係る液晶表示装置の回路図、(B)は第12の実施形態に係る液晶表示装置の回路図。

- 【図18】(A)は第13の実施形態に係る液晶表示装置の構成を説明する為の平面図、

- (B)は(A)のA B断面図及びC-D断面図。

- 【図19】(A)は第14の実施形態に係る液晶表示装置の構成を説明する為の断面図、

- (B)は第15の実施形態に係る液晶表示装置の構成を説明する為の断面図。

- 【図20】第16の実施形態に係る液晶表示装置の構成を説明する為の断面図。

- 【図21】(A)は図20に示した液晶表示装置の平面図、(B)は(A)の画素部の拡大図。

- 【図22】(A)は第17の実施形態に係る液晶表示装置の平面図、(B)は(A)の画素部の拡大図。

- 【図23】第18の実施形態に係る液晶表示装置の構成を説明する為の断面図。

- 【図24】第19の実施形態に係るFFS方式の液晶表示装置の電極の形状を説明する為の平面図。

- 【図25】第20の実施形態に係るIPS方式の液晶表示装置の電極の形状を説明する為の平面図。

- 【図26】(A)~(E)は、実施例1の液晶表示モジュールの製造方法を示す断面図。

- 【 図 2 7 】 ( A ) ~ ( D ) は 、 実 施 例 1 の 液 晶 表 示 モ ジ ュ ー ル の 製 造 方 法 を 示 す 断 面 図 。

- 【図 2 8 】(A)は実施例 1 の液晶表示モジュールの平面図、(B)は(A)の K L 断面図。

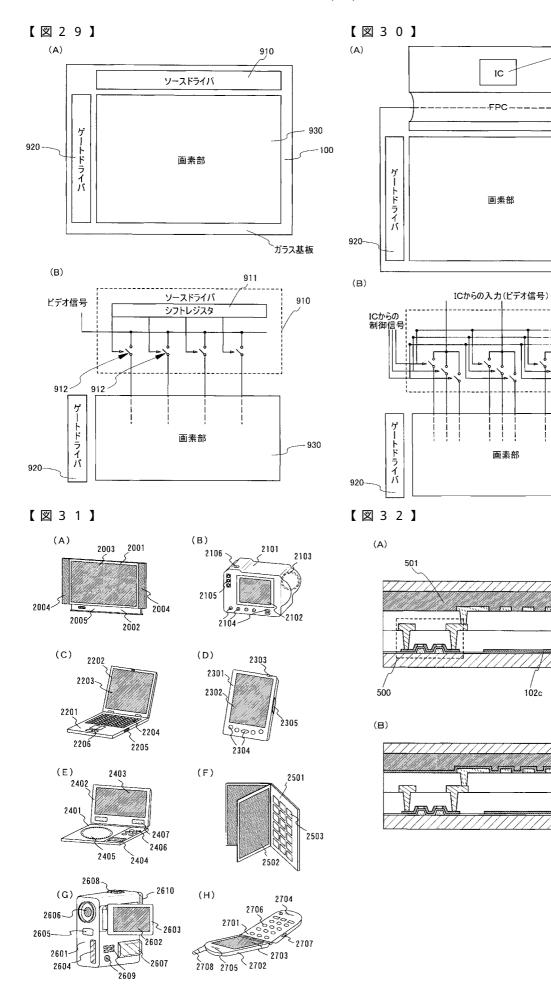

- 【図29】実施例2に係る液晶表示モジュールを説明する為の図。

- 【図30】実施例2に係る液晶表示モジュールを説明する為の図。

- 【 図 3 1 】( A ) ~ ( H ) は 、 実 施 例 3 に よ る 電 子 機 器 を 示 す 斜 視 図 。

- 【図32】第21の実施形態に係る無機EL素子の構成を説明するための断面図。

- 【図33】第22の実施形態に係る有機EL素子の構成を説明するための断面図。

- 【図34】第23の実施形態に係る反射型液晶表示装置の構成および作製工程を説明するための断面図。

- 【発明を実施するための形態】

- [0049]

- 以下、本発明の実施形態について図面を参照しながら説明する。但し、本発明は多くの 異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することな

くその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施形態の記載内容に限定して解釈されるものではない。

### [0050]

(第1の実施形態)

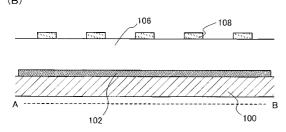

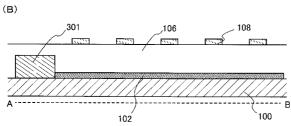

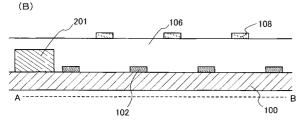

図1は、本発明の基本的な場合の例を示す。図1(A)には、平面図、図1(B)には、断面図を示す。

[0051]

基板100の上に、第1の電極102が形成されている。第1の電極102は、従来は、ITO(インジウム錫酸化物)を用いて形成されていた。

## [0052]

本発明において、第1の電極102は、一例としては、シリコンを含む半導体材料で形成される。ただし、これに限定されない。また、アモルファス(非晶質)シリコンでもよいが、導電性をあげるために、ポリ(多結晶)シリコンや単結晶シリコンなども用いられる。また、さらに導電性をあげるために、リンやボロンやガリウムやヒ素などの不純物(p型不純物やn型不純物)を含む場合が多い。

[0053]

第1の電極102にシリコンを含む半導体材料を用いるのは、シリコンの透過率が高いためである。また第1の電極102は、膜厚が薄いため、光を透過させることが出来る。 透過率は、好ましくは50%以上、より好ましくは、80%以上が望ましい。これにより 、視認性のよいものが実現できる。

[0054]

なお、基板100と第1の電極102との間には、別の絶縁層や導電層が配置されていてもよい。例えば、基板100から侵入する不純物をブロックするための絶縁層や、ゲート電極や、ゲート配線や、ゲート絶縁膜などが配置されていてもよい。

[0055]

第1の電極102の上には、絶縁膜106が形成されている。なお、絶縁膜106は、 単層でもよいし、多層構造になっていてもよい。

[0056]

なお、絶縁膜106を構成する材料は、無機材料又は有機材料を用いることができる。有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト、シロキサン、又はポリシラザンなどを用いることができる。無機材料としては、酸化シリコン(SiO $_{\times}$  N $_{y}$  :  $_{\times}$  と 文)、窒化シリコン(SiN $_{\times}$  )、酸化窒化シリコン(SiO $_{\times}$  N $_{y}$  :  $_{\times}$  と 文)、窒化酸化シリコン(SiN $_{\times}$  O $_{y}$  :  $_{\times}$  > y)など、酸素又は窒素を有する絶縁物質を用いることができる。また、これらの膜を複数積層した積層膜であってもよい。また、有機材料と無機材料を組み合わせて積層膜にしてもよい。

[0057]

なお、絶縁膜として無機材料を用いることにより、水分や不純物の侵入を止めることが 出来る。特に、窒素を含む層を用いると、水分や不純物をブロックする機能が高い。

[0058]

なお、絶縁膜として有機材料を用いることにより、表面を平坦にすることが出来る。そのため、その上の層に対して、よい効果をもたらすことが出来る。例えば、有機材料の上に形成する層も平坦にすることが出来るため、液晶の配向の乱れを防いだりすることが出来たり、配線が切れてしまうことを防いだり、レジストを正確に形成することができたりする。

[0059]

絶縁膜106の上には、第2の電極108を形成する。第2の電極108は、光透過性の高い材料が望ましい。例えば、インジウム(In)、錫(Sn)、酸素(O)で構成された群から選ばれた一つ又は複数の元素、もしくは、前記群から選ばれた一つ又は複数の元素を成分とする化合物や合金材料(例えば、インジウム錫酸化物(ITS)、インジウム亜鉛酸化物(ITSO))が望ま

10

20

30

40

しい。特に、IZOは、パターニングしやすく、正確な形状で微細に形成しやすいため、 好適である。ただし、これに限定されない。

### [0060]

なお、第2の電極108では、開口パターン(スリット)を形成する。なお、この開口パターンは、第1の電極102と第2の電極108との間に、基板に概略平行な方向の電界を発生させるためのものである。したがって、基板に概略平行な方向を含む電界を発生させることが可能であれば、さまざまな形状を取ることが出来る。ここで、概略平行とは、多少のずれを含みつつ、平行な場合を指す。したがって、表示に支障が出ない範囲において、平行な方向からずれていてもよい。例えば、±10度、より望ましくは±5度程度のずれを有している場合を含んでいる。

[0061]

よって、前記開口パターンには、スリット等の閉じられた開口パターンのみではなく、例えば櫛歯形状の電極における櫛歯部分の相互間のスペース等、導電体パターンの相互間に位置していて該導電体パターンが形成されていないスペースを含むものとする。つまり、電極と電極との間に、隙間や間隔があいていればよい。

[0062]

このように、第2の電極108と第1の電極102との間で電界を発生させ、液晶分子の配向状態を制御することが出来る。

[0063]

なお、各画素に電極が形成されている場合、映像信号に応じて画素毎に異なる信号が供給される電極、いわゆる画素電極は、第2の電極108と第1の電極102のどちらにおいても適用させることが出来る。よって、例えば、第2の電極108を画素電極とし、第1の電極102を共通電極とすることが可能であるし、また第2の電極108を共通電極とし、第1の電極102を画素電極とすることも可能である。

[0064]

画素電極は、トランジスタのソースもしくはドレインと接続される場合が多いため、第1の電極102や第2の電極108を画素電極とすることにより、構造を簡略化することが出来る。また、共通電極は、全ての画素同士で接続される場合が多いため、第1の電極102や第2の電極108を共通電極にすることにより、構造を簡略化することが出来る

[0065]

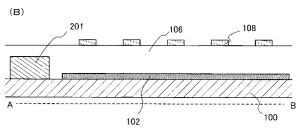

次に、トランジスタ 2 0 1 を有する場合について、図 2 ( A )には、平面図、図 2 ( B )には、断面図を示す。トランジスタ 2 0 1 は、第 1 の電極 1 0 2 や第 2 の電極 1 0 8 の近辺に配置される。

[0066]

このとき、トランジスタ201が有する膜と、第1の電極102とを同時に形成することが出来る。その結果、第1の電極を、マスク数(レチクル数)や製造工程数を増やすことなく製造することが出来る。

[0067]

一例としては、トランジスタ201が有する半導体層と、第1の電極102とを同時に 形成することが出来る。したがって、トランジスタ201が有する半導体層と第1の電極 102を同時に成膜し、同時にエッチングすることによって、同時にパターニングするこ とが出来る。また、半導体層がポリシリコンの場合は、同時に結晶化されることとなる。

[0068]

そのため、トランジスタ201が有する半導体層と、第1の電極102とは、同じ材料を含むこととなる。

[0069]

なお、トランジスタ201が有する半導体層の一部に、リンやボロンやガリウムやヒ素などの不純物(p型不純物やn型不純物)を導入する場合、同時に、第1の電極102にも、導入することが望ましい。同時に導入する場合は、導入される部分の上の膜の厚さや

10

20

30

40

20

30

40

50

材質に影響を受けるが、同様な層構造の下に形成されている場合は、少なくとも、トランジスタ201が有する半導体層の一部のある領域では、第1の電極102のある領域と、概ね等しい濃度の不純物(p型不純物やn型不純物)を有することとなる。例えば、トランジスタ201が有する半導体層のうちソース領域又はドレイン領域を形成する層と第1の電極102を形成する半導体層とが概ね等しい濃度の不純物領域を有することとなる。【0070】

なお、トランジスタ201が有する半導体層には、チャネル形成領域を含む場合が多い。チャネル形成領域上には、ゲート絶縁膜を介して、ゲート電極が配置されている。このチャネル形成領域には、通常、濃度の高い不純物(p型不純物やn型不純物)は、導入されない。ただし、濃度が非常に低い不純物(p型不純物やn型不純物)は、しきい値電圧値を調整するために、導入される場合がある。また、トランジスタ201が有する半導体層には、濃度が低い不純物(p型不純物やn型不純物)が、LDD(Lightly doped drain)領域を形成するために、導入される場合がある。以上のことから、トランジスタ201が有する半導体層は、様々な濃度の不純物(p型不純物やn型不純物)を有する領域が複数存在する場合が多い。

[0071]

なお、トランジスタ201が有する半導体層と、第1の電極102とにおいて、同時に不純物(p型不純物やn型不純物)を導入する場合、トランジスタ201が有する半導体層と第1の電極102とは、非常に近接して配置されていてもよい。なぜなら、同じ不純物(p型不純物やn型不純物)を導入することが多いためである。そのため、トランジスタ201と第1の電極102とを、非常に効率的にレイアウトすることができ、開口率を向上させることが出来る。

[0072]

ただし、トランジスタ201が有する半導体層の一部と、第1の電極102とで、導電型が異なっていてもよい。その場合は、トランジスタ201とは別のトランジスタと同時に、不純物(p型不純物やn型不純物)が導入されることとなる。したがってその場合は、少なくとも、トランジスタ201とは別のトランジスタが有する半導体層の一部のある領域では、第1の電極102のある領域と、概ね等しい濃度の不純物(p型不純物やn型不純物)を有することとなる。一例としては、トランジスタ201とは別のトランジスタは、ソース信号線駆動回路やゲート信号線駆動回路などの一部として配置されている。

[0073]

なお、トランジスタ201と、第1の電極102、もしくは、第2の電極108とは、電気的に接続される場合が多い。そして、電気的に接続された電極が、画素電極となる場合が多い。トランジスタ201と、第1の電極102、もしくは、第2の電極108とは、接続孔や配線などを介して、電気的に接続される場合が多い。

[0074]

なお、図2では、第1の電極102が、トランジスタ201が有する膜と同時に形成される場合について述べたが、これに限定されない。第1の電極102が、別のもの、例えば、配線や抵抗素子や容量素子などが有する膜と同時に形成されてもよい。

[0075]

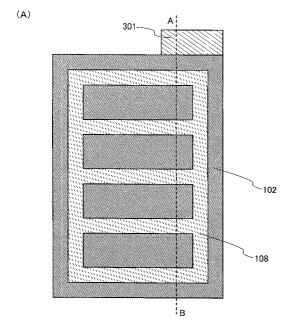

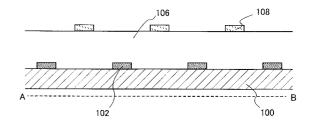

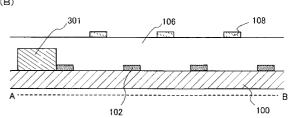

次に、トランジスタ301を有していて、かつ、トランジスタ301の一部と、第1の電極102とが地続きになっていて、一つの島(アイランド)を形成している場合について、図3に示す。図3(A)には、平面図、図3(B)には、断面図を示す。なお、本明細書中において、地続きとは、一体に形成されていることを言うものとする。

[0076]

このとき、トランジスタ301が有する膜と、第1の電極102とは、1つの膜として繋がっているため、同時に形成することが出来る。その結果、第1の電極を、マスク数(レチクル数)や製造工程数を増やすことなく製造することが出来る。

[0077]

一例としては、トランジスタ301が有する半導体層と、第1の電極102とが繋がっ

ていて、同時に形成することが出来る。したがって、トランジスタ301が有する半導体層と第1の電極102とを同時に成膜し、同時にエッチングすることによって、同時にパターニングすることが出来る。また、半導体層がポリシリコンの場合は、同時に結晶化されることとなる。この場合、トランジスタ301が有する半導体層と第1の電極102を構成する半導体層の結晶の粒界は概略同一の方向に向かって延伸している。ここで、結晶の粒界が概略同一の方向に向かって延伸している、とは、例えば、結晶化において形成される長手方向及び該長手方向と直交する方向(短手方向ともいう)を有する粒界の、該長手方向の向きがそろっていることを言う。

[0078]

そのため、トランジスタ301が有する半導体層と、第1の電極102とは、同じ材料を含むこととなる。

[0079]

なお、トランジスタ301が有する半導体層と、第1の電極102とは、地続きになっていて、繋がっているため、トランジスタ301が有する半導体層がどこまでであり、第1の電極102がどこまでであるかは、明確には区別出来ない場合がある。

【0080】

なお、トランジスタ301が有する半導体層の一部に、リンやボロンやガリウムやヒ素などの不純物(p型不純物やn型不純物)を導入する場合、同時に、第1の電極102にも、導入することが望ましい。同時に導入することにより、地続きになっているため、電気的に接続された状態とすることが出来る。

[0081]

その場合、トランジスタ301が有する半導体層と、第1の電極102とを接続するために、接続孔を設けて、別の配線を用いて接続する必要がない。そのため、効率的にレイアウトすることができ、開口率を向上させることが出来る。

[0082]

なお、トランジスタ301と、第1の電極102とは、地続きになっているため、電気的に接続された状態にある場合が多く、そのため、電気的に接続された電極が、画素電極となる場合が多い。

[0083]

なお、同時に不純物を導入する場合は、導入される部分の上の膜の厚さや材質に影響を受けるが、同様な層構造の下に形成されている場合は、少なくとも、トランジスタ301 が有する半導体層の一部のある領域では、第1の電極102のある領域と、概ね等しい濃度の不純物(p型不純物やn型不純物)を有することとなる。

[0084]

なお、トランジスタ301が有する半導体層には、チャネル形成領域を含む場合がおおい。チャネル形成領域は、ゲート絶縁膜を介して、ゲート電極が配置されている。このチャネル形成領域には、通常、濃度の高い不純物(p型不純物やn型不純物)は、導入されない。ただし、濃度が非常に低い不純物(p型不純物やn型不純物)は、しきい値電圧値を調整するために、導入される場合がある。また、濃度が低い不純物(p型不純物やn型不純物)は、LDD(Lightly doped drain)領域を形成するために、導入される場合がある。以上のことから、トランジスタ301が有する半導体層は、様々な濃度の不純物(p型不純物やn型不純物)を有する領域が複数存在する場合が多い。

[0085]

ただし、トランジスタ301が有する半導体層の一部と、第1の電極102とで、導電型が異なっていてもよい。その場合は、トランジスタ301とは別のトランジスタと同時に、不純物(p型不純物やn型不純物)が導入されることとなる。したがってその場合は、少なくとも、トランジスタ301とは別のトランジスタが有する半導体層の一部のある領域では、第1の電極102のある領域と、概ね等しい濃度の不純物(p型不純物やn型不純物)を有することとなる。一例としては、トランジスタ301とは別のトランジスタは、ソース信号線駆動回路やゲート信号線駆動回路などの一部として配置されている。

10

20

30

40

20

30

40

50

#### [0086]

なお、トランジスタ301と、第1の電極102とは、電気的に接続される場合が多い。そして、電気的に接続された電極、つまり、第1の電極102が、画素電極となる場合が多い。その結果、効率的に電極とトランジスタを配置することができるため、好適である。

## [0087]

なお、図3では、第1の電極102が、トランジスタ301が有する膜と同時に形成される場合について述べたが、これに限定されない。第1の電極102が、別のもの、例えば、配線や抵抗素子や容量素子などが有する膜と同時に形成されてもよい。

## [ 0 0 8 8 ]

なお、図1、図2、図3において、第2の電極108のみ、開口パターンを有する場合について記載したが、これに限定されない。第1の電極102でも同様に、開口パターンを有しても良い。これにより、基板に概略平行な電界を発生させ、液晶分子を制御することが出来る。この場合の図を、図4、図5、図6に示す。図4は、図1について、第1の電極102も開口パターンを有している場合に相当する。図6は、図3について、第1の電極102も開口パターンを有している場合に相当する。図6は、図3について、第1の電極102も開口パターンを有している場合に相当する。

#### [0089]

図4、図5、図6のように、第1の電極102に開口パターンがあると、その開口パターンの部分は、光の透過量が増える。なぜなら、第1の電極102が第2の電極108に重なっていないからである。第1の電極102が重なっていると、透過率が100%でない限り、光の透過量が減ってしまう。それに対して、第1の電極102が重なっていない部分は、光が減衰しないため、光の透過量が増える。その結果、輝度を向上させることや、消費電力を低減させることが出来る。

### [0090]

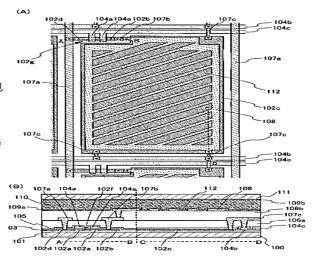

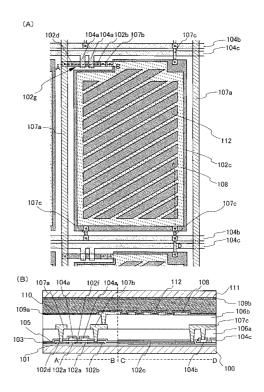

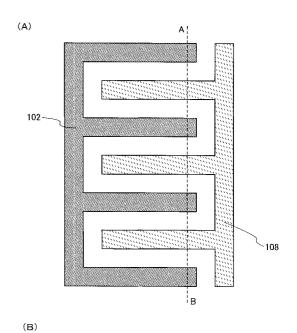

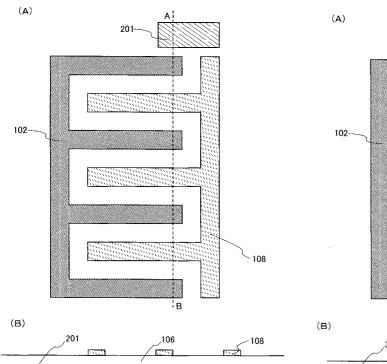

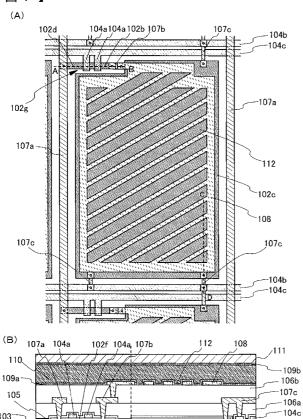

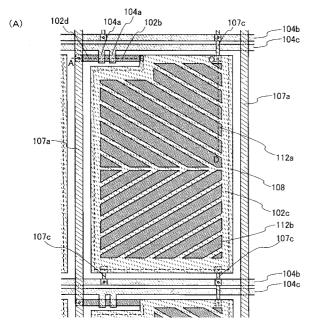

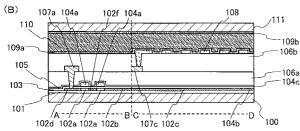

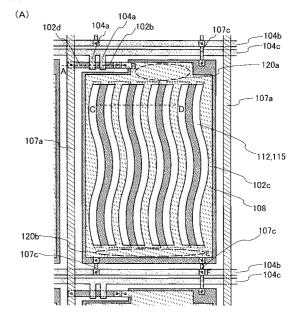

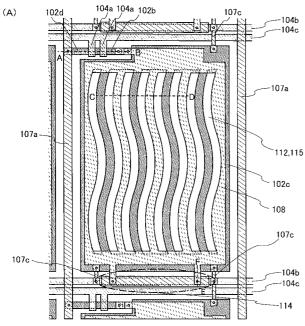

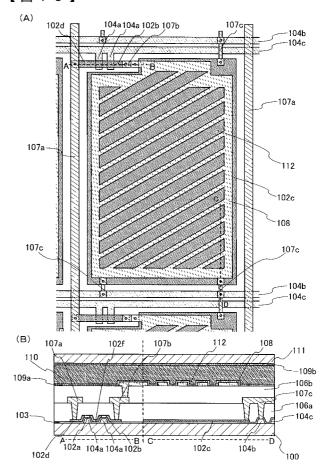

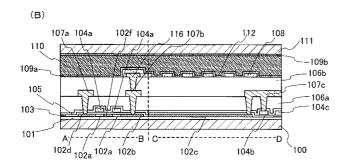

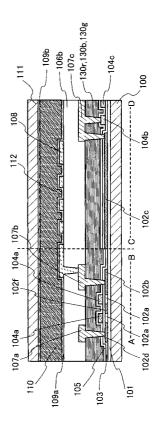

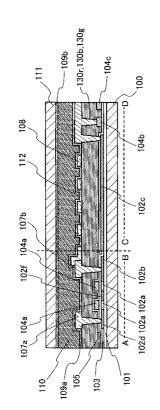

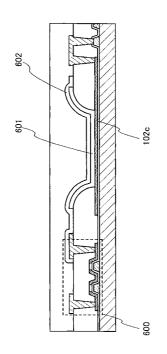

図7(A)は、本発明の第1の実施形態に係る液晶表示装置の構成を説明する為の平面図である。なお、ここでは、液晶表示装置に設けられた複数の画素のうち、1画素分の画素を示している。この液晶表示装置は、FFS方式で液晶の配向方向を制御する装置である。本図において、複数のソース配線107aが互いに平行(図中上下方向に延伸)かつ離間した状態で配置されている。複数のゲート配線104cは、ソース配線107aに略直交する方向(図中左右方向)に延伸し、かつ互いに離間するように配置されている。補助配線104bは、複数のゲート配線104cそれぞれに隣り合う位置に配置されており、ゲート配線104cに略平行な方向、つまり、ソース配線107aに略直交する方向(図中左右方向)に延伸している。ソース配線107aと、補助配線104b及びゲート配線104cとによって、略長方形の空間が囲まれているが、この空間に液晶表示装置の画素電極が配置されている。画素電極を駆動する薄膜トランジスタは、図中左上の角に配置されている。

#### [0091]

なお、ゲート配線104c、補助配線104b、及びソース配線107aなどは、アルミニウム(A1)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、ネオジム(Nd)、クロム(Cr)、ニッケル(Ni)、白金(Pt)、金(Au)、銀(Ag)、銅(Cu)、マグネシウム(Mg)、スカンジウム(Sc)、コバルト(Co)、ニッケル(Ni)、亜鉛(Zn)、ニオブ(Nb)、シリコン(Si)、リン(P)、ボロン(B)、ヒ素(As)、ガリウム(Ga)、インジウム(In)、錫(Sn)、酸素(O)で構成された群から選ばれた一つ又は複数の元素、もしくは、前記群から選ばれた一つ又は複数の元素を成分とする化合物や合金材料(例えば、インジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、アルミネオジム(A1・Nd)、マグネシウム銀(Mg・Ag)など)、もしくは、これらの化合物を組み合わせた物質などを用いて形成される。もしくは、それらとシリコンの化合物(シリサイド)(例えば、アルミ

20

30

40

50

シリコン、モリブデンシリコン、ニッケルシリサイドなど)や、それらと窒素の化合物( 例えば、窒化チタン、窒化タンタル、窒化モリブデン等)を有して形成される。なお、シ リコン(Si)には、n型不純物(リンなど)やp型不純物(ボロンなど)を多く含んで いてもよい。これらの不純物を含むことにより、導電率が向上して、通常の導体と同様な 振る舞いをするため、配線や電極として利用しやすくなる。なお、シリコンは、単結晶で もよいし、多結晶(ポリシリコン)でもよいし、非晶質(アモルファスシリコン)でもよ い。単結晶シリコンや多結晶シリコンを用いることにより、抵抗を小さくすることが出来 る。非晶質シリコンを用いることにより、簡単な製造工程で作ることが出来る。なお、ア ルミニウムや銀は、導電率が高いため、信号遅延を低減することができ、エッチングしや すいので、パターニングしやすく、微細加工を行うことが出来る。なお、銅は、導電率が 高いため、信号遅延を低減することが出来る。なお、モリブデンは、ITOやIZOなど の酸化物半導体や、シリコンと接触しても、材料が不良を起こすなどの問題が生じること なく製造でき、パターニングやエッチングがしやすく、耐熱性も高いため、望ましい。な お、チタンは、ITOやIZOなどの酸化物半導体や、シリコンと接触しても、材料が不 良を起こすなどの問題が生じることなく製造でき、耐熱性も高いため、望ましい。なお、 タングステンは、耐熱性が高いため、望ましい。なお、ネオジムは、耐熱性が高いため、 望ましい。特に、ネオジムとアルミニウムとの合金にすると、耐熱性が向上し、アルミニ ウムがヒロックをおこしにくくなるため、望ましい。なお、シリコンは、トランジスタが 有する半導体層と同時に形成でき、耐熱性も高いため、望ましい。なお、インジウム錫酸 化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化珪素を添加したインジウム錫酸 化物(ITSO)、酸化亜鉛(ZnO)、シリコン(Si)は、透光性を有しており、光 を透過させるような部分に用いることができるため、望ましい。たとえば、画素電極や共 通電極として用いることができる。

#### [0092]

なお、これらが単層で配線や電極を形成していてもよいし、多層構造になっていてもよ い。単層構造で形成することにより、製造工程を簡略化することができ、工程数を少なく でき、コストを低減することが出来る。また、多層構造にすることにより、それぞれの材 料のメリットを生かし、デメリットを低減させ、性能の良い配線や電極を形成することが 出来る。たとえば、抵抗の低い材料(アルミニウムなど)を多層構造の中に含むようにす ることにより、配線の低抵抗化を図ることができる。また、耐熱性が高い材料を含むよう にすれば、例えば、耐熱性が弱いが、別のメリットを有する材料を、耐熱性が高い材料で 挟むような積層構造にすることにより、配線や電極全体として、耐熱性を高くすることが 出来る。例えば、アルミニウムを含む層を、モリブデンやチタンを含む層で挟んだような 形にした積層構造にすると望ましい。また、別の材料の配線や電極などと直接接するよう な部分がある場合、お互いに悪影響を及ぼすことがある。例えば、一方の材料が他方の材 料の中に入っていって、性質を変えてしまい、本来の目的を果たせなくなったり、製造す るときに、問題が生じて、正常に製造できなくなったりすることがある。そのような場合 、ある層を別の層で挟んだり、覆ったりすることにより、問題を解決することが出来る。 例えば、インジウム錫酸化物(ITO)と、アルミニウムを接触させたい場合は、間に、 チタンやモリブデンを挟むことが望ましい。また、シリコンとアルミニウムを接触させた い場合は、間に、チタンやモリブデンを挟むことが望ましい。

#### [0093]

なお、ゲート配線104c、補助配線104bの方が、ソース配線107aよりも耐熱性が高い材料を用いることが望ましい。なぜなら、ゲート配線104c、補助配線104bの方が、製造工程の過程で、高い温度状態に配置されることが多いからである。

# [0094]

なお、ソース配線107aの方が、ゲート配線104cよりも、抵抗の低い材料を用いることが望ましい。なぜなら、ゲート配線104cには、H信号とL信号の2値の信号を与えるだけであるが、ソース配線107aには、アナログの信号を与え、それが表示に寄与するからである。よって、ソース配線107aには、正確な大きさの信号を供給できる

20

30

40

50

ようにするため、抵抗の低い材料を用いることが望ましい。

#### [0095]

なお、補助配線104bを設けなくてもよいが、補助配線104bを設けることにより、各画素における共通電極の電位を安定化させることができる。なお、図7では、補助配線104bは、ゲート配線104cと概略平行には配置されているが、これに限定されない。ソース配線107aと概略平行に配置されていてもよい。その時は、ソース配線107aと同じ材質で形成されることが望ましい。

### [0096]

ただし、補助配線104bは、ゲート配線104cと概略平行に配置したほうが、開口率を大きくすることができ、効率的にレイアウトできるため、好適である。

## [0097]

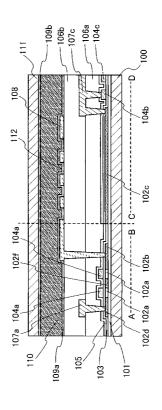

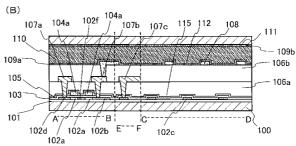

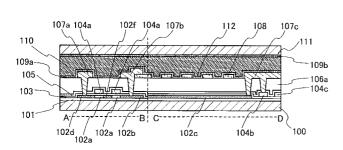

図 7 ( B )は、図 7 ( A )の A - B 断面図及び C - D 断面図である。図 7 ( B )に示すように、基板 1 0 0 上には、基板 1 0 0 から不純物が拡散することを防止するために、下地絶縁膜 1 0 1 が形成されている。下地絶縁膜 1 0 1 は、例えば、酸化シリコン(SiO $_{\rm X}$ )、窒化シリコン(SiN $_{\rm X}$ )、酸化窒化シリコン(SiО $_{\rm X}$  N  $_{\rm y}$  :  $_{\rm X}$  > y )、窒化砂 化シリコン(SiN $_{\rm X}$  の  $_{\rm y}$  :  $_{\rm X}$  > y )など、酸素又は窒素を有する絶縁物質から構成される。また、これらの膜を複数積層した積層膜であってもよい。

#### [0098]

なお、基板100は、ガラス基板、石英基板、アルミナなど絶縁物で形成される基板、 後工程の処理温度に耐え得る耐熱性を有するプラスチック基板、シリコン基板、または金 属基板である。また、ポリシリコンであってもよい。

#### [0099]

なお、透過型の表示装置として動作させる場合は、基板100は、光透過性を有することが望ましい。

### [0100]

下地絶縁膜101上には、半導体膜102 f 及び液晶の配向方向を制御する第1の電極102 c は、例えばポリコの電極102 c は、例えばこことであり、同時に成膜された同で選択的にエット地膜102 f と第1の電極102 c は、ア地膜101上で選択的にエット地膜101上でので選択的にエット地膜101上であって、同層に形成される。ただし、同時に成膜することや、同てエ程でエッジクの気に、本発明を限定するものではない。半導体膜102 f には、アースははアースははアースはは、102 f には、アースははアースはは、102 b は、102 b は、102 b は、102 c は、10

### [0101]

第1の電極102cは、他の画素においても共通の電圧が供給される共通電極として機能し、例えば不純物が導入されたポリシリコン膜によって形成されている。第1の電極102cは、不純物が導入されることにより抵抗が下がり、電極として機能する。図7(A)の点線で示すように、第1の電極102cは、長方形の一角(図中左上の角)に角を欠いた部分102gを有する形状であり、画素の略全面に形成されている。なお、長方形の角を欠いた部分102eには薄膜トランジスタが配置されている。この角を欠いた部分102eには薄膜トランジスタが配置されている。この角を欠いた部分102eに薄膜トランジスタを配置することにより、画素内における表示に有効な領域を、より効率的に形成することができる。つまり、開口率の向上につながる。第1の電極102cは、膜厚が例えば45nm以上60nm以下であり、光の透過率を更に上げる場合には、第1の電極102cの膜厚を40nm以下にするこ

20

30

40

50

とが望ましい。

#### [0102]

第1の電極102cは、例えばポリシリコンで形成されているが、他の半導体材料、例えばアモルファスシリコン、単結晶シリコン、有機半導体、又はカーボンナノチューブで形成されていてもよい。この場合、薄膜トランジスタには、半導体膜102fの代わりにアモルファスシリコン膜又は有機半導体膜などが用いられる。なお、トランジスタを形成する半導体膜102fと第1の電極102cとは同一の膜を同時に選択的にエッチングすることにより形成されることが望ましい。この場合、マスク(レチクル)数や工程数を削減できるため、製造コストを低減することができる。また、不純物領域102b,不純物領域102dを互いに近接して配置しても、問題なく不純物元素が同時に導入されることが望ましい。なぜならに近接して配置しても、問題なく不純物元素を導入することができるため、より密なレイアウトを構成することができるからである。p型又はn型どちらか一方のみの不純物元素を導入することにより、異なる種類の不純物元素を導入する場合と比較して低コストで製造できるため望ましい。

#### [0103]

半導体膜102 f 上を含む全面上には、トランジスタのゲート絶縁膜103が形成されている。

## [0104]

ただし、ゲート絶縁膜103は、チャネル形成領域近傍にのみ配置され、それ以外の部分では、配置されていない場合もある。また、場所によって厚さや積層構造や厚さが異なる場合がある。例えば、チャネル近傍のみ厚かったり、層の数が多かったりして、それ以外の場所では、膜厚が薄かったり、層の数が少なかったりする場合もある。このようにすることにより、ソース領域やドレイン領域への不純物の添加が制御しやすくなる。また、チャネル近傍のゲート絶縁膜103の厚さや層の数を変えることにより、半導体層への不純物の添加量が場所によって変わるようにして、LDD領域等を形成することが出来る。LDD領域を形成することにより、漏れ電流の低減や、ホットキャリアの発生を抑えて信頼性を向上させることが出来る。

## [0105]

ゲート絶縁膜103は、例えば、酸化シリコン(SiO $_{\times}$ )、窒化シリコン(SiN $_{\times}$ )、酸化窒化シリコン(SiО $_{\times}$ N $_{y}$ : $_{\times}$ >  $_{y}$ )、窒化酸化シリコン(SiN $_{\times}$ O $_{y}$  :  $_{\times}$  >  $_{y}$ )など、酸素又は窒素を有する絶縁物質から構成される。また、これらの膜を複数積層した積層膜であってもよい。ゲート絶縁膜103上には、2本のゲート電極104aが形成されている。図7(B)及び図7(A)に示すように、ゲート電極104aは補助配線104b及びゲート配線104cと同一配線層であり、ゲート配線104cに電気的に接続している。半導体膜102 f において、ゲート電極104aの下方に位置する領域102aは、チャネル形成領域として機能する。なお、2つのチャネル形成領域102aの相互間に位置する半導体領域にも、不純物領域102b,102 d と同一の不純物が導入されている。なお、本実施形態においては、2本のゲート電極104aを有するマルチゲート構造としたが、本発明をこの構成に限定するものではない。

## [0106]

ゲート絶縁膜103上及びゲート電極104a上には、絶縁膜105及び第1層間絶縁膜106aがこの順に形成されている。

# [0107]

なお、絶縁膜 1 0 5 及び第 1 層間絶縁膜 1 0 6 a のいずれか 1 つのみが形成されていてもよいし、各々の絶縁膜が、多層構造になっていてもよい。また、これらの絶縁膜には、無機材料又は有機材料を用いることができる。有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト、シロキサン、又はポリシラザンなどを用いることができる。無機材料としては、酸化シリコン(SiO $_{\times}$ )、窒化シリコン(SiN $_{\times}$ 0、。

x > y )など、酸素又は窒素を有する絶縁物質を用いることができる。また、これらの膜を複数積層した積層膜であってもよい。また、有機材料と無機材料を組み合わせて積層膜にしてもよい。

#### [0108]

ゲート絶縁膜103、絶縁膜105及び第1層間絶縁膜106aには、不純物領域10 2 b上に位置する接続孔、不純物領域102d上に位置する接続孔、第1の電極102c 上に位置する接続孔、及び補助配線104b上に位置する接続孔が形成されている。第1 層間絶縁膜106a上には、ソース配線107a、ドレイン配線107b、及び接続用配線107cが形成されている。

なお、絶縁膜として無機材料を用いることにより、水分や不純物の侵入を止めることが 出来る。特に、窒素を含む層を用いると、水分や不純物をプロックする機能が高い。

#### [0109]

なお、絶縁膜として有機材料を用いることにより、平面を平坦にすることが出来る。そのため、その上の層に対して、よい効果をもたらすことが出来る。例えば、有機材料の上に形成する層も平坦にすることが出来るため、液晶の配向の乱れを防ぐことが出来る。

#### [0110]

ソース配線107aは、ソースすなわち不純物領域102dの上方に位置しており、一部が接続孔に埋め込まれることにより、不純物領域102dに電気的に接続している。したがって、ソース電極は、ソース配線107aの一部となって存在していることとなる。ドレイン配線107bは、ドレインすなわち不純物領域102bの上方に位置しており、一部が接続孔に埋め込まれることにより、不純物領域102bに接続している。

#### [0111]

接続用配線107cは、第1の電極102cの上方から補助配線104bの上方まで延伸しており、一部が接続孔に埋め込まれることにより、第1の電極102c及び補助配線104bそれぞれに電気的に接続している。このように、接続用配線107cを配置することにより、接続孔を深くあける必要がないので、正確に形成することが出来る。

#### [0112]

また、図7(B)に示す例では、ソース配線107a及び接続用配線107cと同時にドレイン配線107bが形成される。この場合、ドレイン配線107bの一部が埋め込まれている接続孔とは位置が互いに異なっている。このようにすることにより、ドレイン配線107b及び第2の電極108のうち、接続孔上に位置する部分が窪んでも、この窪みが重なることはない。このため、第2の電極108に深く窪む部分が形成されずに、上に形成されるレジストパターンの形成不良が発生することを抑制できる。

# [0113]

ただし、図8に示すように、第2の電極108と、不純物領域102bとを、ドレイン配線107bを介さずに、直接接続してもよい。この場合、第2の電極108と、不純物領域102bとを接続するための接続孔は、深く開ける必要が出てくるが、図7(B)におけるドレイン配線107bが必要ないため、その領域を開口領域として画像表示に利用できる。そのため、開口率が向上し、低消費電力化をはかることが出来る。

## [0114]

このように、第1の電極102cは、接続用配線107cを介して補助配線104bに接続している。なお、接続用配線107cは、抵抗を下げるために複数設けられるのが好ましい。このようにすると、第1の電極102cの電位が安定化する。図7(A)に示す例では、接続用配線107cは、第1の電極102cが有する4つの角のうち、薄膜トランジスタの近くの角を除く3つの角の上方それぞれに形成されている。このように、複数の経路で接続させることにより、第1の電極102c内に電位分布が生じることが抑制される。また、接続用配線107cを介して第1の電極102cと補助配線104bを接続することにより、接続孔を開ける回数を減らすことが出来るので、プロセス工程を簡略化することが出来る。

10

20

30

20

30

40

50

#### [0115]

なお、接続用配線107cは、ソース配線107aと同時に、同じ材料を用いて形成したが、これに限定されない。第2の電極108と同時に、同じ材料を用いて形成してもよい。

## [0116]

ソース配線107a、ドレイン配線107b、接続用配線107c、及び第1層間絶縁膜106a上には、第2層間絶縁膜106bが形成されている。なお、第2層間絶縁膜106bを形成しない構成としても良い。第2層間絶縁膜106bには、無機材料又は有機材料を用いることができる。有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト、又はシロキサン、ポリシラザンなどを用いることができる。無機材料としては、酸化シリコン(SiOx)、窒化シリコン(SiNx)、酸化窒化シリコン(SiOxNy:xゝy)、窒化酸化シリコン(SiNxOy:xゝy)など、酸素又は窒素を有する絶縁物質を用いることができる。また、これらの膜を複数積層した積層膜であってもよい。また、有機材料と無機材料を組み合わせて積層膜にしてもよい。第2層間絶縁膜106bには、ドレイン配線107b上に位置する接続孔が形成されている

### [0117]

第2層間絶縁膜106b上には、液晶の配向方向を制御する第2の電極108が形成されている。第2の電極108は、画素ごとに個別の電圧が供給される画素電極として機能し、ITO(インジウム錫酸化物)、ZnO(酸化亜鉛)、又は酸化インジウムに2~20wt%のZnOを混合したターゲットを用いて形成されたIZOなどによって形成されている。なお、第2の電極108と不純物領域102bは、ドレイン配線107bを介して電気的に接続してもよいが、相互に直接接続してもよい。

#### [ 0 1 1 8 ]

なお、図 8 に示すように、接続用配線がない場合は、第 2 の電極 1 0 8 は、薄膜トランジスタの不純物領域 1 0 2 b に直接接続している。

### [0119]

図8及び図7(A)に示すように、第2の電極108は略長方形であり、第1の電極102cの上方及びその周囲に位置しているが、第1の電極102cの上方に位置している部分に、複数の開口パターン112を有している。開口パターン112の例としては、スリット状で互いに平行であるものを多く含み、図7(A)に示す例ではソース配線107aに対して斜めである。開口パターン112が形成されることにより、基板に平行な成分を有する電界が、第2の電極108の上方において生じる。このため、第2の電極108の電位を制御することにより、後述する液晶の配向方向を制御することができる。なお、開口パターンの形状は本実施形態の形状に限定されない。第2の実施形態以降で記載する開口パターンの形状も適用することができる。すなわち開口パターンには、例えば櫛歯形状の電極における櫛歯部分の相互間のスペース等、導電体パターンが形成されていないスペースも含まれるものとする。

## [0120]

また、開口パターンの向きが異なるものを配置することによって、液晶分子の動く方向が異なる領域を複数設けることが出来る。つまり、マルチドメイン(配向分割ともいう)構造にすることが出来る。マルチドメイン構造にすることにより、ある特定の方向から見たとき、画像の表示が正しくなくなってしまうことを防ぐことができ、その結果、視野角を向上させることが出来る。

# [0121]

また、図7(A)に示すように、基板100に対して垂直な方向から見た場合に、共通電極として機能する第1の電極102cの周縁部が、画素電極として機能する第2の電極108よりも外側に配置するように形成されている。このようにすることにより、信号を受け取った後フローティング状態になった第2の電極108が、ソース配線107aを介して他の画素へ伝達される信号の影響を受けることが抑制される。その結果、クロストー

クなどの画質不良を低減することが出来る。なお、本発明はこのような電極構造に限定されるものではなく、第1の電極102cが第2の電極108の内側に配置される部分を有していても良い。

### [0122]

第2層間絶縁膜106b上及び第2の電極108上には、第1配向膜109a及び液晶110が積層されている。

#### [ 0 1 2 3 ]

液晶110としては、強誘電性液晶(FLC)、ネマティック液晶、スメクティック液晶、ホモジニアス配向になるような液晶、又はホメオトロピック配向になるような液晶などを用いることができる。液晶110上には、第2配向膜109bを有する対向基板111が配置されている。なお、対向基板111には、カラーフィルタが配置されていることが多い。また、基板100及び対向基板111それぞれには、外側に、偏光板が設けられている。なお、偏光板のほかに、位相差板や / 4板などが配置されている場合も多い。【0124】

なお、本発明に係る積層の構成は、本実施形態における積層の構成に限定されない。

#### [ 0 1 2 5 ]

次に、本半導体装置、本液晶表示装置の製造方法の一例について説明する。まず、基板100上に下地絶縁膜101を形成する。次いで、下地絶縁膜101上にポリシリコン膜又はアモルファスシリコン膜等の半導体膜を形成し、この半導体膜上にレジストパターン(図示せず)を形成する。次いで、このレジストパターンをマスクとして半導体膜を選択的にエッチングする。このようにして、半導体膜102f及び第1の電極102cが同一工程で形成される。その後、レジストパターンを除去する。

### [0126]

次いで、半導体膜102 f 上、第1の電極102 c 上、及び下地絶縁膜101上に、ゲート絶縁膜103を形成する。ゲート絶縁膜103は例えば酸化窒化シリコン膜又は酸化シリコン膜であり、プラズマCVD法により形成される。なお、ゲート絶縁膜103を窒化シリコン膜、若しくは窒化シリコン及び酸化シリコンを有する多層膜により形成してもよい。次いで、ゲート絶縁膜103上に導電膜を形成し、この導電膜を、レジストパターンをマスクとしたエッチングを行うことにより、選択的に除去して、パターニングする。これにより、半導体膜102 f 上に位置するゲート絶縁膜103上には、2つのゲート電極104aが形成される。また、ゲート電極104aと同時に補助配線104b及びゲート配線104cが形成される。

#### [0127]

なお、上記したように補助配線104bを設けることにより、各画素において第1の電極102cや第2の電極108の電位を安定化させることができる。また、補助配線104bを形成しなくてもよい。また、補助配線104bを他の層(例えばソース配線107aと同一の層、又は第1の電極102cと同一の層、又は第2の電極108と同一の層)に設けてもよく、複数の層に分けて形成してもよい。また、本図において補助配線104bは、ソース配線107aと同一方向に延伸する構成であってもよい。

## [ 0 1 2 8 ]

なお、導電膜は、アルミニウム(Al)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、ネオジム(Nd)、クロム(Cr)、ニッケル(Ni)、白金(Pt)、金(Au)、銀(Ag)、銅(Cu)、マグネシウム(Mg)、スカンジウム(Sc)、コバルト(Co)、ニッケル(Ni)、亜鉛(Zn)、ニオブ(Nb)、シリコン(Si)、リン(P)、ボロン(B)、ヒ素(As)、ガリウム(Ga)、インジウム(In)、錫(Sn)、酸素(O)で構成された群から選ばれた一つ又は複数の元素、もしくは、前記群から選ばれた一つ又は複数の元素を成分とする化合物や合金材料(例えば、インジウム錫酸化物(ITSO)、でルミネオジム

10

20

30

40

(A1-Nd)、マグネシウム銀(Mg-Ag)など)、もしくは、これらの化合物を組み合わせた物質などを用いて形成される。もしくは、それらとシリコンの化合物(シリサイド)(例えば、アルミシリコン、モリブデンシリコン、ニッケルシリサイドなど)や、それらと窒素の化合物(例えば、窒化チタン、窒化タンタル、窒化モリブデン等)を用いて形成される。なお、シリコン(Si)には、n型不純物(リンなど)やp型不純物(ボロンなど)を多く含んでいてもよい。

#### [0129]

なお、これらが単層で配線や電極を形成していてもよいし、多層構造になっていてもよ い。単層構造で形成することにより、製造工程を簡略化することができ、工程数を少なく でき、コストを低減することが出来る。また、多層構造にすることにより、それぞれの材 料のメリットを生かし、デメリットを低減させ、性能の良い配線や電極を形成することが 出来る。たとえば、抵抗の低い材料(アルミニウムなど)を多層構造の中に含むようにす ることにより、配線の低抵抗化を図ることができる。また、耐熱性が高い材料を含むよう にすれば、例えば、耐熱性が弱いが、別のメリットを有する材料を、耐熱性が高い材料で 挟むような積層構造にすることにより、配線や電極全体として、耐熱性を高くすることが 出来る。例えば、アルミニウムを含む層を、モリブデンやチタンを含む層で挟んだような 形にした積層構造にすると望ましい。また、別の材料の配線や電極などと直接接するよう な部分がある場合、お互いに悪影響を及ぼすことがある。例えば、一方の材料が他方の材 料の中に入っていって、性質を変えてしまい、本来の目的を果たせなくなったり、製造す るときに、問題が生じて、正常に製造できなくなったりすることがある。そのような場合 、ある層を別の層で挟んだり、覆ったりすることにより、問題を解決することが出来る。 例えば、インジウム錫酸化物(ITO)と、アルミニウムを接触させたい場合は、間に、 チタンやモリブデンを挟むことが望ましい。また、シリコンとアルミニウムを接触させた い場合は、間に、チタンやモリブデンを挟むことが望ましい。

### [0130]

次いで、ゲート電極104a及びレジストパターン(図示せず)などをマスクとして、 半導体膜102 fに不純物を注入する。これにより、半導体膜102 fには、不純物領域 102b,102d、及びゲート電極104a相互間に位置する不純物領域が形成される 。なお、n型、p型の不純物元素を個別に注入してもよいし、特定の領域にはn型の不純 物元素及びp型の不純物元素を共に注入してもよい。ただし後者の場合には、n型の不純 物元素又はp型の不純物元素のどちらか一方の注入量が多くなるようにする。

# [0131]

なお、このとき、ゲート絶縁膜103の厚さや積層構造を変えることにより、LDD領域を形成してもよい。LDD領域を形成したい部分は、ゲート絶縁膜103を厚くすることや、層の数を増やせばよい。その結果、不純物の注入量が減るため、LDD領域を容易に形成することが出来る。

## [0132]

なお、本工程において、レジストパターンをマスクとして用いてもよい。

## [0133]

また、不純物領域を形成する工程において、第1の電極102cに不純物元素を注入してもよい。このようにすると、第1の電極102cを不純物領域102b,102dと同時に形成することができるため、工程が増加せずに済み、液晶表示装置の製造コストを低コストにすることができる。

## [0134]

なお、不純物領域に対する不純物元素の注入は、ゲート電極104aを形成する前、例えばゲート絶縁膜103を形成する前又は形成した後に行ってもよい。その場合は、レジストパターンをマスクとして用い注入する。このとき、第1の電極102cに不純物元素を注入しても良い。この場合においても、トランジスタの不純物領域の形成工程と、第1の電極102cに不純物元素を注入する工程を同一の工程にすることができるため、液晶表示装置の製造コストを低コストにすることができる。

10

20

30

40

#### [0135]

また、これにより、ゲートと同じ層の電極と、不純物が注入された半導体膜との間で、容量を形成することが出来る。ゲートと同じ層の電極と、不純物が注入された半導体膜との間には、ゲート絶縁膜が配置されているので、膜厚がうすく、大きな容量を形成することが出来る。

## [0136]

次いで、第1層間絶縁膜106a及び各接続孔を形成する。次いで、第1層間絶縁膜106a上及び各接続孔中に導電膜(例えば金属膜)を形成し、この金属膜をパターニング、すなわち選択的に除去する。これにより、ソース配線107a、ドレイン配線107b、及び接続用配線107cが形成される。なお、導電膜は、既に述べたように、様々な材料を用いて、様々な構造で形成することができ、一例としては、アルミニウム(A1)、ニッケル(Ni)、タングステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ネオジム(Nd)、白金(Pt)、金(Au)、銀(Ag)などから形成された膜、これらの合金で形成された膜、又は、これらの積層膜を用いることができる。また、n型不純物が導入されたシリコン(Si)を用いてもよい。

#### [ 0 1 3 7 ]

次いで、第2層間絶縁膜106b及び各接続孔を形成する。次いで、第2層間絶縁膜106b上及び各接続孔中にITO膜、IZO膜、又はZnO膜を形成し、この膜をレジストパターンを用い選択的に除去する。これにより、第2の電極108が形成される。

### [0138]

なお、ドレイン配線107bの一部が埋め込まれている接続孔と、第2の電極108の一部が埋め込まれている接続孔とは位置が互いに異なっている。このようにすることにより、ドレイン配線107b及び第2の電極108のうち、接続孔上に位置する部分が窪んでも、この窪みが重なることはない。このため、第2の電極108に深く窪む部分が形成されず、上記したレジストパターンの形状不良が発生することを抑制できる。その後、レジストパターンを除去する。

#### [0139]

ただし、これに限定されない。例えば、ドレイン配線107bの一部が埋め込まれている接続孔と、第2の電極108の一部が埋め込まれている接続孔とは、位置が重なってオーバーラップしていてもよい。その場合、1つの場所に収めることが出来るため、効率的にレイアウトすることが出来る。そのため、開口率を向上させることが出来る。

# [0140]

次いで、第1配向膜109aを形成し、第2配向膜109bが形成された対向基板111との間に液晶を封止する。その後、液晶110と接しない側の対向基板111や基板100(すなわち、液晶表示装置の外側)に、偏光板、位相差板、 / 4板、拡散板、又はプリズムシート等の光学フィルム等を設ける。さらに、バックライトやフロントライトを設ける。バックライトとしては、直下型やサイドライト型を用いることが出来る。光源としては、冷陰極管やLED(発光ダイオード)を用いることができる。LEDとしては、白色LEDや、色ごとのLED(例えば、白、赤、青、緑、シアン、マゼンダ、イエローなど)を組み合わせて用いればよい。LEDを用いると、光の波長のピークが鋭いため、色純度を上げることが出来る。このようにして、液晶表示装置が形成される。

#### [0141]

なお、液晶表示装置とは、基板と対向基板と、それに挟まれた液晶のみの部分を呼ぶものとしても良く、また、それに、偏光板や位相差板などの光学フィルムを配置したものまで含めても良いし、さらに、拡散板やプリズムシートや光源(冷陰極管やLEDなど)や導光板などを含んでいても良い。

#### [0142]

以上、本発明の第1の実施形態によれば、FFS方式で液晶の配向方向を制御する液晶表示装置において、第1の電極102cは不純物が導入されたポリシリコン膜によって形成されており、薄膜トランジスタのソース領域、ドレイン領域及びチャネル形成領域が形

10

20

30

40

成されている半導体膜102fと同一工程で形成される。従って、共通電極をITOで形成する場合と比較して、製造工程数を少なくして製造コストを低くすることができる。

### [0143]

なお、本実施形態では、接続用配線107cを、ソース配線107a及びドレイン配線107bと同一層に配置したが、他の配線層(例えばゲート配線104c、第1の電極102c、又は第2の電極108と同一層)に配置してもよい。また、ゲート絶縁膜103は全面に形成されていなくてもよい。

### [0144]

また、補助配線104bは、ソース配線107aと同一層でもよい。この場合、補助配線104bをゲート配線104cと平行に配置し、かつソース配線107aと交差する部分のみゲート配線104cと同一層にしてもよい。また、補助配線104bをソース配線107aと平行に配置してもよい。

## [0145]

また、ゲート電極104aとゲート配線104cは別の層に形成されていてもよいし、 別の材料で形成されていてもよい。

#### [0146]

また、本実施形態では、チャネル形成領域の上方にゲート電極を配置した、いわゆるトップゲート型の薄膜トランジスタについて説明をしたが、本発明は特にこれに限定されるものではない。チャネル形成領域の下方にゲート電極が配置された、いわゆるボトムゲート型の薄膜トランジスタにしてもよいし、チャネル形成領域の上下にゲート電極が配置された構造を有するトランジスタを形成してもよい。

#### [0147]

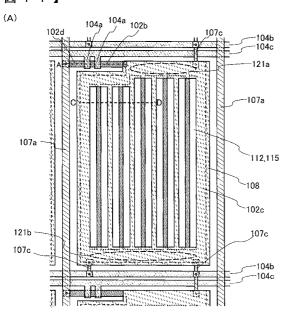

### (第2の実施形態)

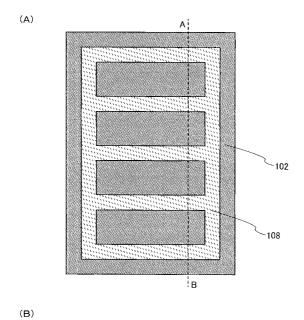

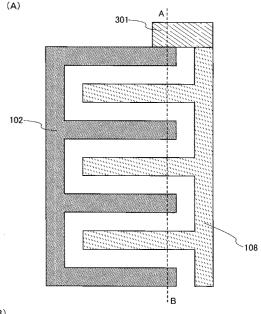

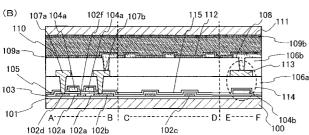

図9(A)は、本発明の第2の実施形態に係るFFS方式の液晶表示装置の構成を説明する為の平面図であり、図9(B)は、図9(A)のA-B断面図及びC-D断面図である。本実施形態は、第1の電極102cがトランジスタを介してソース配線107aに電気的に接続されていて画素電極として機能している点、第2の電極108が補助配線104bに電気的に接続されていて共通電極として機能している点、第2の電極108に形成された開口パターン112の形状が異なる点、並びに、第1の電極102c及び第2の電極108と各配線の接続構造が異なる点を除いて、第1の実施形態と同様の構成である。また、本実施形態に係る液晶表示装置の製造方法は、第1の実施形態と略同様である。従って、第1の実施形態で述べた内容は、本実施形態においても適用することが可能である。以下、第1の実施形態と同様の構成については同一の符号を付し、説明を省略する。

## [0148]

トランジスタのドレインもしくはソースとなる不純物領域102bは、第1の電極102cに直接接続している。つまり、トランジスタを構成している半導体層と、第1の電極102cとは、地続きとなっていて、一つのアイランド(島)を形成している。また、第1層間絶縁膜106aには、第1の実施形態と異なり、不純物領域102b上に位置する接続孔、及び第1の電極102c上に位置する接続孔が形成されていない。従って、その領域を表示領域として利用することができるため、開口率を向上させることができる。

## [0149]

なお、トランジスタのドレインもしくはソースとなる不純物領域102bと、第1の電極102cとは、地続きになっていて、繋がっているため、トランジスタが有する不純物領域102bがどこまでであり、第1の電極102cがどこまでであるかは、明確には区別出来ない場合がある。

# [0150]

なお、トランジスタのドレインもしくはソースとなる不純物領域に、リンやボロンやガリウムやヒ素などの不純物(p型不純物やn型不純物)を導入する場合、同時に同じ導電型の不純物を、第1の電極102cにも、導入することが望ましい。同時に導入することにより、地続きになっているため、電気的に接続された状態とすることが出来る。このと

10

20

30

40

き、導入される部分の上の膜の厚さや材質に影響を受けるが、同様な層構造の下に形成されている部分は、少なくとも、トランジスタのドレインもしくはソースとなる不純物領域のある領域では、第1の電極102cのある領域と、概ね等しい濃度の不純物(p型不純物やn型不純物)を有することとなる。

### [0151]

第2層間絶縁膜106bには、接続用配線107c上に位置する接続孔が形成されている。第2の電極108は、一部がこの接続孔に埋め込まれることにより、接続用配線107cに接続している。

### [0152]

また、図9(A)に示すように、本実施形態では、第2の電極108には、2種類の開口パターン112a,112bが形成されている。図中上側の領域に形成された開口パターン112bとは、向きが互いに異なる。

## [0153]

開口パターン112a,112bのように、開口パターンの向きが異なるものを配置することによって、液晶分子の動く方向が異なる領域を複数設けることが出来る。つまり、マルチドメイン構造にすることにより、ある特定の方向から見たとき、画像の表示が正しくなくなってしまうことを防ぐことができ、その結果、視野角を向上させることが出来る。

## [0154]

また、図9に示すように、第1の電極102cが画素電極として機能し、第2の電極108が共通電極として機能し、画素電極よりも、共通電極の方が液晶と近接して配置されている。その結果、画素ごとに画素電極の電圧が変化しても、液晶が存在する部分の電界は、画像によって変化しにくいので、隣接する別の画素に影響を与えにくく、クロストークを低減することが出来る。

### [0155]

本実施形態でも、第1の実施形態と同様の効果を得ることができる。また、第2の電極108に、互いに向きが異なる開口パターン112a,112bを形成している。このため、第1の電極102cと第2の電極108の間で生じる電界勾配のうち液晶110に位置する部分の方向を、基板に平行な面内で2つに分けることができる。従って、液晶表示装置の視野角をさらに広げることができる。

## [0156]

なお、第1の実施形態において、第2の電極108の形状を本実施形態のようにしてもよい。また、第2の電極108が有する開口パターンの形状を第1の実施形態のようにしてもよい。また、本図では画素を一つのみ図示したが、実際には複数の画素がマトリックス状に配置されている。この場合、接続用配線107cを介して、各画素の第2の電極108を相互に接続してもよい。このようにすることにより、抵抗を低くし、第2の電極108に電圧が十分に加わるようにすることができる。

### [0157]

なお、本実施形態は、第1の実施形態で述べた内容を、一部変更、改良、又は変形した場合の一例を示している。したがって、第1の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

### [0158]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、複数の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

### [0159]

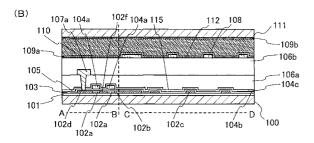

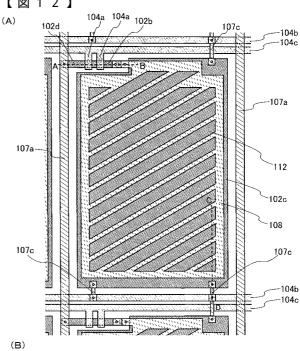

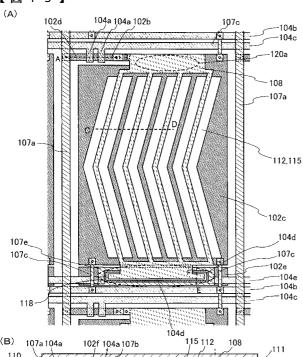

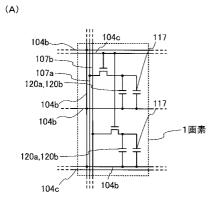

## (第3の実施形態)

図10(A)は、本発明の第3の実施形態に係る液晶表示装置の構成を説明する為の平面図である。図10(B)は、図10(A)のA-B断面図、C-D断面図、及びE-F

10

20

30

40

断面図である。本実施形態は、第1の電極102cに開口パターン115が形成されている点、及び開口パターン112の形状を除いて、第1の実施形態と同様の構成である。すなわち本実施形態に係る液晶表示装置は、IPS方式で液晶の配向方向を制御する装置であり、液晶表示装置の基板100に対して垂直な方向から見た場合に、画素電極及び共通電極が主要部分で互い違いかつ略平行となっている。上記したFFS方式では、画素電極及び共通電極のうち下方に位置する電極は開口パターンを有していない。なお、本実施形態に係る液晶表示装置の製造方法は、第1の実施形態と略同様である。従って、第1の実施形態で述べた内容は、本実施形態においても適用することが可能である。以下、第1の実施形態と同様の構成については同一の符号を付し、説明を省略する。

#### [0.160]

開口パターン115は、第2の電極108のうち開口パターン112が形成されていない領域の下方及びその周囲に位置している。このようにすることにより、共通電極である第1の電極102cと、画素電極である第2の電極108が周辺部分を除いて互い違いかつ略平行となる。このような電極構造を有することにより、第1の電極102cと第2の電極108の間で基板に平行方向の電界を発生させることができ、IPS方式の特徴である視野角向上という効果を得ることができる。開口パターン112,115は、本実施形態では波線形状をしている。

#### [0161]

このように、開口パターンの向きが異なるように配置することによって、液晶分子の動く方向が異なる領域を複数設けることが出来る。つまり、マルチドメイン構造にすることが出来る。マルチドメイン構造にすることにより、ある特定の方向から見たとき、画像の表示が正しくなくなってしまうことを防ぐことができ、その結果、視野角を向上させることが出来る。

### [0162]

また、本実施形態では、第1の電極102cと第2の電極108とが、一部(図中符号120a,120bで示す部分)で、ゲート絶縁膜103、絶縁膜105、第1層間絶縁膜106a、及び第2層間絶縁膜106bを挟んでいる。このため、符号120a,120bで示す部分において、第1の電極102c、第2の電極108、及びこれらの間に位置する絶縁膜は、容量素子として機能する。容量素子120a,120bを設けることにより、保持容量を大きくすることができる。従って、薄膜トランジスタがオフになったとき、第2の電極108の電位は保持されやすくなる。

# [0163]

本実施形態でも、第1の実施形態と同様の効果を得ることができる。なお、本実施形態において、第2の電極108が有する開口パターン112の形状を、図7又は図9に示した開口パターン112の形状にしてもよい。この場合、第1の電極102cが有する開口パターン115の形状も、図7又は図9に示した開口パターン112と同様の形状になる。ただし、液晶表示装置の基板100に対して垂直な方向から見た場合に、開口パターン112、115は、第1の電極102c及び第2の電極108が周辺部分を除いて互い違いかつ略平行になるように配置される必要がある。

#### [0164]

また、第1又は第2の実施形態において、開口パターン112の形状を本実施形態のようにしてもよい。この場合、開口パターン112の形状が図10に示した形状である、 F F S 方式の液晶表示装置を得ることができる。

# [0165]

なお、本実施形態では、第1の電極102cに開口パターン115がある。そのため、その開口パターンの部分は、光の透過量が増える。なぜなら、第1の電極102が無いからである。第1の電極102があると、透過率が100%とならないため、光の透過量が減ってしまう。それに対して、第1の電極102が無い部分は、光が減衰しないため、光の透過量が増える。その結果、輝度を向上させ、消費電力を低減させることが出来る。

### [0166]

10

20

30

20

30

40

50

なお、本実施形態は、第1~第2の実施形態で述べた内容を、一部変更、改良、又は変形した場合の一例を示している。したがって、第1~第2の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

### [0167]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

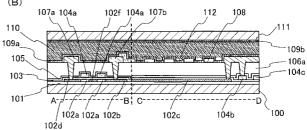

### [0168]

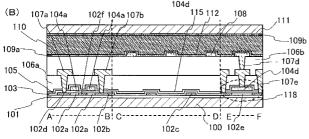

### (第4の実施形態)

図11(A)は、本発明の第4の実施形態に係るIPS方式の液晶表示装置の構成を説明する為の平面図である。図11(B)は、図11(A)のA-B断面図及びC-D断面図である。本実施形態は、第1の電極102cに開口パターン115が形成されている点、及び開口パターン112の形状を除いて、第2の実施形態と同様の構成である。また、本実施形態に係る液晶表示装置の製造方法は、第2の実施形態と略同様である。従って、第1の実施形態で述べた内容は、本実施形態においても適用することが可能である。以下、第2の実施形態と同様の構成については同一の符号を付し、説明を省略する。

### [0169]

このように、トランジスタのドレインもしくはソースとなる不純物領域102bは、第1の電極102cに直接接続している。つまり、トランジスタを構成している半導体層と、第1の電極102cとは、地続きとなっていて、一つのアイランド(島)を形成している。また、第1層間絶縁膜106aには、第1の実施形態と異なり、不純物領域102b上に位置する接続孔、及び第1の電極102c上に位置する接続孔が形成されていない。従って、その領域を表示領域として利用することができるため、開口率を向上させることができる。

### [0170]

開口パターン115は、第2の電極108のうち開口パターン112が形成されていない領域の下方及びその周囲に位置している。このようにすることにより、画素電極である第1の電極102cと、共通電極である第2の電極108が周辺部分を除いて互い違いかつ略平行となる。このような電極構造を有することにより、第1の電極102cと第2の電極108の間で横方向の電界を発生させることができ、IPS方式の特徴である視野角向上という効果を得ることができる。開口パターン112,115は、本実施形態ではソース配線107aと略平行である。

#### [0171]

また、本実施形態では、第1の電極102cと第2の電極108とが、一部(図中符号121a,121bで示す部分)で、ゲート絶縁膜103、絶縁膜105、第1層間絶縁膜106a、及び第2層間絶縁膜106bを挟んでいる。このため、符号121a,121bで示す部分において、第1の電極102c、第2の電極108、及びこれらの間に位置する絶縁膜は、容量素子として機能する。容量素子121a,121bを設けることにより、保持容量を大きくすることができる。従って、薄膜トランジスタがオフになったとき、第1の電極102cの電位は保持されやすくなる。

## [0172]

本実施形態でも、第1の実施形態と同様の効果を得ることができる。なお、本実施形態において、開口パターン112,115の形状を図10に示した形状にしてもよい。また、開口パターン112の形状を、図7又は図9に示した形状にしてもよい。この場合、開口パターン115の形状も、図7又は図9に示した開口パターン112と同様の形状になる。ただし、液晶表示装置の基板100に対して垂直な方向から見た場合に、開口パターン112,115は、第1の電極102c及び第2の電極108が周辺部分を除いて互い違いかつ略平行になるように配置される必要がある。

### [0173]

また、第3の実施形態に示したIPS方式の液晶表示装置において、開口パターン11

2 , 1 1 5 の形状を図 1 1 に示した形状にしてもよい。また、第 1 又は第 2 の実施形態において、開口パターン 1 1 2 の形状を本実施形態のようにしてもよい。後者の場合、開口パターン 1 1 2 の形状が図 1 1 に示した形状である、 F F S 方式の液晶表示装置を得ることができる。

### [0174]

なお、本実施形態では、第1の電極102cに開口パターン115がある。そのため、その開口パターンの部分は、光の透過量が増える。なぜなら、第1の電極102が無いからである。第1の電極102があると、透過率が100%とならないため、光の透過量が減ってしまう。それに対して、第1の電極102が無い部分は、光が減衰しないため、光の透過量が増える。その結果、輝度を向上させることや、消費電力を低減させることが出来る。

[ 0 1 7 5 ]

なお、本実施形態は、第1~第3の実施形態で述べた内容を、一部変更、改良、又は変形した場合の一例を示している。したがって、第1~第3の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

[0176]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

[0177]

(第5の実施形態)

図12(A)は、本発明の第5の実施形態に係るFFS方式の液晶表示装置の構成を説明する為の平面図である。図12(B)は、図12(A)のA-B断面図及びC-D断面図である。本実施形態は、第2層間絶縁膜106bが形成されておらず、第1層間絶縁膜106a上に第2の電極108が形成されている点を除いて、第1の実施形態と同様である。第2の電極108は、一部がドレイン配線107b上に位置しており、この部分を介してドレイン配線107bに直接接続している。

[0178]

第2の電極108は、ソース配線107a、ドレイン配線107b、及び接続用配線107cが形成された後に形成される。ドレイン配線107bを形成した後で第2の電極108を形成すると、第2の電極108の表面にドレイン配線107bをエッチングした際の残渣が残らないため、第2の電極108の表面を平坦にすることができる。なお、第2の電極108がドレイン配線107bを覆う構成であってもよい。

[0179]

なお、第2の電極108は、ソース配線107aやドレイン配線107bと同時に形成してもよい。つまり、同様な材料を用いて、同時にパターニングして形成してもよい。その結果、透明な電極を形成する工程を省くことが出来、コストを低減することが出来る。

[0180]

よって、第2の電極108は、光透過性を有していなくてもよい。つまり、光を反射する性質も持っていてもよい。

[0181]

また、本実施形態に係る液晶表示装置の製造方法は、第2層間絶縁膜106bの形成工程が省略される点を除いて、第1の実施形態と略同様である。従って、第1の実施形態で述べた内容は、本実施形態においても適用することが可能である。なお、第2層間絶縁膜106bの形成工程が省略されることにより、液晶表示装置の製造コストが低くなる。以下、第1の実施形態と同様の構成については同一の符号を付し、説明を省略する。

[0182]

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、層間 絶縁膜が第1の実施形態より1層少ないため、第1の電極102c及び第2の電極108 相互間の電界勾配が大きくなる。従って、低電圧でも同等の電位勾配を得ることができる 10

20

30

40

ため、液晶表示装置を低消費電力化することができる。この効果は、第1層間絶縁膜106aを誘電率の高い材料(例えば窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタル等)で形成すると、大きくなる。なお、第1層間絶縁膜106aを誘電率の高い材料で形成した場合、電極間の保持容量が大きくなるという効果も得ることができる。また、第2層間絶縁膜106bの形成工程が省略されているため、第1の実施形態と比較して製造コストが低くなる。

#### [0183]

なお、本実施形態において、第2の実施形態と同様の構造によって第1の電極102cとドレインとなる不純物領域102bを接続し、第1の電極102cを画素電極として機能させてもよい。この場合、第2の実施形態と比較して、第2層間絶縁膜106bを形成しなくてもよいという効果がある。また第2の電極108は、図12におけるドレイン配線107bと第2の電極108の接続構造のように、一部が接続用配線107c上に位置することにより、接続用配線107cに直接接続する。これにより、第2の電極108は共通電極として機能する。

#### [0184]

また、本実施形態において、第2の電極108の形状を、開口パターン112の形状を含めて、図9、図10、又は図11に示した形状にしてもよい。図10又は図11に示した形状にすると、図10において符号120a,120bで示した容量素子、又は図11において符号121a,121bで示した容量素子が形成されるため、保持容量を大きくすることができる。従って、薄膜トランジスタがオフになったとき、第2の電極108の電位は保持されやすくなる。

#### [0185]

なお、本実施形態は、第1~第4の実施形態で述べた内容を、一部変更、改良、又は変形した場合の一例を示している。したがって、第1~第4の実施形態で述べた内容は、本 実施形態にも適用することや、組み合わせることが出来る。

#### [0186]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

### [0187]

#### (第6の実施形態)

図13(A)は、本発明の第6の実施形態に係るIPS方式の液晶表示装置の構成を説明する為の平面図である。図13(B)は、図13(A)のA-B断面図、C-D断面図、及びE-F断面図である。本実施形態に係る液晶表示装置は、第2の電極108に接続している容量素子114を有している点を除いて、第3の実施形態と同様の構成である。なお、容量素子は補助配線104bと第2の電極108に接続される構成であればよく、本実施形態に示す構成に限定されない。また、本実施形態に係る液晶表示装置の製造方法は、第3の実施形態と略同様である。従って、第3の実施形態で述べた内容は、本実施形態においても適用することが可能である。以下、第3の実施形態と同一の構成については同一の符号を付し、説明を省略する。

# [ 0 1 8 8 ]

第1層間絶縁膜106a上には、補助配線104bの上方に位置する容量素子用電極113が形成されている。容量素子用電極113は、ソース配線107aと同一層に位置しており、ソース配線107aと同一工程で形成される。容量素子114は、補助配線104bと容量素子用電極113の間に、絶縁膜105及び第1層間絶縁膜106aが位置することにより形成されている。補助配線104bの上方に容量素子を形成しているため、開口部の面積が小さくならない。従って、容量素子を設けた場合にも開口率が下がらない

### [0189]

第2層間絶縁膜106bには、容量素子用電極113上に位置する接続孔が形成されて

10

20

30

40

いる。第2の電極108は、一部がこの接続孔に埋め込まれることにより、容量素子用電極113に接続している。

### [0190]

本実施形態によっても、第3の実施形態と同様の効果を得ることができる。また、画素電極として機能する第2の電極108及び補助配線104bの間に容量素子114を接続したため、薄膜トランジスタがオフになったときに、第2の電極108の電圧が保持されやすい。

## [0191]

なお、本実施形態において、開口パターン112,115の形状を図11に示した形状にしても良い。さらに、開口パターン112の形状を図7又は図9に示した形状にしてもよい。この場合、第1の電極102cが有する開口パターン115の形状も、図7又は図9に示した開口パターン112の形状になる。ただし、液晶表示装置の基板100に対して垂直な方向から見た場合に、開口パターン112,115は、第1の電極102c及び第2の電極108が周辺部分を除いて互い違いかつ略平行になるように配置される必要がある。

#### [0192]

また、図7に示した第1の実施形態において、容量素子114を形成して第2の電極108に接続しても、本実施形態と同様の効果を得ることができる。また、容量素子用電極113を、ゲート配線104cの上方に配置しても、同様の効果を得ることができる。なぜなら、ゲート配線104cの電位は、画素が非選択の状態では略一定値になっているためである。容量素子は、画素電極の電位を保持できればよいので、画素電極と、ある一定の電位を有する配線の間に形成すればよい。より望ましくは、容量素子を接続するゲート配線104cは一行前のゲート配線である。なぜなら、選択状態が既に終了しているため、電位が略一定に保たれているためである。

## [ 0 1 9 3 ]

このように、開口パターンの向きや形状が異なるように配置することによって、液晶分子の動く方向が異なる領域を複数設けることが出来る。つまり、マルチドメイン構造にすることが出来る。マルチドメイン構造にすることにより、ある特定の方向から見たとき、画像の表示が正しくなくなってしまうことを防ぐことができ、その結果、視野角を向上させることが出来る。

### [0194]

なお、本実施形態では、第1の電極102cに開口パターン115がある。そのため、その開口パターンの部分は、光の透過量が増える。なぜなら、第1の電極102が無いからである。第1の電極102があると、透過率が100%とならないため、光の透過量が減ってしまう。それに対して、第1の電極102が無い部分は、光が減衰しないため、光の透過量が増える。その結果、輝度を向上させることや、消費電力を低減させることが出来る。

### [0195]

なお、本実施形態は、第1~第5の実施形態で述べた内容を、一部変更、改良、又は変形した場合の一例を示している。したがって、第1~第5の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

#### [0196]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

# [0197]

### (第7の実施形態)

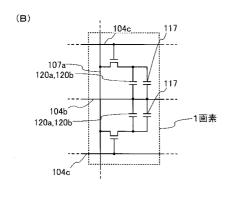

図14(A)は、本発明の第7の実施形態に係るIPS方式の液晶表示装置の構成を説明する為の平面図である。図14(B)は、図14(A)のA B断面図、C-D断面図、及びE-F断面図である。本実施形態は、開口パターン115及び開口パターン112

10

20

30

50

の形状が略く字形状である点、及び、第1の電極102cと補助配線104bに電気的に接続している容量素子117を有する点を除いて、第4の実施形態に係るIPS方式の液晶表示装置と同様の構成である。従って、第4の実施形態で述べた内容は、本実施形態においても適用することが可能である。以下、第4の実施形態と同様の構成については同一の符号を付し、説明を省略する。

## [0198]

容量素子117は、第1の電極102cの一部(図14(A)の中では下端部)を補助配線104bの下方に位置させることにより形成される。すなわち、容量素子117は、第1の電極102c、補助配線104b、及びこれらの間に位置するゲート絶縁膜103によって構成される。

[0199]

本実施形態に係る液晶表示装置の製造方法は、第1の電極102cへの不純物注入が、補助配線104bとなる導電膜が形成される前に行われ、ゲート電極104a及び補助配線104b等が形成された後に半導体膜102fへの不純物注入が行われる点を除いて、第3の実施形態に係る液晶表示装置の製造方法と同様である。このため、第1の電極102cは、容量素子117を形成する部分の全体が低抵抗になり、補助配線104bに対する第1の電極102cの電位を変化させるだけで、容量素子117が動作する。

[0200]

本実施形態によっても、第4の実施形態と同様の効果を得ることができる。また、画素電極として機能する第1の電極102c及び補助配線104bの間に容量素子117を接続したため、薄膜トランジスタがオフになったときに、第1の電極102cの電圧が保持されやすい。

[0201]

なお、第2の実施形態において容量素子117を設けてもよい。この場合、本実施形態と同様の効果を得ることができる。

[0202]

また、本実施形態において開口パターン112,115の形状を、図10又は図11に示す形状にしてもよい。さらに、開口パターン112の形状を図7又は図9に示した形状にしてもよい。この場合、開口パターン115の形状も、図7又は図9に示した開口パターン112の形状になる。ただし、液晶表示装置の基板100に対して垂直な方向から見た場合に、開口パターン112,115は、第1の電極102c及び第2の電極108が周辺部分を除いて互い違いかつ略平行になるように配置される必要がある。

[0203]

また、第3、第4、又は第6の実施形態に係るIPS方式の液晶表示装置において、開口パターン112,115の形状を図14に示す形状にしてもよい。また、第1、第2、又は第5の実施形態に係るFFS方式の液晶表示装置において、開口パターン112の形状を図14に示す形状にしてもよい。

[0204]

このように、トランジスタのドレインもしくはソースとなる不純物領域102bは、第1の電極102cに直接接続している。つまり、トランジスタを構成している半導体層と、第1の電極102cとは、地続きとなっていて、一つのアイランド(島)を形成している。また、第1層間絶縁膜106aには、第1の実施形態と異なり、不純物領域102b上に位置する接続孔、及び第1の電極102c上に位置する接続孔が形成されていない。従って、その領域を表示領域として利用することができるため、開口率を向上させることができる。

[0205]

このように、開口パターンの向きが異なるように配置することによって、液晶分子の動く方向が異なる領域を複数設けることが出来る。つまり、マルチドメイン構造にすることが出来る。マルチドメイン構造にすることにより、ある特定の方向から見たとき、画像の表示が正しくなくなってしまうことを防ぐことができ、その結果、視野角を向上させるこ

10

20

30

40

20

30

40

50

とが出来る。

## [0206]

なお、本実施形態では、第1の電極102cに開口パターン115がある。そのため、その開口パターンの部分は、光の透過量が増える。なぜなら、第1の電極102が無いからである。第1の電極102があると、透過率が100%とならないため、光の透過量が減ってしまう。それに対して、第1の電極102が無い部分は、光が減衰しないため、光の透過量が増える。その結果、輝度を向上させることや、消費電力を低減させることが出来る。

### [0207]

なお、本実施形態は、第1~第6の実施形態で述べた内容を、一部変更、改良、又は変形した場合の一例を示している。したがって、第1~第6の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

#### [0208]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

### [0209]

### (第8の実施形態)

図15(A)は、本発明の第8の実施形態に係るIPS方式の液晶表示装置の構成を説明する為の平面図である。図15(B)は、図15(A)のA B断面図、C-D断面図、及びE-F断面図である。本実施形態は、容量素子120bの代わりに容量素子118を有している点、第2の補助配線104eが形成されている点、及び開口パターン112,115の形状が略く字形状である点を除いて、第3の実施形態に係るIPS方式の液晶表示装置と同様の構成である。従って、第3の実施形態で述べた内容は、本実施形態においても適用することが可能である。以下、第3の実施形態と同様の構成については同一の符号を付し、説明を省略する。

#### [ 0 2 1 0 ]

容量素子118は、第2の電極108と第2の補助配線104eの間に接続されており、下地絶縁膜101上に位置する半導体膜102e、半導体膜102e上に位置するゲート絶縁膜103、及びゲート絶縁膜103上に形成されていて半導体膜102eの一部の上方に位置する導電体パターン104dによって構成されており、第1の電極102cとは重ならない位置に配置されている。半導体膜102e及び導電体パターン104dはそれぞれ長方形であり、補助配線104bに隣接する位置に、補助配線104bに対して略平行に配置されている。半導体膜102eは、導電体パターン104dの下方に位置する領域を除いて、第1の電極102cと同一の不純物が導入されている。

#### [0211]

第1層間絶縁膜106aには、導電体パターン104dの上方に位置する接続孔、及び半導体膜102eのうち不純物が導入された領域の上方に位置している接続孔が形成されている。第1層間絶縁膜106a上には導電体パターン107d,107eが形成されている。導電体パターン107dは接続孔を介して導電体パターン104dに電気的に接続しており、導電体パターン107eは接続孔を介して、半導体膜102eのうち不純物が導入された領域に電気的に接続している。導電体パターン107dは細長い長方形であり、補助配線104bに対して略平行に配置されている。導電体パターン107eは略口字形状であり、導電体パターン107dを囲んでいる。

#### [ 0 2 1 2 ]

第2層間絶縁膜106bには、導電体パターン107dの上方に位置する接続孔が形成されている。第2の電極108は、この接続孔を介して導電体パターン107d及び導電体パターン104dに電気的に接続している。

#### [ 0 2 1 3 ]

また、ゲート絶縁膜103上には第2の補助配線104eが形成されている。第2の補

20

30

40

50

助配線104 e は補助配線104 b に隣接する位置に配置されており、補助配線104 b と平行に延伸している。第1層間絶縁膜106 a には、第2の補助配線104 e 上に位置する接続孔が複数形成されており、この接続孔を介して導電体パターン107 e が第2の補助配線104 e に電気的に接続している。

### [ 0 2 1 4 ]

第2の補助配線104eは、導電体パターン104dと同一層に位置しているが、途中で分断されている。分断されている領域には導電体パターン104dが配置されている。ただし、第2の補助配線104eのうち分断されている部分は、導電体パターン107eを介して互いに電気的に接続されている。第2の補助配線104eの電位は、半導体膜102eにn型不純物が導入されている場合、ソース配線107aの最低電位より低くなっており、半導体膜102eにp型不純物が導入されている場合、ソース配線107aの最高電位より高くなっている。

#### [0215]

このような構造を有する液晶表示装置において、駆動用の薄膜トランジスタがオンになると、導電体パターン 1 0 4 e のうち導電体パターン 1 0 4 d の下方に位置する部分には電荷が蓄積される。このようにして容量素子 1 1 8 は機能する。

### [0216]

なお、半導体膜102eは半導体膜102fと同一工程で形成される。また導電体パターン104d及び第2の補助配線104eは、補助配線104bと同一工程で形成される。また半導体膜102fに不純物を注入して不純物領域102b,102dを形成する工程において、半導体膜102eのうち導電体パターン104dに覆われていない領域に不純物が注入される。また導電体パターン107d,107eは、ソース配線107aと同一工程で形成される。また、第1層間絶縁膜106aに形成される接続孔は全て同一工程で形成され、第2層間絶縁膜106bに形成される接続孔は全て同一工程で形成される。液晶表装置の製造工程の他の部分は、第3の実施形態に係る液晶表示装置の製造工程と同様である。

#### [0217]

本実施形態によっても、第3の実施形態と同様の効果を得ることができる。また、画素電極として機能する第2の電極108と第2の補助配線104eの間に容量素子118を接続したため、薄膜トランジスタがオフになったときに、第2の電極108の電圧が保持されやすい。また、半導体膜102fに不純物を注入して不純物領域102b,102dが形成される工程において、半導体膜102eのうち導電体パターン104dに覆われている領域に不純物が注入され、覆われている領域には不純物を注入する必要がないため、製造工程数を増加させなくてよい。

## [0218]

なお第1の実施形態において容量素子118を設けてもよい。この場合においても、本 実施形態と同様の効果を得ることができる。

#### [0219]

また、本実施形態において開口パターン112,115の形状を、図10又は図11に示す形状にしてもよい。さらに、開口パターン112の形状を図7又は図9に示した形状にしてもよい。この場合、開口パターン115の形状も、図7又は図9に示した開口パターン112の形状になる。ただし、液晶表示装置の基板100に対して垂直な方向から見た場合に、開口パターン112,115は、第1の電極102c及び第2の電極108が周辺部分を除いて互い違いかつ略平行になるように配置される必要がある。

#### [0220]

このように、トランジスタのドレインもしくはソースとなる不純物領域102bは、第1の電極102cに直接接続している。つまり、トランジスタを構成している半導体層と、第1の電極102cとは、地続きとなっていて、一つのアイランド(島)を形成している。また、第1層間絶縁膜106aには、第1の実施形態と異なり、不純物領域102b上に位置する接続孔、及び第1の電極102c上に位置する接続孔が形成されていない。

従って、その領域を表示領域として利用することができるため、開口率を向上させることができる。

## [0221]

このように、開口パターンの向きが異なるように配置することによって、液晶分子の動く方向が異なる領域を複数設けることが出来る。つまり、マルチドメイン構造にすることが出来る。マルチドメイン構造にすることにより、ある特定の方向から見たとき、画像の表示が正しくなくなってしまうことを防ぐことができ、その結果、視野角を向上させることが出来る。

### [0222]

なお、本実施形態では、第1の電極102cに開口パターン115がある。そのため、その開口パターンの部分は、光の透過量が増える。なぜなら、第1の電極102が無いからである。第1の電極102があると、透過率が100%とならないため、光の透過量が減ってしまう。それに対して、第1の電極102が無い部分は、光が減衰しないため、光の透過量が増える。その結果、輝度を向上させることや、消費電力を低減させることが出来る。

#### [0223]

なお、本実施形態は、第1~第7の実施形態で述べた内容を、一部変更、改良、又は変形した場合の一例を示している。したがって、第1~第7の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

## [0224]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

### [ 0 2 2 5 ]

### (第9の実施形態)

図16(A)は、第9の実施形態に係る液晶表示装置の回路図である。本実施形態に係る液晶表示装置は、複数の画素がマトリックス状に配置されている。各画素の構成は、図中縦方向に延伸する第2の補助配線104fが形成されている点を除いて、第7の実施形態に係る液晶表示装置の構成と同様である。第2の補助配線104fは補助配線104bと同一層に形成されており、補助配線104bと交差する部分それぞれで補助配線104bと電気的に接続している。

## [0226]

本実施形態によっても第7の実施形態と同様の効果を得ることができる。また、第2の補助配線104 f を設けたことにより、すべての画素において、共通電極の電位を同一の値に保ちやすくなる。なお、本実施形態に係る液晶表示装置は、FFS方式であってもよいしIPS方式であってもよい。また、画素電極及び共通電極が有する開口パターンの形状は、上記した第1~第8の実施形態で示した開口パターンと同様の形状にしてもよいが、これらに限定されない。

## [0227]

なお、本実施形態は、第1~第8の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第8の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

### [0228]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

## [0229]

#### (第10の実施形態)

図16(B)は、第10の実施形態に係る液晶表示装置の回路図である。本実施形態に

10

20

30

40

係る液晶表示装置は、複数の画素がマトリックス状に配置されている。各画素の構成は、 第8の実施形態に係る液晶表示装置と同様である。

# [0230]

本実施形態によっても第8の実施形態と同様の効果を得ることができる。なお、本実施形態に係る液晶表示装置は、FFS方式であってもよいしIPS方式であってもよい。また、画素電極及び共通電極が有する開口パターンの形状は、上記した第1~第8の実施形態で示した開口パターンと同様の形状にしてもよいが、これらに限定されない。

### [0231]

なお、本実施形態は、第1~第9の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第9の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

### [ 0 2 3 2 ]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

### [0233]

### (第11の実施形態)

図17(A)は、第11の実施形態に係る液晶表示装置の回路図である。本実施形態に係る液晶表示装置は、FFS方式又はIPS方式の液晶表示装置であり、一つの画素が複数(例えば二つ)のサブ画素で構成されている。各サブ画素の構造は、第1~第10の実施形態で示した画素のいずれかと同様の構造である。従って、第1~第10の実施形態で説明した内容は本実施形態においても適用可能である。本図では、第7の実施形態で示した画素と同様の構成である場合を例示している。以下、第7の実施形態と同様の構成については同一の符号を付し、説明を省略する。

### [0234]

同一の画素を構成する複数のサブ画素は、同一のゲート配線 1 0 4 c に電気的に接続しており、かつ互いに異なる補助配線 1 0 4 b に電気的に接続している。

### [0235]

本実施形態によっても、第1~第10の実施形態で示した液晶表示装置と同様の効果を得ることができる。また、一つの画素を複数のサブ画素で構成したため、視野角をさらに広げることができる。なお、画素に冗長性を持たせることができるという効果、及び面積階調表示が可能である、という効果も得ることができる。

## [0236]

なお、本実施形態は、第1~第10の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第10の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

## [0237]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

### [0238]

# (第12の実施形態)

図17(B)は、第12の実施形態に係る液晶表示装置の回路図である。本実施形態に係る液晶表示装置は、FFS方式又はIPS方式の液晶表示装置であり、同一の画素を構成する複数のサブ画素が互いに異なるゲート配線104cに電気的に接続している点、及び、同一の画素を構成する複数のサブ画素が同一の補助配線104bに電気的に接続している点を除いて、第11の実施形態と同様の構成である。各サブ画素の構造は、第1~第10の実施形態で示した画素のいずれかと同様の構造である。従って、第1~第10の実

10

20

30

40

施形態で説明した内容は本実施形態においても適用可能である。本図では、第7の実施形態で示した画素と同様の構成である場合を例示している。以下、第7の実施形態と同様の構成については同一の符号を付し、説明を省略する。

本実施形態によっても、第11の実施形態と同様の効果を得ることができる。

### [0239]

なお、本実施形態は、第1~第11の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第11の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

### [0240]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

## [ 0 2 4 1 ]

### (第13の実施形態)

図18(A)は、本発明の第13の実施形態に係る液晶表示装置の構成を説明する為の平面図である。図18(B)は、図18(A)のA B断面図及びC-D断面図である。本実施形態は、画素を駆動するトランジスタがボトムゲート型であり、下地絶縁膜101が形成されていない点を除いて、第1の実施形態と同様の構成である。すなわち本実施形態は、FFS方式の液晶表示装置である。従って、第1の実施形態で述べた内容は、本実施形態においても適用することが可能である。以下、第1の実施形態と同様の構成については同一の符号を付し、説明を省略する。

### [0242]

本実施形態において、ゲート電極104a、補助配線104b、及びゲート配線104 c は基板100上に形成されており、ゲート絶縁膜103は、基板100、ゲート電極1 0 4a、補助配線104b、及びゲート配線104cそれぞれ上に形成されている。また 、半導体膜102f及び第1の電極102cは、ゲート絶縁膜103上に形成されている

## [0243]

本実施形態に係る液晶表示装置の製造方法は、以下の通りである。まず、基板100上に導電膜を形成し、この導電膜を選択的に除去する。これにより、基板100上には、2つのゲート電極104a、補助配線104b、及びゲート配線104cが形成される。なお、導電膜としては、アルミニウム(A1)、ニッケル(Ni)、タングステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ネオジム(Nd)、白金(Pt)、金(Au)、銀(Ag)などから形成された膜、これらの合金で形成された膜、又は、これらの積層膜を用いることができる。また、n型不純物が導入されたシリコン(Si)を用いてもよい。次いで、ゲート絶縁膜103を形成する。

#### [0244]

次いで、ゲート絶縁膜103上にポリシリコン膜を形成し、このポリシリコン膜上にレジストパターンを形成する。次いで、このレジストパターンをマスクとしてポリシリコン膜をエッチングする。このようにして、半導体膜102 f 及び第1の電極102 c が、同一工程で形成される。その後、レジストパターンを除去する。

### [0245]

次いで、半導体膜102 f 上にマスクパターンを形成し、このマスクパターンをマスクとして半導体膜102 f に不純物を注入する。これにより、不純物領域102b,102 d、及びゲート電極104 a 相互間に位置する不純物領域が形成される。なお、本処理において、第1の電極102 c にも不純物が注入される。なお、基板100がガラス等の透過性を有する材料から形成されている場合、マスクパターンを形成する際に、露光用のマスクを用いずに、ゲート配線を露光用パターンとして基板100の裏面から露光することにより、マスクパターンを形成する場合もある。この場合は露光用のマスクを用いない分

10

20

30

40

だけ工程を省略できるため、製造コストを削減できる。また、自己整合的にマスクパターンを形成できるため、マスクパターンのずれが抑制され、このずれを考慮しなくても良い、という利点もある。

その後の工程は、第1の実施形態と同様である。

#### [0246]

本実施形態でも、第1の実施形態と同様の効果を得ることができる。なお、第2又は第5の実施形態に示したFFS方式の液晶表示装置において、画素を駆動するトランジスタを、本実施形態と同様の構造を有するボトムゲート型のトランジスタとしてもよい。また第3、第4、第6~12のいずれかの実施形態に示したIPS方式の液晶表示装置において、画素を駆動するトランジスタを、本実施形態と同様の構造を有するボトムゲート型のトランジスタとしてもよい。このように、上記したいずれのFFS方式の液晶表示装置及びIPS方式の液晶表示装置においても、ボトムゲート型のトランジスタを採用することができる。

# [0247]

また、本実施形態に係る液晶表示装置、又は第1~第12のいずれかの実施形態において、画素を駆動するトランジスタを本実施形態と同様の構造を有するボトムゲート型のトランジスタとした液晶表示装置において、ゲート絶縁膜103上にポリシリコン膜を形成する前に、基板100上に位置するゲート絶縁膜103を、ゲート電極104aの周囲に位置する部分を除いて除去してもよい。この場合、第1の電極102cは基板100上に直接形成される。

#### [0248]

なお、本実施形態は、第1~第12の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第12の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

#### [0249]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

# [0250]

#### (第14の実施形態)

図19(A)は、本発明の第14の実施形態に係る液晶表示装置の構成を説明する為の断面図である。この断面図は、図12のA-B断面及びC-D断面に相当する断面を示している。本実施形態は、第2の電極108の全てが第1層間絶縁膜106a上に位置置している点、及びドレイン配線107bの一部が第2の電極108上に位置している点を除びて、第5の実施形態に示したFFS方式の液晶表示装置と同様の構成である。本実の形成された後、ドレイン配線107bが形成される。では、第2の電極108が形成された後、ドレイン配線107bが形成される。つまり、な構成とすることにより、第2の電極108がドレイン配線107bの上部に形成ができる。第5の実施形態のように第2の電極108が段切れを起こしてしまう可能性があるに形と、第2の電極108よりドレイン配線107bの端部で第2の電極108をドレイン配線107bのように形成すれば、第2の電極108が段切れを起こすことを防止できる。なお、上記したようにドレイン配線107bは厚く形成される場合が多いため、ドレイン配線107bが段切れを起こす可能性は低い。

# [0251]

また、本実施形態に係る液晶表示装置の製造方法は、第5の実施形態と略同様である。このため、第1の実施形態で述べた内容は、本実施形態においても適用することが可能である。以下、第5の実施形態と同一の構成については同一の符号を付し、説明を省略する。なお、第2の電極108が有する開口パターン112の形状は、第1~第4、第7のい

10

20

30

40

ずれかで示した形状にすることができるが、他の形状であっても良い。

#### [0252]

本実施形態によっても、第5の実施形態と同様の効果を得ることができる。なお、第1の電極102cに、第2の電極108が有する開口パターン112に平行な開口パターンを形成することにより、IPS方式の液晶表示装置にすることもできる。開口パターンの形状は、上記した第1~第4、第7の実施形態のいずれかで示した形状にすることができる。ただし、液晶表示装置の基板100に対して垂直な方向から見た場合に、第1の電極102c及び第2の電極102cの開口パターン及び開口パターン112は、第1の電極102c及び第2の電極108が周辺部分を除いて互い違いかつ略平行になるように配置される必要がある。

#### [ 0 2 5 3 ]

なお、本実施形態は、第1~第13の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第13の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

#### [0254]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

#### [ 0 2 5 5 ]

# (第15の実施形態)

図19(B)は、本発明の第15の実施形態に係る液晶表示装置の構成を説明する為の断面図である。この断面図は、図7のA-B断面及びC-D断面に相当する断面を示している。本実施形態は、第2層間絶縁膜106b上に第2のドレイン配線116が形成されている点、及び第2の電極108が第2のドレイン配線116を覆うように形成されている点を除いて、第1の実施形態に示したFFS方式の液晶表示装置と同様の構成である。なお、第2の電極108の一部が第2のドレイン配線116上に重なる構成としても良い。また、本実施形態に係る液晶表示装置の製造方法は、第1の実施形態と略同様である。従って、第1の実施形態で述べた内容は本実施形態においても適用することが可能である。以下、第1の実施形態と同一の構成については同一の符号を付し、説明を省略する。なお、第2の電極108が有する開口パターン112の形状は、第1~第4、第7のいずれかで示した形状にすることができるが、他の形状であっても良い。

# [0256]

本実施形態でも、第1の実施形態と同様の効果を得ることができる。なお、第1の電極102cに、第2の電極108が有する開口パターン112に平行な開口パターンを形成することにより、IPS方式の液晶表示装置にすることもできる。開口パターンの形状は、上記した第1~第4、第7の実施形態のいずれかで示した形状にすることができる。ただし、液晶表示装置の基板100に対して垂直な方向から見た場合に、第1の電極102cの開口パターン及び開口パターン112は、第1の電極102c及び第2の電極108が周辺部分を除いて互い違いかつ略平行になるように配置される必要がある。

#### [0257]

なお、本実施形態は、第1~第14の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第14の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

# [0258]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

#### [0259]

# (第16の実施形態)

10

20

30

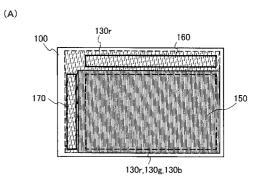

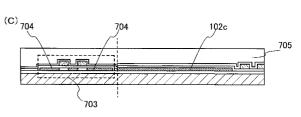

図20は、本発明の第16の実施形態に係るFFS方式の液晶表示装置の画素部の構成を説明する為の断面図である。本実施形態に係る液晶表示装置の画素部は、第1層間絶縁膜106aの代わりに赤色のカラーフィルタ130r、青色のカラーフィルタ130b、及び緑色のカラーフィルタ130gを配置した点を除いて、第1の実施形態に示した液晶表示装置と略同様の構成である。従って、第1の実施形態で説明した内容は本実施形態においても適用できる。以下、第1の実施形態と同様の構成については同一の符号を付し、説明を省略する。なお、絶縁膜105は、カラーフィルタ130r,130b,130gと半導体膜102fに不純物が拡散することを抑制する、という機能も有することになる。

#### [0260]

本実施形態に係る液晶表示装置の製造方法は、第1層間絶縁膜106aを形成する工程の代わりにカラーフィルタ130r,130g,130bを形成する工程が入る点を除いて、第1の実施形態に係る液晶表示装置の製造方法と同様である。カラーフィルタ目30r,130g,130bは、カラーフィルタ層を形成する工程、カラーフィルタ層上にレジストパターンを形成する工程、及びレジストパターンをマスクとしてカラーフィルタ層を選択的にドライエッチングする工程を3回繰り返すことにより形成される。なお、カラーフィルタ層相互間にスペースが生じるが、このスペースには第2層間絶縁膜106bが埋め込まれる。また、カラーフィルタ130r,130g,130bは液滴吐出法(例えばインクジェット法)を用いても形成することができる。

#### [0261]

このため、液晶表示装置の製造工程数を減らすことができる。また、基板 1 0 0 側にカラーフィルタを設けているため、対向基板にカラーフィルタを設ける場合と比較して、対向基板との間に位置ずれが生じても、開口率の低下が抑制できる。すなわち対向基板の位置ずれに対するマージンが大きくなる。

#### [0262]

なお、カラーフィルタの色は、赤、青、緑以外の色でも良いし、3色よりも多く、例えば、4色や6色でもよい。例えば、イエローやシアンやマゼンダや白が追加されてよい。また、カラーフィルタだけでなく、ブラックマトリックス(ブラックマスクとも呼ぶ)も配置してもよい。

## [0263]

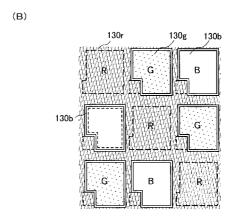

図21(A)は、図20に示した液晶表示装置の平面図である。図21(A)に示すように、本液晶表示装置は、画素部150の周囲に、周辺駆動回路であるソース線駆動回路160及びゲート線駆動回路170が設けられている。ソース線駆動回路160及びゲート線駆動回路170ぞれ上には、赤色のカラーフィルタ130rが設けられている。カラーフィルタ130rが設けられることにより、ソース線駆動回路160及びゲート線駆動回路170が有する薄膜トランジスタの活性層の光劣化が防止され、かつ平坦化が図られている。

#### [0264]

図21(B)は、図21(A)の画素部150の一部(3×3行列)を拡大した図である。画素部150には、赤色のカラーフィルタ130r、青色のカラーフィルタ130b、及び緑色のカラーフィルタ130gがストライプ状に交互に配置されている。また、各画素が有する薄膜トランジスタ上には赤色のカラーフィルタ130rが配置されている。

# [ 0 2 6 5 ]

また、ソース配線(図示せず)及びゲート配線(図示せず)は、各カラーフィルタの相 互間のスペースと重なるように配置されているため、光漏れが生じることが抑制される。

# [0266]

このようにカラーフィルタ130rはブラックマスクの役割を果たすため、従来必要であったブラックマスクの形成工程を省略できる。

#### [0267]

以上、本実施形態によれば、第1の実施形態と同様の効果を得ることができる。また、

10

20

30

40

第 1 層間絶縁膜 1 0 6 a の代わりにカラーフィルタ 1 3 0 r , 1 3 0 b , 1 3 0 g を設けたため、液晶表示装置の製造工程数を減らすことができる。また、対向基板にカラーフィルタを設ける場合と比較して、対向基板との間に位置ずれが生じても、開口率の低下が抑制できる。すなわち対向基板の位置ずれに対するマージンが大きくなる。

[0268]

なお、第2~第4、第6~13、及び第15の実施形態で示したFFS方式又はIPS方式の液晶表示装置において、本実施形態と同様に、第1層間絶縁膜106aの代わりにカラーフィルタ130r,130b,130gを設けてもよい。この場合においても、本実施形態と同様の効果を得ることができる。

[0269]

なお、ゲート電極と、ソース配線との間に、カラーフィルタを配置してもよいが、これに限定されない。ソース配線と第2の電極108の間に配置してもよい。

[0270]

また、カラーフィルタだけでなく、ブラックマトリックスを配置してもよい。

[0271]

なお、カラーフィルタとソース配線との間や、カラーフィルタと第 2 の電極 1 0 8 との間に、無機材料の絶縁膜を配置してもよい。無機材料としては、酸化シリコン(SiO $_{\times}$ )、窒化シリコン(SiN $_{\times}$ )、酸化窒化シリコン(SiО $_{\times}$ N $_{y}$ :  $_{x}$  >  $_{y}$  )、窒化酸化シリコン(SiN $_{x}$  の  $_{y}$  :  $_{x}$  >  $_{y}$  )など、酸素又は窒素を有する絶縁物質から構成される。不純物の侵入をブロックするためには、窒素を多く含む材料にすることが望ましい。

[0272]

なお、本実施形態は、第1~第15の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第15の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

[0273]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

[0274]

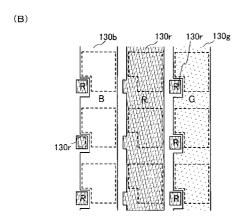

(第17の実施形態)

図22(A)は、本発明の第17の実施形態に係るFFS方式の液晶表示装置の構成を説明する為の平面図であり、図22(B)は、図22(A)の画素部の構成を説明するための拡大図である。本実施形態に係る液晶表示装置は、カラーフィルタ130r,130b,130gのレイアウトを除いて、第16の実施形態と同様の構成である。従って、第16の実施形態で説明した内容は本実施形態においても適用できる。以下、第16の実施形態と同様の構成については同一の符号を付し、説明を省略する。

[0275]

本実施形態では、カラーフィルタ130r,130b,130gは、画素単位でマトリクス状に交互に配置されている。詳細には、青色のカラーフィルタ130b及び緑色の130gの隙間を埋めるように、赤色のカラーフィルタ130rが設けられている。また、周辺駆動回路であるソース線駆動回路160及びゲート線駆動回路170の上にもカラーフィルタ130rが設けられているが、ソース線駆動回路160及びゲート線駆動回路170それぞれと画素部150の間のスペースにも、カラーフィルタ130rが設けられている。このため、カラーフィルタ層相互間にスペースが生じることが抑制される。

[0276]

本実施形態によっても第16の実施形態と同様の効果を得ることができる。なお、第1層間絶縁膜106aを形成した上で、第2層間絶縁膜106bの代わりにカラーフィルタ130r,130b,130gを設けてもよい。この場合においても本実施形態と同様の効果を得ることができる。

10

20

30

40

また、第2~第4、第6~13、及び第15の実施形態で示したFFS方式又はIPS方式の液晶表示装置において、本実施形態と同様に、第1層間絶縁膜106aの代わりにカラーフィルタ130r,130b,130gを設けてもよい。この場合においても、本実施形態と同様の効果を得ることができる。

[0278]

なお、本実施形態は、第1~第16の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第16の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

[0279]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

[0280]

(第18の実施形態)

図23は、本発明の第18の実施形態に係るFFS方式の液晶表示装置の構成を説明する為の断面図である。本実施形態に係る液晶表示装置は、第1層間絶縁膜106aの代わりにカラーフィルタ130r,130b,130gが設けられている点を除いて、第5の実施形態と同様の構成である。本実施形態におけるカラーフィルタ130r,130b,130gのレイアウトは、第17の実施形態に示したレイアウトと同様である。従って、第5の実施形態で説明した内容、及び第17の実施形態で説明した内容それぞれは、本実施形態においても適用することができる。以下、第5の実施形態と同様の構成、及び第17の実施形態と同様の構成については同一の符号を付し、説明を省略する。

[0281]

本実施形態においても第17の実施形態と同様の効果を得ることができる。なお、第14の実施形態で示したFFS方式の液晶表示装置において、本実施形態と同様に、第1層間絶縁膜106aの代わりにカラーフィルタ130r,130b,130gを設けてもよい。この場合においても、本実施形態と同様の効果を得ることができる。

[0282]

なお、カラーフィルタ130 r ,130 b ,130 g のレイアウトは、上記した第16~第18の実施形態に示したレイアウトに限定されるものではなく、三角モザイク配列、R G B G 四画素配列、R G B W 四画素配列等、様々なレイアウトを取ることができる。なお、これらの場合においても、薄膜トランジスタの活性層の上方に赤色のカラーフィルタ130 r を配置することが望ましい。

[0283]

なお、本実施形態は、第1~第17の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第17の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

[0284]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

[0285]

(第19の実施形態)

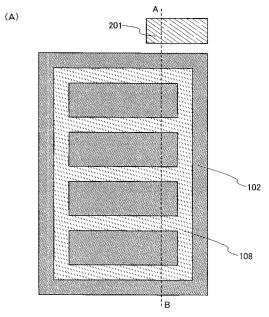

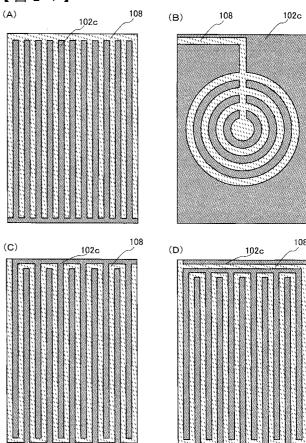

図24(A)~(D)それぞれは、本発明の第19の実施形態に係るFFS方式の液晶表示装置の電極の形状を説明する為の平面図である。各図に示す実施形態は、第2の電極108の形状を除いて、第1の実施形態で示したFFS方式の液晶表示装置と同様の構成であるため、第1の電極102c及び第2の電極108を除いて図示を省略している。

10

20

30

40

10

20

30

40

50

#### [0286]

図24(A)において第2の電極108は櫛歯状の形状を有しており、櫛歯部分の相互間に位置するスペースが、第1の実施形態で示した開口パターン112の役割を果たしている。

#### [0287]

図24(B)において第2の電極108は、それぞれが円周に沿う形状を有していて半径が異なる複数の電極を同心に配置し、これらを接続した形状である。そして、各電極の相互間のスペースが、第1の実施形態で示した開口パターン112の役割を果たしている

#### [0288]

図24(C)において第2の電極108は、長方形の第1の電極102cの長辺方向に延伸する直線状の電極を、互いに重ならないように第1の電極102cの面内に複数配置し、互いに隣接する直線状の電極の上端部及び下端部のいずれかを交互に接続した形状である。すなわち第2の電極108は、細長い電極を第1の電極102cの面内を上下に繰り返し引き回した形状であるが、その一方の端部は、第1の電極102cの一方の長辺(図では右側の長辺)に最も近い部分に配置され、かついずれにも接続されていない。そして、直線状の電極の相互間のスペースが、第1の実施形態で示した開口パターン112の役割を果たしている。

# [0289]

図24(D)において第2の電極108は、図24(C)に示した第2の電極108において、第1の電極102cの一方の長辺(図では右側の長辺)に最も近い部分に配置された端部を更に延伸して、第1の電極102cの短辺(図では上側の短辺)に沿って引き戻し、第1の電極102cの他方の長辺(図では右側の長辺)に最も近い部分に接続した形状である。第2の電極108の両端が互いに接続されているため、図24(C)に示した形状と比較して第2の電極108の電位を一定に保ちやすい。

#### [0290]

本実施形態に係る液晶表示装置の製造方法は、いずれの場合においても第1の実施形態と略同様である。従って、第1の実施形態で述べた内容は本実施形態にも適用することができる。

# [0291]

本実施形態によっても第1の実施形態と同様の効果を得ることができる。なお、第2の実施形態、第5の実施形態、及び、第13~第18の実施形態それぞれにおいて、第2の電極108の形状を図24のいずれかに示す形状にしてもよい。

#### [0292]

なお、本実施形態は、第1~第18の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第18の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

# [0293]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さらなる構成を作ることも可能である。

#### [0294]

# (第20の実施形態)

図25(A)~(D)それぞれは、本発明の第20の実施形態に係るIPS方式の液晶表示装置の電極の形状を説明する為の平面図である。本実施形態は、第1の電極102c及び第2の電極108それぞれの形状を除いて、第3の実施形態と同様の構成であるため、第1の電極102c及び第2の電極108を除いて、図示を省略している。

# [0295]

図25(A)において、第1の電極102c及び第2の電極108それぞれは櫛歯形状

であり、互いに逆向きに配置されている。そして櫛歯の部分は、互い違いに配置されている。

#### [0296]

図25(B)において第1の電極102には、長方形の本体部分の中央部に円形の開口パターン115を設け、開口パターン115内に、円周に沿う形状であり互いに半径が異なる複数の電極を開口パターン115と同心に配置し、これら円周に沿う形状の電極それぞれを一本の直線状の電極で本体部分に接続した形状である。また、第2の電極108は、長方形の本体部分の中央部に円形の開口パターン112を設け、開口パターン112内に、円周に沿う形状の電極を開口パターン112と同心に配置し、この電極と本体部分を直線状の電極で接続した形状である。なお、第2の電極108が有する円周に沿う形状の電極は、複数であってもよい。

#### [0297]

また、開口パターン 1 1 2 , 1 1 5 は互いに同心であるため、第 1 の電極 1 0 2 c が有する円周に沿う形状の電極と、第 2 の電極 1 0 8 が有する円周に沿う形状の電極は、互いに同心である。なお、第 1 の電極 1 0 2 c が有する円周に沿う形状の電極と、第 2 の電極 1 0 8 が有する円周に沿う形状の電極は、互いに半径が異なるため、互い違いかつ互い平行である。

# [0298]

図25(C)において第1の電極102cは、図中上下に延伸する直線状の電極を複数互いに平行に配置し、これらの上端部及び下端部それぞれを、図中横方向に延伸する直線状の電極で接続した形状である。また第2の電極108は櫛歯形状であり、櫛歯部分が、第1の電極102cを構成する直線状の電極相互間のスペースに位置している。

#### [0299]

図25(D)において第1の電極102c及び第2の電極108は、それぞれ図中上下に延伸する直線状の電極を、互いに重ならないように複数互いに平行に配置し、互いに隣接する直線状の電極の上端部及び下端部のいずれかを交互に接続した形状である。すなわち第2の電極108は、細長い電極を第1の電極102cの面内を上下に繰り返し引き回した形状である。そして第1の電極102c及び第2の電極108は、図中上下に延伸する部分が互い違いかつ互い平行になっており、かつ図中横に延伸する部分が互いにずれている。

#### [0300]

本実施形態に係る液晶表示装置の製造方法は、いずれの場合においても第3の実施形態と略同様である。従って、第3の実施形態で述べた内容は本実施形態にも適用することができる。

#### [0301]

本実施形態によっても、第3の実施形態と同様の効果を得ることができる。なお、第4の実施形態、第6~第12の実施形態それぞれにおいて、第1の電極102c及び第2の電極108の形状を、図25のいずれかに示した形状にしてもよい。

#### [0302]

また、上記した各実施形態において、半導体膜102fの代わりに他の半導体膜(例えば有機半導体又はアモルファスシリコン膜)を用いてもよい。この場合、第1の電極10 2cも、上記した他の半導体膜により形成してもよい。

#### [0303]

なお、本実施形態は、第1~第19の実施形態で述べた内容を、一部変更、改良、変形、別の見方をする、又は別の観点から記載した場合の一例を示している。したがって、第1~第19の実施形態で述べた内容は、本実施形態にも適用することや、組み合わせることが出来る。

# [0304]

また、さまざまな図を用いて述べてきたが、1つの図は、様々な構成要件により成り立っている。したがって、各々の図の中から、各々の構成要件に関して、組み合わせて、さ

10

20

30

40

らなる構成を作ることも可能である。

#### [0305]

# (第21の実施形態)

図32は、本発明を用いた無機EL素子の構成を説明するための断面図である。本実施 形態に係る無機EL素子は、ボトムゲート型のトランジスタを用いた構成を有しており、 第 1 の電極 1 0 2 c と第 2 の電極 1 0 8 を用いる点において、第 1 3 の実施形態に係る液 晶 表 示 装 置 に 近 い 構 成 と な っ て い る 。 ト ラ ン ジ ス タ や 電 極 等 の 構 成 は 本 実 施 形 態 に 示 す 構 成に限られず、トップゲート型のトランジスタを用いても良いし、他の実施形態に示す電 極の構成を用いても良い。本実施形態の断面図においては一つのトランジスタのみを示す が、駆動用トランジスタ、選択用トランジスタ、電流制御用トランジスタなど、一画素に 複数のトランジスタを有する構成としても良い。第2の電極として用いる材料としては、 アルミニウム(A1)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タン グステン(W)、ネオジム(Nd)、クロム(Cr)、ニッケル(Ni)、白金(Pt) 、金(Au)、銀(Ag)、銅(Cu)、マグネシウム(Mg)、スカンジウム(Sc) 、コバルト(Co)、ニッケル(Ni)、亜鉛(Zn)、ニオブ(Nb)、シリコン(S i)、リン(P)、ボロン(B)、ヒ素(As)、ガリウム(Ga)、インジウム(In )、錫(Sn)で構成された群から選ばれた一つ又は複数の元素、もしくは、前記群から 選 ば れ た 一 つ 又 は 複 数 の 元 素 を 成 分 と す る 化 合 物 や 合 金 材 料 ( 例 え ば 、 イ ン ジ ウ ム 錫 酸 化 物(ITO)、インジウム亜鉛酸化物(IZO)、酸化珪素を添加したインジウム錫酸化 物(ITSO)、酸化亜鉛(ZnO)、アルミネオジム(A1-Nd)、マグネシウム銀 ( M g - A g ) など)、もしくは、これらの化合物を組み合わせた物質などが挙げられる 。または、前述した材料とシリコンとの化合物(シリサイド)(例えば、アルミシリコン 、 モリブデンシリコン、ニッケルシリサイドなど)や、前述の材料と窒素との化合物(例 えば、窒化チタン、窒化タンタル、窒化モリブデン等)を用いることができる。なお、シ リコン(Si)には、n型不純物(リンなど)やp型不純物(ボロンなど)を多く含んで いてもよい。

#### [0306]

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類され、前者は、発光材料の粒子をバインダ中に分散させた発光材料を含む層を有し、後者は、薄膜からなる発光材料を含む層を有している点に違いはあるが、高電界で加速された電子を必要とする点では共通である。本実施形態においては、第2の電極108の上方に発光材料を含む層501を設ける。分散型の無機EL素子の場合には、第2の電極上に接して発光材料を含む層501を設ける構成(図32(A)参照)とすることが好ましいが、これに限られない。また、薄膜型の無機EL素子とする場合には、第2の電極108上に誘電体502を形成し、誘電体上502に発光材料を含む層501を設ける構成(図32(B))が好ましいが、これに限られない。

# [0307]

発光のメカニズムとしては、ドナー準位とアクセプター準位を利用するドナー・アクセプター再結合型発光と、金属イオンの内殻電子遷移を利用する局在型発光とが知られている。一般的に、分散型無機 E L ではドナー・アクセプター再結合型発光、薄膜型無機 E L 素子では局在型発光である場合が多い。

#### [0308]

本実施形態の発光材料を含む層 5 0 1 は、母体材料と発光中心となる不純物元素とで構成され、含有させる不純物元素を変化させることで、様々な色の発光を得ることができる。発光材料の作製方法としては、噴霧熱分解法、複分解法、プレカーサーの熱分解反応による方法、逆ミセル法、これらの方法と高温焼成を組み合わせた方法、又は凍結乾燥法などを用いることができる。

# [0309]

固相法は、母体材料と、不純物元素又は不純物元素を含む化合物を秤量し、乳鉢で混合、電気炉で加熱、焼成を行い反応させ、母体材料に不純物元素を含有させる方法である。

10

20

30

40

焼成温度は、700~1500 が好ましい。温度が低すぎる場合は固相反応が進まず、温度が高すぎる場合は母体材料が分解してしまうからである。なお、粉末状態で焼成を行ってもよいが、ペレット状態で焼成を行うことが好ましく、比較的高温での焼成を必要とするが、簡単な方法であるため、生産性がよく大量生産に適している。

#### [0310]

液相法(共沈法)は、母体材料又は母体材料を含む化合物と、不純物元素又は不純物元素を含む化合物を溶液中で反応させ、乾燥させた後、焼成を行う方法であり、発光材料の粒子が均一に分布し、粒径が小さく、低い焼成温度でも反応を促進させることができる。

## [0311]

発光材料に用いる母体材料としては、硫化物、酸化物、窒化物を用いることができる。硫化物としては、例えば、硫化亜鉛(Z n S)、硫化カドミウム(C d S)、硫化カルシウム(C a S)、硫化イットリウム(Y  $_2$  S  $_3$ )、硫化ガリウム(G a  $_2$  S  $_3$ )、硫化ストロンチウム(S r S)、硫化バリウム(B a S)等を用いることができ、酸化物としては、例えば、酸化亜鉛(Z n O)、酸化イットリウム(Y  $_2$  O  $_3$  )等を用いることができる。

#### [0312]

また、窒化物としては、例えば、窒化アルミニウム(AIN)、窒化ガリウム(GaN)、窒化インジウム(InN)等を用いることができる。 さらに、セレン化亜鉛(ZnSe)、テルル化亜鉛(ZnTe)等も用いることができ、硫化カルシウム・ガリウム(CaGa $_2$ S $_4$ )、硫化バリウム・ガリウム(BaGa $_2$ S $_4$ )、硫化バリウム・ガリウム(BaGa $_2$ S $_4$ )等の3元系の混晶であってもよい。

#### [ 0 3 1 3 ]

局在型発光の発光中心として、マンガン(Mn)、銅(Cu)、サマリウム(Sm)、 テルビウム(Tb)、エルビウム(Er)、ツリウム(Tm)、ユーロピウム(Eu)、 セリウム(Ce)、プラセオジウム(Pr)などを用いることができる。なお、電荷補償 として、フッ素(F)、塩素(Cl)などのハロゲン元素が添加されていてもよい。

#### [0314]

一方、ドナー・アクセプター再結合型発光の発光中心として、ドナー準位を形成する第1の不純物元素及びアクセプター準位を形成する第2の不純物元素を含む発光材料を用いることができる。第1の不純物元素としては、例えば、フッ素(F)、塩素(C1)、アルミニウム(A1)等を用いることができ、第2の不純物元素としては、例えば、銅(Cu)、銀(Ag)等を用いることができる。

#### [0315]

なお、無機 E L 発光素子は、一対の電極層間に電圧を印加することにより発光を得ることができるが、本実施形態においては交流駆動を用いることが好ましい。本実施形態に示す無機 E L 発光素子においては、第 1 の電極 1 0 2 c および第 2 の電極 1 0 8 により形成される電界を用いることによって発光させるためである。なお、発光のために形成される電界は、他の実施形態において説明した液晶表示装置における電界と同様である。

# [0316]

本実施形態に用いることのできるバインダとしては、有機材料や無機材料の絶縁材料を用いることができ、有機材料及び無機材料の混合材料を用いてもよい。有機絶縁材料としては、シアノエチルセルロース系樹脂のように、比較的誘電率の高いポリマーや、ポリエチレン、ポリプロピレン、ポリスチレン系樹脂、シリコーン樹脂、エポキシ樹脂、フッ化ビニリデンなどの樹脂を用いることができる。また、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシロキサン樹脂を用いてもよい。

#### [0317]

また、ポリビニルアルコール、ポリビニルブチラールなどのビニル樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂、オキサゾール樹脂(ポリベンゾオキサゾール)等の樹脂材料を用いてもよく、また光硬化型などを用いること

10

20

30

40

10

20

30

40

50

ができる。さらに、これらの樹脂にチタン酸バリウム(BaTiO $_3$ )やチタン酸ストロンチウム(SrTiO $_3$ )等の高誘電率の微粒子を適度に混合して誘電率を調整することもできる。

# [0318]

また、バインダに用いる無機絶縁材料としては、酸化珪素(SiO $_{\rm X}$ )、窒化珪素(SiN $_{\rm X}$ )、酸素及び窒素を含む珪素、窒化アルミニウム(AlN)、酸素及び窒素を含む アルミニウム、又は酸化アルミニウム(Al $_{\rm 2}$ O $_{\rm 3}$ )、酸化チタン(TiO $_{\rm 2}$ )、BaTiO $_{\rm 3}$ 、SrTiO $_{\rm 3}$ 、チタン酸鉛(PbTiO $_{\rm 3}$ )、二オブ酸カリウム(KNbO $_{\rm 3}$ )、二オブ酸鉛(PbNbO $_{\rm 3}$ )、酸化タンタル(Ta $_{\rm 2}$ O $_{\rm 5}$ )、タンタル酸バリウム(BaTa $_{\rm 2}$ O $_{\rm 6}$ )、タンタル酸リチウム(LiTaO $_{\rm 3}$ )、酸化イットリウム(Y $_{\rm 2}$ O $_{\rm 3}$ )、酸化ジルコニウム(ZrO $_{\rm 2}$ )、ZnSその他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。有機材料に、誘電率の高い無機材料を含ませる(添加等によって)ことによって、発光材料及びバインダよりなる発光物質を含む層の誘電率を制御することができ、より誘電率を大きくすることもできる。

#### [0319]

本実施形態に示すように、シリコンを含む電極を無機EL素子の電極として用いることにより、低コストに無機EL素子を作製することができる。また、本実施形態に示す構成とすることにより、電極による光の減衰を考慮せずとも良いため、電極材料の選択の幅を広げることができる。例えば、第2の電極として金属材料を用い、その厚みを大きくすることも可能である。また、第1の電極と第2の電極との間に発光材料を含む層を設ける必要がないため、表示装置としての輝度が向上し、EL素子に対する負荷を低減することができる。

#### [0320]

#### (第22の実施形態)