(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2020-42191

(P2020-42191A)

(43) 公開日 令和2年3月19日(2020.3.19)

| (51) Int.Cl.                 | F 1  |        |      | テーマコード (参考) |        |

|------------------------------|------|--------|------|-------------|--------|

| <b>G09G</b> 3/20 (2006.01)   | GO9G | 3/20   | 624B | 2H092       |        |

| <b>G02F</b> 1/1368 (2006.01) | GO2F | 1/1368 |      | 2H192       |        |

| <b>G02F</b> 1/1343 (2006.01) | GO2F | 1/1343 |      | 5C006       |        |

| <b>G09G</b> 3/36 (2006.01)   | GO9G | 3/20   | 624E | 5C080       |        |

| <b>G09G</b> 3/3225 (2016.01) | GO9G | 3/20   | 624D | 5C380       |        |

| 審査請求 未請求 請求項の数 5             |      |        | O L  | (全 23 頁)    | 最終頁に続く |

|           |                              |            |                                                                                                                                  |

|-----------|------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2018-170052 (P2018-170052) | (71) 出願人   | 502356528                                                                                                                        |

| (22) 出願日  | 平成30年9月11日 (2018. 9. 11)     |            | 株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目 7番 1号                                                                                              |

|           |                              | (74) 代理人   | 110002147                                                                                                                        |

|           |                              |            | 特許業務法人酒井国際特許事務所                                                                                                                  |

|           |                              | (72) 発明者   | 石井 達也<br>東京都港区西新橋三丁目 7番 1号 株式会<br>社ジャパンディスプレイ内                                                                                   |

|           |                              | F ターム (参考) | 2H092 GA59 GA60 JA24 JB21 JB42<br>JB63 JB66 JB68 PA06 RA10<br>2H192 AA24 BC72 CB23 CB24 DA81<br>EA43 FB02 FB27 GA42 GD61<br>JB01 |

(54) 【発明の名称】 表示装置及び電子看板

(57) 【要約】 (修正有)

【課題】低消費電力化を実現でき、高精細化を可能とする表示装置及び電子看板を提供する。

【解決手段】表示装置は、行方向及び列方向に配列される複数の副画素 S P i x を備え、副画素 S P i x はメモリ 5 1 及び反転スイッチ 6 1 に加えて液晶 L Q と副画素電極 1 5 とを含み、メモリ 5 1 は 2 個のコンデンサが直列接続されたと考えられるコンデンサ 5 1 a と、直列接続されたと考えられるコンデンサの間に配置された浮遊電極 5 1 b を有し、コンデンサ 5 1 a の一方端は走査線 G C L a に接続され、他方端はデータ線 S G L に接続され、複数の副画素 S P i x は、浮遊電極 5 1 b の電位に基づいて画像を表示する。

【選択図】図 5

**【特許請求の範囲】****【請求項 1】**

行方向及び列方向に配列されると共に、副画素データを記憶するメモリを各々が含む、複数の副画素を備え、

前記メモリは、

コンデンサと、前記コンデンサの両端間に配置された浮遊電極と、を有し、

前記複数の副画素は、

前記浮遊電極の電位に基づいて画像を表示する、

表示装置。

**【請求項 2】**

前記コンデンサの一端は、導体であり、

前記コンデンサの他端は、半導体であり、

前記浮遊電極は、トンネル酸化膜を挟んで前記半導体と対向するとともに、絶縁膜を挟んで前記導体と対向する、

請求項 1 に記載の表示装置。

**【請求項 3】**

各行に夫々設けられ、各行の前記コンデンサの一端に走査信号を供給する、複数の走査線と、

各列に夫々設けられ、各列の前記コンデンサの他端にデータ信号を供給する、複数のデータ線と、を更に備える、

請求項 2 に記載の表示装置。

**【請求項 4】**

前記複数の副画素の各々は、

副画素電極と、

前記浮遊電極の電位に基づく電位を前記副画素電極に出力するスイッチ回路と、

を更に含み、

前記表示装置は、

複数の前記副画素電極に対向して設けられる共通電極と、

前記共通電極に、基準信号に同期して反転させてなるコモン電位を出力する、共通電極駆動回路と、

前記スイッチ回路に電気的に夫々接続されている、複数の表示信号線と、

前記コモン電位と同相の表示信号及び逆相の反転表示信号を、前記複数の表示信号線に出力する、反転駆動回路と、

を更に備え、

前記スイッチ回路は、

前記浮遊電極の電位に基づいて、前記表示信号及び前記反転表示信号の内の一方を前記副画素電極に出力する、

請求項 1 から 3 のいずれか 1 項に記載の表示装置。

**【請求項 5】**

行方向及び列方向に配列されると共に、副画素データを記憶するメモリを各々が含む、複数の副画素を備え、

前記メモリは、

コンデンサと、前記コンデンサの両端間に配置された浮遊電極と、を有し、

前記複数の副画素は、

前記浮遊電極の電位に基づいて、画像を表示する、

電子看板。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、表示装置及び電子看板に関する。

10

20

30

40

50

## 【背景技術】

## 【0002】

画像を表示する表示装置は、複数の画素を備える。下記の特許文献1には、複数の画素の各々がメモリを含む、いわゆるMIP(Memory In Pixel)型の表示装置が記載されている。特許文献1記載の表示装置では、複数の画素の各々が、複数のメモリとこれらのメモリの切替え回路とを含んでいる。特許文献2には、1ビットのメモリを含む表示素子が記載されている。特許文献3には、不揮発性半導体記憶装置が記載されている。

## 【先行技術文献】

## 【特許文献】

## 【0003】

10

【特許文献1】特開平9-212140号公報

【特許文献2】特開昭58-196582号公報

【特許文献3】特許第2685770号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

特許文献1記載の表示装置では、各画素のメモリには、DRAM(Dynamic Random Access Memory)又はSRAM(Static Random Access Memory)が用いられている。DRAMは、リフレッシュ動作が必要であり、低消費電力化には向かない。SRAMは、回路規模が大きく、高精細化が難しい。

20

## 【0005】

本発明は、高精細化を可能とする表示装置及び電子看板を提供することを目的とする。

## 【課題を解決するための手段】

## 【0006】

本発明の一態様の表示装置は、行方向及び列方向に配列されると共に、副画素データを記憶するメモリを各々が含む、複数の副画素を備える。メモリは、コンデンサと、コンデンサの両端間に配置された浮遊電極と、を有する。複数の副画素は、浮遊電極の電位に基づいて画像を表示する。

## 【0007】

本発明の一態様の電子看板は、行方向及び列方向に配列されると共に、副画素データを記憶するメモリを各々が含む、複数の副画素を備える。メモリは、コンデンサと、コンデンサの両端間に配置された浮遊電極と、を有する。複数の副画素は、浮遊電極の電位に基づいて画像を表示する。

30

## 【図面の簡単な説明】

## 【0008】

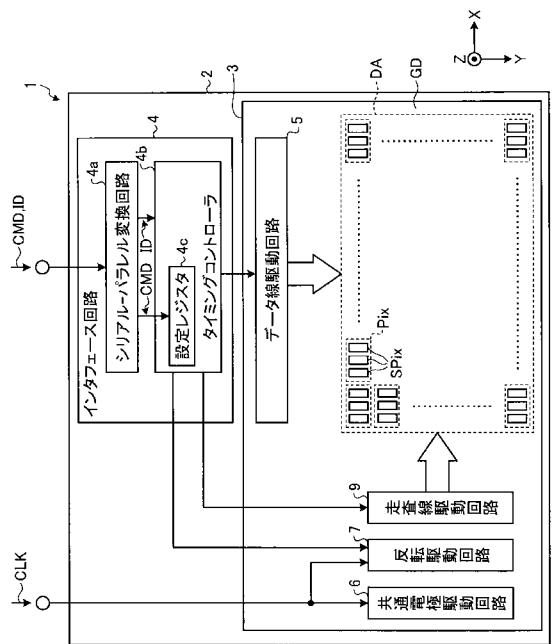

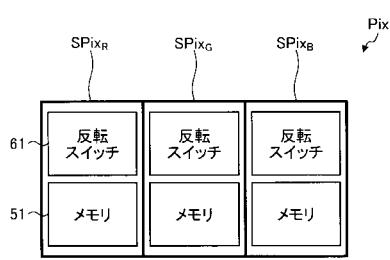

【図1】図1は、実施の形態の表示装置の全体構成の概要を示す図である。

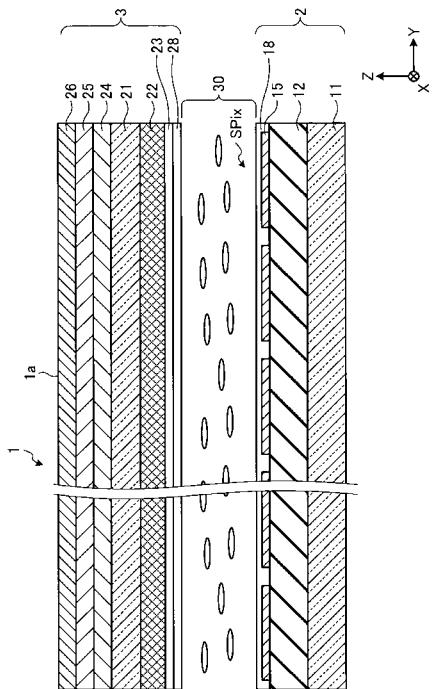

【図2】図2は、実施の形態の表示装置の断面図である。

【図3】図3は、実施の形態の表示装置の画素内での副画素の配置を示す図である。

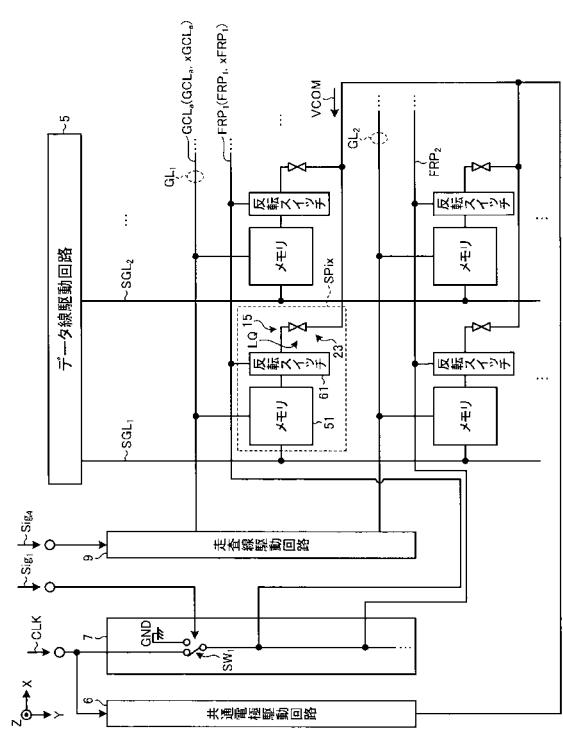

【図4】図4は、実施の形態の表示装置の回路構成を示す図である。

40

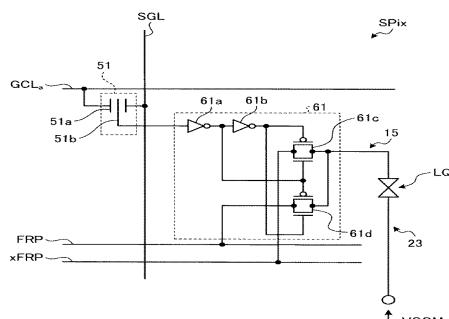

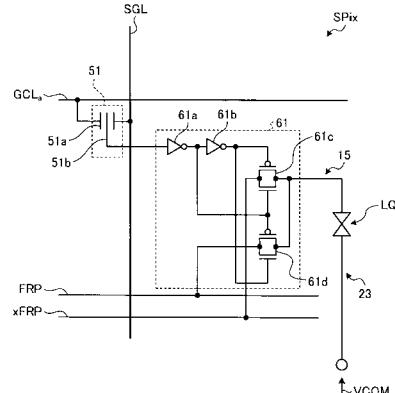

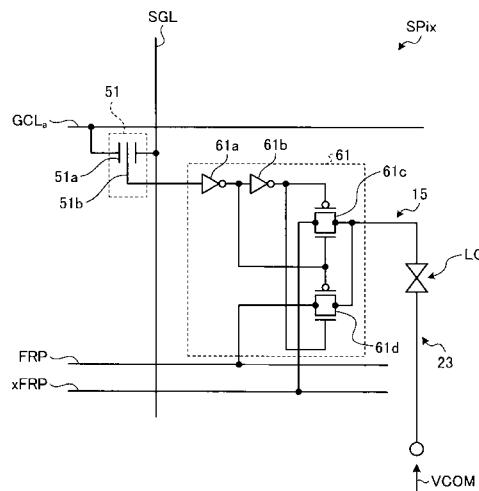

【図5】図5は、実施の形態の表示装置の副画素の回路構成を示す図である。

【図6】図6は、実施の形態の表示装置の副画素の構成を示す図である。

【図7】図7は、実施の形態の表示装置の副画素に書き込まれる副画素データを示す図である。

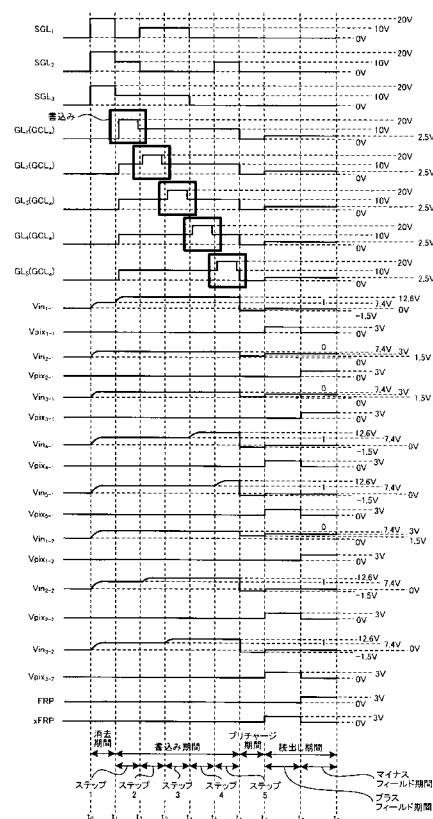

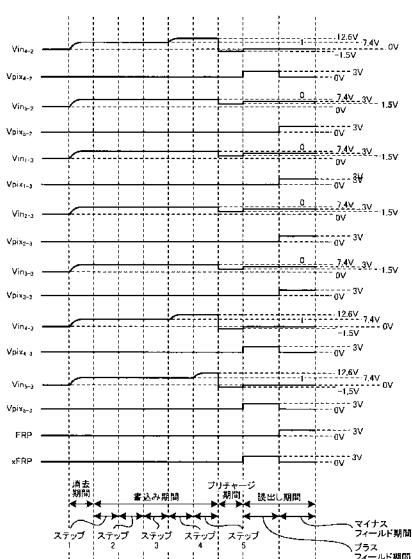

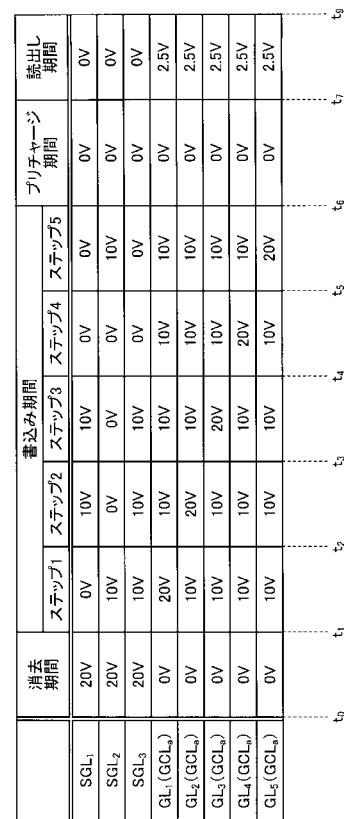

【図8-1】図8-1は、実施の形態の表示装置の動作タイミングを示すタイミング図である。

【図8-2】図8-2は、実施の形態の表示装置の動作タイミングを示すタイミング図である。

【図9】図9は、実施の形態の表示装置の各部の電位を示す図である。

【図10】図10は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth図である。

50

【図11】図11は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth図である。

【図12】図12は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth図である。

【図13】図13は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth図である。

【図14】図14は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth図である。

【図15】図15は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth図である。

【図16】図16は、実施の形態の表示装置の副画素のメモリの浮遊電極の電位を示す図である。

【図17】図17は、実施の形態の表示装置の副画素のレイアウトを示す図である。

【図18】図18は、実施の形態の表示装置の副画素の断面図である。

【図19】図19は、実施の形態の表示装置の副画素のトランジスタ数と、特許文献2の表示素子のトランジスタ数と、を示す図である。

【発明を実施するための形態】

【0009】

本発明を実施するための形態（実施の形態）につき、図面を参照しつつ詳細に説明する。以下の実施の形態に記載した内容により本発明が限定されるものではない。また、以下に記載した構成要素には、当業者が容易に想定できるもの、実質的に同一のものが含まれる。さらに、以下に記載した構成要素は適宜組み合わせることが可能である。なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。

【0010】

（実施の形態）

[全体構成]

図1は、実施の形態の表示装置の全体構成の概要を示す図である。表示装置1は、第1パネル2と、第1パネル2に対向配置された第2パネル3と、を含む。表示装置1は、画像を表示する表示領域DAと、表示領域DAの外側の額縁領域GDと、を有する。表示領域DAにおいて、第1パネル2と第2パネル3との間には、液晶層が封入されている。

【0011】

なお、実施の形態では、表示装置1は、液晶層を使用した液晶表示装置としたが、本開示はこれに限定されない。表示装置1は、液晶層に代えて有機EL（Electro-Luminescence）素子を使用した有機EL表示装置であっても良い。

【0012】

表示領域DA内には、複数の画素Pi×が、第1パネル2及び第2パネル3の主面と平行なX方向にN列（Nは、自然数）、第1パネル2及び第2パネル3の主面と平行且つX方向と交差するY方向にM行（Mは、自然数）のマトリクス状に配置されている。額縁領域GD内には、インターフェース回路4と、データ線駆動回路5と、共通電極駆動回路6と、反転駆動回路7と、走査線駆動回路9と、が、配置されている。なお、これら複数の回路のうち、インターフェース回路4と、データ線駆動回路5と、共通電極駆動回路6と、反転駆動回路7と、をICチップに組み込み、走査線駆動回路9を第1パネル2上に形成した構成を採用することも可能である。或いは、ICチップに組み込まれる回路群を表示装置1外のプロセッサに形成し、それらと表示装置とを接続する構成も採用可能である。

【0013】

10

20

30

40

50

$M \times N$  個の画素  $P_{i \times}$  の各々は、複数の副画素  $S_{P_{i \times}}$  を含む。実施の形態では、複数の副画素  $S_{P_{i \times}}$  は、R(赤)、G(緑)及びB(青)の3個とするが、本開示はこれに限定されない。複数の副画素  $S_{P_{i \times}}$  は、R(赤)、G(緑)及びB(青)にW(白)を加えた4個であっても良い。或いは、複数の副画素  $S_{P_{i \times}}$  は、色が異なる5個以上であっても良い。

【0014】

各画素  $P_{i \times}$  が3個の副画素  $S_{P_{i \times}}$  を含むので、表示領域DA内には、 $M \times N \times 3$  個の副画素  $S_{P_{i \times}}$  が配置されていることになる。また、 $M \times N$  個の画素  $P_{i \times}$  の各々の3個の副画素  $S_{P_{i \times}}$  がX方向に配置されているので、 $M \times N$  個の画素  $P_{i \times}$  の1つの行には、 $N \times 3$  個の副画素  $S_{P_{i \times}}$  が配置されていることになる。

10

【0015】

各副画素  $S_{P_{i \times}}$  が1個のメモリを含むので、表示領域DA内には、 $M \times N \times 3$  個のメモリが配置されていることになる。また、 $M \times N$  個の画素  $P_{i \times}$  の1つの行には、 $N \times 3$  個のメモリが配置されていることになる。

【0016】

各副画素  $S_{P_{i \times}}$  は、各々が含むメモリに格納されている副画素データに基づいて、表示を行う。つまり、 $M \times N \times 3$  個の副画素  $S_{P_{i \times}}$  に含まれる $M \times N \times 3$  個のメモリの集合は、1個のフレームメモリと同等である。

【0017】

インタフェース回路4は、シリアル-パラレル変換回路4aと、タイミングコントローラ4bと、を含む。タイミングコントローラ4bは、設定レジスタ4cを含む。シリアル-パラレル変換回路4aには、コマンドデータCMD及び画像データIDが、外部回路からシリアルに供給される。外部回路は、ホストCPU(Central Processing Unit)又はアプリケーションプロセッサが例示されるが、本開示はこれらに限定されない。

20

【0018】

シリアル-パラレル変換回路4aは、供給されたコマンドデータCMDをパラレルデータに変換して、設定レジスタ4cに出力する。設定レジスタ4cには、データ線駆動回路5、反転駆動回路7及び走査線駆動回路9を制御するための値がコマンドデータCMDに基づいて設定される。

30

【0019】

シリアル-パラレル変換回路4aは、供給された画像データIDをパラレルデータに変換して、タイミングコントローラ4bに出力する。タイミングコントローラ4bは、設定レジスタ4cに設定された値に基づいて、画像データIDをデータ線駆動回路5に出力する。また、タイミングコントローラ4bは、設定レジスタ4cに設定された値に基づいて、反転駆動回路7及び走査線駆動回路9を制御する。

【0020】

共通電極駆動回路6及び反転駆動回路7には、基準クロック信号CLKが、外部回路から供給される。外部回路は、クロックジェネレータが例示されるが、本開示はこれに限定されない。

40

【0021】

液晶表示装置の画面の焼き付きを抑制するための駆動方式として、カラム反転駆動、ライン反転駆動、ドット反転駆動、フレーム反転駆動などの駆動方式が知られている。

【0022】

表示装置1は、上記の各駆動方式のいずれを採用することも可能である。実施の形態では、表示装置1は、フレーム反転駆動の一方式であるコモン反転駆動方式を採用する。表示装置1がコモン反転駆動方式を採用するので、共通電極駆動回路6は、基準クロック信号CLKに同期して、共通電極の電位(コモン電位)を反転する。反転駆動回路7は、タイミングコントローラ4bの制御下で、基準クロック信号CLKに同期して、副画素電極の電位を反転させる。これにより、表示装置1は、コモン反転駆動方式を実現することができる。実施の形態では、表示装置1は、液晶に電圧が印加されていない場合に黒色を表

50

示し、液晶に電圧が印加されている場合に白色を表示する、いわゆるノーマリーブラックとする。ノーマリーブラックでは、副画素電極の電位とコモン電位とが同相の場合には、黒色が表示され、副画素電極の電位とコモン電位とが異相の場合には、白色が表示される。

【0023】

表示装置1にて画像を表示させるべく、各副画素SPixのメモリに副画素データを格納する必要がある。各メモリに副画素データを格納するために、走査線駆動回路9は、タイミングコントローラ4bの制御下で、M×N個の画素P<sub>ix</sub>の内の1つの行を選択するための走査信号を出力する。

【0024】

各副画素SPixが1個のメモリを含むので、1つの行(画素行(副画素行))当たり1本の走査線が配置される。なお、副画素SPixが、走査信号に加えて、走査信号を反転した反転走査信号とで動作する場合には、1つの行当たり、2本の走査線が配置される。

【0025】

1つの行当たりに配置されている1本又は2本の走査線が、本開示の走査線群に対応する。表示装置1は、M行の画素P<sub>ix</sub>を有するので、M群の走査線群が配置されている。

【0026】

走査線駆動回路9は、M行の画素P<sub>ix</sub>に対応して、M個の出力端子を有している。走査線駆動回路9は、タイミングコントローラ4bの制御下で、M行の内の1つの行を選択するための走査信号を、M個の出力端子から順次出力する。

【0027】

データ線駆動回路5は、タイミングコントローラ4bの制御下で、走査信号によって選択されているメモリにデータ信号(副画素データ)を夫々出力する。これにより、各副画素のメモリに順次副画素データが夫々格納される。

【0028】

表示装置1は、M行の画素P<sub>ix</sub>を線順次走査することによって、1個のフレームデータの副画素データが各副画素SPixのメモリに格納される。

【0029】

[断面構造]

図2は、実施の形態の表示装置の断面図である。図2に示すように、表示装置1は、第1パネル2と、第2パネル3と、液晶層30とを含む。第2パネル3は、第1パネル2と対向して配置される。液晶層30は、第1パネル2と第2パネル3との間に設けられる。第2パネル3の一主面たる表面が、画像を表示させるための表示面1aである。

【0030】

表示面1a側の外部から入射した光は、第1パネル2の副画素電極(反射電極)15によって反射されて表示面1aから出射する。実施の形態の表示装置1は、この反射光を利用して、表示面1aに画像を表示する反射型液晶表示装置である。なお、本明細書において、表示面1aと平行な方向をX方向とし、表示面1aと平行な面においてX方向と交差する方向をY方向とする。また、表示面1aに垂直な方向をZ方向とする。

【0031】

第1パネル2は、第1基板11と、絶縁層12と、副画素電極15と、配向膜18とを有する。第1基板11は、ガラス基板又は樹脂基板が例示される。第1基板11の表面には、図示しない回路素子や、走査線、データ線等の各種配線が設けられる。回路素子は、TFT(Thin Film Transistor)等のスイッチング素子や、容量素子を含む。

【0032】

絶縁層12は、第1基板11の上に設けられ、回路素子や各種配線等の表面を全体として平坦化している。副画素電極15は、絶縁層12の上に複数設けられる。配向膜18は、副画素電極15と液晶層30との間に設けられる。副画素電極15は、各副画素SPix毎に矩形状に設けられている。副画素電極15は、アルミニウム(A1)又は銀(Ag)

)で例示される金属で形成されている。また、副画素電極15は、これらの金属材料と、ITO(Indium Tin Oxide)で例示される透光性導電材料と、を積層した構成としても良い。副画素電極(反射電極)15は、良好な反射率を有する材料が用いられ、外部から入射する光を反射させる反射板として機能する。

【0033】

第2パネル3は、第2基板21と、カラーフィルタ22と、共通電極23と、配向膜28と、1/4波長板24と、1/2波長板25と、偏光板26とを含む。第2基板21の両面のうち、第1パネル2と対向する面に、カラーフィルタ22及び共通電極23が、この順で設けられる。共通電極23と液晶層30との間に配向膜28が設けられる。第2基板21の、表示面1a側の面に、1/4波長板24、1/2波長板25及び偏光板26が、この順で積層されている。

10

【0034】

第2基板21は、ガラス基板又は樹脂基板が例示される。共通電極23は、ITOで例示される透光性導電材料で形成されている。共通電極23は、複数の副画素電極15と対向して配置され、各副画素SPixに対する共通の電位を供給する。カラーフィルタ22は、R(赤)、G(緑)、及び、B(青)の3色のフィルタを有することが例示されるが、本開示はこれに限定されない。これらにW(白色)を加えることも可能である。また、カラーフィルタを用いない構成も採用可能である。この場合、副画素単位で画素を構成する。

20

【0035】

液晶層30は、ネマティック(Nematic)液晶を含んでいることが例示される。液晶層30は、共通電極23と副画素電極15との間の電圧レベル(電位差)が変更されることにより、液晶分子の配向状態が変化する。これによって、液晶層30を透過する光が副画素SPix毎に変調する。

20

【0036】

外光等が表示装置1の表示面1a側から入射する入射光となり、第2パネル3及び液晶層30を透過して副画素電極15に到達する。そして、入射光は各副画素SPixの副画素電極15で反射される。かかる反射光は、副画素SPix毎に変調されて表示面1aから出射される。これにより、画像の表示が行われる。

30

【0037】

[回路構成]

図3は、実施の形態の表示装置の画素内での副画素の配置を示す図である。画素PiXは、R(赤)の副画素SPixRと、G(緑)の副画素SPixGと、B(青)の副画素SPixBと、を含む。

【0038】

副画素SPixR、SPixG及びSPixBの各々は、メモリ51と、反転スイッチ61と、を含む。

【0039】

メモリ51は、1ビットのデータを格納するメモリセルとするが、本開示はこれに限定されない。メモリ51は、2ビット以上のデータを格納するメモリセルであっても良い。

40

【0040】

反転スイッチ61は、メモリ51と副画素電極15(図2参照)との間に電気的に接続されている。反転スイッチ61は、メモリ51から出力される副画素データに基づいて、反転駆動回路7から出力される表示信号又は反転表示信号を選択して、副画素電極15に出力する。表示信号FRP及び反転表示信号xFRPは、基準クロック信号CLKに同期して、反転される。

【0041】

表示信号が反転する周期は、共通電極23の電位(コモン電位)が反転する周期と同じである。

【0042】

50

反転スイッチ 6 1 が、本開示のスイッチ回路に対応する。

【0043】

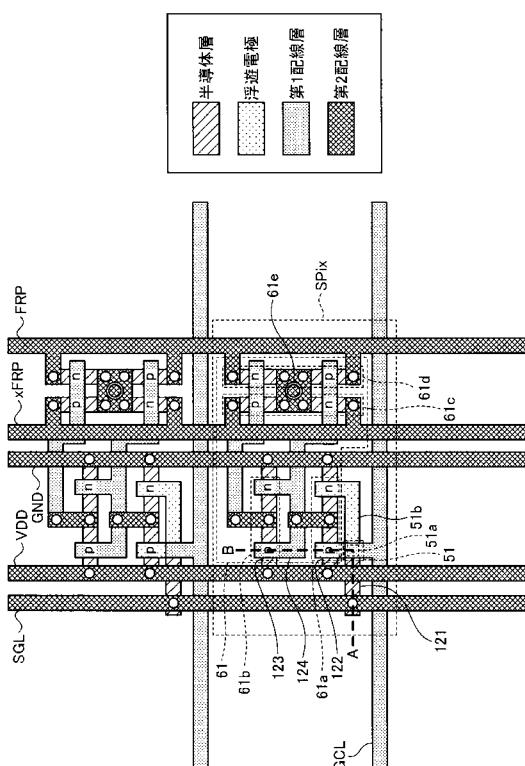

図 4 は、実施の形態の表示装置の回路構成を示す図である。図 4 では、M 行 × (N × 3) 列の副画素 S P i x の内の 2 × 2 個の副画素 S P i x を示している。

【0044】

副画素 S P i x は、メモリ 5 1 及び反転スイッチ 6 1 に加えて、液晶 L Q と、副画素電極 1 5 (図 2 参照) と、を含む。

【0045】

共通電極駆動回路 6 は、各副画素 S P i x に共通するコモン電位 V C O M を、基準クロック信号 C L K に同期して反転させて、共通電極 2 3 (図 2 参照) に出力する。共通電極駆動回路 6 は、基準クロック信号 C L K を共通電極 2 3 にそのままコモン電位 V C O M として出力しても良いし、電流駆動能力を増幅するバッファ回路を介して共通電極 2 3 にコモン電位 V C O M として出力しても良い。表示時のコモン電位 V C O M としては、例えば後述するように 3 V と 0 V といった一対の電圧が採用される。基準クロック信号 C L K に従って、一方の電圧から他方の電圧に反転し、これを繰り返すことで交流のコモン信号が形成され、共通電位線に供給される。

【0046】

走査線駆動回路 9 は、M 行の画素 P i x に対応して、M 個の出力端子を有している。走査線駆動回路 9 は、タイミングコントローラ 4 b から供給される制御信号 S i g 4 に基づいて、M 行の内の 1 つの行を選択するための走査信号を、M 個の出力端子から出力する。

【0047】

走査線駆動回路 9 は、制御信号 S i g 4 (スキャン開始信号及びクロックパルス信号) に基づいて、走査信号を M 個の出力端子から順次出力するスキャナ回路であっても良い。或いは、走査線駆動回路 9 は、符号化された制御信号 S i g 4 を復号化し、該制御信号 S i g 4 で指定された出力端子に走査信号を出力するデコーダ回路であっても良い。

【0048】

第 1 パネル 2 上には、M 行の画素 P i x に対応して、M 群の走査線群 G L 1 、 G L 2 、 · · · が配置されている。

【0049】

M 群の走査線群 G L 1 、 G L 2 、 · · · の各々は、当該行のメモリ 5 1 (図 3 参照) に電気的に接続された走査線 G C L a を含む。M 群の走査線群 G L 1 、 G L 2 、 · · · の各々は、表示領域 D A (図 1 参照) 内において、X 方向に沿う。

【0050】

第 1 パネル 2 上には、N × 3 列の副画素 S P i x に対応して、N × 3 本のデータ線 S G L 1 、 S G L 2 、 · · · が配置されている。各データ線 S G L 1 、 S G L 2 、 · · · の各々は、表示領域 D A (図 1 参照) 内において、Y 方向に沿う。データ線駆動回路 5 は、走査信号によって選択されている各副画素 S P i x のメモリに対して、データ線 S G L 1 、 S G L 2 、 · · · を介して、データ信号 (副画素データ) を夫々出力する。

【0051】

走査信号が供給された行の副画素 S P i x は、走査信号が供給された走査線 G C L に応じて、データ線 S G L に供給されている副画素データを、メモリ 5 1 に格納する。

【0052】

第 1 パネル 2 上には、M 行の画素 P i x に対応して、M 本の表示信号線 F R P 1 、 F R P 2 、 · · · が配置されている。M 本の表示信号線 F R P 1 、 F R P 2 、 · · · の各々は、表示領域 D A (図 1 参照) 内において、X 方向に延在している。なお、本実施の形態では、反転スイッチ 6 1 が、表示信号に加えて、表示信号を反転した反転表示信号とで動作する。従って、1 つの行当たり、表示信号線 F R P 及び反転表示信号線 × F R P が設けられる。

【0053】

1 つの行当たりに配置されている 1 本又は 2 本の表示信号線が、本開示の表示信号線に

対応する。

【0054】

反転駆動回路7は、スイッチSW<sub>1</sub>を含む。スイッチSW<sub>1</sub>は、タイミングコントローラ4bから供給される制御信号Sig<sub>1</sub>によって制御される。スイッチSW<sub>1</sub>は、制御信号Sig<sub>1</sub>が第1の値の場合には、基準クロック信号CLKを各表示信号線FRP<sub>1</sub>、FRP<sub>2</sub>、…に供給する。これにより、基準クロック信号CLKに同期して、副画素電極15の電位が反転する。スイッチSW<sub>1</sub>は、制御信号Sig<sub>1</sub>が第2の値の場合には、基準電位(接地電位)GNDを各表示信号線FRP<sub>1</sub>、FRP<sub>2</sub>、…に供給する。

【0055】

図5は、実施の形態の表示装置の副画素の回路構成を示す図である。図5では、1個の副画素SPixを示している。

【0056】

副画素SPixは、メモリ51と、反転スイッチ61と、液晶LQと、を含む。

【0057】

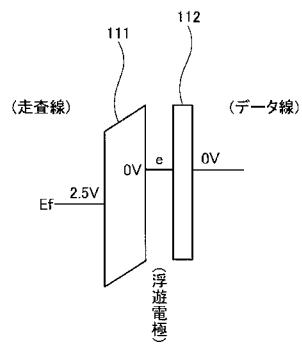

メモリ51は、コンデンサ51aを含む。更に、メモリ51は、コンデンサ51aの両端間に配置された浮遊電極51bを含む。メモリ51は、2個のコンデンサが直列接続されたものと考えることもできる。

【0058】

コンデンサ51aの一方端は、走査線GCL<sub>a</sub>に接続されている。コンデンサ51aの他方端は、データ線SGLに接続されている。

【0059】

メモリ51は、電子が浮遊電極51bから引き抜かれた状態で、副画素データ「0」を記憶する。一方、メモリ51は、電子が浮遊電極51bに注入された状態で、副画素データ「1」を記憶する。

【0060】

反転スイッチ61は、バッファ(インバータ)61aと、インバータ61bと、トランスマニアゲート61c及び61dと、を含む。

【0061】

バッファ61aの入力端子は、浮遊電極51bに接続されている。バッファ61aの出力端子は、インバータ61bの入力端子、トランスマニアゲート61cの非反転入力端子、及び、トランスマニアゲート61dの反転入力端子に接続されている。インバータ61bの出力端子は、トランスマニアゲート61cの反転入力端子及びトランスマニアゲート61dの非反転入力端子に接続されている。

【0062】

トランスマニアゲート61cは、バッファ61aの出力電圧がハイレベル、即ちメモリ51が副画素データ「1」を記憶している場合、反転表示信号線×FRP上の反転表示信号を副画素電極15に出力する。

【0063】

トランスマニアゲート61dは、バッファ61aの出力電圧がローレベル、即ちメモリ51が副画素データ「0」を記憶している場合、表示信号線FRP上の表示信号を副画素電極15に出力する。

【0064】

表示信号線FRPに供給される表示信号は、基準クロック信号CLKに同期して、反転する。共通電極23に供給されるコモン電位VCOMも、基準クロック信号CLKに同期して、表示信号と同相で、反転する。表示信号とコモン電位VCOMとが同相である場合、液晶LQは、電圧が印加されないので、液晶分子の方向が変化しない。これにより、副画素SPixは、黒表示(反射光を透過させない状態。反射光がカラーフィルタを透過せず、色が表示されない状態)となる。これにより、表示装置1は、コモン反転駆動方式を実現することができる。

【0065】

10

20

30

40

50

反転表示信号線  $\times$  F R P に供給される反転表示信号は、基準クロック信号 C L K に同期して、反転する。共通電極 2 3 に供給されるコモン電位 V C O M は、基準クロック信号 C L K に同期して、反転表示信号と異相で、反転する。反転表示信号とコモン電位 V C O M とが異相である場合、液晶 L Q は、電圧が印加されるので、液晶分子の方向が変化する。これにより、副画素 S P i x は、白表示（反射光を透過させる状態。反射光がカラーフィルタを透過して色が表示される状態）となる。これにより、表示装置 1 は、コモン反転駆動方式を実現することができる。

#### 【 0 0 6 6 】

##### [ 動作 ]

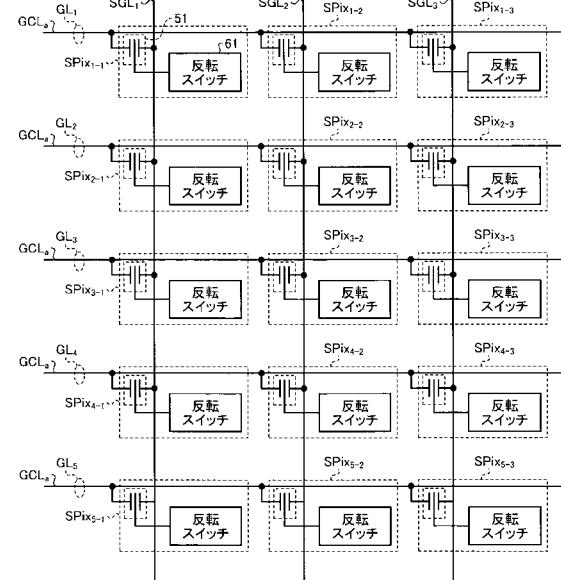

図 6 は、実施の形態の表示装置の副画素の構成を示す図である。図 6 では、M 行  $\times$  (N  $\times$  3) 列の副画素 S P i x の内の、5 行  $\times$  3 列の 15 個の副画素 S P i x を示している。図 6 では、表示信号線 F R P、反転表示信号線  $\times$  F R P 及び液晶 L Q の記載を省略している。

10

#### 【 0 0 6 7 】

各行の副画素 S P i x のメモリ 5 1 の一方端は、走査線 G C L a に接続されている。各列の副画素 S P i x のメモリ 5 1 の他方端は、データ線 S G L に接続されている。

20

#### 【 0 0 6 8 】

図 7 は、実施の形態の表示装置の副画素に書き込まれる副画素データを示す図である。図 8 - 1 及び図 8 - 2 は、実施の形態の表示装置の動作タイミングを示すタイミング図である。図 9 は、実施の形態の表示装置の各部の電位を示す図である。

20

#### 【 0 0 6 9 】

図 8 - 1 及び図 8 - 2 において、各副画素 S P i x の反転スイッチ 6 1 の入力電位（メモリ 5 1 の出力電位）を V i n とし、各副画素 S P i x の反転スイッチ 6 1 の出力電位を V p i x としている。

#### 【 0 0 7 0 】

図 6 から図 9 を参照して、表示装置 1 の動作について説明する。

#### 【 0 0 7 1 】

浮遊電極 5 1 b を有するメモリ 5 1 は、副画素データの書き込みの前に、消去が必要である。図 8 - 1、図 8 - 2 及び図 9 において、タイミング  $t_0$  からタイミング  $t_1$  までが、消去期間である。

30

#### 【 0 0 7 2 】

消去期間後のタイミング  $t_1$  からタイミング  $t_6$  までが、書き込み期間である。書き込み期間は、タイミング  $t_1$  からタイミング  $t_2$  までのステップ 1、タイミング  $t_2$  からタイミング  $t_3$  までのステップ 2、タイミング  $t_3$  からタイミング  $t_4$  までのステップ 3、タイミング  $t_4$  からタイミング  $t_5$  までのステップ 4、及び、タイミング  $t_5$  からタイミング  $t_6$  までのステップ 5 を含む。

#### 【 0 0 7 3 】

ステップ 1 は、第 1 行目の副画素 S P i x <sub>1 - 1</sub>、S P i x <sub>1 - 2</sub> 及び S P i x <sub>1 - 3</sub> への書き込み期間である。ステップ 2 は、第 2 行目の副画素 S P i x <sub>2 - 1</sub>、S P i x <sub>2 - 2</sub> 及び S P i x <sub>2 - 3</sub> への書き込み期間である。ステップ 3 は、第 3 行目の副画素 S P i x <sub>3 - 1</sub>、S P i x <sub>3 - 2</sub> 及び S P i x <sub>3 - 3</sub> への書き込み期間である。

40

#### 【 0 0 7 4 】

ステップ 4 は、第 4 行目の副画素 S P i x <sub>4 - 1</sub>、S P i x <sub>4 - 2</sub> 及び S P i x <sub>4 - 3</sub> への書き込み期間である。ステップ 5 は、第 5 行目の副画素 S P i x <sub>5 - 1</sub>、S P i x <sub>5 - 2</sub> 及び S P i x <sub>5 - 3</sub> への書き込み期間である。

#### 【 0 0 7 5 】

書き込み期間後のタイミング  $t_6$  からタイミング  $t_7$  までが、プリチャージ期間である。プリチャージ期間では、浮遊電極 5 1 b の電位を安定させる。

#### 【 0 0 7 6 】

プリチャージ期間後のタイミング  $t_7$  からタイミング  $t_9$  までが、読み出し期間である。

50

タイミング  $t_7$  からタイミング  $t_8$  までが、プラスフィールド期間である。タイミング  $t_8$  からタイミング  $t_9$  までが、マイナスフィールド期間である。

【0077】

図8-1、図8-2及び図9を参照すると、消去期間開始のタイミング  $t_0$  において、走査線駆動回路9は、走査線群  $GL_1$  から  $GL_5$  の走査線  $GCL_a$  に、0Vの走査信号を出力する。データ線駆動回路5は、データ線  $SGL_1$ 、 $SGL_2$  及び  $SGL_3$  に、20Vのデータ信号を出力する。

【0078】

従って、高電界(20V)が、全部の副画素  $SPix$  のメモリ51のコンデンサ  $S_{51a}$  の両端間に、印加される。これにより、トンネル効果によって、電子が、全部の副画素  $SPix$  のメモリ51の浮遊電極  $51b$  からデータ線  $SGL$  側に引き抜かれる。つまり、全部の副画素  $SPix$  のメモリ51は、副画素データ「0」(黒)を記憶する。

10

【0079】

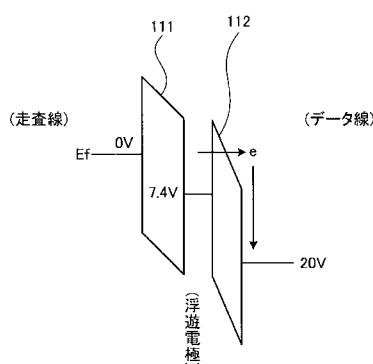

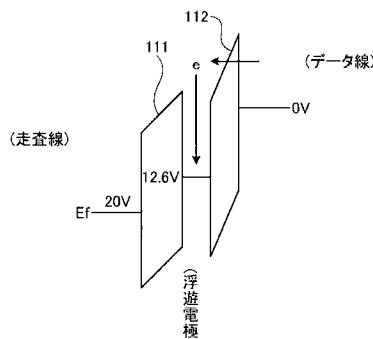

図10は、実施の形態の表示装置の副画素のメモリのエネルギーバンド図である。詳しくは、図10は、浮遊電極  $51b$  からデータ線  $SGL$  側に電子を引き抜く場合の、副画素  $SPix$  のメモリ51のエネルギーバンド図である。

20

【0080】

図10において、熱酸化膜である第1絶縁膜  $111$  の膜厚は、350オングストローム(35ナノメートル)、誘電率は、3(は、熱酸化膜の誘電率)とする。また、熱酸化膜である第2絶縁膜(トンネル酸化膜)  $112$  の膜厚は、200オングストローム(20ナノメートル)、誘電率は、とする。これらの数値は、特許文献3の数値を利用している。

20

【0081】

浮遊電極  $51b$  内の電子がトンネル効果によってデータ線  $SGL$  側に抜けるように、第2絶縁膜  $112$  に高電界がかかる条件が設定される。即ち、第2絶縁膜  $112$  の膜厚が、第1絶縁膜  $111$  の膜厚よりも薄く、且つ、第2絶縁膜  $112$  の誘電率が第1絶縁膜  $111$  の誘電率よりも低い(低容量側に高電圧がかかるため)条件にバランスされている。なお、走査線-データ線間の電位差が10Vの場合は、トンネル効果は発生しない。

30

【0082】

上記した数値を使用すると、第1絶縁膜  $111$  の静電容量  $C_2$  は、次の式(1)で表される。

$$C_2 = 3 / (350 \text{ オングストローム}) \quad \dots \quad (1)$$

【0083】

また、第2絶縁膜  $112$  の静電容量  $C_1$  は、次の式(2)で表される。

$$C_1 = / (200 \text{ オングストローム}) \quad \dots \quad (2)$$

【0084】

ここで、 $=1$  とすると、 $C_2 = 8571428.571$  (ファラッド)、 $C_1 = 500000$  (ファラッド)となる。

40

【0085】

従って、第1絶縁膜  $111$  の電圧  $V_2$  は、次の式(3)で表される。

$$V_2 = 20 \times C_1 / (C_1 + C_2) = 7.368421 \text{ (ボルト)} \quad \dots \quad (3)$$

【0086】

また、第2絶縁膜  $112$  の電圧  $V_1$  は、次の式(4)で表される。

$$V_1 = 20 \times C_2 / (C_1 + C_2) = 12.63158 \text{ (ボルト)} \quad \dots \quad (4)$$

【0087】

再び図8-1及び図8-2を参照すると、消去期間においては、全部の副画素  $SPix$  のメモリ51の浮遊電極  $51b$  の電位は、上記計算式のとおり7.4Vとなる。その結果、電子が、全部の副画素  $SPix$  のメモリ51の浮遊電極  $51b$  からデータ線  $SGL$  側に引き抜かれる。

50

【0088】

次に、書込み期間のステップ1の開始のタイミング  $t_1$ において、データ線駆動回路5は、データ線  $SGL_1$  に、0Vのデータ信号を出力する。また、データ線駆動回路5は、データ線  $SGL_2$  及び  $SGL_3$  に、10Vのデータ信号を出力する。

【0089】

タイミング  $t_1$  から待ち時間が経過した後、走査線駆動回路9は、走査線群  $GL_1$  の走査線  $GCL_a$  に、20Vの走査信号を出力する。また、走査線駆動回路9は、走査線群  $GL_2$  から  $GL_5$  の走査線  $GCL_a$  に、10Vの走査信号を出力する。

【0090】

従って、高電界(20V)が、副画素  $SPix_{1-1}$  のメモリ51のコンデンサ  $S51a$  の両端間に、印加される。このとき、副画素  $SPix_{1-1}$  のメモリ51の浮遊電極  $S51b$  の電位  $V_{in_{1-1}}$  は、12.6Vとなる。これにより、トンネル効果によって、電子が、データ線  $SGL_1$  側から、副画素  $SPix_{1-1}$  のメモリ51の浮遊電極  $S51b$  に、注入される。つまり、副画素  $SPix_{1-1}$  のメモリ51は、副画素データ「1」(白)を記憶する。

10

【0091】

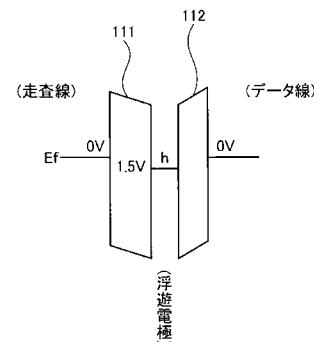

図11は、実施の形態の表示装置の副画素のメモリのエネルギーバンド図である。詳しくは、図11は、電子をデータ線  $SGL$  側からメモリ51のコンデンサ  $S51a$  の浮遊電極  $S51b$  に注入する場合の、副画素  $SPix$  のメモリ51のエネルギーバンド図である。

【0092】

再び図8-1及び図8-2を参照すると、高電界(20V)ではなく、10Vが、副画素  $SPix_{1-2}$  及び  $SPix_{1-3}$  のメモリ51のコンデンサ  $S51a$  の両端間に印加される。つまり、副画素  $SPix_{1-2}$  及び  $SPix_{1-3}$  のメモリ51は、副画素データ「0」(黒)を維持する。

20

【0093】

次に、書込み期間のステップ2の開始のタイミング  $t_2$ において、データ線駆動回路5は、データ線  $SGL_1$  及び  $SGL_3$  に、10Vのデータ信号を出力する。また、データ線駆動回路5は、データ線  $SGL_2$  に、0Vのデータ信号を出力する。

【0094】

タイミング  $t_2$  から待ち時間が経過した後、走査線駆動回路9は、走査線群  $GL_1$  並びに  $GL_3$  から  $GL_5$  の走査線  $GCL_a$  に、10Vの走査信号を出力する。また、走査線駆動回路9は、走査線群  $GL_2$  の走査線  $GCL_a$  に、20Vの走査信号を出力する。

30

【0095】

従って、高電界(20V)が、副画素  $SPix_{2-2}$  のメモリ51のコンデンサ  $S51a$  の両端間に、印加される。このとき、副画素  $SPix_{2-2}$  のメモリ51の浮遊電極  $S51b$  の電位  $V_{in_{2-2}}$  は、12.6Vとなる。これにより、トンネル効果によって、電子が、データ線  $SGL_2$  側から、副画素  $SPix_{2-2}$  のメモリ51の浮遊電極  $S51b$  に、注入される。つまり、副画素  $SPix_{2-2}$  のメモリ51は、副画素データ「1」(白)を記憶する。

【0096】

一方、高電界(20V)ではなく、10Vが、副画素  $SPix_{2-1}$  及び  $SPix_{2-3}$  のメモリ51のコンデンサ  $S51a$  の両端間に印加される。つまり、副画素  $SPix_{2-1}$  及び  $SPix_{2-3}$  のメモリ51は、副画素データ「0」(黒)を維持する。

40

【0097】

次に、書込み期間のステップ3の開始のタイミング  $t_3$ において、データ線駆動回路5は、データ線  $SGL_1$  及び  $SGL_3$  に、10Vのデータ信号を出力する。また、データ線駆動回路5は、データ線  $SGL_2$  に、0Vのデータ信号を出力する。

【0098】

タイミング  $t_3$  から待ち時間が経過した後、走査線駆動回路9は、走査線群  $GL_1$ 、 $GL_2$ 、 $GL_4$ 、及び、 $GL_5$  の走査線  $GCL_a$  に、10Vの走査信号を出力する。また、走査線駆動回路9は、走査線群  $GL_3$  の走査線  $GCL_a$  に、20Vの走査信号を出力する

50

。

## 【0099】

従って、高電界(20V)が、副画素 $SPi \times 3 \cdot 2$ のメモリ51のコンデンサ51aの両端間に、印加される。このとき、副画素 $SPi \times 3 \cdot 2$ のメモリ51の浮遊電極51bの電位 $V_{in} \cdot 3 \cdot 2$ は、12.6Vとなる。これにより、トンネル効果によって、電子が、データ線 $SGL_2$ 側から、副画素 $SPi \times 3 \cdot 2$ のメモリ51の浮遊電極51bに、注入される。つまり、副画素 $SPi \times 3 \cdot 2$ のメモリ51は、副画素データ「1」(白)を記憶する。

## 【0100】

一方、高電界(20V)ではなく、10Vが、副画素 $SPi \times 3 \cdot 1$ 及び $SPi \times 3 \cdot 3$ のメモリ51のコンデンサ51aの両端間に印加される。つまり、副画素 $SPi \times 3 \cdot 1$ 及び $SPi \times 3 \cdot 3$ のメモリ51は、副画素データ「0」(黒)を維持する。

## 【0101】

次に、書き込み期間のステップ4の開始のタイミング $t_4$ において、データ線駆動回路5は、データ線 $SGL_1$ から $SGL_3$ に、0Vのデータ信号を出力する。

## 【0102】

タイミング $t_4$ から待ち時間が経過した後、走査線駆動回路9は、走査線群 $GL_1$ から $GL_3$ 、及び、 $GL_5$ の走査線 $GCL_a$ に、10Vの走査信号を出力する。また、走査線駆動回路9は、走査線群 $GL_4$ の走査線 $GCL_a$ に、20Vの走査信号を出力する。

## 【0103】

従って、高電界(20V)が、副画素 $SPi \times 4 \cdot 1$ 、 $SPi \times 4 \cdot 2$ 、及び、 $SPi \times 4 \cdot 3$ のメモリ51のコンデンサ51aの両端間に、印加される。これにより、トンネル効果によって、電子が、データ線 $SGL_1$ 側から、副画素 $SPi \times 4 \cdot 1$ のメモリ51の浮遊電極51bに、注入される。同様に、電子が、データ線 $SGL_2$ 側から、副画素 $SPi \times 4 \cdot 2$ のメモリ51の浮遊電極51bに、注入される。同様に、電子が、データ線 $SGL_3$ 側から、副画素 $SPi \times 4 \cdot 3$ のメモリ51の浮遊電極51bに、注入される。つまり、副画素 $SPi \times 4 \cdot 1$ 、 $SPi \times 4 \cdot 2$ 、及び、 $SPi \times 4 \cdot 3$ のメモリ51は、副画素データ「1」(白)を記憶する。

## 【0104】

次に、書き込み期間のステップ5の開始のタイミング $t_5$ において、データ線駆動回路5は、データ線 $SGL_1$ 及び $SGL_3$ に、0Vのデータ信号を出力する。また、データ線駆動回路5は、データ線 $SGL_2$ に、10Vのデータ信号を出力する。

## 【0105】

タイミング $t_5$ から待ち時間が経過した後、走査線駆動回路9は、走査線群 $GL_1$ から $GL_4$ の走査線 $GCL_a$ に、10Vの走査信号を出力する。また、走査線駆動回路9は、走査線群 $GL_5$ の走査線 $GCL_a$ に、20Vの走査信号を出力する。

## 【0106】

従って、高電界(20V)が、副画素 $SPi \times 5 \cdot 1$ 、及び、 $SPi \times 5 \cdot 3$ のメモリ51のコンデンサ51aの両端間に、印加される。これにより、トンネル効果によって、電子が、データ線 $SGL_1$ 側から、副画素 $SPi \times 5 \cdot 1$ のメモリ51の浮遊電極51bに、注入される。同様に、電子が、データ線 $SGL_3$ 側から、副画素 $SPi \times 5 \cdot 3$ のメモリ51の浮遊電極51bに、注入される。つまり、副画素 $SPi \times 5 \cdot 1$ 、及び、 $SPi \times 5 \cdot 3$ のメモリ51は、副画素データ「1」(白)を記憶する。

## 【0107】

一方、高電界(20V)ではなく、10Vが、副画素 $SPi \times 5 \cdot 2$ のメモリ51のコンデンサ51aの両端間に印加される。つまり、副画素 $SPi \times 5 \cdot 2$ のメモリ51は、副画素データ「0」(黒)を維持する。

## 【0108】

次に、プリチャージ期間の開始のタイミング $t_6$ において、データ線駆動回路5は、データ線 $SGL_1$ から $SGL_3$ に、0Vのデータ信号を出力する。走査線駆動回路9は、走

10

20

30

40

50

査線群  $GL_1$  から  $GL_5$  の走査線  $GCL_a$  に、0Vの走査信号を出力する。

【0109】

図12は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth 図である。詳しくは、図12は、プリチャージ時の、副画素データ「0」(黒)を記憶している副画素  $SPix$  のメモリ51のエネルギー bandwidth 図である。プリチャージ時、副画素データ「0」(黒)を記憶している副画素  $SPix$  のメモリ51の浮遊電極51bの電位は、1.5Vになる。

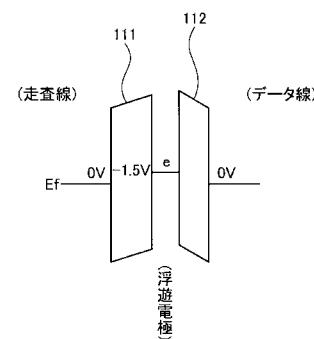

【0110】

図13は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth 図である。詳しくは、図13は、プリチャージ時の、副画素データ「1」(白)を記憶している副画素  $SPix$  のメモリ51のエネルギー bandwidth 図である。プリチャージ時、副画素データ「1」(白)を記憶している副画素  $SPix$  のメモリ51の浮遊電極51bの電位は、-1.5Vになる。

10

【0111】

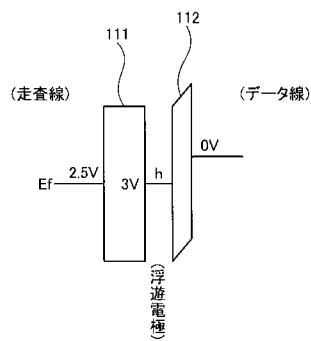

次に、プラスフィールド期間の開始のタイミング  $t_7$  において、データ線駆動回路5は、データ線  $SGL_1$  から  $SGL_3$  に、0Vのデータ信号を出力する。走査線駆動回路9は、走査線群  $GL_1$  から  $GL_5$  の走査線  $GCL_a$  に、2.5Vの走査信号を出力する。反転駆動回路7は、0Vの表示信号を表示信号線  $F RP$  に出力する。反転駆動回路7は、3Vの反転表示信号を反転表示信号線  $\times F RP$  に出力する。

20

【0112】

図14は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth 図である。詳しくは、図14は、読み出し時の、副画素データ「0」(黒)を記憶している副画素  $SPix$  のメモリ51のエネルギー bandwidth 図である。タイミング  $t_7$  において、走査線  $GCL$  に2.5Vの走査信号が出力されているので、メモリ51の浮遊電極51bの電位  $V_{in}$  が上昇している。読み出し時、副画素データ「0」(黒)を記憶している副画素  $SPix$  のメモリ51の浮遊電極51bの電位は、3Vになる。

30

【0113】

図15は、実施の形態の表示装置の副画素のメモリのエネルギー bandwidth 図である。詳しくは、図15は、読み出し時の、副画素データ「1」(白)を記憶している副画素  $SPix$  のメモリ51のエネルギー bandwidth 図である。タイミング  $t_7$  において、走査線  $GCL$  に2.5Vの走査信号が出力されているので、メモリ51の浮遊電極51bの電位  $V_{in}$  が上昇している。読み出し時、副画素データ「1」(白)を記憶している副画素  $SPix$  のメモリ51の浮遊電極51bの電位は、0Vになる。

30

【0114】

図16は、実施の形態の表示装置の副画素のメモリの浮遊電極の電位を示す図である。詳しくは、図16は、プリチャージ時及び読み出し時の、副画素  $SPix$  のメモリ51の浮遊電極51bの電位を示す図である。

40

【0115】

副画素データ「1」(白)を記憶している副画素  $SPix$  のメモリ51の電位は、プリチャージ時は-1.5Vになり、読み出し時は0Vになる。

【0116】

副画素データ「0」(黒)を記憶している副画素  $SPix$  のメモリ51の電位は、プリチャージ時は1.5Vになり、読み出し時は3Vになる。

【0117】

各副画素  $SPix$  は、浮遊電極51bの電位(0V又は3V)に基づいて、画像を表示する。

【0118】

タイミング  $t_7$  において、副画素  $SPix_{1-1}$  のメモリ51の浮遊電極51bの電位  $V_{in_{1-1}}$  は、0Vである。従って、副画素  $SPix_{1-1}$  の反転スイッチ61の出力電位  $V_{pix_{1-1}}$  は、3V( $\times F RP$ )である。また、共通電位  $V COM$  は、0Vであ

50

る。これにより、副画素  $S P i x_{1-1}$  では、液晶  $L Q$  に電圧が印加される。従って、副画素  $S P i x_{1-1}$  は、白を表示する。

【0119】

副画素  $S P i x_{4-1}$ 、 $S P i x_{5-1}$ 、 $S P i x_{2-2}$ 、 $S P i x_{3-2}$ 、 $S P i x_{4-2}$ 、 $S P i x_{4-3}$ 、及び、 $S P i x_{5-3}$  も、副画素  $S P i x_{1-1}$  と同様に、白を表示する。

【0120】

タイミング  $t_7$  において、副画素  $S P i x_{2-1}$  のメモリ  $51$  の浮遊電極  $51b$  の電位  $V_{in_{2-1}}$  は、 $3V$  である。従って、副画素  $S P i x_{2-1}$  の反転スイッチ  $61$  の出力電位  $V_{pix_{2-1}}$  は、 $0V$  ( $F R P$ ) である。また、共通電位  $V_{COM}$  は、 $0V$  である。これにより、副画素  $S P i x_{2-1}$  では、液晶  $L Q$  に電圧が印加されない。従って、副画素  $S P i x_{2-1}$  は、黒を表示する。

10

【0121】

副画素  $S P i x_{3-1}$ 、 $S P i x_{1-2}$ 、 $S P i x_{5-2}$ 、 $S P i x_{1-3}$ 、 $S P i x_{2-3}$ 、及び、 $S P i x_{3-3}$  も、副画素  $S P i x_{2-1}$  と同様に、黒を表示する。

【0122】

次に、マイナスフィールド期間の開始のタイミング  $t_8$  において、データ線駆動回路  $5$  は、データ線  $S G L_1$  から  $S G L_3$  を  $0V$  に維持する。走査線駆動回路  $9$  は、走査線群  $G L_1$  から  $G L_5$  の走査線  $G C L_a$  を  $2.5V$  に維持する。反転駆動回路  $7$  は、 $3V$  の表示信号を表示信号線  $F R P$  に出力する。反転駆動回路  $7$  は、 $0V$  の反転表示信号を反転表示信号線  $\times F R P$  に出力する。

20

【0123】

タイミング  $t_8$  において、副画素  $S P i x_{1-1}$  のメモリ  $51$  の浮遊電極  $51b$  の電位  $V_{in_{1-1}}$  は、 $0V$  である。従って、副画素  $S P i x_{1-1}$  の反転スイッチ  $61$  の出力電位  $V_{pix_{1-1}}$  は、 $0V$  ( $\times F R P$ ) である。また、共通電位  $V_{COM}$  は、 $3V$  である。これにより、副画素  $S P i x_{1-1}$  では、液晶  $L Q$  に電圧が印加される。従って、副画素  $S P i x_{1-1}$  は、白を表示する。

【0124】

副画素  $S P i x_{4-1}$ 、 $S P i x_{5-1}$ 、 $S P i x_{2-2}$ 、 $S P i x_{3-2}$ 、 $S P i x_{4-2}$ 、 $S P i x_{4-3}$ 、及び、 $S P i x_{5-3}$  も、副画素  $S P i x_{1-1}$  と同様に、白を表示する。

30

【0125】

タイミング  $t_8$  において、副画素  $S P i x_{2-1}$  のメモリ  $51$  の浮遊電極  $51b$  の電位  $V_{in_{2-1}}$  は、 $3V$  である。従って、副画素  $S P i x_{2-1}$  の反転スイッチ  $61$  の出力電位  $V_{pix_{2-1}}$  は、 $3V$  ( $F R P$ ) である。また、共通電位  $V_{COM}$  は、 $3V$  である。これにより、副画素  $S P i x_{2-1}$  では、液晶  $L Q$  に電圧が印加されない。従って、副画素  $S P i x_{2-1}$  は、黒を表示する。

【0126】

副画素  $S P i x_{3-1}$ 、 $S P i x_{1-2}$ 、 $S P i x_{5-2}$ 、 $S P i x_{1-3}$ 、 $S P i x_{2-3}$ 、及び、 $S P i x_{3-3}$  も、副画素  $S P i x_{2-1}$  と同様に、黒を表示する。

40

【0127】

なお、実施の形態では、浮遊電極  $51b$  の電位を安定させる、或いは、表示装置  $1$  の動作を判り易くするために、プリチャージ期間を設けたが、プリチャージ期間は無くても良い。即ち、書き込み期間の直後に読み出し期間を設けても良い。

【0128】

[副画素のレイアウト]

図  $17$  は、実施の形態の表示装置の副画素のレイアウトを示す図である。図  $17$  では、2 個の副画素  $S P i x$  を示している。

【0129】

副画素  $S P i x$  は、メモリ  $51$  と、反転スイッチ  $61$  と、を含む。反転スイッチ  $61$  は

50

、バッファ（インバータ）61aと、インバータ61bと、トランスファーゲート61c及び61dと、を含む。

【0130】

メモリ51は、半導体層と、第1配線層の配線と、第2配線層の配線と、で構成されている。

【0131】

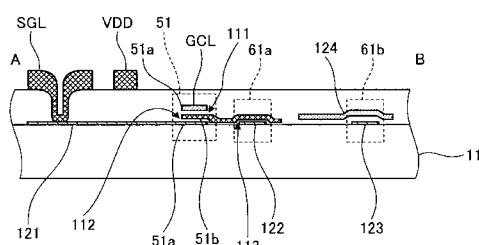

図18は、実施の形態の表示装置の副画素の断面図である。詳しくは、図18は、図17中のA-B線での断面図である。

【0132】

半導体層（多結晶シリコン（ポリシリコン））121の一端（図中左端）は、金属（導体）配線であるデータ線SGLに接続されている。半導体層121の他端（図中右端）の上層（図中上側）には、第2絶縁膜（トンネル酸化膜）112を介して、浮遊電極51bの一端（図中左端）が形成されている。浮遊電極51bの上層には、第1絶縁膜111を介して、金属（導体）配線である走査線GCLが形成されている。半導体層121と、走査線GCLとが、コンデンサ51aを構成する。コンデンサ51aと、浮遊電極51bとが、メモリ51を構成する。

【0133】

浮遊電極51bの他端（図中右端）は、半導体層122の上層まで延在している。半導体層122と、浮遊電極51bとの間には、絶縁膜（誘電体膜）113が形成されている。半導体層122と、浮遊電極51bとは、バッファ（インバータ）61aの一部を構成する。

【0134】

つまり、浮遊電極51bは、メモリ51と、バッファ（インバータ）61aとで、共用されている。

【0135】

半導体層123の上層には、金属配線124が形成されている。半導体層123と、金属配線124とは、インバータ61bの一部を構成する。

【0136】

インバータ61bに浮遊電極51bを直接接続すると、浮遊電極51bの負荷が大きい。例えば、浮遊電極51b 金属配線 インバータ61bのゲート電極の順にコンタクト接続すると、浮遊電極51bの負荷が大きい。

【0137】

そこで、実施の形態では、インバータ61bの前段に、バッファ（インバータ）61aを設けている。そして、バッファ（インバータ）61aのゲート電極は、浮遊電極51bそのものを用いている。これにより、浮遊電極51bの負荷を軽減できる。また、浮遊電極51bそのものをバッファ（インバータ）61aのゲート電極に用いることにより、絶縁膜（誘電体膜）113が薄くなり、浮遊電極51bがバッファ（インバータ）61aを駆動する駆動能力が上がる利点も得られる。

なお、本実施形態ではメモリ（コンデンサ）の一方電極として半導体層を採用しているが、当該一方電極として金属電極を採用することも可能である。

【0138】

図19は、実施の形態の表示装置の副画素のトランジスタ数と、特許文献2の表示素子のトランジスタ数と、を示す図である。

【0139】

反転スイッチ61に関して、本願の実施の形態の表示装置1と、特許文献2の表示素子とで、基本構成は同一である。しかしながら、特許文献2の表示素子（第7図参照）では、メモリセルの電位信号の反転信号もメモリ回路で生成されるので、インバータを必要としない。従って、特許文献2の表示素子では、反転スイッチのトランジスタ数は、4個（トランスファーゲート20及び21）である。一方、本願の実施の形態の表示装置1では、反転スイッチ61は、バッファ（インバータ）61a及びインバータ61b（図5参照

10

20

30

40

50

)を含む。従って、実施の形態の表示装置1では、反転スイッチ61のトランジスタ数は、8個(バッファ(インバータ)61a、インバータ61b、並びに、トランスファーゲート61c及び61d)である。

【0140】

メモリに関して、本願の実施の形態の表示装置1では、メモリ51のトランジスタ数は、0個である。一方、特許文献2の表示素子では、メモリのトランジスタ数は、6個(トランジスタ5及び6、並びに、インバータ14及び15)である。

【0141】

以上を累計すると、本願の実施の形態の表示装置1は、トランジスタ数が8個である。一方、特許文献2の表示素子は、トランジスタ数が10個である。

10

【0142】

このように、本願の実施の形態の表示装置1は、特許文献2の表示素子と比べて、トランジスタ数を削減することができる。これにより、本願の実施の形態の表示装置1は、回路規模を縮小でき、高精細化が可能である。

【0143】

また、表示装置1は、トランジスタ密度の低下により、異物等による短絡のリスクが低減され、歩留まりを向上することができる。

【0144】

また、SRAMを利用した従来のMIP型の表示装置では、副画素データを維持するためには、電源供給を維持する必要があった。一方、表示装置1は、電源供給が絶たれても、副画素データを維持することができる。これにより、表示装置1は、低消費電力化が可能である。

20

【0145】

実施の形態の表示装置は、電子看板又は電子棚札に適用すると好適である。その理由は、次の2点である。

【0146】

第1に、フラッシュメモリでは、半導体基板と浮遊電極との間に形成された第2絶縁膜(トンネル酸化膜)112は、電子が通過する都度、劣化する。つまり、第2絶縁膜(トンネル酸化膜)112は、副画素データが書き込まれる都度、劣化する。従って、フラッシュメモリは、書き換え回数に上限がある。

30

【0147】

実施の形態の表示装置をスマートフォンやパソコンコンピュータに適用すると、副画素データが副画素SPixに書き込まれる頻度が高く、装置寿命が短くなってしまう可能性が高い。従って、実施の形態の表示装置をスマートフォンやパソコンコンピュータに適用すると、装置寿命を考慮する必要がある。

【0148】

一方、電子看板又は電子棚札では、副画素データが副画素SPixに書き込まれるのは、広告内容又は告知内容の変更や、商品価格の変更や、商品入替などの場合である。従って、実施の形態の表示装置を電子看板又は電子棚札に適用すると、副画素データが副画素SPixに書き込まれる頻度が低く、装置寿命が短くなってしまう可能性が低い。従って、実施の形態の表示装置を電子看板又は電子棚札に適用すると、装置寿命を考慮する必要を、実質的に抑制できる。

40

【0149】

第2に、電子看板又は電子棚札では、広告内容又は告知内容の変更や、商品価格の変更や、商品入替などがあれば、同じ画像が何日間か繰り返して表示される可能性がある。もし、電子看板又は電子棚札にDRAMやSRAMなどの揮発性メモリを用いるとすると、たとえ前日までと同じ画像を表示する場合であっても、商品販売店の毎日の開店時刻前に、副画素データをDRAMやSRAMなどに書き込む必要がある。或いは、電子看板又は電子棚札に記憶保持用のバッテリを備えて、DRAMやSRAMなどに記憶されている、前日までの副画素データを保持する必要がある。

50

## 【0150】

一方、実施の形態の表示装置を電子看板又は電子棚札に適用すると、副画素 S P i x が不揮発性のフラッシュメモリを用いているので、前日までと同じ画像を表示する場合は、商品販売店の毎日の開店時刻前に、副画素データを副画素 S P i x に書込む必要がない。また、電子看板又は電子棚札に記憶保持用のバッテリを備える必要がない。従って、実施の形態の表示装置を電子看板又は電子棚札に適用すると、商品販売店の利便性を向上させることができる。

## 【0151】

以上、本発明の好適な実施の形態を説明したが、本発明はこのような実施の形態に限定されるものではない。実施の形態で開示された内容はあくまで一例にすぎず、本発明の趣旨を逸脱しない範囲で種々の変更が可能である。本発明の趣旨を逸脱しない範囲で行われた適宜の変更についても、当然に本発明の技術的範囲に属する。上述した各実施形態及び各変形例の要旨を逸脱しない範囲で、構成要素の種々の省略、置換及び変更のうち少なくとも1つを行うことができる。

10

## 【符号の説明】

## 【0152】

1 表示装置

1 a 表示面

2 第1パネル

3 第2パネル

20

4 インタフェース回路

4 a シリアル-パラレル変換回路

4 b タイミングコントローラ

4 c 設定レジスタ

5 データ線駆動回路

6 共通電極駆動回路

7 反転駆動回路

9 走査線駆動回路

1 1 第1基板

1 5 副画素電極(反射電極)

30

2 1 第2基板

2 3 共通電極

3 0 液晶層

5 1 メモリ

6 1 反転スイッチ

F R P 表示信号線

G L 走査線群

G C L 走査線

P i x 画素

S G L データ線

S P i x 副画素

x F R P 反転表示信号線

40

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

| 行 \ 列 | 第1列  | 第2列  | 第3列  |

|-------|------|------|------|

| 第1行   | 1(白) | 0(黒) | 0(黒) |

| 第2行   | 0(黒) | 1(白) | 0(黒) |

| 第3行   | 0(黒) | 1(白) | 0(黒) |

| 第4行   | 1(白) | 1(白) | 1(白) |

| 第5行   | 1(白) | 0(黒) | 1(白) |

【図8-1】

【図 8 - 2】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 1 4】

【図 1 6】

|                 | プリチャージ時 | 読み出し時 |

|-----------------|---------|-------|

| 副画素データ「1」(書き込み) | -1.5V   | 0V    |

| 副画素データ「0」(消去)   | 1.5V    | 3V    |

【図 1 5】

【図 1 7】

【図 1 8】

【図 1 9】

|         | 本願の実施の形態 | 特許文献2 |

|---------|----------|-------|

| トランジスタ数 | 反転スイッチ   | 8     |

|         | メモリ      | 0     |

| 総数      |          | 10    |

## フロントページの続き

| (51) Int.CI. | F I     | テーマコード(参考)   |

|--------------|---------|--------------|

|              | G 0 9 G | 3/20 6 2 1 B |

|              | G 0 9 G | 3/20 6 2 3 D |

|              | G 0 9 G | 3/20 6 1 1 A |

|              | G 0 9 G | 3/36         |

|              | G 0 9 G | 3/20 6 6 0 U |

|              | G 0 9 G | 3/3225       |

| F ターム(参考) | 5C006 | AA02 | AA22 | AC11 | AC21 | AC24 | AC25 | AC27 | AC28 | AF13 | AF25 |

|-----------|-------|------|------|------|------|------|------|------|------|------|------|

|           | AF33  | AF42 | AF43 | AF44 | AF51 | AF67 | AF69 | AF72 | BB16 | BB28 |      |

|           | BC02  | BC03 | BC06 | BC12 | BC22 | BC23 | BF16 | BF42 | EB04 | EC08 |      |

|           | FA33  | FA43 | FA47 | FA48 |      |      |      |      |      |      |      |

|           | 5C080 | AA06 | AA10 | BB05 | CC01 | CC03 | DD07 | DD22 | DD26 | DD28 | DD29 |

|           | EE01  | EE17 | EE30 | FF03 | FF11 | GG02 | GG11 | GG12 | JJ02 | JJ03 |      |

|           | JJ04  | JJ06 | KK04 | KK05 | KK07 | KK31 | KK34 |      |      |      |      |

|           | 5C380 | AA01 | AB06 | AB08 | AB09 | AB34 | AB36 | AC08 | AC11 | AC12 | AC16 |

|           | AC20  | BA01 | BA13 | BA29 | BC02 | BC03 | BC09 | BC13 | BD01 | BD10 |      |

|           | CA14  | CA53 | CA54 | CB01 | CB31 | CC24 | CC33 | CC57 | CE01 | CF05 |      |

|           | CF22  | CF23 | CF51 | CF62 | CF64 | DA32 | DA33 | DA35 | DA41 | DA47 |      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和电子招牌                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2020042191A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2020-03-19 |

| 申请号            | JP2018170052                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2018-09-11 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 石井達也                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 石井 達也                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/20 G02F1/1368 G02F1/1343 G09G3/36 G09G3/3225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/20.624.B G02F1/1368 G02F1/1343 G09G3/20.624.E G09G3/20.624.D G09G3/20.621.B G09G3/20.623.D G09G3/20.611.A G09G3/36 G09G3/20.660.U G09G3/3225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H092/GA59 2H092/GA60 2H092/JA24 2H092/JB21 2H092/JB42 2H092/JB63 2H092/JB66 2H092/JB68 2H092/PA06 2H092/RA10 2H192/AA24 2H192/BC72 2H192/CB23 2H192/CB24 2H192/DA81 2H192/EA43 2H192/FB02 2H192/FB27 2H192/GA42 2H192/GD61 2H192/JB01 5C006/AA02 5C006/AA22 5C006/AC11 5C006/AC21 5C006/AC24 5C006/AC25 5C006/AC27 5C006/AC28 5C006/AF13 5C006/AF25 5C006/AF33 5C006/AF42 5C006/AF43 5C006/AF44 5C006/AF51 5C006/AF67 5C006/AF69 5C006/AF72 5C006/BB16 5C006/BB28 5C006/BC02 5C006/BC03 5C006/BC06 5C006/BC12 5C006/BC22 5C006/BC23 5C006/BF16 5C006/BF42 5C006/EB04 5C006/EC08 5C006/FA33 5C006/FA43 5C006/FA47 5C006/FA48 5C080/AA06 5C080/AA10 5C080/BB05 5C080/CC01 5C080/CC03 5C080/DD07 5C080/DD22 5C080/DD26 5C080/DD28 5C080/DD29 5C080/EE01 5C080/EE17 5C080/EE30 5C080/FF03 5C080/FF11 5C080/GG02 5C080/GG11 5C080/GG12 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C080/KK04 5C080/KK05 5C080/KK07 5C080/KK31 5C080/KK34 5C380/AA01 5C380/AB06 5C380/AB08 5C380/AB09 5C380/AB34 5C380/AB36 5C380/AC08 5C380/AC11 5C380/AC12 5C380/AC16 5C380/AC20 5C380/BA01 5C380/BA13 5C380/BA29 5C380/BC02 5C380/BC03 5C380/BC09 5C380/BC13 5C380/BD01 5C380/BD10 5C380/CA14 5C380/CA53 5C380/CA54 5C380/CB01 5C380/CB31 5C380/CC24 5C380/CC33 5C380/CC57 5C380/CE01 5C380/CF05 5C380/CF22 5C380/CF23 5C380/CF51 5C380/CF62 5C380/CF64 5C380/DA32 5C380/DA33 5C380/DA35 5C380/DA41 5C380/DA47 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

### 摘要(译)

要解决的问题:提供一种能够实现低功耗和高清晰度的显示装置和电子招牌。显示装置包括在行方向和列方向上排列的多个子像素SPix,该子像素SPix除了存储器51和反转开关61之外还包括液晶LQ和子像素电极15。在图51中,具有被认为是串联连接的两个电容器的电容器51a,和被认为是串联连接的,配置在电容器之间的浮置电极51b,电容器51a的一端与扫描线GCLa连接,另一端连接到数据线SGL,并且多个子像素SPix基于浮动电极51b的电势显示图像。 [选择图]图5