(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-45704

(P2019-45704A)

(43) 公開日 平成31年3月22日(2019.3.22)

(51) Int.Cl.

G02F 1/1335 (2006.01)

G02F 1/1368 (2006.01)

F 1

G02F 1/1335

G02F 1/1368

テーマコード(参考)

2H192

2H291

審査請求 未請求 請求項の数 7 O L (全 14 頁)

(21) 出願番号

(22) 出願日特願2017-169110 (P2017-169110)

平成29年9月4日(2017.9.4)(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 梅田 博嗣

東京都千代田区丸の内二丁目7番3号 三菱

電機株式会社内

F ターム(参考) 2H192 AA24 BC63 CB05 CC04 CC24

CC62 EA22

2H291 FA14Y FD26 NA09 NA30

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】本発明は、表示品位の低下を抑えて低コスト化が可能な液晶表示装置を提供することを目的とする。

【解決手段】本発明による液晶表示装置は、行列状に配列された複数の画素電極と、各画素電極間の行方向に延設された複数の走査信号線3、4と、各画素電極間の列方向であって2列ごとに延設された複数の映像信号線5と、各画素電極上であって、平面視において各画素電極間の行方向および列方向に配置された遮光層22とを備え、各画素電極は、列方向に並んで設けられた、光を反射する反射領域部18と、光を透過する透過領域部19とを有し、遮光層22は、平面視において映像信号線5と重畳する遮光領域部23と、列方向であって平面視において映像信号線5と重畳しない遮光領域部24とを有し、各画素電極の反射領域部18間ににおける遮光領域部24の幅は、各画素電極の透過領域部19間ににおける遮光領域部23の幅よりも小さい。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

行列状に配列された複数の画素電極と、

各前記画素電極間の行方向に延設された複数の走査信号線と、

各前記画素電極間の列方向であって2列ごとに延設された複数の映像信号線と、

前記各画素電極上であって、平面視において各前記画素電極間の前記行方向および前記列方向に配置された遮光層と、

を備え、

各前記画素電極は、前記列方向に並んで設けられた、光を反射する反射領域部と、光を透過する透過領域部とを有し、

前記遮光層は、平面視において前記映像信号線と重畳する第1遮光領域部と、前記列方向であって平面視において前記映像信号線と重畳しない第2遮光領域部とを有し、

各前記画素電極の前記反射領域部間における前記第2遮光領域部の幅は、各前記画素電極の前記透過領域部間における前記第1遮光領域部の幅よりも小さいことを特徴とする、液晶表示装置。

**【請求項 2】**

前記透過領域部間において、前記第1遮光領域部の幅と前記第2遮光領域部の幅とは同じであり、

前記反射領域部間において、前記第2遮光領域部の幅は、前記第1遮光領域部の幅よりも小さいことを特徴とする、請求項1に記載の液晶表示装置。

**【請求項 3】**

前記反射領域部間における前記第2遮光領域部の幅は、少なくとも平面視において前記第2遮光領域部を挟んで隣接する各前記画素電極に対応する色が混色しない幅であることを特徴とする、請求項1に記載の液晶表示装置。

**【請求項 4】**

前記透過領域部間における前記第2遮光領域部の幅は、前記反射領域部間における前記第2遮光領域部の幅と同じであり、

前記透過領域部間における前記第2遮光領域部を挟んで隣接する各前記画素電極の前記反射領域部は、前記透過領域部間における前記第2遮光領域部に沿って前記透過領域部側に延設され、かつ当該延設された前記反射領域部と前記透過領域部との境界は、前記反射領域部間における前記第2遮光領域部から平面視で突出し、

前記透過領域部間における前記第1遮光領域部の幅は、前記透過領域部間における前記第2遮光領域部を挟んで隣接する各前記境界間の距離と同じであることを特徴とする、請求項1に記載の液晶表示装置。

**【請求項 5】**

行列状に配列された複数の画素電極と、

各前記画素電極間の行方向に延設された複数の走査信号線と、

各前記画素電極間の列方向であって2列ごとに延設された複数の映像信号線と、

前記各画素電極上であって、平面視において各前記画素電極間の前記行方向および前記列方向に配置された遮光層と、

を備え、

各前記画素電極は、前記列方向に並んで設けられた、光を反射する反射領域部と、光を透過する透過領域部とを有し、

前記遮光層は、平面視において前記映像信号線と重畳する第1遮光領域部と、前記列方向であって平面視において前記映像信号線と重畳しない第2遮光領域部とを有し、

各前記画素電極の前記透過領域部間において、前記第1遮光領域部の幅と前記第2遮光領域部の幅とは同じであり、

各前記画素電極の前記反射領域部間において、前記第1遮光領域部の幅と前記第2遮光領域部の幅とは同じであり、

前記反射領域部間における前記第1遮光領域部および前記第2遮光領域部の幅は、前記

10

20

30

40

50

透過領域部間における前記第1遮光領域部および前記第2遮光領域部の幅よりも小さいことを特徴とする、液晶表示装置。

【請求項6】

行列状に配列された複数の画素電極と、

各前記画素電極間の行方向に延設された複数の走査信号線と、

各前記画素電極間の列方向であって2列ごとに延設された複数の映像信号線と、

前記各画素電極上であって、平面視において各前記画素電極間の前記行方向および前記列方向に配置された遮光層と、

を備え、

各前記画素電極は、前記列方向に並んで設けられた、光を反射する反射領域部と、光を透過する透過領域部とを有し、

前記遮光層は、平面視において前記映像信号線と重畳する第1遮光領域部と、前記列方向であって平面視において前記映像信号線と重畳しない第2遮光領域部とを有し、

前記第1遮光領域部の幅は、前記第2遮光領域部の幅と同じであり、

各前記画素電極の前記反射領域部は、前記第1遮光領域部および前記第2遮光領域部に沿って前記透過領域部側に延設され、かつ当該延設された前記反射領域部と前記透過領域部との境界は、前記反射領域部間における前記第1遮光領域部および前記第2遮光領域部から平面視で突出し、

前記透過領域部間における前記第1遮光領域部を挟んで隣接する各前記境界間の距離は、前記透過領域部間における前記第2遮光領域部を挟んで隣接する各前記境界間の距離と同じであることを特徴とする、液晶表示装置。

【請求項7】

少なくとも各前記映像信号線を覆う有機樹脂膜をさらに備え、

各前記画素電極は、前記有機樹脂膜上であって、平面視において一部が各前記映像信号線と重畳していることを特徴とする、請求項5または6に記載の液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置に関し、特に、2倍走査線方式の半透過液晶表示装置に関する。

【背景技術】

【0002】

液晶表示装置の一つとして、屋外での視認性を向上させるために、1つの画素内に光を反射する反射領域部と、光を透過する透過領域部とを備える半透過液晶表示装置がある。また、液晶表示装置に適用可能な技術として2倍走査線方式と呼ばれる技術がある（例えば、特許文献1参照）。2倍走査線方式の液晶表示装置は、行列状に配置された複数の画素と、2つの画素ごとに列方向に延設された映像信号線と、行方向に配置された各画素を挟むように行方向に2本ずつ延設された走査信号線とを備え、行方向に配置された各画素は、交互に異なる走査信号線に接続されている。このような構成とすることによって、2倍走査線方式の液晶表示装置では、1本の映像信号線に対して2つの画素が配置されるため、1画素あたりの映像信号線の本数を半減することができ、映像信号線に信号を供給するIC（Integrated Circuit）チップなどの部品点数を削減することができる。従って、液晶表示装置全体の低コスト化を図ることができる。

【0003】

2倍走査線方式の液晶表示装置では、1本の映像信号線に対して2つの画素が配置されるため、隣接する画素間に映像信号線が配置されていない領域が存在する。当該領域では、映像信号線の近傍で発生する電界漏れ、または液晶の配向不良などによる液晶層からの光漏れを遮光する必要がない。従って、隣接する画素間に映像信号線が延設されていない領域に対応して配置される遮光層の幅は、隣接する画素間に映像信号線が延設されている領域に対応して配置される遮光層の幅よりも小さくなる傾向にある。しかし、このような

10

20

30

40

50

構成では、列方向に明暗のスジが視認されるという問題がある。

【0004】

上記の問題の対策として、従来、隣接する画素間に映像信号線が延設されている領域に対応して配置される遮光層の幅と、隣接する画素間に映像信号線が延設されていない領域に対応して配置される遮光層の幅とを同じにする構成が開示されている（例えば、特許文献2参照）。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007-219524号公報

10

【特許文献2】特開2006-79104号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献2では、隣接する画素間に映像信号線が延設されていない領域が、当該領域に対応して配置される遮光層によって必要以上に遮光される。従って、特許文献2の技術を半透過液晶表示装置に適用した場合、画素内の反射領域部および透過領域部の開口率が低くなるため、反射領域部の反射率が低下するとともに、透過領域部の透過率が低下するという問題がある。すなわち、表示品位が低下するという問題がある。また、反射領域部の反射率が低下しないように反射領域部に対応する遮光層の開口面積を大きくした場合は、それに伴って透過領域部に対応する遮光層の開口面積が小さくなつて透過領域部の輝度が低下する。当該輝度の低下を防ぐためにはバックライトの輝度を上げる必要があり、そのためにはバックライトであるLED（Light Emitting Diode）の数を増やす、またはバックライトの消費電力を増やさなければならない。これは、液晶表示装置のコストアップにつながるとともに、消費電力が増加するため省エネルギー化に反することになる。

20

【0007】

本発明は、このような問題を解決するためになされたものであり、表示品位の低下を抑えて低コスト化が可能な液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

30

上記の課題を解決するために、本発明による液晶表示装置は、行列状に配列された複数の画素電極と、各画素電極間の行方向に延設された複数の走査信号線と、各画素電極間の列方向であつて2列ごとに延設された複数の映像信号線と、各画素電極上であつて、平面視において各画素電極間の行方向および列方向に配置された遮光層とを備え、各画素電極は、列方向に並んで設けられた、光を反射する反射領域部と、光を透過する透過領域部とを有し、遮光層は、平面視において映像信号線と重畳する第1遮光領域部と、列方向であつて平面視において映像信号線と重畳しない第2遮光領域部とを有し、各画素電極の反射領域部間における第2遮光領域部の幅は、各画素電極の透過領域部間における第1遮光領域部の幅よりも小さい。

40

【発明の効果】

【0009】

本発明によると、液晶表示装置は、行列状に配列された複数の画素電極と、各画素電極間の行方向に延設された複数の走査信号線と、各画素電極間の列方向であつて2列ごとに延設された複数の映像信号線と、各画素電極上であつて、平面視において各画素電極間の行方向および列方向に配置された遮光層とを備え、各画素電極は、列方向に並んで設けられた、光を反射する反射領域部と、光を透過する透過領域部とを有し、遮光層は、平面視において映像信号線と重畳する第1遮光領域部と、列方向であつて平面視において映像信号線と重畳しない第2遮光領域部とを有し、各画素電極の反射領域部間における第2遮光領域部の幅は、各画素電極の透過領域部間における第1遮光領域部の幅よりも小さいため、表示品位の低下を抑えて低コスト化が可能となる。

50

**【図面の簡単な説明】****【0010】**

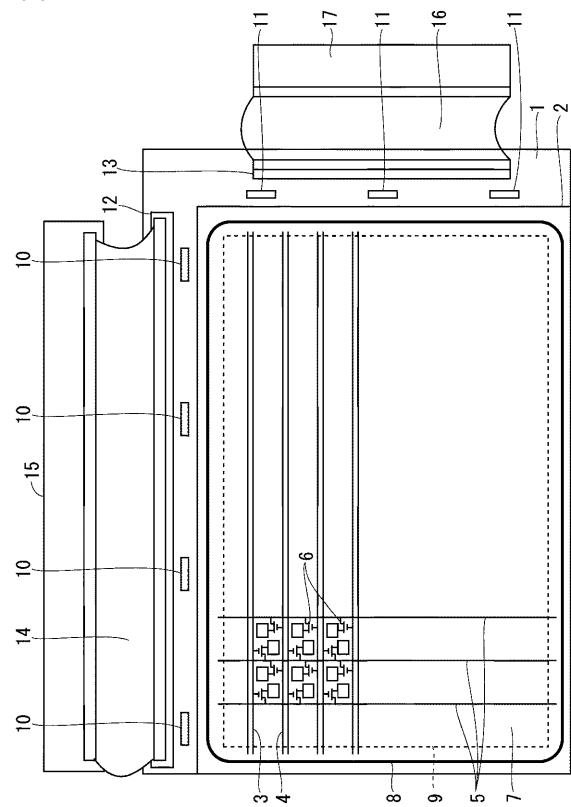

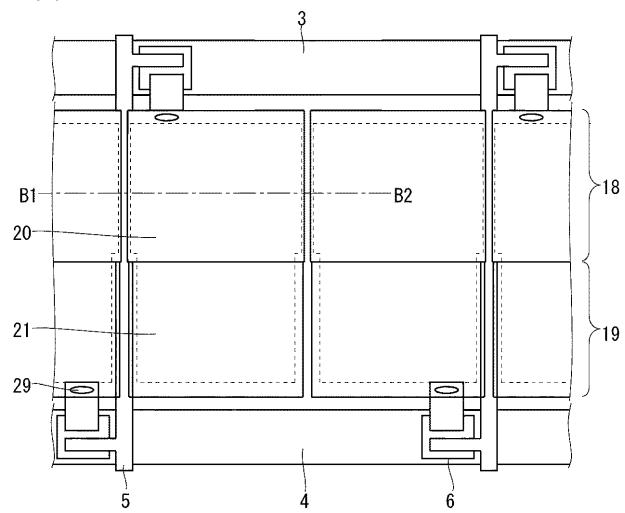

【図1】本発明の実施の形態1による液晶表示装置の全体的な構成の一例を示す平面図である。

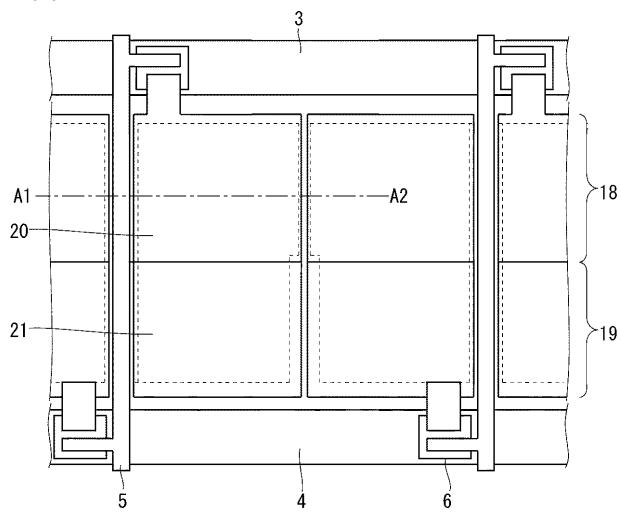

【図2】本発明の実施の形態1によるアレイ基板の構成の一例を示す平面図である。

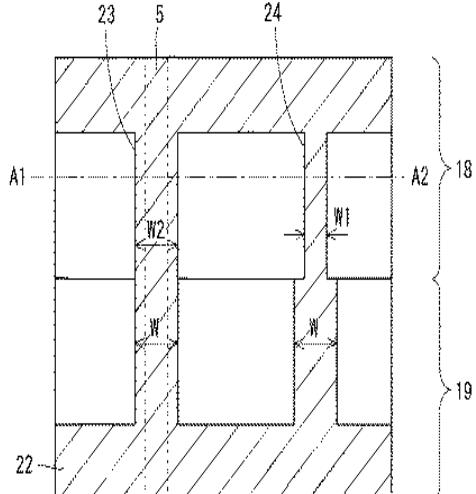

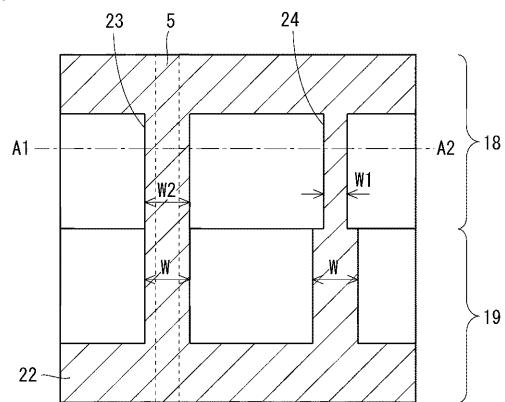

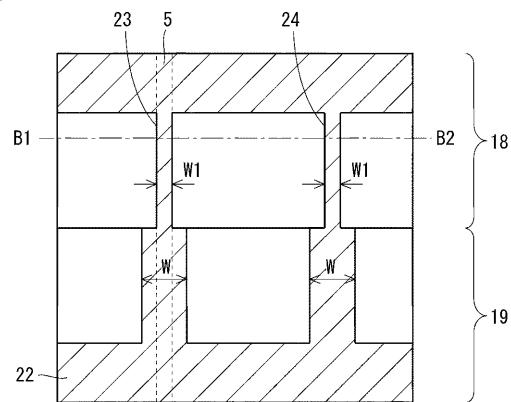

【図3】本発明の実施の形態1による遮光層の構成の一例を示す平面図である。

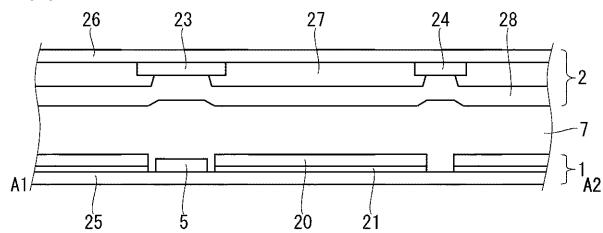

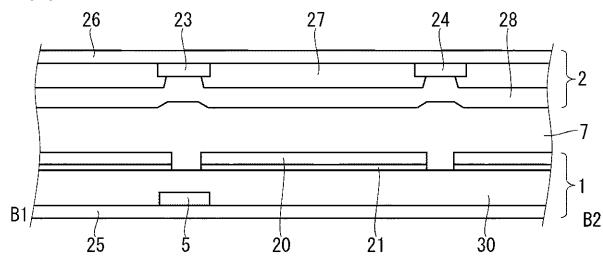

【図4】図2, 3のA1-A2断面を示す図である。

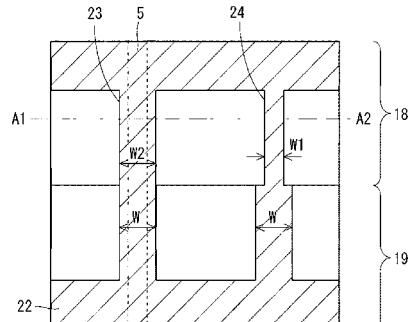

【図5】本実施の形態1の変形例による遮光層の構成の一例を示す平面図である。

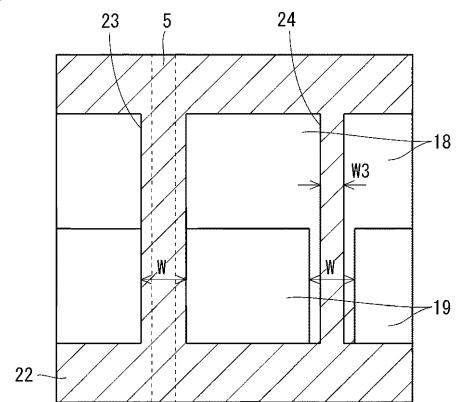

【図6】本発明の実施の形態1の変形例によるアレイ基板の構成の一例を示す平面図である。

10

【図7】本発明の実施の形態2によるアレイ基板の構成の一例を示す平面図である。

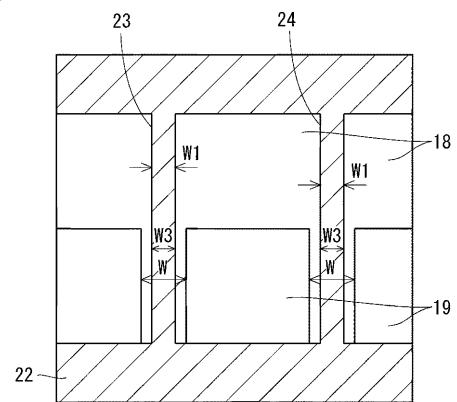

【図8】本発明の実施の形態2による遮光層の構成の一例を示す平面図である。

【図9】図7, 8のB1-B2断面を示す図である。

【図10】本発明の実施の形態2の変形例による遮光層の構成の一例を示す平面図である。

【図11】前提技術による液晶表示装置の構成の一例を示す図である。

【図12】前提技術による遮光層の構成の一例を示す平面図である。

**【発明を実施するための形態】****【0011】**

本発明の実施の形態について、図面に基づいて以下に説明する。

20

**【0012】****<前提技術>**

本発明の前提となる技術である前提技術について説明する。

**【0013】**

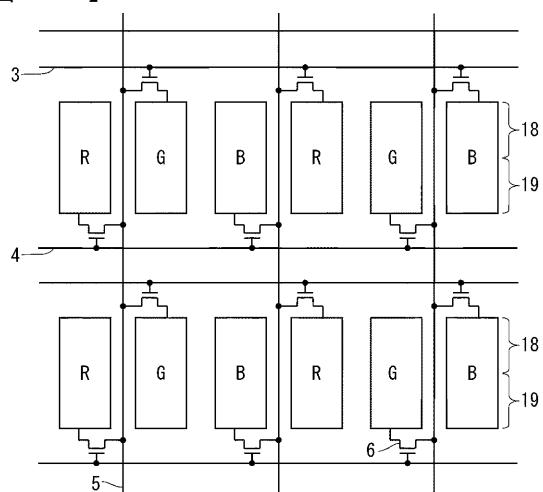

図11は、前提技術による液晶表示装置の構成の一例を示す図であり、より具体的には2倍走査線方式の半透過液晶表示装置の構成の模式的な回路図を示している。なお、図11では、半透過液晶表示装置の一部を示している。

**【0014】**

図11に示すように、R(赤)、G(緑)、およびB(青)の各画素が行列状に配置されている。走査信号線3, 4は、x方向である行方向に配置された複数の画素を挟むようにそれぞれ行方向に延設されている。映像信号線5は、2画素ごとにy方向である列方向に延設されている。各画素の画素電極は、列方向に並んで設けられた反射領域部18と透過領域部19とを有している。

30

**【0015】**

TFT (Thin Film Transistor) 6は、各画素に配置されており、ゲート電極が走査信号線3または走査信号線4に接続され、ソース電極が映像信号線5に接続され、ドレイン電極が画素電極に接続されている。映像信号線5を挟んで配置されている2つの画素に注目すると、各画素のTFT 6のソース電極は共通の映像信号線5に接続され、各画素のTFT 6のゲート電極は互いに異なる走査信号線3, 4に接続されている。すなわち、行方向に配置された各画素のTFT 6のゲート電極は、交互に走査信号線3, 4に接続されている。

40

**【0016】**

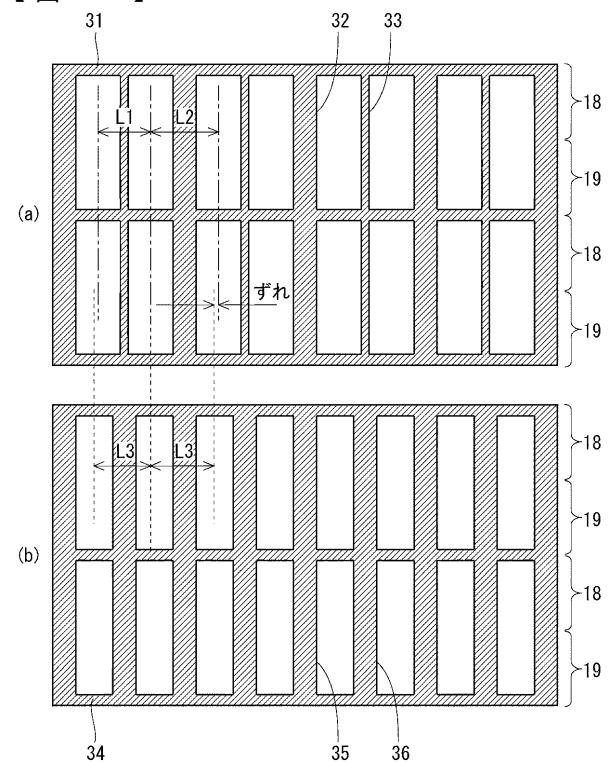

図12は、遮光層31, 34の構成の一例を示す平面図である。図12(a)は、遮光領域部33の幅が遮光領域部32の幅よりも小さい遮光層31のパターンを示している。図12(b)は、遮光領域部35の幅と遮光領域部36の幅とが同じである遮光層34のパターンを示している。

**【0017】**

図12(a)に示すように、遮光層31は、図11に示す各画素に対応する位置に開口部を有している。遮光層31の一部である遮光領域部32は、隣接する画素間に映像信号線5が延設されている領域に対応して配置されている。遮光層31の一部である遮光領域

50

部33は、隣接する画素間に映像信号線5が延設されていない領域に対応して配置されている。なお、図12(a)に示す一点鎖線は、遮光層31の開口部の中心を列方向に通る中心線である。幅L1は、遮光領域部33を挟んで隣接する各開口部の中心線の間隔である。幅L2は、遮光領域部32を挟んで隣接する各開口部の中心線の間隔である。

【0018】

図12(b)に示すように、遮光層34は、図11に示す各画素に対応する位置に開口部を有している。遮光層34の一部である遮光領域部35は、隣接する画素間に映像信号線5が延設されている領域に対応して配置されている。遮光層34の一部である遮光領域部36は、隣接する画素間に映像信号線5が延設されていない領域に対応して配置されている。なお、図12(b)に示す破線は、遮光層34の開口部の中心を列方向に通る中心線である。幅L3は、遮光領域部35または遮光領域部36を挟んで隣接する各開口部の中心線の間隔である。

10

【0019】

図12(b)に示す遮光層34のパターンでは、遮光層34の各開口部間が幅L3の等間隔であるため、列方向に明暗のスジが視認されることはない。一方、図12(a)に示す遮光層31のパターンでは、遮光層31の各開口部間が幅L1および幅L2と幅が異なる。従って、図12(b)に示す遮光層34のパターンと比較して、開口部の中心線が、隣接する画素間に映像信号線5が延設されていない領域の方向にずれる。その結果、列方向に明暗のスジが視認される。

20

【0020】

なお、上記説明した明暗のスジが視認されるか否かに関わる遮光層31の開口部の中心を列方向に通る中心線、あるいは遮光層34の開口部の中心を列方向に通る中心線の位置については、遮光層31の開口部あるいは遮光層34の開口部が矩形でない場合には、これら開口部における重心位置を開口部の中心に読み替えて、当該開口部の中心を列方向に通る中心線と解釈すればよく、明暗のスジが視認されるか否かについて同様の関係性となる。

20

【0021】

上述の通り、列方向に視認される明暗のスジを防ぐためには、図12(b)に示すような遮光層のパターンとすればよい。しかし、このような遮光層のパターンでは、必要以上に遮光するため表示品位が低下するという問題がある。また、コストアップ等の問題もある。本発明は、このような問題を解決するためになされたものであり、以下に詳細に説明する。

30

【0022】

<実施の形態1>

図1は、本発明の実施の形態1による液晶表示装置の全体的な構成の一例を示す平面図である。図2は、アレイ基板1の構成の一例を示す平面図である。図3は、遮光層22の構成の一例を示す平面図である。図4は、図2, 3のA1-A2断面を示す図である。なお、以下では、本実施の形態1による液晶表示装置は、2倍走査線方式の半透過液晶表示装置であるものとして説明する。図2は、アレイ基板1の一部を示している。

30

【0023】

図1に示すように、本実施の形態1による液晶表示装置は、アレイ基板1と、カラーフィルタ基板2と、液晶層7と、シール材8とを備えている。これらは、液晶表示パネルを構成している。

40

【0024】

アレイ基板1は、行列状に配列された複数の画素電極と、各画素電極間の行方向に延設された複数の走査信号線3, 4と、各画素電極間の列方向であって2列ごとに延設された複数の映像信号線5と、各画素電極に配置されたTFT6とを備えている。これらの構成は、既に説明した図11に示す構成と同様であるため、ここでは詳細な説明は省略する。各画素電極は、図11に示すR、G、およびBの各画素に対応して配置されている。図2に示すように、画素電極は、反射画素電極20と透過画素電極21とから構成され、TFT

50

T 6 に接続されている。反射画素電極 2 0 が形成されている領域は、上記で説明した反射領域部 1 8 に対応している。透過画素電極 2 1 が形成されている領域は、上記で説明した透過領域部 1 9 に対応している。

【0025】

なお、反射画素電極 2 0 および透過画素電極 2 1 の構成は、公知の構成でよい。例えば、透過画素電極 2 1 は、ITO (Indium Tin Oxide) 膜などの一般的な透明導電膜の単層で構成してもよい。また、反射画素電極 2 0 は、例えば、一般的な反射電極膜となるAl 膜の単層、またはAl 膜を表層としMo 等のコンタクト層を下層とした多層で構成してもよい。図4に示すように、本実施の形態1では、反射領域部 1 8 において反射画素電極 2 0 の下層に透過画素電極 2 1 が配置された構成となっている。

10

【0026】

カラーフィルタ基板 2 は、図示しないカラーフィルタを備えており、アレイ基板 1 と対向して配置されている。シール材 8 は、アレイ基板 1 とカラーフィルタ基板 2 との間に設けられている。液晶層 7 は、アレイ基板 1 、カラーフィルタ基板 2 、およびシール材 8 に囲まれる間隙に密封されている。液晶層 7 が存在する領域は、表示領域 9 に対応している。

【0027】

アレイ基板 1 の外形は、カラーフィルタ基板 2 の外形よりも大きく、平面視においてアレイ基板 1 の一部がカラーフィルタ基板 2 の端部から突出している。当該突出部には、駆動ICチップ 1 0 , 1 1 および信号端子 1 2 , 1 3 が配置されている。駆動ICチップ 1 0 , 1 1 は、各 TFT 6 に信号を供給するために、走査信号線 3 , 4 および映像信号線 5 に接続されている。

20

【0028】

信号端子 1 2 は、接続配線であるFFC (Flexible Flat Cable) 1 4 を介して制御基板 1 5 に接続されている。また、信号端子 1 2 は、駆動ICチップ 1 0 にも接続されている。制御基板 1 5 は、駆動ICチップ 1 0 を制御する制御信号などを生成する制御ICチップなどを備えている。制御基板 1 5 から出力された制御信号は、FFC 1 4 および信号端子 1 2 を介して駆動ICチップ 1 0 に入力される。駆動ICチップ 1 0 は、制御基板 1 5 から入力された制御信号に基づいて映像信号または走査信号である出力信号を生成して出力する。駆動ICチップ 1 0 から出力された出力信号は、図示しない複数の信号引き出し配線を介してTFT 6 に供給される。

30

【0029】

信号端子 1 3 は、FFC 1 6 を介して制御基板 1 7 に接続されている。また、信号端子 1 3 は、駆動ICチップ 1 1 にも接続されている。制御基板 1 7 は、駆動ICチップ 1 1 を制御する制御信号などを生成する制御ICチップなどを備えている。制御基板 1 7 から出力された制御信号は、FFC 1 6 および信号端子 1 3 を介して駆動ICチップ 1 1 に入力される。駆動ICチップ 1 1 は、制御基板 1 7 から入力された制御信号に基づいて映像信号または走査信号である出力信号を生成して出力する。駆動ICチップ 1 1 から出力された出力信号は、図示しない複数の信号引き出し配線を介してTFT 6 に供給される。

40

【0030】

上述の通り、本実施の形態1による液晶表示装置は、2倍走査線方式を用いている。従って、映像信号線 5 の本数が2倍走査線方式を用いない液晶表示装置に比べて半減するため、映像信号線に映像信号を供給する駆動ICチップの数も2倍走査線方式を用いない液晶表示装置に比べて半減する。

【0031】

図2, 4に示すように、アレイ基板 1 において、映像信号線 5 と、反射画素電極 2 0 および透過画素電極 2 1 からなる画素電極とは、平面視で重疊せず離間して配置されている。

【0032】

図3, 4に示すように、カラーフィルタ基板 2 には、アレイ基板 1 に設けられた走査信

50

号線 3 , 4 、映像信号線 5 、および TFT 6 と平面視で重畳するように遮光層 22 が配置されている。遮光層 22 は、映像信号線 5 の近傍で発生する電界漏れ、または液晶の配向不良などによる液晶層からの光漏れを遮光するために配置され、ブラックマスクまたはブラックマトリクスとも呼ばれる。第 1 遮光領域部である遮光領域部 23 は、遮光層 22 のうち平面視において映像信号線 5 と重畳する部分である。第 2 遮光領域部である遮光領域部 24 は、遮光層 22 のうち列方向であって平面視において映像信号線 5 と重畳しない部分である。遮光層 22 は、例えば、酸化クロムなどを用いた金属層、あるいは、感光性樹脂中にカーボン系黒色顔料またはチタン系黒色顔料などを分散させてなる黒色樹脂層、いわゆる樹脂ブラックマトリクスで形成されている。

【 0 0 3 3 】

10

また、カラーフィルタ基板 2 には、遮光領域部 23 , 24 で囲まれた遮光層 22 の各領域に、例えば R 、 G 、および B の 3 原色に対応する顔料または染料をレジストである感光性樹脂に分散した透明樹脂層からなる着色層 27 が形成されている。

【 0 0 3 4 】

反射領域部 18 には、遮光領域部 23 , 24 および着色層 27 を覆うように段差形成膜 28 が形成されている。段差形成膜 28 は、反射領域部 18 における液晶層 7 の厚さを、透過領域部 19 における液晶層 7 の厚さの半分程度となるように調整するために形成されている。図 4 の例では、段差形成膜 28 は、カラーフィルタ基板 2 に形成されているが、これに限るものではない。段差形成膜 28 は、例えば、アレイ基板 1 のみに形成してもよく、アレイ基板 1 およびカラーフィルタ基板 2 の両方に形成してもよい。

20

【 0 0 3 5 】

さらに、カラーフィルタ基板 2 には、ITO などの透明導電膜からなる図示しない対向電極が、表示領域 9 の略全面に設けられている。対向電極は、アレイ基板 1 の画素電極との間に電界を生じさせて液晶層 7 の液晶を駆動するために設けられており、トランスファ材を介してアレイ基板 1 側に設けられたトランスファ電極と電気的に接続されている。外部から入力された信号は、トランスファ電極およびトランスファ材を介して対向電極に伝達される。

【 0 0 3 6 】

カラーフィルタ基板 2 には、アレイ基板 1 とカラーフィルタ基板 2 との間に存在する液晶層 7 の厚さを制御するために、図示しない柱状スペーサが形成されている。

30

【 0 0 3 7 】

図 3 に示すように、遮光層 22 は、各画素の反射画素電極 20 および透過画素電極 21 に対応する領域に開口部を形成している。図 2 では、遮光層 22 の開口部を破線で示している。

【 0 0 3 8 】

次に、本実施の形態 1 による液晶表示装置の特徴となる構成について説明する。

【 0 0 3 9 】

図 3 に示すように、透過領域部 19 において、遮光領域部 23 の幅 W と遮光領域部 24 の幅 W とは同じである。この幅 W は、映像信号線 5 の近傍で発生する電界漏れによって液晶層 7 の液晶が所望の表示動作を行うことができない場合に、遮光領域部 23 を位置合わせしたときのずれも考慮して遮光可能な幅に設定すればよく、このとき設定した遮光領域部 23 の幅 W と同じ幅 W となるように遮光領域部 24 の幅を設定すればよい。一方、反射領域部 18 において、遮光領域部 24 の幅 W 1 は、遮光領域部 23 の幅 W 2 よりも小さく設定されている。

40

【 0 0 4 0 】

なお、遮光領域部 23 は、透過領域部 19 における幅 W と反射領域部 18 における幅 W 2 とで異なっている。これは、透過領域部 19 と反射領域部 18 とでは、映像信号線 5 の近傍で遮光するために必要な幅が若干異なるためである。幅 W および幅 W 2 は、必要最小限の異なる幅に設定してもよく、遮光に必要な幅の差が僅かであることから設計の便宜上同じ幅としてもよい。図 3 の例では、幅 W および幅 W 2 は同じ幅で示している。

50

## 【0041】

以上のことから、本実施の形態1によれば、透過領域部19において、遮光領域部23の幅Wと遮光領域部24の幅Wとは同じであるため、透過表示時に列方向に明暗のスジが視認されない。一方、反射領域部18において、遮光領域部24の幅W1は遮光領域部23の幅W2よりも小さいため、反射表示時に上記の図12(a)で説明したように列方向に明暗のスジが視認される懸念がある。しかし、反射領域部18における明暗のスジの視認性は低いため、表示品位が顕著に低下することはない。また、反射領域部18において、遮光領域部24の幅W1は遮光領域部23の幅W2よりも小さいため、反射領域部18に対応する遮光層22の開口部の面積を広げることができるために、換言すれば反射領域部18の開口率を上げることができるために、反射領域部18の反射率を向上させることができる。反射領域部18の開口率が上がった分は、透過領域部19の開口率に寄与することができるため、バックライトであるLEDの数を削減する、またはバックライトの消費電力を低減して省エネルギー化を図ることができる。さらに、本実施の形態1による液晶表示装置は、2倍走査線方式の半透過型液晶表示であるため、上記の効果に加えて、部品点数を削減して低コスト化を図ることができるという相乗効果が得られる。

10

## 【0042】

なお、反射領域部18における遮光領域部24の幅W1は、平面視において遮光領域部24を挟んで隣接する各画素に対応する色が混色することを防止するために必要な最小限の幅にすることができる。この場合、反射領域部18の開口率を最大限に上げることができるために、反射領域部18の反射率をさらに向上させることができる。

20

## 【0043】

## &lt;変形例&gt;

上記では、図3に示すように、透過領域部19において遮光領域部23の幅Wと遮光領域部24の幅Wとが同じである場合について説明した。この構成では、遮光領域部24の幅Wを遮光領域部23の幅Wに合わせているため、必要以上に遮光している遮光領域部24は無駄な領域を有していることになる。この無駄な領域を反射領域部18として利用しても、隣接する画素の透過領域部19の間隔は幅Wで変動しないため、透過領域部19において列方向の明暗のスジが視認されることなく、図3の構成よりも反射領域部18の開口率を向上させることができる。

30

## 【0044】

具体的には、図5,6に示すように、透過領域部19において、遮光領域部23の幅Wは図3に示す遮光領域部23の幅Wと同じであり、遮光領域部24の幅W3は遮光領域部23の幅Wよりも小さく設定されている。また、遮光領域部24を挟んで隣接する各反射領域部18に対応する反射画素電極20は、透過領域部19における遮光領域部24に沿って、かつ平面視において側部が遮光領域部24から突出するように設けられている。このとき、遮光領域部24の幅と、各反射画素電極20の遮光領域部24から突出した部分の幅とを合わせた幅Wは、遮光領域部23の幅Wと同じである。すなわち、透過領域部19間ににおける遮光領域部24を挟んで隣接する各画素電極の反射領域部18は、透過領域部19間ににおける遮光領域部24に沿って透過領域部19側に延設され、かつ当該延設された反射領域部18と透過領域部19との境界は、反射領域部18間ににおける遮光領域部24から平面視で突出し、透過領域部19間ににおける遮光領域部23の幅は、透過領域部19間ににおける遮光領域部24を挟んで隣接する各反射領域部18と透過領域部19との境界間の距離と同じである。

40

## 【0045】

上記の構成とすることによって、隣接する画素間ににおける透過領域部19の間隔は幅Wであるため、図3に示す構成と同様、透過表示時に明暗のスジが視認されないという効果が得られる。また、反射領域部18の領域を広げているため、反射領域部18の開口率をさらに向上させることが可能となる。

## 【0046】

## &lt;実施の形態2&gt;

50

実施の形態1では、映像信号線5と、反射画素電極20および透過画素電極21からなる画素電極とが、平面視で重畠せず離間して配置される場合について説明した。本発明の実施の形態2では、映像信号線5と、反射画素電極20および透過画素電極21からなる画素電極とが、平面視で重畠して配置される場合について説明する。

【0047】

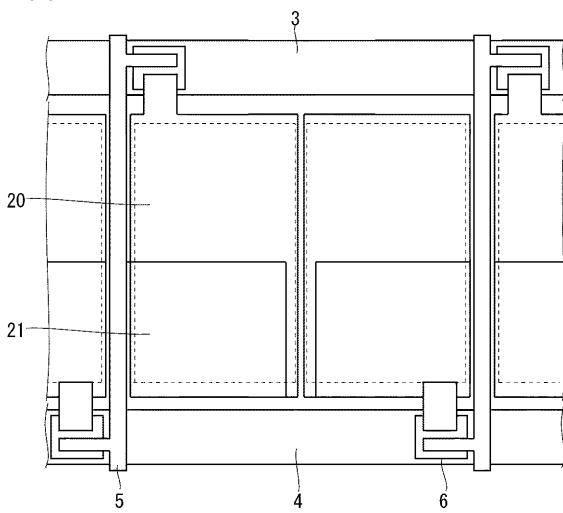

図7は、本発明の実施の形態2によるアレイ基板1の構成の一例を示す平面図である。図8は、遮光層22の構成の一例を示す平面図である。図9は、図7、8のB1-B2断面を示す図である。なお、以下では、本実施の形態2による液晶表示装置は、2倍走査線方式の半透過液晶表示装置であるものとして説明する。

【0048】

図7、9に示すように、アレイ基板1では、映像信号線5を覆うように平坦化膜30が設けられている。平坦化膜30は、例えば1μm～3μm程度の厚さの有機樹脂膜である。反射画素電極20および透過画素電極21は、平坦化膜30上であって、かつ平面視において映像信号線5の一部と重畠するように設けられている。なお、反射画素電極20および透過画素電極21からなる画素電極は、TFT6の近傍において、平坦化膜30を開口して設けられた画素コンタクトホール29を介してTFT6に接続されている。

【0049】

なお、平坦化膜30は、反射領域部18における液晶層7の厚さを、透過領域部19における液晶層7の厚さの半分程度となるように調整する機能を有してもよい。この場合、段差形成膜28は不要である。例えば、平坦化膜30は、透過領域部19では開口部などを設けて除去する。また、平坦化膜30は、反射領域部18では映像信号線5を覆うように形成し、透過領域部19では映像信号線5を覆わずに形成してもよい。この場合、反射領域部18において、反射画素電極20のみを平坦化膜30上であって、かつ平面視において映像信号線5の一部と重畠するように設けることができる。

【0050】

次に、本実施の形態2による液晶表示装置の特徴となる構成について説明する。

【0051】

図9に示すように、透過領域部19において、遮光領域部23の幅Wと遮光領域部24の幅Wとは同じである。なお、遮光領域部23の幅Wは、図3に示す透過領域部19における遮光領域部23の幅Wよりも小さく設定することができる。上記の通り、反射画素電極20および透過画素電極21からなる画素電極は、平坦化膜30上であって、かつ平面視において映像信号線5の一部と重畠するように設けられている。従って、映像信号線5によって遮光される範囲外となる映像信号線5の両側端部に対応する位置まで、液晶のオンオフによる表示動作を行うため、透過領域部19における遮光領域部23の幅Wは、当該遮光領域部23と映像信号線5との平面視におけるずれを考慮して映像信号線5の幅よりも大きければよい。結果的に、透過領域部19における遮光領域部23の幅Wは、図3に示す透過領域部19における遮光領域部23の幅Wよりも小さく設定することができる。また、これに合わせて、透過領域部19における遮光領域部24の幅Wも小さく設定することができる。

【0052】

一方、反射領域部18において、反射画素電極20は、平坦化膜30上であって、かつ平面視において映像信号線5の一部と重畠するように設けられている。特に、反射領域部18では、反射画素電極20の下方に設けられる映像信号線5によって表示動作に影響がなく、映像信号線5と平面視で重畠している領域を含めて反射画素電極20上の全体の領域が表示動作する。従って、反射領域部18における遮光領域部23の幅W1は、透過領域部19における遮光領域部23の幅Wよりも小さく設定することができる。また、これに合わせて、反射領域部18における遮光領域部24の幅W1は、反射領域部18における遮光領域部23の幅W1と同じ幅に設定する。

【0053】

以上のことから、本実施の形態2によれば、映像信号線5が設けられているか否かにか

かわらず、反射領域部18における遮光領域部23の幅W1と遮光領域部24の幅W1とは同じである。また、透過領域部19において、遮光領域部23の幅Wと遮光領域部24の幅Wとは同じである。従って、透過表示時および反射表示時のいずれの場合であっても、明暗のスジが視認されることはない。また、反射領域部18の開口率を上げることができる。

【0054】

<変形例>

上記で説明した構成では、透過領域部19において、遮光領域部24の幅Wを遮光領域部23の幅Wに合わせているため、必要以上に遮光している遮光領域部24は無駄な領域を有していることになる。この無駄な領域を反射領域部18として利用したとしても、隣接する画素の透過領域部19の間隔は幅Wで変動しないため、透過領域部19において列方向の明暗のスジが視認されることなく、上記の構成よりも反射領域部18の開口率を向上させることができる。

10

【0055】

具体的には、図10に示すように、反射領域部18において、遮光領域部23および遮光領域部24の幅W1は、図8に示す遮光領域部23および遮光領域部24の幅W1と同じである。また、透過領域部19において、遮光領域部23および遮光領域部24の幅W3は、反射領域部18における遮光領域部23および遮光領域部24の幅W1と同じである。遮光領域部23または遮光領域部24の各々を挟んで隣接する各反射領域部18に対応する反射画素電極20は、透過領域部19における遮光領域部23または遮光領域部24に沿って、かつ平面視において側部が遮光領域部23または遮光領域部24から突出するように設けられている。このとき、遮光領域部23または遮光領域部24の幅と、各反射画素電極20の遮光領域部23または遮光領域部24から突出した部分の幅とを合わせた幅Wは、図8に示す遮光領域部23および遮光領域部24の幅Wと同じである。すなわち、各画素電極の反射領域部18は、遮光領域部23および遮光領域部24に沿って透過領域部19側に延設され、かつ当該延設された反射領域部18と透過領域部19との境界は、反射領域部18間ににおける遮光領域部23および遮光領域部24から平面視で突出し、透過領域部19間ににおける遮光領域部23を挟んで隣接する各反射領域部18と透過領域部19との境界間の距離は、透過領域部19間ににおける遮光領域部24を挟んで隣接する各反射領域部18と透過領域部19との境界間の距離と同じである。

20

【0056】

上記の構成とすることによって、図8に示す構成によって得られる効果に加えて、反射領域部18の領域を広げているため、反射領域部18の開口率をさらに向上させることが可能となる。

30

【0057】

なお、実施の形態1,2では、1つの画素を上下に2分割して反射領域部18および透過領域部19を設け、反射領域部18および透過領域部19が行方向にストライプ状に配置される構成を一例として説明したが、これに限るものではない。2倍走査線方式では、基本的に、各画素でTFT6の配置が列ごとに異なるため、1つの画素を上下に2分割し、TFT6に近い側を反射領域部18とし、TFT6から遠い側を透過領域とし、反射領域部18および透過領域部19が行方向に互い違いに配置される構成としてもよい。また、1つの画素を上中下に3分割し、中央部を透過領域部19とし、上部および下部を反射領域部18としてもよい。

40

【0058】

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

【符号の説明】

【0059】

1 アレイ基板、2 カラーフィルタ基板、3, 4 走査信号線、5 映像信号線、6 TFT、7 液晶層、8 シール材、9 表示領域、10, 11 駆動ICチップ、1

50

2, 13 信号端子、14 FFC、15 制御基板、16 FFC、17 制御基板、

18 反射領域部、19 透過領域部、20 反射画素電極、21 透過画素電極、22

遮光層、23, 24 遮光領域部、25, 26 ガラス基板、27 着色層、28 段

差形成膜、29 画素コンタクトホール、30 平坦化膜、31 遮光層、32, 33

遮光領域部、34 遮光層、35, 36 遮光領域部。

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図 8】

【図 10】

【図 9】

【図 11】

【図 12】

|                |                                                                                                                            |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2019045704A</a>                                                                                              | 公开(公告)日 | 2019-03-22 |

| 申请号            | JP2017169110                                                                                                               | 申请日     | 2017-09-04 |

| [标]申请(专利权)人(译) | 三菱电机株式会社                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 三菱电机株式会社                                                                                                                   |         |            |

| [标]发明人         | 梅田博嗣                                                                                                                       |         |            |

| 发明人            | 梅田 博嗣                                                                                                                      |         |            |

| IPC分类号         | G02F1/1335 G02F1/1368                                                                                                      |         |            |

| FI分类号          | G02F1/1335 G02F1/1368                                                                                                      |         |            |

| F-TERM分类号      | 2H192/AA24 2H192/BC63 2H192/CB05 2H192/CC04 2H192/CC24 2H192/CC62 2H192/EA22 2H291 /FA14Y 2H291/FD26 2H291/NA09 2H291/NA30 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                  |         |            |

### 摘要(译)

本发明的目的是提供一种能够通过抑制显示质量的劣化来降低成本的液晶显示装置。根据本发明的液晶显示装置包括以矩阵排列的多个像素电极，在像素电极之间沿行方向延伸的多条扫描信号线3和4，以及像素电极并且，在平面图中，每两列延伸的多个视频信号线5和在像素电极之间的行方向和列方向上的每个像素电极上设置的遮光层22。并且，每个像素电极具有用于反射光的反射区域部分18和用于透射光的透射区域部分19，其在列方向上并排设置，并且遮光层22是平面图中的图像。在平面图中与信号线5重叠的遮光区域部分24和在列方向上不与视频信号线5重叠的遮光区域部分24，以及在各个像素电极的反射区域部分18之间的遮光区域部分24小于每个像素电极的透射区域19之间的遮光区域23的宽度。[选中图]图3