(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-149493

(P2014-149493A)

(43) 公開日 平成26年8月21日(2014.8.21)

|                   |           |                             |

|-------------------|-----------|-----------------------------|

| (51) Int.Cl.      | F 1       | テーマコード (参考)                 |

| <b>G09G 3/36</b>  | (2006.01) | G09G 3/36 2 H 1 9 3         |

| <b>G09G 3/20</b>  | (2006.01) | G09G 3/20 6 2 3 C 5 C 0 0 6 |

| <b>G02F 1/133</b> | (2006.01) | G09G 3/20 6 2 1 A 5 C 0 8 0 |

|                   |           | G09G 3/20 6 2 3 D           |

|                   |           | G09G 3/20 6 4 1 C           |

審査請求 未請求 請求項の数 10 O L (全 21 頁) 最終頁に続く

|           |                            |          |                                               |

|-----------|----------------------------|----------|-----------------------------------------------|

| (21) 出願番号 | 特願2013-19407 (P2013-19407) | (71) 出願人 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日  | 平成25年2月4日 (2013.2.4)       | (74) 代理人 | 110000752<br>特許業務法人朝日特許事務所                    |

|           |                            | (72) 発明者 | 若林 淳一<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

|           |                            | (72) 発明者 | 西村 陽彦<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

|           |                            | (72) 発明者 | 保坂 宏行<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

最終頁に続く

(54) 【発明の名称】画像処理装置、液晶表示装置、電子機器および駆動方法

## (57) 【要約】

【課題】配向不良が発生するおそれのある2つの画素間のコントラストの低下を抑制しつつ、配向不良の発生を抑制する。

【解決手段】画像処理装置は、第1方向および第2方向に配置された画素群のうち第1画素および当該第1画素と隣り合う第2画素に挟まれた境界であって、第1画素および第2画素の入力映像信号により示される印加電圧の差がしきい値以上である境界を検出する境界検出手段と、前記第1画素および前記第2画素の少なくとも一方の画素の印加電圧を、当該画素の階調に応じて決まる、第1電圧および前記第1電圧より低い第2電圧のパターンを、配向不良の発生速度よりも短い間隔の時分割で当該画素に印加する補正を行う補正手段と、前記補正手段により補正された電圧に応じた信号を、前記画素群を有する液晶パネルを駆動する駆動回路に出力する出力手段とを有する。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

第1方向および第2方向に配置された画素群のうち第1画素および当該第1画素と隣り合う第2画素に挟まれた境界であって、第1画素および第2画素の入力映像信号により示される印加電圧の差がしきい値以上である境界を検出する境界検出手段と、

前記第1画素および前記第2画素の少なくとも一方の画素の印加電圧を、当該画素の階調に応じて決まる、第1電圧および前記第1電圧より低い第2電圧のパターンを、配向不良の発生速度よりも短い間隔の時分割で当該画素に印加する補正を行う補正手段と、

前記補正手段により補正された電圧に応じた信号を、前記画素群を有する液晶パネルを駆動する駆動回路に出力する出力手段と

を有する画像処理装置。

10

**【請求項 2】**

前記補正手段は、前記第1画素および前記第2画素のうち前記補正がされる画素について、当該画素の補正後の印加電圧により示される階調値の積分が、当該画素の入力映像信号により示される階調値の積分と等しくなるように前記補正をする

ことを特徴とする請求項1に記載の画像処理装置。

**【請求項 3】**

前記時分割された期間において、前記第1電圧が印加される期間と前記第2電圧が印加される期間の比率があらかじめ決められており、

前記補正手段は、前記補正が行われる画素の階調に応じて決定された前記第1電圧および前記第2電圧のパターンを用いて前記補正を行う

20

ことを特徴とする請求項1または2に記載の画像処理装置。

**【請求項 4】**

前記第1電圧および前記第2電圧があらかじめ決められており、

前記補正手段は、前記補正が行われる画素の階調に応じて決定された、前記第1電圧が印加される期間と前記第2電圧が印加される期間の比率を有する前記パターンを用いて前記補正を行う

ことを特徴とする請求項1または2に記載の画像処理装置。

**【請求項 5】**

前記補正手段は、前記第1画素および前記第2画素のうち、少なくとも、印加電圧がより低い画素の印加電圧を補正する

30

ことを特徴とする請求項1ないし4のいずれか一項に記載の画像処理装置。

**【請求項 6】**

前記補正手段は、前記第1画素および前記第2画素のうち一方の画素のみについて前記補正をする

ことを特徴とする請求項1ないし5のいずれか一項に記載の画像処理装置。

**【請求項 7】**

前記補正手段は、前記第1画素および前記第2画素の両方の画素について前記補正をする

40

ことを特徴とする請求項1ないし5のいずれか一項に記載の画像処理装置。

**【請求項 8】**

第1方向および第2方向に配置された画素群を有する液晶パネルと、

前記液晶パネルを駆動する駆動回路と、

前記画素群のうち第1画素および当該第1画素と隣り合う第2画素に挟まれた境界であって、第1画素および第2画素の印加電圧の差がしきい値以上である境界を検出する境界検出手段と、

前記第1画素および前記第2画素の少なくとも一方の画素の印加電圧を、当該画素の階調に応じて決まる、第1電圧および前記第1電圧より低い第2電圧のパターンを、配向不良の発生速度よりも短い間隔の時分割で当該画素に印加する補正を行う補正手段と、

前記補正手段により補正された電圧に応じた信号を、前記駆動回路に出力する出力手段

50

と

を有する液晶表示装置。

【請求項 9】

請求項 8 に記載の液晶表示装置を有する電子機器。

【請求項 10】

第 1 方向および第 2 方向に配置された画素群のうち第 1 画素および当該第 1 画素と隣り合う第 2 画素に挟まれた境界であって、第 1 画素および第 2 画素の印加電圧の差がしきい値以上である境界を検出するステップと、

前記第 1 画素および前記第 2 画素の少なくとも一方の画素の印加電圧を、当該画素の階調に応じて決まる、第 1 電圧および前記第 1 電圧より低い第 2 電圧のパターンを、配向不良の発生速度よりも短い間隔の時分割で当該画素に印加する補正を行うステップと、

前記補正手段により補正された電圧に応じた信号を、前記画素群を有する液晶パネルを駆動する駆動回路に出力するステップと

を有する表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶パネルにおける表示上の不具合を低減する技術に関する。

【背景技術】

【0002】

液晶パネルは本来、画素内における画素電極と対向電極との間の電界により液晶分子の配向状態を制御するものである。しかし、例えば液晶パネルが高精細化され、隣り合う画素間の距離が短くなると、2つの画素の画素電極間の電界（横電界）が発生し、液晶分子が意図しない向きに配向してしまう配向不良（いわゆるディスクリネーションまたはリバースチルトドメイン）が発生する場合がある。配向不良の発生は、液晶パネルの表示品位を低下させる原因となる。特許文献 1 から特許文献 5 は、配向不良の発生を抑えるための技術を開示している。

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2009 - 25417 号公報

【特許文献 2】特開 2009 - 104053 号公報

【特許文献 3】特開 2009 - 104055 号公報

【特許文献 4】特開 2009 - 237366 号公報

【特許文献 5】特開 2009 - 237524 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献 1 ないし 5 に記載された技術においては、隣り合う 2 つの画素の印加電圧の差を小さくする補正が行われるため、これら 2 つの画素間のコントラストが低下してしまうという問題があった。

これに対し本発明は、配向不良が発生するおそれのある 2 つの画素間のコントラストの低下を抑制しつつ、配向不良の発生を抑制する技術を提供する。

【課題を解決するための手段】

【0005】

本発明は、第 1 方向および第 2 方向に配置された画素群のうち第 1 画素および当該第 1 画素と隣り合う第 2 画素に挟まれた境界であって、第 1 画素および第 2 画素の印加電圧の差がしきい値以上である境界を検出する境界検出手段と、前記第 1 画素および前記第 2 画素の少なくとも一方の画素の印加電圧を、当該画素の階調に応じて決まる、第 1 電圧および前記第 1 電圧より低い第 2 電圧のパターンを、配向不良の発生速度よりも短い間隔の時

10

20

30

40

50

分割で当該画素に印加する補正を行う補正手段と、前記補正手段により補正された電圧に応じた信号を、前記画素群を有する液晶パネルを駆動する駆動回路に出力する出力手段とを有する画像処理装置を提供する。

この画像処理装置によれば、配向不良が発生するおそれのある第1画素および第2画素の間のコントラストの低下を抑制しつつ、配向不良の発生を抑制することができる。

#### 【0006】

前記補正手段は、前記第1画素および前記第2画素のうち前記補正がされる画素について、当該画素の補正後の印加電圧により示される階調値の積分が、当該画素の入力映像信号により示される階調値の積分と等しくなるように前記補正をしてもよい。

この画像処理装置によれば、第1画素および第2画素の間のコントラストを、入力映像信号により示されるコントラストと等しくすることができる。 10

#### 【0007】

前記時分割された期間において、前記第1電圧が印加される期間と前記第2電圧が印加される期間の比率があらかじめ決められており、前記補正手段は、前記補正が行われる画素の階調に応じて決定された前記第1電圧および前記第2電圧のパターンを用いて前記補正を行ってもよい。

この画像処理装置によれば、印加される期間の比率があらかじめ決められている場合において、配向不良が発生するおそれのある第1画素および第2画素の間のコントラストの低下を抑制しつつ、配向不良の発生を抑制することができる。

#### 【0008】

前記第1電圧および前記第2電圧があらかじめ決められており、前記補正手段は、前記補正が行われる画素の階調に応じて決定された、前記第1電圧が印加される期間と前記第2電圧が印加される期間の比率を有する前記パターンを用いて前記補正を行ってもよい。 20

この画像処理装置によれば、第1電圧および第2電圧の値があらかじめ決められている場合において、配向不良が発生するおそれのある第1画素および第2画素の間のコントラストの低下を抑制しつつ、配向不良の発生を抑制することができる。

#### 【0009】

前記補正手段は、前記第1画素および前記第2画素のうち、少なくとも、印加電圧がより低い画素の印加電圧を補正してもよい。

この画像処理装置によれば、より効果的に配向不良の発生を抑制することができる。 30

#### 【0010】

前記補正手段は、前記第1画素および前記第2画素のうち一方の画素のみについて前記補正をしてもよい。

この画像処理装置によれば、より低負荷で配向不良の発生を抑制することができる。

#### 【0011】

前記補正手段は、前記第1画素および前記第2画素の両方の画素について前記補正をしてもよい。

この画像処理装置によれば、配向不良の発生をより強く抑制することができる。

#### 【0012】

また、本発明は、第1方向および第2方向に配置された画素群を有する液晶パネルと、前記液晶パネルを駆動する駆動回路と、前記画素群のうち第1画素および当該第1画素と隣り合う第2画素に挟まれた境界であって、第1画素および第2画素の印加電圧の差がしきい値以上である境界を検出する境界検出手段と、前記第1画素および前記第2画素の少なくとも一方の画素の印加電圧を、当該画素の階調に応じて決まる、第1電圧および前記第1電圧より低い第2電圧のパターンを、配向不良の発生速度よりも短い間隔の時分割で当該画素に印加する補正を行う補正手段と、前記補正手段により補正された電圧に応じた信号を、前記駆動回路に出力する出力手段とを有する液晶表示装置を提供する。 40

この液晶表示装置によれば、配向不良が発生するおそれのある第1画素および第2画素の間のコントラストの低下を抑制しつつ、配向不良の発生を抑制することができる。

#### 【0013】

10

20

30

40

50

さらに、本発明は、上記の液晶表示装置を有する電子機器を提供する。

この電子機器によれば、配向不良が発生するおそれのある第1画素および第2画素の間のコントラストの低下を抑制しつつ、配向不良の発生を抑制することができる。

#### 【0014】

さらに、本発明は、第1方向および第2方向に配置された画素群のうち第1画素および当該第1画素と隣り合う第2画素に挟まれた境界であって、第1画素および第2画素の印加電圧の差がしきい値以上である境界を検出するステップと、前記第1画素および前記第2画素の少なくとも一方の画素の印加電圧を、当該画素の階調に応じて決まる、第1電圧および前記第1電圧より低い第2電圧のパターンを、配向不良の発生速度よりも短い間隔の時分割で当該画素に印加する補正を行うステップと、前記補正手段により補正された電圧に応じた信号を、前記画素群を有する液晶パネルを駆動する駆動回路に出力するステップとを有する表示装置の駆動方法を提供する。

この駆動方法によれば、配向不良が発生するおそれのある第1画素および第2画素の間のコントラストの低下を抑制しつつ、配向不良の発生を抑制することができる。

#### 【図面の簡単な説明】

#### 【0015】

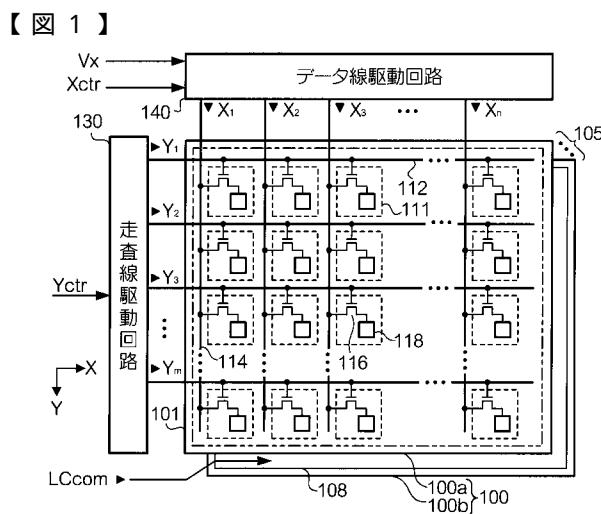

【図1】液晶表示装置の概略構成を示す図。

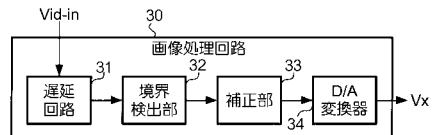

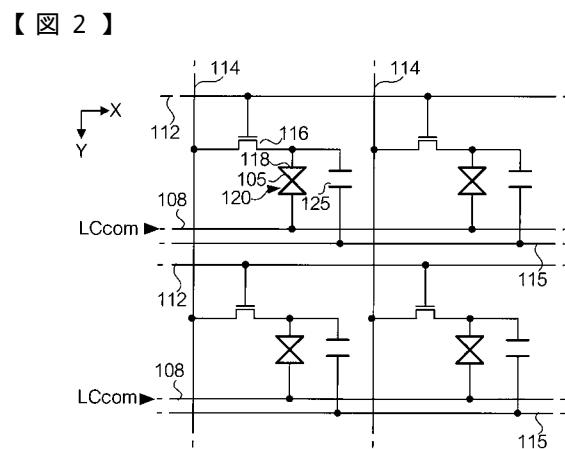

【図2】画素111の等価回路を示す図。

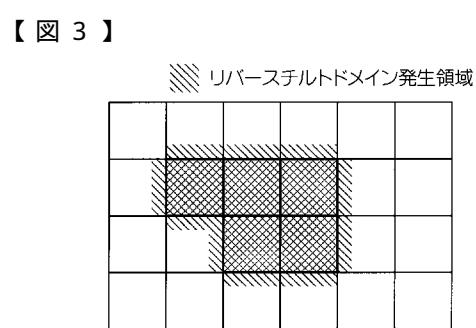

【図3】リバースチルトドメインによる表示不具合を例示する図。

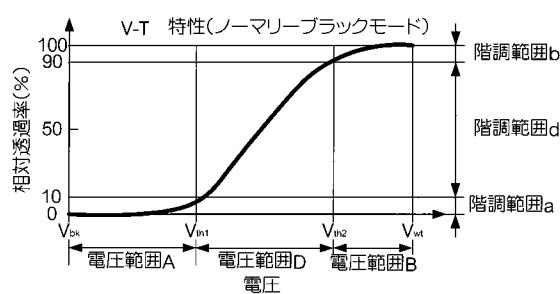

【図4】液晶素子120のV-T特性を例示する図。

10

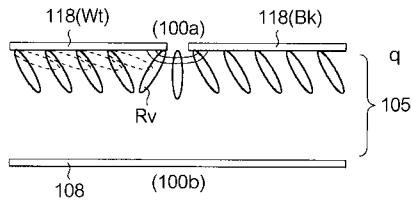

【図5】リバースチルトドメイン発生時の液晶分子の配向状態を例示する模式図。

20

【図6】従来の補正を例示する図。

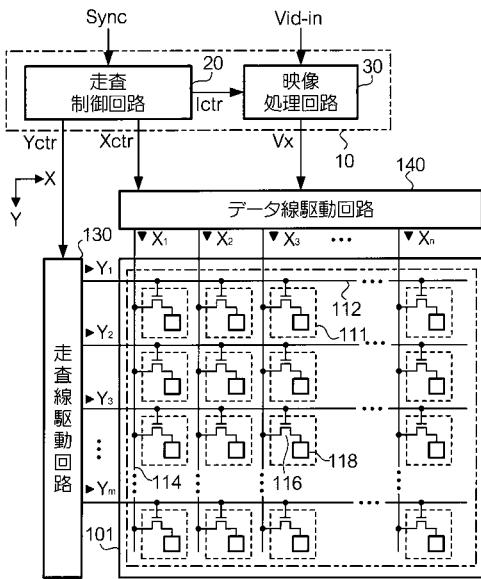

【図7】第1実施形態に係る液晶表示装置1の構成を示すブロック図。

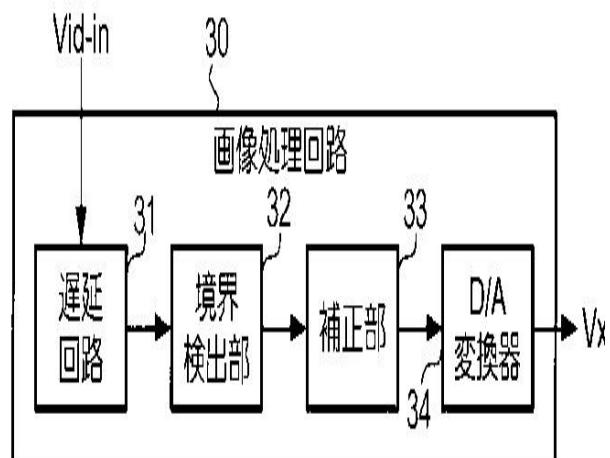

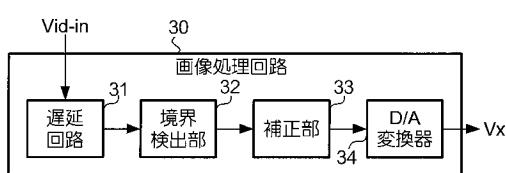

【図8】画像処理回路30の構成を示す図。

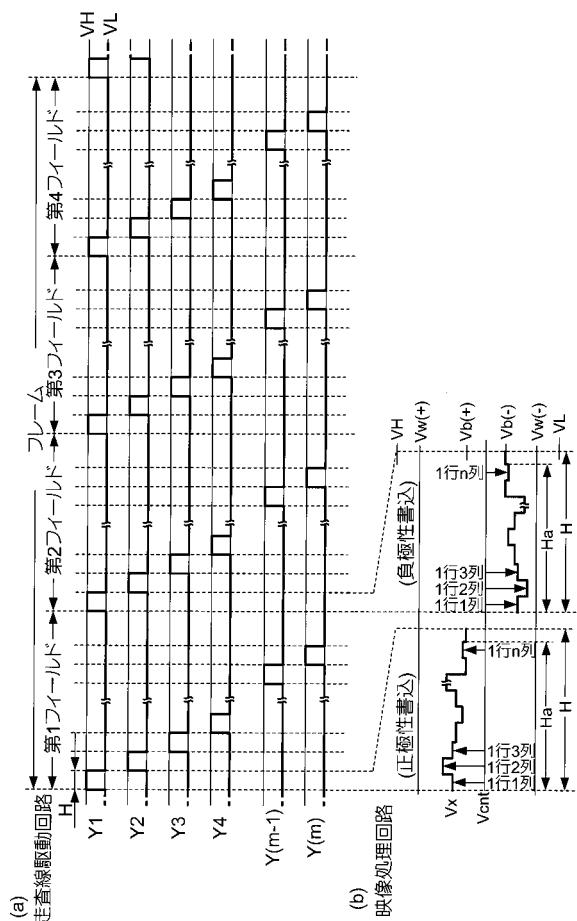

【図9】液晶表示装置1の動作を示すタイミングチャート。

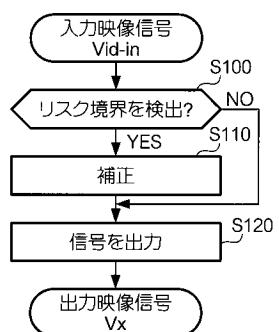

【図10】画像処理回路30の動作を示すフローチャート。

【図11】第1実施形態における補正の具体例を示す図。

【図12】第2実施形態における補正の具体例を示す図。

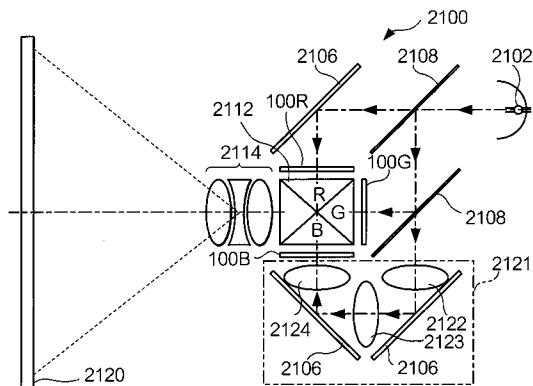

【図13】変形例5に係るプロジェクター2100を例示する図。

30

#### 【発明を実施するための形態】

#### 【0016】

#### 1. 液晶表示装置の構成と問題点

実施形態に係る装置の構成およびその動作の説明に先立ち、液晶表示装置の構成および問題点について説明する。

#### 【0017】

#### 1-1. 液晶表示装置の概略

図1は、液晶表示装置の概略構成を示す図である。この液晶表示装置は、液晶パネル100と、走査線駆動回路130と、データ線駆動回路140とを有する。

#### 【0018】

液晶パネル100は、供給される信号に応じて画像を表示する装置である。液晶パネル100は、m行n列のマトリクス状に配置された画素111を有する。画素111は、走査線駆動回路130及びデータ線駆動回路140から供給される信号に応じた光学状態を示す。液晶パネル100は、複数の画素111の光学状態を制御することにより画像を表示する。

#### 【0019】

液晶パネル100は、素子基板100aと、対向基板100bと、液晶105とを有する。素子基板100aと対向基板100bとは、一定の間隙を保って貼り合わせられている。この間隙に、液晶105が挟まれている。

#### 【0020】

素子基板100aは、対向基板100bとの対向面において、m行の走査線112およ

40

50

び  $n$  列のデータ線 114 を有する。走査線 112 は X (横) 方向に沿って、データ線 114 は Y (縦) 方向に沿って、それぞれ設けられており、互いに絶縁されている。一の走査線 112 を他の走査線 112 と区別するときは、図において上から順に第 1、第 2、第 3、…、第 ( $m - 1$ )、および第  $m$  行の走査線 112 という。同様に、一のデータ線 114 を他のデータ線 114 と区別するときは、図において左から順に第 1、第 2、第 3、…、第 ( $n - 1$ )、第  $n$  列のデータ線 114 という。画素 111 は、X 軸および Y 軸に垂直な位置にある視点からみたときに、走査線 112 およびデータ線 114 の交差に対応して設けられている。

#### 【0021】

図 2 は、画素 111 の等価回路を示す図である。画素 111 は、TFT116 と、液晶素子 120 と、保持容量 125 とを有する。液晶素子 120 は、画素電極 118 と、液晶 105 と、コモン電極 108 とを有する。画素電極 118 は、画素 111 毎に個別に設けられた電極である。コモン電極 108 は、すべての画素 111 に共通の電極である。画素電極 118 は素子基板 100a に、コモン電極 108 は対向基板 100b に、それぞれ設けられている。液晶 105 は、画素電極 118 およびコモン電極 108 に挟まれている。コモン電極 108 には、コモン電圧 LCCOM が印加される。

10

#### 【0022】

TFT116 は、画素電極 118 への電圧の印加を制御するスイッチング素子の一例であり、この例では、 $n$  チャネル型の電界効果トランジスターである。TFT116 は、画素 111 毎に個別に設けられている。第  $i$  行第  $j$  列の TFT116 のゲートは第  $i$  行の走査線 112 に、ソースは第  $j$  列のデータ線 114 に、ドレインは画素電極 118 に、それぞれ接続されている。保持容量 125 は、一端が画素電極 118 に、他端が容量線 115 に、それぞれ接続されている。容量線 115 には、時間的に一定の電圧が印加される。

20

#### 【0023】

第  $i$  行の走査線 112 に H (High) レベルの電圧（以下「選択電圧」という）が印加されると、第  $i$  行第  $j$  列の TFT116 はオン状態となり、ソースとドレインが導通する。このとき、第  $j$  列のデータ線 114 に、第  $i$  行第  $j$  列の画素 111 の階調値（データ）に応じた電圧（以下「データ電圧」という）が印加されると、データ電圧は、TFT116 を介して第  $i$  行第  $j$  列の画素電極 118 に印加される。

30

#### 【0024】

その後、第  $i$  行の走査線 112 に L (Low) レベルの電圧（以下「非選択電圧」という）が印加されると、TFT116 はオフ状態になり、ソースとドレインは高インピーダンス状態となる。TFT116 がオン状態のとき画素電極 118 に印加された電圧は、液晶素子 120 の容量性および保持容量 125 によって、TFT116 がオフ状態になった後も保持される。

40

#### 【0025】

液晶素子 120 には、データ電圧とコモン電圧との電位差に相当する電圧が印加される。液晶 105 の分子配向状態は、液晶素子 120 に印加される電圧に応じて変化する。画素 111 の光学状態は、液晶 105 の分子配向状態に応じて変化する。例えば、液晶パネル 100 が透過型のパネルである場合、変化する光学状態は透過率である。

40

#### 【0026】

再び図 1 を参照する。走査線駆動回路 130 は、 $m$  本の走査線 112 の中から一の走査線 112 を順次排他的に選択する（すなわち走査線 112 を走査する）回路である。具体的には、走査線駆動回路 130 は、制御信号 Yctrl に従って、第  $i$  行の走査線 112 に、走査信号  $Y_i$  を供給する。この例で、走査信号  $Y_i$  は、選択される走査線 112 に対しては選択電圧となり、選択されない走査線 112 に対しては非選択電圧となる信号である。

#### 【0027】

データ線駆動回路 140 は、 $n$  本のデータ線 114 にデータ電圧を示す信号（以下「データ信号」という）を出力する回路である。具体的には、データ線駆動回路 140 は、画

50

像処理回路 30 から供給されるデータ信号  $V_x$  を、制御信号  $X_{ctr}$  に従ってサンプリングし、第 1 ~ 第  $n$  列のデータ線 114 にデータ信号  $X_1 \sim X_n$  として出力する。なお、本説明において電圧については、液晶素子 120 の印加電圧を除き、特に明記しない限り図示省略した接地電位を基準（ゼロ  $V$ ）として表す。

#### 【0028】

液晶パネル 100 に表示される画像は、所定の周期で書き換えられる。以下、この書き換えの周期を「フレーム」という。例えば、画像が 60 Hz で書き換えられる場合、1 フレームは約 16.7 msec である。走査線駆動回路 130 が 1 フレームに 1 回、m 本の走査線 112 を走査し、データ線駆動回路 140 がデータ信号を出力することにより、液晶パネル 100 に表示される画像が書き換えられる。

10

#### 【0029】

##### 1 - 2. リバースチルトドメインによる表示不具合

図 3 は、リバースチルトドメインによる表示不具合を例示する図である。図 3 は、映像信号  $V_{idle-in}$  により示される画像が、白画素の背景上にグレー画素が連続するパターンとして描かれている例を示している。この場合、背景領域のうちパターンと隣接する部分（境界部分）において階調が白にならず中間階調になってしまふという現象が顕在化する。

#### 【0030】

この表示不具合は、液晶素子 120 において、横電界の影響により、印加電圧に応じた配向状態になりにくくなることが原因の一つであると考えられている。ここで、「横電界」とは、素子基板 100a の面に沿った方向（XY 平面に沿った方向）の電界をいう。これに対し画素電極 118 とコモン電極 108 との間に印加される電圧による電界を「縦電界」という。液晶分子の配向状態について説明する前に、まず、液晶素子 120 における印加電圧と透過率との関係を説明する。

20

#### 【0031】

図 4 は、液晶素子 120 における印加電圧と透過率との関係（V-T 特性）を例示する図である。この例で、液晶 105 は VA 方式であり、電圧無印加時において液晶素子 120 は黒状態（透過率ゼロ）となるノーマリーブラックモードである。印加電圧  $V$  が  $V_{bk}$   $\leq V \leq V_{th1}$  の範囲（以下この範囲を「電圧範囲 A」という。この例では  $V_{bk} = 0 V$ ）にある場合、相対透過率は 0% ~ 10% の範囲にある（以下この範囲を「階調範囲 a」という）。印加電圧  $V$  が  $V_{th1} \leq V \leq V_{th2}$  の範囲（以下この範囲を「電圧範囲 D」という）にある場合、相対透過率は 10% ~ 90% の範囲にある（以下この範囲を「階調範囲 d」という）。印加電圧  $V$  が  $V_{th2} \leq V \leq V_{wt}$  の範囲（以下この範囲を「電圧範囲 B」という）にある場合、相対透過率は 90% ~ 100% の範囲にある（以下この範囲を「階調範囲 b」という）。ここでは、しきい値電圧  $V_{th1}$  が透過率 10% 相当の電圧であり、しきい値電圧  $V_{th2}$  が透過率 90% 相当の電圧である例を説明したが、しきい値電圧  $V_{th1}$  および  $V_{th2}$  はこれに限定されるものではない。

30

#### 【0032】

このように、液晶素子 120 は、縦電界すなわち画素電極 118 とコモン電極 108 との間に印加される電圧によりその透過率を制御するものであるが、液晶パネル 100 が小型化または高精細化されると、隣接する 2 つの液晶素子 120 間の距離が短くなり、横電界すなわち 2 つの画素電極 118 間の電界の影響が無視できなくなる。すなわち、横電界の影響により、液晶分子の配向状態が本来あるべき状態（縦電界で制御された状態）と異なる状態となってしまう領域（リバースチルトドメイン）が発生する。

40

#### 【0033】

図 5 は、リバースチルトドメイン発生時の液晶分子の配向状態を例示する模式図である。図 5 は、液晶パネル 100 を、垂直面で破断したときの断面模式図である。液晶分子は、電界に対して垂直な方向に向くように配向状態が変化する。この例では、白画素の画素電極 118 (Wt) と黒画素の画素電極 118 (Bk) との間隙で生じる電位差が、白画素の画素電極 118 (Wt) とコモン電極 108 との間で生じる電位差と同程度である上

50

に、画素電極同士の間隙が画素電極 118 とコモン電極 108 との間隙よりも狭い。したがって、白画素の画素電極 118 (Wt) と黒画素の画素電極 118 (Bk) との間隙で生じる横電界は、白画素の画素電極 118 (Wt) とコモン電極 108 との間隙で生じる縦電界よりも強い。このような状況では、白画素の画素電極 118 (Wt) のうち黒画素との境界部分においては、リバースチルトドメイン Rv が発生する。黒画素と白画素とが隣接する領域において、横電界の影響によって、リバースチルトドメイン Rv が発生しやすい状況にあるということができる。

#### 【0034】

以上の説明から、リバースチルトドメインが発生する条件は以下のとおりである。

・隣接する 2 つの画素の印加電圧の差（電位差）がしきい値より大きい。なお、これら隣接する 2 つの画素のうち、より暗い階調の画素を「暗画素」といい、より明るい階調の画素を「明画素」という。黒画素および白画素は、暗画素および明画素の一例である。ノーマリーブラックの場合、暗画素の印加電圧が低く、明画素の印加電圧が高い。

上記の条件が満たされると、印加電圧が高い画素においてリバースチルトドメインが発生する。

#### 【0035】

##### 1 - 3 . リバースチルトドメインの抑制

リバースチルトドメインの発生を抑制するには、上記の条件が満たされなくなる補正処理を行えばよい。例えば、映像信号 V<sub>id-in</sub> が、上記の条件を満たす、隣接する 2 つの画素があることを示していた場合、これら 2 つの画素の印加電圧の差を小さくするように、印加電圧が補正される。ここで、映像信号 V<sub>id-in</sub> により上記の条件を満たすことが示される暗画素と明画素との境界を「リスク境界」という。より具体的には、暗画素が階調範囲 a (電圧範囲 A) にあり、明画素が階調範囲 b (電圧範囲 B) にある場合、すなわち、暗画素と明画素の電圧差が (V<sub>th2</sub> - V<sub>th1</sub>) 以上である場合、その境界はリスク境界と判断される。また、リスク境界ではない境界を「非リスク境界」という。

#### 【0036】

印加電圧の補正は、暗画素および明画素の少なくとも一方に対して行われる。すなわち、暗画素の印加電圧を上げるように補正してもよいし、明画素の電圧を下げるよう印加電圧を補正してもよいし、その両方を行ってもよい。補正によって暗画素と明画素との印加電圧の差がしきい値を下回れば、リバースチルトドメインは発生しない。しかし、この補正には、次のような問題点がある。

#### 【0037】

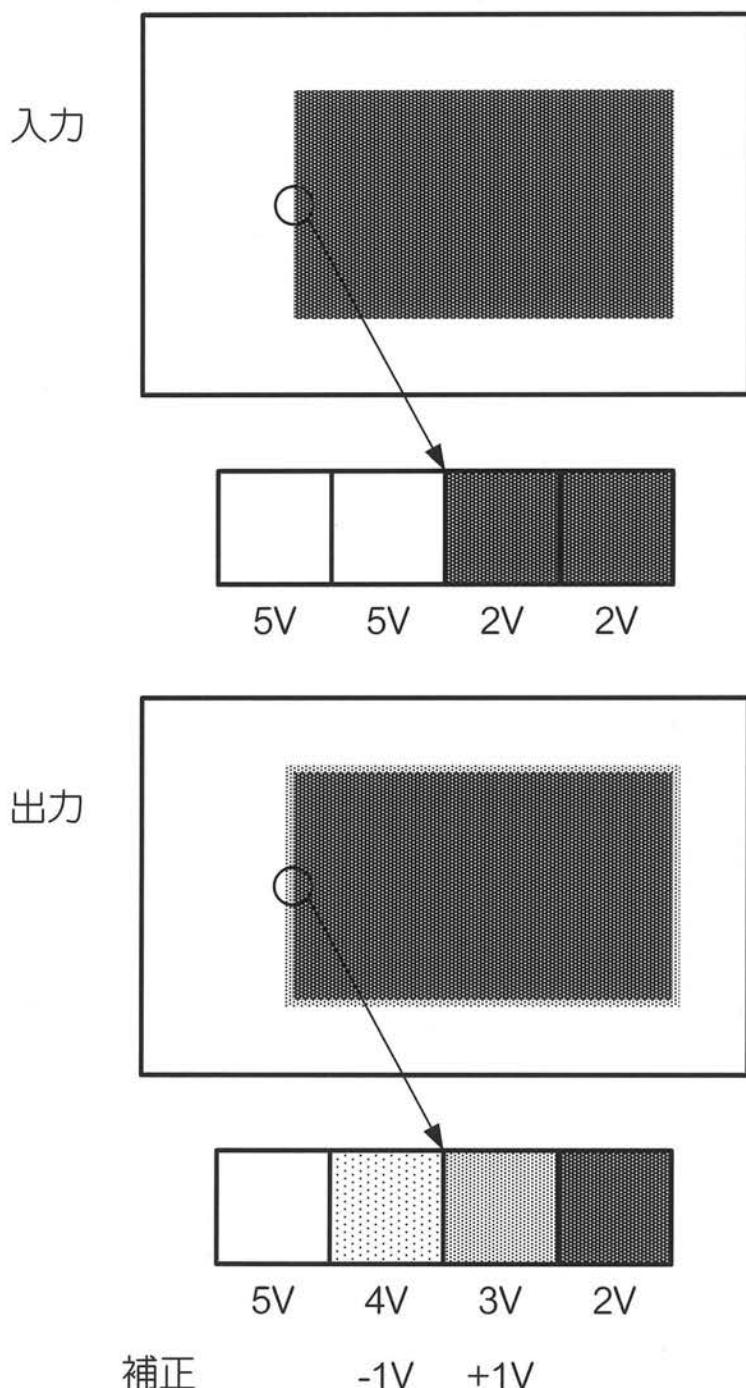

図 6 は、従来の補正を例示する図である。この例では、横方向に連続する 4 つの画素について、映像信号 V<sub>id-in</sub> により示される印加電圧が、5V、5V、2V、および2V である。左から 2 番目の画素および 3 番目の画素の境界がリスク境界である。すなわち、左から 2 番目の画素が明画素であり、3 番目の画素が暗画素である。この例では、暗画素と明画素との電位差を小さくする補正により、明画素の印加電圧が 1V 減らされ、暗画素の印加電圧が 1V 増やされる。この補正によれば、暗画素と明画素との電位差は減少するが、境界のコントラストが低下することにより、輪郭がぼやけてしまうという問題がある。本実施形態は、境界のコントラストを低下させずに、リバースチルトドメインを抑制する（配向不良を緩和させる）技術を提供する。

#### 【0038】

##### 2 . 第 1 実施形態

###### 2 - 1 . 装置構成

図 7 は、第 1 実施形態に係る液晶表示装置 1 の構成を示すブロック図である。液晶表示装置 1 は、カラー画像を表示する装置であり、例えばプロジェクター（電子機器の一例）に用いられる。液晶表示装置 1 は、液晶パネル 100、走査線駆動回路 130、およびデータ線駆動回路 140 を 3 組と、制御回路 10 とを有する。各組は、それぞれ、色成分 R、色成分 G、および色成分 B に対応している。ここでは、図面が煩雑になるのを避けるため、1 組の液晶パネル 100、走査線駆動回路 130、およびデータ線駆動回路 140 の

10

20

30

40

50

みを図示している。

【0039】

制御回路10は、上位装置から供給される映像信号Vid-inおよび同期信号Syncに応じて走査線駆動回路130およびデータ線駆動回路140を制御する信号を出力する。映像信号Vid-inは、液晶パネル100における各画素の階調値をそれぞれ指定するデジタル信号である。映像信号Vid-inは、同期信号Syncと同期して供給される。同期信号は、垂直走査信号、水平走査信号およびドットクロック信号（いずれも図示省略）を含んでいる。この例で、映像信号Vid-inの周波数は60Hzである。すなわち、映像信号Vid-inにより示される画像は、16.67ミリ秒毎に書き換えられる。

10

【0040】

なお、映像信号Vid-inは直接的には階調値を指定するものであるが、階調値に応じて液晶素子に印加される電圧（以下「印加電圧」という）が定まるので、映像信号Vid-inは液晶素子の印加電圧を指定するものといえる。

【0041】

制御回路10は、走査制御回路20と画像処理回路30とを有する。走査制御回路20は、制御信号Xctr、制御信号Yctr、制御信号Ictr等、各種の制御信号を生成して、同期信号Syncに同期して各部を制御する。画像処理回路30は、デジタルの映像信号Vid-inを処理して、各色成分毎にアナログのデータ信号Vxを出力する。映像信号Vid-inは、(m×n)個の画素の各々について、複数の色成分の階調値を示す入力映像信号の一例である。

20

【0042】

図8は、画像処理回路30の構成を示す図である。この例で、画像処理回路30は、リスク境界の隣の画素（リスク境界を挟む画素）のうち少なくとも1つの画素の印加電圧を補正する。以下、補正される画素を補正画素という。この例で、補正画素の印加電圧は、入力映像信号により示される階調値に応じた電圧（以下この電圧を「補正前電圧」といい、後述する処理により補正された電圧を「補正後電圧」という）より高い第1電圧と、補正前電圧より低い第2電圧を時分割で交互に印加するパターンに補正される。時分割された一期間は、液晶分子の配向不良が発生するまでの時間よりも短い期間である。

30

【0043】

なお、液晶分子の配向不良が発生するまでの時間は、例えば以下の方法により決定される。全面が最高階調（例えば白）の画像が表示された状態から、一部の領域に最低階調（例えば黒）となる画像を表示させる。このときに、最高階調の領域と最低階調の領域の境界部分を観察する。境界部分には配向不良が発生し、例えば白画素の領域に、黒くなる部分が発生する。この部分の光学状態（例えば輝度）の時間変化を観測し、飽和状態に致るまでの時間、または最小値（または最大値）に対して所定の係数（例えば90%）を乗算した光学状態に至るまでの時間を、配向不良が発生するまでの時間とする。

【0044】

本実施形態において、第1電圧のデューティ比は補正前電圧によらず固定されており、第1電圧および第2電圧の電圧値は、補正前電圧に応じて変化する。第1電圧のデューティ比は固定されており、この例では0.5である。なお、第1電圧のデューティ比とは、第1電圧および第2電圧のパターンの1サイクル分の期間に対する、第1電圧が印加される期間の比をいう。デューティ比が0.5であるということは、第1電圧が印加される時間と第2電圧が印加される時間が等しいことを意味する。

40

【0045】

画像処理回路30は、遅延回路31と、境界検出部32と、補正部33と、D/A変換器34とを有する。なお、画像処理回路30の前段または画像処理回路30内において遅延回路31の前段には、映像信号Vid-inにより示される階調値を、例えばLUT（Look Up Table）を参照して電圧に変換する変換部が設けられている。この例で、画像処理回路30は、印加電圧を示す信号（説明の便宜上、この信号も映像信号Vid-inと

50

表記する)に対して以下で説明する処理を行う。

【0046】

遅延回路31は、リスク境界を検出するため、対象となる画素の印加電圧を1フレーム保持する。したがって、遅延回路31の出力信号は、映像信号Vid-inより1フレーム分(すなわち1画素分)遅れている。すなわち、遅延回路31の出力信号により印加電圧が示される画素と映像信号Vid-inにより印加電圧が示される画素とは、映像信号Vid-inにおける画素の走査方向(例えば行方向)において隣り合う画素である。

【0047】

境界検出部32は、これら2つの画素について、リスク境界の条件を満たすか判断する。以下、境界検出部32における判断の対象となる2つの画素に挟まれる境界を「対象境界」という。この例で、リスク境界の条件は、対象境界の両隣の画素の印加電圧の差(電位差)があらかじめ決められたしきい値以上であるという条件である。境界検出部32は、判断結果を示す信号(例えば、リスク境界の条件が満たされた場合にはHレベルの信号、条件が満たされなかった場合にはLレベルの信号)を出力する。

10

【0048】

補正部33は、境界検出部32の出力信号に応じて、補正前電圧を補正する。具体的には、境界検出部32の出力信号がHレベルの画素については印加電圧を補正し、Lレベルの画素については印加電圧を補正しない。また、補正部33には、フレームが切り替わるタイミングを示す信号が入力される。この信号は、例えば、奇数フレームではLレベルとなり、偶数フレームではHレベルとなる信号である。補正部33は、例えば、奇数フレームにおいては印加電圧を第1電圧に補正し、偶数フレームにおいては印加電圧を第2電圧に補正する。補正部33は、補正された印加電圧を示す信号を出力する(補正が行われない場合は、補正前電圧を示す信号を出力する)。

20

【0049】

D/A変換器34は、補正部33の出力信号をアナログ信号に変換し、データ信号Vxとして後段の回路に出力する。

【0050】

境界検出部32は、第1方向(例えば行方向)および第2方向(例えば列方向)に配置された画素111のうち第1画素(例えば暗画素)およびこの第1画素と隣り合う第2画素(例えば明画素)に挟まれた境界であって、第1画素および第2画素の印加電圧の差がしきい値以上である境界(リスク境界)を検出する境界検出手段の一例である。補正部33は、第1画素および第2画素の少なくとも一方の画素の印加電圧を、その画素の階調に応じて決まる、第1電圧およびこの第1電圧より低い第2電圧のパターンを、配向不良(ディスクリネーション)の発生速度よりも短い間隔の時分割でその画素に印加する補正を行う補正手段の一例である。D/A変換器34は、補正部33により補正された電圧に応じた信号を、画素111を有する液晶パネル100を駆動する駆動回路(例えばデータ線駆動回路140)に出力する出力手段の一例である。画像処理回路30は、上記の境界検出手段と、補正手段と、出力手段とを有する画像処理装置の一例である。

30

【0051】

2-2.動作

40

図9は、液晶表示装置1の動作を示すタイミングチャートである。この例では、1フレームが4つのフィールドに分割される、いわゆる4倍速駆動が行われる。例えば、映像信号Vid-inにより示される画像が60Hzで更新される場合、1フレームは約16.7ミリ秒である。この場合、データ信号Vxは240Hzの信号であり、1フィールドは約4.17ミリ秒である。

【0052】

各フィールドにおいて、走査線駆動回路130は、m本の走査線112を順次排他的に選択する走査信号Yiを出力する。データ線駆動回路140は、第i行の走査線112が選択されているときに、第i行第1~n列の画素のデータ信号Vxをサンプリングし、データ信号X1~Xnとして出力する。データ信号Vxの電圧は、奇数フィールドにおいて

50

正極性であり、偶数フィールドにおいて負極性である。データ信号  $V_x$  の振幅の中間電位は電位  $V_{cnt}$  である。いわゆるプッシュダウン（フィードスルー）の影響を考慮し、コモン電圧  $LCCom$  は、中間電位  $V_{cnt}$  よりも低い値に設定されている。

#### 【0053】

図10は、画像処理回路30の動作を示すフローチャートである。図10のフローは、例えば画像処理回路30への電力の供給が開始されたことを契機として、所定の間隔で繰り返し実行される。図10のフローは単一の画素についての処理のみを示しており、実際には、複数の境界の中から対象境界が一つずつ順番に特定され、対象画素について図10のフローが実行される。

#### 【0054】

ステップS100において、画像処理回路の境界検出部32は、リスク境界を検出する。すなわち、境界検出部32は、対象境界が、上述のリスク境界の条件を満たすか判断する。リスク境界の条件を満たすと判断された場合（S100：YES）、画像処理回路30は、処理をステップS110に移行する。リスク境界の条件を満たさないと判断された場合（S100：NO）、画像処理回路は、処理をステップS120に移行する。

#### 【0055】

ステップS110において、補正部33は、対象境界（リスク境界）を挟む暗画素および明画素のうち少なくとも一方の画素の印加電圧を補正する。ここでは、暗画素および明画素のうち暗画素のみが補正画素となる例（片側補正）を説明する。

#### 【0056】

ステップS110における補正処理の詳細は以下のとおりである。まず、補正部33は、第1電圧および第2電圧の値  $V_1$  および  $V_2$  を決定する。この例で、補正部33は、印加電圧の値と、その印加電圧に対応する第1電圧および第2電圧の値とを対応させるLUTを記憶したメモリーを有する。このLUTに印加電圧の値を入力すると、対応する第1電圧  $V_1$  および第2電圧  $V_2$  が出力される。ここで、第1電圧  $V_1$  および第2電圧  $V_2$  は、以下の条件を満たす電圧である。

$$(a) V_2 > (V_{id-in}) > V_1 \quad \dots (1) \quad \text{かつ}$$

$$(b) P_1 \times d_1 + P_2 \times d_2 = P_{in} \quad \dots (2)$$

なお、 $P_1$  および  $P_2$  はそれぞれ、電圧  $V_1$  および  $V_2$  が印加された場合の画素111の階調値を示す。また、 $P_{in}$  は、入力映像信号  $V_{id-in}$  により示される階調値を示す。さらに、 $d_1$  は第1電圧のデューティ比を、 $d_2$  は第2電圧のデューティ比を表す。この例では、 $d_1 = d_2 = 0.5$  である。

#### 【0057】

式(1)は、第1電圧が補正前電圧より低く、第2電圧が補正前電圧より高いことを意味する。式(2)は、所定の期間（第1電圧を印加する期間と第2電圧を印加する期間が繰り返されるサイクルの基本周期。この例では2フレーム）における階調値の積分が、入力映像信号により示される階調値の積分と等しいことを意味する。

#### 【0058】

次に、補正部33は、フレームの偶奇に応じて、第1電圧  $V_1$  および第2電圧  $V_2$  のうちいずれを補正後の電圧として用いるか決定する。例えば、補正部33は、奇数フレームにおいては第1電圧  $V_1$  を、偶数フレームにおいては第2電圧  $V_2$  を、補正後電圧として用いる。

#### 【0059】

ステップS120において、D/A変換器38は、印加電圧に応じたデータ信号  $V_x$  を出力する。データ信号  $V_x$  は、補正が行われた画素については補正後電圧を、補正が行われていない画素については補正前電圧を示している。また、フレーム内において、奇数フィールドにおいては正極性の電圧が印加され、偶数フィールドにおいては負極性の電圧が印加される。

#### 【0060】

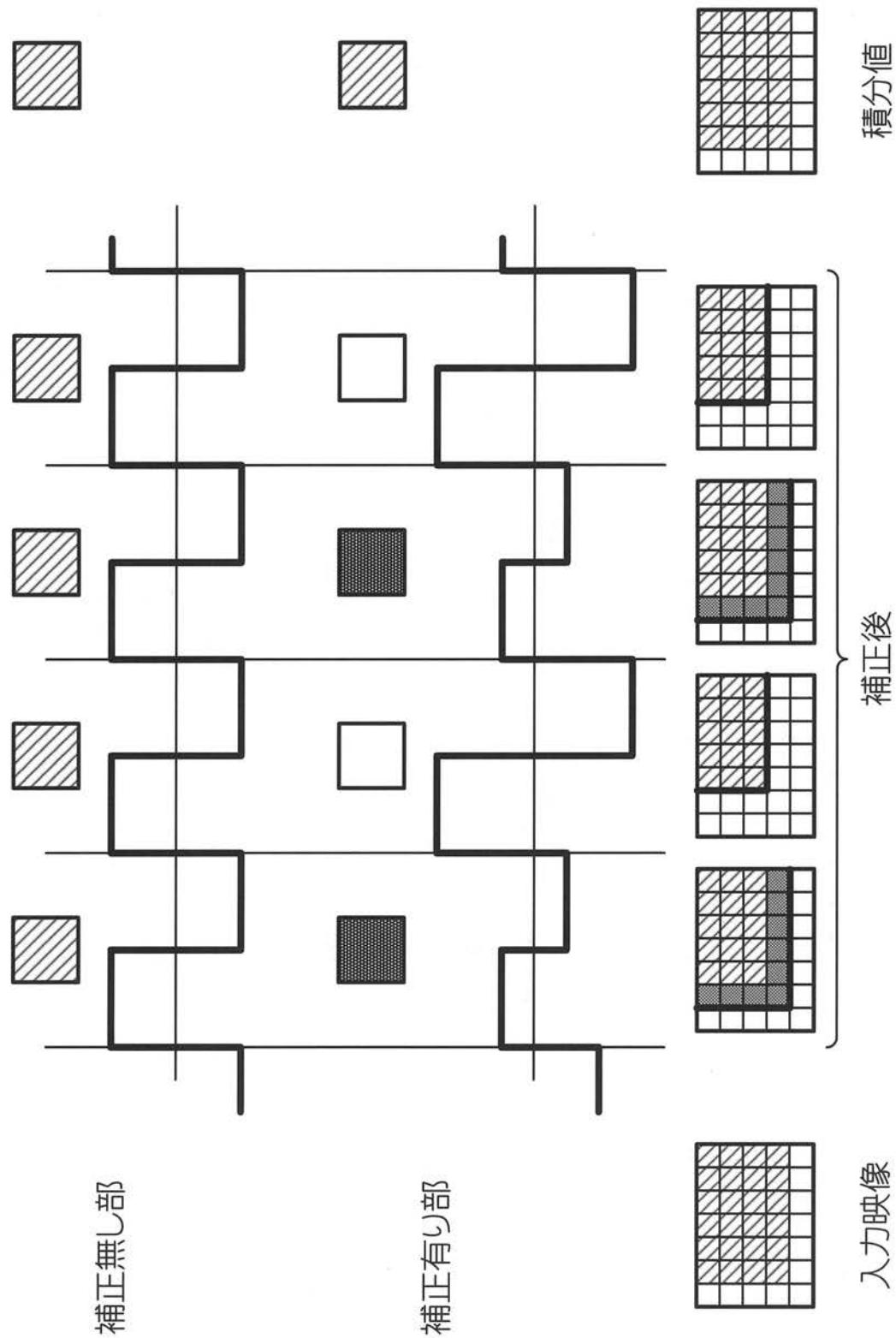

図11は、第1実施形態における補正の具体例を示す図である。この例では、連続する

10

20

30

40

50

4つのフレームにおいて変化しない画像（すなわち静止画）に補正が適用されている。この例では、白い背景の上に中間階調で塗られた四角形（図では4行6列の画素で構成される）のパターンが形成されている。図11には、この四角形を構成する画素のうち、補正されない画素（補正無し画素）と補正される画素（補正有り画素）のそれにおける印加電圧が示されている。なおこの例では、図面を簡略化するため、1フレームが2フィールドに分割されており、各フレームにおいて、奇数フィールドでは正極性の電圧が、偶数フィールドでは負極性の電圧が、それぞれ印加される例が示されている。

#### 【0061】

この例によれば、第1電圧が印加されるフレームと第2電圧が印加されるフレームとで、リスク境界の位置（図において太線で示されている）が移動している。このとき、1フレームの時間、すなわち、印加電圧が第1電圧から第2電圧に（またはその逆に）切り替えるまでの時間がディスクリネーションの発生する時間よりも短ければ、ディスクリネーションの発生が低減される。さらにこの例では、所定期間（例えば2フレーム）における階調値の積分値が、入力映像信号V<sub>i d - i n</sub>により示される階調値に等しくなるように補正が行われる。したがって、リスク境界を挟む画素の電位差が小さくなるように単純に補正をする場合と比較して、画像の輪郭部分のコントラストの低下（ボケ）を低減することができる。

10

#### 【0062】

##### 3. 第2実施形態

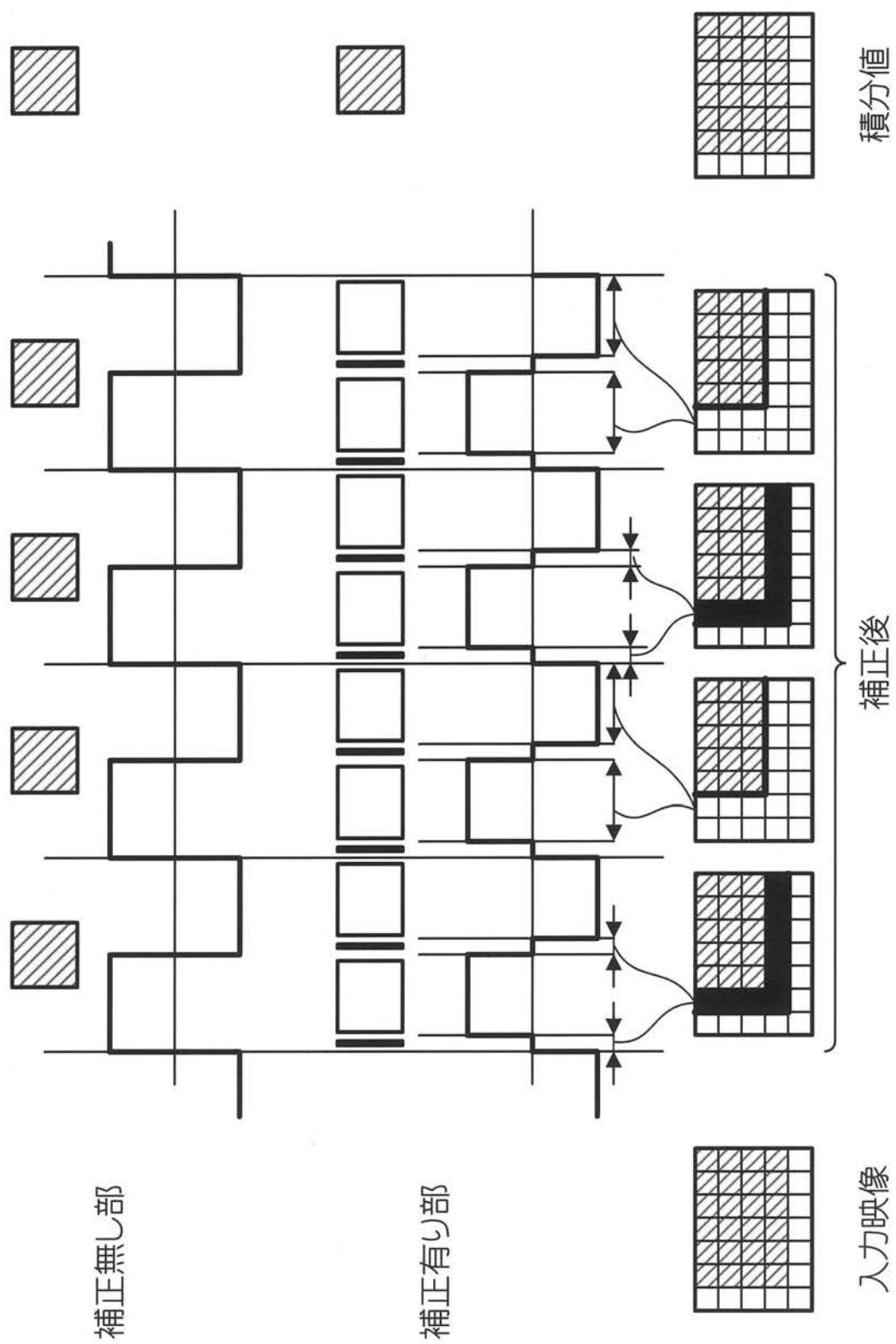

第1実施形態においては、第1電圧のデューティ比が固定されており、補正画素の階調値に応じて第1電圧および第2電圧が決められる例を説明した。第2実施形態においては、第1電圧および第2電圧が固定されており、補正画素の階調値に応じてデューティ比が決められる例を説明する。なお以下において第1実施形態と共通する事項については説明を省略する。

20

#### 【0063】

第2実施形態において、ステップS110における補正処理の詳細は以下のとおりである。まず、補正部33は、第1電圧のデューティ比d1を決定する。この例で、補正部33は、印加電圧の値と、その印加電圧に対応するデューティ比とを対応させるLUTを記憶したメモリーを有する。このLUTに印加電圧の値を入力すると、対応するデューティ比d1が出力される。この例で、第1電圧V1は最高階調（白）に相当する電圧であり、第2電圧V2は最低階調（黒）に相当する電圧であり、いずれも固定されている。デューティ比d1は、第1実施形態でも説明した式(2)の条件(b)を満たす。

30

$$(b) P_1 \times d_1 + P_2 \times d_2 = P_{in} \dots (2)$$

なお、d1 + d2 = 1である。

#### 【0064】

第2実施形態において、走査制御回路20は、走査線112の走査を開始させる制御信号Y<sub>c t r</sub>を同期信号Syncに同期して出力するだけでなく、画像処理回路30からの指示に応じて、制御信号Y<sub>c t r</sub>を出力する。詳細には以下のとおりである。補正部33は、制御信号I<sub>c t r</sub>により新たなフィールドが開始されたことが示されると、第1電圧V1を補正電圧として用いる。新たなフィールドが開始されてから、デューティ比d1に相当する時間t1(t1 = tf × d1。tfは1フレームの時間を示す)が経過すると、補正部33は、走査線112の走査開始を走査制御回路20に指示する。また、このタイミングで、補正部33は、第2電圧V2を補正電圧として用いる。

40

#### 【0065】

図12は、第2実施形態における補正の具体例を示す図である。この例によれば、1フィールド内において、第1電圧が印加される期間と第2電圧が印加される期間とで、リスク境界の位置（図において太線で示されている）が移動している。このとき、第1電圧が連続して印加される時間および第2電圧が連続して印加される時間がディスクリネーションの発生する時間よりも短ければ、ディスクリネーションの発生が低減される。さらにこの例では、所定期間（例えば1フレーム）における階調値の積分値が、入力映像信号V<sub>i</sub>

50

$d - i_n$  により示される階調値に等しくなるように補正が行われる。したがって、リスク境界を挟む画素の電位差が小さくなるように単純に補正をする場合と比較して、画像の輪郭部分のコントラストの低下（ボケ）を低減することができる。

#### 【0066】

##### 4. 变形例

本発明は上述の実施形態に限定されるものではなく、種々の变形実施が可能である。以下、变形例をいくつか説明する。以下の变形例のうち2つ以上のものが組み合わせて用いられてもよい。

#### 【0067】

##### 4-1. 变形例1

第1実施形態において補正部33が第1電圧V1および第2電圧V2を決定する方法、並びに第2実施形態において補正部33がデューティ比d1を決定する方法は、LUTを用いるものに限定されない。例えば、第1実施形態において、補正部33は、入力映像信号により示される印加電圧V<sub>in</sub>に対し、所定の補正量Vを加算した電圧を第1電圧V1とし、Vを減算した電圧を第2電圧V2としてもよい。

$$V_1 = V_{in} + V \quad \dots (3)$$

$$V_2 = V_{in} - V \quad \dots (4)$$

なおこの方法では、補正画素の階調値の積分が、入力映像信号V<sub>id</sub>-<sub>i</sub><sub>n</sub>により示される階調値の積分と等しくならない場合もあるが、電圧幅2Vの範囲で液晶素子120のV-T特性が線形であるという近似によれば、補正画素の階調値の積分は、入力映像信号V<sub>id</sub>-<sub>i</sub><sub>n</sub>により示される階調値の積分とほぼ等しい（誤差が許容範囲内）といえる。

#### 【0068】

##### 4-2. 变形例2

第1実施形態および第2実施形態においては、リスク境界を挟む暗画素および明画素のうち暗画素のみを補正する片側補正の例を説明した。しかし、補正画素となる画素は、暗画素に限定されない。明画素が補正されてもよいし、暗画素および明画素が両方とも補正されてもよい（両側補正）。なお、暗画素と明画素のうち、少なくとも、印加電圧がより低い画素の印加電圧が補正されることが好ましい。

#### 【0069】

##### 4-3. 变形例3

対象境界がリスク境界と判定される条件は、実施形態で説明したものに限定されない。例えば、実施形態で説明した条件に加え、液晶分子のチルト方位を考慮して以下の条件が追加されてもよい。

- ・対象境界において、印加電圧が高い画素が、印加電圧の低い画素に対して、チルト方位の上流側に位置する。

この条件を追加することにより、補正が行われる画素が、リバースチルトドメインが発生する確率がより高いものに絞り込まれ、映像信号V<sub>id</sub>-<sub>i</sub><sub>n</sub>により示される元の画像からの変更が多すぎることによる画質の低下を抑制することができる。

#### 【0070】

なお、チルト方位とは、液晶素子120にゼロVの電圧を印加した状態（初期配向状態）における、画素電極118の側から平面視したときの、Y軸（データ線114）からの液晶分子の傾きの方向をいう。また、液晶分子は、初期配向状態において画素電極118（素子基板100a）に対しても傾いている。素子基板100aの基板法線を基準にした液晶分子の傾きをチルト角という。チルト方位について、液晶分子の素子基板100aに近い方を上流側、素子基板100aから遠い方を下流側という。例えば、チルト方位が45°であり、画素電極118の側から平面視したとき素子基板100aの法線に対して液晶分子が右上方向（X軸正方向かつY軸負方向）に傾いている場合、左下がチルト方位の上流側であり、右上がチルト方位の下流側である。

#### 【0071】

##### 4-4. 变形例4

10

20

30

40

50

図13は、変形例5に係るプロジェクター2100を例示する図である。プロジェクター2100は、液晶表示装置1を用いた電子機器の一例である。プロジェクター2100において、液晶パネル100がライトバルブとして用いられている。この図に示されるように、プロジェクター2100の内部には、ハロゲンランプ等の白色光源を有するランプユニット2102が設けられている。ランプユニット2102から射出された投射光は、内部に配置された3枚のミラー2106および2枚のダイクロイックミラー2108によってR(赤)色、G(緑)色、B(青)色の3原色に分離される。分離された投射光は、各原色に対応するライトバルブ100R、100Gおよび100Bにそれぞれ導かれる。なお、B色の光は、他のR色やG色と比較すると光路が長いので、その損失を防ぐために、入射レンズ2122、リレーレンズ2123および出射レンズ2124を有するリレーレンズ系2121を介して導かれる。

10

#### 【0072】

プロジェクター2100において、液晶パネル100を含む液晶表示装置が、R色、G色、B色のそれぞれに対応して3組設けられている。ライトバルブ100R、100Gおよび100Bの構成は、上述した液晶パネル100と同様である。R色、G色、B色のそれぞれの原色成分の階調レベルを指定するに映像信号がそれぞれ外部上位回路から供給されて、ライトバルブ100R、100Gおよび100Bがそれぞれ駆動される。ライトバルブ100R、100G、100Bによってそれぞれ変調された光は、ダイクロイックプリズム2112に3方向から入射する。そして、ダイクロイックプリズム2112において、R色およびB色の光は90度に屈折し、G色の光は直進する。したがって、各原色の画像が合成された後、スクリーン2120には、投射レンズ群2114によってカラー画像が投射される。

20

#### 【0073】

なお、ライトバルブ100R、100Gおよび100Bには、ダイクロイックミラー2108によって、R色、G色、B色のそれぞれに対応する光が入射するので、カラーフィルタを設ける必要はない。また、ライトバルブ100R、100Bの透過像は、ダイクロイックプリズム2112により反射した後に投射されるのに対し、ライトバルブ100Gの透過像はそのまま投射される。したがって、ライトバルブ100R、100Bによる水平走査方向は、ライトバルブ100Gによる水平走査方向と逆向きにして、左右を反転させた像を表示する構成となっている。

30

#### 【0074】

電気光学装置1が用いられる電子機器としては、図10に例示したプロジェクターの他にも、テレビジョンや、ビューファインダー型・モニタ直視型のビデオテープレコーダー、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、デジタルスチルカメラ、携帯電話機、タッチパネルを備えた機器等などが挙げられる。

30

#### 【0075】

##### 4-5.他の変形例

実施形態においては、リスク境界の検出や補正処理は印加電圧を示すデータに対して行われたが、階調値を示すデータに対してこれらの処理が行われてもよい。

40

液晶105は、VA液晶に限定されない。TN液晶等、VA液晶以外の液晶が用いられてもよい。また、液晶105は、ノーマリーホワイトモードの液晶であってもよい。

実施形態で説明したパラメーター(例えば、階調数、フレーム周波数、画素数など)および信号の極性やレベルはあくまで例示であり、本発明はこれに限定されない。

#### 【符号の説明】

#### 【0076】

1...液晶表示装置、10...制御回路、20...走査制御回路、30...画像処理回路、31...遅延回路、32...境界検出部、33...補正部、34...D/A変換器、100...液晶パネル、105...液晶、108...コモン電極、111...画素、112...走査線、114...データ線、115...容量線、116...TFT、118...画素電極、120...液晶素子、125...

50

保持容量、130...走査線駆動回路、140...データ線駆動回路

【図4】

【図7】

【図5】

【図8】

【図9】

【図10】

【図13】

【図 6】

【図 11】

【図 12】

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 1 P |

| G 0 9 G | 3/20  | 6 4 1 A |

| G 0 9 G | 3/20  | 6 4 1 K |

| G 0 9 G | 3/20  | 6 4 2 A |

| G 0 9 G | 3/20  | 6 5 0 M |

| G 0 9 G | 3/20  | 6 1 2 U |

| G 0 9 G | 3/20  | 6 4 2 E |

| G 0 2 F | 1/133 | 5 0 5   |

F ターム(参考) 2H193 ZA04 ZA07 ZB16 ZC16 ZC39 ZE04 ZH23 ZH53 ZR04

5C006 AA15 AA16 AA17 AC21 AF46 AF53 AF71 BB16 FA18 FA25

FA54

5C080 AA10 BB05 DD05 EE28 FF11 JJ01 JJ02 JJ03 JJ04 JJ05

JJ06 JJ07

|                |                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 图像处理设备，液晶显示设备，电子设备和驱动方法                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2014149493A</a>                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2014-08-21 |

| 申请号            | JP2013019407                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2013-02-04 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 若林淳一<br>西村陽彥<br>保坂宏行                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 若林 淳一<br>西村 陽彥<br>保坂 宏行                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                     |         |            |

| F1分类号          | G09G3/36 G09G3/20.623.C G09G3/20.621.A G09G3/20.623.D G09G3/20.641.C G09G3/20.641.P<br>G09G3/20.641.A G09G3/20.641.K G09G3/20.642.A G09G3/20.650.M G09G3/20.612.U G09G3/20.642.E G02F1/133.505                                                                                                                                                                  |         |            |

| F-Term分类号      | 2H193/ZA04 2H193/ZA07 2H193/ZB16 2H193/ZC16 2H193/ZC39 2H193/ZE04 2H193/ZH23 2H193/ZH53 2H193/ZR04 5C006/AA15 5C006/AA16 5C006/AA17 5C006/AC21 5C006/AF46 5C006/AF53 5C006/AF71 5C006/BB16 5C006/FA18 5C006/FA25 5C006/FA54 5C080/AA10 5C080/BB05 5C080/DD05 5C080/EE28 5C080/FF11 5C080/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C080/JJ07 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                       |         |            |

## 摘要(译)

解决的问题：在抑制对准缺陷的同时，抑制具有发生对准缺陷的风险的两个像素之间的对比度的恶化。解决方案：图像处理器具有边界检测装置，该边界检测装置用于检测夹在第一像素和第二像素之间的边界。在第一方向和第二方向上排列的像素组中与第一像素相邻的第二像素，其中第一像素和第二像素的输入视频信号所示的施加电压之间的差等于或大于阈值，校正装置，用于执行校正，该校正装置将至少一个像素的施加电压施加在第一像素和第二像素之间，以及根据像素的灰度级确定的第一电压和低于第一电压的第二电压的图案。以比对准缺陷的发生速度短的间隔的时分方式输出像素，以及用于输出的输出装置将与由校正装置校正的电压相对应的信号提供给用于驱动具有像素组的液晶面板的驱动电路。