(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-180414

(P2018-180414A)

(43) 公開日 平成30年11月15日(2018.11.15)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2 H 1 9 3   |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 5 C 0 0 6   |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20 | 5 C 0 8 0   |

|                             | G09G 3/20 | 6 2 3 R     |

|                             | G09G 3/20 | 6 2 1 G     |

|                             | G09G 3/20 | 6 7 0 K     |

審査請求 未請求 請求項の数 5 O L (全 12 頁) 最終頁に続く

|           |                            |          |                                                |

|-----------|----------------------------|----------|------------------------------------------------|

| (21) 出願番号 | 特願2017-82927 (P2017-82927) | (71) 出願人 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号     |

| (22) 出願日  | 平成29年4月19日 (2017.4.19)     | (74) 代理人 | 100108431<br>弁理士 村上 加奈子                        |

|           |                            | (74) 代理人 | 100153176<br>弁理士 松井 重明                         |

|           |                            | (74) 代理人 | 100109612<br>弁理士 倉谷 泰孝                         |

|           |                            | (74) 代理人 | 100116643<br>弁理士 伊達 研郎                         |

|           |                            | (72) 発明者 | 鷹木 二朗<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内           |

|           |                            |          | F ターム (参考) 2H193 ZA04 ZE38 ZH22 ZH52<br>最終頁に続く |

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】 液晶表示装置において、シャットダウン時に放電時に全てのゲート配線をHigh状態に一定時間維持するための電圧を確保する方法を提供する。

【解決手段】 ゲートドライバ5と、ソース配線9を駆動するソースドライバ4と、電源生成部2とを具備し、その電源生成部に入力する入力電源電圧11が所定の電圧以下に降下すると電圧降下信号14を内部生成し、複数の放電用トランジスタ10からなり、前記ソース配線の電位を放電するソース線放電回路23において、前記電圧降下信号に応じて前記放電用トランジスタをONさせて全ての前記ソース配線と放電用ドレイン配線6を導通状態とし、液晶表示パネル1内の残留電荷を、前記放電用ドレイン配線を介して放電させて、前記残留電荷を前記電源生成部のゲート配線ON電圧12の電圧生成回路に電荷回収するようにした。

【選択図】 図1

**【特許請求の範囲】**

**【請求項 1】**

複数のゲート配線および複数のソース配線とで囲まれる複数の画素電極がマトリクス状に配置され、前記画素電極に接続された複数の画素トランジスタを前記ゲート配線により供給されるゲート選択信号によって導通制御し、前記画素トランジスタを介して前記ソース配線により供給される画素書き込み電圧を、前記画素電極とその画素電極に対向して配置された対向電極との間に供給するようにした構成したマトリクス基板と、該マトリクス基板に液晶層を挟持するよう対向配置された対向基板とからなる液晶表示パネルと、前記ゲート配線に前記ゲート選択信号を供給するゲート配線制御回路と、前記ソース配線に前記画素書き込み電圧を供給するソース配線駆動回路と、前記ゲート配線制御回路と前記ソース配線駆動回路と前記対向電極の駆動電圧生成回路に電源電圧を供給する電源生成部とを具備する液晶表示装置において、

前記電源生成部に入力する入力電源電圧が所定の電圧以下に降下すると電圧降下信号を出力する電圧降下検出回路と、

複数の放電用トランジスタからなり、前記ソース配線の電位を放電するソース線放電回路と、

前記電圧降下信号に応じて前記放電用トランジスタのON/OFFを制御する放電制御信号を生成する放電制御信号生成回路を備え、

前記ソース線放電回路は、前記放電制御信号に応じて、前記放電用トランジスタをONさせて全ての前記ソース配線と放電用ドレイン配線を導通状態とし、

前記液晶表示パネル内の残留電荷を、前記放電用ドレイン配線を介して放電させ、

前記残留電荷を前記電源生成部内のゲート配線ON電源の電圧生成回路に電荷回収するようにしたことを特徴とする液晶表示装置。

**【請求項 2】**

請求項1の液晶表示装置であって、

前記電圧降下検出回路が前記入力電源電圧の電圧降下を検出すると、前記対向電極の残留電荷を前記電源生成部の前記ゲート配線ON電源の電圧生成回路に電荷回収するようにしたことを特徴とする液晶表示装置。

**【請求項 3】**

請求項1または2の液晶表示装置であって、

前記電圧降下検出回路が前記ソース配線駆動回路に含まれた液晶表示装置。

**【請求項 4】**

請求項1または2の液晶表示装置であって、

前記電圧降下検出回路が前記ゲート配線駆動回路に含まれた液晶表示装置。

**【請求項 5】**

前記画素トランジスタが酸化物半導体TFTから構成される請求項1から4のいずれか一項に記載の液晶表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

この発明は、液晶表示装置の電源停止時の残像現象や表示焼付き防止に関する。

**【背景技術】**

**【0002】**

液晶表示装置は、表示パネル内の対向電極と画素電極間にかかる電圧の強弱により、その間で挟持されている液晶層の偏光作用を用いて階調表示制御を行っている。その電圧は、対向電圧生成を伴う電源生成部や、入力信号によって画素電極への印加電圧を決めるソース配線駆動回路（以後、「ソースドライバ」と称する）や、画素電極への印加電圧を与える際のスイッチとして機能する薄膜トランジスタ（以降、「TFT」と称する）や、TFTをON/OFF制御するゲート配線制御回路（以後、「ゲートドライバ」と称する）によって制御される。

10

20

30

40

50

**【0003】**

液晶表示装置の表示部である液晶表示パネルは、液晶層にかかる電圧によって階調表現をしているが、一定時間同極性電位を印加し続けると所望の偏光作用ができなくなり、入力画像が切り替わったときにもそれまでの画像が残って見える「焼き付き」と言われる現象が発生する。通常これを解消するため、60Hz程度の周期で印加電圧の極性を切り替えている。通常動作時はこのように印加電圧の極性切り替え動作で焼きつきが防止できるが、システムの電源停止（シャットダウンとも言う）時には TFT の OFF リーク特性により、残留電荷が緩やかに放電され、「残像現象」と呼ばれる表示上の事象が発生する。

**【0004】**

さらに近年では酸化物半導体を利用した TFT などにより OFF リーク特性が向上し、TFT が OFF 状態（非導通状態）時に電荷が抜けにくくなつた。画素電極の印加電圧が残ったままになると最終画像がそのまま残るという残像現象が発生すると共に、次の電源立ち上げ時に上述した焼きつきが発生してしまう。

10

**【0005】**

これを解決するためシステム停止時には入力信号の有無を判断し、表示パネル内の残留電荷を放電する回路を取り入れるなどの対策が周知であるが、入力信号と電源が通常入力状態から入力コネクタを抜く、など定常動作から突然電源を OFF するときは上記残留電荷が放電されず、残像現象や焼き付きが発生する。

**【0006】**

また、特許文献 1 では電源停止時の放電方法が記載されているが、放電動作を行うためのロジック回路を動作させるための仕組みとしてアナログ電源を電圧レギュレータで降圧してロジック電源に用いるようになっている。

20

**【先行技術文献】****【特許文献】****【0007】****【特許文献 1】特開 2015 - 210299 号公報****【発明の開示】****【発明が解決しようとする課題】****【0008】**

しかしながら、放電時にゲート配線を全て ON させるための電源確保の方法について不明であるため、ロジック動作が確保されたとしてもパネル内の TFT を全て ON させる電源確保の方法が明確でなく、放電が完全に成されるか不確かであり、残像現象や表示焼きの原因となる可能性がある。

30

**【課題を解決するための手段】****【0009】**

この発明に係る液晶表示装置の態様は、複数のゲート配線および複数のソース配線とで囲まれる複数の画素電極がマトリクス状に配置され、前記画素電極に接続された複数の画素トランジスタを前記ゲート配線により供給されるゲート選択信号によって導通制御し、前記画素トランジスタを介して前記ソース配線により供給される画素書き込み電圧を、前記画素電極とその画素電極に対向して配置された対向電極との間に供給するようにした構成したマトリクス基板と、該マトリクス基板に液晶層を挟持するよう対向配置された対向基板とからなる液晶表示パネルと、前記ゲート配線に前記ゲート選択信号を供給するゲートドライバと、前記ソース配線に前記画素書き込み電圧を供給するソースドライバと、前記ゲートドライバと前記ソースドライバと前記対向電極の駆動電圧生成回路に電源電圧を供給する電源生成部とを具備する液晶表示装置において、前記電源生成部に入力する入力電源電圧が所定の電圧以下に降下すると電圧降下信号を出力する電圧降下検出回路と、

40

複数の放電用トランジスタからなり、前記ソース配線の電位を放電するソース線放電回路と、前記電圧降下信号に応じて前記放電用トランジスタの ON / OFF を制御する放電制御信号を生成する放電制御信号生成回路を備え、前記ソース線放電回路は、前記放電制御信号に応じて、前記放電用トランジスタを ON させて全ての前記ソース配線と放電

50

用ドレイン配線を導通状態とし、前記液晶表示パネル内の残留電荷を、前記放電用ドレイン配線を介して放電させ、前記残留電荷を前記電源生成部内のゲート配線ON電源の電圧生成回路に電荷回収するようにしたことを特徴とする。

**【発明の効果】**

**【0010】**

液晶表示装置において、電源停止時にパネル内電荷を有効的に用いて、画素に溜まった電荷を早期に放電させ、残像現象や表示焼付きを低減する。

**【図面の簡単な説明】**

**【0011】**

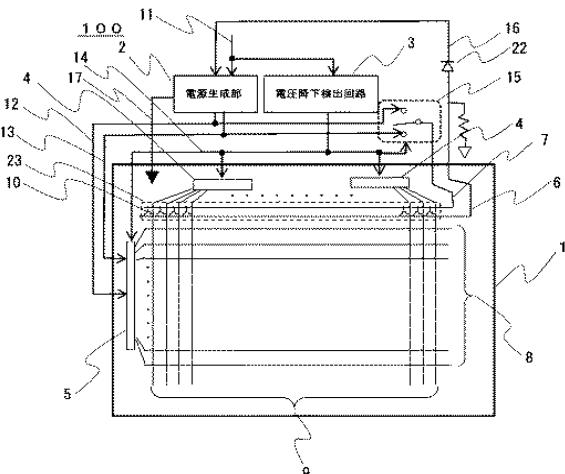

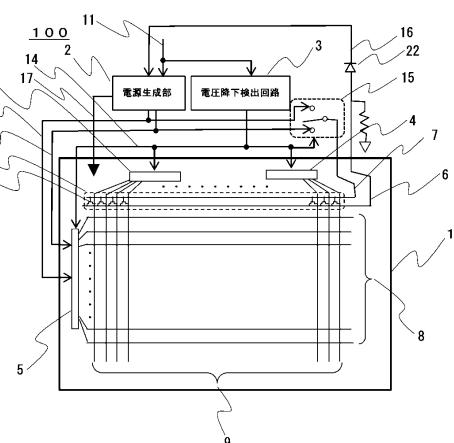

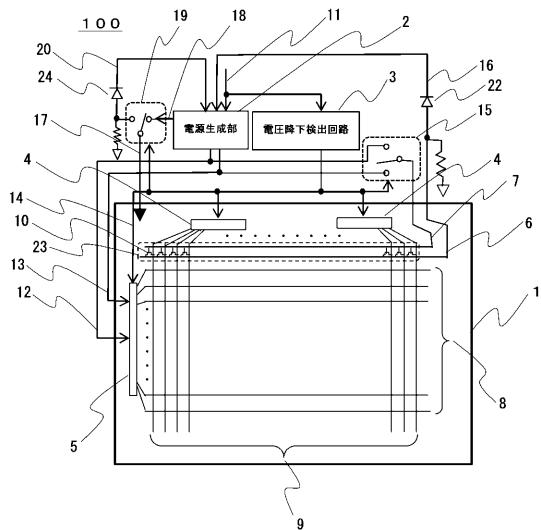

【図1】実施の形態1に係る液晶表示装置の構成を表すブロック図である。 10

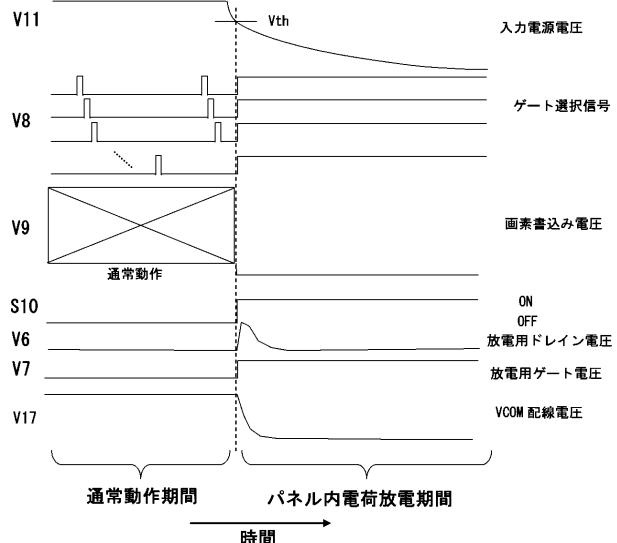

【図2】シャットダウン時のソース線放電回路に係る信号のタイミングチャートである。

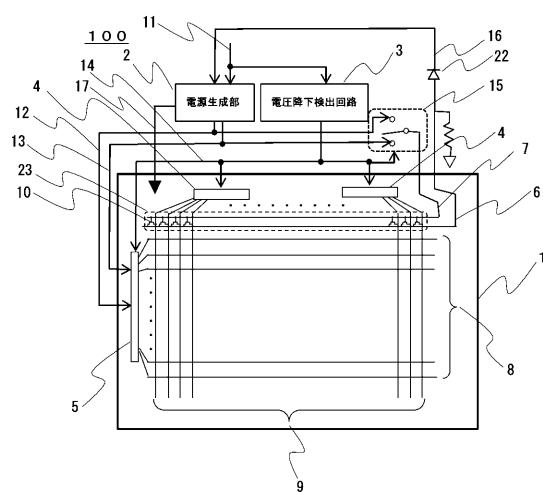

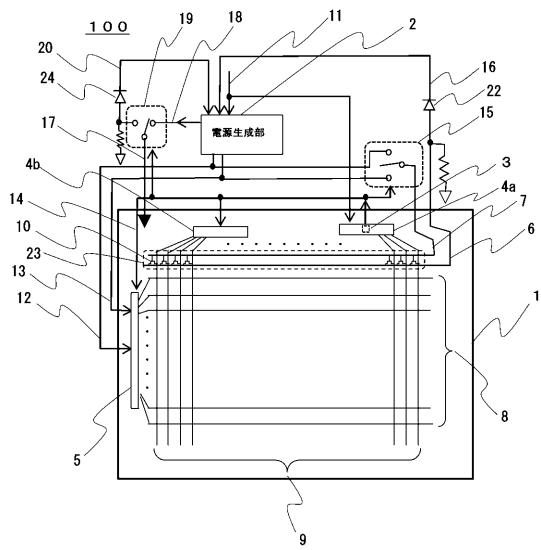

【図3】実施の形態2に係る液晶表示装置の構成を表すブロック図である。

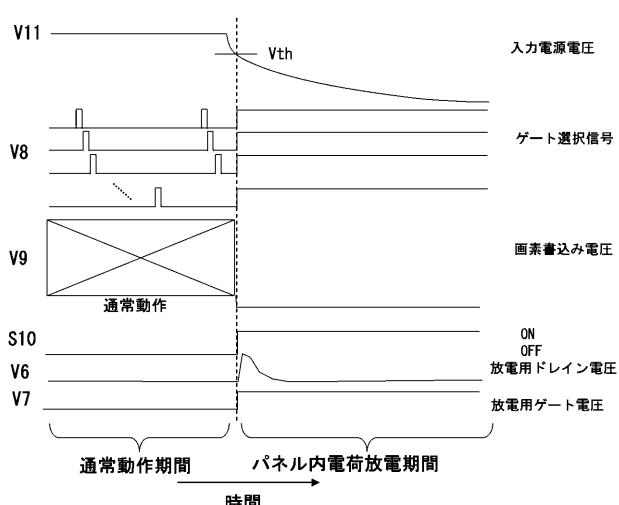

【図4】図3中のVCOM配線のシャットダウン時における信号波形のタイミングチャートである。

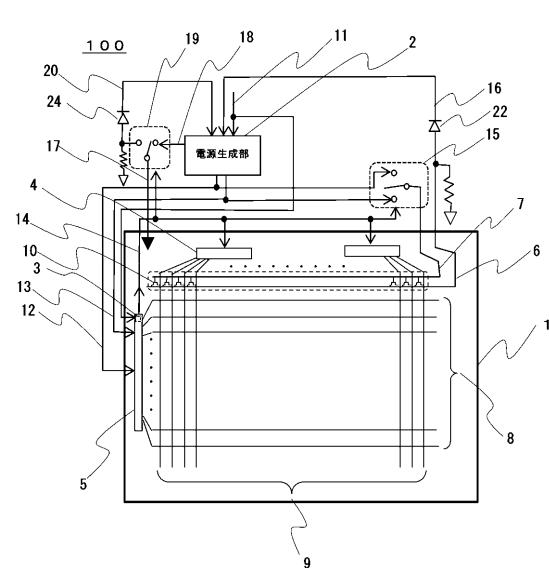

【図5】実施の形態3に係る液晶表示装置の構成を表すブロック図である。

【図6】図5中のソースドライバの検出信号出力ポート構成例である。

【図7】実施の形態4に係る液晶表示装置の構成を表すブロック図である。

【図8】図1の電源生成部の構成図である。

**【発明を実施するための形態】**

**【0012】**

実施の形態1.

本発明の実施の形態について以下に図面を参照して説明する。以下の説明は、本発明の好適な実施の形態を示すものであって、本発明の範囲が以下の実施の形態に限定されるものではない。以下の説明において、同一の符号が付されたものは実質的に同様の内容を示している。

**【0013】**

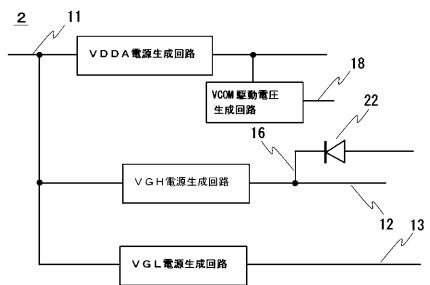

図1は本実施の形態1に係る液晶表示装置の構成を表すブロック図である。図1において、液晶表示装置100は、複数の表示用ゲート配線8および複数の表示用ソース配線9とで囲まれる複数の表示用画素電極（非図示）が行列状に配置され、その画素電極に接続された複数の画素 TFT を前記ゲート配線8により供給されるゲート選択信号によってON/OFF制御し、前記画素 TFT を介して、表示用ソース配線9により供給される画素書き込み電圧を前記画素電極と、この画素電極に対向して配置された対向電極（非図示）との間に供給するようにしたマトリクス基板と、このマトリクス基板に、液晶層を挟持して対向配置された対向基板（非図示）と、前記ゲート配線に前記ゲート選択信号を供給するゲートドライバ5と、前記表示用ソース配線9に前記画素書き込み電圧を供給するソースドライバ4と、これらソースドライバ4とゲートドライバ5に、アナログ電圧（VDDA）、ゲートON電圧（VGH）、ゲートOFF電圧（VGL）などの各種電源を供給する電源生成部2などから構成される。図8に電源生成部2の構成図を示す。 30

**【0014】**

本実施の形態1においては、さらに液晶表示パネル1の中に放電用ドレイン配線6と放電用ゲート配線7と複数の放電用TFT10から成るソース線放電回路23を設ける。ソース線放電回路23内の複数の放電用TFT10の各ソース電極はそれぞれ前記複数の表示用ソース配線9に接続され、各ドレイン電極は共通の一本の放電用ドレイン配線6に接続され、各ゲート電極は共通の一本の放電用ゲート配線7に接続されている。 40

**【0015】**

電源生成部2に入力する入力電源11の電源電圧は、通常3.3Vまたは5Vが規定電圧であるが、その電圧降下を検出するため入力電源11が電圧降下検出回路3にも入力している。電圧降下検出回路3は入力電源11の電圧低下を検出すると、電圧低下検出信号14を放電用スイッチ15（第1の放電用スイッチ）、ソースドライバ4およびゲートドライバ5に出力する。放電用スイッチ15は、電圧低下検出信号14によって切り換え制 50

御される切換回路（放電制御信号生成回路）であり、電圧低下検出信号 14 が Low のときは、放電用ゲート配線 7 がゲート OFF 電圧 13 に接続され、電圧低下検出信号 14 が High の時は、放電用ゲート配線 7 がゲート ON 電圧 12 (VGH) に接続される。また、ゲート ON 電圧 12 およびゲート OFF 電圧 13 (VGL) は、電源生成部 2 からゲートドライバ 5 にも入力され、ゲートドライバ 5 の出力段用電源となる。対向電極の駆動電位（以後、VCOM 駆動電圧と称する）も電源生成部 2 にて生成され、VCOM 配線 17 を介して VCOM 駆動電圧 18 が液晶パネル 1 に供給される。

#### 【0016】

上述したような構成を採用した本実施の形態 1 の液晶表示装置 100 は、通常表示状態では、入力電源 11 が所定の電圧以上であり、電圧低下検出信号 14 が Low となり、放電用スイッチ 15 内の放電用ゲート配線 7 はゲート OFF 電圧 13 に接続され、その結果ソース線放電回路 23 内の各放電用 TFT 10 のゲート電極には Low の電圧が印加され、各放電用 TFT 10 は全て OFF 状態（非導通状態）である。この場合、液晶パネル 1 の表示への影響はない。

10

#### 【0017】

一方、シャットダウン時は、入力電源 11 が降下し、所定の電圧を下回ると、電圧降下検出回路 3 から出力する電圧低下検出信号 14 が High 状態となり、放電用スイッチ 15 内で放電用ゲート配線 7 がゲート ON 電圧 12 に接続され、ソース線放電回路 23 内の各放電用 TFT 10 のゲート電極には High の電圧が印加され、各放電用 TFT 10 は全て ON 状態となる。これにより表示用ソース配線 9 は全て放電用ドレイン配線 6 と導通状態となる。

20

#### 【0018】

このようにゲート配線 7 の電圧は、ゲート ON 電圧 12 またはゲート OFF 電圧 13 のどちらか择一であり、ソース線放電回路 23 の放電機能 ON / OFF を制御する信号（放電制御信号）である。この放電制御信号が、ソース線放電回路 23 内の複数の放電用 TFT 10 の ON / OFF を制御する。従って、放電用スイッチ 15 は、ソース線放電回路 23 の放電制御信号生成回路である。

30

#### 【0019】

このように入力電源 11 の電圧降下を検出した時は、また、電圧低下検出信号 14 の High の状態がゲートドライバ 5 とソースドライバ 4 に入力し、先ずゲートドライバ 5 は表示用ゲート配線 8 の全出力端子を High 出力（以後、ALL\_ON と称する）となるよう制御する。また同時に電圧低下検出信号 14 の High の状態が入力したソースドライバ 4 はその全出力をハイ・インピーダンス状態（以後、Hi-Z と称する）となるよう制御し、その結果、全ての表示用ソース配線 9 がソースドライバ 4 の出力部から切り離される。この状態で、表示用ゲート配線 8 の全出力端子が High であるため、全ての画素 TFT（非図示）が ON 状態（導通状態）となり、液晶パネル 1 内の全ての表示用画素電極が各表示用ソース配線 9 と接続される。こうして画素電極（補助容量も含む）から各表示用ソース配線 9 への放電経路が確保される。

#### 【0020】

上述したように、入力電源 11 の電圧降下を検出によって、液晶パネル 1 内の全画素電極が、画素 TFT、表示用ソース配線 9 および放電用 TFT 10 を介して放電用ドレイン配線 6 と接続されるため、液晶パネル 1 内の残留電荷が放電用ドレイン配線 6 を経由して GND に放電される。

40

#### 【0021】

上述した液晶パネル 1 内の残留電荷の一連の動作を図 2 に示す。図 2 は、シャットダウン時の残像現象対策回路のタイミングチャートである。図中破線より左側が通常動作期間を表し、右側がシャットダウン後のパネル内電荷放電期間の状態を示している。図中の破線のタイミングが、シャットダウンが発生したあとシステム側から液晶表示装置へ入力する入力電源 11 の電圧 V11 が漸減して所定の電圧（閾値電圧）Vth を下回り、電圧降下検出回路 3 から電圧低下検出信号 14 が High となる時点である。

50

## 【0022】

電圧低下検出信号14がHighとなることにより、ゲートドライバ5の出力電圧V8(ゲート選択信号)はALL\_ONとなり、ソースドライバ4の出力電圧V9(画素書き込み電圧)は出力を停止する。また、放電用ゲート配線7の電圧V7(放電制御信号)がHighとなることにより、放電用TFT10のON/OFF状態S10は、ON状態となる。その結果、液晶パネル1内の全画素電極が放電用ドレイン配線6と接続されるため、放電用ドレイン配線6の電圧V6は、一旦電圧が上昇し、その後、放電抵抗やダイオード22(第1のダイオード)、電荷回収経路16(第1の電荷回収経路)さらに電源生成部2を経由してパネル内の電荷がGNDに放電されたため、GNDレベルに向かって漸減する波形となる。

10

## 【0023】

また、本実施の形態1では、上述したようにシャットダウンの過渡状態でパネル内電荷を全て放電させるため、放電用ドレイン配線6から得られる放電電荷を、ダイオード22を介して電源生成部へ回収する電荷回収機能を有する。上述したように、パネル内電荷放電期間の初期状態において、放電用ドレイン配線6の電圧V6は、一旦電圧が上昇する。図8に示したように、この上昇電圧を逆流防止用のダイオード22を介して電源生成部2のゲートON電圧12生成用のDC/DCコンバータ回路(VGH電圧生成回路)の出力段に印加する。こうすることで、ゲートON電圧12の電圧を一定期間維持することができ、液晶パネル1内の電荷放電作業を早期に完結させることができる。

20

## 【0024】

さらに、本実施の形態1では、ソース線放電回路23内の放電用TFT10として、活性層に酸化物半導体TFTを採用している。酸化物半導体TFTは、駆動能力が高く、ON抵抗が低いため、シャットダウン時の放電用ドレイン配線6の電圧V6の瞬時上昇電圧が高くなり、ゲートON電圧12の電圧降下を遅らせることができる。また、放電用TFT10のサイズを小型化することもでき、液晶パネル1の非表示領域の狭小化にも有利である。なお、上記酸化物半導体TFTには、活性層に、酸化亜鉛(ZnO)系材料、またはインジウム(In)とガリウム(Ga)と亜鉛(Zn)と酸素(O)とを含むInGaZnOなどの酸化物などが用いられる。

30

## 【0025】

なお、電源生成部2の停止閾値電圧に対して電圧降下検出回路3の閾値電圧Vthを高く設定することで電源が動作中にいち早く放電作業を始めることができる。

## 【0026】

さらには、電圧降下検出回路3の閾値電圧Vthを通常動作時の入力電圧の変動などで電圧降下の誤検出が発生しない電圧に設定することは言うまでもない。

## 【0027】

実施の形態2.

図3は、本実施の形態2に係る液晶表示装置の構成を表すブロック図である。本実施の形態2における液晶表示装置の構成は、上述の実施の形態1の構成中の電源生成部2からVCOM配線17への経路中に放電用スイッチ19(第2の放電用スイッチ)を挿入し、さらに電荷回収経路20(第2の電荷回収経路)、ダイオード24(第2のダイオード)、放電抵抗などを追加した構成である。また、電源生成部2からVCOM配線17から放電用スイッチ19までの配線の電圧がVCOM駆動電圧18となる。それ以外の構成および動作は、上述の実施の形態1と同様であるので、ここでは詳細な説明は省略する。

40

## 【0028】

図3において、通常動作時は電圧降下検出回路3から出力する電圧低下検出信号14がLowであるので、VCOM配線17が放電用スイッチ19を経由してVCOM駆動電圧18側に接続され、電源生成部2からVCOM駆動電圧18が液晶パネル1に供給される。次に、シャットダウンにより入力電源11の電圧が低下して電圧降下検出回路3の閾値電圧Vthを下回ると、電圧低下検出信号14がHighとなり、放電用スイッチ19がVCOM配線17をVCOM駆動電圧18側から切り離して、ダイオード24のアノード側

50

に接続し、V C O M配線17の放電経路が確保される。このときV C O M配線17から得られる電荷を、ダイオード24を介して電源生成部2へ回収し、ゲートO N電圧12の電圧降下を遅らせることで放電作業を完結させる。このV C O M配線17から得られる電荷は、液晶パネル1全体で一つの大きな電極と考えられる対向電極の電圧が放電することにより得られる電荷である。従って、電源生成部2へ電荷回収量多く、この電荷回収によるゲートO N電圧12の電圧保持効果も高い。

#### 【0029】

これら一連の動作を図4に示す。同図は、図3中のV C O M配線のシャットダウン時ににおける信号波形のタイミングチャートを示したものであり、入力電源11の電圧V11、ゲートドライバ5の出力電圧V8(ゲート選択信号)、ソースドライバ4の出力電圧V9(画素書き込み電圧)、放電用TFT10のON/OFF状態S10、放電用ドレイン配線6の電圧V6、放電用ゲート配線7の電圧V7は、上述の実施の形態1で説明した図2と同様であるので、ここでは説明を省略する。図4に示したように、V C O M配線17の電圧V17は、破線の時点でV C O M配線17がV C O M駆動電圧18から切り離され、ダイオード24のアノード側に接続されたことにより、比較的低インピーダンスの放電路が確保され、短時間でGNDレベルに到達する。なお、ダイオード24のカソード側の電荷回収経路20は、上述のダイオード22のカソード側の電荷回収経路16と同様に、電源生成部2のゲートO N電圧12生成用のD C / D Cコンバータ回路の入力段に印加する。

10

#### 【0030】

実施の形態3.

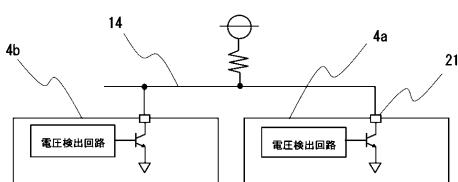

図5は本実施の形態3に係る液晶表示装置の構成を表すブロック図である。図5に図示したように、本実施の形態では図上の右側に配置されたソースドライバ4aが電圧検出回路3を有し、入力電源11(ロジック電源)の電圧降下を検出すると外部に電圧検出信号14を出力するように構成されている。その他の構成は、上述の実施の形態2と同様であるので、詳しい説明は省略する。図5において、液晶パネル1に実装された2つのソースドライバ4a、4bは、両方とも同一のソースドライバであり、2つとも圧降下検出回路3を内蔵している。しかし、本例では、ソースドライバは外部からの設定で電圧降下検出回路3の動作がON/OFFできるように構成されており、本実施の形態では右側のソースドライバ4aだけ電圧降下検出回路3を動作させて電圧低下検出信号14を制御している。液晶パネル1内の配線の都合で、左側のソースドライバ4b内の電圧降下検出回路3を動作させて電圧低下検出信号14を制御してもよい。

20

30

#### 【0031】

ソースドライバ4aに電圧降下検出回路3を内蔵したことにより、液晶表示装置100内の制御回路基板(非図示)内に電圧降下検出回路3を設ける必要が無くなり、安価な構成で残像現象の改善ができる。

40

#### 【0032】

<変形例>

図6は、本変形例におけるソースドライバの検出信号出力ポート構成例である。図6に示したように、ソースドライバ4a、4bの電圧降下検出信号14の電圧検出信号出力ポート21をオープンドレイン出力として、外部でプルアップにするなどして2つのソースドライバの電圧降下検出信号14間を接続する。その結果、ソースドライバ4a、4bが両方とも電圧降下を検出した場合に電圧降下検出信号14がHighとなり、入力電源電圧11へのノイズ重畠による影響を低下することができる。

40

#### 【0033】

実施の形態4.

図7は本実施の形態3に係る液晶表示装置の構成を表すブロック図である。図7に図示したように、本実施の形態では液晶パネル1上に実装されたゲートドライバ5が電圧検出回路3を有し、入力電源11(ロジック電源)の電圧降下を検出すると外部に電圧検出信号14を出力するように構成されている。その他の構成は、上述の実施の形態2と同様であ

50

るので、詳しい説明は省略する。

【0034】

ゲートドライバ5に電圧降下検出回路3を内蔵したことにより、液晶表示装置100内の制御回路基板(非図示)内に電圧降下検出回路3を設ける必要が無くなり、安価な構成で残像現象の改善ができる。

【0035】

<変形例>

上述の実施の形態4の構成の変形例として、放電用スイッチ15をゲートドライバ5に内蔵した事例を説明する。図7で示されているように、ゲートドライバ5には、ゲートON電圧12とゲートOFF電圧13が入力しており、ゲートドライバ5に放電用スイッチ15を内蔵することは容易である。出力として放電用ゲート配線7が増えるだけである。その配線の配置も表示用ゲート配線8と隣接して容易に配置できる。10

【0036】

ゲートドライバ5に放電用スイッチ15を内蔵したことにより、液晶表示装置100内の制御回路基板(非図示)内に放電用スイッチ15を設ける必要が無くなり、さらに安価な構成で残像現象の改善ができる。

【0037】

実施の形態5.

上述の実施の形態1では、ソース線放電回路23が酸化物半導体TFTにて構成されていたが、ゲートドライバ5を構成するトランジスタ素子として、酸化物半導体TFTを採用する。そして、液晶表示パネル1にソース線放電回路23を形成する工程と同一行程で液晶パネル1上に形成する。20

【0038】

<その他の変形例>

上述の実施の形態1~5では、入力電源11の電圧降下を検出した場合、電圧低下検出信号14のHigh信号がソースドライバ4に入力し、そのHigh信号を入力したソースドライバ4はその全出力をHi-Zとなるよう制御し、さらに、全ての表示用ソース配線9がソースドライバ4の出力部から切り離されるよう構成した。そこで、ソースドライバ4内にその切り離された表示用ソース配線9の隣接端子同士を接続するスイッチを設けておき、前記High信号がソースドライバ4に入力した場合に、隣接する異極性の駆動信号(画素書き込み電圧)が印加されていた端子同士を前記スイッチでショートし、表示用ソース配線9の電位を急速に中心電位に到達させるチャージシェア回路を追加することも有効である。30

【0039】

上述の実施の形態1~5では、画素電極への書き込み電圧を与える際のスイッチTFT(画素TFT)については、特に説明していなかったが、アモルファスシリコンTFT(a-SiTFT)や低温ポリシリコンTFT(LTPS-TFT)だけでなく、酸化物半導体TFTであっても良いのは無論である。

【0040】

また、上述の実施の形態5では、ゲートドライバ5を構成するトランジスタ素子として、酸化物半導体TFTを採用したが、アモルファスシリコンTFT(a-SiTFT)や低温ポリシリコンTFT(LTPS-TFT)であっても良い。さらに、上述の実施の形態4の変形例で、放電用スイッチ15をゲートドライバ5に内蔵した事例を示したが、ゲートドライバ5を酸化物半導体TFT、アモルファスシリコンTFT(a-SiTFT)または低温ポリシリコンTFT(LTPS-TFT)で構成すると、放電用スイッチ15もゲートドライバ5と同一のTFTで構成でき、ゲートドライバ5への内蔵化も容易である。40

【0041】

さらには、ソース線放電回路23の放電制御信号生成回路である放電用スイッチ15は、ゲートON電圧12とゲートOFF電圧13を切り替えるスイッチ回路として例示した

10

20

30

40

50

が、スイッチ回路に代えて電圧低下検出信号 14 を入力とするレベルシフタ回路と出力バッファ回路で構成してもよい。すなわち、レベルシフタ回路で電圧低下検出信号 14 をゲート ON 電圧 12 とゲート OFF 電圧 13 間の信号レベルに増幅し、ゲートドライバ 5 の出力段と同一の出力バッファ回路で放電用ゲート配線 7 を駆動する構成とすることも容易であり、ゲートドライバ 5 内の他のゲート配線制御回路との共通部分が多い。当該レベルシフタ回路と出力バッファ回路は、ゲート配線制御回路内のシフトレジスタ回路からの出力回路と同様の回路でよく、少しの TFT 素子の追加で容易に実現できる。

#### 【符号の説明】

##### 【0042】

- |                              |    |

|------------------------------|----|

| 1 液晶表示パネル                    | 10 |

| 2 電源生成部                      |    |

| 3 電圧降下検出回路                   |    |

| 4、4 a、4 b ソースドライバ（ソース配線駆動回路） |    |

| 5 ゲートドライバ（ゲート配線制御回路）         |    |

| 6 放電用ドレイン配線                  |    |

| 7 放電用ゲート配線                   |    |

| 8 表示用ゲート配線                   |    |

| 9 表示用ソース配線                   |    |

| 10 放電用 TFT                   |    |

| 11 入力電源電圧                    | 20 |

| 12 ゲート ON 電圧                 |    |

| 13 ゲート OFF 電圧                |    |

| 14 電圧低下検出信号                  |    |

| 15 放電用スイッチ（放電制御信号生回路）        |    |

| 23 ソース線放電回路                  |    |

#### 【図 1】

#### 【図 2】

【図3】

【 図 4 】

〔 5 〕

〔 図 7 〕

〔 6 〕

【図8】

---

フロントページの続き

| (51) Int.CI. | F I     | テーマコード(参考)   |

|--------------|---------|--------------|

|              | G 0 9 G | 3/20 6 4 1 C |

|              | G 0 9 G | 3/20 6 2 2 D |

|              | G 0 9 G | 3/20 6 2 4 C |

|              | G 0 9 G | 3/20 6 8 0 G |

|              | G 0 9 G | 3/20 6 2 1 M |

|              | G 0 2 F | 1/133 5 5 0  |

F ターム(参考) 5C006 AA16 AC22 AC26 AF43 AF51 AF53 AF64 AF67 AF71 BB16

BC02 BC03 BC11 BC20 BC23 BF03 BF14 BF24 BF25 BF26

BF34 BF36 BF42 BF46 EB05 FA11 FA31 FA34 FA36 FA37

FA38 FA51

5C080 AA10 BB05 DD08 DD09 DD12 DD14 DD19 DD25 DD29 EE29

FF03 FF11 JJ02 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2018180414A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2018-11-15 |

| 申请号            | JP2017082927                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2017-04-19 |

| [标]申请(专利权)人(译) | 三菱电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 三菱电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 鷹木二朗                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 鷹木 二朗                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/36 G09G3/20.670.D G09G3/20.623.R G09G3/20.621.G G09G3/20.670.K G09G3/20.641.C<br>G09G3/20.622.D G09G3/20.624.C G09G3/20.680.G G09G3/20.621.M G02F1/133.550                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZE38 2H193/ZH22 2H193/ZH52 5C006/AA16 5C006/AC22 5C006/AC26 5C006<br>/AF43 5C006/AF51 5C006/AF53 5C006/AF64 5C006/AF67 5C006/AF71 5C006/BB16 5C006/BC02<br>5C006/BC03 5C006/BC11 5C006/BC20 5C006/BC23 5C006/BF03 5C006/BF14 5C006/BF24 5C006<br>/BF25 5C006/BF26 5C006/BF34 5C006/BF36 5C006/BF42 5C006/BF46 5C006/EB05 5C006/FA11<br>5C006/FA31 5C006/FA34 5C006/FA36 5C006/FA37 5C006/FA38 5C006/FA51 5C080/AA10 5C080<br>/BB05 5C080/DD08 5C080/DD09 5C080/DD12 5C080/DD14 5C080/DD19 5C080/DD25 5C080/DD29<br>5C080/EE29 5C080/FF03 5C080/FF11 5C080/JJ02 5C080/JJ04 |         |            |

| 代理人(译)         | 村上佳菜子<br>松井茂明<br>伊达 研郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

要解决的问题：提供一种方法，用于在液晶显示装置中的关闭时的放电期间确保用于将所有栅极布线维持在高状态一定时间的电压。一内部栅极驱动器5，用于驱动源极线9，其包括发电单元2的源极驱动器4中，输入电源电压11被输入到发电单元下降到预定电压的电压降信号14的下方并且包括多个放电晶体管10，并且放电源极布线的电位在源极线放电电路23的电力，与所有的源极线通过对放电晶体管为导通状态的放电漏极线6响应于所述电压降信号，在液晶显示面板1中的残留电荷，通过放电排扰线对电荷放电以释放残余电荷并且电荷被恢复到源生成部分的栅极布线导通电压12的电压生成电路。发明背景