(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-40911

(P2015-40911A)

(43) 公開日 平成27年3月2日(2015.3.2)

| (51) Int.Cl.                | F 1        | テーマコード (参考)       |

|-----------------------------|------------|-------------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36  | 2 H 1 9 3         |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 6 2 4 C 5 C 0 0 6 |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20  | 6 2 4 E 5 C 0 8 0 |

|                             | G09G 3/20  | 6 2 4 D           |

|                             | GO2F 1/133 | 5 5 0             |

審査請求 未請求 請求項の数 5 O L (全 13 頁)

|           |                              |          |                                                                                                                                    |

|-----------|------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2013-170643 (P2013-170643) | (71) 出願人 | 000201113<br>船井電機株式会社<br>大阪府大東市中垣内7丁目7番1号                                                                                          |

| (22) 出願日  | 平成25年8月20日 (2013.8.20)       | (74) 代理人 | 100148460<br>弁理士 小俣 純一                                                                                                             |

|           |                              | (72) 発明者 | 森 丈弘<br>大阪府大東市中垣内7丁目7番1号 船井<br>電機株式会社内                                                                                             |

|           |                              |          | F ターム (参考) 2H193 ZA04 ZE40 ZF21 ZF31 ZF59<br>ZQ16<br>5C006 AC25 AC26 BB16 BC22 FA47<br>5C080 AA10 BB05 DD26 FF11 JJ02<br>JJ03 JJ04 |

|           |                              |          |                                                                                                                                    |

## (54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】消費電力および発熱量を低減することが可能になる液晶表示装置を提供する。

【解決手段】共通電極 C\_E と、画素値に応じた電圧が印加される画素電極 P\_E と、共通電極 C\_E と画素電極 P\_E との間に形成された液晶層 L\_L を備える複数の画素 C\_1\_1 ~ C\_m\_n と、複数の画素 C\_1\_1 ~ C\_m\_n のうちの第一画素の共通電極 C\_E に接続される第一共通配線 COM\_L\_1 と、複数の画素 C\_1\_1 ~ C\_m\_n のうちの第二画素の共通電極 C\_E に接続される第二共通配線 COM\_L\_2 と、第一共通配線 COM\_L\_1 に対し第一共通電圧 V\_COM を印加し、第二共通配線 COM\_L\_2 に対し第一共通電圧 V\_COM とは異なる第二共通電圧 V\_COM' を印加するコモンドライバ 2\_3 を備える。

【選択図】図 2

## 【特許請求の範囲】

## 【請求項 1】

共通電極と、画素値に応じた電圧が印加される画素電極と、前記共通電極と前記画素電極との間に形成された液晶層とを備える複数の画素と、

前記複数の画素のうちの第一画素の共通電極に接続される第一共通配線と、

前記複数の画素のうちの第二画素の共通電極に接続される第二共通配線と、

前記第一共通配線に対し第一共通電圧を印加し、前記第二共通配線に対し前記第一共通電圧とは異なる第二共通電圧を印加するコマンドライバとを備える

液晶表示装置。

## 【請求項 2】

10

前記複数の画素は、マトリクス状に配置され、

前記第一画素は、前記複数の画素のうち、奇数列の奇数行に配置された画素と偶数列の偶数行に配置された画素であり、

前記第二画素は、前記複数の画素のうち、偶数列の奇数行に配置された画素と奇数列の偶数行に配置された画素である

請求項 1 に記載の液晶表示装置。

## 【請求項 3】

20

前記複数の画素は、複数の画素グループに分類され、

前記複数の画素グループは、マトリクス状に配置され、

前記第一画素は、前記複数の画素のうち、奇数列の奇数行に配置された画素グループと偶数列の偶数行に配置された画素グループとに含まれる画素であり、

前記第二画素は、前記複数の画素のうち、偶数列の奇数行に配置された画素グループと奇数列の偶数行に配置された画素グループとに含まれる画素である

請求項 1 に記載の液晶表示装置。

## 【請求項 4】

30

前記コマンドライバは、

前記第一共通配線に対し、前記第一共通電圧として、高電圧側の共通電圧と低電圧側の共通電圧とを交互に繰り返し印加し、

前記第二共通配線に対し、前記第二共通電圧として、前記第一共通配線に前記高電圧側の共通電圧を印加している期間に前記低電圧側の共通電圧を印加し、前記第一共通配線に前記低電圧側の共通電圧を印加している期間に前記高電圧側の共通電圧を印加する

請求項 1 ~ 3 のいずれか 1 項に記載の液晶表示装置。

## 【請求項 5】

40

前記画素電極に対し、前記画素値に応じた電圧を印加するソースドライバを備え、

前記ソースドライバは、

前記共通電極に前記高電圧側の共通電圧が印加されている画素の前記画素電極に対し、印加される電圧の極性が負極性となるように、前記高電圧側の共通電圧よりも低い電圧を印加し、

前記共通電極に前記低電圧側の共通電圧が印加されている画素の前記画素電極に対し、印加される電圧の極性が正極性となるように、前記低電圧側の共通電圧よりも高い電圧を印加する

請求項 4 に記載の液晶表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本発明は、液晶表示装置に関する。

## 【背景技術】

## 【0 0 0 2】

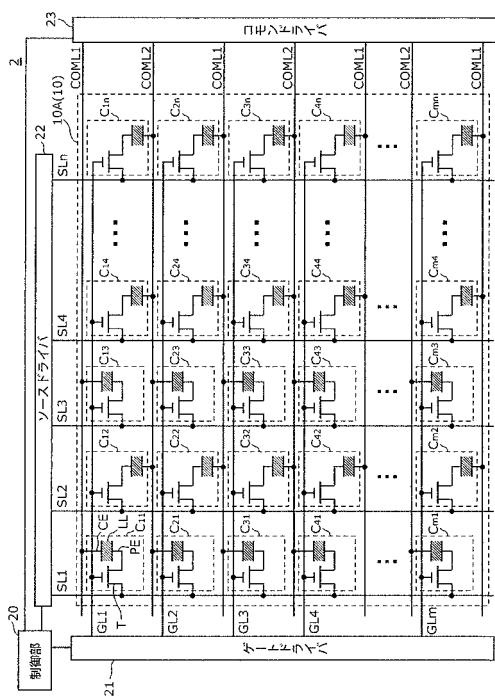

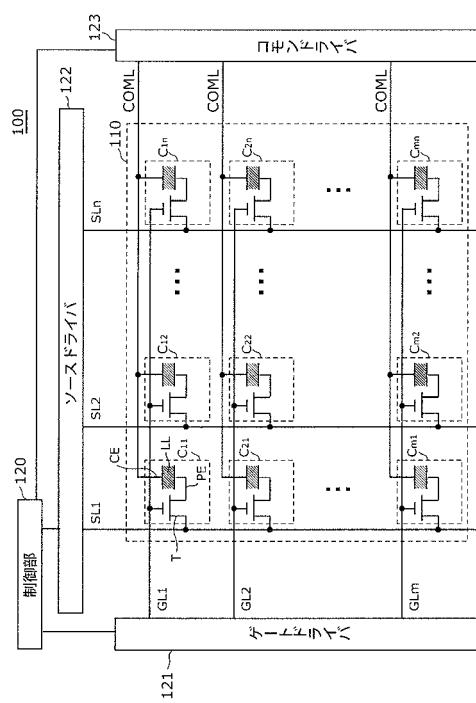

液晶表示装置は、一般的に、画像の表示を行う液晶パネルとその駆動回路とを備える表示部を備えている（例えば、特許文献 1 参照）。図 8 は、IPS（In Plane S

50

w i t c h i n g ) 方式の液晶パネルを用いた表示部の一例を示す図である。

【0003】

表示部100は、例えば、図8に示すように、液晶パネル110と、制御部120と、ゲートドライバ121と、ソースドライバ122と、コマンドライバ123とを備えている。

【0004】

液晶パネル110は、 $m \times n$  個のマトリクス状に配置された画素  $C_{1,1} \sim C_{m,n}$  と、ソース線  $S L_1 \sim S L_n$  と、ゲート線  $G L_1 \sim G L_m$  と、共通配線  $C O M_L$  を備えて構成されている。画素  $C_{i,j}$  ( $i = 1 \sim m$ 、 $j = 1 \sim n$ ) は、共通電極  $C E$  と、画素電極  $P E$  と、共通電極  $C E$  と画素電極  $P E$ との間に形成された液晶層  $L L$  と、スイッチング素子  $T$  とを備えている。共通電極  $C E$  は、共通配線  $C O M_L$  に接続されている。スイッチング素子  $T$  は、例えば、TFT (Thin Film Transistor) であり、ゲート端子がゲート線  $G L_i$  に、ドレイン端子が画素電極  $P E$  に、ソース端子がソース線  $S L_j$  にそれぞれ接続されている。

10

【0005】

制御部120は、後述するゲートドライバ121およびソースドライバ122の動作を制御する回路である。制御部120は、例えば、ゲートドライバ121に対し、選択された画素  $C_{i,j}$  の行アドレスを示す信号を出力し、ソースドライバ122に対し、選択された画素  $C_{i,j}$  の列アドレスおよび画素値を示す信号を出力する。

20

【0006】

ゲートドライバ121は、選択された画素  $C_{i,j}$  に接続されているゲート線  $G L_i$  に対し、スイッチング素子  $T$  をON状態にするための電圧を印加する。

【0007】

ソースドライバ122は、選択された画素  $C_{i,j}$  に接続されているソース線  $S L_j$  に対し、選択された画素  $C_{i,j}$  の画素値に応じた電圧である信号線電圧を印加する。

30

【0008】

コマンドライバ123は、共通配線  $C O M_L$  に、共通電圧  $V C O M$  を印加する。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2007-304560号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、上述した液晶表示装置では、消費電力および発熱量のさらなる低減が求められている。

【0011】

本発明は上述の課題を解決するためになされたものであり、消費電力および発熱量を低減することが可能になる液晶表示装置を提供することを目的とする。

40

【課題を解決するための手段】

【0012】

上記目的を達成するために、本発明の一態様に係る液晶表示装置は、共通電極と、画素値に応じた電圧が印加される画素電極と、前記共通電極と前記画素電極との間に形成された液晶層とを備える複数の画素と、前記複数の画素のうちの第一画素の共通電極に接続される第一共通配線と、前記複数の画素のうちの第二画素の共通電極に接続される第二共通配線と、前記第一共通配線に対し第一共通電圧を印加し、前記第二共通配線に対し前記第一共通電圧とは異なる第二共通電圧を印加するコマンドライバとを備える。

【0013】

上記構成の液晶表示装置では、2種類の共通電圧（第一共通電圧および第二共通電圧）を用い、画素を第一画素および第二画素の2つに分けて、第一画素に第一共通電圧を、第

50

二画素に第二共通電圧を印加している。

【0014】

IPS方式の液晶パネルに対しドット反転駆動方式で画素に電圧を印加する場合、従来のように、1種類の共通電圧VCOMを用いるときは、ソースドライバは、共通電圧VCOMを基準として、 $\pm V_{max}$ の範囲の信号線電圧を出力する必要があった。

【0015】

これに対し、上記構成の液晶表示装置では、第一共通電圧および第二共通電圧の2種類の共通電圧を用いるため、ソースドライバが outputする電圧の範囲を狭くすることが可能になる。例えば、所定のフレームにおいて、第一画素に正極性の電圧を印加し、第二画素に負極性の電圧を印加するように構成する。この場合、第一画素に印加する第一共通電圧の電圧値を低い電圧値に設定すれば、ソースドライバが outputする電圧の最大値を低く抑えることが可能になる。また、第二画素に印加する第二共通電圧の電圧値を高い電圧値に設定すれば、ソースドライバが outputする電圧の最小値を、従来よりも高い値に設定することが可能になる。

10

【0016】

つまり、上記構成の液晶表示装置では、ソースドライバが outputする電圧の範囲を、狭くすることが可能になる。これにより、信号配線を駆動するソースドライバに必要とされる駆動能力を小さくすることが可能になる。さらに、ソースドライバが outputする電圧の範囲を狭くすることが可能になるので、画素間のリーク電圧を低減することが可能になる。これにより、消費電力を低減し、発熱量を低減させることが可能になる。

20

【0017】

例えば、前記複数の画素は、マトリクス状に配置され、前記第一画素は、前記複数の画素のうち、奇数列の奇数行に配置された画素と偶数列の偶数行に配置された画素であり、前記第二画素は、前記複数の画素のうち、偶数列の奇数行に配置された画素と奇数列の偶数行に配置された画素であっても良い。あるいは、前記複数の画素は、複数の画素グループに分類され、前記複数の画素グループは、マトリクス状に配置され、前記第一画素は、前記複数の画素のうち、奇数列の奇数行に配置された画素グループと偶数列の偶数行に配置された画素グループとに含まれる画素であり、前記第二画素は、前記複数の画素のうち、偶数列の奇数行に配置された画素グループと奇数列の偶数行に配置された画素グループとに含まれる画素であっても良い。

30

【0018】

上記構成の液晶表示装置では、共通電極に第一共通電圧が印加される第一画素と、共通電極に第二共通電圧が印加される第二画素とを交互に配置するので、液晶パネル全体で、電位の偏りを低減することが可能になる。また、千鳥状に第一画素と第二画素とを配置した場合、隣接画素間でのリーク電流を低減することが可能になる。

【0019】

また、前記コモンドライバは、前記第一共通配線に対し、前記第一共通電圧として、高電圧側の共通電圧と低電圧側の共通電圧とを交互に繰り返し印加し、前記第二共通配線に対し、前記第二共通電圧として、前記第一共通配線に前記高電圧側の共通電圧を印加している期間に前記低電圧側の共通電圧を印加し、前記第一共通配線に前記低電圧側の共通電圧を印加している間に前記高電圧側の共通電圧を印加しても良い。

40

【0020】

上記構成の液晶表示装置では、高電圧側の共通電圧と低電圧側の共通電圧とを、交互に印加するので、各画素に印加する電圧の極性をフレーム毎変化させる場合でも、ソースドライバが outputする電圧の範囲を狭くすることが可能になり、リークおよび焼き付きを低減可能になる。これにより、駆動能力の小さいソースドライバを利用することが可能になる。

【0021】

また、前記画素電極に対し、前記画素値に応じた電圧を印加するソースドライバを備え、前記ソースドライバは、前記共通電極に前記高電圧側の共通電圧が印加されている画素

50

の前記画素電極に対し、印加される電圧の極性が負極性となるように、前記高電圧側の共通電圧よりも低い電圧を印加し、前記共通電極に前記低電圧側の共通電圧が印加されている画素の前記画素電極に対し、印加される電圧の極性が正極性となるように、前記低電圧側の共通電圧よりも高い電圧を印加しても良い。

#### 【0022】

上記構成の液晶表示装置では、高電圧側の共通電圧が印加されている画素が負極性となるように、画素電極の電圧値を設定し、低電圧側の共通電圧が印加されている画素が正極性となるように、画素電極の電圧値を設定するので、ソースドライバの出力電圧の範囲を狭くすることが可能になる。これにより、駆動能力の小さいソースドライバを利用することが可能になる。

10

#### 【0023】

なお、本発明は、このような特徴的な処理部を備える液晶表示装置として実現することができるだけでなく、液晶表示装置に含まれる特徴的な処理部が実行する処理をステップとする液晶表示方法として実現することができる。また、液晶表示装置に含まれる特徴的な処理部としてコンピュータを機能させるためのプログラムまたは液晶表示方法に含まれる特徴的なステップをコンピュータに実行させるプログラムとして実現することもできる。そして、そのようなプログラムを、CD-ROM (Compact Disc - Read Only Memory) 等のコンピュータ読取可能な非一時的な記録媒体あるいはインターネット等の通信ネットワークを介して流通させることができるのは、言うまでもない。

20

#### 【発明の効果】

#### 【0024】

本発明によると、消費電力および発熱量を低減することが可能になる液晶表示装置を提供することが可能になる。

#### 【図面の簡単な説明】

#### 【0025】

【図1】液晶表示装置の一例を示す図である。

【図2】実施の形態1の表示部の構成の一例を示す図である。

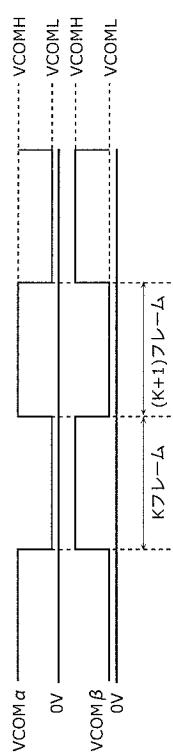

【図3】第一共通電圧および第二共通電圧の一例を示す波形図である。

【図4】選択された画素の画素値と、選択された画素に印加する電圧の極性と、ソース線に印加する電圧値との関係を示す表である。

30

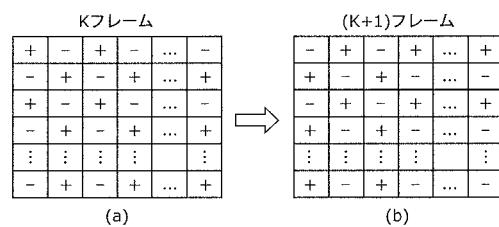

【図5】(a)は、図3に示す第Kフレームにおいて、各画素に印加される電圧の極性を示す図であり、(b)は、図3に示す第(K+1)フレームにおいて、各画素に印加される電圧の極性を示す図である。

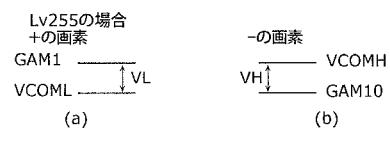

【図6】図3に示す第Kフレームの第一画素および第二画素に印加される電圧を示す模式図である。

【図7】実施の形態2の表示部の構成の一例を示す図である。

【図8】従来の表示部の構成の一例を示す図である。

#### 【発明を実施するための形態】

#### 【0026】

以下、本発明の実施の形態について、図面を用いて詳細に説明する。なお、各図は、必ずしも各寸法あるいは各寸法比等を厳密に図示したものではない。

40

#### 【0027】

また、以下で説明する実施の形態は、いずれも本発明の好ましい一具体例を示すものである。以下の実施の形態で示される数値、形状、材料、構成要素、構成要素の配置位置及び接続形態、ステップ、ステップの順序などは、一例であり、本発明を限定する主旨ではない。本発明は、特許請求の範囲によって特定される。よって、以下の実施の形態における構成要素のうち、独立請求項に記載されていない構成要素については、本発明の課題を達成するのに必ずしも必要ではないが、より好ましい形態を構成するものとして説明される。

50

## 【0028】

(実施の形態1)

実施の形態1の液晶表示装置について、図1～図6を基に説明する。

## 【0029】

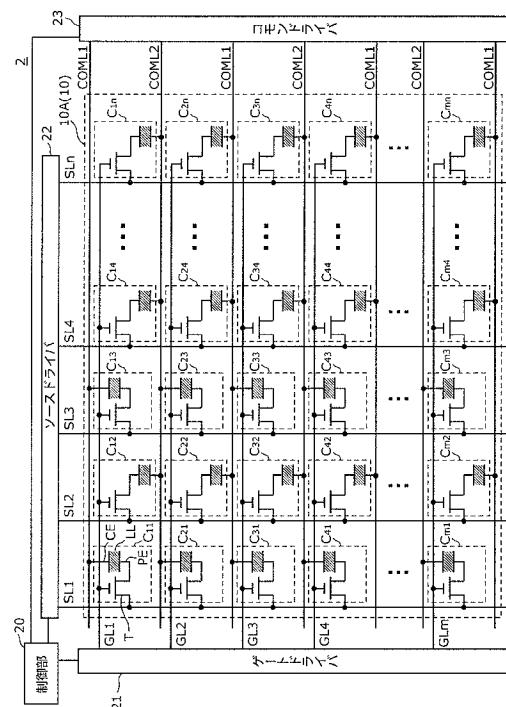

図1は、液晶表示装置の一例を示す図である。液晶表示装置1は、図1に示すように、画像の表示を行う液晶パネル10とその駆動回路とを備える表示部を備えている。

## 【0030】

なお、後で詳述するが、本実施の形態の表示部は、液晶パネル10を構成する画素を第一画素および第二画素の2つに分類し、第一画素に対して第一共通電圧VCOMを、第二画素に対して第二共通電圧VCOMを印加するように構成されている。つまり、本実施の形態の表示部は、2種類の共通電圧を用いている。10

## 【0031】

<1-1. 表示部の構成>

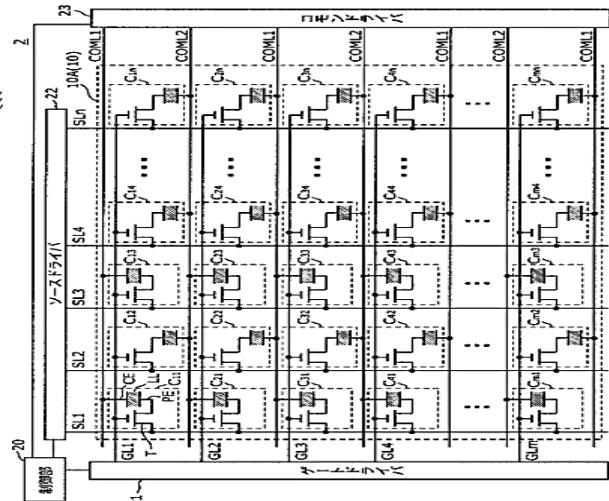

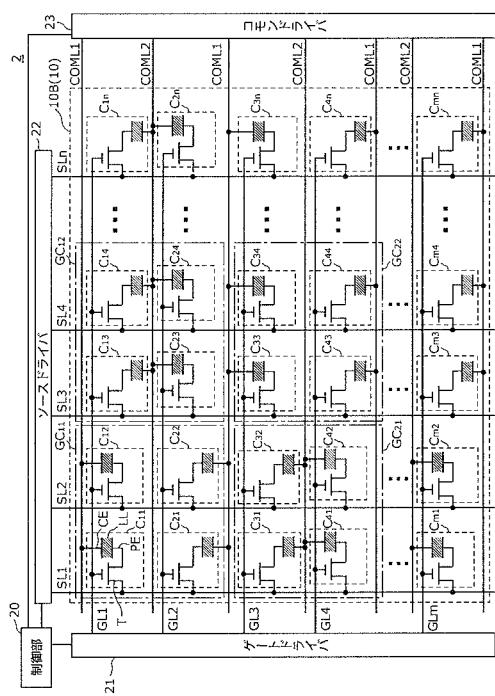

表示部の構成について、図2を基に説明する。図2は、表示部の一例を示す図である。

## 【0032】

表示部2は、本実施の形態では、図2に示すように、液晶パネル10A(10)と、制御部20と、ゲートドライバ21と、ソースドライバ22と、コマンドライバ23とを備えている。なお、図示しないが、表示部2は、さらに、LED(Light Emitter Diode)等を用いたバックライト、および、電源回路等を備えている。20

## 【0033】

液晶パネル10Aは、 $m \times n$ 個のマトリクス状に配置された画素 $C_{1,1} \sim C_{m,n}$ と、ソース線S<sub>L1</sub>～S<sub>Ln</sub>と、ゲート線G<sub>L1</sub>～G<sub>Lm</sub>と、第一共通配線COML1と、第二共通配線COML2とを備えて構成されている。

## 【0034】

画素 $C_{i,j}$ ( $i = 1 \sim m$ 、 $j = 1 \sim n$ )は、共通電極CEと、画素電極PEと、共通電極CEと画素電極PEとの間に形成された液晶層LLと、スイッチング素子Tとを備えている。スイッチング素子Tは、例えば、TFT(Thin Film Transistor)であり、ゲート端子がゲート線G<sub>Li</sub>に、ドレイン端子が画素電極PEに、ソース端子がソース線S<sub>Lj</sub>にそれぞれ接続されている。30

## 【0035】

本実施の形態では、画素 $C_{i,j}$ ( $i = 1 \sim m$ 、 $j = 1 \sim n$ )は、第一画素および第二画素の2つに分類されている。具体的には、第一画素は、画素 $C_{1,1} \sim C_{m,n}$ のうち、奇数列の奇数行に配置された画素 $C_{i,j}$ ( $C_{1,1}, C_{1,3}, \dots$ )と偶数列の偶数行に配置された画素 $C_{i,j}$ ( $C_{2,2}, C_{2,4}, \dots$ )である。また、第二画素は、残りの偶数列の奇数行に配置された画素 $C_{i,j}$ ( $C_{2,1}, C_{2,3}, \dots$ )と奇数列の偶数行に配置された画素 $C_{i,j}$ ( $C_{1,2}, C_{1,4}, \dots$ )である。第一画素の共通電極CEは、第一共通配線COML1に接続されている。また、第二画素の共通電極CEは、第二共通配線COML2に接続されている。このように配線することで、隣接する2つの画素が異なる共通配線に接続される構成となっている。

## 【0036】

制御部20は、後述するゲートドライバ21およびソースドライバ22の動作を制御する回路である。制御部20は、例えば、ゲートドライバ21に対し、選択された画素 $C_{i,j}$ の行アドレスを示す信号を出力し、ソースドライバ22に対し、選択された画素 $C_{i,j}$ の列アドレスおよび画素値を示す信号を出力する。40

## 【0037】

ゲートドライバ21は、選択された画素 $C_{i,j}$ に接続されているゲート線G<sub>Li</sub>に対し、スイッチング素子TをON状態にするための電圧を印加する。

## 【0038】

ソースドライバ22は、選択された画素 $C_{i,j}$ に接続されているソース線S<sub>Lj</sub>に対し、選択された画素 $C_{i,j}$ の画素値に応じた電圧を印加する。50

## 【0039】

コモンドライバ23は、第一共通配線COML1に第一共通電圧VCOMを、第二共通配線COML2に第二共通電圧VCOMをそれぞれ印加する。第一共通電圧VCOMおよび第二共通電圧VCOMについては、後述する。

## 【0040】

<1-2. 電圧印加方法>

コモンドライバ23およびソースドライバ22における電圧の印加方法について、図3～図6を基に説明する。

## 【0041】

なお、本実施の形態では、フレームごとに、各画素に印加される電圧の極性を反転させるドット反転駆動方式を用いる場合について説明する。

10

## 【0042】

コモンドライバ23は、上述したように、第一画素の共通電極CEに接続される第一共通配線COML1に第一共通電圧VCOMを印加する。コモンドライバ23は、さらに、第二画素の共通電極CEに接続される第二共通配線COML2に第二共通電圧VCOMをそれぞれ印加する。

## 【0043】

ここで、図3は、第一共通電圧VCOMと第二共通電圧VCOMの一例を示す波形図である。

20

## 【0044】

コモンドライバ23は、図3に示すように、第一共通配線COML1に対し、第一共通電圧VCOMとして、高電圧側の共通電圧VCOMHと低電圧側の共通電圧VCOMLとを交互に繰り返し印加する。コモンドライバ23は、さらに、第二共通配線COML2に対し、第二共通電圧VCOMとして、第一共通配線COML1に高電圧側の共通電圧VCOMHを印加している期間に低電圧側の共通電圧VCOMLを印加し、第一共通配線COML1に低電圧側の共通電圧VCOMLを印加している期間に高電圧側の共通電圧VCOMHを印加する。

## 【0045】

図3では、コモンドライバ23は、第Kフレームの期間に、第一共通配線COML1に対し低電圧側の共通電圧VCOMLを、第二共通配線COML2に対し高電圧側の共通電圧VCOMHをそれぞれ印加している。

30

## 【0046】

また、図3では、コモンドライバ23は、第(K+1)フレームの期間に、第一共通配線COML1に対し高電圧側の共通電圧VCOMHを、第二共通配線COML2に対し低電圧側の共通電圧VCOMLをそれぞれ印加している。

## 【0047】

なお、高電圧側の共通電圧VCOMHは、例えば、5.5Vである。低電圧側の共通電圧VCOMLは、例えば、0.5Vである。

## 【0048】

ソースドライバ22は、上述したように、選択された画素C<sub>i,j</sub>に接続されているソース線SLjに対し、選択された画素C<sub>i,j</sub>の画素値に応じた電圧を印加する。

40

## 【0049】

図4は、選択された画素C<sub>i,j</sub>の画素値(Lv0～Lv255)と、選択された画素C<sub>i,j</sub>に印加する電圧の極性と、ソース線に印加する電圧値GAM1～GAM10との関係を示す表である。図4では、8ビット表示の場合の一例を示している。図4において、「+」は、正極性の電圧を印加する画素を、「-」は、負極性の電圧を印加する画素を示している。

## 【0050】

具体的には、図4において、「+」の画素については、画素値Lv255～Lv0に応じてGAM1～GAM5が割り当てられている。「-」の画素については、画素値Lv2

50

55 ~ Lv0 に応じて GAM10 ~ GAM6 が割り当てられている。また、画素値 Lv255 に対応する GAM1 および GAM10 の電圧値は、5V となっている。画素値 Lv0 に対応する GAM5 および GAM6 の電圧値は、1V となっている。

#### 【0051】

図5の(a)は、図3に示す第Kフレームにおいて、各画素  $C_{i,j}$  に印加される電圧の極性を示す図である。図5の(b)は、図3に示す第(K+1)フレームにおいて、各画素  $C_{i,j}$  に印加される電圧の極性を示す図である。図5において、「+」は、正極性の電圧を印加する画素を、「-」は、負極性の電圧を印加する画素を示している。

#### 【0052】

なお、図4および図5において、「+」となる期間には、コマンドライバ23により低電圧側の共通電圧 VCOML が印加される。「-」となる期間には、コマンドライバ23により低電圧側の共通電圧 VCOMH が印加される。

#### 【0053】

言い換えると、共通電極 CE に高電圧側の共通電圧 VCOMH ( 例えば、5.5V ) が印加される画素の画素電極 PE には、印加される電圧の極性が負極性となるように、高電圧側の共通電圧 VCOMH よりも低い電圧 ( 例えば、1V ~ 5V ) が印加される。共通電極 CE に低電圧側の共通電圧 VCOML ( 例えば、0.5V ) が印加される画素の画素電極 PE には、印加される電圧の極性が負極性となるように、低電圧側の共通電圧 VCOML よりも高い電圧 ( 例えば、1V ~ 5V ) が印加される。

#### 【0054】

以下、具体的な数値を用いて説明する。

#### 【0055】

ここでは、図3に示す第Kフレームについて、第一画素および第二画素に印加される電圧について説明する。図6は、図3に示す第Kフレームの第一画素および第二画素に印加される電圧を示す模式図である。

#### 【0056】

第Kフレームでは、図3より、第一画素の共通電極 CE には、VCOML が印加され、第二画素の共通電極 CE には、VCOMH が印加されている。また、図5の(a)より、第一画素に印加される電圧の極性は「+」、第二画素に印加される電圧の極性は「-」となっている。

#### 【0057】

第Kフレームにおいて、第一画素の画素値が Lv255 の場合、極性が「+」であることから、図4より、GAM1 が選択される。第一画素に印加される電圧の絶対値は、図6に示すように、 $GAM1 - VCOML = 5 - 0.5 = 4.5$  となる。

#### 【0058】

第Kフレームにおいて、第二画素の画素値が Lv255 の場合、極性が「-」であることから、図4より、GAM10 が選択される。画素に印加される電圧の絶対値は、図6に示すように、 $VCOMH - GAM10 = 5.5 - 1 = 4.5$  となる。

#### 【0059】

< 1 - 3 . 効果等 >

本実施の形態の液晶表示装置1では、第一共通電圧 VCOM および第二共通電圧 VCOM の2種類の共通電圧を用い、画素を第一画素および第二画素の2つに分けて、第一画素に第一共通電圧を、第二画素に第二共通電圧を印加している。このように、複数の共通電圧を用いることで、画素電極側(信号配線)に印加する電圧値の範囲を狭くすることが可能になる。これにより、信号配線を駆動するソースドライバ22に必要とされる駆動能力が小さくなる。さらに、画素間のリーク電圧を低減し、ソースドライバ22の消費電力を低減し、液晶パネル10の発熱量を低減させることが可能になる。

#### 【0060】

より具体的には、共通電圧 VCOM が1種類の場合、極性の反転を考慮すると、従来は、例えば、共通電圧 VCOM が 0V の場合、ソースドライバ22は、-4.5V ~ +4.5

10

20

30

40

50

Vの電圧を出力する必要が生じる。つまり、ソースドライバ22から出力する電圧の幅は、9Vとなる。

#### 【0061】

これに対し、本実施の形態の液晶表示装置1では、上述したように、1V～5Vまでの電圧を出力すればよい。つまり、ソースドライバ22から出力する電圧の幅は、4Vとなる。電圧の変化の幅が少ないことから、ソースドライバ22の消費電力の低減を図ることが可能になる。また、ソースドライバ22から出力される電圧の幅が小さいことから、液晶パネル10内でのリークを押えることが可能になる。

#### 【0062】

また、本実施の形態1では、画素単位で、画素に印加される電圧の極性を反転させているので、画質を均一にすることが可能になる。

#### 【0063】

(実施の形態2)

実施の形態2の液晶表示装置について、図7を基に説明する。

#### 【0064】

本実施の形態の液晶表示装置1は、図1に示す実施の形態1の液晶表示装置1と同様に、画像の表示を行う液晶パネル10とその駆動回路とを備える表示部を備えている。

#### 【0065】

本実施の形態では、実施の形態1とは、液晶パネル10の構成が異なる場合について説明する。

#### 【0066】

なお、本実施の形態の液晶表示装置1は、実施の形態1と同様に、液晶パネル10構成する画素を第一画素および第二画素の2つに分類し、第一画素に対して第一共通電圧VCOMを、第二画素に対して第二共通電圧VCOMを印加するように構成されている。

#### 【0067】

<2-1. 表示部の構成>

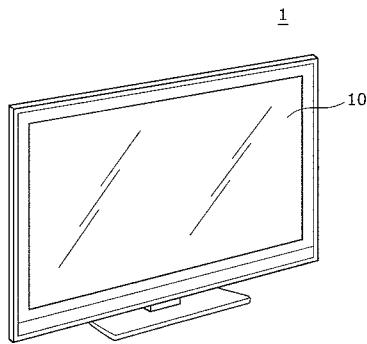

表示部の構成について、図7を基に説明する。図7は、表示部の一例を示す図である。

#### 【0068】

表示部2は、本実施の形態では、図7に示すように、液晶パネル10B(10)と、制御部20と、ゲートドライバ21と、ソースドライバ22と、コモンドライバ23とを備えている。また、図示しないが、表示部2は、さらに、LED(Light Emitter Ring Diode)等を用いたバックライト、および、電源回路等を備えている。なお、制御部20、ゲートドライバ21、ソースドライバ22およびコモンドライバ23の構成および動作は、実施の形態1と同じである。

#### 【0069】

液晶パネル10Bは、 $m \times n$ 個のマトリクス状に配置された画素 $C_{1,1} \sim C_{m,n}$ と、ソース線 $S L_1 \sim S L_n$ と、ゲート線 $G L_1 \sim G L_m$ と、第一共通配線 $C O M L_1$ と、第二共通配線 $C O M L_2$ とを備えて構成されている。

#### 【0070】

画素 $C_{i,j}$ ( $i = 1 \sim m, j = 1 \sim n$ )は、共通電極CEと、画素電極PEと、共通電極CEと画素電極PEとの間に形成された液晶層LLと、スイッチング素子Tとを備えている。スイッチング素子Tは、例えば、TFTであり、ゲート端子がゲート線 $G L_i$ に、ドレン端子が画素電極PEに、ソース端子がソース線 $S L_j$ にそれぞれ接続されている。

#### 【0071】

本実施の形態では、画素 $C_{i,j}$ ( $i = 1 \sim m, j = 1 \sim n$ )は、 $2 \times 2$ のマトリクス状に配置された4つの画素からなる複数の画素グループ $G C_{1,1} \sim G C_{(2/m)(2/n)}$ に分類されている。さらに、画素グループ $G C_{1,1} \sim G C_{(2/m)(2/n)}$ は、マトリクス状に配置されている。

#### 【0072】

10

20

30

40

50

また、本実施の形態では、画素  $C_{1,1} \sim C_{m,n}$  のうち、奇数列の奇数行に配置された画素グループ G C ( $C_{1,1}, C_{1,3}, \dots$ ) と偶数列の偶数行に配置された画素グループ G C ( $G C_{2,2}, G C_{2,4}, \dots$ ) とに含まれる画素を第一画素とする。

#### 【0073】

また、画素  $C_{1,1} \sim C_{m,n}$  のうち、偶数列の奇数行に配置された画素グループ G C ( $G C_{2,1}, G C_{2,3}, \dots$ ) と奇数列の偶数行に配置された画素グループ G C ( $G C_{1,2}, G C_{1,4}, \dots$ ) とに含まれる画素を第二画素とする。

#### 【0074】

このように配線することで、同じ画素グループに属する画素は、同じ共通配線に接続され、隣接する 2 つの画素グループ間では、異なる共通配線に接続される構成となる。

10

#### 【0075】

なお、本実施の形態では、画素グループが  $2 \times 2$  のマトリクス状の画素グループである場合を例に説明したが、これに限るものではない。画素グループの大きさは任意であり、列単位あるいは行単位に設定しても良い。

#### 【0076】

##### < 2 - 2 . 効果等 >

本実施の形態の液晶表示装置では、実施の形態 1 と同様に、第一共通電圧 V COM および第二共通電圧 V COM の 2 種類の共通電圧を用い、画素を第一画素および第二画素の 2 つに分けて、第一画素に第一共通電圧を、第二画素に第二共通電圧を印加している。このように、複数の共通電圧を用いることで、画素電極側（信号配線）に印加する電圧値の範囲を狭くすることが可能になる。これにより、信号配線を駆動するソースドライバ 2 2 に必要とされる駆動能力が小さくなる。さらに、画素間のリーク電圧を低減し、ソースドライバ 2 2 の消費電力を低減し、液晶パネル 1 0 の発熱量を低減させることができることになる。

20

#### 【0077】

##### (その他の実施の形態)

以上、本発明の実施の形態に係る液晶表示装置について説明したが、本発明は、この実施の形態に限定されるものではない。

#### 【0078】

(1) 上記実施の形態 1 および実施の形態 2 では、液晶パネル 1 0 を構成する画素を、第一画素および第二画素の 2 つのグループに分類したが、3 以上のグループに分類しても構わない。

30

#### 【0079】

(2) 上記実施の形態 1 および実施の形態 2 において示した第一共通電圧 V COM 、第二共通電圧 V COM およびソースドライバ 2 2 の出力電圧 G A M 1 ~ G A M 1 0 は一例であり、他の電圧値であっても構わない。

#### 【0080】

(3) 上記実施の形態 1 および実施の形態 2 では、第一画素（のグループ）と第二画素（のグループ）とが千鳥状に配置されている場合について示したが、これに限るものではない。列単位、行単位、あるいは、ランダムに配置するように構成しても良い。また、第一画素と第二画素とは、同じ数である必要はない。第一画素と第二画素の割合および分布は、任意であるが、例えば、電圧値が偏らないように決定してもよい。

40

#### 【0081】

(4) 上記の各装置を構成する構成要素の一部（制御部 2 0 ）は、1 個のシステム L S I (Large Scale Integration : 大規模集積回路) から構成されているとしても良い。システム L S I は、複数の構成部を 1 個のチップ上に集積して製造された超多機能 L S I であり、具体的には、マイクロプロセッサ、R O M、R A Mなどを含んで構成されるコンピュータシステムである。R A M には、コンピュータプログラムが記憶されている。マイクロプロセッサが、コンピュータプログラムに従って動作することにより、システム L S I は、その機能を達成する。

50

## 【0082】

さらにまた、上記の各装置を構成する構成要素の一部または全部は、各装置に脱着可能なI Cカードまたは単体のモジュールから構成されているとしても良い。I Cカードまたはモジュールは、マイクロプロセッサ、ROM、RAMなどから構成されるコンピュータシステムである。I Cカードまたはモジュールは、上記の超多機能LSIを含むとしても良い。マイクロプロセッサが、コンピュータプログラムに従って動作することにより、I Cカードまたはモジュールは、その機能を達成する。このI Cカードまたはこのモジュールは、耐タンパ性を有するとしても良い。

## 【0083】

さらに、上記実施の形態及び上記変形例をそれぞれ組み合わせるとしても良い。

10

## 【産業上の利用可能性】

## 【0084】

本発明は、液晶表示装置に有用である。

## 【符号の説明】

## 【0085】

|                                                |          |    |

|------------------------------------------------|----------|----|

| 1                                              | 液晶表示装置   |    |

| 2、100                                          | 表示部      |    |

| 10、10A、10B、110                                 | 液晶パネル    |    |

| 20、120                                         | 制御部      |    |

| 21、121                                         | ゲートドライバ  | 20 |

| 22、122                                         | ソースドライバ  |    |

| 23、123                                         | コモンドライバ  |    |

| C <sub>1</sub> ~C <sub>i</sub> ~C <sub>m</sub> | 画素       |    |

| C E                                            | 共通電極     |    |

| P E                                            | 画素電極     |    |

| L L                                            | 液晶層      |    |

| T                                              | スイッチング素子 |    |

| COM L、COM L 1、COM L 2                          | 共通配線     |    |

| G L 1、G L m、G L i                              | ゲート線     |    |

| S L 1、S L n、S L j                              | ソース線     | 30 |

【図1】

【図2】

【図3】

【図4】

|       | +    |    | -     |    |

|-------|------|----|-------|----|

| Lv255 | GAM1 | 5V | GAM10 | 1V |

|       | GAM2 | 4V | GAM9  | 2V |

|       | GAM3 | 3V | GAM8  | 3V |

|       | GAM4 | 2V | GAM7  | 4V |

| Lv0   | GAM5 | 1V | GAM6  | 5V |

【図5】

【図6】

【図7】

【図8】

|                |                                                                                                                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2015040911A</a>                                                                                                                                                                          | 公开(公告)日 | 2015-03-02 |

| 申请号            | JP2013170643                                                                                                                                                                                           | 申请日     | 2013-08-20 |

| [标]申请(专利权)人(译) | 船井电机株式会社                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 船井电机株式会社                                                                                                                                                                                               |         |            |

| [标]发明人         | 森丈弘                                                                                                                                                                                                    |         |            |

| 发明人            | 森 丈弘                                                                                                                                                                                                   |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/36 G09G3/20.624.C G09G3/20.624.E G09G3/20.624.D G02F1/133.550                                                                                                                                    |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZE40 2H193/ZF21 2H193/ZF31 2H193/ZF59 2H193/ZQ16 5C006/AC25 5C006 /AC26 5C006/BB16 5C006/BC22 5C006/FA47 5C080/AA10 5C080/BB05 5C080/DD26 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 |         |            |

| 代理人(译)         | 纯一奥玛特                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                              |         |            |

### 摘要(译)

提供一种能够减少功耗和热量产生的液晶显示装置。多个像素C11分别包括公共电极CE，被施加与像素值相对应的电压的像素电极PE，以及形成在公共电极CE与像素电极PE之间的液晶层LL。)至Cmn，多个像素C11至C mn，连接至第一像素的公共电极CE的第一公共布线COML1以及多个像素C11至C mn将第一公共电压VCOMα施加到与 mn 中的第二像素的公共电极CE连接的第二公共布线COML2和第一公共布线COML1，并且将第一公共电压施加到第二公共布线COML2。公共驱动器23施加与电压VCOMα不同的第二公共电压VCOMβ。[选择图]图2