(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-191616

(P2019-191616A)

(43) 公開日 令和1年10月31日(2019.10.31)

(51) Int.Cl.

**G02F 1/1368 (2006.01)**

**G02F 1/1343 (2006.01)**

**G02F 1/1333 (2006.01)**

F 1

GO2F 1/1368

GO2F 1/1343

GO2F 1/1333

テーマコード(参考)

2H092

2H189

2H192

審査請求 有 請求項の数 5 O L (全 13 頁)

(21) 出願番号 特願2019-145901 (P2019-145901)

(22) 出願日 令和1年8月8日 (2019.8.8)

(62) 分割の表示 特願2018-165677 (P2018-165677)

原出願日 平成26年4月17日 (2014.4.17)

(71) 出願人 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 110000350

ポレール特許業務法人

(72) 発明者 沖田 光隆

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

F ターム(参考) 2H092 GA14 GA35 GA62 JA26 JB05

JB14 JB56 NA01 PA08 PA09

QA06

2H189 AA14 HA05 HA16 JA14 LA03

LA10 LA14 LA15 LA28 LA31

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】ソース線上に共通電極の分割領域が位置するとともに、ソース線からの漏れ電界が共通電極の分割領域を通して液晶層に影響を与える。

【解決手段】表示装置は、アレイ基板と対向基板とを備える。前記アレイ基板は、走査信号配線と、映像信号配線と、補助配線と、第1の絶縁層と、第2の絶縁層と、前記補助配線よりも下層に前記第1の絶縁層を介して配置される共通電極と、前記補助配線よりも上層に前記第2の絶縁層を介して配置される画素電極と、を備える。前記補助配線は平面視で前記映像信号配線を覆う位置に配置するようにされる。前記共通電極は前記映像信号配線上で前記第2の方向に分割するようにされる。

【選択図】図10

**【特許請求の範囲】****【請求項 1】**

第1の基板と、第2の基板と、前記第1の基板と前記第2の基板の間に配置される液晶層と、を備える表示装置であって、

前記第1の基板は、

複数の走査信号配線と、

複数の映像信号配線と、

複数の補助配線と、

共通電極と、

画素電極と、

を備え、

前記第2の基板は、

複数の色相のカラーフィルタを備え、

前記共通電極は、前記映像信号配線と重畠する重畠領域と、前記映像信号配線の延在方向に沿って設けられる非形成領域を有し、

前記補助配線は、前記映像信号配線と重畠する位置に配置され、且つ前記映像信号配線と同じ方向に延在し、

複数の前記補助配線のうち少なくとも一つは、前記共通電極の非形成領域に重なって配置され、その他の複数の前記補助配線は前記共通電極に重なって配置されることを特徴とする表示装置。

10

20

30

40

40

50

**【請求項 2】**

断面視で見て、前記共通電極と前記補助配線との間には、第1の絶縁膜が形成され、

前記共通電極は、前記第1の絶縁膜に形成されたコンタクトホールを介して、前記補助配線と接続されることを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記第2の基板は遮光層を備え、

断面視で見て、前記遮光層は、前記補助配線と前記映像信号配線が重畠する位置に配置されることを特徴とする請求項1または2に記載の表示装置。

**【請求項 4】**

前記共通電極および前記画素電極は透明性導電膜であり、

前記補助配線は遮光性導電膜であることを特徴とする請求項1乃至3の何れか一項に記載の表示装置。

**【請求項 5】**

前記共通電極はタッチパネルの電極配線の機能を兼ねることを特徴とする請求項1乃至4の何れか一項に記載の表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示は表示装置に関し、例えばインセル型タッチパネルを有する表示装置に適用可能である。

**【背景技術】****【0002】**

近年、モバイル用途の液晶表示装置ではスマートフォン向けを中心に入力機能としての静電容量タッチパネルが導入されている。さらにこの静電容量タッチパネルは、液晶表示装置内にその機能を組み込むインセル化がすすめられている。

国際公開第2012/073792号(特許文献1)に開示されるように、コモン電極(共通電極)はインセルタッチパネル用の駆動電極および検出電極と兼ねるために、コモン電極が複数に分離されている。コモン電極の分離領域は色画素境界上を行方向(走査線延在方向)および/または列方向(信号線延在方向)に延びるように形成されている。さらに、共通電極にスリットを設け、このスリット(細長い孔)が色画素境界上を行方向お

および／または列方向に延びるように形成されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】国際公開第2012/073792号

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1のような共通電極の分離領域が信号線上に位置すると、信号線からの漏れ電界が共通電極の分離領域を通して液晶層に影響を与える。このため、共通電極の分離領域に隣接する画素では信号線から電界の影響で所望の表示ができないことがあり、特に対向基板とアレイ基板の組立てずれが生じた場合には共通電極の分離領域がスジとして見えてしまう。

その他の課題と新規な特徴は、本開示の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0005】

本開示のうち、代表的なものの概要を簡単に説明すれば、下記のとおりである。

(1) 表示装置は第1の基板と第2の基板とを備える。前記アレイ基板は、第1の方向に延在する第1の信号配線層と、前記第1の方向と異なる第2の方向に延在する第2の信号配線層と、前記第2の信号配線層よりも上層に配置される画素電極層と、前記画素電極層よりも上層に配置される共通電極層と、前記共通電極層の上に接するように配置される配線層と、を備える。前記共通電極層は平面視で前記第2の信号配線層を覆う位置に配置するようになれる。前記配線層は平面視で前記第2の信号配線層を覆う位置に配置するようになれる。前記共通電極層は前記第2の方向に分割するようになれる。

(2) 表示装置は第1の基板と第2の基板とを備える。前記第1の基板は、第1の方向に延在する第1の信号配線層と、前記第1の方向と異なる第2の方向に延在する第2の信号配線層と、前記第2の方向に延在する第1の配線層と、第1の絶縁層と、第2の絶縁層と、前記第1の配線層よりも下層に前記第1の絶縁層を介して配置される共通電極層と、前記第1の配線層よりも上層に前記第2の絶縁層を介して配置される画素電極層と、を備える。前記第1の配線層は平面視で前記第2の信号配線層を覆う位置に配置するようになれる。前記共通電極層は前記第2の信号配線層上で前記第2の方向に分割するようになれる。

【図面の簡単な説明】

【0006】

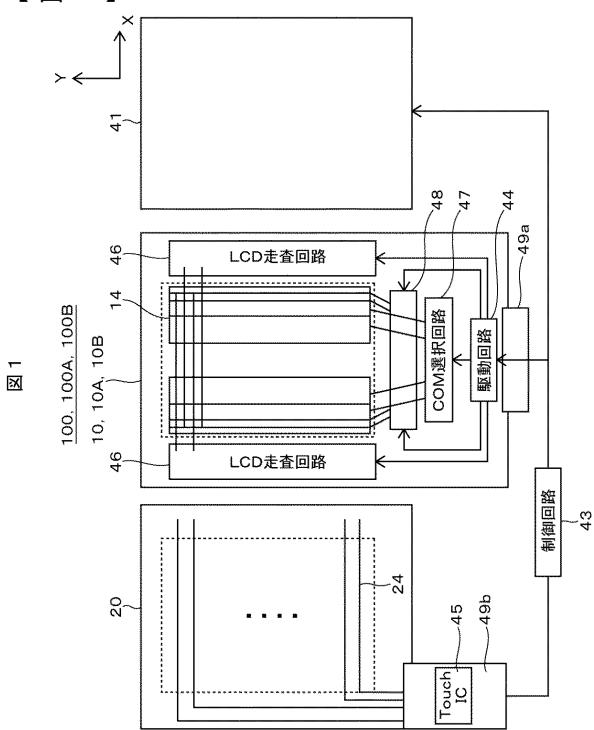

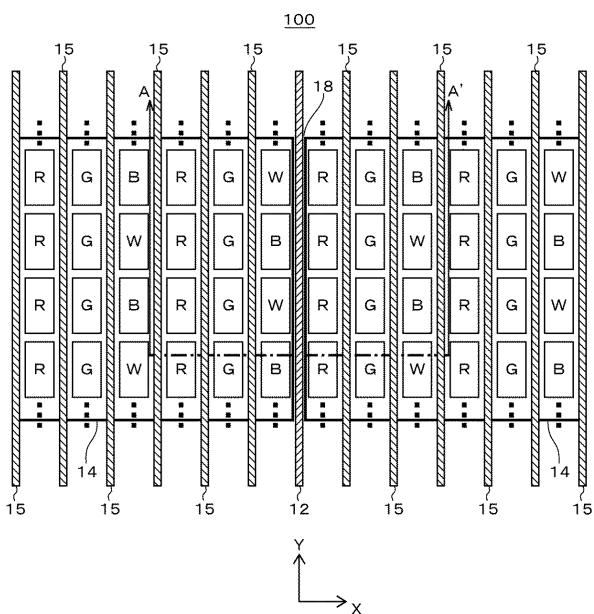

【図1】実施例および比較例に係る表示装置の構成を示す平面図である。

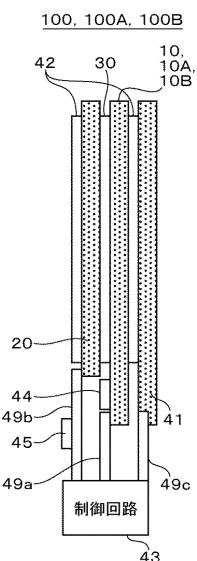

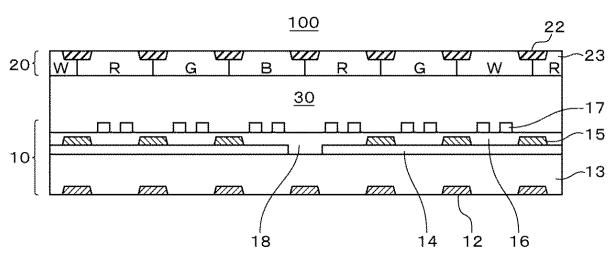

【図2】実施例および比較例に係る表示装置の構成を示す側面図である。

【図3】比較例に係る表示装置の構造を説明するための平面図である。

【図4】図1のA-A'線における断面図である。

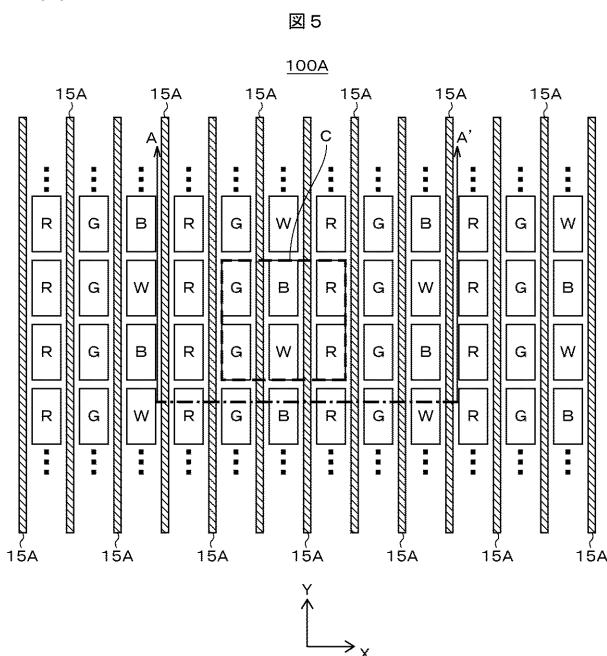

【図5】実施例1に係る表示装置の構造を説明するための平面図である。

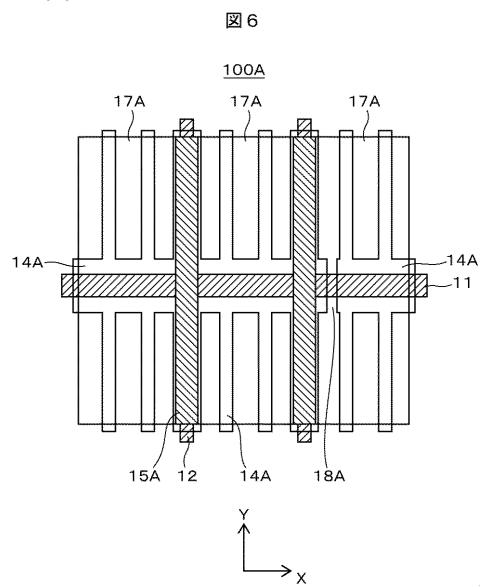

【図6】図5の破線Cの箇所の拡大図である。

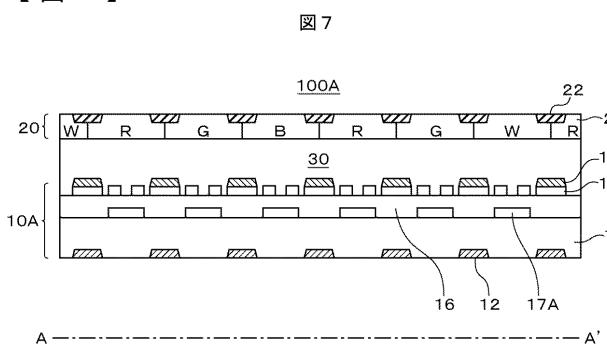

【図7】図5のA-A'線における断面図である。

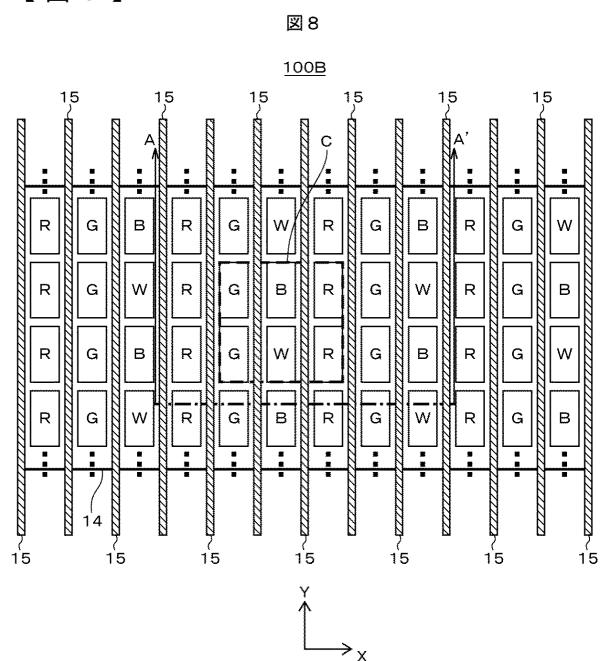

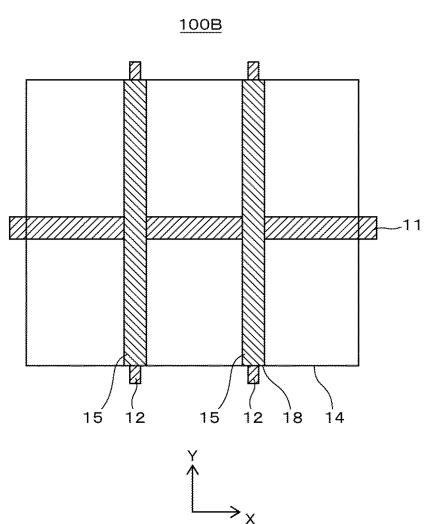

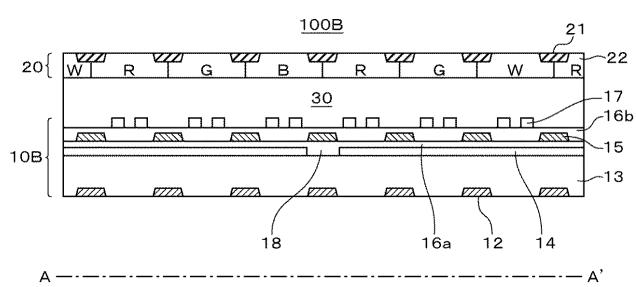

【図8】実施例2に係る表示装置の構造を説明するための平面図である。

【図9】図8の破線Cの箇所の拡大図である。

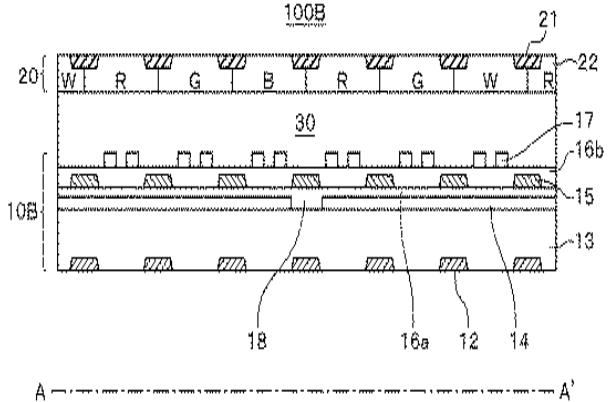

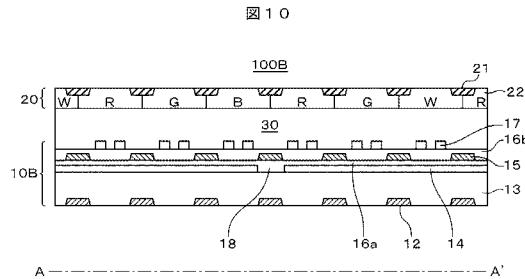

【図10】図8のA-A'線における断面図である。

【図11】アレイ基板周辺部における断面図である。

【発明を実施するための形態】

【0007】

以下に、実施例および比較例について、図面を参照しつつ説明する。なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到

10

20

30

40

50

し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。

#### 【0008】

まず、本開示に先立って検討した技術（以下、比較例という。）、実施例1および実施例2に共通する内容について図1および図2を用いて説明する。

図1は実施例および比較例に係る表示装置の構成を示す平面図である。図2は実施例および比較例に係る表示装置の構成を示す側面図である。比較例、実施例1および実施例2に係る液晶表示装置100、100A、100Bは、インセルタイプのタッチパネル機能を有し、共通電極層がタッチパネルの駆動電極層の機能を兼ねている。

10

表示装置100、100A、100Bは、アレイ基板10、10A、10Bと対向基板20と液晶層30とバックライト41と偏光板42と制御回路43とタッチIC45とケーブル49a、49b、49cを有する。表示装置100、100A、100Bは縦長である（Y方向の長さがX方向の長さよりも大きい）。アレイ基板10、10A、10Bには、LCD走査回路46と共に電極選択回路（COM選択回路）47と信号線選択回路48がTFTで形成されている。また、アレイ基板10、10A、10Bには、CMOS等の半導体集積回路（IC）で構成された駆動回路44がCOG（Chip on Glass）実装されている。駆動回路44はケーブル49aを介してICで構成された制御回路43に接続されている。対向基板20の上面（液晶層30とは反対側）にはX方向に延在する複数の検出電極配線層24が形成され、検出電極配線層24はケーブル49bを介して、ケーブル49b上に実装されたタッチIC（Touch IC）45に接続されている。ケーブル49bは制御回路43と接続されている。バックライト41は、ケーブル49cを介して制御回路43に接続されている。偏光板42は、バックライト41とアレイ基板10、10A、10Bとの間および対向基板20の上面に配置されている。

20

タッチパネルの駆動電極配線層の機能を兼ねる共通電極配線層14はY方向に延在し、X方向に分割されて周期的に配置されており、検出電極配線層24はX方向に延在し、Y方向に複数配置されている。共通電極配線層（タッチパネルの駆動電極配線層）がY方向に延在することにより、タッチパネルの駆動電極配線層がソース配線層と交わらないため、タッチパネルの駆動電極配線層-ソース配線層容量の影響でタッチパネルの駆動電極の負荷が増大するのを抑えることができる。

30

なお、比較例、実施例1および実施例2に係る液晶表示装置100、100A、100Bは、アレイ基板10、10A、10Bの構造の除き、基本的に同じ構成である。

#### 【0009】

次に、比較例について図3および図4を用いて説明する。

図3は比較例に係る表示装置の構造を説明するための平面図である。図4は図3のA-A'線における断面図である。

比較例に係る表示装置100は赤（R）、緑（G）、青（B）、白（W）の縦ストライプ形状の副画素を備え、RGBおよびRGWをそれぞれ1画素とし、RGB画素とRGW画素が交互に配置される。BおよびWのそれぞれはRまたはGの半分の画素数である。表示装置100は、アレイ基板10と、対向基板20と、アレイ基板10と対向基板20との間に配置される液晶層30とを備える。

40

アレイ基板10において、信号配線層12の上に平坦化膜13を介して共通電極層14が配置される。共通電極層14の上に絶縁層16を介して画素電極層17が配される。共通電極層14は信号配線層12と平行な方向（Y方向）に延在し、X方向に分割されて周期的に配置されており、信号配線層12の上には共通電極層14と接する形で補助配線層15が配置されている。言い換えると補助配線層15は異色副画素間に配置されている。ただし、分割された共通電極層14同士をショートしないようにするために、共通電極層14の分割位置（分割領域）18には補助配線層15は配置されていない。共通電極層1

50

4 および画素電極層 17 は ITO (Indium Tin Oxide) 等の透光導体膜で形成され、補助配線層 15 および信号配線層 12 は遮光導体膜（低抵抗導体膜、金属膜）で形成されている。補助配線層 15 は共通電極層 14 の抵抗を低減するために設けられている。

対向基板 20 は、ブラックマトリクス（遮光層）22 と、R、G、B、W のカラーフィルタ（着色層）23 と、を備える。カラーフィルタ 23 は、行方向（X 方向）に R、G、B、R、G、W の順に繰り返し配置されている。また、カラーフィルタ 23 の R と G は、列方向（Y 方向）に同色が配置され、B と W は交互に配置されている。カラーフィルタ 23 は平面視で、X 方向の長さが Y 方向の長さより短いストライプ形状（矩形状）をしている。

上述したように、表示装置 100 では信号配線層 12 上に分割領域 18 が位置するので、分割領域 18 を通した信号配線層 12 からの漏れ電界が液晶層 30 に影響を与える。このため、分割領域 18 に隣接する副画素では信号配線層 12 から電界の影響で所望の表示ができないことがあり、特に対向基板 20 とアレイ基板 10 の組立てずれが生じた場合には分割領域 18 がスジとして見えてしまう。

そこで、実施の形態に係る表示装置は、信号配線層 12 の上にシールド層を設けて、信号配線層 12 からの漏れ電界が液晶層 30 に影響を与えないようにする。シールド層としては電位が固定される配線層を用いるのが好ましい。

#### 【0010】

以下に説明する実施例では、FFS (Fringe Field Switching) 方式の液晶表示パネルを例に説明するが、それに限定されるものではない。IPS (In-Plane-Switching) 方式等の横電界の液晶表示パネルにも適用することができる。

#### 【実施例 1】

#### 【0011】

信号配線層の上にシールド層を設ける第 1 の実施例（実施例 1）について図 5 から図 7 を用いて説明する。

図 5 は実施例 1 に係る表示装置の構造を説明するための平面図である。図 6 は図 5 の破線 C の箇所の拡大図である。図 7 は図 5 の A - A' 線における断面図である。

実施例 1 に係る表示装置 100A は、比較例に係る表示装置 100 と画素構成および配列は同じである。すなわち、対向基板 20 の構造は同じである。表示装置 100A は、アレイ基板 10A と、対向基板 20 と、アレイ基板 10A と対向基板 20 との間に配置される液晶層 30 とを備える。なお、R、G、B の縦ストライプ形状の副画素を備え、RGB を 1 画素とするものであってもよい。すなわち、カラーフィルタ 23 は、行方向（X 方向）に R、G、B の順に繰り返し配置され、カラーフィルタ 23 の列方向（Y 方向）に同色が配置されているものであってもよい。

アレイ基板 10A において、信号配線層（映像信号配線層、第 2 の信号配線層）12 の上に平坦化膜 13 を介して画素電極層 17A が配置される。画素電極層 17A の上に絶縁層 16 を介して共通電極層 14A が配される。共通電極層 14A は信号配線層 12 と平行な方向（Y 方向）に延在し、X 方向に分割されて周期的に配置されている。走査配線層（走査信号配線層、第 1 の信号配線層）11 は X 方向に延在している。共通電極 14A の分割領域 18A は信号配線層 12 が配置されない位置であって走査配線層 11 を横切る位置に配置される。副画素の開口部分の共通電極層 14A にはスリットが形成されている。信号配線層 12 は共通電極層 14A で覆われている。また、信号配線層 12 の上には共通電極層 14A と接する形で補助配線層（第 1 の配線層）15A が配置されている。言い換えると補助配線層 15A は異色副画素間に配置されている。補助配線層 15A は遮光層 22 に覆われるよう配置される。走査配線層 11 の上には共通電極層 14A がある。分割領域 18A は補助配線層 15A が配置されない位置であって走査配線層 11 を横切る位置に配置される。分割領域 18A は遮光層 22 に覆われるよう配置される。共通電極層 14A および画素電極層 17A は ITO (Indium Tin Oxide) 等の透光導体膜で形成され、補助配線層 15A および信号配線層 12 は金属膜（遮光性導電膜）で形成されている。

#### 【0012】

10

20

30

40

50

上述したように、表示装置 100A では信号配線層 12 上に共通電極層 14A を配置するので、信号配線層 12 からの漏れ電界を共通電極層 14A でシールドすることができる。これにより、比較例に係る表示装置のような分割領域 18 がスジとして見えることを防止することができる。

なお、信号配線層 12 からの漏れ電界をシールドするためには、補助配線層 15A は必ずしも必要ない。ただし、補助配線層 15A が遮光膜で形成される場合は、高精細パネルにおいて、対向基板 20 とアレイ基板 10 の組立ずれが起きたときに生じる視野角混色を低減することができる。また、補助配線層 15A が低抵抗の導電膜で形成される場合は、共通電極層 14A の抵抗を低減することができる。

#### 【0013】

10

以上の実施例 1 の概要を簡単に説明すれば、下記のとおりである。

(1) 表示装置は、アレイ基板と、対向基板と、前記アレイ基板と前記対向基板の間に配置される液晶層と、を備える。前記アレイ基板は、第 1 の方向に延在する走査信号配線層と、前記第 1 の方向と異なる第 2 の方向に延在する映像信号配線層と、前記映像信号配線層よりも上層に配置される画素電極層と、前記画素電極層よりも上層に配置される共通電極層と、を備える。前記共通電極層は平面視で前記映像信号配線層を覆う位置に配置するようになされ、前記共通電極層は前記第 2 の方向に分割するようになされる。

(2) 上記(1)の表示装置において、前記共通電極層が分割される個所はいずれかの隣接する映像信号配線層間の前記走査信号配線層を横切る位置にするようになされる。

(3) 上記(1)の表示装置において、前記共通電極層の上に接するようになされる補助配線層を有し、前記補助配線層は平面視で前記映像信号配線層を覆う位置に配置するようになされる。

20

(4) 上記(3)の表示装置において、前記共通電極層が分割される個所は前記補助配線層が配置されていない位置にするようになされる。

(5) 上記(3)の表示装置において、前記補助配線層は遮光性導電膜である。

(6) 上記(1)の表示装置において、前記共通電極層は平面視で前記走査信号配線層を覆う位置に配置するようになされる。

(7) 上記(1)の表示装置において、前記対向基板は遮光層と着色層を備える。前記遮光層は平面視で前記補助配線層を覆う位置に配置するようになされる。

30

(8) 上記(7)の表示装置において、前記遮光層は平面視で前記共通電極層が分割される個所を覆う位置に配置するようになれる。

(9) 上記(1)の表示装置において、前記画素電極および共通電極層は透明性導電膜である。

(10) 上記(1)の表示装置において、前記対向基板は、前記第 1 の方向に延在する検出電極配線層を備える。前記共通電極層はインセルタッチパネルの駆動電極配線層の機能を兼ねる。

#### 【0014】

40

(11) 表示装置は第 1 の基板と第 2 の基板とを備える。前記アレイ基板は、第 1 の方向に延在する第 1 の信号配線層と、前記第 1 の方向と異なる第 2 の方向に延在する第 2 の信号配線層と、前記第 2 の信号配線層よりも上層に配置される画素電極層と、前記画素電極層よりも上層に配置される共通電極層と、前記共通電極層の上に接するようになされる第 1 の配線層と、を備える。前記共通電極層は平面視で前記第 2 の信号配線層を覆う位置に配置するようになれる。前記共通電極層は前記第 2 の方向に分割するようになれる。

(12) 上記(11)の表示装置において、前記共通電極層が分割される個所は前記第 1 の配線層が配置されていない位置にするようになれる。

(13) 上記(11)の表示装置において、前記共通電極層は平面視で前記第 1 の信号配線層を覆う位置に配置するようになれる。

(14) 上記(11)の表示装置において、前記第 2 の基板は遮光層を備える。前記遮光層は平面視で前記配線層を覆う位置に配置するようになれる。

50

(15) 上記(11)の表示装置において、前記第1の配線層は平面視で異色副画素間に配置するようにされる。

(16) 上記(11)の表示装置において、前記画素電極および共通電極層は透明性導電膜である。前記第1の配線層は遮光性導電膜である。

(17) 上記(11)の表示装置において、前記第2の基板は、前記第1の方向に延在する検出電極配線層を備える。前記共通電極層はインセルタッチパネルの駆動電極配線層の機能を兼ねる。

(18) 上記(11)の表示装置において、前記第1の信号配線層は走査信号配線層である。前記第2の信号配線層は映像信号配線層である。

(19) 上記(11)の表示装置において、さらに、前記第1の基板と前記第2の基板の間に配置される液晶層を備える。

10

### 【実施例2】

#### 【0015】

信号配線層の上にシールド層を設ける第2の実施例(実施例2)について図8から図11を用いて説明する。

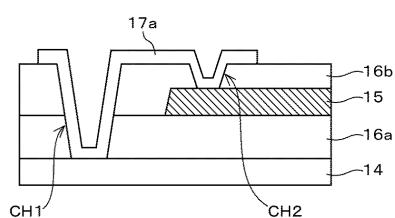

図8は実施例2に係る表示装置の構造を説明するための平面図である。図9は図8の破線Cの箇所の拡大図である。図10は図8のA-A'線における断面図である。図11はアレイ基板周辺部における断面図である。

実施例2に係る表示装置100Bは、比較例に係る表示装置と画素構成および配列は同じである。すなわち、対向基板20の構造は同じである。表示装置100Bは、アレイ基板(第1の基板)10Bと、対向基板(第2の基板)20と、アレイ基板10Bと対向基板20との間に配置される液晶層30とを備える。なお、R、G、Bの縦ストライプ形状の副画素を備え、RGBを1画素とするものであってもよい。すなわち、カラーフィルタ23は、行方向(X方向)にR、G、Bの順に繰り返し配置され、カラーフィルタ23の列方向(Y方向)に同色が配置されているものであってもよい。

アレイ基板10Bにおいて、信号配線層(映像信号配線層、第2の信号配線層)12の上に平坦化膜13を介して共通電極層14が配置される。共通電極層14の上に絶縁層(第1の絶縁層)16aを介して補助配線層(第1の配線層)15が配置される。補助配線層15の上に絶縁層(第2の絶縁層)16bを介して画素電極層17が配置される。共通電極層14は信号配線層12と平行な方向(Y方向)に延在し、X方向に分割されて周期的に配置されている。走査配線層(走査信号配線層、第1の信号配線層)11はX方向に延在している。補助配線層15は信号配線層12と平行な方向(Y方向)に延在し、各異色副画素間に配置されている。補助配線層15は高精細パネルにおいて、対向基板20とアレイ基板10Bの組立ずれが起きたときに生じる視野角混色を防止する遮光層の役割と共通電極層14の抵抗低減する役割を兼ねている。補助配線層15は共通電極層14の分割位置(分割領域)18の上にも配置されている。共通電極層14および画素電極層17はITO等の透光導体層で形成され、補助配線層15および信号配線層12は遮光導体層(低抵抗導体層、金属層)で形成されている。

図11に示すように、アレイ基板10Bの表示領域外の周辺領域において、共通電極層14と補助配線層15とは配線層(第2の配線層)17aを介して接続される。配線層17aは画素電極層17と同層の配線である。絶縁層16aと絶縁層16bとを同時にパターニングしてコンタクトホールCH1を形成する。また、絶縁層16bパターニングしてコンタクトホールCH2を形成する。コンタクトホールCH1とコンタクトホールCH2の中および絶縁層16bの上面にITO膜を成膜し、パターニングすることにより、画素電極層17と配線層17aを形成する。

20

#### 【0016】

上述したように、表示装置100Bでは信号配線層12の分割領域18の上に補助配線層15を配置するので、信号配線層12からの画素電極17へ漏れ電界シールドすることができる。これにより、比較例に係る表示装置のような分割領域18がスジとして見えることを防止することができる。

30

40

50

また、比較例に係る表示装置とは異なりすべての信号配線上に補助配線層15を配置することができるので、対向基板20とアレイ基板10Bの組立ずれが起きたときに生じる視野角混色を低減することができる。

#### 【0017】

共通電極層14と画素電極層17との間の絶縁膜を複数層とするが、複数層の絶縁膜は同時にパターニングすることで、成膜回数は増えるがフォトリソ工程の回数は比較例と同じであるため製造プロセスへの負荷を小さくすることできる。

共通電極層14と補助配線層15は例えば表示領域外のパネル周辺部で接続することで画素内に開口率を低下要因となるコンタクトホールを設けることなく信号配線層からの画素電極層への漏れ電界のシールド効果を高めることができる。補助配線層15が共通電極層14と接続することができるので、共通電極層14の抵抗を低減することができる。

#### 【0018】

以上の実施例2の概要を簡単に説明すれば、下記のとおりである。

(1) 表示装置は、アレイ基板と、対向基板と、前記アレイ基板と前記対向基板の間に配置される液晶層と、を備える。前記アレイ基板は、第1の方向に延在する走査信号配線層と、前記第1の方向と異なる第2の方向に延在する映像信号配線層と、前記第2の方向に延在する補助配線層と、第1の絶縁層と、第2の絶縁層と、前記補助配線層よりも下層に前記第1の絶縁層を介して配置される共通電極層と、前記補助配線層よりも上層に前記第2の絶縁層を介して配置される画素電極層と、を備える。前記補助配線層は平面視で前記映像信号配線層を覆う位置に配置するようになれる。前記共通電極層は前記映像信号配線層上で前記第2の方向に分割するようになれる。

(2) 上記(1)の表示装置において、前記画素電極層とは孤立しあつ前記画素電極層とは同層の配線層を有する。前記共通電極層は、前記配線層を介して前記補助配線層と接続するようになれる。

(3) 上記(2)の表示装置において、前記共通電極上の前記第1の絶縁層と前記第2の絶縁層を貫通する第1のコンタクトホールと、前記補助配線層上の前記第2の絶縁層の第2のコンタクトホールと、を有する。前記配線層は前記第1のコンタクトホール内の前記共通電極層と前記第2のコンタクトホール内の前記補助配線層とを接続するようになれる。

(4) 上記(1)の表示装置において、前記対向基板は着色層と遮光層を備える。前記遮光層は平面視で前記補助配線層を覆う位置に配置するようになれる。

(5) 上記(1)の表示装置において、前記補助配線層は平面視で異色副画素間に配置するようになれる。

(6) 上記(1)の表示装置において、前記共通電極層および前記画素電極層は透明性導電膜である。前記補助配線層は遮光性導電膜である。

(7) 上記(1)の表示装置において、前記対向基板は、前記第1の方向に延在する検出電極配線層を備える。前記共通電極層はインセルタッチパネルの駆動電極配線層の機能を兼ねる。

#### 【0019】

(8) 表示装置は第1の基板と第2の基板とを備える。前記第1の基板は、第1の方向に延在する第1の信号配線層と、前記第1の方向と異なる第2の方向に延在する第2の信号配線層と、前記第2の方向に延在する第1の配線層と、第1の絶縁層と、第2の絶縁層と、前記第1の配線層よりも下層に前記第1の絶縁層を介して配置される共通電極層と、前記第1の配線層よりも上層に前記第2の絶縁層を介して配置される画素電極層と、を備える。前記第1の配線層は平面視で前記第2の信号配線層を覆う位置に配置するようになれる。前記共通電極層は前記第2の信号配線層上で前記第2の方向に分割するようになれる。

(9) 上記(8)の表示装置において、前記画素電極層とは孤立しあつ前記画素電極層とは同層の第2の配線層を有する。前記共通電極層は前記第2の配線層を介して前記第1の配線層と接続するようになれる。

10

20

30

40

50

(10) 上記(9)の表示装置において、前記共通電極層上の前記第1の絶縁層と前記第2の絶縁層を貫通する第1のコンタクトホールと、前記第1の配線層上の前記第2の絶縁層の第2のコンタクトホールと、を有する。前記第2の配線層は前記第1のコンタクトホール内の前記共通電極層と前記第2のコンタクトホール内の前記補助配線層とを接続するようされる。

(11) 上記(8)の表示装置において、前記第2の基板は遮光層および着色層を備える。前記遮光層は平面視で前記第1の配線層を覆う位置に配置するようされる。

(12) 上記(8)の表示装置において、前記第1の配線層は平面視で異色副画素間に配置するようされる。

(13) 上記(8)の表示装置において、前記共通電極層および画素電極層は透明性導電膜である。前記第1の配線層は遮光性導電膜である。 10

(14) 上記(8)の表示装置において、前記第2の基板は前記第1の方向に延在する検出電極配線層を備える。前記共通電極層はインセルタッチパネルの駆動電極配線層の機能を兼ねる。

(15) 上記(8)の表示装置において、前記第1の信号配線層は走査信号の配線層である。前記第2の信号配線層は映像信号の配線層である。

(16) 上記(8)の表示装置において、さらに、前記第1の基板と前記第2の基板の間に配置される液晶層を備える。

#### 【符号の説明】

##### 【0020】

10、10A、10B・・・アレイ基板

20・・・対向基板

11・・・走査配線層（走査信号配線層、第1の信号配線層）

12・・・信号配線層（映像信号配線層、第2の信号配線層）

13・・・平坦化層

14、14A・・・共通電極層

15、15A・・・補助配線層（第1の配線層）

16・・・絶縁層

16a・・・絶縁層（第1の絶縁層）

16b・・・絶縁層（第2の絶縁層）

17、17A・・・画素電極層

17a・・・配線層（第2の配線層）

18・・・分割領域（分割位置）

21・・・ブラックマトリクス（遮光層）

22・・・カラーフィルタ（着色層）

24・・・検出電極配線層

30・・・液晶層

41・・・バックライト

42・・・偏光板

43・・・制御回路

44・・・駆動回路

45・・・タッチIC

46・・・LCD走査回路

47・・・共通電極選択回路

48・・・信号線選択回路

49a、49b、49c・・・ケーブル

100、100A、100B・・・表示装置

10

20

30

40

【 図 1 】

【 図 2 】

図 2

〔 3 〕

図3

( 四 4 )

図 4

【圖 5】

【 四 6 】

【図7】

〔 四 8 〕

【図9】

図9

【図10】

図10

【図11】

図11

---

フロントページの続き

F ターム(参考) 2H192 AA24 BA17 BA51 BB13 BB73 BB83 BB84 CB05 EA04 EA22

EA43 EA66 EA72 EA74 GB33 JA32

|                |                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2019191616A</a>                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2019-10-31 |

| 申请号            | JP2019145901                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2019-08-08 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 沖田光隆                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 沖田 光隆                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G02F1/1368 G02F1/1343 G02F1/1333                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G02F1/1368 G02F1/1343 G02F1/1333                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/GA35 2H092/GA62 2H092/JA26 2H092/JB05 2H092/JB14 2H092/JB56 2H092/NA01 2H092/PA08 2H092/PA09 2H092/QA06 2H189/AA14 2H189/HA05 2H189/HA16 2H189/JA14 2H189/LA03 2H189/LA10 2H189/LA14 2H189/LA15 2H189/LA28 2H189/LA31 2H192/AA24 2H192/BA17 2H192/BA51 2H192/BB13 2H192/BB73 2H192/BB83 2H192/BB84 2H192/CB05 2H192/EA04 2H192/EA22 2H192/EA43 2H192/EA66 2H192/EA72 2H192/EA74 2H192/GB33 2H192/JA32 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

为了解决以下问题：当公共电极的分隔区域位于源极线上时，来自源极线的泄漏电场通过公共电极的分隔区域影响液晶层。阵列基板和相对基板。阵列基板包括扫描信号线，视频信号线，辅助线，第一绝缘层，第二绝缘层，布置在辅助线下方并在其间具有第一绝缘层的公共电极，以及布置在上方的像素电极。辅助线之间具有第二绝缘层。在平面图中，辅助线布置在覆盖视频信号线的位置。公共电极沿第二方向在视频信号线上分开。

图 10