(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-60025

(P2015-60025A)

(43) 公開日 平成27年3月30日(2015.3.30)

| (51) Int.Cl.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>G02F 1/1368 (2006.01)</b> | G02F 1/1368 | 2H192       |

| <b>G09G 3/36 (2006.01)</b>   | G09G 3/36   | 5C006       |

| <b>G09G 3/20 (2006.01)</b>   | G09G 3/20   | 624B        |

|                              | G09G 3/20   | 624C        |

|                              | G09G 3/20   | 680F        |

審査請求 未請求 請求項の数 4 O L (全 16 頁)

|                                                                                                       |                              |            |                                |

|-------------------------------------------------------------------------------------------------------|------------------------------|------------|--------------------------------|

| (21) 出願番号                                                                                             | 特願2013-192690 (P2013-192690) | (71) 出願人   | 308036402                      |

| (22) 出願日                                                                                              | 平成25年9月18日 (2013.9.18)       |            | 株式会社 JVCケンウッド                  |

| (出願人による申告) 平成23年度、独立行政法人情報通信研究機構「高度通信・放送研究開発委託研究／究極立体映像用超高密度・超多画素表示デバイスの研究開発」、産業技術力強化法第19条の適用を受ける特許出願 |                              |            |                                |

|                                                                                                       |                              | (74) 代理人   | 神奈川県横浜市神奈川区守屋町3丁目12番地          |

|                                                                                                       |                              |            | 100083806                      |

|                                                                                                       |                              | (74) 代理人   | 弁理士 三好 秀和                      |

|                                                                                                       |                              |            | 100101247                      |

|                                                                                                       |                              | (74) 代理人   | 弁理士 高橋 俊一                      |

|                                                                                                       |                              | (72) 発明者   | 古屋 正人                          |

|                                                                                                       |                              |            | 神奈川県横浜市神奈川区守屋町3丁目12番地          |

|                                                                                                       |                              | F ターム (参考) | 2H192 AA24 BC31 BC72 CB02 CB13 |

|                                                                                                       |                              |            | CB22 CB33 CC73 DA23 DA52       |

|                                                                                                       |                              |            | DA65 DA67 GD61                 |

|                                                                                                       |                              |            | 5C006 AC25 AC26 BB16 BB28 BC06 |

|                                                                                                       |                              |            | 最終頁に続く                         |

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】液晶を十分に駆動できる画素信号を転送できる容量を確保しつつ、構成の小型化を図ることができる液晶表示装置を提供する。

【解決手段】第1保持容量部C1は、第1トランジスタTr1を介して選択的に入力された画素信号を保持し、保持容量部C11、保持容量部C12ならびに保持容量部C13で構成され、第1トランジスタTr1ならびに第2トランジスタTr2が形成された半導体基板400よりも上層の第1の容量形成層ならびに第2の容量形成層に形成されている。第2保持容量部C2は、第2トランジスタTr2を介して選択的に転送された画素信号を保持し、第1トランジスタTr1ならびに第2トランジスタTr2が形成された半導体基板400よりも上層の第2の容量形成層に形成されている。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

半導体基板と透光性基板との間に挟まれて、マトリックス状に配列された複数の画素回路を有し、

前記画素回路は、前記半導体基板に形成された画素電極と前記透光性基板に形成された共通電極に挟まれた液晶を備え、前記液晶は前記画素電極に印加される電圧と前記共通電極に印加される電圧との電位差に応じて駆動され、前記透光性基板から入射した光が前記液晶にて前記電位差に応じて変調される画素部と、

前記半導体基板に形成され、選択的に画素信号を入力する第1トランジスタと、前記第1トランジスタを介して選択的に入力された画素信号を保持する第1保持容量部と、前記半導体基板に形成され、前記第1保持容量部に保持された画素信号を転送する第2トランジスタと、前記第2トランジスタを介して転送された画素信号を保持する第2保持容量部とを備え、前記第2保持容量部に保持された画素信号の電圧を前記画素電極に印加して前記液晶を駆動する駆動部とを有し、

前記第1保持容量部は、誘電体が電極で挟み込まれ、前記第1トランジスタならびに第2トランジスタが形成された前記半導体基板よりも上層の第1の容量形成層ならびに第2の容量形成層に形成され、前記第2保持容量部は、誘電体が電極で挟み込まれ、前記第2の容量形成層に形成されている

ことを特徴とする液晶表示装置。

**【請求項 2】**

前記第1保持容量部の一方の電極と前記第2保持容量部の一方の電極とは、同一の配線層により共通に形成されている

ことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

前記第1保持容量部の容量値と前記第2保持容量部の容量値とは、前記第1保持容量部の一方の電極と前記第2保持容量部の一方の電極との面積比率により設定される

ことを特徴とする請求項1または2に記載の液晶表示装置。

**【請求項 4】**

前記第1の容量形成層に形成された前記第1保持容量部は、前記第1トランジスタならびに前記第2トランジスタが形成された前記半導体基板の形成領域を上方に略平行移動した位置で、かつ前記第1トランジスタならびに前記第2トランジスタが形成された形成領域の面積と略同等の面積内に形成され、前記第2の容量形成層に形成された前記第1保持容量部ならびに前記第2保持容量部は、前記第1トランジスタならびに前記第2トランジスタが形成された前記半導体基板の形成領域を上方に略平行移動した位置で、かつ前記第1トランジスタならびに前記第2トランジスタが形成された形成領域の面積と略同等の面積内に形成されている

ことを特徴とする請求項1～3のいずれか1項に記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、対向する半導体基板と透光性基板との間に液晶を挟み込む構造を採用した反射型の液晶表示装置に関する。

**【背景技術】****【0002】**

従来、この種の技術としては、例えば以下に示す特許文献1に記載されたものが知られている。特許文献1には、シリコン基板21上にマトリックス状に配置された複数の画素回路7を備えた反射型の液晶表示装置が記載されている。画素回路7は、画素信号がトランジスタTr2を介してコンデンサCs2に書き込まれて保持され、保持された画素信号はトランジスタTr1を介してコンデンサCs1に転送されて保持される。コンデンサCs1に保持された画素信号は、液晶表示素子8の反射電極9aに印加され、液晶表示素子

10

20

30

40

50

8が駆動される。

【0003】

コンデンサCs2は、トランジスタTr2が形成されたシリコン基板21に形成されている。すなわちコンデンサCs2は、シリコン基板の酸化膜をポリシリコン205と高拡散領域209とで挟んだMIS構造で構成されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004-133147号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記従来の液晶表示装置において、液晶を十分に駆動するためには、コンデンサCs2は、コンデンサCs1の容量値に対して、保持した画素信号をコンデンサCs1に十分に転送できる容量値を確保する必要がある。

【0006】

一方、液晶表示装置を小型化したり、高解像度化のために画素数を増やそうとして、画素ピッチを微細化する場合には、単位画素回路の面積が縮小される。これにともなって、シリコン基板21に形成されたコンデンサCs2の面積も縮小され、コンデンサCs2の容量値が減少する。このため、画素ピッチを微細化しようとすると、コンデンサCs2の容量値を十分に確保できず、液晶を十分に駆動できないおそれがあった。

20

【0007】

言い換えれば、コンデンサCs2の容量値を十分に確保して液晶を駆動しようとする、画素ピッチを微細化して液晶表示装置を小型化したり高解像度化を図ることが困難になっていた。

【0008】

本発明の目的は、液晶を十分に駆動できる容量を確保しつつ、構成の小型化や高解像度化を図ることができる液晶表示装置を提供することである。

【課題を解決するための手段】

【0009】

本発明は、半導体基板(400)と透光性基板(412)との間に挟まれて、マトリックス状に配列された複数の画素回路(11)を有し、画素回路は、半導体基板に形成された画素電極(16a)と透光性基板に形成された共通電極(16b)に挟まれた液晶(LC)を備え、液晶は画素電極に印加される電圧と共通電極に印加される電圧との電位差に応じて駆動され、透光性基板から入射した光が液晶にて電位差に応じて変調される画素部と、半導体基板に形成され、選択的に画素信号を入力する第1トランジスタ(Tr1)と、第1トランジスタを介して選択的に入力された画素信号を保持する第1保持容量部(C1)と、半導体基板に形成され、第1保持容量部に保持された画素信号を転送する第2トランジスタ(Tr2)と、第2トランジスタを介して転送された画素信号を保持する第2保持容量部(C2)とを備え、第2保持容量部に保持された画素信号の電圧を画素電極に印加して液晶を駆動する駆動部とを有し、第1保持容量部は、誘電体(410)が電極(L21, L31, M11, M12, M21)で挟み込まれ、第1トランジスタならびに第2トランジスタが形成された半導体基板よりも上層の第1の容量形成層ならびに第2の容量形成層に形成され、第2保持容量部は、誘電体が電極(L33, M22)で挟み込まれ、第2の容量形成層に形成されていることを特徴とする液晶表示装置を提供する。

40

【発明の効果】

【0010】

本発明の液晶表示装置によれば、液晶を十分に駆動できる容量を確保しつつ、構成の小型化や高解像度化を図ることが可能な液晶表示装置を提供することができる。

【図面の簡単な説明】

50

## 【0011】

【図1】本発明の実施形態に係る液晶表示装置の構成を示す図である。

【図2】液晶の駆動電圧と透過率との特性の一例を示す図である。

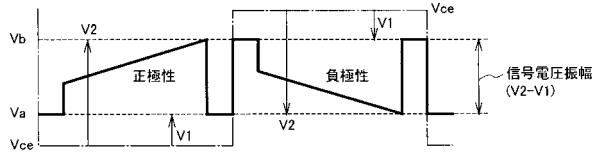

【図3】液晶に印加される電圧と液晶の駆動態様とを模式的に示す図である。

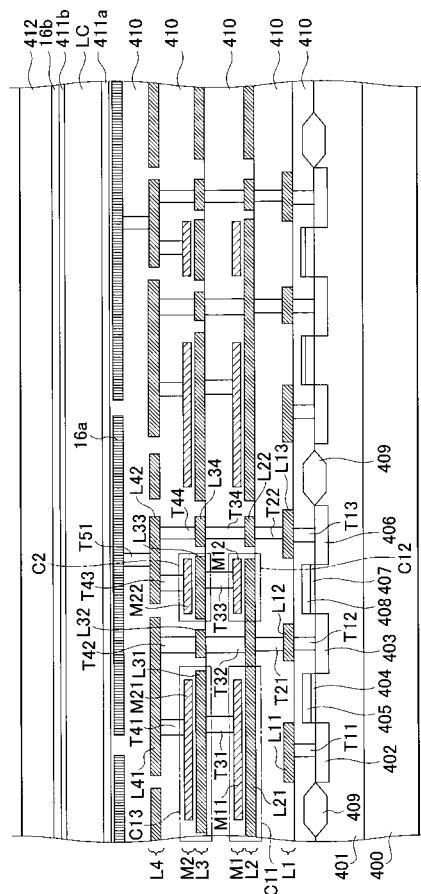

【図4】本発明の実施形態に係る液晶表示装置における画素回路の模式的な断面構造を示す図である。

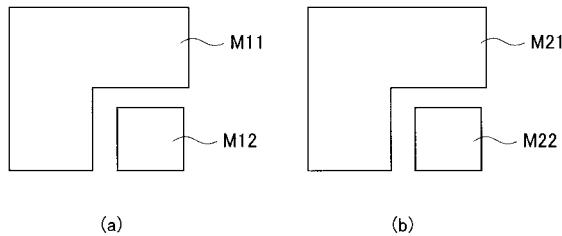

【図5】画素回路の第1容量保持部と第2容量保持部の一方の電極の平面構造を示す図である。

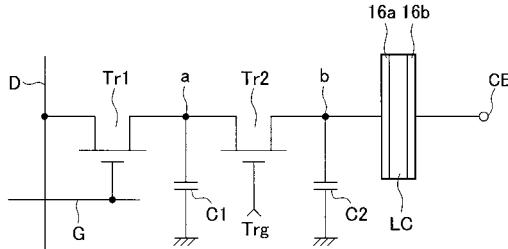

【図6】画素回路における第1容量保持部ならびに第2容量保持部の容量値と画素信号の転送との関係を説明するための図である。

10

## 【発明を実施するための形態】

## 【0012】

以下、図面を用いて本発明を実施するための実施形態を説明する。

## 【0013】

## (実施形態)

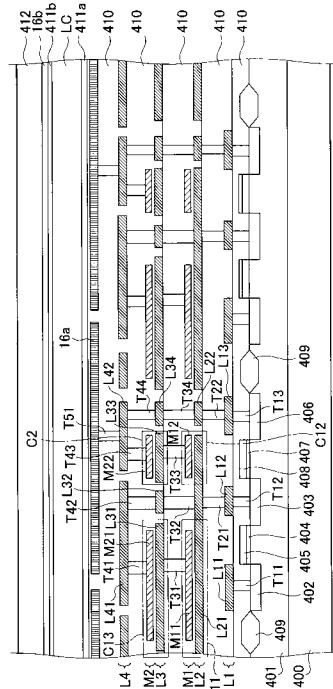

図1を参照して、本発明の一実施形態に係る液晶表示装置の回路構成を説明する。図1において、液晶表示装置は、画素回路11、水平走査回路12ならびに垂直走査回路13を備えている。

## 【0014】

画素回路11は、m本の列データ線D(D1～Dm)とn本の行走査線G(G1～Gn)との各交差部にマトリクス状に複数(m×n個)配置されている。複数の画素回路11は、すべて同一に構成されている。したがって、ここでは、列データ線D1と行走査線G1との交差部に配置された画素回路11を代表して、画素回路11の構成を説明する。

20

## 【0015】

画素回路11は、第1トランジスタTr1、第2トランジスタTr2、第1保持容量部C1、第2保持容量部C2、ならびに液晶LCを備えている。

## 【0016】

第1トランジスタTr1は、スイッチングトランジスタであり、例えばNチャネルのMOS型の電界効果トランジスタで構成されている。第1トランジスタTr1は、ゲート端子が行走査線G1に接続され、ドレイン端子が列データ線D1に接続されている。第1トランジスタTr1は、行走査線G1に与えられる行選択信号に応じて導通制御され、列データ線D1に与えられる画素信号を選択的に画素回路11に入力する。

30

## 【0017】

第2トランジスタTr2は、転送トランジスタであり、例えばNチャネルのMOS型の電界効果トランジスタで構成されている。第2トランジスタTr2は、ゲート端子がトリガ信号線TSに接続され、ドレイン端子が第1トランジスタTr1のソース端子に接続されている。第2トランジスタTr2は、トリガ信号線TSに与えられるトリガ信号(Trg)に応じて導通制御される。第2トランジスタTr2は、第1保持容量部C1に保持された画素信号を第2保持容量部C2に転送する。

40

## 【0018】

第1保持容量部C1は、金属からなる第1電極14aならびに第2電極14bで誘電体(図示せず)を挟んだ、所謂MIM(Metal-Insulator-Metal)構造で構成されている。第1保持容量部C1は、第1電極14aが第1トランジスタTr1のソース端子ならびに第2トランジスタTr2のドレイン端子に接続され、第2電極14bが基準電位共通端子Comに接続されている。基準電位共通端子Comには、予め設定された基準電圧Vcom、例えば接地電位が与えられる。第1保持容量部C1は、第1トランジスタTr1を介して選択的に入力された画素信号を保持する。

## 【0019】

第2保持容量部C2は、金属からなる第1電極15aならびに第2電極15bで誘電体(図示せず)を挟んだ、所謂MIM(Metal-Insulator-Metal)構

50

造で構成されている。第2保持容量部C2は、第1電極15aが第2トランジスタTr2のソース端子に接続され、第2電極15bが基準電位共通端子Comに接続されている。第2保持容量部C2は、第2トランジスタTr2を介して第1保持容量部C1から転送された画素信号を保持する。

【0020】

液晶LCは、光反射性を有する画素電極16aと、画素電極16aに離間して対向配置された共通電極16bとの間に充填封止されて構成されている。画素電極16aは、第2トランジスタTr2のソース端子ならびに第2保持容量部C2の第1電極15aに接続されている。共通電極16bは、共通電極端子CEに接続されている。共通電極端子CEには、画素電極16aに与えられる画素信号の電圧に応じて予め設定された共通電極電圧Vceが与えられる。

【0021】

液晶LCは画素電極16aに与えられる画素信号の電圧と、共通電極16bに与えられる共通電極電圧Vceとの電位差に応じて駆動される。

【0022】

水平走査回路12には、列データ線D(D1～Dm)が接続されている。水平走査回路12は、水平同期信号(Hst)、水平走査用のクロック信号(Hck)ならびに画素信号を入力する。水平走査回路12は、水平同期信号、水平走査用のクロック信号に基づいて、画素信号を列データ線D1～Dmに順次、1水平走査期間単位で出力する。

【0023】

垂直走査回路13には、行走査線G1～Gnが接続されている。垂直走査回路13は、垂直同期信号(Vst)、垂直走査用のクロック信号(Vck)を入力する。垂直走査回路13は、垂直同期信号、垂直走査用のクロック信号に基づいて、例えば行走査線G1からGnに順次行選択信号を1水平走査期間単位で供給する。

【0024】

上述したように、画素回路11は、画素電極16aと共に電極16bに挟まれた液晶LCを備えた画素部と、第1トランジスタTr1、第2トランジスタTr2、第1保持容量部C1、ならびに第2保持容量部を備えた駆動部とを備えている。

【0025】

次に、上記構成の液晶表示装置の動作について説明する。

【0026】

水平走査回路12から各列データ線D1～Dmに対応した各画素信号が、1水平走査期間の間、各列データ線D1～Dmに出力される。一方、第1トランジスタTr1を導通状態にする選択信号が垂直走査回路13から行走査線G、例えば行走査線G1に1水平走査期間の間出力される。これにより、ゲート端子が行走査線G1に接続されたm個の第1トランジスタTr1は導通状態となる。

【0027】

各列データ線D1～Dmに出力された各画素信号は、各列データ線D1～Dmに対応して接続された第1トランジスタTr1を介して第1保持容量部C1に与えられて書き込まれる。この後、第1トランジスタTr1を非導通状態にする選択信号が垂直走査回路13から行走査線G1に出力される。これにより、ゲート端子が行走査線G1に接続されたm個の第1トランジスタTr1は非導通状態となる。

【0028】

第1保持容量部C1に書き込まれた画素信号は、次の垂直走査期間に新たな画素信号が与えられるまでの非選択期間中、第1保持容量部C1に保持される。なお、すべての画素回路11の第1保持容量部C1に画素信号が書き込まれて保持される動作が終了するまでは、第2トランジスタTr2は非導通状態にある。

【0029】

このような画素信号の書き込み動作は、すべての行走査線Gに対して実行され、1フレーム分の画素信号がm×n個のすべての画素回路11の第1保持容量部C1に順次書き込

まれて保持される。

【0030】

1フレーム分の画素信号の書き込み動作が終了すると、第2トランジスタTr2を導通状態とするトリガ信号がすべての画素回路11の第2トランジスタTr2のゲート端子に共通に与えられる。これにより、すべての画素回路11において、第1保持容量部C1に保持された画素信号は、第2トランジスタTr2を介して第2保持容量部C2に一斉に転送されるとともに画素信号に対応した電圧として画素電極16aに印加される。第2保持容量部C2に転送された画素信号は、第2保持容量部C2に保持される。

【0031】

すべての画素回路11の各画素電極16aに画素信号に対応した電圧が印加された後、第2トランジスタTr2を非導通状態とするトリガ信号が第2トランジスタTr2のゲート端子に与えられ、第2トランジスタTr2は非導通状態となる。この後、上述したようにして、次フレームの画素信号の書き込み動作が開始される。

【0032】

次フレームの画素信号の書き込み動作が行われている間、第2トランジスタTr2は非導通状態を維持している。これにより、第2保持容量部C2に転送された画素信号は、第2保持容量部C2に保持されると共に、画素信号に対応した電圧として画素電極16aに印加された状態を保持する。

【0033】

第2保持容量部C2に保持されている画素信号は、信号電圧が画素電極16aに印加される。画素電極16aに印加された画素信号の電圧と、共通電極16bに印加された共通電極電圧Vceとの電位差に応じて液晶LCが駆動され、各画素回路11に書き込まれた画素信号に応じた表示が行われる。

【0034】

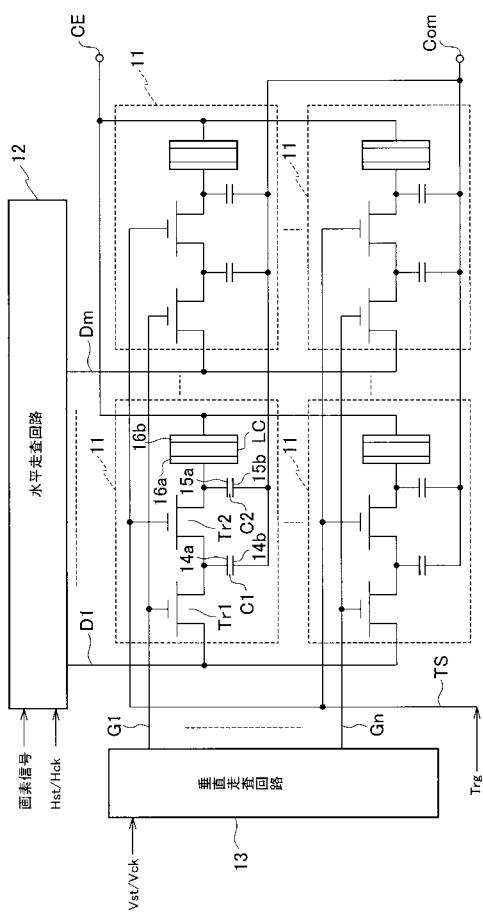

反射型液晶表示装置に好適な液晶表示モードとしては、電界効果複屈折モードがある。電界効果複屈折モードでは、液晶の誘電異方性と初期配向によってノーマリーブラック型あるいはノーマリーホワイト型の特性を得ることができる。本実施形態では、図2を参照して、ノーマリーブラック型について説明する。

【0035】

図2は本実施形態で用いられる液晶LCの液晶駆動電圧-透過率特性の一例を示す図である。図2において、横軸は液晶LCの画素電極16aに印加される電圧であり、縦軸は表示画像のモノクロ(白黒)の表示色を示しており、電圧V1は、表示画像の黒色(出力光強度Pb)に対応し、電圧V2は表示画像の白色(出力光強度Pw)に対応している。

【0036】

液晶表示装置において、通常液晶は表示画像の焼き付きや液晶材料の劣化を防止する観点から、正極性の電圧印加と負極性の電圧印加とを交互に設定した交流電圧で駆動することが好ましい。ここで、正極性とは、画素電極16aに印加する電圧が共通電極電圧Vceよりも高い場合であり、負極性とは、画素電極16aに印加する電圧が共通電極電圧Vceよりも低い場合である。

【0037】

画素信号を1つのトランジスタを介して1つの保持容量部に取り込んで保持するような構成の画素回路では、すべての画素回路の液晶に同時に画素信号を供給することができない。これにより、液晶LCの共通電極16bに印加する共通電極電圧Vceを変化させず、黒を表示するときには共通電極電圧Vce+電圧V1となる電圧と、共通電極電圧Vce-電圧V1となる電圧とが交互に画素電極16aに印加される。一方、白を表示するときには共通電極電圧Vce+電圧V2となる電圧と、共通電極電圧Vce-電圧V2となる電圧とが交互に画素電極16aに印加される。ここで、電圧V1, V2は図2に示す電圧である。このような駆動態様では、液晶LCの画素電極16aに印加される電圧の振幅は、最大で $2 \times V2$ となる。

10

20

30

40

50

## 【0038】

これに対して、本実施形態では、図3に示すようにして液晶LCに電圧を印加して駆動している。図3は本実施形態で用いられる液晶LCに印加される電圧と、液晶LCの駆動様式を模式的に示したものである。

## 【0039】

図3に示すように、正極性で黒色表示する際に画素電極16aに印加する電圧Vaと、負極性で白色表示する際に画素電極16aに印加する電圧Vaとが略等しいレベルとなる。また、正極性で白色表示する際に画素電極16aに印加する電圧Vbと、負極性で黒色表示する際に画素電極16aに印加する電圧Vbとが略等しいレベルとなる。このように、画素電極16aには、正負各極性の電圧範囲およびレベルを振幅方向でオーバラップさせた形態の電圧を供給する。

10

## 【0040】

正極性において黒色表示する際に、共通電極16bには、画素電極16aに印加される電圧Vaに対して電圧V1だけ低い電圧の共通電極電圧Vceが印加される。また、負極性において黒色表示する際に、共通電極16bには、画素電極16aに印加される電圧Vbに対して電圧V1だけ高い電圧の共通電極電圧Vceが印加される。すなわち、共通電極電圧Vceは、正極性では電圧Va - 電圧V1となり、負極性では電圧Vb + 電圧V1となる。

20

## 【0041】

一方、正極性において白色表示する際に、共通電極16bには、画素電極16aに印加される電圧Vbに対して電圧V2だけ低い電圧の共通電極電圧Vceが印加される。また、負極性において白色表示する際に、共通電極16bには、画素電極16aに印加される電圧Vaに対して電圧V2だけ低い電圧の共通電極電圧Vceが印加される。すなわち、共通電極電圧Vceは、正極性では電圧Vb - 電圧V2となり、負極性では電圧Va + 電圧V2となる。

20

## 【0042】

このように、正負の極性において黒色表示もしくは白色表示をする場合には、図3に示すように、画素電極16aに印加される電圧の振幅は電圧Va - 電圧Vb、すなわち電圧V2 - 電圧V1となる。これにより、画素電極16aに印加すべき印加電圧は、共通電極電圧Vceを変化させない場合に比べて、小振幅にすることが可能となる。この結果、第1トランジスタTr1、第2トランジスタTr2や第1保持容量部C1、第2保持容量部C2の必要耐圧を低減させることができることが可能となり、素子の高密度化を実現することができる。

30

## 【0043】

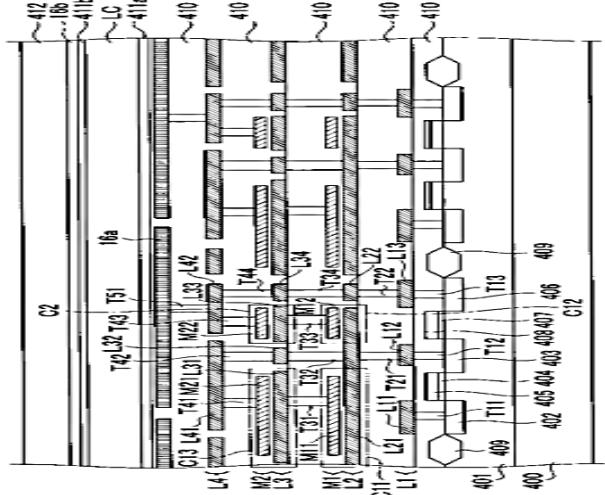

図4は本実施形態の液晶表示装置における画素回路の模式的な断面構造を示す図である。図4には紙面の横方向に2つ画素回路の断面構造が図示されているが、すべての画素回路は同様な構造であるので、図4の左側に図示された画素回路を代表して、画素回路の構造を説明する。

## 【0044】

図4において、例えばシリコン基板からなる半導体基板400上には、ウェル領域401が形成されている。ウェル領域401には、図1に示す第1トランジスタTr1、第2トランジスタTr2が形成されている。第1トランジスタTr1ならびに第2トランジスタTr2をNチャネルの電界効果トランジスタで構成した場合には、ウェル領域401は、P型のウェル領域となる。

40

## 【0045】

ウェル領域401には、不純物が拡散された拡散層402、403が所定の距離離間して形成されている。第1トランジスタTr1をNチャネルの電界効果トランジスタで構成した場合には、拡散層402、403には例えばボロンなどのN型の不純物が注入されて拡散される。

## 【0046】

50

拡散層402と拡散層403との間のウェル領域401上には、ゲート酸化膜となるシリコン酸化膜404を介してポリシリコン405が形成されている。これにより、第1トランジスタTr1は、拡散層402をドレイン領域、拡散層403をソース領域、ポリシリコン405をゲート電極として形成されている。

## 【0047】

また、ウェル領域401には、不純物が拡散された拡散層406が拡散層403と所定の距離離間して形成されている。第2トランジスタTr2をNチャネルの電界効果トランジスタで構成した場合には、拡散層406には例えばボロンなどのN型の不純物が注入されて拡散される。

## 【0048】

拡散層403と拡散層406との間のウェル領域401上には、ゲート酸化膜となるシリコン酸化膜407を介してポリシリコン408が形成されている。これにより、第2トランジスタTr2は、拡散層403をドレイン領域、拡散層406をソース領域、ポリシリコン408をゲート電極として形成されている。

## 【0049】

第1トランジスタTr1のソース領域ならびに第2トランジスタTr2のドレイン領域となる拡散層403は双方のトランジスタで共通化されている。これにより、第1トランジスタTr1のソースと第2トランジスタTr2のドレインが電気的に接続されている。

## 【0050】

拡散層402ならびに拡散層406に隣接して、第1トランジスタTr1ならびに第2トランジスタTr2の周囲を取り囲むように素子分離領域409が形成されている。すなわち、素子分離領域409の内側が第1トランジスタTr1ならびに第2トランジスタTr2の形成領域となる。この素子分離領域409により第1トランジスタTr1と第2トランジスタTr2は、隣接する他の画素回路の第1トランジスタTr1と第2トランジスタTr2と電気的に分離されている。

## 【0051】

第1トランジスタTr1ならびに第2トランジスタTr2が形成された領域を上方に略平行移動した位置で、かつ第1トランジスタTr1ならびに第2トランジスタTr2が形成された形成面積と略同等の面積内に、多層配線構造が構築されている。この多層配線構造により、1つの画素回路11の第1保持容量部C1ならびに第2保持容量部C2が形成されている。すなわち、1つの画素回路の第1保持容量部C1ならびに第2保持容量部C2は、双方のトランジスタが形成された領域の上方に、双方のトランジスタが形成された形成面積と略同等の面積内に形成されている。

## 【0052】

この多層配線構造では、半導体基板400から上方に向かって順に第1配線層L1、第2配線層L2、第3配線層L3、第4配線層L4が形成されている。これらの第1配線層L1～第4配線層L4は、例えはアルミニウムや銅などの金属で構成されている。第1配線層L1～第4配線層L4のそれぞれの配線層間は、例えはシリコン酸化膜などの層間絶縁膜410により互いに絶縁されている。

## 【0053】

第1配線層L1は、第1配線部L11、第2配線部L12、第3配線部L13を備えている。第1配線部L11、第2配線部L12ならびに第3配線部L13は、それぞれ電気的に分離されている。

## 【0054】

第1配線層L1の第1配線部L11は、スルーホールT11を介して第1トランジスタTr1のドレイン領域となる拡散層402に接合されている。第1配線層L1の第2配線部L12は、スルーホールT12を介して第1トランジスタTr1のソース領域ならびに第2トランジスタTr2のドレイン領域となる拡散層403に接合されている。第1配線層L1の第3配線部L13は、スルーホールT13を介して第2トランジスタTr2のソース領域となる拡散層406に接合されている。

10

20

30

40

50

## 【0055】

図4に示す構造では、第1保持容量部C1は、3つの保持容量部C11，C12，C13に分割されて構成されている。すなわち、3つの保持容量部C11，C12，C13は、電気的に並列接続されて第1保持容量部C1を構成している。

## 【0056】

第2配線層L2は、第1配線部L21、第2配線部L22を備えている。第1配線部L21と第2配線部L22は、互いに電気的に分離されている。

## 【0057】

第2配線層L2の第1配線部L21は、保持容量部C11，C12の一方の電極を構成している。第2配線層L2の第1配線部L21は、スルーホールT21を介して第1配線層L1の第2配線部L12に接合されている。第2配線層L2の第2配線部L22は、スルーホールT22を介して第1配線層L1の第3配線部L13に接合されている。

10

## 【0058】

第2配線層L2と第3配線層L3との間には、第1金属層M1が形成されている。第1金属層M1は、第2配線層L2の第1配線部L21と所定の間隔離間して対向して形成されている。第1金属層M1と第2配線層L2の第1配線部L21との間には、層間絶縁膜410が形成されている。

20

## 【0059】

第1金属層M1は、例えば窒化チタン(TiN)やチタン(Ti)などの金属で構成されている。第1金属層M1は、第1電極部M11と第2電極部M12とを形成している。第1電極部M11と第2電極部M12とは、互いに電気的に分離されている。

20

## 【0060】

第1電極部M11は、保持容量部C11の他方の電極を構成している。したがって、保持容量部C11は、誘電体となる層間絶縁膜410が第2配線層L2の第1配線部L21と第1金属層M1の第1電極部M11とで挟み込まれたMIM構造で形成されている。

30

## 【0061】

第2電極部M12は、保持容量部C12の他方の電極を構成している。したがって、保持容量部C12は、誘電体となる層間絶縁膜410が第2配線層L2の第1配線部L21と第1金属層M1の第2電極部M12とで挟み込まれたMIM構造で形成されている。

## 【0062】

第1金属層M1の上層には、第3配線層L3が形成されている。第3配線層L3は、第1配線部L31、第2配線部L32、第3配線部L33、第4配線部L34を備えている。第1配線部L31、第2配線部L32、第3配線部L33、第4配線部L34は、互いに電気的に分離されている。

40

## 【0063】

第3配線層L3の第1配線部L31は、先の図1に示す基準電位共通端子Comに接続され、基準電位Vcomとして例えば接地電位が与えられる。第3配線層L3の第1配線部L31は、スルーホールT31を介して第1金属層M1の第1電極部M11に接合されている。第3配線層L3の第2配線部L32は、スルーホールT32を介して第2配線層L2の第1配線部L21に接合されている。

## 【0064】

第3配線層L3の第3配線部L33は、先の図1に示す基準電位共通端子Comに接続され、基準電位Vcomとして例えば接地電位が与えられる。第3配線層L3の第3配線部L33は、スルーホールT33を介して第1金属層M1の第2電極部M12に接合されている。第3配線層L3の第4配線部L34は、スルーホールT34を介して第2配線層L2の第2配線部L22に接合されている。

40

## 【0065】

第3配線層L3と第4配線層L4との間には、第2金属層M2が形成されている。第2金属層M2は、例えば窒化チタン(TiN)やチタン(Ti)などの金属で構成されている。第2金属層M2は、第1電極部M21と第2電極部M22とを形成している。第1電

50

極部M21と第2電極部M22とは、互いに電気的に分離されている。

【0066】

第2金属層M2の第1電極部M21は、第3配線層L3の第1配線部L31と所定の間隔離間して対向して形成されている。第2金属層M2の第1電極部M21と第3配線層L3の第1配線部L31との間には、層間絶縁膜410が形成されている。

【0067】

第2金属層M2の第1電極部M21は、保持容量部C13の他方の電極を構成している。したがって、保持容量部C13は、誘電体となる層間絶縁膜410が第3配線層L3の第1配線部L31と第1電極部M21とで挟み込まれたMIM構造で構成されている。

【0068】

第2金属層M2の第2電極部M22は、第3配線層L3の第3配線部L33と所定の間隔離間して対向して形成されている。第2金属層M2の第2電極部M22と第3配線層L3の第3配線部L33との間には、層間絶縁膜410が形成されている。

【0069】

第2金属層M2の第2電極部M22は、第2保持容量部C2の他方の電極を構成している。したがって、第2保持容量部C2は、誘電体となる層間絶縁膜410が第3配線層L3の第3配線部L33と第2金属層M2の第2電極部M22とで挟み込まれたMIM構造で構成されている。

【0070】

第2金属層M2の上層には、第4配線層L4が形成されている。第4配線層L4は、第1配線部L41、第2配線部L42を備えている。第1配線部L41、第2配線部L42は、互いに電気的に分離されている。

【0071】

第4配線層L4の第1配線部L41は、スルーホールT41を介して第2金属層M2の第1電極部M21に接合されている。第4配線層L4の第1配線部L41は、スルーホールT42を介して第3配線層L3の第2配線部L32に接合されている。第4配線層L4の第2配線部L42は、スルーホールT43を介して第2金属層M2の第2電極部M22に接合されている。第4配線層L4の第2配線部L42は、スルーホールT44を介して第3配線層L3の第4配線部L34に接合されている。

【0072】

上記積層構造においては、保持容量部C11ならびに保持容量部C12の一方の電極を構成する第2配線層L2の第1配線部L21と、保持容量部C13の一方の電極を構成する第2金属層M2の第1電極部M21とが電気的に接続されている。また、保持容量部C11の他方の電極となる第1金属層M1の第1電極部M11と、保持容量部C13の他方の電極となる第3配線層L3の第1配線部L31とは電気的に接続され、接地電位が与えられている。さらに、保持容量部C12の他方の電極となる第1金属層M1の第2電極部M12は、第3配線層L3の第3配線部L33と電気的に接続され、接地電位が与えられている。

【0073】

これにより、保持容量部C11、保持容量部C12ならびに保持容量部C13は、並列接続されている。接地電位が与えられていない並列接続された、保持容量部C11、保持容量部C12ならびに保持容量部C13の電極は、第1トランジスタTr1のソース領域ならびに第2トランジスタTr2のドレイン領域となる拡散層403に電気的に接続されている。したがって、保持容量部C11、保持容量部C12ならびに保持容量部C13の並列接続された電極は、第1保持容量部C1の第1電極14aを構成する。

【0074】

保持容量部C11、保持容量部C12ならびに保持容量部C13は、それぞれの他方の電極に接地電位が共通に与えられている。すなわち、保持容量部C11、保持容量部C12ならびに保持容量部C13の接地電位が与えられたそれぞれの電極は、第1保持容量部C1の第2電極14bを構成する。

10

20

30

40

50

## 【0075】

上記積層構造において、第2保持容量部C2の一方の電極となる第2金属層M2の第2電極部M22は、第2トランジスタTr2のソース領域となる拡散層406に電気的に接続されている。第2保持容量部C2の他方の電極となる第3配線層L3の第3配線部L33は、接地電位が与えられている。これにより、第2保持容量部C2の一方の電極となる第2金属層M2の第2電極部M22は、図1に示す第2保持容量部C2の第1電極15aを構成する。第2保持容量部C2の他方の電極となる第3配線層L3の第3配線部L33は、図1に示す第2保持容量部C2の第2電極15bを構成する。

## 【0076】

第1保持容量部C1を構成する保持容量部C11、保持容量部C12ならびに保持容量部C13と第2保持容量部C2とは、それぞれ双方の電極で挟み込まれた誘電体ならびに双方の電極間の距離は同等に形成されている。したがって、第1保持容量部C1を構成する保持容量部C11、保持容量部C12ならびに保持容量部C13と第2保持容量部C2とのそれぞれの容量値は、それぞれの保持容量部の電極の面積で決まる。

10

## 【0077】

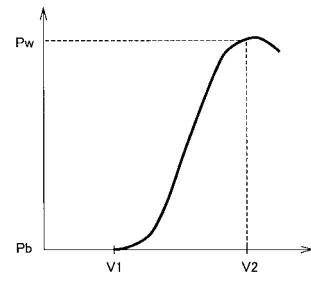

図5(a)は第1金属層M1の平面構造を示す図であり、同図(b)は第2金属層M2の平面構造を示す図である。

## 【0078】

図5(b)に示すように、保持容量部C13の一方の電極となる第2金属層M2の第2電極部M21の面積は、第2保持容量部C2の一方の電極となる第2金属層M2の第2電極部M22の面積に比べて大きく形成されている。これは、詳しくは後述するが第1保持容量部C1の容量値を第2保持容量部C2の容量値よりも大きくするためである。

20

## 【0079】

図5(a)に示すように、保持容量部C11の一方の電極となる第1金属層M1の第1電極部M11と保持容量部C12の一方の電極となる第2電極部M12とは、電気的に分離して形成されている。第1金属層M1の第1電極部M11の面積は、図5(b)に示す第2金属層M2の第1電極部M21の面積と同等に形成されている。第1金属層M1の第2電極部M12の面積は、図5(b)に示す第2金属層M2の第2電極部M22の面積と同等に形成されている。

30

## 【0080】

これは、第1金属層M1と第2金属層M2とを同一のマスクパターンを使用して形成するためである。このようにすることで、第1金属層M1と第2金属層M2とを異なるマスクパターンを用いて形成する場合に比べて、マスクパターンを削減して製造プロセスを容易化することができる。また、第1金属層M1もしくは第2金属層M2に接合するスルーホールを形成する際の面積を少なくすることが可能となる。

40

## 【0081】

なお、第1金属層M1の第1電極部M11と第2電極部M12とを分離せずに一体化し、保持容量部C11と保持容量部C12とを1つの保持容量部として形成することもできる。この場合には、保持容量部を分割する場合に比べて第1保持容量部C1の容量値を大きくすることが可能となる。

40

## 【0082】

図4に戻って、第4配線層L4の上層には、層間絶縁膜410を介して画素電極16aが形成されている。画素電極16aは、スルーホールT51を介して第4配線層L4の第2配線部L42に接合されている。これにより、画素電極16aは、第1配線層L1～第4配線層L4ならびにそれらを接合するスルーホールを介して、第2トランジスタTr2のソース領域を形成する拡散層406に電気的に接続されている。

## 【0083】

画素電極16aの上層には、液晶LCの初期分子配列を所定の方向に配向する配向層411a, 411bに挟まれて液晶LCが形成されている。

## 【0084】

50

液晶 L C の上層には、共通電極 1 6 b が形成されている。これにより、液晶 L C は、画素電極 1 6 a と共に電極 1 6 b との間に充填封止されて形成されている。

【 0 0 8 5 】

共通電極 1 6 b の上層には、透光性基板 4 1 2 が形成されている。これにより、画素回路 1 1 は、半導体基板 4 0 0 と透光性基板 4 1 2 との間に挟まれて形成されている。

【 0 0 8 6 】

透光性基板 4 1 2 から入射した入射光は、液晶 L C を通過して画素電極 1 6 a に至り、画素電極 1 6 a に到達した入射光は画素電極 1 6 a で反射して再度液晶 L C を通過して透光性基板 4 1 2 から出射する。この過程において、入射光は画素電極 1 6 a に印加される画素信号の電圧に応じて液晶 L C で変調され、画素信号に応じた表示がなされる。

10

【 0 0 8 7 】

図 6 は画素回路 1 1 の第 1 保持容量部 C 1 ならびに第 2 保持容量部 C 2 の容量値と、画素電極 1 6 a への画素信号の転送との関係を説明するための図である。図 6 において、図 1 と同一構成部分には同一符号を付し、その説明は省略する。図 6 を参照して、本発明による液晶表示装置の画素回路 1 1 を構成する第 1 保持容量部 C 1 、第 2 保持容量部 C 2 の容量値について説明する。

【 0 0 8 8 】

ここで、第 1 保持容量部 C 1 に保持された画素信号の電圧が第 2 保持容量部 C 2 に転送される動作を考える。先ず、第 1 パワートランジスタ T r 1 ならびに第 2 パワートランジスタ T r 2 が非導通状態において、第 1 保持容量部 C 1 には画素信号の電圧として電圧 V a が保持されているものとする。第 2 保持容量部 C 2 には、前フレームに画素電極 1 6 a に印加された電圧 V p ( n - 1 ) が保持されているものとする。すなわち、第 1 保持容量部 C 1 の一方の電極が第 1 パワートランジスタ T r 1 と第 2 パワートランジスタ T r 2 とに接続された接続点 a は、電圧 V a となる。また、第 2 保持容量部 C 2 の一方の電極が第 2 パワートランジスタ T r 2 と画素電極 1 6 a に接続された接続点 b は、電圧 V p ( n - 1 ) となる。

20

【 0 0 8 9 】

このような状態において、トリガ信号 ( T r g ) により第 2 パワートランジスタ T r 2 が導通状態になると、第 2 パワートランジスタ T r 2 を介して接続点 a と接続点 b とは電気的に接続される。これにより、接続点 a の電圧と接続点 b の電圧とが同電圧となる。このときの接続点 b の電圧を V p ( n ) とすると、電圧 V p ( n ) は次式 ( 1 ) で表される。

30

【 0 0 9 0 】

$$V p ( n ) = K \times V s + ( 1 - K ) \times V p ( n - 1 ) \quad \dots ( 1 )$$

上式 ( 1 ) において、第 1 保持容量部 C 1 の容量値を C 1 c とし、第 2 保持容量部 C 2 の容量値を C 2 c とすると、 $K = C 1 c / ( C 1 c + C 2 c )$  となる。

【 0 0 9 1 】

ここで、第 1 保持容量部 C 1 の容量値 C 1 c と第 2 保持容量部 C 2 の容量値 C 2 c とに、 $C 1 c > > C 2 c$  の関係が成り立つ場合には、式 ( 1 ) において、 $K \rightarrow 1$  となり  $V p ( n ) \rightarrow V s$  となる。すなわち、電圧 V p ( n - 1 ) の値にかかわらず、電圧 V p ( n ) は、電圧 V s とほぼ等しくなる。

40

【 0 0 9 2 】

したがって、画素信号を接続点 a から接続点 b に効率よく転送するには、第 1 保持容量部 C 1 の容量値 C 1 c と第 2 保持容量部 C 2 の容量値 C 2 c との比率  $C 1 c / C 2 c$  をできるだけ大きく設定することが必要となる。例えば、少なくとも  $C 1 c / C 2 c = 5$  程度が必要となり、好ましくは  $C 1 c / C 2 c = 10$  程度に設定することが望まれる。

【 0 0 9 3 】

これにより、画素回路 1 1 に書き込まれて第 1 保持容量部 C 1 に保持された画素信号は、第 2 保持容量部 C 2 に効率よく転送することができる。この結果、書き込まれた画素信号の電圧と概ね等しい電圧で液晶 L C を十分に駆動することが可能となり、良好な液晶表示を実現することができる。

【 0 0 9 4 】

50

第1保持容量部C1の容量値C1cと第2保持容量部C2の容量値C2cとの比率C1c/C2cをできるだけ大きく設定するには、容量値C1cを大きくするか、もしくは容量値C2cを小さくすることが考えられる。

【0095】

しかしながら、容量値C2cを小さくすると、第2保持容量部C2に画素信号を保持すといった機能が低下するおそれがある。したがって、このような不具合を招かないために、容量値C1cを大きくすることが望まれる。

【0096】

この実施形態においては、図4、図5に示すように、第1保持容量部C1は、第2配線層L2と第1金属層M1とからなる第1の容量形成層と、第3配線層L3と第2金属層M2とからなる第2容量形成層に形成されている。第2保持容量部C2は、第3配線層L3ならびに第2金属層M2とからなる第2の容量形成層に形成されている。すなわち、第1保持容量部C1ならびに第2保持容量部C2は、2つの異なる容量形成層によって形成されている。

10

【0097】

これにより、第1保持容量部C1ならびに第2保持容量部C2を1つの容量形成層に形成する場合に比べて、双方の保持容量部の電極の面積を決める際の自由度を高めることができる。すなわち、第1保持容量部C1の容量値C1cならびに第2保持容量部C2の容量値C2cを決める際の自由度を高めることができる。

20

【0098】

また、第1保持容量部C1は、上記第1の容量形成層ならびに第2の容量形成層の2つの異なる容量形成層に形成されているのに対して、第2保持容量部C2は第2の容量形成層にのみ形成されている。さらに、第2の容量形成層に形成された第1保持容量部C1の電極は第2保持容量部C2の電極よりも大きく形成されている。すなわち、第2の容量形成層に形成された第1保持容量部C1の一部容量を担う保持容量部C13の容量値は、第2保持容量部C2の容量値よりも大きく設定されている。

20

【0099】

これにより、上述したように、この実施形態で採用した図4に示す構造では、第1保持容量部C1の容量値C1cと第2保持容量部C2の容量値C2cとの比率C1c/C2cを大きく設定することが可能となる。

30

【0100】

以上説明したように、この実施形態では、第1トランジスタTr1ならびに第2トランジスタTr2が形成された半導体基板400の上層に、MIM構造で第1保持容量部C1ならびに第2保持容量部C2を形成している。これにより、第1トランジスタTr1ならびに第2トランジスタTr2が形成された形成領域の面積と略同等の面積に第1保持容量部C1ならびに第2保持容量部C2を形成することが可能となる。

30

【0101】

この結果、保持容量部を半導体基板に形成する従来の構成に比べて、画素回路を小型化することができる。例えば、従来の1画素回路の画素ピッチは、4.0μm程度であったのに対して、この実施形態で採用した構成では、3.5μm程度にまで縮小することができる。したがって、多数の画素回路を有する液晶表示装置を小型化することができる。

40

【0102】

第1保持容量部C1と第2保持容量部C2とは、複数の層に形成されている。これにより、第1保持容量部C1と第2保持容量部C2とを形成する際の設計の自由度を、単一の層に形成する場合に比べて高めることができる。この結果、第1保持容量部C1の容量値を第2保持容量部C2の容量値よりも大きくすることができます。したがって、上述したように液晶を十分に駆動できる容量値を確保しつつ、画素回路を小型化することができる。

【0103】

第1保持容量部C1ならびに第2保持容量部C2の基準電位として接地電位が与えられ

50

る電極は、同一の第3配線層L3により共通に形成されている。これにより、第1保持容量部C1ならびに第2保持容量部C2の基準電位として接地電位が与えられる電極を、单一の配線層で形成することが可能となる。この結果、第1保持容量部C1ならびに第2保持容量部C2を形成する際に用いられる配線層を削減することが可能となり、製造プロセスの簡略化、ならびに装置の小型化に貢献することができる。

#### 【0104】

なお、上述した図4及びその説明では、説明をわかりやすくするために、第2配線層L2と第1金属層M1との間の層間絶縁膜も、第1金属層M1と第3配線層L3との間の層間絶縁膜も、層間絶縁膜410として一体に表し、その具体的な説明を省略している。実際には、第2配線層L2を形成した後に第1の層間絶縁膜を形成し、この第1の層間絶縁膜上に第1金属層M1を形成し、さらにこの第1金属層M1上に第2の層間絶縁膜を形成する。即ち、第2配線層L2と第3配線層L3との間の層間絶縁膜410は、これら第1及び第2の層間絶縁膜により構成されている。

10

#### 【0105】

また、第3配線層L3と第4配線層L4との間の層間絶縁膜410についても、上記の第2配線層L2と第3配線層L3との間の層間絶縁膜410と同様に2層の層間絶縁膜により構成されている。

#### 【符号の説明】

#### 【0106】

20

- 11...画素回路

- 16a...画素電極

- 16b...共通電極

- 400...半導体基板

- 410...層間絶縁膜

- 412...透光性基板

- C1...第1保持容量部

- C2...第2保持容量部

- C11, C12, C13...保持容量部

- L1...第1配線層

- L2...第2配線層

- L3...第3配線層

- L4...第4配線層

- LC...液晶

- M1...第1金属層

- M2...第2金属層

30

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

---

フロントページの続き

F ターム(参考) 5C080 AA10 BB05 DD07 FF11 FF12 JJ02 JJ03 JJ04 JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2015060025A</a>                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2015-03-30 |

| 申请号            | JP2013192690                                                                                                                                                                                                                                                                                                        | 申请日     | 2013-09-18 |

| [标]申请(专利权)人(译) | JVC 建伍株式会社                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | JVC建伍公司                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 古屋正人                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 古屋 正人                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/1368 G09G3/36 G09G3/20                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G02F1/1368 G09G3/36 G09G3/20.624.B G09G3/20.624.C G09G3/20.680.F                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H192/AA24 2H192/BC31 2H192/BC72 2H192/CB02 2H192/CB13 2H192/CB22 2H192/CB33 2H192/CC73 2H192/DA23 2H192/DA52 2H192/DA65 2H192/DA67 2H192/GD61 5C006/AC25 5C006/AC26 5C006/BB16 5C006/BB28 5C006/BC06 5C080/AA10 5C080/BB05 5C080/DD07 5C080/FF11 5C080/FF12 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 |         |            |

| 代理人(译)         | 三好秀<br>高桥俊                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                           |         |            |

## 摘要(译)

要解决的问题：提供一种液晶显示装置，其确保传输能够令人满意地驱动液晶的像素信号的容量，并且允许减小尺寸。解决方案：第一保持电容部分C1保持通过第一选择性地输入的像素信号。晶体管Tr1包括保持电容部分C11，保持电容部分C12和保持电容部分C13，并且形成在第一电容形成层和第二电容形成层上，第一电容形成层和第二电容形成层位于其上具有第一晶体管的半导体衬底400上方形成Tr1和第二晶体管Tr2。第二保持电容部分C2保持经由第二晶体管Tr2选择性地转移的像素信号，并且形成在第二电容形成层上，该第二电容形成层位于其上形成有第一晶体管Tr1和第二晶体管Tr2的半导体基板400上方。