(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-126080

(P2016-126080A)

(43) 公開日 平成28年7月11日(2016.7.11)

(51) Int.Cl.

G02F 1/1368 (2006.01)

F 1

G02F 1/1368

テーマコード(参考)

2H192

審査請求 未請求 請求項の数 4 O L (全 13 頁)

(21) 出願番号

特願2014-265270 (P2014-265270)

(22) 出願日

平成26年12月26日 (2014.12.26)

(71) 出願人 000103747

京セラディスプレイ株式会社

滋賀県野洲市市三宅 641-1

(72) 発明者 市村 照彦

滋賀県野洲市市三宅 641-1 京セラディスプレイ株式会社内

F ターム(参考) 2H192 AA24 BC31 CB05 CB45 CC17

CC24 CC33 CC42 CC62 EA04

EA15 EA22 EA43 EA67 GD61

JB02

(54) 【発明の名称】 液晶表示装置

(57) 【要約】 (修正有)

【課題】画素部の開口率を高く維持した状態で TFT 素子のチャネル部及びその周囲に対する遮光性を向上させることができる LCD を提供する。

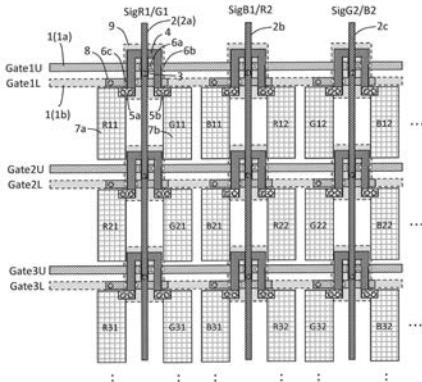

【解決手段】LCD は、1 本の画像信号線 2 に対してゲート信号線 1 と画像信号線 2 の交差部の左側及び右側に、1 本の画像信号線 2 に電気的に接続された状態で形成されているチャネル部 6a ~ 6c を有する TFT 素子及び画素電極 7a, 7b と、を有しており、ゲート信号線 1 は、行方向に並んだ 1 群の画素電極 7a, 7b に対応して第 1 及び第 2 のゲート信号線 1a, 1b の 2 本が形成されている LCD であって、第 1 及び第 2 のゲート信号線 1a, 1b は、基板の上面に垂直な方向において互いに異なる位置にあるとともに基板に近い方が遠い方よりも幅広に形成されている。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

基板の上面の第1の方向に形成された複数本のゲート信号線と、前記第1の方向に交差する第2の方向に前記ゲート信号線と交差させて前記ゲート信号線の上方に形成された複数本の画像信号線と、1本の前記画像信号線に対して前記ゲート信号線と前記画像信号線の交差部の左側及び右側に、それぞれ1本の前記画像信号線に電気的に接続された状態で形成されているチャネル部を有する薄膜トランジスタ素子及び画素電極と、を有しております。前記ゲート信号線は、前記第1の方向に並んだ1群の前記画素電極に対応して第1及び第2のゲート信号線の2本が平面視で近接して形成されており、前記第1のゲート信号線が前記右側の薄膜トランジスタ素子に対して2つのチャネル部を形成するとともに前記右側の画素電極に画像信号を入力するように構成されており、前記第2のゲート信号線が前記左側の薄膜トランジスタ素子に対して1つのチャネル部を形成するとともに前記左側の画素電極に画像信号を入力するように構成されている液晶表示装置であって、前記第1及び第2のゲート信号線は、前記基板の上面に垂直な方向において前記基板の上面の側に互いに異なる位置にあるとともに前記基板に近い方が遠い方よりも幅広に形成されている液晶表示装置。

**【請求項 2】**

前記第1及び第2のゲート信号線のうち前記基板に近い方は、平面視ですべての前記チャネル部と重なる延出部を有している請求項1に記載の液晶表示装置。

**【請求項 3】**

前記第1及び第2のゲート信号線は、平面視で少なくとも部分的に重なっている請求項1または請求項2に記載の液晶表示装置。

**【請求項 4】**

前記ゲート信号線は、Al, Mo, Cr, Ti, Ta, W及びPdのうちの少なくとも一つを含む金属膜から成る請求項1乃至請求項3のいずれかに記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、画像信号線(ソース信号線)の本数を削減して開口率を向上させ得るとともに、高輝度のバックライト装置を使用可能なように薄膜トランジスタ(Thin Film Transistor : TFT)素子のチャネル部等を遮光する遮光膜を有する液晶表示装置(Liquid Crystal Display : LCD)に関するものである。

**【背景技術】****【0002】**

従来、LCDは、TFT素子を含む画素部が多数形成されたアレイ側基板と、カラーフィルタ及びブラックマトリクスが形成されたカラーフィルタ側基板とを互いに対向させて、それらの基板を所定の間隔でもって貼り合わせ、それらの基板間に液晶を充填、封入させることによって作製される。また、一般的に、カラーフィルタ側基板は、TFT素子及び画素電極に対向する側の面(液晶側の面)の全面に、画素電極との間で液晶に印加する垂直電界を形成するための共通電極が形成されている。また、LCDが画素電極と共に電極との間で液晶に印加する横電界を形成するIPS(In-Plane Switching)方式のLCDである場合、共通電極はアレイ側基板の画素電極と同じ面内に形成される。LCDが画素電極と共に電極との間で液晶に印加する端部電界を形成するFFS(Fringe Field Switching)方式のLCDである場合、共通電極はアレイ側基板の画素部に画素電極の上方または下方に絶縁層を挟んで形成される。また、カラーフィルタ側基板の液晶側の面には、それぞれの画素部に対応する赤(R)、緑(G)、青(B)のカラーフィルタが形成されており、それぞれの画素部を通過する光が相互に干渉することを防ぐブラックマトリクスがカラーフィルタの外周を囲むように形成されている。

**【0003】**

従来のアクティブマトリクス型のLCDの基本構成の1例を図2に示す。例えばIPS

10

20

30

40

50

方式のLCDの場合、TFT素子21を含む画素部P11, P12, P13~Pnmが多数形成されたTFTアレイ側基板は、その上の第1の方向（例えば、行方向）に形成された複数本のゲート信号線GL1, GL2, GL3~GLnと、第1の方向と交差する第2の方向（例えば、列方向）にゲート信号線GL1, GL2, GL3~GLnと交差させて形成された複数本の画像信号線（ソース信号線）SL1, SL2, SL3~SLmと、ゲート信号線GL1, GL2, GL3~GLnと画像信号線SL1, SL2, SL3~SLmの交差部に形成された、TFT素子21、画素電極PE11, PE12, PE13~PEnm及びその画素電極PE11, PE12, PE13~PEnmとの間で液晶に印加する横電界（水平電界）を形成するための共通電極（基準電極）を含む画素部P11, P12, P13~Pnmと、共通電極に共通電圧（Vcom）を供給する共通電圧線22と、を有する構成である。なお、図4において、23はゲート信号線GL1, GL2, GL3~GLnに順次ゲート信号を入力するゲート信号線駆動回路、24は画像信号線SL1, SL2, SL3~SLmに順次画像信号を入力する画像信号線駆動回路である。IPS方式のLCDは、垂直電界によってツイステッドネマチック（Twisted Nematic：TN）液晶を駆動するLCDと比較して、コントラスト、グレー反転、色ずれ等の視野角特性を高めることができる。その結果、広視野角を得ることができるので、大型のLCDに好適に用いられている。

#### 【0004】

そして、図2のLCDにおける多数のTFT素子21及び画素電極のうち一部を拡大して示す拡大平面図を図3に示す。図3に示すように、ゲート信号線31（Gate1, Gate2, Gate3）と画像信号線32（SigR1, SigG1, SigB1, SigR2, SigG2, SigB2）との交差部に、TFT素子21及びインジウム錫酸化物（Indium Tin Oxide：ITO）等の透明電極から成る画素電極R11, G11, B11~B32が形成されている。TFT素子21は、画像信号線32にコンタクトホール等によって電気的に接続されたソース電極33、ソース電極33からドレイン電極35にかけて形成されたn+型アモルファスシリコン（以下、n+型a-Siとも称する），n+型多結晶シリコン（以下、n+型p-Siとも称する）等から成る半導体膜34、半導体膜34及び画素電極R11, G11, B11~B32にコンタクトホール等によって電気的に接続されたドレイン電極35を含む。また、ゲート信号線31と半導体膜34との2つの交差部には、それぞれチャネル部36a, 36bがあり、ゲート信号線31にゲート信号が入力されてオン状態になったときにチャネル部36a, 36bが導通状態となる。チャネル部36a, 36bが導通状態のときに画像信号が入力されたら、画素電極R11, G11, B11~B32に所定の画素電圧が印加されて液晶を駆動し、画像表示が実行される。

#### 【0005】

図4は、図3の画像信号線32a（SigR1）, 32b（SigG1）, 32c（SigB1）, 32d（SigR2）, 32e（SigG2）, 32f（SigB2）に画像信号を入力するための画像信号入力部の回路図である。画像信号線32a~32fのそれぞれの画像信号入力部には、CMOSトランスマニアゲート素子40a, 40b, 40c, 40d, 40e, 40fがそれぞれ接続されており、CMOSトランスマニアゲート素子40a~40cの各ソース電極は画像信号入力線S1に共通接続され、CMOSトランスマニアゲート素子40d~40fの各ソース電極は画像信号入力線S2に共通接続されている。画像信号入力線S1, S2は、チップオンガラス（Chip On Glass：COG）方式で基板上に実装された画像信号線駆動用IC, LSI等から画像信号を入力するものである。また、CMOSトランスマニアゲート素子40a~40cの各ドレイン電極は、それぞれ画像信号線32a, 32b, 32cに接続され、CMOSトランスマニアゲート素子40d~40fの各ドレイン電極は、それぞれ画像信号線32d, 32e, 32fに接続されている。

#### 【0006】

CMOSトランスマニアゲート素子40a~40fはそれぞれ、p型CMOSトランジスタとn型CMOSトランジスタが、それらのソース電極とドレイン電極が共通接続されて成り、p型CMOSトランジスタのゲート電極とn型CMOSトランジスタのゲート電極が制御入力電極とされている。即ち、p型CMOSトランジスタのゲート電極にロー（L）の信号が入力されるとともにn型CMOSトランジスタのゲート電極にハイ（H）の信号が入力されたときに、ソース電極とドレイン電極との間に電流が流れて画像信号が入力される。

## 【0007】

また、MUX1, XMUX1, MUX2, XMUX2, MUX3, XMUX3は、画像信号線32a～32fを時分割駆動するための時分割信号入力線である。MUX1は、CMOSトランジスタのゲート電極に接続され、XMUX1( MUX1の反転信号線 )はCMOSトランジスタのゲート電極に接続されており、MUX1にHの信号が入力されるとともにXMUX1にLの信号が入力されたときに、画像信号入力線S1, S2から入力された画像信号SigR1, SigR2が、画像信号線32a, 32dを伝送される。MUX2は、CMOSトランジスタのゲート電極に接続され、XMUX2( MUX2の反転信号線 )はCMOSトランジスタのゲート電極に接続され、XMUX2( MUX2の反転信号線 )はCMOSトランジスタのゲート電極に接続されており、MUX2にHの信号が入力されるとともにXMUX2にLの信号が入力されたときに、画像信号入力線S1, S2から入力された画像信号SigG1, SigG2が、画像信号線32b, 32eを伝送される。MUX3は、CMOSトランジスタのゲート電極に接続され、XMUX3( MUX3の反転信号線 )はCMOSトランジスタのゲート電極に接続され、XMUX3( MUX3の反転信号線 )はCMOSトランジスタのゲート電極に接続されるとともにXMUX3にLの信号が入力されたときに、画像信号入力線S1, S2から入力された画像信号SigB1, SigB2が、画像信号線32c, 32fを伝送される。

10

## 【0008】

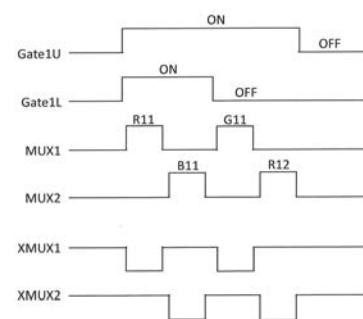

図5は、図3の画素電極R11, G11, B11を駆動するためのタイミングチャートである。ゲート信号線(Gate1)がオン状態のときであって、MUX1にHの信号が入力されるとともにXMUX1にLの信号が入力されたときに、画素電極R11に所定の画像信号が入力される。ゲート信号線(Gate1)がオン状態のときであって、MUX2にHの信号が入力されるとともにXMUX2にLの信号が入力されたときに、画素電極G11に所定の画像信号が入力される。ゲート信号線(Gate1)がオン状態のときであって、MUX3にHの信号が入力されるとともにXMUX3にLの信号が入力されたときに、画素電極B11に所定の画像信号が入力される。

20

## 【0009】

また、他の従来例として、1本の信号線の両側に左側TFTと右側TFTを設け、左側TFTにゲート信号を供給する第1走査線を設け、右側TFTにゲート信号を供給する第2走査線を設け、2つの信号線に対し、4画素分の画像信号を供給する画像出力回路を設けることにより、制御線の数を減らすことのできる液晶表示装置が提案されている(例えば、特許文献1を参照)。

30

## 【0010】

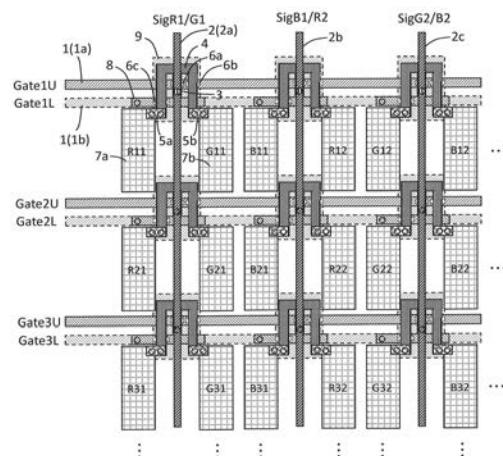

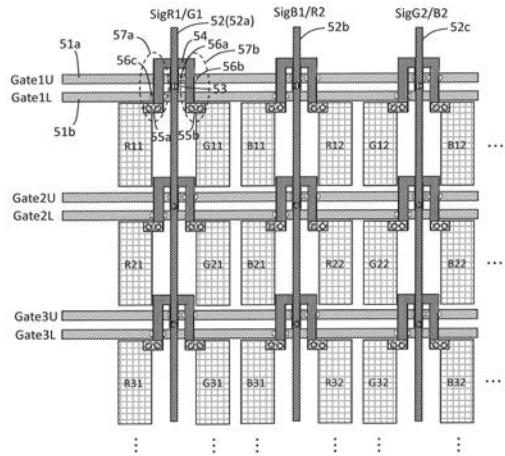

図6は、上記構成と類似した構成のLCDにおける多数のTFT素子及び画素電極のうち一部を拡大して示す拡大平面図である。1本の画像信号線52の両側に左側TFT57aと右側TFT57bが設けられ、左側TFT57aと右側TFT57bのいずれか一方が選択的にオン状態になるように構成されている。1行の画素電極群R11, G11, B11, R12, G12, B12～に対して、上側ゲート信号線51a(Gate1U)及び下側ゲート信号線51b(Gate1L)から成る一对のゲート信号線が設けられている。上側ゲート信号線51a及び下側ゲート信号線51bがオン状態のときに、画素電極R11、画素電極B11が順次オン状態になり、上側ゲート信号線51aのみがオン状態のときに、画素電極G11、画素電極R12が順次オン状態になる。

40

## 【0011】

上側ゲート信号線51a及び下側ゲート信号線51bがオン状態のときに、チャネル部56a, 56cが導通状態になり、画像信号SigR1が、画像信号線52、半導体膜54、ドレイン電極55aを経由して画素電極R11に入力される。その後、上側ゲート信号線51a及び下側ゲート信号線51bがオン状態のときに、同様にして画像信号SigB1が画素電極B11に入力される。次いで、上側ゲート信号線51aのみがオン状態のときに、チャネル部56a, 56bが導通状態になり、画像信号SigG1が、画像信号線52、半導体膜54、ドレイン電極55bを経由して画素電極G11に入力される。その後、上側ゲート信号線51aのみがオン状態のときに、同様にして画像信号SigR2が画素電極R12に入力される。

## 【0012】

50

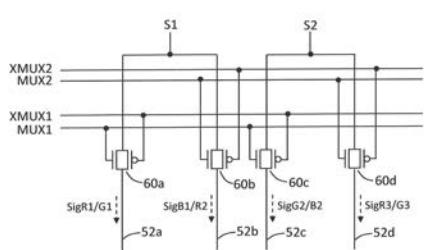

図7は、図6の画像信号線52a (SigR1/G1) , 52b (SigB1/R2) , 52c (SigG2/B2) , 52d (SigR3/G3) (図6に図示せず) に画像信号を入力するための画像信号入力部の回路図である。画像信号線52a～52dのそれぞれの画像信号入力部には、CMOSトランスマジックゲート素子60a, 60b, 60c, 60dがそれぞれ接続されており、CMOSトランスマジックゲート素子60a, 60bの各ソース電極は画像信号入力線S1に共通接続され、CMOSトランスマジックゲート素子60c, 60dの各ソース電極は画像信号入力線S2に共通接続されている。画像信号入力線S1, S2は、チップオンガラス(Chip On Glass : COG)方式で基板上に実装された画像信号線駆動用IC, LSI等から画像信号を入力するものである。また、CMOSトランスマジックゲート素子60a, 60bの各ドレイン電極は、それぞれ画像信号線52a, 52bに接続され、CMOSトランスマジックゲート素子60c, 60dの各ドレイン電極は、それぞれ画像信号線52c, 52dに接続されている。10

#### 【0013】

また、MUX1, XMUX1, MUX2, XMUX2は、画像信号線52a～52dを時分割駆動するための時分割信号入力線である。MUX1は、CMOSトランスマジックゲート素子60a, 60cのn型CMOSトランジスタのゲート電極に接続され、XMUX1 (MUX1の反転信号線) はCMOSトランスマジックゲート素子60a, 60cのp型CMOSトランジスタのゲート電極に接続されており、MUX1にHの信号が入力されるとともにXMUX1にLの信号が入力されたときに、画像信号入力線S1, S2から入力された画像信号SigR1/G1, SigG2/B2が、画像信号線52a, 52cを伝送される。MUX2は、CMOSトランスマジックゲート素子60b, 60dのn型CMOSトランジスタのゲート電極に接続され、XMUX2 (MUX2の反転信号線) はCMOSトランスマジックゲート素子60b, 60dのp型CMOSトランジスタのゲート電極に接続されており、MUX2にHの信号が入力されるとともにXMUX2にLの信号が入力されたときに、画像信号入力線S1, S2から入力された画像信号SigB1/R2, SigR3/G3が、画像信号線52b, 52dを伝送される。20

#### 【0014】

図8は、図6の画素電極R11, G11, B11, R12を駆動するためのタイミングチャートである。上側ゲート信号線51a (Gate1U) 及び下側ゲート信号線51b (Gate1L) がオン状態のときであって、MUX1にHの信号が入力されるとともにXMUX1にLの信号が入力されたときに画素電極R11に所定の画像信号が入力され、次いでMUX2にHの信号が入力されるとともにXMUX2にLの信号が入力されたときに画素電極B11に所定の画像信号が入力される。上側ゲート信号線51a (Gate1U) がオン状態で下側ゲート信号線51b (Gate1L) がオフ状態のときであって、MUX1にHの信号が入力されるとともにXMUX1にLの信号が入力されたときに画素電極G11に所定の画像信号が入力され、次いでMUX2にHの信号が入力されるとともにXMUX2にLの信号が入力されたときに画素電極R12に所定の画像信号が入力される。30

#### 【先行技術文献】

#### 【特許文献】

#### 【0015】

【特許文献1】特開2006-201315号公報

【特許文献2】特開2003-229578号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0016】

しかしながら、図6に示した上記構成の従来のLCDにおいては、TFT素子の裏面側から入射する光を遮光するために、チャネル部56a, 56b, 56c及びその周囲に平面視で重なるように遮光膜を形成した場合、高輝度のバックライト装置を用いた際に遮光性が不十分である場合があった（例えば、特許文献2を参照）。

#### 【0017】

また、遮光性を高めるためにゲート信号線51a, 51b、画像信号線52a, 52b, 52cに遮光性を付与することも考えられるが、画素部の開口率を高めるためにゲート信号線51a, 51b、画像信号線52a, 52b, 52cはかなり細線化されており、その結果、ゲート信号線51a, 51b、画像信号線52a, 52b, 52cによって遮光することが困難であった。4050

**【0018】**

従って、本発明は、上記従来の問題点に鑑みて完成されたものであり、その目的は、画素部の開口率を高く維持した状態で TFT 素子のチャネル部及びその周囲に対する遮光性を向上させることができる LCD とすることである。

**【課題を解決するための手段】****【0019】**

本発明の液晶表示装置は、基板の上面の第 1 の方向に形成された複数本のゲート信号線と、前記第 1 の方向に交差する第 2 の方向に前記ゲート信号線と交差させて前記ゲート信号線の上方に形成された複数本の画像信号線と、1 本の前記画像信号線に対して前記ゲート信号線と前記画像信号線の交差部の左側及び右側に、それぞれ 1 本の前記画像信号線に電気的に接続された状態で形成されているチャネル部を有する薄膜トランジスタ素子及び画素電極と、を有しており、前記ゲート信号線は、前記第 1 の方向に並んだ 1 群の前記画素電極に対応して第 1 及び第 2 のゲート信号線の 2 本が平面視で近接して形成されており、前記第 1 のゲート信号線が前記右側の薄膜トランジスタ素子に対して 2 つのチャネル部を形成するとともに前記右側の画素電極に画像信号を入力するように構成されており、前記第 2 のゲート信号線が前記左側の薄膜トランジスタ素子に対して 1 つのチャネル部を形成するとともに前記左側の画素電極に画像信号を入力するように構成されている液晶表示装置であって、前記第 1 及び第 2 のゲート信号線は、前記基板の上面に垂直な方向において前記基板の上面の側に互いに異なる位置にあるとともに前記基板に近い方が遠い方よりも幅広に形成されている構成である。

10

20

30

40

**【0020】**

本発明の液晶表示装置は、好ましくは、前記第 1 及び第 2 のゲート信号線のうち前記基板に近い方は、平面視ですべての前記チャネル部と重なる延出部を有している。

**【0021】**

また本発明の液晶表示装置は、好ましくは、前記第 1 及び第 2 のゲート信号線は、平面視で少なくとも部分的に重なっている。

**【0022】**

また本発明の液晶表示装置は、好ましくは、前記ゲート信号線は、Al, Mo, Cr, Ti, Ta, W 及び Pd のうちの少なくとも一つを含む金属膜から成る。

**【発明の効果】****【0023】**

本発明の液晶表示装置は、基板の上面の第 1 の方向に形成された複数本のゲート信号線と、第 1 の方向に交差する第 2 の方向にゲート信号線と交差させてゲート信号線の上方に形成された複数本の画像信号線と、1 本の画像信号線に対してゲート信号線と画像信号線の交差部の左側及び右側に、それぞれ 1 本の画像信号線に電気的に接続された状態で形成されているチャネル部を有する薄膜トランジスタ素子及び画素電極と、を有しており、ゲート信号線は、第 1 の方向に並んだ 1 群の画素電極に対応して第 1 及び第 2 のゲート信号線の 2 本が平面視で近接して形成されており、第 1 のゲート信号線が右側の薄膜トランジスタ素子に対して 2 つのチャネル部を形成するとともに右側の画素電極に画像信号を入力するように構成されており、第 2 のゲート信号線が左側の薄膜トランジスタ素子に対して 1 つのチャネル部を形成するとともに左側の画素電極に画像信号を入力するように構成されている液晶表示装置であって、第 1 及び第 2 のゲート信号線は、基板の上面に垂直な方向において基板の上面の側に互いに異なる位置にあるとともに基板に近い方が遠い方よりも幅広に形成されていることから、以下ののような効果を奏する。即ち、画像信号線の数を削減することができるので、画素部の開口率を向上させることができ。また、第 1 及び第 2 のゲート信号線は、基板の上面に垂直な方向において互いに異なる位置にあるので、それらのうちの少なくとも一方に遮光性を付与するために幅広に形成することが可能となる。その結果、画素部の開口率を高く維持した状態で薄膜トランジスタのチャネル部及びその周囲に対する遮光性を高めることができる。

**【0024】**

50

本発明の液晶表示装置は、好ましくは、第1及び第2のゲート信号線のうち基板に近い方は、平面視ですべてのチャネル部と重なる延出部を有していることから、延出部がチャネル部に対する遮光膜として機能し、基板の裏面側、例えばバックライト装置側からチャネル部に入り込む光を遮光することができる。

#### 【0025】

また本発明の液晶表示装置は、好ましくは、第1及び第2のゲート信号線は、平面視で少なくとも部分的に重なっていることから、第1及び第2のゲート信号線が1つの幅広い遮光膜として機能することとなる。また、画素部の開口率が低下することを抑えて遮光性を高めることができる。

#### 【0026】

また本発明の液晶表示装置は、好ましくは、ゲート信号線は、Al, Mo, Cr, Ti, Ta, W及びPdのうちの少なくとも一つを含む金属膜から成ることから、基板の裏面側から照射される高輝度のバックライトの光を有効に遮光することができる。

#### 【図面の簡単な説明】

#### 【0027】

【図1】図1は、本発明の液晶表示装置について実施の形態の1例を示す図であり、多数のTFT素子及び画素電極のうち一部を拡大して示す拡大平面図である。

#### 【図2】図2は、従来の液晶表示装置の1例のブロック回路図である。

【図3】図3は、従来の液晶表示装置の1例について多数のTFT素子及び画素電極のうち一部を拡大して示す拡大平面図である。

【図4】図4は、図3の各画像信号線に画像信号を時分割で入力するための画像信号入力部の回路図である。

【図5】図5は、図3の各画素電極を時分割で駆動するためのタイミングチャートである。

【図6】図6は、従来の液晶表示装置の他例について多数のTFT素子及び画素電極のうち一部を拡大して示す拡大平面図である。

【図7】図7は、図6の各画像信号線に画像信号を時分割で入力するための画像信号入力部の回路図である。

【図8】図8は、図6の各画素電極を時分割で駆動するためのタイミングチャートである。

#### 【発明を実施するための形態】

#### 【0028】

以下、本発明のLCDの実施の形態について、図面を参照しながら説明する。但し、以下で参照する各図は、本発明のLCDの主要な構成部材等を示している。従って、本発明のLCDは、図に示されていない回路基板、配線導体、制御IC, LSI等の周知の構成部材を備えていてもよい。

#### 【0029】

本発明のLCDは、図1に示すように、ガラス基板等から成る基板の上面の第1の方向(例えば、行方向)に形成された複数本のゲート信号線1と、第1の方向に交差する第2の方向(例えば、列方向)にゲート信号線1と交差させてゲート信号線1の上方に形成された複数本の画像信号線2と、1本の画像信号線2に対してゲート信号線1と画像信号線2の交差部の左側及び右側に、それぞれ1本の画像信号線2に電気的に接続された状態で形成されているチャネル部6a, 6b, 6cを有するTFT素子及び画素電極7a, 7bと、を有しており、ゲート信号線1は、第1の方向に並んだ1群の画素電極7a, 7bに対応して第1及び第2のゲート信号線1a, 1bの2本が平面視で近接して形成されており、第1のゲート信号線1aが右側のTFT素子に対して2つのチャネル部6a, 6bを形成するとともに右側の画素電極7bに画像信号を入力するように構成されており、第2のゲート信号線1bが左側のTFT素子に対して1つのチャネル部6cを形成するとともに左側の画素電極7aに画像信号を入力するように構成されているLCDであって、第1及び第2のゲート信号線1a, 1bは、基板の上面に垂直な方向において基板の上面の側

10

20

30

40

50

に互いに異なる位置にあるとともに基板に近い方が遠い方よりも幅広に形成されていることから、以下のような効果を奏する。即ち、画像信号線2の数を削減することができるのと、画素部の開口率を向上させることができる。また、第1及び第2のゲート信号線1a, 1bは、基板の上面に垂直な方向において互いに異なる位置にあるので、それらのうちの少なくとも一方に遮光性を付与するために幅広に形成することが可能となる。その結果、画素部の開口率を高く維持した状態でTFT素子のチャネル部6a, 6b, 6c及びその周囲に対する遮光性を高めることができる。第1及び第2のゲート信号線1a, 1bのうちの少なくとも一方に遮光性を付与するために幅広に形成するとは、それらの少なくとも一方が幅広部としての延出部(遮光膜9)を有するように形成すること、またそれらの少なくとも一方が幅広部としての延出部(遮光膜9)を有するとともに線幅が他方よりも幅広になるように形成することを含む。

10

### 【0030】

図1に示すように、ゲート信号線1(1a, 1b)と画像信号線2(2a, 2b, 2c)との交差部において、1本の画像信号線2の左側及び右側にそれぞれ、その1本の画像信号線2に電気的に接続された状態でTFT素子及びITO等の透明電極から成る画素電極R11, G11, B11~B32が形成されている。TFT素子は、画像信号線2にコンタクトホール等によって電気的に接続されたソース電極3、ソース電極3からドレイン電極5a, 5bにかけて形成されたn+型a-Si, n+型p-Si等から成る半導体膜4、半導体膜4及び画素電極R11, G11, B11~B32にコンタクトホール等によって電気的に接続されたドレイン電極5a, 5bを含む。また、ゲート信号線1と半導体膜4との3つの交差部には、それぞれチャネル部6a, 6b, 6cがあり、ゲート信号線1にゲート信号が入力されてオン状態になったときにチャネル部6a, 6b, 6cが導通状態となる。チャネル部6a, 6b, 6cが導通状態のときに画像信号SigR1/G1, SigB1/R2, SigG2/B2が入力されたら、画素電極R11, G11, B11~B32に所定の画素電圧が印加されて液晶を駆動し、画像表示が実行される。なお、駆動方法については、上述した図6~図8に示した従来のLCDと同様であるので、その詳細な説明は省く。

20

### 【0031】

また、図1のLCDは、第1のゲート信号線1a及び第2のゲート信号線1bのうち第2のゲート信号線1bが幅広部としての延出部(遮光膜9)を有している。即ち、第2のゲート信号線1bが基板の上面に形成されるとともにその延出部である遮光膜9に連続している。チャネル部6cは、第1のゲート信号線1aと同層に形成された部分ゲート信号線8と半導体膜4との交差部にある。部分ゲート信号線8と第2のゲート信号線1bとはコンタクトホール等によって電気的に接続されている。この場合、遮光膜9と第2のゲート信号線1bとの間で光の反射が生じてチャネル部6a~6cへ光が入り込むことを抑えることができる。また、遮光膜9と第2のゲート信号線1bを1つの薄膜形成工程で形成することができるので、製造が容易になる。

30

### 【0032】

図1のLCDは、基板の上面に垂直な方向の積層構造は、例えば以下のようになっている。基板の上面に遮光膜9及び第2のゲート信号線1bが形成されており、その上に順次、絶縁層を介して第1のゲート信号線1a及び部分ゲート信号線8、他の絶縁層を介してソース電極3、さらに他の絶縁層を介して半導体膜4、さらに他の絶縁層を介して画素電極7a, 7b、さらに他の絶縁層を介して画像信号線2が形成されている。画像信号線2とソース電極3はコンタクトホール等によって電気的に接続され、ソース電極3と半導体膜4はコンタクトホール等によって電気的に接続され、半導体膜4と画素電極7a, 7bはコンタクトホール等によって電気的に接続されている。

40

### 【0033】

ゲート信号線1、画像信号線2、ドレイン電極5a, 5b、ソース電極3は、導電層から成り、例えばタンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、クロム(Cr)、銀(Ag)、銅(Cu)、ネオジウム(Nd)等から選ばれた元素、それらの元素を主成分とする合金材料、窒化チタン、窒化

50

タンタル、窒化モリブデン等の金属窒化物等の導電性を有する材料から成ることがよい。導電層は、これらの材料の単層構造または複数層の積層構造とすることができます。積層構造とすることにより、低抵抗化を実現することができる。また、ゲート信号線1、画像信号線2、ドレイン電極5a, 5b、ソース電極3は、一般に遮光性を有している。また、画素電極7a, 7bは、透光性導電層から成り、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化珪素を添加したインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、リンやボロンが含まれるシリコン(Si)等の導電性材料であって透光性を有する材料から成る。

#### 【0034】

基板と導電層との間、また導電層間にある絶縁層は、単層構造または複数層の積層構造とすることができます。これらの絶縁層の材料としては、無機材料または有機材料を用いることができる。無機材料としては、酸化珪素(SiO<sub>2</sub>)または窒化珪素(SiN<sub>x</sub>)を用いることができる。有機材料としては、アクリル樹脂、ポリイミド、ポリアミド、ポリイミドアミド、ベンゾシクロブテン、シロキサン、ポリシラザンを用いることができる。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が形成される。その置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基、少なくとも水素を含む有機基とフルオロ基を用いてもよい。ポリシラザンは、珪素(Si)と窒素(N)の結合を有するポリマー材料を出発原料として形成される。これらの絶縁層の材料として有機材料を用いると、その表面の平坦性を高めることができ、好みしい。これらの絶縁層の材料として無機材料を用いると、半導体膜4、ゲート信号線1の表面形状に沿うような表面を有するものとなる。また、この場合であっても、厚膜化することにより平坦性を有するものとなる。

10

20

30

40

#### 【0035】

半導体膜4はアモルファスシリコン、多結晶シリコン等から成るが、その多結晶シリコンは低温多結晶シリコン(Low-temperature Poly Silicon: LTPS)である。そして、LTPSから成る半導体膜4は以下のようにして作製される。まず、ガラス基板等の基板上に、プラズマCVD(Chemical Vapor Deposition)法によって、アモルファスシリコン層を形成する。次に、アモルファスシリコン層を多結晶化するために、450℃以下のガラス基板の温度でアモルファスシリコン層にエキシマレーザ光を照射する。エキシマレーザ光のエネルギーによってアモルファスシリコンは瞬間的に溶融し凝固する。その結果、平均粒径0.3μm程度のLTPS層に変化する。半導体膜4を構成するLTPSは、n型LTPS、p型LTPSのいずれであってもよいが、高い電荷(電子等)の移動度が得られる点でn型LTPSが好みしい。

#### 【0036】

遮光膜9は、スパッタリング法、CVD法等の薄膜形成法等によって形成される。また、遮光膜9は金属、合金、金属酸化物、金属窒化物、黒色系樹脂等の遮光性のある材料から成ればよい。例えば、遮光膜9及びゲート信号線1は、アルミニウム(A1)、モリブデン(Mo)、クロム(Cr)、チタン(Ti)、タンタル(Ta)、タングステン(W)及びパラジウム(Pd)のうちの少なくとも一つを含む金属膜から成ることが好みしい。遮光性を有する第2のゲート信号線1bも同様の材料から成ることがよい。この場合、ガラス基板の下方から照射される高輝度(100万カンデラ以上)のバックライト装置の光を有效地に遮光することができる。従って、この遮光膜9を有するLCDは、ヘッドアップディスプレイ、プロジェクタ装置等の高輝度のバックライト装置を用いるLCDに好適なものである。

#### 【0037】

遮光膜9の他の材料としては、銀(Ag)、銅(Cu)、ネオジウム(Nd)等から選ばれた元素、またはそれらの元素を主成分とする合金材料、及び窒化チタン、窒化タンタル、窒化モリブデン等の金属窒化物等の導電性を有する材料を採用し得る。遮光膜9は、これらの材料から成る単層構造、または複数層の積層構造とすることができます。

#### 【0038】

50

遮光膜9の厚みは、遮光膜9の光学濃度(Optical Density : O D)値が3程度以上となるような厚みであればよい。

#### 【0039】

遮光膜9は、その平面視における形状が、長方形、角部を丸めた長方形、橢円形、長円形等の種々の形状とし得る。また遮光膜9は、その形状線(アウトライン)とチャネル部6a～6cの形状線(アウトライン)との間の平面視での距離が、いずれの方向においても光リーク電流発生抑止距離以上であることが好ましい。この光リーク電流発生抑止距離は、例えば4μm以上である。4μm未満では、不活性状態のチャネル部6a～6cに光リーク電流が流れやすくなる。

#### 【0040】

なお、チャネル部6a～6cは、n型LTPSから成る場合、ノンドープであるか、TFT素子の閾値電圧を制御するためにリン(P)またはホウ素(B)を $5 \times 10^{11} \sim 2 \times 10^{12} / \text{cm}^2$ 程度ドープしたものである。また、半導体膜4のチャネル部6a～6cの周りに、リーク電流低減のために低濃度ドープドレイン(Lightly Doped Drain : LDD)部を形成してもよい。このLDD部は、例えばリン(P)を $1 \times 10^{12} \sim 5 \times 10^{13} / \text{cm}^2$ 程度ドープしたものである。半導体膜4のソース電極3の部位、ドレイン電極5a, 5bの部位は、トランジスタの動作信頼性を高めるために、例えばリン(P)またはホウ素(B)を $5 \times 10^{14} \sim 5 \times 10^{15} / \text{cm}^2$ 程度ドープしたものである。

#### 【0041】

半導体膜4がLDD部を有する場合、遮光膜9の形状線(アウトライン)とLDD部の形状線(アウトライン)との間の平面視での距離が、いずれの方向においても光リーク電流発生抑止距離以上であることが好ましい。この光リーク電流発生抑止距離は、例えば4μm以上である。

#### 【0042】

また本発明のLCDは、第1のゲート信号線1aの線幅は3μm～10μm程度であり、線幅が細いために、光が第1のゲート信号線1aを回り込む等して遮光性が発現しにくくなっている。一方、第2のゲート信号線1bの線幅も3μm～10μm程度であるが、TFT素子の下方(基板側)にある遮光膜9が幅広部となっているために、光が部分ゲート信号線8及び第1のゲート信号線1aを回り込む等することを抑えて、チャネル部6a, 6b, 6cに対する遮光性が発現する。

#### 【0043】

また本発明のLCDは、第1及び第2のゲート信号線1a, 1bは、平面視で部分的に若しくは全体的に重なっていることが好ましい。この場合、第1及び第2のゲート信号線1a, 1bの両方によってチャネル部6a, 6b, 6cに対する遮光性が発現するとともに、画素部の開口率が向上する。この場合、特にチャネル部6b, 6cに対する遮光性が向上する。

#### 【0044】

本発明のLCDは以下のようにして作製される。LCDは、TFT素子を含む画素部が多数形成されたガラス基板等から成るTFTアレイ側基板と、カラーフィルタ及びブラックマトリクスが形成されたガラス基板等から成るカラーフィルタ側基板とを互いに対向させて、それらの基板を所定の間隔でもって貼り合わせ、それらの基板間に液晶を充填、封入することによって作製される。また、一般的に、カラーフィルタ側基板は、TFT素子及び画素電極に対向する側の正面(正面aとする)の全面に、画素電極との間で液晶に印加する垂直電界を形成するための共通電極(基準電極)が形成されている。この共通電極は、IPS(In-Plane Switching)方式のLCDの場合、TFTアレイ側基板の画素部に画素電極と同じ面内に形成されることによって横電界を生じさせるものとなる。また共通電極は、FFS(Fringe Field Switching)方式のLCDの場合、TFTアレイ側基板の画素部に画素電極の上方または下方に絶縁層を挟んで形成されることによって端部電界(Fringe Field)を生じさせるものとなる。また、カラーフィルタ側基板の正面aには、それぞれの画素に対応する赤(R)、緑(G)、青(B)のカラーフィルタが形成され

10

20

30

40

50

ており、それぞれの画素を通過する光が相互に干渉することを防ぐブラックマトリクスがカラーフィルタの外周を囲むように形成されている。

【0045】

なお、本発明のLCDは、上記実施の形態に限定されるものではなく、適宜の設計的な変更、改良を含んでいてもよい。

【産業上の利用可能性】

【0046】

本発明のアクティブマトリクス型のLCDは各種の電子機器に適用できる。その電子機器としては、ヘッドアップディスプレイ、プロジェクタ装置、自動車経路誘導システム（カーナビゲーションシステム）、船舶経路誘導システム、航空機経路誘導システム、スマートフォン端末、携帯電話、タブレット端末、パーソナルデジタルアシスタント（PDA）、ビデオカメラ、デジタルスチルカメラ、電子手帳、電子書籍、電子辞書、パーソナルコンピュータ、複写機、ゲーム機器の端末装置、テレビジョン、商品表示タグ、価格表示タグ、産業用のプログラマブル表示装置、カーオーディオ、デジタルオーディオプレイヤー、ファクシミリ、プリンター、現金自動預け入れ払い機（ATM）、自動販売機、デジタル表示式腕時計などがある。

10

【符号の説明】

【0047】

1 ゲート信号線

1 a 第1のゲート信号線

20

1 b 第2のゲート信号線

2 画像信号線（ソース信号線）

3 ソース電極

4 半導体膜

5 a , 5 b ドレイン電極

6 a , 6 b , 6 c チャネル部

7 a , 7 b 画素電極

8 部分ゲート信号線

9 遮光膜（延出部）

【図1】

【圖 5】

【 四 6 】

【 図 7 】

【 四 8 】

|                |                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2016126080A</a>                                                                                                                                                   | 公开(公告)日 | 2016-07-11 |

| 申请号            | JP2014265270                                                                                                                                                                    | 申请日     | 2014-12-26 |

| [标]申请(专利权)人(译) | 京瓷显示器株式会社                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 京瓷显示器有限公司                                                                                                                                                                       |         |            |

| [标]发明人         | 市村照彦                                                                                                                                                                            |         |            |

| 发明人            | 市村 照彦                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/1368                                                                                                                                                                      |         |            |

| FI分类号          | G02F1/1368                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H192/AA24 2H192/BC31 2H192/CB05 2H192/CB45 2H192/CC17 2H192/CC24 2H192/CC33 2H192/CC42 2H192/CC62 2H192/EA04 2H192/EA15 2H192/EA22 2H192/EA43 2H192/EA67 2H192/GD61 2H192/JB02 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                       |         |            |

#### 摘要(译)

提供一种能够在保持像素部的高开口率的同时提高相对于TFT元件的沟道部及其周围的遮光性的LCD。LCD电连接到相对于一条图像信号线2在选通信号线1和图像信号线2的交点的左侧和右侧的一条图像信号线2。并且，TFT元件具有形成在其中的沟道部分6a至6c以及像素电极7a和7b，并且栅极信号线1对应于在行方向上布置的一组像素电极7a和7b。在形成有两条第一和第二栅极信号线1a和1b的LCD中，第一和第二栅极信号线1a和1b在垂直于基板的上表面的方向上彼此不同。它形成在更靠近基板并且比远离基板更宽的位置处。 [选型图]图1