(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-68856

(P2015-68856A)

(43) 公開日 平成27年4月13日(2015.4.13)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G02F 1/133 (2006.01)</b> | G02F 1/133 | 550 2H193   |

| <b>G09G 3/36 (2006.01)</b>  | G02F 1/133 | 520 5C006   |

| <b>G09G 3/20 (2006.01)</b>  | G09G 3/36  | 5C080       |

|                             | G09G 3/20  | 670D        |

|                             | G09G 3/20  | 642A        |

審査請求 未請求 請求項の数 6 O L (全 19 頁) 最終頁に続く

|           |                              |            |                                                                                                                                                       |

|-----------|------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2013-200444 (P2013-200444) | (71) 出願人   | 000005049<br>シャープ株式会社<br>大阪府大阪市阿倍野区長池町22番22号                                                                                                          |

| (22) 出願日  | 平成25年9月26日 (2013. 9. 26)     | (74) 代理人   | 110000338<br>特許業務法人HARAKENZO WORKS<br>PATENT & TRADEMA                                                                                                |

|           |                              | (72) 発明者   | R K<br>澤辺 大一<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内                                                                                                      |

|           |                              | F ターム (参考) | 2H193 ZA04 ZA07 ZB05 ZB12 ZE38<br>5C006 AA16 AF67 BB16 FA34 FA51<br>5C080 AA10 BB05 CC03 DD05 DD27<br>EE29 EE30 FF11 FF12 JJ02<br>JJ03 JJ04 JJ05 JJ06 |

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】電源オフ時に絵素に電荷が蓄積されにくい液晶表示装置を提供する。

【解決手段】電源オフ動作の開始から電源オフ動作の完了までの少なくとも一部の期間に、補助容量配線を介して液晶補助容量に印加される電位である補助容量電位V<sub>C S</sub>の降下速度が、対向電極に印加される電位である対向電位V<sub>C O M</sub>の降下速度よりも速くなる構成にする。

【選択図】図9

## 【特許請求の範囲】

## 【請求項 1】

複数のゲートバスラインと、上記ゲートバスラインと交差する複数のソースバスラインと、上記ゲートバスラインと上記ソースバスラインとの交差部毎に設けられた絵素とを備え、上記絵素が、液晶層を介して対向配置された絵素電極および対向電極と、ゲート端子が上記ゲートバスラインに接続され、ソース端子が上記ソースバスラインに接続され、ドレイン端子が上記絵素電極に接続されたスイッチング素子と、上記絵素電極に対向配置されて上記絵素電極との間で液晶補助容量を形成する補助容量配線とを備えている液晶表示装置であって、

電源オフ動作の開始から電源オフ動作の完了までの少なくとも一部の期間に、上記補助容量配線の電位である補助容量電位の降下速度が、上記対向電極の電位である対向電位の降下速度よりも速くなることを特徴とする液晶表示装置。 10

## 【請求項 2】

電源オフ動作開始前の上記補助容量電位が、上記対向電位よりも高い電位に設定されていることを特徴とする請求項 1 に記載の液晶表示装置。

## 【請求項 3】

電源オフ動作開始前の上記補助容量電位が上記対向電位と同電位または上記対向電位よりも高い電位に設定されており、

電源オフ動作の開始から電源オフ動作の完了までの少なくとも一部の期間に、上記補助容量配線を、対向電位よりも低い電位を供給する低電位供給源に接続する電源切替回路を備えていることを特徴とする請求項 1 に記載の液晶表示装置。 20

## 【請求項 4】

入力電源電圧が所定値以下に低下したことを検知する電圧検知部と、

上記電圧検知部によって入力電源電圧が所定値以下に低下したことが検知された後、上記対向電位が降下開始する前に、上記補助容量配線を、上記対向電位よりも低い電位を供給する低電位供給源に接続する電源切替回路とを備えていることを特徴とする請求項 1 に記載の液晶表示装置。

## 【請求項 5】

上記補助容量配線は、上記ゲートバスラインに接続されていることを特徴とする請求項 1 に記載の液晶表示装置。 30

## 【請求項 6】

上記スイッチング素子は、酸化物半導体からなるチャネル層を有する薄膜トランジスタであることを特徴とする請求項 1 から 5 のいずれか 1 項に記載の液晶表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、液晶表示装置の電源オフ時に各絵素の電荷を除去するための技術に関するものである。

## 【背景技術】

## 【0002】

従来、液晶表示装置において絵素（あるいは画素）に対して同一極性の電界を印加し続けると、液晶分子の分極が生じて絵素の階調表示特性の変化や画像の焼き付き等の不具合が生じることが知られている。

## 【0003】

また、画像を表示させたまま液晶表示装置の電源をオフにした場合、各絵素には電源がオフされる直前の印加電圧が印加されたままになり、同じ画像を描画させ続けることになるので、この場合にも焼き付き現象が生じることが知られている。

## 【0004】

このため、従来の液晶表示装置では、電源をオフにする際、液晶表示パネルの各絵素に印加された電荷を放出させるための所定のオフシーケンスを実行するようになっている。 50

## 【0005】

例えば、特許文献1には、電源回路に電解コンデンサを備えておき、液晶表示装置の電源がオフされたときに、この電解コンデンサに蓄えられた電荷を用いて液晶表示パネルの全画面に所定の固定パターンを描画する処理を行うことで絵素に蓄積される電荷を低減する技術が記載されている。

## 【先行技術文献】

## 【特許文献】

## 【0006】

【特許文献1】特開2000-131671号公報(2000年5月12日公開)

10

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0007】

ところで、近年、酸化物半導体(例えばインジウムガリウム亜鉛酸化物半導体)などからなるオフリーケ電流の少ないTFT(薄膜トランジスタ)を絵素のスイッチング素子として用いることにより、縦シャドーの低減、および間欠駆動による消費電力の低減を図った液晶表示装置が開発されている。

## 【0008】

しかしながら、この種の液晶表示装置は、従来のアモルファスシリコンや低温ポリシリコンなどからなるTFTを用いた液晶表示装置に比べてオフリーケ電流が非常に少ないため、電源オフ時に絵素に蓄積された電荷が抜けにくいという特性を有している。

20

## 【0009】

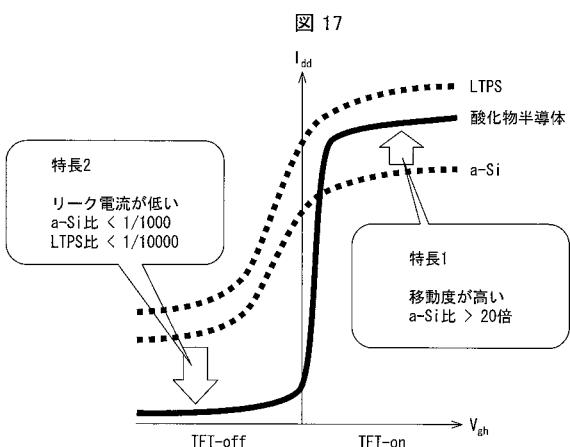

図17は、インジウムガリウム亜鉛酸化物半導体からなるTFT、低温ポリシリコン(LTPS)からなるTFT、およびアモルファスシリコン(a-Si)からなるTFTのオフリーケ電流特性を比較したグラフである。図17の横軸はTFTのゲート-ソース間の電位差(Vg-Vs)、縦軸はソース-ドレイン間を流れる電流を示している。

## 【0010】

図17に示したように、インジウムガリウム亜鉛酸化物半導体からなるTFTは、オフリーケ電流がアモルファスシリコンからなるTFTの1/1000以下、低温ポリシリコンからなるTFTの1/1000以下であるという特性を有している。

30

## 【0011】

酸化物半導体からなるTFTが有する上記のオフリーケ電流が少ないという特性は、駆動時の特性の向上(低消費電力の低減等)をもたらすが、その一方で、液晶表示装置の電源がオフされた時に絵素電極にチャージされた電荷が抜けにくいという問題を招来する。絵素電極に電荷が残っていると、絵素電極と対向電極との間の電位差によって液晶層に一定方向の電界がかかり、有極性分子からなる液晶分子に分極が生じて特性ずれや画像の焼き付き等の不具合が生じる場合がある。

## 【0012】

このため、酸化物半導体等からなるオフリーケ電流の少ないTFTを用いる場合、上記特許文献1に開示されている処理により電源オフ時に絵素に蓄積される電荷を低減しても、当該処理では除去しきれずに絵素に残留した電荷により、焼き付き等の不具合が生じる場合がある。また、特許文献1の技術には、オフシーケンスを実行する回路やオフシーケンスを実行するための電力を充電しておく電界コンデンサ等の充電手段を設ける必要があるので、製造コストの増大を招くという問題もある。

40

## 【0013】

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、電源オフ時に絵素に電荷が蓄積されにくい液晶表示装置を提供することにある。

## 【課題を解決するための手段】

## 【0014】

本発明の一態様にかかる液晶表示装置は、複数のゲートバスラインと、上記ゲートバスラインと交差する複数のソースバスラインと、上記ゲートバスラインと上記ソースバスラ

50

インとの交差部毎に設けられた画素とを備え、上記画素が、液晶層を介して対向配置された絵素電極および対向電極と、ゲート端子が上記ゲートバスラインに接続され、ソース端子が上記ソースバスラインに接続され、ドレイン端子が上記絵素電極に接続されたスイッチング素子と、上記絵素電極に対向配置されて上記絵素電極との間で液晶補助容量を形成する補助容量配線とを備えている液晶表示装置であって、電源オフ動作の開始から電源オフ動作の完了までの少なくとも一部の期間に、上記補助容量配線の電位である補助容量電位の降下速度が、上記対向電極の電位である対向電位の降下速度よりも速くなることを特徴としている。

【発明の効果】

【0015】

10

上記の構成によれば、液晶補助容量の両電極（絵素電極および補助容量配線）の電位が当該両電極間の電位差を保つように変化するため、補助容量電位を迅速に低下させることにより絵素電極の電位を迅速に低下させることができる。その結果、スイッチング素子のゲート端子とソース端子との電位差を大きくできるので、スイッチング素子のリーク電流を増加させて絵素電極の電荷をソースバスラインにより効果的に逃がすことができる。これにより、電源オフ時に絵素に電荷が蓄積されにくい、簡易な構成の液晶表示装置を実現できる。

【図面の簡単な説明】

【0016】

20

【図1】本発明の実施形態1にかかる液晶表示装置の概略構成を示す説明図である。

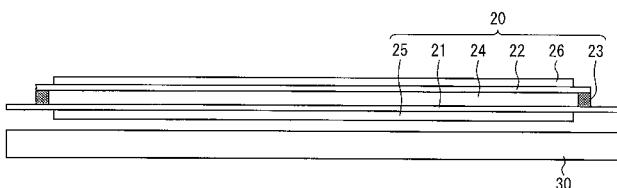

【図2】図1に示した液晶表示装置に備えられる液晶パネルの構成を示す説明図である。

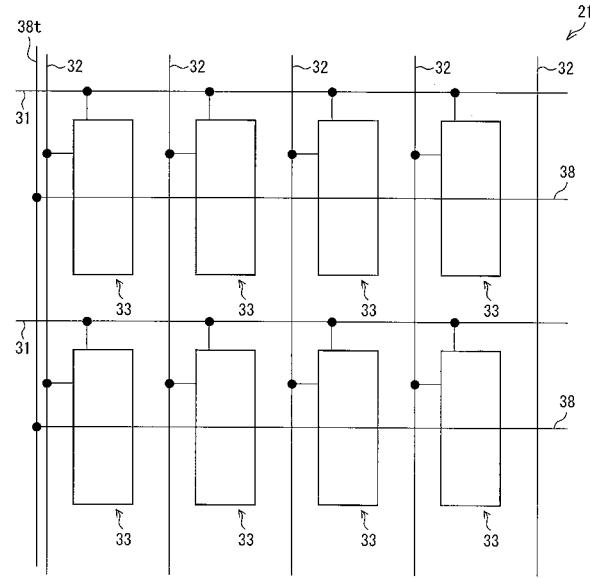

【図3】図2に示した液晶パネルに備えられるTFT基板の構成を示す説明図である。

【図4】図2に示した液晶パネルに備えられる絵素の構成を示す説明図である。

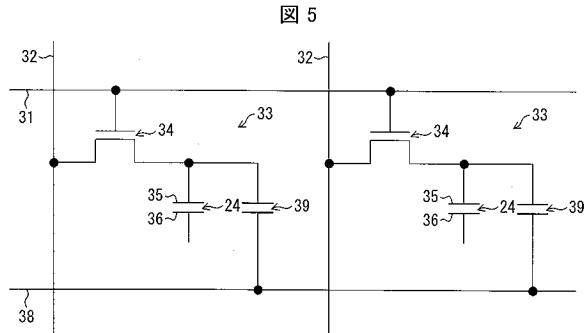

【図5】図4に示した絵素の等価回路図である。

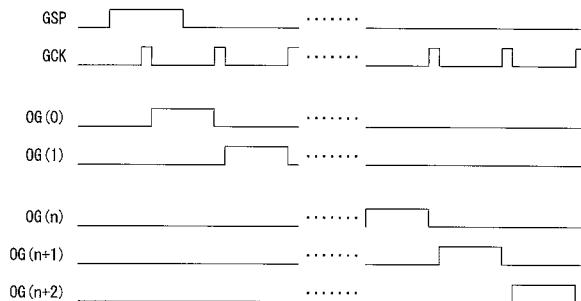

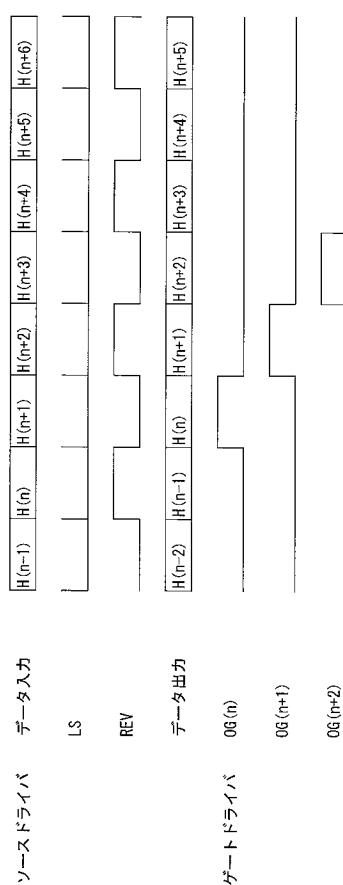

【図6】図7に示したゲートドライバの出力信号の波形を示す説明図である。

【図7】図1に示した液晶表示装置におけるソースバスラインおよびゲートバスラインに対する電圧印加タイミングを示す説明図である。

【図8】図1に示した液晶表示装置における各絵素への印加電圧の例を示す説明図である。

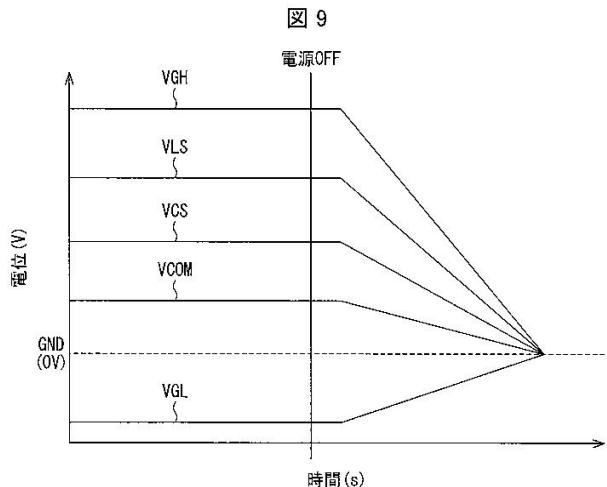

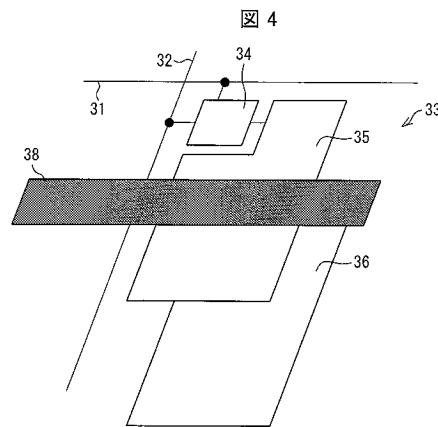

【図9】図1に示した液晶表示装置における電源オフ時の各部の電圧波形を概略的に示したグラフである。

30

【図10】本発明の実施形態2にかかる液晶表示装置のCS電源回路に備えられる電源切替回路の構成を示す説明図である。

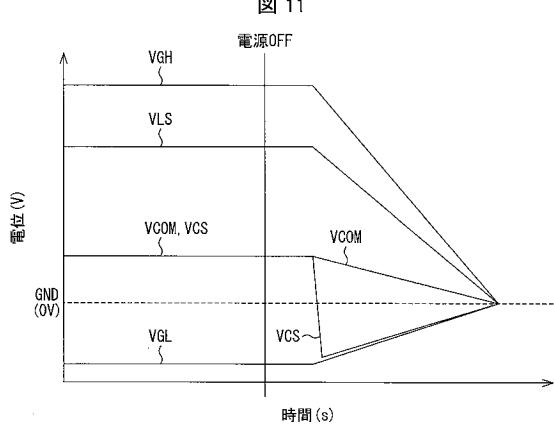

【図11】本発明の実施形態2にかかる液晶表示装置における電源オフ時の各部の電圧波形を概略的に示したグラフである。

【図12】本発明の実施形態3にかかる液晶表示装置のCS電源回路に備えられる電源切替回路の構成を示す説明図である。

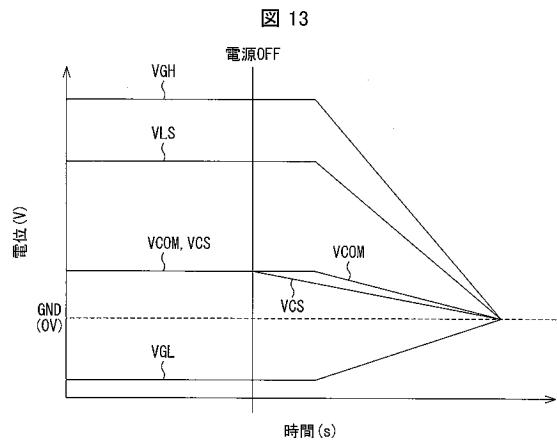

【図13】本発明の実施形態3にかかる液晶表示装置における電源オフ時の各部の電圧波形を概略的に示したグラフである。

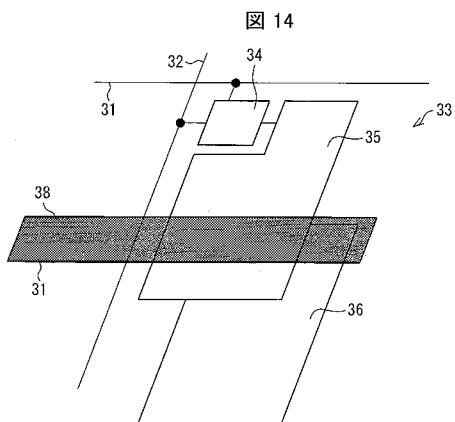

【図14】本発明の実施形態4にかかる液晶表示装置における絵素の構成を示す説明図である。

40

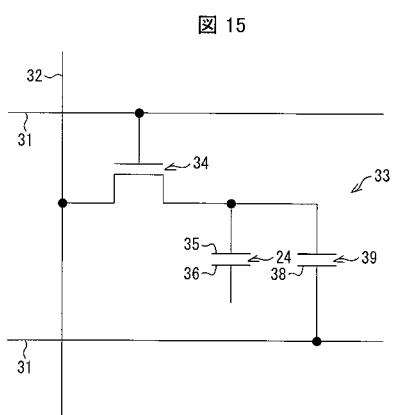

【図15】本発明の実施形態4にかかる液晶表示装置に備えられる絵素の透過回路図である。

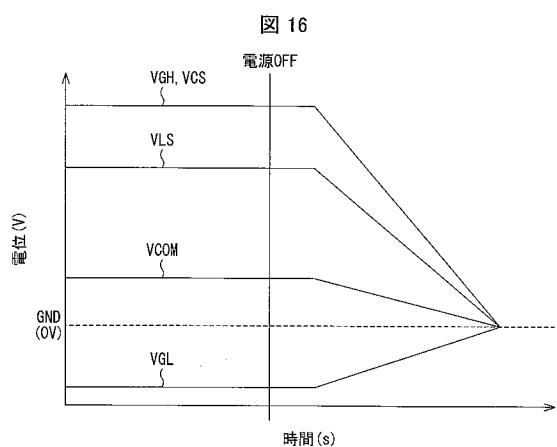

【図16】本発明の実施形態4にかかる液晶表示装置における電源オフ時の各部の電圧波形を概略的に示したグラフである。

【図17】TFTの種類に応じたオフリーク電流特性を示す説明図である。

【発明を実施するための形態】

【0017】

〔実施形態1〕

本発明の一実施形態について説明する。

50

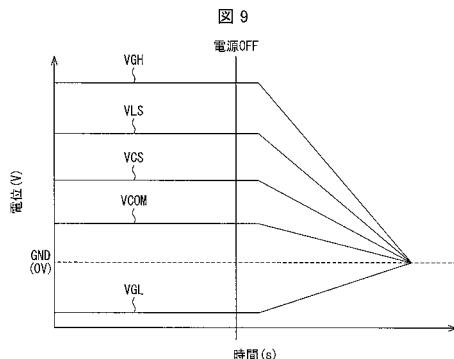

## 【0018】

図1は本実施形態にかかる液晶表示装置1の概略構成を示す説明図であり、図2は液晶表示装置1に備えられる液晶パネル20の構成を示す説明図である。

## 【0019】

図2に示したように、液晶パネル20は、スペーサ23を介して互いに対向配置されたTFT基板21および対向基板22と、TFT基板21と対向基板22との間に封入された液晶材料からなる液晶層24と、TFT基板21の裏面側（対向基板22との対向面とは反対側の面側）に配置された第1偏光板25と、対向基板22の表面側（TFT基板21との対向面とは反対側の面側）に配置された第2偏光板26とを備えている。また、液晶パネル20の裏面側には、バックライト30が配置されている。バックライト30の構成は特に限定されるものではなく、例えば、光源と、反射板と、1または複数の光学シートとを備えた、従来から公知のバックライトを用いることができる。

10

## 【0020】

第1偏光板25は、バックライト30から照射された光のうち、当該第1偏光板25の偏光軸方向に応じた偏光を有する光のみを透過させる。また、各絵素の液晶層24には画像データに応じた電圧が印加されるようになっており、これによって各絵素における液晶の複屈折が画像データに応じて変化し、各絵素を通過する光の偏光方向は画像データに応じて変化する。また、第2偏光板26は、液晶層24を通過した光のうち、当該第2偏光板26の偏光軸方向に応じた偏光を有する光のみを透過させる。これにより、液晶パネル20を透過する光の光量を画像データに応じて絵素毎に制御して画像表示を行うようになっている。

20

## 【0021】

また、対向基板22における各絵素（サブピクセル）に対応する領域には、R（赤）、G（緑）、B（青）のいずれかのカラーフィルタが形成されており、R、G、Bの3つの絵素の組み合わせによって1つの画素（ピクセル）が形成されている。これにより、各画素のR、G、Bの透過光量が画像データに応じて画素毎に制御され、画像データに応じた画像が表示される。

20

## 【0022】

図3はTFT基板21の概略構成を示す説明図である。この図に示すように、TFT基板21上には、多数のゲートバスライン31と、各ゲートバスライン31と交差するように配置された多数のソースバスライン32と、ゲートバスライン31とソースバスライン32との交差部毎に設けられた絵素33とが設けられている。また、基板面法線方向から見て各絵素33と重疊する領域には、ゲートバスライン31と略平行なCS配線（補助容量配線）38が配置されている。なお、各CS配線38はCS幹配線38tを介して図1に示したCS電源回路11に接続されている。

30

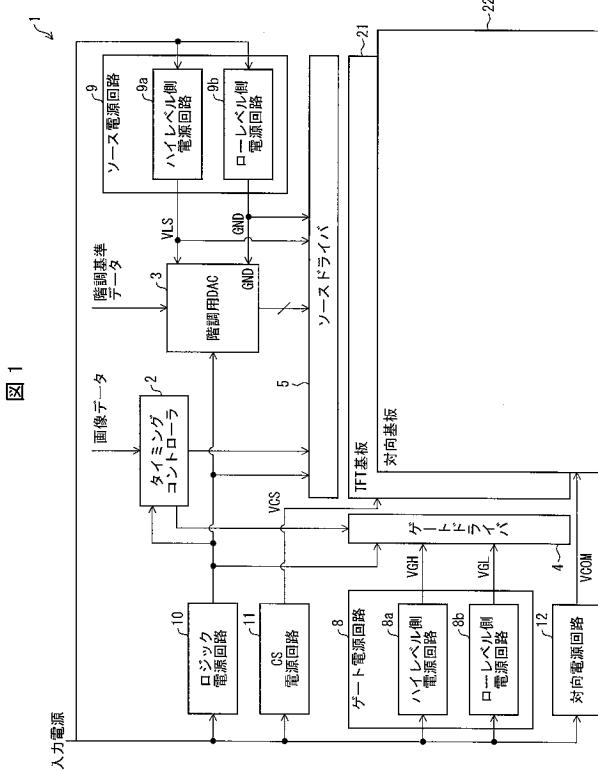

## 【0023】

図4は液晶パネル20に備えられる絵素33の絵素構造を示す説明図である。

## 【0024】

各絵素33は、図4に示すように、スイッチング素子としてのTFT（Thin Film Transistor、薄膜トランジスタ）34と、絵素電極35と、対向電極36とを備えている。また、TFT34のゲート端子はゲートバスライン31に接続されており、ソース端子はソースバスライン32に接続されており、ドレイン端子は絵素電極35に接続されている。また、絶縁膜（図示せず）を介して絵素電極35に対向するようにCS配線38が設けられている。すなわち、本実施形態では、各絵素電極35と対向するように配置されたCS配線38を有する、CSオンコモン（CS on Common）方式の液晶パネル20を用いている。

40

## 【0025】

なお、本実施形態では、TFT34として、インジウムガリウム亜鉛酸化物半導体（酸化物半導体）からなるチャネル層を有するTFTを用いている。ただし、TFT34の構成はこれに限るものではなく、例えば、インジウムガリウム亜鉛酸化物半導体以外の酸化

50

物半導体からなるチャネル層を有するものを用いてもよく、酸化物半導体以外の材質（例えば、アモルファスシリコン、低温ポリシリコンなど）からなるチャネル層を有するものを用いてもよい。

【0026】

また、各ゲートバスライン31はゲートドライバ4に接続されており、各ソースバスライン32はソースドライバ5に接続されており、各CS配線38はCS幹配線38tを介してCS電源回路11に接続されている。また、対向電極36は対向基板22上に配置された対向配線（図示せず）を介して後述する対向電源回路12に接続されている。

【0027】

画像表示時には、ゲートドライバ4が書込対象のゲートバスライン31を周期的に切り替え、ソースドライバ5がゲートドライバ4と同期して、書込対象として選択されているゲートバスライン31に接続されている各絵素33に対応するソースバスライン32に画像データの階調値に応じた印加電圧を印加する。これにより、各絵素33の液晶層24に画像データに応じた電圧を印加して液晶分子の配向方向を制御し、表示を行う。

【0028】

図5は、絵素33の等価回路図である。TFT34のゲート端子の電位が当該TFT34のソース端子の電位よりも所定値以上高くなるとTFT34がオンになり、ソース端子とドレイン端子との間を電流が流れ、ソースバスライン32の電位が液晶容量（液晶層24）に印加される。なお、図5に示した等価回路図では、絵素電極35、対向電極36、および液晶層24はコンデンサ（液晶容量）として表されている。また、上述したように、絵素電極35に対して絶縁層（図示せず）を介して対向する位置にはCS配線38が設けられており、これによって絵素電極35とCS配線38との間に液晶補助容量（結合容量）39が形成されている。液晶補助容量39は、図5に示すように、液晶容量（絵素電極35、液晶層24、および対向電極36）に対して並列に配置され、各絵素33に印加された画像データに応じた電位を次回の電圧印加（次フレーム）まで保持するための容量として機能する。

【0029】

なお、本実施形態では、R、G、Bの絵素を備えているものとしているが、これに限るものではなく、他の色の絵素を備えていてもよい。

【0030】

図1に示したように、液晶表示装置1は、液晶パネル20およびバックライト30に加えて、タイミングコントローラ2、階調用DAC（階調用デジタルアナログコンバータ）3、ゲートドライバ4、ソースドライバ5、ゲート電源回路8、ソース電源回路9、ロジック電源回路10、CS電源回路（補助容量電源回路）11、および対向電源回路12を備えている。

【0031】

ロジック電源回路10は、外部から供給される入力電位Vinをタイミングコントローラ2、階調用DAC3、ゲートドライバ4、およびソースドライバ5に備えられるロジック回路（図示せず）の駆動電圧に応じた電位に変換して各ロジック回路に出力する。

【0032】

ゲート電源回路8は、ゲートドライバ4に駆動電力を供給するものであり、外部から供給される入力電位Vinをゲートドライバ4のハイレベル側電位VGHに変換してゲートドライバ4に供給するハイレベル側電源回路8aと、ローレベル側電位VGLに変換してゲートドライバ4に供給するローレベル側電源回路8bとを備えている。なお、ハイレベル側電源回路8aおよびローレベル側電源回路8bの構成は特に限定されるものではなく、従来から公知の電源回路を用いることができる。

【0033】

ソース電源回路9は、ソースドライバ5に駆動電力を供給するものであり、外部から供給される入力電位Vinをソースドライバ5のハイレベル側電位VLSに変換してソースドライバ5に供給するハイレベル側電源回路9aと、ローレベル側電位（本実施形態では

10

20

30

40

50

グランド ( GND ) 電位 ) に変換してソースドライバ 5 に供給するローレベル側電源回路 9 b とを備えている。なお、ハイレベル側電源回路 9 a は、階調用 DAC 3 にもアナログ電源電力を供給する。また、ローレベル側電源回路 9 b は、階調用 DAC 3 のグランド ( GND ) 端子にも電力を供給する。なお、本実施形態では、ローレベル側電源回路 9 b からソースドライバ 5 への出力電位をグランド電位としているが、これに限るものではなく、例えばグランド電位よりも低い電位としてもよい。

【 0034 】

CS 電源回路 11 は、外部から供給される入力電位  $V_{in}$  を所定の CS 電位 ( 補助容量電位 )  $V_{CS}$  に変換し、CS 幹配線 38 t を介して各 CS 配線 38 に供給する。なお、本実施形態では、電源オン期間 ( 電源オフ動作開始前 ) の CS 電位を 9 V に設定している。

10

【 0035 】

対向電源回路 12 は、外部から供給される入力電位  $V_{in}$  を所定の対向電位  $V_{COM}$  ( 本実施形態では 6 V ) に変換して各対向電極 36 に供給する。

【 0036 】

タイミングコントローラ 2 は、外部 ( 例えば液晶表示装置 1 の制御部 ) から入力される画像データに基づいてゲートドライバ 4 およびソースドライバ 5 の動作を制御するための制御信号を生成し、ゲートドライバ 4 およびソースドライバ 5 に出力する。

【 0037 】

ゲートドライバ 4 は、タイミングコントローラ 2 から入力される制御信号に基づいて、液晶パネル 20 の TFT 基板 21 に備えられる各ゲートバスライン 31 に印加する電圧を制御することにより、書込対象のゲートバスライン 31 を周期的に切り替える。

20

【 0038 】

図 6 は、ゲートドライバ 4 から各ゲートバスライン 31 への出力信号 OG ( OG ( 0 ) , OG ( 2 ) , ··· ) の信号波形を示したグラフである。この図に示すように、ゲートドライバ 4 は、タイミングコントローラ 2 からゲートスタートパルス GSP が入力された後、タイミングコントローラ 2 からゲートクロック信号 GCK のパルスが入力される毎に、ゲートバスライン 31 に 1 本ずつ順次ハイレベル電圧を印加する。ただし、ゲートドライバ 4 の駆動波形はこれに限るものではなく、従来から公知の駆動方法を用いることができる。

【 0039 】

階調用 DAC 3 は、外部 ( 例えば液晶表示装置 1 の制御部 ) から入力される階調基準データ ( 出力電圧値データ ) に基づいて、ソースドライバ 5 において階調値に応じた電圧を生成する際に用いられる階調基準電圧を生成し、ソースドライバ 5 に出力する。なお、上記の階調基準データは、液晶パネル毎に異なる絵素の浮遊容量に起因する最適な階調電圧のばらつきを調整するように、例えば液晶表示装置 1 の生産時などに設定される。

30

【 0040 】

ソースドライバ 5 は、タイミングコントローラ 2 から入力される制御信号と、階調用 DAC 3 から入力される階調基準電圧とに基づいて、液晶パネル 20 の TFT 基板 21 に備えられる各ソースバスライン 32 に印加する電圧を制御する。具体的には、ソースドライバ 5 は、各ソースバスライン 32 に印加するための電位 ( 各ソースバスライン 32 に接続された絵素 33 のうち書き込み対象の絵素 33 に印加するための電位 ) を生成し、生成した電位をゲートドライバ 4 による書込対象のゲートバスライン 31 の切替動作と同期したタイミングで各ソースバスライン 32 に印加する。

40

【 0041 】

図 7 は、ソースバスライン 32 およびゲートバスライン 31 に対する電圧印加のタイミングを示す説明図である。この図に示すように、ソースドライバ 5 は、画像データに応じた 1 ゲートバスライン分の電位をタイミングコントローラ 2 から入力されるラッチパルス L S に応じたタイミングで各ソースバスライン 32 に出力する。また、ゲートドライバ 4 は、ソースドライバ 5 の出力タイミングと同期したタイミングでソースドライバ 5 の出力に対応するゲートバスライン 31 への供給電圧をハイレベルに切り替える。すなわち、n

50

ライン目のゲートバスライン 3 1 の電圧がハイレベルである期間中にソースドライバ 5 から各ソースバスライン 3 2 に  $n$  ライン目のデータが出力される。この処理を全てのゲートバスライン 3 1 について順次行うことで、各絵素 3 3 に画像データに応じた電荷をチャージして一画面分の表示を行う。なお、ソースドライバ 5 は、タイミングコントローラ 2 から入力される極性反転信号 R E V に基づいて、1 ゲートバスライン毎に各ソースバスライン 3 2 への出力電圧の極性を反転させる。

【0042】

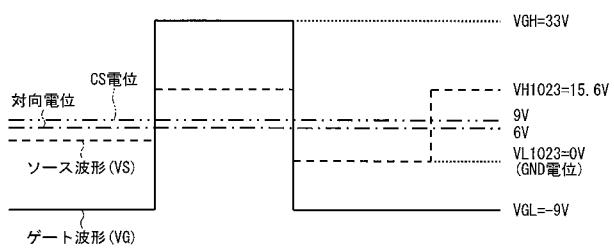

図 8 は、本実施形態にかかる液晶表示装置 1 における各絵素 3 3 に印加される電圧波形の一例を示す説明図である。ゲート波形 ( V G ) は TFT 3 4 のゲート端子に印加される電圧、ソース波形 ( V S ) は TFT 3 4 のソース端子に印加される電圧、対向電位は対向電極 3 6 に印加される電圧、CS 電位は CS 配線 3 8 に印加される電圧を示している。

10

【0043】

この図に示すように、本実施形態では、ゲート端子に印加される電圧はハイレベル側が 3 3 V、ローレベル側が - 9 V に設定されている。また、ソース端子に印加される電圧は、+ 極性の場合の最大値 ( V H 1 0 2 3 ) が 15.6 V、- 極性の場合の最小値 ( V L 1 0 2 3 ) が 0 V ( GND 電位 ) に設定されている。また、対向電位は 6 V に設定されており、CS 電位は対向電位より高い 9 V に設定されている。

【0044】

このように、ゲート端子に印加されるハイレベル側の電圧は、ソース端子の印加電圧にかかわらず TFT 3 4 をオンさせることができるように、ソース端子に印加される電圧の最大値よりも十分高く設定されている。また、ゲート端子に印加されるローレベル側の電圧は、ソース端子の印加電圧にかかわらず TFT 3 4 をオフさせることができるように、ソース端子に印加される電圧の最小値よりも十分低く設定されている。これにより、ゲート端子に印加される電圧がハイレベルである場合に TFT 3 4 がオンしてソース端子とドレイン端子との間を電流が流れ、絵素電極 3 5 の電位がソースバスライン 3 2 の電位と等しくなって絵素 3 3 への書き込みが行われる。

20

【0045】

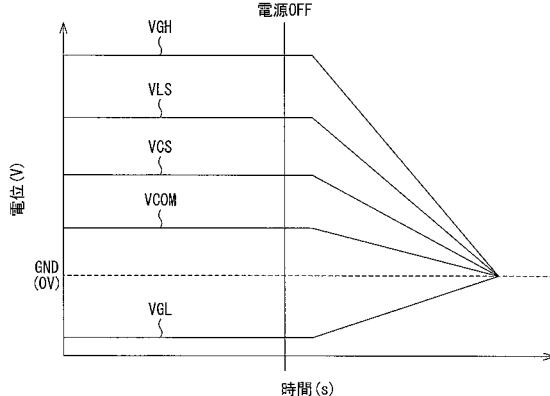

図 9 は、電源オフ時の各部の電圧波形を概略的に示したグラフである。この図に示すように、液晶表示装置 1 の電源がオフされると、電源オフ直後の短い期間は液晶表示装置 1 に内蔵されているコンデンサ等により各部の電圧は維持されるが、その後はグランド電位まで変化していく。

30

【0046】

この際、本実施形態では、通常時 ( 液晶表示装置 1 の電源がオンされている期間中 ) の CS 電位 V CS を対向電位 V COM よりも高く設定しているので、電源オフ時の CS 電位 V CS の単位時間当たりの降下量は対向電位 V COM の単位時間あたりの降下量よりも大きくなる。すなわち、CS 電位 V CS の降下速度が対向電位 V COM の降下速度よりも速くなる。そして、CS 電位 V CS の降下速度が速いことにより、液晶補助容量 3 9 は極板間の電位差を保つように作用するので液晶補助容量 3 9 における絵素電極 3 5 側の電位が下がり、それによって絵素電極 3 5 の電位が低下する。

40

【0047】

これにより、TFT 3 4 におけるゲート - ソース間の電位差が大きくなり、TFT 3 4 のリーク電流が増大して絵素電極 3 5 に蓄積された電荷がソースバスライン 3 2 に抜けやすくなる。

【0048】

すなわち、上述した図 17 に示したように、TFT は、ゲート - ソース間の電位差が大きいほどリーク電流が大きくなるという特性を有している。このため、絵素電極 3 5 の電位を低下させて TFT 3 4 のゲート - ソース間の電位差を増加させることにより、TFT 3 4 のリーク電流を増加させて絵素電極 3 5 の電荷をソースバスライン 3 2 に逃がすことができる。

【0049】

50

以上のように、本実施形態にかかる液晶表示装置1では、CS電源回路11が、通常時(液晶表示装置1の電源がオンされている期間中)におけるCS電位VCSを、対向電位VCOMよりも高く設定(グランド電位との電位差が大きくなるように設定)する。

【0050】

これにより、電源オフ時に絵素電極35の電位を低下させてTFT34のゲート-ソース間の電位差を大きくすることができるので、TFT34のリーク電流を増加させて絵素電極35に蓄積された電荷をソースバスライン32に逃がすことができる。したがって、電源オフ後に絵素電極35に電荷が蓄積され続けることにより焼き付き等の不具合が生じることを防止できる。

【0051】

特に、本実施形態では、TFT34として、オフリーク電流が非常に少ないという特性を有するインジウムガリウム亜鉛酸化物半導体からなるTFTを用いているため、電源オフ時に絵素電極35に電荷が蓄積されやすい傾向があるが、インジウムガリウム亜鉛酸化物半導体からなるTFTを用いた場合であっても電源オフ時に絵素電極35に蓄積される電荷を低減できる。

【0052】

なお、本実施形態では、通常時(電源オン時)のCS電位VCSを9V、対向電位VCOMを6Vに設定しているが、これら両電位の値はこれに限るものではなく、少なくともCS電位VCSの方が対向電位VCOMよりも高くなるように、液晶パネル20の特性等に応じて適宜設定すればよい。

【0053】

また、従来の液晶表示装置では、例えば上述した特許文献1のように、電源オフ時に絵素電極から電荷を抜くための処理を行う回路と、当該回路を電源供給が遮断された状態でも駆動できるようにするためのコンデンサ等の充電手段とを設ける必要があった。これに對して、本実施形態によれば、CS電位VCSを対向電位VCOMよりも高く設定するためのCS電源回路11を設けるだけで上記回路および上記充電手段を設けなくても電源オフ時に各絵素の電荷を抜くことができる。したがって、液晶表示装置1の製造コストを低減することができる。

【0054】

ただし、本実施形態にかかる液晶表示装置1において、駆動時の印加電圧を上述したように設定するとともに、電源オフ時に絵素電極から電荷を抜くための処理を行う回路と、当該回路を電源供給が遮断された状態でも駆動できるようにするためのコンデンサ等の充電手段とを設け、電源オフ時に各絵素に蓄積される電荷を低減するための電位(グランド電位またはそれに近い電位)を各絵素に書き込む処理を行うようにしてもよい。

【0055】

また、本実施形態では、液晶表示装置1がバックライト30から出射される光を用いて表示を行う透過型の液晶表示装置である場合について説明したが、これに限るものではない。例えば、外部からの入射光を反射させて表示光として用いる反射型の液晶表示装置であってもよく、透過型の液晶表示装置の機能と反射型の液晶表示装置の機能とを併せ持つ半透過型の液晶表示装置であってもよい。

【0056】

また、本実施形態では、絵素電極がTFT基板21に備えられ、対向電極が対向基板22に備えられた液晶表示装置について説明したが、これに限らず、絵素電極および対向電極の両方が同一基板に備えられた構成であってもよい。

【0057】

〔実施形態2〕

本発明の他の実施形態について説明する。なお、説明の便宜上、実施形態1と共通の機能を有する部材については実施形態1と同じ符号を付し、その説明を省略する。

【0058】

実施形態1では、通常時(電源オン時)のCS電位VCSを対向電位VCOMよりも高

10

20

30

40

50

く設定しておくことにより、電源オフ時におけるCS電位V<sub>CS</sub>の降下速度を対向電位V<sub>COM</sub>の降下速度よりも速くする構成について説明した。これに対して、本実施形態では、通常時（電源オン時）にはCS電位V<sub>CS</sub>と対向電位V<sub>COM</sub>とを同値に設定しておき、電源オフ時（電源オフ動作期間中）にCS電位V<sub>CS</sub>を対向電位V<sub>COM</sub>よりも低い電位に切り替えることにより、電源オフ動作の開始から終了までの少なくとも一部の期間におけるCS電位V<sub>CS</sub>の降下速度を対向電位V<sub>COM</sub>の降下速度よりも速くする。

#### 【0059】

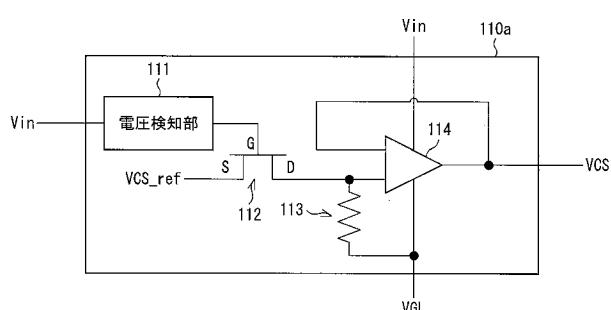

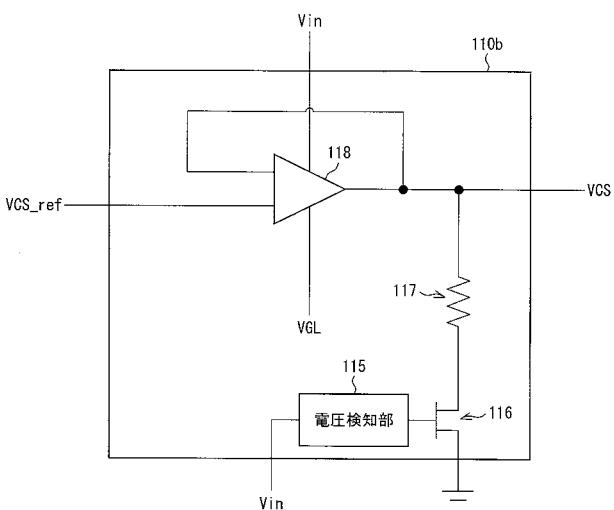

具体的には、本実施形態にかかる液晶表示装置1は、CS電源回路11の出力段に、図10に示す電源切替回路110aを備えている。

#### 【0060】

図10に示すように、電源切替回路110aは、電圧検知部111、MOSFET112、抵抗113、およびオペアンプ114を備えている。

#### 【0061】

電圧検知部111は、入力電源とMOSFET112のゲート端子Gとの間に接続されており、入力電位V<sub>in</sub>（入力電源電圧）に応じてMOSFET112の動作を制御する。具体的には、電圧検知部111は、入力電位V<sub>in</sub>が所定値以上である場合にはMOSFET112のソース-ドレイン間を導通させ、入力電位V<sub>in</sub>が所定値未満である場合にはMOSFET112のソース-ドレイン間を遮断させるようにゲート端子Gに対する出力電圧を制御する。

#### 【0062】

MOSFET112のソース端子SにはCS電源回路11で生成されたCS基準電位V<sub>CS\_ref</sub>（本実施形態ではV<sub>CS\_ref</sub>=V<sub>COM</sub>）が供給されており、ドレイン端子Dはオペアンプ114の入力端子に接続されている。したがって、入力電位V<sub>in</sub>が所定値以上である場合にはCS基準電位V<sub>CS\_ref</sub>がオペアンプ114に入力される。また、入力電位V<sub>in</sub>が所定値未満である場合にはMOSFET112のソース-ドレイン間は遮断される。

#### 【0063】

抵抗113は、一端側がMOSFET112とオペアンプ114との間に接続され、他端側がゲートドライバ4のローレベル側電源回路8b（低電位供給源）の出力側に接続されている。

#### 【0064】

オペアンプ114は、ボルテージフォロワ回路になっており、当該オペアンプ114に対する入力電位と同じ電位をCS幹配線38tに出力するようになっている。したがって、オペアンプ114の出力電位は、液晶表示装置1の入力電位V<sub>in</sub>が所定値以上の場合にはV<sub>CS\_ref</sub>となり、所定値未満の場合にはV<sub>GL</sub>となる。

#### 【0065】

図11は、CS基準電位V<sub>CS\_ref</sub>を対向電位V<sub>COM</sub>と同電位に設定した場合の、電源オフ時の各部の電位の変化を概略的に示したグラフである。

#### 【0066】

この図に示すように、液晶表示装置1の電源がオン状態である期間中にはCS電位V<sub>CS</sub>は対向電位V<sub>COM</sub>と同値（V<sub>CS\_ref</sub>=V<sub>COM</sub>）に設定されているが、電源がオフされてMOSFET112が遮断されると、CS電位V<sub>CS</sub>はゲートドライバ4のローレベル側電位V<sub>GL</sub>に引き下げられる。

#### 【0067】

この際、CS電位V<sub>CS</sub>の降下速度は少なくともMOSFET112が遮断されてV<sub>GL</sub>まで引き下げられる期間中には対向電位V<sub>COM</sub>の降下速度よりも速くなる。

#### 【0068】

このため、CS電位V<sub>CS</sub>の降下速度が速いことにより、液晶補助容量39は極板間の電位差を保つように作用して液晶補助容量39における絵素電極35側の電位が下がり、絵素電極35の電位が低下する。これにより、TFT34におけるゲート-ソース間の電

10

20

30

40

50

位差が大きくなり、TFT34のリーク電流が増大して絵素電極35に蓄積された電荷がソースバスライン32に抜けやすくなる。

【0069】

以上のように、本実施形態では、電源オフ時にCS幹配線38tに対する出力電位を対向電位VCOMよりも低い電位に切り替えることにより、電源オフ動作の開始から電源オフ動作の完了までの少なくとも一部の期間におけるCS電位VCSの降下速度を対向電位VCOMの降下速度よりも速くする。

【0070】

これにより、実施形態1と同様、TFT34のゲート-ソース間の電位差を大きくして絵素電極35の電荷がソースバスライン32に逃げやすくなることができる。

10

【0071】

なお、本実施形態では、電源オフ時にオペアンプ114にゲートドライバ4のローレベル側電位VGLが入力される構成としているが、これに限るものではなく、少なくとも対向電位VCOMよりも低い電位が入力される構成であればよい。例えば、電源オフ時にオペアンプ114の入力側をグランド（低電位供給源）に接続してもよく、出力電位が対向電位VCOMよりも低い各種ロジック電源回路等（低電位供給源）に接続してもよい。

20

【0072】

また、本実施形態では、通常時（電源がオンされている期間中）におけるCS電位VCSの値（VCS\_ref）を対向電位VCOMと同値に設定しているが、これに限るものではなく、対向電位VCOMと異なる値であってもよい。通常時におけるCS電位VCSの値（VCS\_ref）を対向電位VCOMと異なる値に設定する場合、電源オフ時にMOSFET112が遮断されたときにオペアンプ114に入力される電位が、CS電位VCSの降下速度の方が対向電位VCOMの降下速度よりも速くなる電位になるように、抵抗113の他端側の接続先（オペアンプ114に対する電位供給源）を選定すればよい。

20

【0073】

〔実施形態3〕

本発明のさらに他の実施形態について説明する。なお、説明の便宜上、上述した実施形態と共に通の機能を有する部材については当該実施形態と同じ符号を付し、その説明を省略する。

30

【0074】

本実施形態では、通常時（液晶表示装置1の電源がオンされている期間中）にはCS電位VCSと対向電位VCOMとを同値に設定しておき、電源オフ時にCS電位VCSの降下を対向電位VCOMの降下よりも早いタイミングで開始させ、それによって電源オフ動作の開始から終了までの少なくとも一部の期間におけるCS電位VCSの降下速度を対向電位VCOMの降下速度よりも速くする。

30

【0075】

具体的には、本実施形態にかかる液晶表示装置1は、CS電源回路11の出力段に、図12に示す電源切替回路110bを備えている。

【0076】

図10に示すように、電源切替回路110bは、電圧検知部115、MOSFET116、抵抗117、およびオペアンプ118を備えている。

40

【0077】

オペアンプ118は、ボルテージフォロワ回路になっており、当該オペアンプ118に対する入力電位と同じ電位を出力するようになっている。また、オペアンプ118の入力側には、CS電源回路11で生成されたCS基準電位VCS\_ref（本実施形態ではVCS\_ref = VCOM）が入力されるようになっている。したがって、オペアンプ118の出力電位はVCS\_refである。

【0078】

電圧検知部115は、入力電源とMOSFET112のゲート端子Gとの間に接続されており、入力電位Vin（入力電源電圧）に応じてMOSFET112の動作を制御する

50

。具体的には、電圧検知部 111 は、入力電位  $V_{in}$  が所定値以上である場合には MOSFET 112 のソース - ドレイン間を遮断させ、入力電位  $V_{in}$  が所定値未満である場合には MOSFET 112 のソース - ドレイン間を導通させるようにゲート端子 G に対する出力電圧を制御する。

【0079】

MOSFET 112 のソース端子 S はグランドに接続されており、ドレイン端子 D は抵抗 117 を介してオペアンプ 114 の出力側と CS 幹配線 38t との間に接続されている。したがって、入力電位  $V_{in}$  が所定値以上である場合には CS 幹配線 38t の電位はオペアンプ 114 から出力される CS 基準電位  $V_{CS\_ref}$  となり、入力電位  $V_{in}$  が所定値未満である場合にはグランド電位になる。

10

【0080】

図 13 は、CS 基準電位  $V_{CS\_ref}$  を対向電位  $V_{COM}$  と同電位に設定した場合の、電源オフ時の各部の電位の変化を概略的に示したグラフである。

【0081】

この図に示すように、液晶表示装置 1 の電源がオン状態である期間中には CS 電位  $V_{CS}$  は対向電位  $V_{COM}$  と同値の  $V_{CS\_ref}$  に設定されているが、電圧検知部 115 によって入力電位の低下（液晶表示装置 1 の電源オフ）が検出されて MOSFET 116 が導通すると、CS 電位  $V_{CS}$  はグランド電位に向けて降下し始める。

【0082】

この際、対向電位  $V_{COM}$  は、電源オフ直後の所定期間は液晶表示装置 1 に内蔵されているコンデンサ等により電源オン時の電位に維持され、その後にグランド電位に向けて降下し始める。

20

【0083】

したがって、CS 電位  $V_{CS}$  の降下の方が対向電位  $V_{COM}$  の降下よりも早いタイミングで開始され、少なくとも入力電位  $V_{in}$  の低下が検知された直後には CS 電位  $V_{CS}$  の降下速度の方が対向電位  $V_{COM}$  の降下速度よりも速くなる。

【0084】

このため、CS 電位  $V_{CS}$  の降下速度が速いことにより、液晶補助容量 39 は極板間の電位差を保つように作用して液晶補助容量 39 における絵素電極 35 側の電位が下がり、絵素電極 35 の電位が低下する。これにより、TFT 34 におけるゲート - ソース間の電位差が大きくなり、TFT 34 のリーク電流が増大して絵素電極 35 に蓄積された電荷がソースバスライン 32 に抜けやすくなる。

30

【0085】

以上のように、本実施形態では、電源オフ時に CS 電位  $V_{CS}$  の降下開始タイミングを対向電位  $V_{COM}$  の降下開始タイミングよりも早く生じさせることにより、電源オフ動作の開始から電源オフ動作の完了までの少なくとも一部の期間における CS 電位  $V_{CS}$  の降下速度を対向電位  $V_{COM}$  の降下速度よりも速くする。

【0086】

これにより、実施形態 1, 2 と同様、TFT 34 のゲート - ソース間の電位差を大きくして絵素電極 35 の電荷がソースバスライン 32 に逃げやすくすることができる。

40

【0087】

なお、本実施形態では、通常時（電源がオンされている期間中）における CS 電位  $V_{CS}$  の値（ $V_{CS\_ref}$ ）を対向電位  $V_{COM}$  と同値に設定しているが、これに限るものではなく、対向電位  $V_{COM}$  と異なる値であってもよい。

【0088】

また、本実施形態では、電源オフ時に CS 幹配線 38t をグランドに接続する構成しているが、これに限るものではなく、少なくとも対向電位  $V_{COM}$  よりも低い電位源に接続する構成であればよい。例えば、電源オフ時に CS 幹配線 38t を出力電位が対向電位  $V_{COM}$  よりも低い各種ロジック電源回路に接続してもよい。

【0089】

50

## 〔実施形態4〕

本発明のさらに他の実施形態について説明する。なお、説明の便宜上、上述した実施形態と共に機能を有する部材については当該実施形態と同じ符号を付し、その説明を省略する。

## 【0090】

上述した各実施形態では、CS電源回路11からCS配線38にCS電位VCSを供給していた。これに対して、本実施形態では、CS配線38がゲートバスライン31に接続された、CSオンゲート(CS on Gate)方式の液晶パネル20を用いる。

## 【0091】

図14は本実施形態にかかる液晶表示装置1に備えられる液晶パネル20の絵素33の構成を示す説明図であり、図15はその等価回路図である。

10

## 【0092】

図14および図15に示したように、CS配線38は、当該CS配線38に対向配置された絵素33を駆動するゲートバスライン31に隣接するゲートバスライン31に接続されている。なお、本実施形態では、CS配線38の電位はゲートドライバ4によって制御されるので、CS電源回路11は備えられていない。

## 【0093】

図16は、本実施形態にかかる液晶表示装置1における電源オフ時の各部の電位の変化を概略的に示したグラフである。

20

## 【0094】

図16に示すように、液晶表示装置1の電源がオフされると、電源オフ直後の短い期間は液晶表示装置1に内蔵されているコンデンサ等により各部の電圧は維持されるが、その後はグランド電位まで変化していく。また、本実施形態では、CS配線38がゲートバスライン31に接続されており、各ゲートバスライン31には電源オフ時にはハイレベル側電位VGHが供給されるようになっている。

30

## 【0095】

このため、CS電位VCHは、電源オフ時には対向電位VCOMよりも高い電位からグランド電位に向かって低下していくので、電源オフ時のCS電位VCSの降下速度は、実施形態1と同様、対向電位VCOMの降下速度よりも速くなる。そして、CS電位VCSの降下が速いことにより、液晶補助容量39は極板間の電位差を保つように作用して液晶補助容量39における絵素電極35側の電位が下がり、絵素電極35の電位が低下する。

30

## 【0096】

これにより、TFT34におけるゲート-ソース間の電位差が大きくなり、TFT34のリーク電流が増大して絵素電極35に蓄積された電荷がソースバスライン32に抜けやすくなる。

## 【0097】

## 〔まとめ〕

本発明の態様1にかかる液晶表示装置は、複数のゲートバスラインと、上記ゲートバスラインと交差する複数のソースバスラインと、上記ゲートバスラインと上記ソースバスラインとの交差部毎に設けられた絵素とを備え、上記絵素が、液晶層を介して対向配置された絵素電極および対向電極と、ゲート端子が上記ゲートバスラインに接続され、ソース端子が上記ソースバスラインに接続され、ドレイン端子が上記絵素電極に接続されたスイッチング素子と、上記絵素電極に対向配置されて上記絵素電極との間で液晶補助容量を形成する補助容量配線とを備えている液晶表示装置であって、電源オフ動作の開始から電源オフ動作の完了までの少なくとも一部の期間に、上記補助容量配線の電位である補助容量電位の降下速度が、上記対向電極の電位である対向電位の降下速度よりも速くなることを特徴としている。

40

## 【0098】

上記の構成によれば、液晶補助容量の両電極(絵素電極および補助容量配線)の電位が当該両電極間の電位差を保つように変化するため、補助容量電位を迅速に低下させること

50

により絵素電極の電位を迅速に低下させることができる。その結果、スイッチング素子のゲート端子とソース端子との電位差を大きくできるので、スイッチング素子のリーク電流を増加させて絵素電極の電荷をソースバスラインにより効果的に逃がすことができる。これにより、電源オフ時に絵素に電荷が蓄積されにくい、簡易な構成の液晶表示装置を実現できる。

【0099】

本発明の態様2にかかる液晶表示装置は、上記態様1において、電源オフ動作開始前の上記補助容量電位が、上記対向電位よりも高い電位に設定されている構成である。

【0100】

上記の構成によれば、電源オフ動作開始前の補助容量電位が対向電位よりも高い電位に設定されているので、電源オフ動作開始後の補助容量電位の降下速度は対向電位の降下速度よりも速くなる。これにより、絵素電極の電位を迅速に低下させてスイッチング素子のゲート端子とソース端子との電位差を大きくし、スイッチング素子のリーク電流を増加させて絵素電極の電荷をソースバスラインにより効果的に逃がすことができる。

10

【0101】

本発明の態様3にかかる液晶表示装置は、上記態様1において、電源オフ動作開始前の上記補助容量電位が上記対向電位と同電位または上記対向電位よりも高い電位に設定されており、電源オフ動作の開始から電源オフ動作の完了までの少なくとも一部の期間に、上記補助容量配線を、対向電位よりも低い電位を供給する低電位供給源に接続する電源切替回路を備えている構成である。

20

【0102】

上記の構成によれば、電源オフ動作期間中に補助容量配線を対向電位よりも低い電位を供給する低電位供給源に接続することにより、補助容量電位の降下速度を対向電位の降下速度よりも速くできる。これにより、絵素電極の電位を迅速に低下させてスイッチング素子のゲート端子とソース端子との電位差を大きくし、スイッチング素子のリーク電流を増加させて絵素電極の電荷をソースバスラインにより効果的に逃がすことができる。

30

【0103】

本発明の態様4にかかる液晶表示装置は、上記態様1において、入力電源電圧が所定値以下に低下したことを検知する電圧検知部と、上記電圧検知部によって入力電源電圧が所定値以下に低下したことが検知された後、上記対向電位が降下開始する前に、上記補助容量配線を、上記対向電位よりも低い電位を供給する低電位供給源に接続する電源切替回路とを備えている構成である。

【0104】

上記の構成によれば、少なくとも電源オフ動作の開始から対向電位の降下開始までの期間においては、補助容量電位の降下速度を対向電位の降下速度よりも速くできる。これにより、絵素電極の電位を迅速に低下させてスイッチング素子のゲート端子とソース端子との電位差を大きくし、スイッチング素子のリーク電流を増加させて絵素電極の電荷をソースバスラインにより効果的に逃がすことができる。

40

【0105】

本発明の態様5にかかる液晶表示装置は、上記態様1において、上記補助容量配線は、上記ゲートバスラインに接続されている構成である。すなわち、上記液晶表示装置は、各絵素がCSオンゲート構造を有している構成である。

【0106】

上記の構成によれば、電源オフ時の補助容量電位の降下速度を対向電位の降下速度よりも速くできる。これにより、絵素電極の電位を迅速に低下させてスイッチング素子のゲート端子とソース端子との電位差を大きくし、スイッチング素子のリーク電流を増加させて絵素電極の電荷をソースバスラインにより効果的に逃がすことができる。

【0107】

本発明の液晶表示装置は、上記態様1から5において、上記スイッチング素子は、酸化物半導体からなるチャネル層を有する薄膜トランジスタである構成である。

50

## 【0108】

酸化物半導体からなるチャネル層を備えた薄膜トランジスタは、オフリーク電流が非常に少ないという特性を有しており、液晶表示装置の電源をオフしたときに絵素電極と対向電極との間に電位差が残っていると、電源がオフされている期間中にその電位差が印加され続けることにより焼き付き等の不具合が生じやすい。

## 【0109】

これに対して、上記の構成によれば、電源オフ時に蓄積される絵素電極と対向電極との間の電位差を低減できるので、酸化物半導体からなるチャネル層を備えた薄膜トランジスタを用いている場合であっても絵素電極と対向電極との間に電位差によって焼き付き等の不具合が生じることを防止できる。

10

## 【0110】

本発明は上述した実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能である。すなわち、請求項に示した範囲で適宜変更した技術的手段を組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

## 【産業上の利用可能性】

## 【0111】

本発明は、液晶表示装置に適用でき、スイッチング素子としてオフリーク電流が少ない酸化物半導体等からなる薄膜トランジスタを用いた液晶表示装置に特に好適に適用できる。

20

## 【符号の説明】

## 【0112】

- |                   |                  |    |

|-------------------|------------------|----|

| 1                 | 液晶表示装置           | 30 |

| 4                 | ゲートドライバ          |    |

| 5                 | ソースドライバ          |    |

| 8                 | ゲート電源回路          |    |

| 8 a               | ハイレベル側電源回路       |    |

| 8 b               | ローレベル側電源回路       |    |

| 1 1               | C S 電源回路         |    |

| 1 2               | 対向電源回路           |    |

| 2 0               | 液晶パネル            |    |

| 2 4               | 液晶層              |    |

| 3 1               | ゲートバスライン         |    |

| 3 2               | ソースバスライン         |    |

| 3 3               | 絵素               |    |

| 3 4               | T F T (スイッチング素子) |    |

| 3 5               | 絵素電極             |    |

| 3 6               | 対向電極             |    |

| 3 8               | C S 配線           |    |

| 3 8 t             | C S 幹配線          |    |

| 3 9               | 液晶補助容量           |    |

| 1 1 0 a , 1 1 0 b | 電源切替回路           | 40 |

| 1 1 1 , 1 1 5     | 電圧検知部            |    |

| 1 1 2 , 1 1 6     | M O S F E T      |    |

| 1 1 3 , 1 1 7     | 抵抗               |    |

| 1 1 4 , 1 1 8     | オペアンプ            |    |

【 図 1 】

〔 4 〕

【 四 5 】

【 図 2 】

图 2

【図3】

四 3

〔 図 6 〕

図 6

【図 7】

図 7

【図 8】

図 8

【図 9】

図 9

【図 10】

図 10

【図 11】

図 11

【図 12】

図 12

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G

3/20

6 4 1 C

テーマコード(参考)

|                |                                                                                                                                                                                                                                                                         |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2015068856A</a>                                                                                                                                                                                                                                           | 公开(公告)日 | 2015-04-13 |

| 申请号            | JP2013200444                                                                                                                                                                                                                                                            | 申请日     | 2013-09-26 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 澤辺 大一                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 澤辺 大一                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G02F1/133 G09G3/36 G09G3/20                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G02F1/133.550 G02F1/133.520 G09G3/36 G09G3/20.670.D G09G3/20.642.A G09G3/20.641.C                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZA07 2H193/ZB05 2H193/ZB12 2H193/ZE38 5C006/AA16 5C006/AF67 5C006/BB16 5C006/FA34 5C006/FA51 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD05 5C080/DD27 5C080/EE29 5C080/EE30 5C080/FF11 5C080/FF12 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                               |         |            |

### 摘要(译)

要解决的问题：提供一种液晶显示装置，其中当电源关闭时，电荷几乎不累积在像素中。解决方案：在从断电操作开始到断电操作完成的时段的至少一部分时间内，经由存储电容器布线施加到液晶存储电容器的电位即辅助电位电位VCS的下降速度，设定为比作为施加于电极的电位的对置电位VCOM的下降速度快。9系统技术领域