(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-145950

(P2012-145950A)

(43) 公開日 平成24年8月2日(2012.8.2)

| (51) Int.Cl.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>G02F 1/1343 (2006.01)</b> | GO2F 1/1343 | 2H092       |

| <b>G02F 1/1368 (2006.01)</b> | GO2F 1/1368 | 2H193       |

| <b>G02F 1/133 (2006.01)</b>  | GO2F 1/133  | 5CO06       |

| <b>G09G 3/36 (2006.01)</b>   | GO9G 3/36   | 5CO80       |

| <b>G09G 3/20 (2006.01)</b>   | GO9G 3/20   | 611A        |

審査請求 有 請求項の数 5 O L (全 17 頁) 最終頁に続く

|            |                                     |          |                                                      |

|------------|-------------------------------------|----------|------------------------------------------------------|

| (21) 出願番号  | 特願2012-34672 (P2012-34672)          | (71) 出願人 | 502356528<br>株式会社ジャパンディスプレイイースト<br>千葉県茂原市早野3300番地    |

| (22) 出願日   | 平成24年2月21日 (2012.2.21)              | (74) 代理人 | 110000154<br>特許業務法人はるか国際特許事務所                        |

| (62) 分割の表示 | 特願2007-130624 (P2007-130624)<br>の分割 | (71) 出願人 | 506087819<br>パナソニック液晶ディスプレイ株式会社<br>兵庫県姫路市飾磨区妻鹿日田町1-6 |

| 原出願日       | 平成19年5月16日 (2007.5.16)              | (72) 発明者 | 桶 隆太郎<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内           |

|            |                                     | (72) 発明者 | 小野 記久雄<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内          |

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

**【課題】** 1つの画素が2つのスイッチング素子および2つの画素電極を有する液晶表示装置において、駆動回路の発熱量を低く抑え、かつ、画質の劣化を防ぐ。

**【解決手段】** 第1のスイッチング素子および前記第1のスイッチング素子に接続された第1の画素電極と、第2のスイッチング素子および前記第2のスイッチング素子に接続された第2の画素電極とを有する画素の集合により表示領域が設定されている液晶表示装置であって、1つの画素における前記第1のスイッチング素子と前記第2のスイッチング素子とは、それぞれ、異なる映像信号線に接続されており、1フレーム期間中の、1つの画素の前記第1の画素電極に加わる信号の電位と対向電極に加わる信号の電位との関係と、当該1つの画素の前記第2の画素電極に加わる信号の電位と対向電極に加わる信号の電位との関係とは、一方が正極性の関係であり、他方が負極性の関係である液晶表示装置。

【選択図】 図5

**【特許請求の範囲】****【請求項 1】**

複数本の走査信号線、複数本の映像信号線、複数個のスイッチング素子、および複数個の画素電極を有する第1の基板と、

対向電極を有する第2の基板と、

前記第1の基板と前記第2の基板との間に挟持された液晶材料とを有し、

前記第1の基板は、一対の前記走査信号線と一対の前記映像信号線で囲まれた複数の画素を有し、

前記画素の間には、隣接して2本の前記映像信号線が配置され、

前記画素のそれぞれには、第1のスイッチング素子および前記第1のスイッチング素子に接続された第1の画素電極と、第2のスイッチング素子および前記第2のスイッチング素子に接続された第2の画素電極とを有する液晶表示装置であって、

1つの画素における前記第1のスイッチング素子と前記第2のスイッチング素子とは、それぞれ、異なる映像信号線に接続されており、

前記映像信号線の延在方向には、前記第1のスイッチング素子が第1の映像信号線に接続し、前記第2のスイッチング素子が第2の映像信号線に接続している画素と、前記第2のスイッチング素子が前記第1の映像信号線に接続し、前記第1のスイッチング素子が前記第2の映像信号線に接続している画素とが交互に並んでいることを特徴とする液晶表示装置。

**【請求項 2】**

前記第1の映像信号線と前記第2の映像信号線とは、各映像信号線に接続しているスイッチング素子を有する画素を挟んで配置され、かつ、前記走査信号線の延在方向に並んで隣接している2つの画素の間には、当該2つの画素のうちの一方の画素に対する前記第2の映像信号線と、当該2つの画素のうちの他方の画素に対する前記第1の映像信号線とが配置されていることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

1フレーム期間中の、前記第1の映像信号線に加わる信号の電位と前記対向電極の電位との関係、および前記第2の映像信号線に加わる信号の電位と前記対向電極の電位との関係は、それぞれ、常に正極性の関係または常に負極性の関係のいずれかであり、かつ、一方の関係が常に正極性の関係であるときに、他方の関係が常に負極性の関係であることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 4】**

前記第1の画素電極と前記第2の画素電極のうちの一方の画素電極は、その平面形状が、他方の画素電極を囲む閉じた環状であることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 5】**

前記スイッチング素子は、TFT素子であることを特徴とする請求項1に記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置に関し、特に、1つの画素が異なる映像信号線に接続された2つの画素電極を有する液晶表示装置に適用して有効な技術に関するものである。

**【背景技術】****【0002】**

従来、液晶表示装置には、表示領域が、TFT素子などのスイッチング素子および画素電極を有する画素の集合により設定されているものがあり、そのような液晶表示装置には、VA方式(Vertical Alignment方式)と呼ばれるものがある。

**【0003】**

VA方式の液晶表示装置に用いられる液晶表示パネルは、たとえば、液晶材料を挟持す

10

20

30

40

50

る2枚の基板のうちの一方の基板に、複数本の走査信号線、複数本の映像信号線、複数個のスイッチング素子、および複数個の画素電極が形成され、前記2枚の基板のうちの他方の基板に、対向電極（共通電極と呼ぶこともある。）が形成されている。

#### 【0004】

また、VA方式の液晶表示パネルにおいて、1つの画素の階調（輝度）の制御に用いられるスイッチング素子および画素電極の数は、通常、それぞれ1つずつである。

#### 【0005】

しかしながら、近年、視認性を向上させるために、たとえば、1つの画素の階調（輝度）の制御に用いられるスイッチング素子および画素電極の数を、それぞれ2つずつにしたVA方式の液晶表示装置が提案されている（たとえば、特許文献1を参照）。 10

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

【特許文献1】特開2006-309239号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

前記特許文献1に記載されたような構成のVA方式の液晶表示装置では、たとえば、1つの画素に対して2本の映像信号線を設け、当該1つの画素が有する2つの画素電極を、スイッチング素子を介してそれぞれ異なる映像信号線に接続している。そして、当該1つの画素が有する2つの画素電極のそれぞれに、別個のデータ電圧を印加することで、視認性を向上させている。 20

#### 【0008】

しかしながら、前記特許文献1に記載されたような構成のVA方式の液晶表示装置では、たとえば、1フレーム期間中に1つの画素が有する2つの画素電極に加わる信号が、同じ極性である。なお、前記極性というのは、画素電極に加わった信号の電位と対向電極との電位の関係であり、一般に、画素電極に加わった信号の電位が対向電極の電位よりも高い場合は正極性といい、対向電極の電位よりも低い場合は負極性という。

#### 【0009】

また、前記特許文献1に記載されたような構成のVA方式の液晶表示装置では、たとえば、ドット反転と呼ばれる、1フレーム期間中の各画素の画素電極の極性の関係が市松格子状の関係になる駆動方法で映像や画像を表示することにより、たとえば、フリッカと呼ばれる現象や縦スメアと呼ばれる現象の発生を抑え、画質の劣化を防ぐことができる。 30

#### 【0010】

しかしながら、前記特許文献1に記載されたような構成およびデータ電圧（映像信号）の印加方法でドット反転駆動をさせる場合、各映像信号線に加える映像信号を生成する段階で、映像信号がドット反転している必要がある。そのため、映像信号を生成する駆動回路の発熱量が高くなり、駆動回路の誤動作あるいは故障が起こりやすいという問題がある。

#### 【0011】

また、前記特許文献1に記載されたような構成のVA方式の液晶表示装置では、たとえば、カラム反転と呼ばれる、1フレーム期間中の各画素の画素電極の極性の関係が縦縞状の関係になる駆動方法で映像や画像を表示することも可能であり、カラム反転で駆動させることで、映像信号を生成する駆動回路の発熱量を低く抑えることができる。 40

#### 【0012】

しかしながら、前記特許文献1に記載されたような構成およびデータ電圧（映像信号）の印加方法でカラム反転駆動をさせる場合、たとえば、フリッカ（縦筋流れ）と呼ばれる現象や縦スメアと呼ばれる現象が発生し、画質が劣化しやすいという問題がある。

#### 【0013】

本発明の目的は、1つの画素が2つのスイッチング素子および2つの画素電極を有する

10

20

30

40

50

液晶表示装置において、駆動回路の発熱量を低く抑え、かつ、画質の劣化を防ぐことが可能な技術を提供することにある。

【0014】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面によって明らかになるであろう。

【課題を解決するための手段】

【0015】

本願において開示される発明のうち、代表的なものの概略を説明すれば、以下の通りである。

【0016】

(1) 複数本の走査信号線、複数本の映像信号線、複数個のスイッチング素子、および複数個の画素電極を有する第1の基板と、対向電極を有する第2の基板と、前記第1の基板と前記第2の基板との間に挟持された液晶材料とを有し、第1のスイッチング素子および前記第1のスイッチング素子に接続された第1の画素電極と、第2のスイッチング素子および前記第2のスイッチング素子に接続された第2の画素電極とを有する画素の集合により表示領域が設定されている液晶表示装置であって、1つの画素における前記第1のスイッチング素子と前記第2のスイッチング素子とは、それぞれ、異なる映像信号線に接続されており、1フレーム期間中の、1つの画素の前記第1の画素電極に加わる信号の電位と前記対向電極に加わる信号の電位との関係と、当該1つの画素の前記第2の画素電極に加わる信号の電位と前記対向電極に加わる信号の電位との関係とは、一方が正極性の関係であり、他方が負極性の関係である液晶表示装置。

10

20

【0017】

(2) 前記(1)の液晶表示装置において、1フレーム期間中の、1つの画素の前記第1の画素電極に加わる信号の電位と前記対向電極に加わる信号の電位との関係と、走査信号線または映像信号線を挟んで当該1つの画素に隣接する別の1つの画素の前記第1の画素電極に加わる信号の電位と前記対向電極に加わる信号の電位との関係とは、一方が正極性の関係であり、他方が負極性の関係である液晶表示装置。

【0018】

(3) 複数本の走査信号線、複数本の映像信号線、複数個のスイッチング素子、および複数個の画素電極を有する第1の基板と、対向電極を有する第2の基板と、前記第1の基板と前記第2の基板との間に挟持された液晶材料とを有し、第1のスイッチング素子および前記第1のスイッチング素子に接続された第1の画素電極と、第2のスイッチング素子および前記第2のスイッチング素子に接続された第2の画素電極とを有する画素の集合により表示領域が設定されている液晶表示装置であって、1つの画素における前記第1のスイッチング素子と前記第2のスイッチング素子とは、それぞれ、異なる映像信号線に接続されており、前記映像信号線の延在方向には、前記第1のスイッチング素子が第1の映像信号線に接続し、前記第2のスイッチング素子が第2の映像信号線に接続している画素と、前記第2のスイッチング素子が前記第1の映像信号線に接続し、前記第1のスイッチング素子が前記第2の映像信号線に接続している画素とが交互に並んでいる液晶表示装置。

30

【0019】

(4) 前記(3)の液晶表示装置において、前記第1の映像信号線と前記第2の映像信号線とは、各映像信号線に接続しているスイッチング素子を有する画素を挟んで配置され、かつ、前記走査信号線の延在方向に並んで隣接している2つの画素の間には、当該2つの画素のうちの一方の画素に対する前記第2の映像信号線と、当該2つの画素のうちの他方の画素に対する前記第1の映像信号線とが配置されている液晶表示装置。

40

【0020】

(5) 前記(3)または(4)の液晶表示装置において、1フレーム期間中の、前記第1の映像信号線に加わる信号の電位と前記対向電極の電位との関係、および前記第2の映像信号線に加わる信号の電位と前記対向電極の電位との関係は、それぞれ、常に正極性の関係または常に負極性の関係のいずれかであり、かつ、一方の関係が常に正極性の関係で

50

あるときに、他方の関係が常に負極性の関係である液晶表示装置。

【0021】

(6) 前記(3)乃至(5)のいずれかの液晶表示装置において、前記第1の画素電極と前記第2の画素電極のうちの一方の画素電極は、その平面形状が、他方の画素電極を囲む閉じた環状である液晶表示装置。

【0022】

(7) 前記(3)乃至(6)のいずれかの表示装置において、前記スイッチング素子は、TFT素子である液晶表示装置。

【発明の効果】

【0023】

本発明の液晶表示装置によれば、1つの画素が2つのスイッチング素子および2つの画素電極を有するVA方式の液晶表示装置で映像や画像を表示するときに、カラム反転駆動に対応した映像信号を生成しつつ、液晶表示パネルの各画素をドット反転で駆動させることができ。そのため、映像信号を生成する駆動回路の発熱量を低く抑えることができるとともに、フリッカなどの発生による画質の劣化を防ぐことができる。

10

【図面の簡単な説明】

【0024】

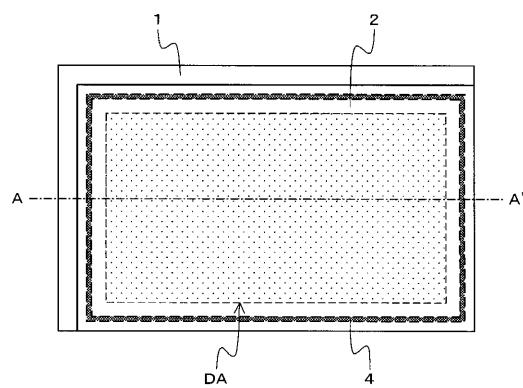

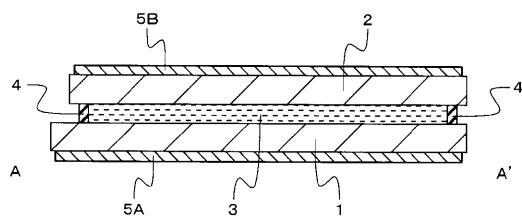

【図1(a)】液晶表示パネルの概略構成を示す模式平面図である。

【図1(b)】図1(a)のA-A'線断面図である。

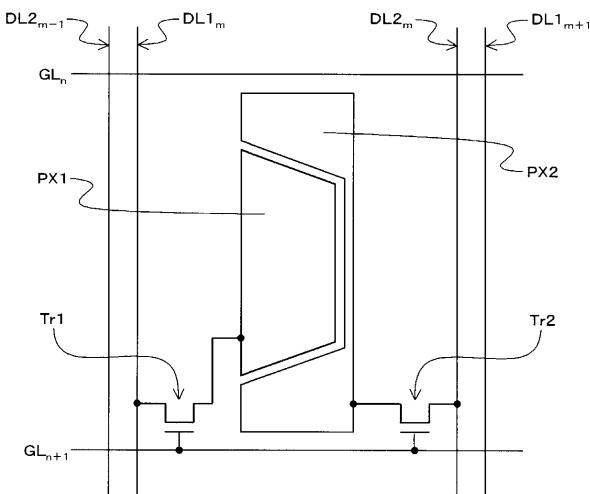

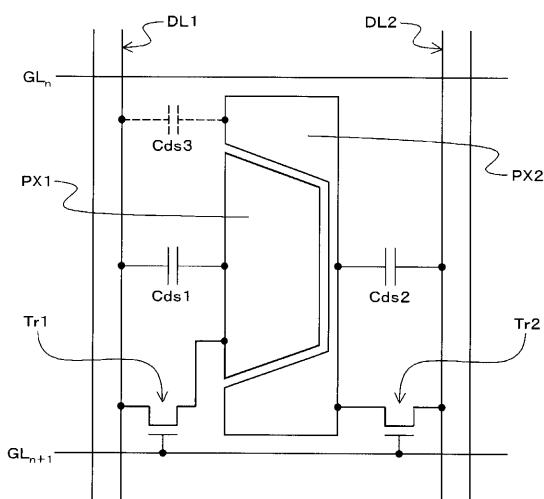

【図2】本発明に関わる液晶表示パネルのTFT基板における1つの画素の一構成例を示す模式回路図である。

20

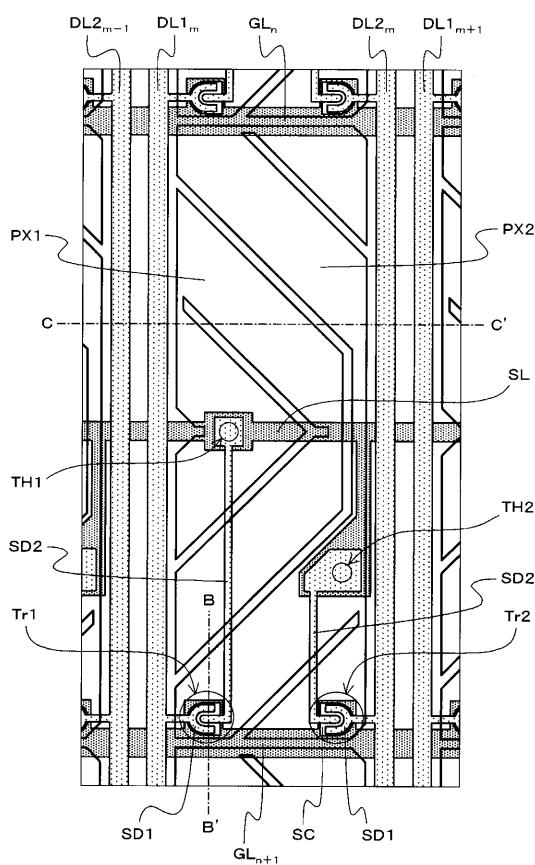

【図3(a)】本発明に関わる液晶表示パネルのTFT基板における1つの画素の一具体例を示す模式平面図である。

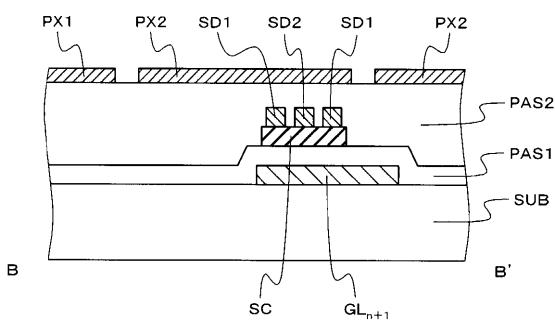

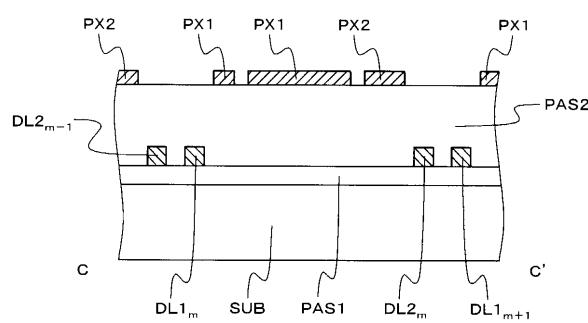

【図3(b)】図3(a)のB-B'線断面図である。

【図3(c)】図3(a)のC-C'線断面図である。

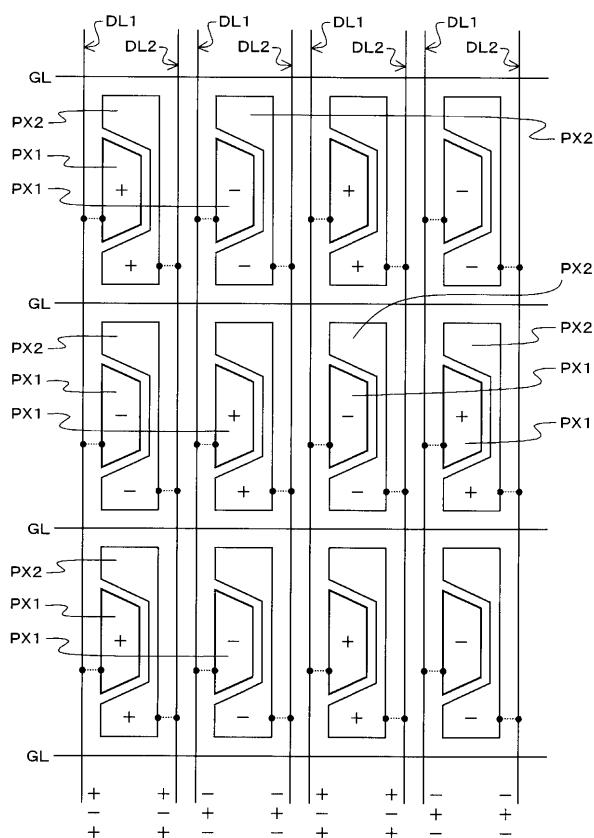

【図4(a)】本発明に関わる液晶表示パネルの従来の構成および駆動方法の一例を示す模式図である。

【図4(b)】本発明に関わる液晶表示パネルの従来の構成および駆動方法の別の例を示す模式図である。

30

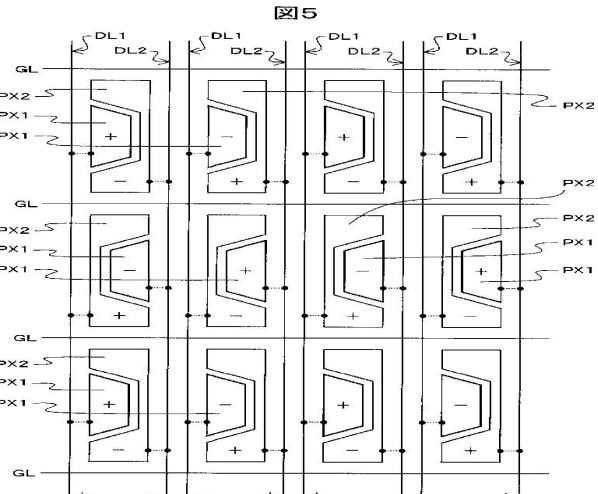

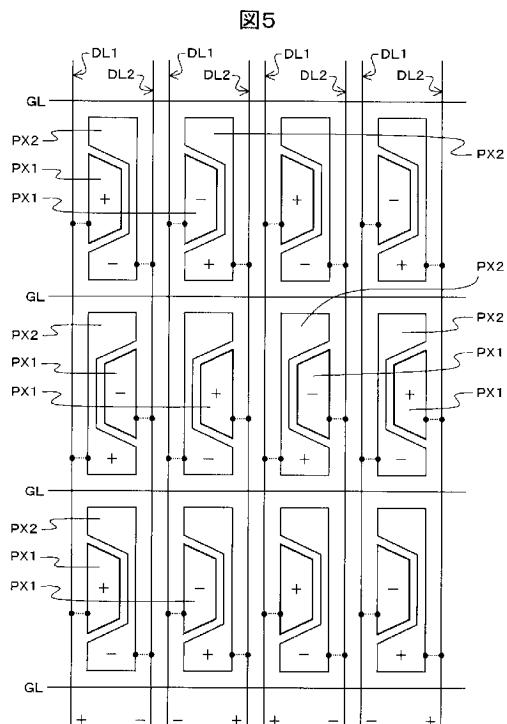

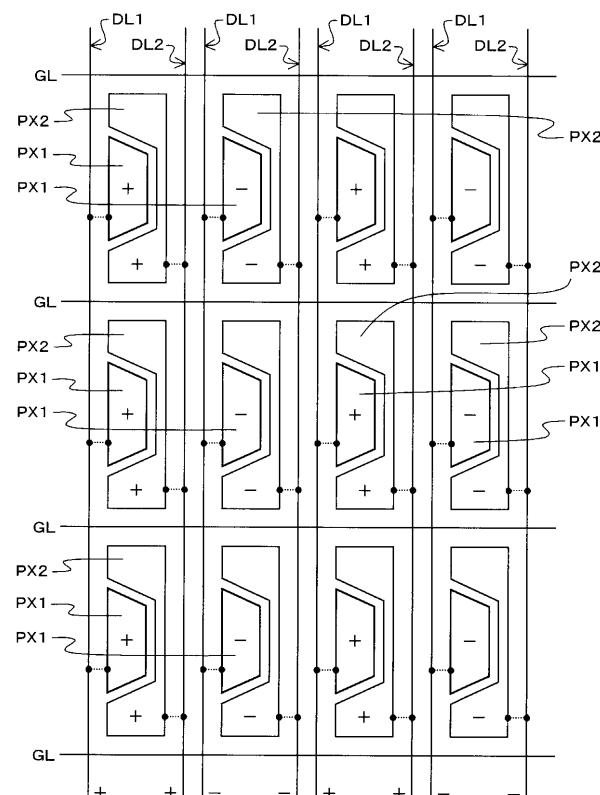

【図5】本発明による実施例1の液晶表示パネルの一構成例を示す模式図である。

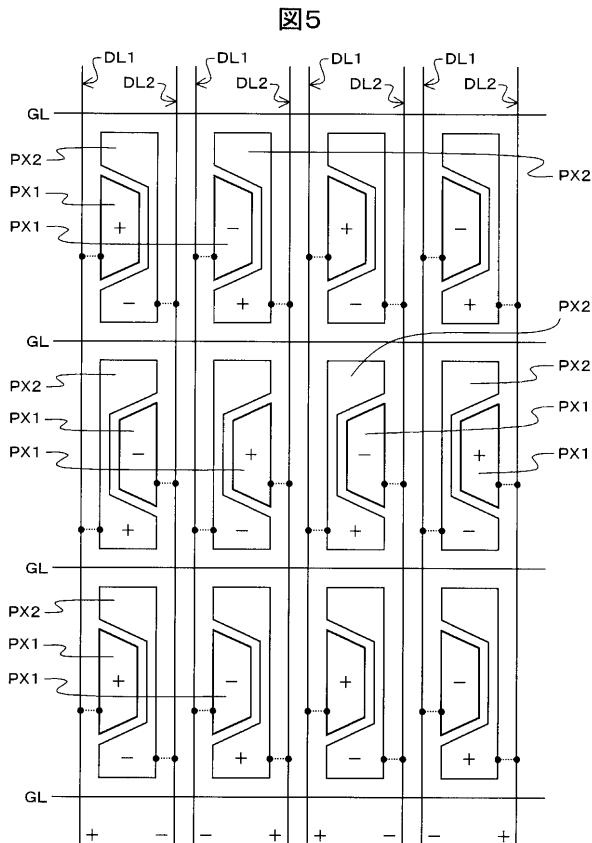

【図6】実施例1の液晶表示パネルの変形例を示す模式図である。

【図7(a)】実施例1の液晶表示パネルにおいて1つの画素に生じる寄生容量の一例を示す模式回路図である。

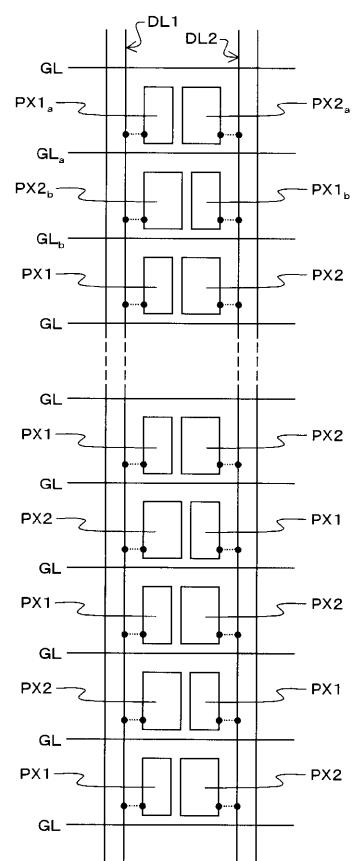

【図7(b)】寄生容量に着目して映像信号線の延在方向に並んだ画素の構成を示した模式図である。

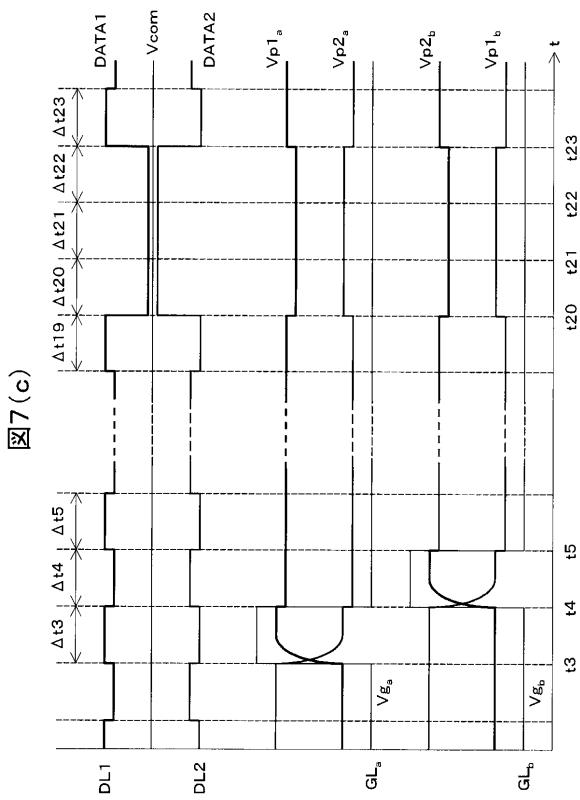

【図7(c)】図7(b)に示した映像信号線に加わる映像信号と画素電極の電位の変化を示す模式チャート図である。

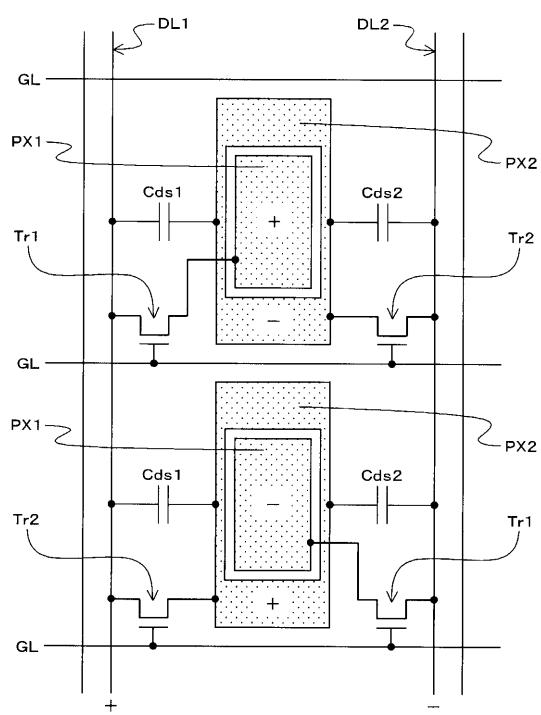

【図8】本発明による実施例2の液晶表示パネルの一構成例を示す模式回路図である。

【発明を実施するための形態】

【0025】

以下、本発明について、図面を参照して実施の形態(実施例)とともに詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは、同一符号を付け、その繰り返しの説明は省略する。

【0026】

図1(a)および図1(b)、図2、図3(a)乃至図3(c)は、それぞれ、本発明に関わる液晶表示装置の概略構成を示す模式図である。

図1(a)は、液晶表示パネルの概略構成を示す模式平面図である。図1(b)は、図1(a)のA-A'線断面図である。

図2は、本発明に関わる液晶表示パネルのTFT基板における1つの画素の一構成例を

40

50

示す模式回路図である。

図3(a)は、本発明に関わる液晶表示パネルのTFT基板における1つの画素の一具体例を示す模式平面図である。図3(b)は、図3(a)のB-B'線断面図である。図3(c)は、図3(a)のC-C'線断面図である。

#### 【0027】

本発明は、液晶表示装置のうちの、VA方式と呼ばれる液晶表示装置に関し、特に、表示領域を構成する各画素が、2つのスイッチング素子および2つの画素電極を有する液晶表示装置の液晶表示パネルの構成および駆動方法に関する。 10

#### 【0028】

液晶表示パネルは、たとえば、図1(a)および図1(b)に示すように、第1の基板1、第2の基板2、液晶材料3、シール材4、下偏光板5A、および上偏光板5Bを有する。

#### 【0029】

第1の基板1は、複数本の走査信号線、複数本の映像信号線、複数個のスイッチング素子、複数個の画素電極などを有する基板である。また、スイッチング素子がTFT素子である場合、第1の基板1は、TFT基板と呼ばれる。以下、第1の基板1のことをTFT基板1と呼ぶ。

#### 【0030】

第2の基板2は、対向電極(共通電極と呼ぶこともある。)や表示領域DAを画素領域ごとに分割する遮光膜(ブラックマトリクスと呼ぶこともある。)などを有する基板であり、対向基板と呼ばれる。以下、第2の基板2のことを対向基板と呼ぶ。また、液晶表示装置がテレビやPCのディスプレイなどのカラー液晶表示装置の場合、対向基板2には、カラーフィルタなども有する。 20

#### 【0031】

また、TFT基板1と対向基板2とは、たとえば、表示領域DAの外側に環状に設けられたシール材4で接着されており、液晶材料3は、TFT基板1、対向基板2、およびシール材4で囲まれた空間に挟持(封入)されている。

#### 【0032】

また、液晶表示パネルが透過型または半透過型である場合は、TFT基板1の外側を向いた面に下偏光板5Aが設けられ、対向基板2の外側を向いた面に上偏光板5Bが設けられる。また、図示はしていないが、たとえば、TFT基板1と下偏光板5Aとの間、および対向基板2と上偏光板5Bとの間には、それぞれ、1層乃至複数層の位相差板が設けられていることもある。 30

#### 【0033】

なお、液晶表示パネルが反射型である場合は、通常、下偏光板5Aが不要であり、たとえば、上偏光板5B、および対向基板2と上偏光板5Bとの間の位相差板のみが設けられている。

#### 【0034】

ところで、TFT基板1の表示領域を構成する各画素において、液晶材料3中の液晶分子を駆動させる電界を発生させるために必要なTFT素子および画素電極は、通常、それぞれ1つずつである。しかしながら、本発明に関わる液晶表示パネルのTFT基板1では、1つの画素が、たとえば、図2に示すように、第1のTFT素子Tr1および第2のTFT素子Tr2の2つのTFT素子と、第1の画素電極PX1および第2の画素電極PX2の2つの画素電極とを有する。なお、図2における1つの画素は、2本の隣接する走査信号線GL<sub>n</sub>, GL<sub>n+1</sub>(nは任意の自然数)と、2本の隣接する映像信号線DL<sub>1m</sub>, DL<sub>2m</sub>(mは任意の自然数)とで囲まれた領域に相当する。 40

#### 【0035】

このとき、第1の画素電極PX1は、第1のTFT素子Tr1のソースに接続しており、第1のTFT素子Tr1のドレインは、たとえば、第1の映像信号線DL<sub>1m</sub>に接続している。また、第2の画素電極PX2は、第2のTFT素子Tr2のソースに接続してお

10

20

30

40

50

り、第2のTFT素子Tr2のドレインは、たとえば、第2の映像信号線DL2<sub>m</sub>に接続している。また、第1のTFT素子Tr1のゲートおよび第2のTFT素子Tr2のゲートは、ともに走査信号線GL<sub>n+1</sub>に接続している。

#### 【0036】

また、図2において、第1の映像信号線DL1<sub>m</sub>の左側にある信号線DL2<sub>m-1</sub>は、図2に示した画素の左隣に位置する画素に対する第2の映像信号線であり、第2の映像信号線DL2<sub>m</sub>の右側にある信号線DL1<sub>m+1</sub>は、図2に示した画素の右隣に位置する画素に対する第1の映像信号線である。

#### 【0037】

このような構成の液晶表示パネルでは、1フレーム期間中の、1つの画素の階調（輝度）を表現するときに、第1の映像信号線DL1<sub>m</sub>から第1の画素電極PX1に加えられた信号の電位と対向電極の電位との関係、および第2の映像信号線DL2<sub>m</sub>から第2の画素電極PX2に加えられた信号の電位と対向電極の電位との関係により液晶分子を駆動させて表現する。そのため、第1の画素電極PX1に加わる信号の電位と第2の画素電極PX2に加わる信号の電位を制御することで、視認性を向上させることができる。

#### 【0038】

また、1つの画素の回路構成が、図2に示したような回路構成であるTFT基板1における、実際の1つの画素の構成は、たとえば、図3(a)乃至図3(c)に示したような構成になっている。

#### 【0039】

まず、ガラス基板などの絶縁基板SUBの表面には、走査信号線GL<sub>n</sub>, GL<sub>n+1</sub>を含む複数本の走査信号線GLと、保持容量（補助容量と呼ぶこともある。）を形成するための保持容量線SLとが設けられている。保持容量線SLは、2本の隣接する走査信号線GLの間ごとに設けられており、各保持容量線SLは、たとえば、表示領域DAの外側に設けられるバスラインなどで電気的に接続されている。

#### 【0040】

走査信号線GLなどの上には、TFT素子のゲート絶縁膜としての機能を有する第1の絶縁層PAS1が設けられている。なお、第1の絶縁層PAS1は、たとえば、シリコン酸化膜などを成膜して形成するので、走査信号線GLや保持容量線SLの上だけではなく、絶縁基板SUBの表面全域に設けられている。

#### 【0041】

第1の絶縁層PAS1の上には、TFT素子の半導体層SC、第1の映像信号線DL1<sub>m</sub>および第2の映像信号線DL2<sub>m</sub>を含む複数本の映像信号線DL、TFT素子のドレン電極SD1およびソース電極SD2などが設けられている。このとき、第1のTFT素子Tr1および第2のTFT素子Tr2のソース電極SD2は、それぞれ、半導体層SCの上から保持容量線SLの方向に延在しており、保持容量線SLと重畠する領域を有する。

#### 【0042】

また、第1のTFT素子Tr1および第2のTFT素子Tr2のソース電極SD2は、それぞれ、第1の映像信号線DL1<sub>m</sub>および第2の映像信号線DL2<sub>m</sub>と一体形成されている。

#### 【0043】

映像信号線DLなどの上には、第2の絶縁層PAS2が設けられ、第2の絶縁層PAS2の上には、第1の画素電極PX1および第2の画素電極PX2が設けられている。第2の絶縁層PAS2は、絶縁基板SUB(第1の絶縁層PAS1)の表面全域に設けられており、たとえば、図3(b)および図3(c)に示したように、表面(画素電極が形成される面)が平坦になるように形成されている。なお、第2の絶縁層PAS2は、各領域における厚さが均一になるように形成されていることもある。

#### 【0044】

また、第2の絶縁層PAS2の上に設けられた第1の画素電極PX1は、スルーホール

10

20

30

40

50

T H 1 により第 1 の T F T 素子 T r 1 のソース電極 S D 2 と接続している。また、第 2 の絶縁層 P A S 2 の上に設けられた第 2 の画素電極 P X 2 は、スルーホール T H 2 により第 2 の T F T 素子 T r 2 のソース電極 S D 2 と接続している。

#### 【 0 0 4 5 】

また、1つの画素に対して配置される第1の映像信号線 D L 1<sub>m</sub> と第2の映像信号線 D L 2<sub>m</sub> とは、たとえば、図3(a)に示すように、当該画素の2つの画素電極 P X 1, P X 2 を挟んで配置される。また、走査信号線 G L の延在方向に隣接して並んでいる2つの画素の間には、たとえば、図3(a)に示すように、一方の画素に対する第2の映像信号線と、他方の画素に対する第1の映像信号線とが配置されている。

#### 【 0 0 4 6 】

なお、図3(a)乃至図3(c)に示した構成は、1つの画素の構成の一例であり、保持容量線 S L の位置、各TFT素子のドレイン電極 S D 1 およびソース電極 S D 2 の平面形状、第1の画素電極 P X 1 および第2の画素電極 P X 2 の平面形状などが適宜変更可能であることはもちろんである。

#### 【 0 0 4 7 】

図4(a)は、本発明に関わる液晶表示パネルの従来の構成および駆動方法の一例を示す模式図である。図4(b)は、本発明に関わる液晶表示パネルの従来の構成および駆動方法の別の例を示す模式図である。

なお、図4(a)および図4(b)では、TFT素子(スイッチング素子)を省略している。また、図4(a)および図4(b)において、各画素電極 P X 1, P X 2 に記した+の記号は、当該画素電極に加えられた信号の電位が対向電極に加えられた信号の電位よりも高い(正極性である)ことを意味し、各画素電極 P X 1, P X 2 に記した-の記号は、当該画素電極に加えられた信号の電位が対向電極に加えられた信号の電位よりも低い(負極性である)ことを意味する。

#### 【 0 0 4 8 】

表示領域を構成する各画素の構成が、たとえば、図2に示したような構成の液晶表示パネルにおいて、各画素の第1の画素電極 P X 1 および第2の画素電極 P X 2 と、第1の映像信号線 D L 1 および第2の映像信号線 D L 2 との関係は、たとえば、図4(a)に示すような関係になっている。すなわち、映像信号線の延在方向に並んでいる画素は、すべて、第1の画素電極 P X 1 が第1の映像信号線 D L 1 に接続しており、第2の画素電極 P X 2 が第2の映像信号線 D L 2 に接続している。

#### 【 0 0 4 9 】

このような液晶表示パネルで映像や画像を表示するときには、たとえば、図4(a)に示したように、走査信号線 G L を挟んで隣接する2つの画素の画素電極の極性、および映像信号線 D L 1, D L 2 を挟んで隣接する2つの画素の画素電極の極性が、ともに反対の極性になるように、液晶表示パネルをドット反転駆動させる方法がある。

#### 【 0 0 5 0 】

しかしながら、ドット反転駆動をさせる場合、1フレーム期間に映像信号線に加える映像信号は、たとえば、図4(a)に示したように、正極性(+)の信号と負極性(-)の信号とが交互になるようにする必要がある。そのため、映像信号線に加える映像信号を生成する駆動回路における処理(負荷)が増大し、当該駆動回路の発熱量が高くなる。

#### 【 0 0 5 1 】

また、このような液晶表示パネルで映像や画像を表示するときには、たとえば、図4(b)に示すように、走査信号線 G L を挟んで隣接する2つの画素の画素電極の極性は同じ極性で、映像信号線 D L 1, D L 2 を挟んで隣接する2つの画素の画素電極の極性は反対の極性になるように、液晶表示パネルをカラム反転駆動させる方法がある。

#### 【 0 0 5 2 】

しかしながら、カラム反転駆動をさせる場合、1フレーム期間における各画素の画素電極の極性は、たとえば、図4(b)に示したように、映像信号線の延在方向に並んだ複数個の画素の画素電極の極性がすべて正極性である列(カラム)と、すべて負極性である列

(カラム)とが走査信号線の延在方向に交互に並んだ状態になる。そのため、フリッカ(縦筋流れ)や縦スメアが発生し、画質が劣化しやすい。

#### 【0053】

以下、上記のような構成の液晶表示パネルをもとにして、映像信号を生成する駆動回路の発熱量を低く抑え、かつ、フリッカなどによる画質の劣化を防ぐ液晶表示パネルの構成の一例について説明する。

#### 【実施例1】

#### 【0054】

図5は、本発明による実施例1の液晶表示パネルの一構成例を示す模式図である。

なお、図5では、TFT素子(スイッチング素子)を省略している。また、図5において、各画素電極PX1, PX2に記した+の記号は、当該画素電極に加えられた信号の電位が対向電極の電位よりも高い(正極性である)ことを意味し、各画素電極PX1, PX2に記した-の記号は、当該画素電極に加えられた信号の電位が対向電極の電位よりも低い(負極性である)ことを意味する。

10

#### 【0055】

実施例1の液晶表示パネルは、たとえば、図5に示すように、1つの画素が、第1の画素電極PX1および第2の画素電極PX2の2つの画素電極を有し、各画素の2つの画素電極は、それぞれ、第1の映像信号線DL1と第2の映像信号線DL2で挟まれおり、当該第1の映像信号線DL1または第2の映像信号線DL2とTFT素子(図示しない)を介して接続している。

20

#### 【0056】

また、実施例1の液晶表示パネルでは、映像信号線DL1, DL2の延在方向に並んだ複数個の画素に着目すると、第1の画素電極PX1が第1の映像信号線DL1に接続し、第2の画素電極PX2が第2の映像信号線DL2に接続している画素と、第2の画素電極PX2が第1の映像信号線DL1に接続し、第1の画素電極PX1が第2の映像信号線DL2に接続している画素とが、交互に配置されている。

30

#### 【0057】

また、実施例1の液晶表示パネルでは、走査信号線GLの延在方向に並んだ複数個の画素に着目すると、第1の画素電極PX1が第1の映像信号線DL1に接続し、第2の画素電極PX2が第2の映像信号線DL2に接続している画素のみ、あるいは第2の画素電極PX2が第1の映像信号線DL1に接続し、第1の画素電極PX1が第2の映像信号線DL2に接続している画素のみが配置されている。

30

#### 【0058】

また、実施例1の液晶表示パネルでは、1フレーム期間中に、一対の第1の映像信号線DL1と第2の映像信号線DL2に加わる映像信号の極性は、常に正極性または常に負極性のいずれかであり、かつ、一方の映像信号線に加わる映像信号が常に正極性であれば、他方の映像信号線に加わる映像信号は常に負極性である。

40

#### 【0059】

またさらに、実施例1の液晶表示パネルでは、1フレーム期間中に、走査信号線GLの延在方向で隣接する2つの画素の間に配置された2本の映像信号線DL2, DL1に加わる映像信号線の極性は、同じ極性である。

#### 【0060】

液晶表示パネルの構成、および各映像信号線に加わる映像信号の極性を上記のようにすると、1フレーム期間に、各画素の画素電極PX1, PX2に加わる信号の電位と対向電極の電位との関係(極性)は、図5に示したような関係になる。まず、1つの画素に着目した場合、第1の画素電極PX1の極性と、第2の画素電極PX2の極性は、必ず反対の極性になる。

#### 【0061】

また、走査信号線GLまたは映像信号線DL1, DL2を挟んで隣接する2つの画素に着目した場合、一方の画素の第1の画素電極PX1の極性と他方の画素の第1の画素電極

50

P X 1 の極性、および一方の画素の第 2 の画素電極 P X 2 の極性と他方の画素の第 2 の画素電極 P X 2 の極性は、それぞれ、必ず反対の極性になる。

#### 【 0 0 6 2 】

すなわち、実施例 1 の液晶表示パネルを有する液晶表示装置では、駆動回路において映像信号を生成するときには、カラム反転駆動に対応した生成方法で各映像信号線に加える映像信号を生成することができ、各映像信号線に加えられた映像信号に基づいて液晶表示パネルを駆動させるとときには、ドット反転駆動をさせることができる。

#### 【 0 0 6 3 】

したがって、実施例 1 の液晶表示パネルを有する液晶表示装置は、映像信号を生成する駆動回路の発熱量を低く抑えることができ、かつ、フリッカなどによる画質の劣化を防ぐことができる。

10

#### 【 0 0 6 4 】

なお、図示は省略するが、図 5 に示したような構成の TFT 基板 1 を製造するときには、1 つの画素が、たとえば、図 3 ( a ) 乃至図 3 ( b ) に示したような構成であり、かつ、走査信号線 G L を挟んで隣接する 2 つの画素の平面レイアウトが、図 3 ( a ) に示した平面レイアウトと、図 3 ( a ) を左右反転させた平面レイアウトになるようにすればよい。

#### 【 0 0 6 5 】

図 6 は、実施例 1 の液晶表示パネルの変形例を示す模式図である。

なお、図 6 では、TFT 素子（スイッチング素子）を省略している。また、図 6 において、各画素電極 P X 1 , P X 2 に記した + の記号は、当該画素電極に加えられた信号の電位が対向電極の電位よりも高い（正極性である）ことを意味し、各画素電極 P X 1 , P X 2 に記した - の記号は、当該画素電極に加えられた信号の電位が対向電極の電位よりも低い（負極性である）ことを意味する。

20

#### 【 0 0 6 6 】

実施例 1 の液晶表示パネルの構成を説明するにあたり、図 5 では、第 1 の画素電極 P X 1 が第 1 の映像信号線 D L 1 に接続し、第 2 の画素電極 P X 2 が第 2 の映像信号線 D L 2 に接続している画素と、第 2 の画素電極 P X 2 が第 1 の映像信号線 D L 1 に接続し、第 1 の画素電極 P X 1 が第 2 の映像信号線 D L 2 に接続している画素とで、画素電極の向きが左右反転している場合を例に挙げている。

30

#### 【 0 0 6 7 】

しかしながら、実施例 1 の液晶表示パネルでは、走査信号線 G L を挟んで隣接する 2 つの画素について、各画素電極 P X 1 , P X 2 が接続している映像信号線の関係が、上記の条件を満たしていればよい。そのため、たとえば、図 6 に示すように、走査信号線 G L を挟んで隣接する 2 つの画素の各画素電極 P X 1 , P X 2 が同じ向きで配置されていてもよい。

30

#### 【 実施例 2 】

#### 【 0 0 6 8 】

図 7 ( a ) 乃至図 7 ( c ) は、実施例 1 の液晶表示パネルにおいて発生する可能性がある問題点の一例を説明するための模式図である。

40

図 7 ( a ) は、実施例 1 の液晶表示パネルにおいて 1 つの画素に生じる寄生容量の一例を示す模式回路図である。図 7 ( b ) は、寄生容量に着目して映像信号線の延在方向に並んだ画素の構成を示した模式図である。図 7 ( c ) は、図 7 ( b ) に示した映像信号線に加わる映像信号と画素電極の電位の変化を示す模式チャート図である。

なお、図 7 ( b ) では、TFT 素子（スイッチング素子）を省略している。

#### 【 0 0 6 9 】

実施例 1 の液晶表示パネルの TFT 基板 1 における 1 つの画素の回路構成は、たとえば、図 7 ( a ) に示したような構成になっている。

#### 【 0 0 7 0 】

ところで、第 1 の画素電極 P X 1 および第 2 の画素電極 P X 2 は、たとえば、図 3 ( c )

50

)に示したように、映像信号線 D L 1 , D L 2 などが形成された面の上に、第 2 の絶縁層 P A S 2 を介して形成されている。そのため、たとえば、図 7 ( a )に示すように、第 1 の画素電極 P X 1 と第 1 の映像信号線 D L 1との間には第 1 の寄生容量 C d s 1 が形成され、第 2 の画素電極 P X 2 と第 2 の映像信号線 D L 2 との間には第 2 の寄生容量 C d s 2 が形成される。また、実際には、第 2 の画素電極 P X 2 と第 1 の映像信号線 D L 1との間に第 3 の寄生容量 C d s 3 が形成されるが、第 3 の寄生容量 C d s 3 は、第 1 の寄生容量 C d s 1 および第 2 の寄生容量 C d s 2 に比べて非常に小さいので、本構成では無視する。

#### 【 0 0 7 1 】

このような画素電極と映像信号線の間に形成される寄生容量に着目して、実施例 1 の液晶表示パネルにおける、映像信号線の延在方向に並んだ複数個の画素の構成を模式的に示すと、たとえば、図 7 ( b )のように表すことができる。10

#### 【 0 0 7 2 】

また、1 フレーム期間に、図 7 ( b )に示した各画素の画素電極 P X 1 , P X 2 が接続している第 1 の映像信号線 D L 1 に加わる第 1 の映像信号 D A T A 1 と、第 2 の映像信号線 D L 2 に加わる第 2 の映像信号 D A T A 2 は、たとえば、図 7 ( c )に示したような信号である。

#### 【 0 0 7 3 】

このとき、図 7 ( b )に示した第 1 の画素電極 P X 1<sub>a</sub> および第 2 の画素電極 P X 2<sub>a</sub> には、それぞれ、たとえば、図 7 ( c )に示した時刻 t 3 から t 4 までの期間 t 3 に第 1 の映像信号線 D L 1 に加わる第 1 の映像信号 D A T A 1 および第 2 の映像信号線 D L 2 に加わる第 2 の映像信号 D A T A 2 が書き込まれる。同様に、図 7 ( b )に示した第 1 の画素電極 P X 1<sub>b</sub> および第 2 の画素電極 P X 2<sub>b</sub> には、それぞれ、たとえば、図 7 ( c )に示した時刻 t 4 から t 5 までの期間 t 4 に第 1 の映像信号線 D L 1 に加わる第 1 の映像信号 D A T A 1 および第 2 の映像信号線 D L 2 に加わる第 2 の映像信号 D A T A 2 が書き込まれる。なお、図 7 ( c )において、V p 1<sub>a</sub> は第 1 の画素電極 P X 1<sub>a</sub> の電位、V p 2<sub>a</sub> は第 2 の画素電極 P X 2<sub>a</sub> の電位、V p 1<sub>b</sub> は第 1 の画素電極 P X 1<sub>b</sub> の電位、V p 2<sub>b</sub> は第 2 の画素電極 P X 2<sub>b</sub> の電位である。また、図 7 ( c )において、V g<sub>a</sub> は走査信号線 G L<sub>a</sub> に加わる走査信号の電位、V g<sub>b</sub> は走査信号線 G L<sub>b</sub> に加わる走査信号の電位である。20

#### 【 0 0 7 4 】

第 1 の画素電極 P X 1<sub>a</sub> , P X 1<sub>b</sub> および第 2 の画素電極 P X 2<sub>a</sub> , P X 2<sub>b</sub> に映像信号が書き込まれるときには、書き込みが終了する時点において電位が若干変動するが、その後は、通常、次のフレーム期間の映像信号の書き込みを行うまで、書き込まれた信号の電位が保持される。30

#### 【 0 0 7 5 】

しかしながら、第 1 の画素電極 P X 1<sub>a</sub> , P X 1<sub>b</sub> および第 2 の画素電極 P X 2<sub>a</sub> , P X 2<sub>b</sub> に映像信号を書き込んだ後の、同じフレーム期間の第 1 の映像信号 D A T A 1 および第 2 の映像信号 D A T A 2 には、たとえば、図 7 ( c )に示した期間 t 19 と t 2 0 の境界または期間 t 2 2 と t 2 3 の境界のように、階調が大きく変化するような映像信号が含まれていることがある。40

#### 【 0 0 7 6 】

そうすると、第 1 の画素電極 P X 1<sub>a</sub> , P X 1<sub>b</sub> および第 2 の画素電極 P X 2<sub>a</sub> , P X 2<sub>b</sub> に書き込まれた映像信号の電位は、たとえば、期間 t 2 0 ~ t 2 2 の間だけ変動し、カップリングスマアと呼ばれる現象が発生する。そのため、実施例 1 の液晶表示パネルを有する液晶表示装置では、カップリングスマアにより画質が劣化する可能性がある。

#### 【 0 0 7 7 】

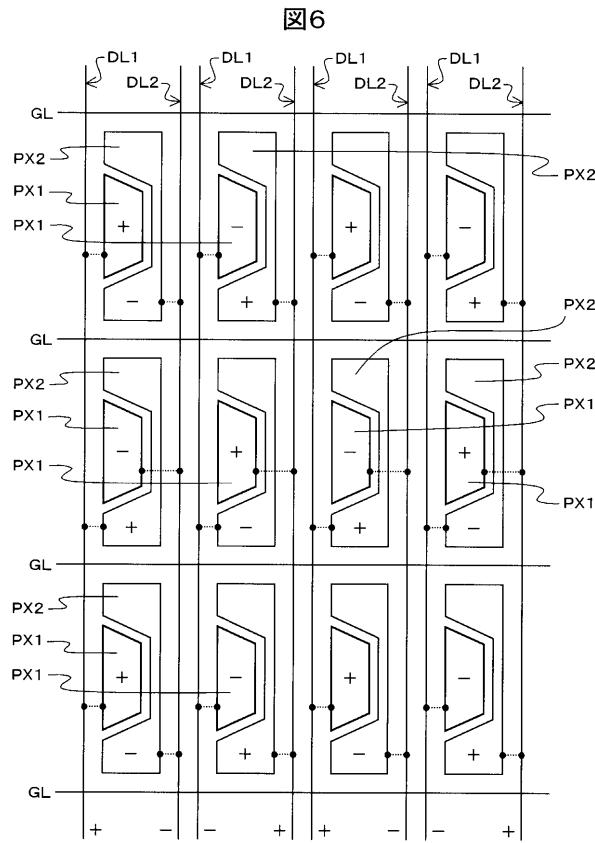

図 8 は、本発明による実施例 2 の液晶表示パネルの一構成例を示す模式回路図である。

#### 【 0 0 7 8 】

上記カップリングスマアの発生は、1 つの画素における第 1 の画素電極 P X 1 および第

10

20

30

40

50

2の画素電極P X 2が、それぞれ、第1の映像信号線D L 1のみ、または第2の映像信号線D L 2のみとの間で寄生容量を形成することと関係している。

#### 【0079】

そのため、実施例2の液晶表示パネルでは、たとえば、図8に示すように、第2の画素電極P X 2の平面形状を、第1の画素電極P X 1を囲む閉じた環状にする。このようにすると、平面で見たときに、第1の画素電極P X 1と第1の映像信号線D L 1との間に第2の画素電極P X 2が延在し、第1の画素電極P X 1と第2の映像信号線D L 2との間にも第2の画素電極P X 2が延在する。

#### 【0080】

したがって、実施例2の液晶表示パネルでは、第2の画素電極P X 2と第1の映像信号線D L 1との間に第1の寄生容量C d s 1が形成され、第2の画素電極P X 2と第2の映像信号線D L 2との間に第2の寄生容量C d s 2が形成され、第1の画素電極P X 1と第1の映像信号線D L 1との間、および第1の画素電極P X 1と第2の映像信号線D L 2との間には寄生容量が形成されない。

10

#### 【0081】

このような構成にすると、第1の画素電極P X 1に書き込まれた信号には、映像信号線D L 1, D L 2との寄生容量による電位の変動が生じない。また、第2の画素電極P X 2に書き込まれた信号には、映像信号線D L 1, D L 2との間に形成される寄生容量による電位の変動が生じるもの、その寄生容量は、第2の画素電極P X 2を挟んで配置される2本の映像信号線D L 1, D L 2との間に形成される。そのため、第2の画素電極P X 2に書き込まれた信号の電位の変動にはかたよりがなく、カップリングスマアの発生を防ぐことができる。

20

#### 【0082】

なお、図8に示した例では、第2の画素電極P X 2の平面形状を閉じた環状にしているが、逆に、第1の画素電極P X 1の平面形状を第2の画素電極P X 2を囲む閉じた環状にしてもよいことはもちろんである。

#### 【0083】

また、図8に示した例では、第2の画素電極P X 2の平面形状を閉じた環状にしているが、これに限らず、たとえば、第2の画素電極P X 2の平面形状が、第1の画素電極P X 1を囲み、かつ、走査信号線G Lと平行に延在する部分が開いた環状、あるいはコの字型であってもよい。

30

#### 【0084】

以上、本発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において、種々変更可能であることはもちろんである。

#### 【符号の説明】

#### 【0085】

1 ... TFT基板

2 ... 対向基板

3 ... 液晶材料

40

4 ... シール材

5 A ... 下偏光板

5 B ... 上偏光板

G L, G L<sub>n</sub>, G L<sub>n+1</sub>, G L<sub>a</sub>, G L<sub>b</sub> ... 走査信号線

D L<sub>1</sub>, D L<sub>1m</sub>, D L<sub>1m+1</sub> ... 第1の映像信号線

D L<sub>2</sub>, D L<sub>2m-1</sub>, D L<sub>2m</sub> ... 第2の映像信号線

T r<sub>1</sub> ... 第1のTFT素子

T r<sub>2</sub> ... 第2のTFT素子

P X<sub>1</sub>, P X<sub>1a</sub>, P X<sub>1b</sub> ... 第1の画素電極

P X<sub>2</sub>, P X<sub>2a</sub>, P X<sub>2b</sub> ... 第2の画素電極

50

S U B ... 絶縁基板

S L ... 保持容量線

P A S 1 ... 第1の絶縁層

S C ... 半導体層

S D 1 ... ドレイン電極

S D 2 ... ソース電極

P A S 2 ... 第2の絶縁層

C d s 1 ... 第1の寄生容量

C d s 2 ... 第2の寄生容量

C d s 3 ... 第3の寄生容量

D A T A 1 ... 第1の映像信号

D A T A 2 ... 第2の映像信号

V p 1<sub>a</sub>, V p 1<sub>b</sub> ... 第1の画素電極の電位

V p 2<sub>a</sub>, V p 2<sub>b</sub> ... 第2の画素電極の電位

V g<sub>a</sub>, V g<sub>b</sub> ... 走査信号の電位

D A ... 表示領域

10

【図1(a)】

図1(a)

【図1(b)】

図1(b)

【図2】

図2

【図3(a)】

図3(a)

【図3(b)】

図3(b)

【図3(c)】

図3(c)

【図4(a)】

図4(a)

【図4(b)】

図4(b)

【圖 5】

【 四 6 】

【図7(a)】

图 7(a)

【図7(b)】

図7(b)

【図7(c)】

【図8】

図8

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 B |

| G 0 9 G | 3/20 | 6 2 4 B |

| G 0 9 G | 3/20 | 6 2 4 A |

| G 0 9 G | 3/20 | 6 1 1 E |

| G 0 9 G | 3/20 | 6 2 1 M |

| G 0 9 G | 3/20 | 6 4 2 A |

| G 0 9 G | 3/20 | 6 8 0 H |

F ターム(参考) 2H092 GA13 JA24 JB05 NA01 PA06 QA09

2H193 ZA04 ZC12 ZF11 ZP03 ZQ11

5C006 AA22 AC27 AC28 AF42 AF43 BB16 BC06 FA23 FA47

5C080 AA10 CC03 DD06 DD26 EE30 FF11 JJ01 JJ03 JJ04 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2012145950A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2012-08-02 |

| 申请号            | JP2012034672                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2012-02-21 |

| [标]申请(专利权)人(译) | 日本显示器东股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 有限公司日本东显示器<br>松下液晶显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 桶隆太郎<br>小野記久雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 桶 隆太郎<br>小野 記久雄                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368 G02F1/133 G09G3/36 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F1分类号          | G02F1/1343 G02F1/1368 G02F1/133.550 G09G3/36 G09G3/20.611.A G09G3/20.621.B G09G3/20.624.B G09G3/20.624.A G09G3/20.611.E G09G3/20.621.M G09G3/20.642.A G09G3/20.680.H                                                                                                                                                                                                                                                                                                          |         |            |

| F-Term分类号      | 2H092/GA13 2H092/JA24 2H092/JB05 2H092/NA01 2H092/PA06 2H092/QA09 2H193/ZA04 2H193/ZC12 2H193/ZF11 2H193/ZP03 2H193/ZQ11 5C006/AA22 5C006/AC27 5C006/AC28 5C006/AF42 5C006/AF43 5C006/BB16 5C006/BC06 5C006/FA23 5C006/FA47 5C080/AA10 5C080/CC03 5C080/DD06 5C080/DD26 5C080/EE30 5C080/FF11 5C080/JJ01 5C080/JJ03 5C080/JJ04 5C080/JJ06 2H192/AA24 2H192/BA25 2H192/BC24 2H192/CB05 2H192/CB44 2H192/CC64 2H192/DA12 2H192/DA43 2H192/DA74 2H192/EA22 2H192/GD61 2H192/JA13 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

### 摘要(译)

在其中一个像素具有两个开关元件和两个像素电极的液晶显示装置中，由驱动电路产生的热量被抑制为低，并且防止了图像质量的劣化。提供了第一开关元件和连接至第一开关元件的第一像素电极，以及第二像素元件，其连接至第二开关元件和第二开关元件。在通过一组像素设置显示区域的液晶显示装置中，一个像素中的第一开关元件和第二开关元件分别连接到不同的视频信号线。在一个帧周期中，施加到一个像素的第一像素电极的信号电位与施加到对电极的信号电位之间的关系，以及施加到一个像素的第二像素电极的信号之间的关系 一种液晶显示装置，其中施加到对电极的电势和信号电势中的一个具有正极性，另一个具有负极性。 [选择图]图5