(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-188949

(P2016-188949A)

(43) 公開日 平成28年11月4日(2016.11.4)

| (51) Int.CI.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G02F 1/133 (2006.01)</b> | GO2F 1/133 | 520 2H193   |

| <b>G09G 3/36 (2006.01)</b>  | GO9G 3/36  | 5C006       |

| <b>G09G 3/20 (2006.01)</b>  | GO9G 3/20  | 612G 5C080  |

|                             | GO9G 3/20  | 670M        |

審査請求 未請求 請求項の数 3 O L (全 8 頁)

|           |                            |            |                                                                                                                                                                                 |

|-----------|----------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2015-69052 (P2015-69052) | (71) 出願人   | 000103747<br>京セラディスプレイ株式会社<br>滋賀県野洲市市三宅641-1                                                                                                                                    |

| (22) 出願日  | 平成27年3月30日 (2015.3.30)     | (72) 発明者   | 安田 仁志<br>滋賀県野洲市市三宅641-1 京セラディスプレイ株式会社内                                                                                                                                          |

|           |                            | F ターム (参考) | 2H193 ZA04 ZF01 ZJ13<br>5C006 AA21 AF67 BB16 BC03 BC06<br>BF42 GA03<br>5C080 AA10 BB05 CC03 DD19 DD29<br>FF11 JJ02 JJ04 KK02 KK07<br>KK21 KK23 KK28 KK29 KK31<br>KK43 KK47 KK49 |

|           |                            |            |                                                                                                                                                                                 |

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

**【課題】** X A O制御の実行時にゲートハイ電源ラインを通じて液晶表示パネル側に流れ込んだラッシュ電流が、配線パターンの断線及びゲート信号線駆動回路の接続端子部の導通劣化等を起こすことを抑制すること。

**【解決手段】** L C Dは、基板上の第1の方向の複数本のゲート信号線5と、第1の方向と交差する第2の方向に形成された複数本の画像信号線6と、ゲート信号線5と画像信号線6の交差部に形成された、T F T 1及び複数の画素部と、複数のゲート信号線5を駆動するゲート信号線駆動回路3と、を有する液晶表示パネル7と、液晶表示パネル7の電源オフ時に複数のゲート信号線5のすべてにゲートハイ電圧を入力するためのゲートハイ電源電圧をゲート信号線駆動回路3に供給する電源回路20と、電源回路20からゲート信号線駆動回路3にかけて設けられているゲートハイ電源線25と、を備えており、ゲートハイ電源線25は抵抗25Rが直列に接続されている。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

基板上の第1の方向に形成された複数本のゲート信号線と、前記第1の方向と交差する第2の方向に前記ゲート信号線と交差させて形成された複数本の画像信号線と、前記ゲート信号線と前記画像信号線の交差部に形成された、薄膜トランジスタ及び画素電極を含む複数の画素部と、複数の前記ゲート信号線を駆動するゲート信号線駆動回路と、を有する液晶表示パネルと、前記液晶表示パネルの電源オフ時に複数の前記ゲート信号線のすべてにゲートハイ電圧を入力するためのゲートハイ電源電圧を前記ゲート信号線駆動回路に供給する電源回路と、前記電源回路から前記ゲート信号線駆動回路にかけて設けられているゲートハイ電源線と、を備えた液晶表示装置であって、前記ゲートハイ電源線は、抵抗が直列に接続されている液晶表示装置。10

**【請求項 2】**

前記抵抗は、抵抗値が50～200である請求項1に記載の液晶表示装置。

**【請求項 3】**

前記抵抗は、前記ゲートハイ電源線の前記電源回路側の端部に接続されている請求項1または請求項2に記載の液晶表示装置。20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示パネルの電源オフ時にXAO(X All On)制御によってゲート信号線のすべてにゲートハイ電圧を入力するためのゲートハイ電源電圧を供給する電源回路を備えた液晶表示装置(Liquid Crystal Display:LCD)に関するものである。20

**【背景技術】****【0002】**

従来、LCDは、薄膜トランジスタ(Thin Film Transistor: TFT)を含む画素部が多数形成されたアレイ側基板と、カラーフィルタ及びブラックマトリクスが形成されたカラーフィルタ側基板とを互いに対向させて、それらの基板を所定の間隔でもって貼り合わせ、それらの基板間に液晶を充填、封入させることによって作製される。また、一般的に、カラーフィルタ側基板は、TFT及び画素電極に対向する側の面(液晶側の面)の全面に、画素電極との間で液晶に印加する垂直電界を形成するための共通電極が形成されている。また、LCDが画素電極と共に電極との間で液晶に印加する横電界を形成するIPS(In-Plane Switching)方式のLCDである場合、共通電極はアレイ側基板の画素電極と同じ面内に形成される。LCDが画素電極と共に電極との間で液晶に印加するフリンジ電界(端部電界)を形成するFFS(Fringe Field Switching)方式のLCDである場合、共通電極はアレイ側基板の画素部に画素電極の上方または下方に絶縁層を挟んで形成される。また、カラーフィルタ側基板の液晶側の面には、それぞれの画素部に対応する赤(R)、緑(G)、青(B)のカラーフィルタが形成されており、それぞれの画素部を通過する光が相互に干渉することを防ぐブラックマトリクスがカラーフィルタの外周を囲むように形成されている。30

**【0003】**

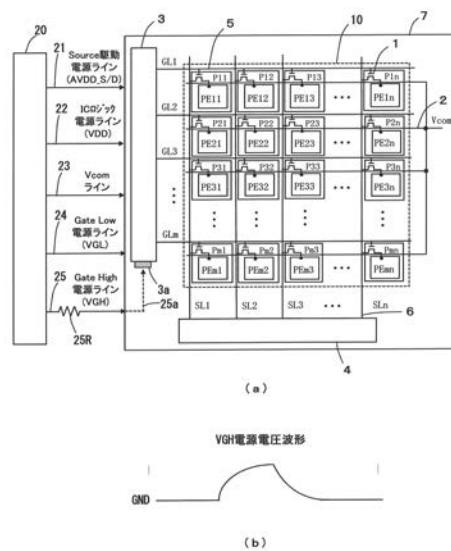

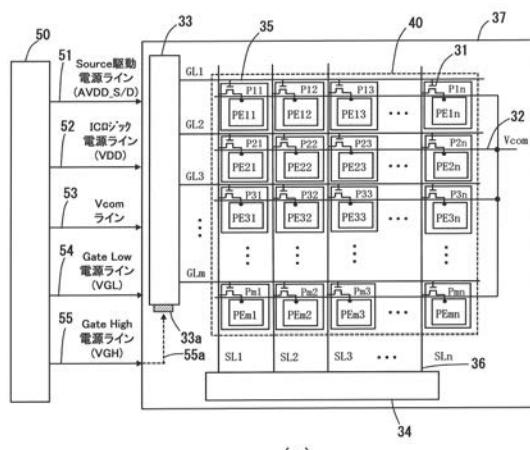

従来のアクティブマトリクス型のLCDの基本構成の1例を図2(a)に示す。例えばIPS方式のLCDの場合、TFT31を含む画素部P11, P12, P13～Pmnが多数形成されたアレイ側基板は、その上の第1の方向(例えば、行方向)に形成された複数本のゲート信号線35(GL1, GL2, GL3～GLm)と、第1の方向と交差する第2の方向(例えば、列方向)にゲート信号線35と交差させて形成された複数本の画像信号線(ソース信号線)36(SL1, SL2, SL3～SLn)と、ゲート信号線35と画像信号線36の交差部に形成されたTFT31と、液晶に印加する横電界(水平電界)を形成するための画素電極PE11, PE12, PE13～PEmn及び共通電極(基準電極)と、それらを含む画素部P11, P12, P13～Pmnと、共通電極に共通電圧(Vcom)を供給する共通電圧線32と、を有する構成である。なお、図2において、33はゲート信号線35に順次ゲート信号を入力するゲート信号線駆動回40

路、34は画像信号線36に順次画像信号を入力する画像信号線駆動回路、37は液晶表示パネル、40は表示部である。

#### 【0004】

また、LCDは、1個以上のIC等の半導体素子から成るゲート信号線駆動回路33、及び1個以上のIC等の半導体素子から成る画像信号線駆動回路34等に、各種の電源電圧を供給する電源回路50を備えている。例えば、画像信号線駆動回路34内部の液晶を駆動するためのアナログ回路にアナログ回路用電源電圧を供給する画像信号(ソース)駆動電源ライン51、画像信号線駆動回路34内部のデジタルロジック回路にデジタルロジック回路用電源電圧を供給するICロジック電源ライン52、共通電圧線32に共通電圧(Vcom)を供給するVcomライン53、ゲート信号線35にゲートロー電圧を入力するためのゲートロー電圧をゲート信号線駆動回路33に供給するゲートロー電源ライン54、ゲート信号線35にゲートハイ電圧を入力するためのゲートハイ電源電圧をゲート信号線駆動回路33に供給するゲートハイ電源ライン55が、電源回路50から液晶表示パネル37にかけて設けられている。電源回路50は、例えばフレキシブル回路基板(Flexible Printed Circuit : FPC)等に形成されており、そのFPCから液晶表示パネル37にかけて設けられたフラットケーブル(Flexible Flat Cable : FFC)等に、画像信号(ソース)駆動電源ライン51、ICロジック電源ライン52、Vcomライン53、ゲートロー電源ライン54、ゲートハイ電源ライン55が、形成されている。

10

#### 【0005】

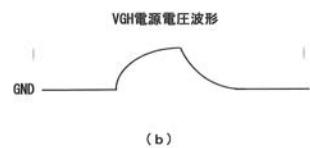

また、電源回路50は、図2(b)に示すような、液晶表示パネル37の電源オフ時にXAO制御によってゲート信号線35のすべてにゲートハイ電圧を入力するためのゲートハイ電源電圧を、ゲート信号線駆動回路33に供給する。XAO制御は、液晶表示パネル37の電源オフ時に、すべてのゲート信号線35に電気的に接続されたすべての画素電極に残留している電荷を画像信号線36を通じて放電させるために、画素電極と画像信号線36とを導通させる制御である。

20

#### 【0006】

また、他の従来例として、表示用電源装置から表示パネルにかけて設けられたゲートハイ電圧ラインに、スイッチ手段及びそれに直列接続された抵抗素子を、並列に接続した構成の画像表示装置が提案されている(例えば、特許文献1を参照)。この構成により、電源オフ時に画素電極に残留した残留電荷の放電時間を抵抗素子の抵抗値によって調整することができ、残留電荷を充分に放電させることができる。

30

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【特許文献1】特開2004-4630号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

しかしながら、図2に示す上記従来のLCDにおいては、XAO制御の実行時に、図2(b)に示すような急峻な立ち上り部を有するVGH(Voltage for Gate High)電源電圧波形を有するラッシュ電流(飛び込み電流)が、液晶表示パネル37の所定の微細な配線パターン45aに流れ、配線パターン45aが溶断し断線することがあるという問題点があった。また、ゲート信号線駆動回路33が、COF(Chip On Film)方式で液晶表示パネル37に実装されている場合、その接続端子33aの電気的接続に用いられている異方性導電膜(Anisotropic Conductive Film : ACF)が、ラッシュ電流によって損傷し導通がとれなくなることがあるという問題点があった。また、これらの問題点は、大型のLCDになるほど発生しやすいものであった。

40

#### 【0009】

また、特許文献1に開示された構成は、残留電荷の放電時間を抵抗素子の抵抗値によって調整するものであり、ラッシュ電流による断線等を防ぐ構成については何等開示されて

50

いない。

#### 【0010】

本発明は、上記の問題点に鑑みて完成されたものであり、その目的は、X AO制御の実行時にゲートハイ電源ラインを通じて液晶表示パネル側に流れ込んだラッシュ電流が、微細な配線パターンの断線及びゲート信号線駆動回路の接続端子部の導通劣化等を起こすことを効果的に抑制することである。

#### 【課題を解決するための手段】

#### 【0011】

本発明の液晶表示装置は、基板上の第1の方向に形成された複数本のゲート信号線と、前記第1の方向と交差する第2の方向に前記ゲート信号線と交差させて形成された複数本の画像信号線と、前記ゲート信号線と前記画像信号線の交差部に形成された、薄膜トランジスタ及び画素電極を含む複数の画素部と、複数の前記ゲート信号線を駆動するゲート信号線駆動回路と、を有する液晶表示パネルと、前記液晶表示パネルの電源オフ時に複数の前記ゲート信号線のすべてにゲートハイ電圧を入力するためのゲートハイ電源電圧を前記ゲート信号線駆動回路に供給する電源回路と、前記電源回路から前記ゲート信号線駆動回路にかけて設けられているゲートハイ電源線と、を備えた液晶表示装置であって、前記ゲートハイ電源線は、抵抗が直列に接続されている構成である。

#### 【0012】

本発明の液晶表示装置は、好ましくは、前記抵抗は、抵抗値が50～200である。

#### 【0013】

また本発明の液晶表示装置は、好ましくは、前記抵抗は、前記ゲートハイ電源線の前記電源回路側の端部に接続されている。

#### 【発明の効果】

#### 【0014】

本発明の液晶表示装置は、基板上の第1の方向に形成された複数本のゲート信号線と、第1の方向と交差する第2の方向にゲート信号線と交差させて形成された複数本の画像信号線と、ゲート信号線と画像信号線の交差部に形成された、薄膜トランジスタ及び画素電極を含む複数の画素部と、複数のゲート信号線を駆動するゲート信号線駆動回路と、を有する液晶表示パネルと、液晶表示パネルの電源オフ時に複数のゲート信号線のすべてにゲートハイ電圧を入力するためのゲートハイ電源電圧をゲート信号線駆動回路に供給する電源回路と、電源回路からゲート信号線駆動回路にかけて設けられているゲートハイ電源線と、を備えた液晶表示装置であって、ゲートハイ電源線は、抵抗が直列に接続されることから、VGH電源電圧波形を緩やかな形状に鈍らせて、ゲートハイ電源線に大きなラッシュ電流が急激に流れることを抑えることができる。その結果、液晶表示パネル側に流れ込んだラッシュ電流が、微細な配線パターンの断線及びゲート信号線駆動回路の接続端子部の導通劣化等を起こすことを効果的に抑制することができる。

#### 【0015】

本発明の液晶表示装置は、抵抗は、抵抗値が50～200である場合、VGH電源電圧波形を緩やかな形状に鈍らせて、ゲートハイ電源線に大きなラッシュ電流が急激に流れることをより抑えることができる。

#### 【0016】

また本発明の液晶表示装置は、抵抗は、ゲートハイ電源線の電源回路側の端部に接続されている場合、ゲートハイ電源線において大きなラッシュ電流が急激に流れる部位がほとんどないようにすることができる。その結果、ゲートハイ電源線自体の断線の発生も抑えることができる。

#### 【図面の簡単な説明】

#### 【0017】

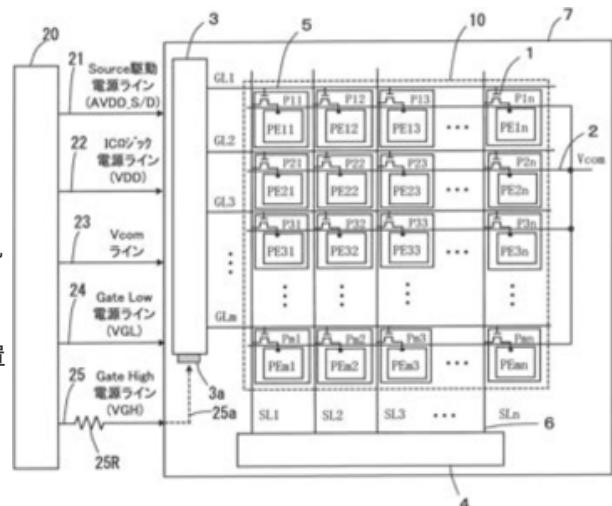

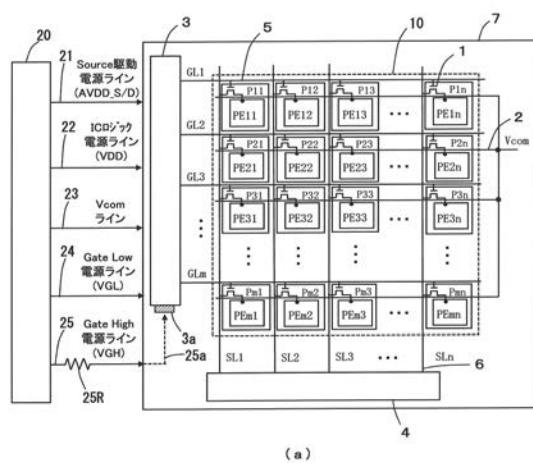

【図1】図1は、本発明の液晶表示装置について実施の形態の1例を示す図であり、液晶表示装置のプロック回路図である。

10

20

30

40

50

【図2】図2は、従来の液晶表示装置のブロック回路図である。

【発明を実施するための形態】

【0018】

以下、本発明のLCDの実施の形態について、図面を参照しながら説明する。但し、以下で参照する各図は、本発明のLCDの実施の形態における構成部材のうち、本発明のLCDを説明するための主要部を示している。従って、本発明のLCDは、図に示されていない回路基板、配線導体、制御IC, LS1等の周知の構成部材を備えていてもよい。

【0019】

本発明のLCDは、図1に示すように、ガラス基板等の基板上の第1の方向に形成された複数本のゲート信号線5と、第1の方向と交差する第2の方向にゲート信号線5と交差させて形成された複数本の画像信号線6と、ゲート信号線5と画像信号線6の交差部に形成された、TFT1及び画素電極を含む複数の画素部と、複数のゲート信号線5を駆動するゲート信号線駆動回路3と、を有する液晶表示パネル7と、液晶表示パネル7の電源オフ時に複数のゲート信号線5のすべてにゲートハイ電圧を入力するためのゲートハイ電源電圧をゲート信号線駆動回路3に供給する電源回路20と、電源回路20からゲート信号線駆動回路3にかけて設けられているゲートハイ電源線25と、を備えたLCDであって、ゲートハイ電源線25は、抵抗25Rが直列に接続されている構成である。この構成により、VGH電源電圧波形を緩やかな形状に鈍らせて、ゲートハイ電源線25に大きなラッシュ電流が急激に流れることを抑えることができる。その結果、液晶表示パネル7側に流れ込んだラッシュ電流が、微細な配線パターン25aの断線及びゲート信号線駆動回路3の接続端子3a部の導通劣化等を起こすことを効果的に抑制することができる。

10

20

30

【0020】

本発明のLCDは以下のようにして作製される。TFTを含む画素部が多数形成されたガラス基板等から成るアレイ側基板と、カラーフィルタ及びブラックマトリクスが形成されたガラス基板等成るカラー側基板とを互いに対向させて、それらの基板を所定の間隔でもって貼り合わせ、それらの基板間に液晶を充填、封入させることによって作製される。また、一般的に、カラーフィルタ側基板は、TFT及び画素電極に対向する側の面(液晶側の面)の全面に、画素電極との間で液晶に印加する垂直電界を形成するための共通電極が形成されている。また、LCDが画素電極と共通電極との間で液晶に印加する横電界を形成するIPS方式のLCDである場合、共通電極はアレイ側基板の画素電極と同じ面内に形成される。LCDが画素電極と共通電極との間で液晶に印加するフリンジ電界(端部電界)を形成するFFS方式のLCDである場合、共通電極はアレイ側基板の画素部に画素電極の上方または下方に絶縁層を挟んで形成される。また、カラーフィルタ側基板の液晶側の面には、それぞれの画素部に対応する赤(R)、緑(G)、青(B)のカラーフィルタが形成されており、それぞれの画素部を通過する光が相互に干渉することを防ぐブラックマトリクスがカラーフィルタの外周を囲むように形成されている。

【0021】

また、例えばIPS方式のLCDの場合、TFT1を含む画素部P11, P12, P13~Pmnが多数形成されたアレイ側基板は、その上の第1の方向(例えば、行方向)に形成された複数本のゲート信号線5(GL1, GL2, GL3~GLm)と、第1の方向と交差する第2の方向(例えば、列方向)にゲート信号線5と交差させて形成された複数本の画像信号線(ソース信号線)6(SL1, SL2, SL3~SLn)と、ゲート信号線5と画像信号線6の交差部に形成されたTFT1と、液晶に印加する横電界(水平電界)を形成するための画素電極PE11, PE12, PE13~PEmn及び共通電極(基準電極)と、それらを含む画素部P11, P12, P13~Pmnと、共通電極に共通電圧(Vcom)を供給する共通電圧線2と、を有する構成である。なお、図1において、3はゲート信号線5に順次ゲート信号を入力するゲート信号線駆動回路、4は画像信号線6に順次画像信号を入力する画像信号線駆動回路、7は液晶表示パネル、10は表示部である。IPS方式のLCDは、垂直電界によってツイステッドネマチック(Twisted Nematic: TN)液晶を駆動するLCDと比較して、コントラスト、グレー反転、色ずれ等の視野角特性を高めることができる。その結果、広視野角を得ることができ

40

50

るので、大型のLCDに好適に用いられている。本発明の構成は、IPS方式のLCD等のような大型のLCDに好適な構成である。即ち、大型のLCDは、画素数が多いためにゲート信号線5の本数も多くなり、ゲートハイ電源線25により大きなラッシュ電流を流す傾向があるからである。

#### 【0022】

また本発明のLCDは、1個以上のIC, LSI等の半導体素子から成るゲート信号線駆動回路3、及び1個以上のIC, LSI等の半導体素子から成る画像信号線駆動回路4等に、各種の電源電圧を供給する電源回路20を備えている。例えば、画像信号線駆動回路4内部の液晶を駆動するためのアナログ回路にアナログ回路用電源電圧を供給する画像信号(ソース)駆動電源ライン21、画像信号線駆動回路4内部のデジタルロジック回路にデジタルロジック回路用電源電圧を供給するICロジック電源ライン22、共通電圧線2に共通電圧(Vcom)を供給するVcomライン23、ゲート信号線5にゲートロー電圧を入力するためのゲートロー電源電圧をゲート信号線駆動回路3に供給するゲートロー電源ライン24、ゲート信号線5にゲートハイ電圧を入力するためのゲートハイ電源電圧をゲート信号線駆動回路3に供給するゲートハイ電源ライン25が、電源回路20から液晶表示パネル7にかけて設けられている。電源回路20は、例えばFPC等に形成されており、そのFPCから液晶表示パネル7にかけて設けられたFFC等に、画像信号(ソース)駆動電源ライン21、ICロジック電源ライン22、Vcomライン23、ゲートロー電源ライン24、ゲートハイ電源ライン25が、形成されている。

#### 【0023】

また、電源回路20は、図2(b)に示すような、液晶表示パネル7の電源オフ時にXA0制御によってゲート信号線5のすべてにゲートハイ電圧を入力するためのゲートハイ電源電圧を、ゲート信号線駆動回路3に供給する。XA0制御は、液晶表示パネル7の電源オフ時に、すべてのゲート信号線5に電気的に接続されたすべての画素電極に残留している電荷を画像信号線6を通じて放電させるために、画素電極と画像信号線6とを導通させる制御である。

#### 【0024】

本発明のLCDにおいて、抵抗(電流制限抵抗)25Rは、抵抗値が50～200であることが好ましい。この場合、図1(b)に示すように、VGH電源電圧波形を緩やかな形状に鈍らせて、ゲートハイ電源線25に大きなラッシュ電流が急激に流れることをより抑えることができる。抵抗25Rの抵抗値が50未満である場合、VGH電源電圧波形を緩やかな形状に鈍らせる効果が低下しやすい傾向がある。抵抗25Rの抵抗値が200を超える場合、VGH電源電圧のピーク電圧(波高値)が低下してすべてのゲート信号線5にハイ電圧(オン電圧)を供給することがむつかしくなる傾向がある。

#### 【0025】

また本発明のLCDは、抵抗25Rは、ゲートハイ電源線25の電源回路20側の端部に接続されていることが好ましい。この場合、ゲートハイ電源線25において大きなラッシュ電流が急激に流れる部位がほとんどないようにすることができる。その結果、ゲートハイ電源線25自体の断線の発生も抑えることができる。また、電源回路20がFPCに形成されており、そのFPCから液晶表示パネル7にかけて設けられたFFCに、画像信号(ソース)駆動電源ライン21、ICロジック電源ライン22、Vcomライン23、ゲートロー電源ライン24、ゲートハイ電源ライン25が、形成されている構成の場合、抵抗25Rは、FPCまたはFFCに設けられていることが好ましい。この場合、抵抗25Rの実装、取り外しが容易になり、抵抗値の調整が容易に行える。また、ゲートハイ電源線25の電源回路20側の端部に抵抗25Rを接続することが容易になる。

#### 【0026】

抵抗25Rは、チップ抵抗素子、薄膜抵抗素子のいずれであってもよい。チップ抵抗素子は、FPC, FFCへの実装、取り外しが容易なものであり、薄膜抵抗素子は液晶表示パネル7の基板上の配線パターン25a上に設けることができる。

#### 【0027】

10

20

30

40

50

抵抗25Rは、1個に限らず、複数個をゲートハイ電源線25に接続してもよい。その場合、VGH電源電圧波形を緩やかな形状に鈍らせることを段階的に行うことができ、大型のLCDに用いるラッシュ電流が大きくなり、さらにゲートハイ電源線25を細線化したとしても、ゲートハイ電源線25自体の断線を抑えることができる。

#### 【0028】

また、抵抗25Rが、ゲートハイ電源線25の電源回路20側の端部に接続されている場合に、ゲートハイ電源線25において、抵抗25Rと液晶表示パネル7との間の配線の線幅、線径を、電源回路20と抵抗25Rとの間の配線の線幅、線径よりも小さくすることが好みしい。この場合、ゲートハイ電源線25の大部分の線幅、線径を細線化することができる。これは、ゲートハイ電源線25における抵抗25Rと液晶表示パネル7との間の配線では、ラッシュ電流の影響が小さくなるからである。また、ゲートハイ電源線25と微細な配線パターン25aとの抵抗の差が小さくなるので、それらの電気的な接続部がラッシュ電流によって劣化しにくくなる。

10

#### 【0029】

なお、本発明のLCDは、上記実施の形態に限定されるものではなく、適宜の設計的な変更、改良を含んでいてもよい。

#### 【産業上の利用可能性】

#### 【0030】

本発明のLCDは各種電子機器に適用でき、その電子機器としては、自動車経路誘導システム（カーナビゲーションシステム）、船舶経路誘導システム、航空機経路誘導システム、スマートフォン端末、携帯電話、タブレット端末、パーソナルデジタルアシスタント（PDA）、ビデオカメラ、デジタルスチルカメラ、電子手帳、電子書籍、電子辞書、コンピュータ、パーソナルコンピュータ、複写機、ゲーム機器の端末装置、テレビジョン、商品表示タグ、価格表示タグ、産業用のプログラマブル表示装置、カーオーディオ、デジタルオーディオプレイヤー、ファクシミリ、プリンター、現金自動預け入れ払い機（ATM）、自動販売機、ヘッドアップディスプレイ装置、プロジェクタ装置、デジタル表示式腕時計、スマートウォッチ、頭部装着型画像表示装置（Head Mounted Display device：HMD）などがある。

20

#### 【符号の説明】

#### 【0031】

30

1 TFT

2 共通電圧線

3 ゲート信号線駆動回路

4 画像信号線駆動回路

5 ゲート信号線

6 画像信号線

7 液晶表示パネル

20 電源回路

25 ゲートハイ電源線

25a 抵抗

40

【図1】

(a)

(b)

【図2】

(a)

(b)

|                |                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2016188949A</a>                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2016-11-04 |

| 申请号            | JP2015069052                                                                                                                                                                                                                                                                                                          | 申请日     | 2015-03-30 |

| [标]申请(专利权)人(译) | 京瓷显示器株式会社                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 京瓷显示器有限公司                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 安田仁志                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 安田 仁志                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G02F1/133 G09G3/36 G09G3/20                                                                                                                                                                                                                                                                                           |         |            |

| F1分类号          | G02F1/133.520 G09G3/36 G09G3/20.612.G G09G3/20.670.M                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZF01 2H193/ZJ13 5C006/AA21 5C006/AF67 5C006/BB16 5C006/BC03 5C006 /BC06 5C006/BF42 5C006/GA03 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD19 5C080/DD29 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/KK02 5C080/KK07 5C080/KK21 5C080/KK23 5C080 /KK28 5C080/KK29 5C080/KK31 5C080/KK43 5C080/KK47 5C080/KK49 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                             |         |            |

## 摘要(译)

流入通过栅极高电源线的液晶显示面板侧的运行时间，本发明XAO控制冲击电流，以抑制布线图形的断线和栅极信号线驱动电路的连接端子部的引起传导恶化。【解决手段】LCD包括多个栅极信号线在基板上的第一方向的5，多个交叉的第一方向形成的第二方向图像信号线6中，栅极信号线5和图像它形成在信号线6的交叉点，一个TFT1和多个像素部，多个驱动栅极信号线的液晶显示面板7的5具有用于在液晶显示面板7的断电的时间输入栅的高电压到所有的多个栅极信号线5的栅极高功率的栅极信号线驱动电路3驱动栅极信号线的电压电源电路20供给驱动电路3，它是通过电源电路20通过栅极信号线驱动电路3中提供的栅极高电源线25，设置有，栅极高电源线25是电阻25R是串联那里。发明背景