(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-132355

(P2014-132355A)

(43) 公開日 平成26年7月17日(2014.7.17)

(51) Int.Cl.

G09G 3/36 (2006.01)

G09G 3/20 (2006.01)

F 1

G09G 3/36

G09G 3/20 624B

G09G 3/20 621B

G09G 3/20 641E

テーマコード(参考)

5C006

5C080

審査請求 有 請求項の数 2 O L (全 23 頁)

(21) 出願番号 特願2014-33830 (P2014-33830)

(22) 出願日 平成26年2月25日 (2014.2.25)

(62) 分割の表示 特願2011-235811 (P2011-235811)

の分割

原出願日 平成23年10月27日 (2011.10.27)

(71) 出願人 308036402

株式会社 J V C ケンウッド

神奈川県横浜市神奈川区守屋町3丁目12

番地

(72) 発明者 岩佐 隆行

神奈川県横浜市神奈川区守屋町3丁目12

番地

F ターム(参考) 5C006 AA14 AC25 AC26 AC28 BB16

BB28 BC06 BC12 BC20 BF03

BF04 BF09 BF27 BF33 FA41

5C080 AA10 BB05 DD22 EE29 FF11

FF12 GG12 JJ02 JJ03 JJ04

JJ05 JJ06

(54) 【発明の名称】 液晶表示装置

(57) 【要約】 (修正有)

【課題】各画素内に2つのS R A Mを用いた画素に比べて画素小型化を可能にすると共に、各画素内に2つのS R A Mを用意した場合において構成でも安定な動作を行う。

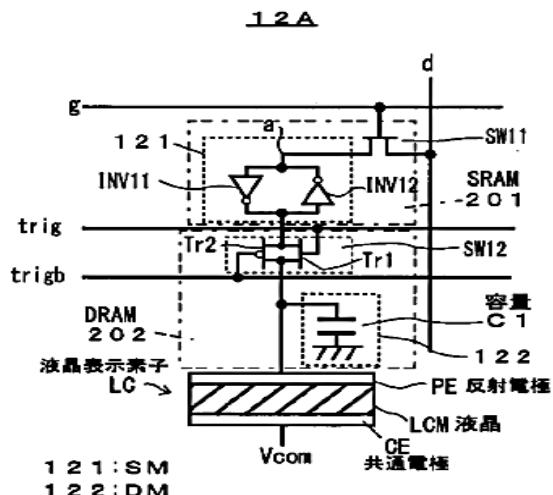

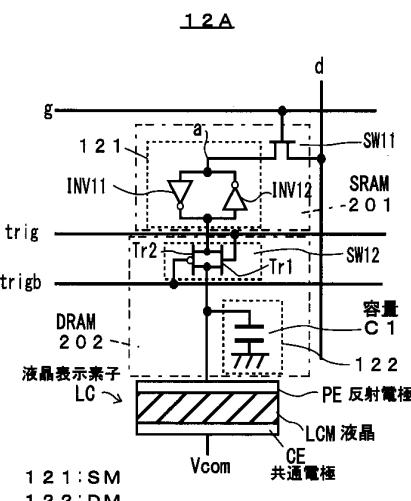

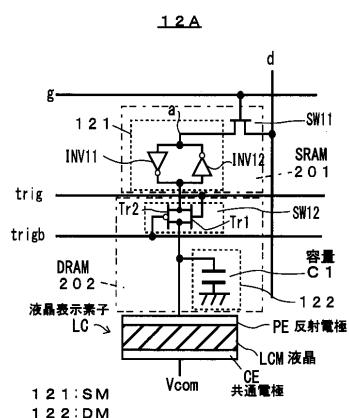

【解決手段】画素12Aは、列データ線dに出力されるデータがスイッチSW11によりサンプリングされてS R A M121に書き込まれる。画像表示部を構成する全ての画素12AのS R A M121にデータが書き込まれる。その後、トリガーパルスにより、全ての画素12AのスイッチSW12がオンとされ、S R A M121のデータがD R A M202を構成する容量C1に一斉に転送されて保持されると共に、反射電極P Eに印加される。画素12Aは、7個のトランジスタと1つの容量C1とから構成されるため、少ない数の構成素子により画素を構成できると共に、S R A M121とD R A M202と反射電極P Eとを、素子の高さ方向に有効に配置することで、画素の小型化を実現できる。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

2本の列データ線を一組とする複数組の列データ線と複数本の行走査線とがそれぞれ交差する交差部に設けられた複数の画素のそれぞれが、

対向する画素電極と共に通電極との間に液晶が充填封入された表示素子と、

映像信号の各フレームを前記映像信号の1フレーム期間より短い表示期間を持つ複数のサブフレームで表示するための正転サブフレームデータを、一組の前記2本の列データ線のうち一方の列データ線を介してサンプリングする第1のスイッチング手段と、

前記正転サブフレームデータと逆論理値の関係にある反転サブフレームデータを、一組の前記2本の列データ線のうち他方の列データ線を介してサンプリングする第2のスイッチング手段と、

前記第1及び第2のスイッチング手段によりそれぞれサンプリングされた前記正転サブフレームデータ及び反転サブフレームデータを記憶する、互いの出力端子が他方の入力端子に接続された第1及び第2のインバータからなり、前記第1及び第2のスイッチング手段と共に第1のスタティック・ランダム・アクセス・メモリを構成する第1の信号保持手段と、

前記第1の信号保持手段と前記第1のスイッチング手段との接続点から前記正転サブフレームデータを出力させる第3のスイッチング手段と、

前記第1の信号保持手段と前記第2のスイッチング手段との接続点から前記反転サブフレームデータを出力させる第4のスイッチング手段と、

前記第3及び第4のスイッチング手段を通して供給される前記第1の信号保持手段に記憶された前記正転サブフレームデータ及び反転サブフレームデータで記憶内容が書き換えられ、出力データを前記画素電極に印加する、互いの出力端子が他方の入力端子に接続された第3及び第4のインバータからなり、前記第3及び第4のスイッチング手段と共に第2のスタティック・ランダム・アクセス・メモリを構成する第2の信号保持手段とを備え、

前記第1及び第2のインバータのうち前記第1のスイッチング手段に出力端子が接続された前記第2のインバータの駆動力が、前記第2のスイッチング手段に出力端子が接続された前記第1のインバータの駆動力よりも小に設定されると共に、前記第1及び第2のインバータの駆動力は、前記第3及び第4のインバータの駆動力よりも大に設定されており、

画像表示部を構成する前記複数の画素のうち、行単位の画素毎に前記正転サブフレームデータ及び反転サブフレームデータを前記第1の信号保持手段に書き込むことを繰り返して前記複数の画素の全てに書き込んだ後、トリガパルスにより前記複数の画素全ての前記第3及び第4のスイッチング手段をオンにして、前記第1の信号保持手段に記憶された前記正転サブフレームデータ及び反転サブフレームデータにより前記複数の画素の前記第2の信号保持手段の記憶内容を書き換える動作をサブフレーム毎に行う画素制御手段を有することを特徴とする液晶表示装置。

## 【請求項 2】

複数本の列データ線と複数本の行走査線とがそれぞれ交差する交差部に設けられた複数の画素のそれぞれが、

対向する画素電極と共に通電極との間に液晶が充填封入された表示素子と、

映像信号の各フレームを前記映像信号の1フレーム期間より短い表示期間を持つ複数のサブフレームで表示するための各サブフレームデータを、前記列データ線を介してサンプリングする1つのトランジスタから構成された第1のスイッチング手段と、

前記第1のスイッチング手段によりサンプリングされた前記サブフレームデータを記憶する、互いの出力端子が他方の入力端子に接続された第1及び第2のインバータからなり、前記第1のスイッチング手段と共に第1のスタティック・ランダム・アクセス・メモリを構成する第1の信号保持手段と、

前記第1の信号保持手段に記憶された前記サブフレームデータを出力させる1つのトランジ

10

20

30

40

50

ンジスタから構成された第2のスイッチング手段と、

前記第2のスイッチング手段を通して供給される前記第1の信号保持手段に記憶された前記サブフレームデータで記憶内容が書き換えられ、出力データを前記画素電極に印加する、互いの出力端子が他方の入力端子に接続された第3及び第4のインバータからなり、前記第2のスイッチング手段と共に第2のスタティック・ランダム・アクセス・メモリを構成する第2の信号保持手段と

を備え、

前記第1及び第2のインバータのうち前記第1のスイッチング手段に出力端子が接続された前記第2のインバータの駆動力が、前記第1のインバータの駆動力よりも小に設定されると共に前記第1のスイッチング手段を構成するトランジスタの駆動力よりも小に設定され、前記第3及び第4のインバータのうち前記第2のスイッチング手段に出力端子が接続された前記第4のインバータの駆動力が、前記第3のインバータの駆動力よりも小に設定されると共に前記第2のスイッチング手段を構成するトランジスタの駆動力よりも小に設定され、かつ、前記第1のインバータの駆動力は前記第4のインバータの駆動力よりも大に設定されており、

画像表示部を構成する前記複数の画素のうち、行単位の画素毎に前記サブフレームデータを前記第1の信号保持手段に書き込むことを繰り返して前記複数の画素の全てに書き込んだ後、トリガパルスにより前記複数の画素全ての前記第2のスイッチング手段をオンにして、前記第1の信号保持手段に記憶された前記サブフレームデータにより前記複数の画素の前記第2の信号保持手段の記憶内容を書き換える動作をサブフレーム毎に行う画素制御手段を有することを特徴とする液晶表示装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は液晶表示装置に係り、特に複数ビットで表わされる階調レベルに応じて、複数のサブフレームの組み合わせによって階調表示を行う液晶表示装置に関する。

#### 【背景技術】

#### 【0002】

従来より、液晶表示装置における中間調表示方式の1つとして、サブフレーム駆動方式が知られている。時間軸変調方式の一種であるサブフレーム駆動方式では、所定の期間（例えば、動画の場合には1画像の表示単位である1フレーム）を複数のサブフレームに分割し、表示すべき階調に応じたサブフレームの組み合わせで画素を駆動する。表示される階調は、所定の期間に占める画素の駆動期間の割合によって決まり、この割合は、サブフレームの組み合わせによって特定される。

#### 【0003】

このサブフレーム駆動方式の液晶表示装置において、各画素が、マスター・ラッチ及びスレーブ・ラッチと、液晶表示素子と、第1～第3の計3つのスイッチングトランジスタとから構成されるものが知られている（例えば、特許文献1参照）。この画素では、マスター・ラッチは2つの入力端子のうち一方の入力端子に1ビットの第1のデータが第1のスイッチングトランジスタを通して印加されると共に、他方の入力端子に第1のデータとは相補的な関係にある第2のデータが第2のスイッチングトランジスタを通して印加され、行走査線を介して印加される行選択信号によりその画素が選択されたときに、上記の第1及び第2のスイッチングトランジスタをオン状態として第1のデータを書き込む。例えば、第1のデータが論理値「1」で、第2のデータが論理値「0」のとき、その画素が表示を行う。

#### 【0004】

全ての画素に対して上記と同様の動作により各データの書き込み後、そのサブフレーム期間内で全画素の第3のスイッチングトランジスタをオン状態としてマスター・ラッチに書き込んだデータを同時に読み出してスレーブ・ラッチへ読み出しスレーブ・ラッチから液晶表示素子の画素電極にそのスレーブ・ラッチでラッチしたデータを印加する。以下、各サブフ

レーム毎に上記の動作を繰り返し、1フレーム期間内の全てのサブフレームの組み合わせによって所望の階調表示を行う。

【0005】

すなわち、サブフレーム駆動方式の液晶表示装置においては、1フレーム期間内の全てのサブフレームは、その表示期間が同一又は異なる所定の期間に予め割り当てられており、各画素において最大階調表示時は全てのサブフレームにおいて表示を行い、最小階調表示時は全てのサブフレームにおいて非表示とし、それ以外の階調の場合は表示する階調に応じて表示するサブフレームを選択する。この従来の液晶表示装置は、入力されるデータが階調を示すデジタルデータであり、2段ラッチ構成のデジタル駆動方式でもある。

10

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特表2001-523847号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記の従来の液晶表示装置では、各画素内の2つのラッチはそれぞれ、スタティック・ランダム・アクセス・メモリ(SRAM)で構成されるため、トランジスタ数が多くなり、画素小型化が困難である。また、上記の2つのラッチをSRAMで構成した場合において、安定した動作ができるSRAMとスイッチングトランジスタとの具体的回路構成については、上記の特許文献1には開示されていない。

20

【0008】

本発明は以上の点に鑑みなされたもので、画素内に2つのSRAMを用いた画素に比べて画素小型化を可能にした液晶表示装置を提供することを目的とする。

【0009】

また、本発明の他の目的は、各画素内に2つのSRAMを用意した構成においても安定な動作を行い得る画素を備える液晶表示装置を提供することにある。

【課題を解決するための手段】

【0010】

上記目的を達成するため、第1の発明の液晶表示装置は、複数本の列データ線と複数本の行走査線とがそれぞれ交差する交差部に設けられた複数の画素のそれぞれが、

30

対向する画素電極と共に通電極との間に液晶が充填封入された表示素子と、映像信号の各フレームを映像信号の1フレーム期間より短い表示期間を持つ複数のサブフレームで表示するための各サブフレームデータを、列データ線を介してサンプリングする第1のスイッチング手段と、第1のスイッチング手段と共にスタティック・ランダム・アクセス・メモリを構成しており、第1のスイッチング手段によりサンプリングされたサブフレームデータを記憶する第1の信号保持手段と、第1の信号保持手段に記憶されたサブフレームデータを出力させる第2のスイッチング手段と、第2のスイッチング手段と共にダイナミック・ランダム・アクセス・メモリを構成しており、第2のスイッチング手段を通して供給される第1の信号保持手段に記憶されたサブフレームデータで記憶内容が書き換えられ、出力データを画素電極に印加する第2の信号保持手段とを備え、

40

画像表示部を構成する複数の画素のうち、行単位の画素毎にサブフレームデータを第1の信号保持手段に書き込むことを繰り返して複数の画素の全てに書き込んだ後、トリガパルスにより複数の画素全ての第2のスイッチング手段をオンにして、第1の信号保持手段に記憶されたサブフレームデータにより複数の画素の第2の信号保持手段の記憶内容を書き換える動作をサブフレーム毎に行う画素制御手段を有することを特徴とする。

【0011】

また、上記目的を達成するため、第2の発明の液晶表示装置は、第2の信号保持手段は容量により構成されており、第2のスイッチング手段は、互いに逆極性の2つのトリガパルスによりスイッチング制御されるトランスマッショングートにより構成されていること

50

を特徴とする。

【0012】

また、上記目的を達成するため、第3の発明の液晶表示装置は、第1のスイッチング手段は1つの第1のトランジスタにより構成され、第1の信号保持手段は互いの出力端子が他方の入力端子に接続された第1及び第2のインバータから構成されており、第1及び第2のインバータのうち、第1のトランジスタからみて入力側の第1のインバータを構成する第2のトランジスタの駆動力が、第1のトランジスタからみて出力側の第2のインバータを構成する第3のトランジスタの駆動力よりも大に設定され、かつ、第1のトランジスタの駆動力は第2のインバータを構成する第3のトランジスタの駆動力よりも大に設定されていることを特徴とする。

10

【0013】

また、上記目的を達成するため、第4の発明の液晶表示装置は、トランスミッショングートを構成する2つのトランジスタが表面に形成された基板の上方に多層配線層が形成されており、多層配線層のうち中間の一つの配線層と層間絶縁膜との間に形成された電極により容量が形成され、多層配線層のうち最上層の配線層により画素電極が形成されていることを特徴とする。

【0014】

また、上記目的を達成するため、第5の発明の液晶表示装置は、2本の列データ線を一組とする複数組の列データ線と複数本の行走査線とがそれぞれ交差する交差部に設けられた複数の画素のそれぞれが、

20

対向する画素電極と共に通電極との間に液晶が充填封入された表示素子と、映像信号の各フレームを映像信号の1フレーム期間より短い表示期間を持つ複数のサブフレームで表示するための正転サブフレームデータを、一組の2本の列データ線のうち一方の列データ線を介してサンプリングする第1のスイッチング手段と、正転サブフレームデータと逆論理値の関係にある反転サブフレームデータを、一組の2本の列データ線のうち他方の列データ線を介してサンプリングする第2のスイッチング手段と、第1及び第2のスイッチング手段によりそれぞれサンプリングされた正転サブフレームデータ及び反転サブフレームデータを記憶する、互いの出力端子が他方の入力端子に接続された第1及び第2のインバータからなり、第1及び第2のスイッチング手段と共に第1のスタティック・ランダム・アクセス・メモリを構成する第1の信号保持手段と、第1の信号保持手段と第1のスイッチング手段との接続点から正転サブフレームデータを出力させる第3のスイッチング手段と、第1の信号保持手段と第2のスイッチング手段との接続点から反転サブフレームデータを出力させる第4のスイッチング手段と、第3及び第4のスイッチング手段を通して供給される第1の信号保持手段に記憶された正転サブフレームデータ及び反転サブフレームデータで記憶内容が書き換えられ、出力データを画素電極に印加する、互いの出力端子が他方の入力端子に接続された第3及び第4のインバータからなり、第3及び第4のスイッチング手段と共に第2のスタティック・ランダム・アクセス・メモリを構成する第2の信号保持手段とを備え、

30

第1及び第2のインバータのうち第1のスイッチング手段に出力端子が接続された第2のインバータの駆動力が、第2のスイッチング手段に出力端子が接続された第1のインバータの駆動力よりも小に設定されると共に、第1及び第2のインバータの駆動力は、第3及び第4のインバータの駆動力よりも大に設定されており、画像表示部を構成する複数の画素のうち、行単位の画素毎に正転サブフレームデータ及び反転サブフレームデータを第1の信号保持手段に書き込むことを繰り返して複数の画素の全てに書き込んだ後、トリガーパルスにより複数の画素全ての第3及び第4のスイッチング手段をオンにして、第1の信号保持手段に記憶された正転サブフレームデータ及び反転サブフレームデータにより複数の画素の第2の信号保持手段の記憶内容を書き換える動作をサブフレーム毎に行う画素制御手段を有することを特徴とする。

40

【0015】

更に、上記目的を達成するため、第6の発明の液晶表示装置は、複数本の列データ線と

50

複数本の行走査線とがそれぞれ交差する交差部に設けられた複数の画素のそれぞれが、

対向する画素電極と共に通電極との間に液晶が充填封入された表示素子と、映像信号の各フレームを映像信号の1フレーム期間より短い表示期間を持つ複数のサブフレームで表示するための各サブフレームデータを、列データ線を介してサンプリングする1つのトランジスタから構成された第1のスイッチング手段と、第1のスイッチング手段によりサンプリングされたサブフレームデータを記憶する、互いの出力端子が他方の入力端子に接続された第1及び第2のインバータからなり、第1のスイッチング手段と共に第1のスタティック・ランダム・アクセス・メモリを構成する第1の信号保持手段と、第1の信号保持手段に記憶されたサブフレームデータを出力させる1つのトランジスタから構成された第2のスイッチング手段と、第2のスイッチング手段を通して供給される第1の信号保持手段に記憶されたサブフレームデータで記憶内容が書き換えられ、出力データを画素電極に印加する、互いの出力端子が他方の入力端子に接続された第3及び第4のインバータからなり、第2のスイッチング手段と共に第2のスタティック・ランダム・アクセス・メモリを構成する第2の信号保持手段とを備え、

第1及び第2のインバータのうち第1のスイッチング手段に出力端子が接続された第2のインバータの駆動力が、第1のインバータの駆動力よりも小に設定されると共に第1のスイッチング手段を構成するトランジスタの駆動力よりも小に設定され、第3及び第4のインバータのうち第2のスイッチング手段に出力端子が接続された第4のインバータの駆動力が、第3のインバータの駆動力よりも小に設定されると共に第2のスイッチング手段を構成するトランジスタの駆動力よりも小に設定され、かつ、第1のインバータの駆動力は第4のインバータの駆動力よりも大に設定されており、

画像表示部を構成する複数の画素のうち、行単位の画素毎にサブフレームデータを第1の信号保持手段に書き込むことを繰り返して複数の画素の全てに書き込んだ後、トリガパルスにより複数の画素全ての第2のスイッチング手段をオンにして、第1の信号保持手段に記憶されたサブフレームデータにより複数の画素の第2の信号保持手段の記憶内容を書き換える動作をサブフレーム毎に行う画素制御手段を有することを特徴とする。

#### 【発明の効果】

#### 【0016】

本発明によれば、画素内に2つのSRAMを用いた従来の液晶表示装置に比べて画素の小型化を可能にできる。また、本発明によれば、画素内に2つのSRAMを用意した場合においても従来の液晶表示装置に比べて安定な動作を行うことができる。

#### 【画面の簡単な説明】

#### 【0017】

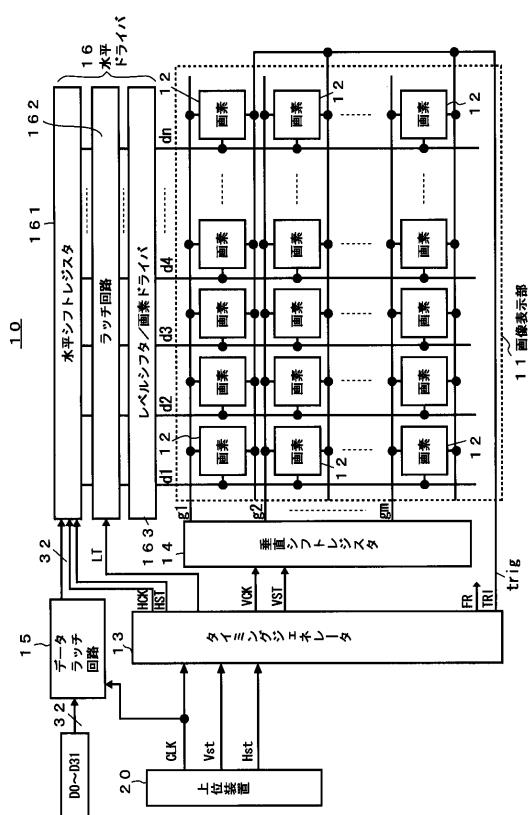

【図1】本発明の液晶表示装置の一実施の形態の全体構成図である。

【図2】本発明の要部である画素の第1の実施の形態の回路図である。

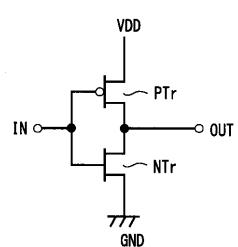

【図3】インバータの一例の回路図である。

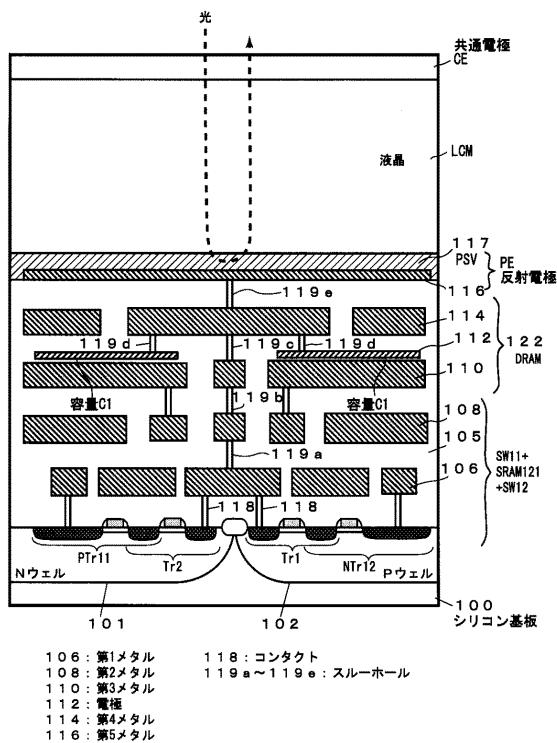

【図4】図2に示す一画素の一例の断面構造図である。

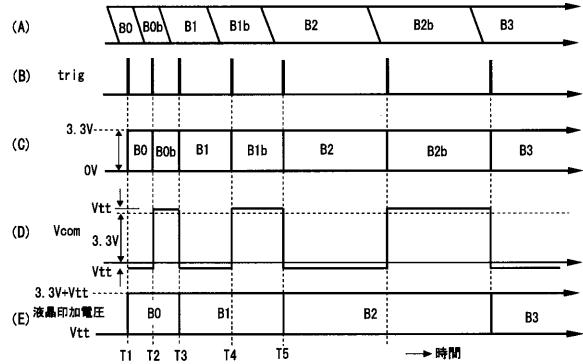

【図5】本発明の液晶表示装置における画素の動作説明用タイミングチャートである。

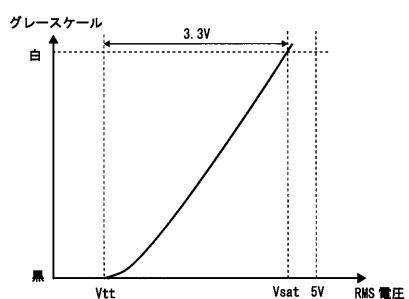

【図6】液晶表示装置の液晶の飽和電圧および液晶の閾値電圧を、2値重みつきパルス幅変調データとして多重化する説明図である。

【図7】本発明の要部である画素の第2の実施の形態の回路図である。

【図8】図7の2つのSRAMを構成する各インバータ間の駆動力の大小関係を説明する図である。

【図9】本発明の要部である画素の第3の実施の形態の回路図である。

#### 【発明を実施するための形態】

#### 【0018】

以下、図面を用いて本発明の実施形態について説明する。

#### 【0019】

図1は、本発明になる液晶表示装置の一実施の形態のプロック図を示す。同図において、本実施の形態の液晶表示装置10は、複数の画素12が規則的に配置された画像表示部

10

20

30

40

50

11と、タイミングジェネレータ13と、垂直シフトレジスタ14と、データラッチ回路15と、水平ドライバ16とから構成される。更に、水平ドライバ16は、水平シフトレジスタ161と、ラッチ回路162と、レベルシフタ／画素ドライバ163とから構成される。

#### 【0020】

画像表示部11は、垂直シフトレジスタ14に一端が接続されて行方向(X方向)に延在するm本(mは2以上の自然数)の行走査線g1～gmと、レベルシフタ／画素ドライバ163に一端が接続されて列方向(Y方向)に延在するn本(nは2以上の自然数)の列データ線d1～dnとが交差する各交差部に設けられ、二次元マトリクス状に配置された、全部でm×n個の画素12を有する。本発明は画素12の回路構成に特徴があり、その各実施の形態については後述する。画像表示部11内の全ての画素12は、一端がタイミングジェネレータ13に接続されたトリガ線trigに共通接続されている。10

#### 【0021】

なお、図1では列データ線はn本の列データ線d1～dnを示しているが、正転データ用列データ線djと反転データ用列データ線dbjとを一組とする、全部でn組の列データ線を使用する場合もある。正転データ用列データ線djが伝送する正転データと、反転データ用列データ線dbjが伝送する反転データとは、常に逆論理値の関係(相補的な関係)にある1ビットのデータである。また、トリガ線trigも図1では1本のみ示しているが、正転トリガパルス用トリガ線trigと反転トリガパルス用トリガ線trigbとからなる2本のトリガ線を使用する場合もある。正転トリガパルス用トリガ線trigが伝送する正転トリガパルスと、反転トリガパルス用トリガ線trigbが伝送する反転トリガパルスとは、常に逆論理値の関係(相補的な関係)にある。20

#### 【0022】

タイミングジェネレータ13は、上位装置20から垂直同期信号Vst、水平同期信号Hst、基本クロックCLKといった外部信号を入力信号として受け、これらの外部信号に基づいて、交流化信号FR、VスタートパルスVST、HスタートパルスHST、クロック信号VCK及びHCK、ラッチパルスLT、トリガパルストRIなどのが各種の内部信号を生成する。

#### 【0023】

上記の内部信号のうち、交流化信号FRは、1サブフレーム毎に極性反転する信号であり、画像表示部11を構成する画素12内の液晶表示素子の共通電極に、後述する共通電極電圧Vcomとして供給される。スタートパルスVSTは、後述する各サブフレームの開始タイミングに出力されるパルス信号であり、このスタートパルスVSTによって、サブフレームの切替わりが制御される。スタートパルスHSTは、水平シフトレジスタ161に入力する開始タイミングに出力されるパルス信号である。クロック信号VCKは、垂直シフトレジスタ14における1水平走査期間(1H)を規定するシフトクロックであり、VCKのタイミングで垂直シフトレジスタ14がシフト動作を行う。クロック信号HCKは、水平シフトレジスタ161におけるシフトクロックであり、32ビット幅でデータをシフトしていくための信号である。30

#### 【0024】

ラッチパルスLTは、水平シフトレジスタ161が水平方向の1行の画素数分のデータをシフトし終わったタイミングで出力されるパルス信号である。トリガパルストRIは、トリガ線trigを通して画像表示部11内の全画素12に供給されるパルス信号である。このトリガパルストRIは、サブフレーム期間内で画像表示部11内の各画素12内の第1の信号保持手段に順次データを書き込み終わった直後に outputされ、そのサブフレーム期間内で画像表示部11内の全画素12の第1の信号保持手段のデータと同じ画素内の第2の信号保持手段に一度に転送する。40

#### 【0025】

垂直シフトレジスタ14は、それぞれのサブフレームの最初に供給されるVスタートパルスVSTを、クロック信号VCKに従って転送し、行走査線g1～gmに対して行走査信50

号を1H単位で順次排他的に供給する。これにより、画像表示部11において最も上にある行走査線 $g_1$ から最も下にある行走査線 $g_m$ に向って、行走査線が1本ずつ順次1H単位で選択されていく。

#### 【0026】

データラッチ回路15は、図示しない外部回路から供給される1サブフレーム毎に分割された32ビット幅のデータを、上位装置20からの基本信号CLKに基づいてラッチした後、基本信号CLKに同期して水平シフトレジスタ161へ出力する。ここで、映像信号の1フレームを、その映像信号の1フレーム期間より短い表示期間を持つ複数のサブフレームに分割してサブフレームの組み合わせによって階調表示を行う本実施の形態では、上記の外部回路は映像信号の各画素毎の階調を示す階調データを、上記複数のサブフレーム全体で各画素の階調を表示するための各サブフレーム単位の1ビットのサブフレームデータに変換する。そして、上記外部回路は、更に同じサブフレームにおける32画素分の上記サブフレームデータをまとめて上記32ビット幅のデータとしてデータラッチ回路15に供給している。

10

#### 【0027】

水平シフトレジスタ161は、1ビットシリアルデータの処理系でみた場合、タイミングジェネレータ13から1Hの最初に供給されるHスタートパルスHSTによりシフトを開始し、データラッチ回路15から供給される32ビット幅のデータをクロック信号HCKに同期してシフトする。ラッチ回路162は、水平シフトレジスタ161が画像表示部11の1行分の画素数nと同じnビット分のデータをシフトし終わった時点でタイミングジェネレータ13から供給されるラッチパルスLTに従って、水平シフトレジスタ161から並列に供給されるnビット分のデータ（すなわち、同じ行のn画素分のサブフレームデータ）をラッチし、レベルシフタ／画素ドライバ163のレベルシフタへ出力する。ラッチ回路162へのデータ転送が終了すると、タイミングジェネレータ13からHスタートパルスが再び出力され、水平シフトレジスタ161はクロック信号HCKに従ってデータラッチ回路15からの32ビット幅のデータのシフトを再開する。

20

#### 【0028】

レベルシフタ／画素ドライバ163のレベルシフタは、ラッチ回路162によりラッチされて供給される1行のn画素に対応したn個のサブフレームデータの信号レベルを液晶駆動電圧までレベルシフトする。レベルシフタ／画素ドライバ163の画素ドライバは、レベルシフト後の1行のn画素に対応したn個のサブフレームデータをn本のデータ線d1～dnに並列に出力する。

30

#### 【0029】

水平ドライバ16を構成する水平シフトレジスタ161、ラッチ回路162及びレベルシフタ／画素ドライバ163は、1H内において今回データを書き込む画素行に対するデータの出力と、次の1H内でデータを書き込む画素行に関するデータのシフトとを並行して行う。ある水平走査期間において、ラッチされた1行分のn個のサブフレームデータが、データ信号としてそれぞれn本のデータ線d1～dnに並列に、かつ、一斉に出力される。

40

#### 【0030】

画像表示部11を構成する複数の画素12のうち、垂直シフトレジスタ14からの行走査信号により選択された1行のn個の画素12は、レベルシフタ／画素ドライバ163から一斉に出力された1行分のn個のサブフレームデータをn本のデータ線d1～dnを介してサンプリングして各画素12内の後述する第1の信号保持手段に書き込む。

#### 【0031】

次に、本発明の液晶表示装置の要部の画素12の各実施の形態について詳細に説明する。

#### 【0032】

図2は、本発明の要部である画素の第1の実施の形態の回路図を示す。同図において、本実施の形態の画素12Aは、図1中の任意の1本の列データ線dと任意の1本の行走査

50

線 g との交差部に設けられた画素で、第 1 のスイッチング手段を構成するスイッチ SW 1 1 と第 1 の信号保持手段 (SM) 1 2 1 とから構成されるスタティック・ランダム・アクセス・メモリ (SRAM) 2 0 1 と、第 2 のスイッチング手段を構成するスイッチ SW 1 2 と第 2 の信号保持手段 (DM) 1 2 2 とから構成されるダイナミック・ランダム・アクセス・メモリ (DRAM) 2 0 2 と、液晶表示素子 LC とより構成されている。液晶表示素子 LC は、離間対向配置された反射電極 PE と共に通電極 CE との間の空間に、液晶 LC M が充填封入された公知の構造である。

#### 【0033】

スイッチ SW 1 1 は、ゲートが行走査線 g に接続され、ドレインが列データ線 d に接続され、ソースが SM 1 2 1 の入力端子に接続されている N チャネル MOS 型トランジスタ (以下、NMOS トランジスタという) により構成されている。SM 1 2 1 は、一方の出力端子が他方の入力端子に接続された 2 つのインバータ INV 1 1 及び INV 1 2 からなる自己保持型メモリである。インバータ INV 1 1 は、その入力端子がインバータ INV 1 2 の出力端子と SW 1 1 を構成する NMOS トランジスタのソースとに接続されている。インバータ INV 1 2 は、その入力端子がスイッチ SW 1 2 とインバータ INV 1 1 の出力端子とに接続されている。インバータ INV 1 1 及び INV 1 2 は、いずれも図 3 に示すような、互いのゲート同士及びドレイン同士が接続された、P チャンネル MOS 型トランジスタ (以下、PMOS トランジスタという) P Tr 及び NMOS トランジスタ N Tr とからなる公知の CMOS インバータの構成であるが、それぞれの駆動力が異なる。

#### 【0034】

すなわち、スイッチ SW 1 1 から見て SM 1 2 1 を構成している入力側のインバータ INV 1 1 内のトランジスタは、スイッチ SW 1 1 から見て SM 1 2 1 を構成している出力側のインバータ INV 1 2 内のトランジスタに比較して、駆動力の大きいトランジスタを用いている。さらにスイッチ SW 1 1 を構成している NMOS トランジスタの駆動力は、インバータ INV 1 2 を構成している NMOS トランジスタの駆動力よりも大きいトランジスタで構成されている。

#### 【0035】

これは、SM 1 2 1 のデータを書き換える場合、特に SM 1 2 1 のスイッチ SW 1 1 の入力側の電圧 a が “L” レベルで、列データ線 d を介して送られてくるデータが “H” レベルの場合、インバータ INV 1 1 が反転する入力電圧よりも電圧 a を高くする必要があるからである。“H” レベルのときの電圧 a はインバータ INV 1 2 を構成する NMOS トランジスタの電流とスイッチ SW 1 1 を構成する NMOS トランジスタの電流との比によって決まる。このとき、スイッチ SW 1 1 は NMOS トランジスタであるため、スイッチ SW 1 1 がオンのときは列データ線 d を介して送られてくる電源の VDD 側の電圧はトランジスタの閾値電圧 Vth により SM 1 2 1 に入力されず、“H” レベルの電圧は VDD から Vth 分低い電圧になる。しかもこの電圧ではトランジスタの Vth 近辺で駆動することになるため、電流が殆ど流れなくなる。つまり、スイッチ SW 1 1 を導通する電圧 a が高くなるほど、スイッチ SW 1 1 で流す電流は少なくなる。

#### 【0036】

つまり、電圧 a が “H” レベルのときにインバータ INV 1 1 の入力側のトランジスタが反転する電圧以上に達するためには、スイッチ SW 1 1 に流れる電流が、出力側のインバータ INV 1 2 のトランジスタを構成する NMOS トランジスタを流れる電流よりも大きい必要がある。従って、スイッチ SW 1 1 を構成している NMOS トランジスタの駆動力はインバータ INV 1 2 を構成している NMOS トランジスタの駆動力よりも大きく構成するため、これを考慮してスイッチ SW 1 1 を構成している NMOS トランジスタのトランジスタサイズと、インバータ INV 1 2 を構成している NMOS トランジスタのトランジスタサイズとを決める必要がある。

#### 【0037】

スイッチ SW 1 2 は、互いのドレイン同士が接続され、かつ、互いのソース同士が接続された NMOS トランジスタ Tr1 と PMOS トランジスタ Tr2 とからなる公知のトランジ

10

20

30

40

50

ミッショングートの構成とされている。N MOSトランジスタTr1のゲートは正転トリガパルス用トリガ線trigに接続され、PMOSトランジスタTr2のゲートは反転トリガパルス用トリガ線trig bに接続されている。

#### 【0038】

また、スイッチSW12は一方の端子がSM121に接続され、他方の端子がDM122と液晶表示素子LCの反射電極PEとにそれぞれ接続されている。従って、スイッチSW12はトリガ線trigを介して供給される正転トリガパルスが“H”レベル（このときは、トリガ線trig bを介して供給される反転トリガパルスは“L”レベル）のときはオンとされ、SM121の記憶データを読み出してDM122及び反射電極PEへ転送する。また、スイッチSW12はトリガ線trigを介して供給される正転トリガパルスが“L”レベル（このときは、トリガ線trig bを介して供給される反転トリガパルスは“H”レベル）のときはオフとされ、SM121の記憶データの読み出しあは行わない。10

#### 【0039】

スイッチSW12はN MOSトランジスタTr1とPMOSトランジスタTr2とからなる公知のトランスマッショングートの構成とされているため、GNDからVDDまでの範囲の電圧をオン、オフすることができる。つまり、N MOSトランジスタTr1とPMOSトランジスタTr2の各ゲートに印加される信号がGND側の電位（“L”レベル）のときは、PMOSトランジスタTr2が導通することができない代わりに、N MOSトランジスタTr1が低抵抗で導通することができる。一方、ゲート入力信号がVDD側の電位（“H”レベル）のときはN MOSトランジスタTr1が導通することができない代わりに、PMOSトランジスタTr2が低抵抗で導通することができる。従って、トリガ線trigを介して供給される正転トリガパルスと、トリガ線trig bを介して供給される反転トリガパルスにより、スイッチSW12を構成するトランスマッショングートをオン／オフ制御することによって、GNDからVDDまでの電圧範囲を低抵抗、高抵抗でスイッチングすることができる。20

#### 【0040】

DM122は、容量C1により構成されている。ここで、SM121の記憶データとDM122の保持データとが異なっていた場合、スイッチSW12がオンとされ、SM121の記憶データがDM122へ転送されたときには、DM122の保持データをSM121の記憶データで置き換える必要がある。30

#### 【0041】

DM122を構成する容量C1の保持データが書き換わる場合、その保持データは充電、または放電によって変化し、また容量C1の充放電はインバータINV11の出力信号によって駆動される。容量C1の保持データを充電によって“L”レベルから“H”レベルに書き換える場合、インバータINV11の出力信号は“H”であり、このときINV11を構成するPMOSトランジスタ（図3のPTr）がオン、NMOSトランジスタ（図3のNTr）がオフするため、インバータINV11のPMOSトランジスタのソースに接続されている電源電圧VDDによって容量C1が充電される。一方、容量C1の保持データを放電によって“H”レベルから“L”レベルに書き換える場合、インバータINV11の出力信号は“L”レベルであり、このときインバータINV11を構成するNMOSトランジスタ（図3のNTr）がオン、PMOSトランジスタ（図3のPTr）がオフするため、容量C1の蓄積電荷がインバータINV11のNMOSトランジスタ（図3のNTr）を通してGNDへ放電される。スイッチSW12は、上述したトランスマッショングートを用いたアナログスイッチの構成であるため、上記の容量C1の高速な充放電が可能になる。40

#### 【0042】

更に、本実施の形態ではインバータINV11の駆動力は、インバータINV12の駆動力よりも大きく設定されているため、DM122を構成する容量C1を高速に充放電駆動することが可能である。また、スイッチSW12をオンにすると、容量C1に蓄えられた電荷はインバータINV12の入力ゲートにも影響を与えるが、インバータINV12

に対してインバータINV11の駆動力を大きく設定していることにより、インバータINV12のデータ入力反転よりもインバータINV11による容量C1の充放電が優先され、SM121の記憶データを書き換えてしまうことはない。

#### 【0043】

なお、SRAM201とDRAM202をそれぞれ容量とスイッチとからなる2段のDRAM構成とすることも考えられるが、この場合、SM121の代わりに用いられる容量とDMを構成する容量とを導通させた場合、電荷の中和が発生してGND、VDD電圧の振幅はとれなくなる。これに対し、図2に示した画素12Aによれば、GND、VDD電圧の振幅で1ビットデータをSM121からDM122へ転送することができ、同じ電源電圧で駆動した場合、液晶表示素子LCの印加電圧を高く設定することができるようになり、ダイナミックレンジを大きく取ることが可能になる。

10

#### 【0044】

また、SRAM201を容量とスイッチとからなる構成に変更し、DRAM202をSRAMに変更することも考えられるが、この場合は図2の本実施の形態の画素12Aと比較して動作が不安定という問題がある。すなわち、上記構成の場合SM121の代わりに用いられる容量に蓄えた電荷によってDM122の代わりに用いられるSRAMの記憶データを書き換える必要があるが、通常は容量の電荷保持能力よりもSRAMによるメモリのデータ保持能力が強いため、DM122の代わりに用いられるSRAMの記憶データによって前段のSM121の代わりに用いられる容量の電荷を書き換えてしまう、という不具合が生じる可能性がある。更に、この場合、SM121の代わりに用いられる容量が後段SRAMデータによって書き換わらないようにすると、容量を大きく取る必要があるため、画素ピッチが増大し、画素小型化に向かないという課題がある。

20

#### 【0045】

図2に示した本実施の形態の画素12Aによれば、上記のように、液晶表示素子LCの印加電圧を高く設定することができ、ダイナミックレンジを大きく取ることが可能になるという効果だけではなく、画素の小型化が可能であるという大なる効果が得られる。この画素の小型化は、図2に示したようにインバータINV11及びINV12が各2個のトランジスタから構成されるので、計7個のトランジスタと1つの容量C1とから構成され、従来の画素よりも少ない数の構成素子により画素を構成できるからという理由に加えて、以下に説明するように、SM121とDM122と反射電極PEとを、素子の高さ方向に有効に配置することができるという理由による。

30

#### 【0046】

図4は、本発明になる液晶表示装置の要部の画素の一実施の形態の断面構成図を示す。図2に示した容量C1には、配線間で容量を形成するMIM(Metal-Insulator-Metal)容量や、基板-ポリシリコン間で容量を形成するDiffusion容量、2層ポリシリコン間で容量を形成するPIP(Poly-Insulator-Poly)容量などを用いることができる。図4は、このうちMIMにより容量C1を構成した場合の液晶表示装置の断面構成図を示す。

#### 【0047】

図4において、シリコン基板100に形成されたNウェル101上に、ドレインとなる拡散層を共通化することでドレイン同士が接続されたインバータINV11のPMOSトランジスタPTR11と、スイッチSW12のPMOSトランジスタTr2とが形成されている。また、シリコン基板100に形成されたPウェル102上に、ドレインとなる拡散層を共通化することでドレイン同士が接続されたインバータINV12のNMOSトランジスタNTr12と、スイッチSW12のNMOSトランジスタTr1とが形成されている。なお、図4にはインバータINV11を構成するNMOSトランジスタとインバータINV12を構成するPMOSトランジスタとは図示されていない。

40

#### 【0048】

また、上記の各トランジスタPTR11、Tr2、Tr1、NTr12の上方には、層間絶縁膜105をメタル間に介在させて第1メタル106、第2メタル108、第3メタル110、電極112、第4メタル114、第5メタル116が積層されている。第5メタル

50

116は画素毎に形成される反射電極P Eを構成している。スイッチSW12を構成するN M O SトランジスタTr1及びP M O SトランジスタTr2の各ソースを構成する各拡散層は、コンタクト118により第1メタル106にそれぞれ電気的に接続され、更に、スルーホール119a、119b、119c、119eを通して第2メタル108、第3メタル110、第4メタル114、第5メタル116に電気的に接続されている。すなわち、スイッチSW12を構成するN M O SトランジスタTr1及びP M O SトランジスタTr2の各ソースは、反射電極P Eに電気的に接続されている。

#### 【0049】

更に、反射電極P E(第5メタル116)上には保護膜としてパッシベーション膜(P S V)117が形成され、透明電極である共通電極C Eに離間対向配置されている。それら画素電極P Eと共通電極C Eとの間に液晶L C Mが充填封止されて、液晶表示素子L Cを構成している。10

#### 【0050】

ここで、第3メタル110上には層間絶縁膜105を介して電極112が形成されている。この電極112は、第3メタル110及び第3メタル110との間の層間絶縁膜105と共に容量C1を構成している。M I Mにより容量C1を構成すると、S M 1 2 1とスイッチSW11、スイッチSW12はトランジスタと第1メタル106及び第2メタル108の1,2層配線、D M 1 2 2はトランジスタ上部の第3メタル110を利用したM I M配線にて形成することが可能になる。電極112は、スルーホール119dを介して第4メタルに電気的に接続され、更に第4メタル114はスルーホール119eを介して反射電極P Eに電気的に接続されているため、容量C1は反射電極P Eに電気的に接続されている。20

#### 【0051】

図示しない光源からの光は、共通電極C E及び液晶L C Mを透過して反射電極P E(第5メタル116)に入射して反射され、元の入射経路を逆進して共通電極C Eを通して出射される。

#### 【0052】

本実施の形態によれば、図4に示すように、5層配線である第5メタル116を反射電極P Eに割り当てるにより、S M 1 2 1とD M 1 2 2、反射電極P Eを高さ方向に有効に配置することが可能になり、画素小型化が実現できる。これにより、例えば3μm以下のピッチの画素を電源電圧3.3Vのトランジスタで構成できる。この3μmピッチの画素では対角の長さ0.55インチの横方向4000画素、縦方向2000画素の液晶表示パネルを実現できる。30

#### 【0053】

次に、本実施の形態の画素12Aを用いた図1の液晶表示装置10の動作について、図5のタイミングチャートを併せ参照して説明する。

#### 【0054】

前述したように、図1の液晶表示装置10において、垂直シフトレジスタ14からの行走査信号により行走査線g1から行走査線gmに向って、行走査線が1本ずつ順次1H単位で選択されていくため、画像表示部11を構成する複数の画素12(12A)は、選択された行走査線に共通に接続された1行のn個の画素単位でデータの書き込みが行われる。そして、画像表示部11を構成する複数の画素12(12A)の全てに書き込みが終わった後、トリガパルスに基づいて全画素一斉に読み出しが行われる。40

#### 【0055】

図5(A)は、水平ドライバ16から列データ線d(d1~dn)に出力される1ビットのサブフレームデータの一画素の書き込み期間及び読み出し期間を模式的に示す。左下がりの斜線が書き込み期間を示す。なお、図5(A)中、B0b、B1b、B2bはビットB0、B1、B2のデータの反転データであることを示す。また、図5(B)は、タイミングジェネレータ13から正転トリガパルス用トリガ線trigに出力されるトリガパルスを示す。このトリガパルスは1サブフレーム毎に出力される。なお、反転トリガパルス用ト50

リガ線 trig\_b に出力される反転トリガパルスは正転トリガパルスと常に逆論理値であるのでその図示は省略してある。

#### 【0056】

まず、画素 12A は行走査信号により選択されると、スイッチ SW11 がオンとされ、その時列データ線 d に出力される図 5 (A) のビット B0 の正転サブフレームデータがスイッチ SW11 によりサンプリングされて画素 12A の SM121 に書き込まれる。以下、同様にして、画像表示部 11 を構成する全ての画素 12A の SM121 にビット B0 のサブフレームデータの書き込みが行われ、その書き込み動作が終了した後の図 5 に示す時刻 T1 で、図 5 (B) に示すように “H” レベルの正転トリガパルスが画像表示部 11 を構成する全ての画素 12A に同時に供給される。

10

#### 【0057】

これにより、全ての画素 12A のスイッチ SW12 がオンとされるため、SM121 に記憶されているビット B0 の正転サブフレームデータがスイッチ SW12 を通して DM122 を構成する容量 C1 に一斉に転送されて保持されると共に、反射電極 PE に印加される。この容量 C1 によるビット B0 の正転サブフレームデータの保持期間は、時刻 T1 から図 5 (B) に示すように次の “H” レベルの正転トリガパルスが入力される時刻 T2 までの 1 サブフレーム期間である。図 5 (C) は、反射電極 PE に印加されるサブフレームデータのビットを模式的に示す。

#### 【0058】

ここで、サブフレームデータのビット値が「1」、すなわち “H” レベルのときには反射電極 PE には電源電圧 VDD (ここでは 3.3V) が印加され、ビット値が「0」、すなわち “L” レベルのときには反射電極 PE には 0V が印加される。一方、液晶表示素子 LC の共通電極 CE には、GND、VDD に制限されることなく、自由な電圧が共通電極電圧 Vcom として印加できるようになっており、“H” レベルの正転トリガパルスが入力される時と同時タイミングで規定の電圧に切り替わるようにされている。ここでは、共通電極電圧 Vcom は、正転サブフレームデータが反射電極 PE に印加されるサブフレーム期間は、図 5 (D) に示すように 0V よりも液晶の閾値電圧 Vtt だけ低い電圧に設定される。

20

#### 【0059】

液晶表示素子 LC は、反射電極 PE の印加電圧と共通電極電圧 Vcom との差電圧の絶対値である液晶 LCM の印加電圧に応じた階調表示を行う。従って、ビット B0 の正転サブフレームデータが反射電極 PE に印加される時刻 T1 ~ T2 の 1 サブフレーム期間では、液晶 LCM の印加電圧は、図 5 (E) に示すように、サブフレームデータのビット値が「1」のときは  $3.3V + V_{tt}$  ( $= 3.3V - (-V_{tt})$ ) となり、サブフレームデータのビット値が「0」のときは  $+V_{tt}$  ( $= 0V - (-V_{tt})$ ) となる。

30

#### 【0060】

図 6 は、液晶の印加電圧 (RMS 電圧) と液晶のグレースケール値との関係を示す。図 6 に示すように、グレースケール値曲線は黒のグレースケール値が液晶の閾値電圧 Vtt の RMS 電圧に対応し、白のグレースケール値が液晶の飽和電圧 Vsat ( $= 3.3V + V_{tt}$ ) の RMS 電圧に対応するようにシフトされる。グレースケール値を液晶応答曲線の有効部分に一致させることができるのである。従って、液晶表示素子 LC は上記のように液晶 LCM の印加電圧が ( $3.3V + V_{tt}$ ) のときは白を表示し、 $+V_{tt}$  のときは黒を表示する。

40

#### 【0061】

続いて、上記のビット B0 の正転サブフレームデータを表示しているサブフレーム期間内において、図 5 (A) に B0b で示すようにビット B0 の反転サブフレームデータの画素 12A の SM121 への書き込みが順番に開始される。そして、画像表示部 11 の全画素 12A の SM121 にビット B0 の反転サブフレームデータが書き込まれ、その書き込み終了後の時刻 T2 で図 5 (B) に示すように “H” レベルの正転トリガパルスが画像表示部 11 を構成する全ての画素 12A に同時に供給される。

#### 【0062】

50

これにより、全ての画素 12A のスイッチ SW12 がオンとされるため、SM121 に記憶されているビット B0 の反転サブフレームデータがスイッチ SW12 を通して DM122 を構成する容量 C1 に転送されて保持されると共に、反射電極 PE に印加される。この容量 C1 によるビット B0 の反転サブフレームデータの保持期間は、時刻 T2 から図 5 (B) に示すように次の “H” レベルの正転トリガパルスが入力される時刻 T3 までの 1 サブフレーム期間である。ここで、ビット B0 の反転サブフレームデータはビット B0 の正転サブフレームデータと常に逆論理値の関係にあるため、ビット B0 の正転サブフレームデータが「1」のときは「0」、ビット B0 の正転サブフレームデータが「0」のときは「1」である。

## 【0063】

10

一方、共通電極電圧 Vcom は、反転サブフレームデータが反射電極 PE に印加されるサブフレーム期間は、図 5 (D) に示すように 3.3V よりも液晶の閾値電圧 Vtt だけ高い電圧に設定される。従って、ビット B0 の反転サブフレームデータが反射電極 PE に印加される時刻 T2 ~ T3 の 1 サブフレーム期間では、液晶 LCM の印加電圧は、サブフレームデータのビット値が「1」のときは  $-V_{tt} (= 3.3V - (3.3V + V_{tt}))$  となり、サブフレームデータのビット値が「0」のときは  $-3.3V - V_{tt} (= 0V - (3.3V + V_{tt}))$  となる。

## 【0064】

20

従って、ビット B0 の正転サブフレームデータのビット値が「1」であった時は続いて入力されるビット B0 の反転サブフレームデータのビット値が「0」であるため、液晶 LCM の印加電圧は、 $- (3.3V + V_{tt})$  となり、液晶 LCM に印加される電位の方向はビット B0 の正転サブフレームデータの時とは逆となるが絶対値が同じであるため、画素 12A はビット B0 の正転サブフレームデータ表示時と同じ白を表示する。同様に、ビット B0 の正転サブフレームデータのビット値が「0」であった時は続いて入力されるビット B0 の反転サブフレームデータのビット値が「1」であるため、液晶 LCM の印加電圧は、 $-V_{tt}$  となり、液晶 LCM に印加される電位の方向はビット B0 の正転サブフレームデータの時とは逆となるが絶対値が同じであるため、画素 12A は黒を表示する。

## 【0065】

30

従って、画素 12A は図 5 (E) に示すように、時刻 T1 ~ 時刻 T3 までの 2 サブフレーム期間は、ビット B0 とビット B0 の相補ビット B0b とで同じ階調を表示すると共に、液晶 LCM の電位方向がサブフレーム毎に反転する交流駆動が行われるため、液晶 LCM の焼き付きを防止することができる。

## 【0066】

続いて、上記の相補ビット B0b の反転サブフレームデータを表示しているサブフレーム期間内において、図 5 (A) に B1 で示すようにビット B1 の正転サブフレームデータの画素 12A の SM121 への書き込みが順番に開始される。そして、画像表示部 11 の全画素 12A の SM121 にビット B1 の正転サブフレームデータが書き込まれ、その書き込み終了後の時刻 T3 で図 5 (B) に示すように “H” レベルの正転トリガパルスが画像表示部 11 を構成する全ての画素 12A に同時に供給される。

## 【0067】

40

これにより、全ての画素 12A のスイッチ SW12 がオンとされるため、SM121 に記憶されているビット B1 の正転サブフレームデータがスイッチ SW12 を通して DM122 を構成する容量 C1 に転送されて保持されると共に、反射電極 PE に印加される。この容量 C1 によるビット B1 の正転サブフレームデータの保持期間は、時刻 T3 から図 5 (B) に示すように次の “H” レベルの正転トリガパルスが入力される時刻 T4 までの 1 サブフレーム期間である。

## 【0068】

50

一方、共通電極電圧 Vcom は、正転サブフレームデータが反射電極 PE に印加されるサブフレーム期間は、図 5 (D) に示すように 0V よりも液晶の閾値電圧 Vtt だけ低い電圧に設定される。従って、ビット B1 の正転サブフレームデータが反射電極 PE に印加され

る時刻 T 3 ~ T 4 の 1 サブフレーム期間では、液晶 L C M の印加電圧は、図 5 ( E ) に示すように、サブフレームデータのビット値が「 1 」のときは  $3.3V + V_{tt}$  ( $= 3.3V - (-V_{tt})$ ) となり、サブフレームデータのビット値が「 0 」のときは  $+V_{tt}$  ( $= 0V - (-V_{tt})$ ) となる。

#### 【 0 0 6 9 】

続いて、上記のビット B 1 の正転サブフレームデータを表示しているサブフレーム期間内において、図 5 ( A ) に B 1 b で示すようにビット B 1 の反転サブフレームデータの画素 1 2 A の S M 1 2 1 への書き込みが順番に開始される。そして、画像表示部 1 1 の全画素 1 2 A の S M 1 2 1 にビット B 1 の反転サブフレームデータが書き込まれ、その書き込み終了後の時刻 T 4 で図 5 ( B ) に示すように“ H ” レベルの正転トリガパルスが画像表示部 1 1 を構成する全ての画素 1 2 A に同時に供給される。

10

#### 【 0 0 7 0 】

これにより、全ての画素 1 2 A のスイッチ S W 1 2 がオンとされるため、 S M 1 2 1 に記憶されているビット B 1 の反転サブフレームデータがスイッチ S W 1 2 を通して D M 1 2 2 を構成する容量 C 1 に転送されて保持されると共に、反射電極 P E に印加される。この容量 C 1 によるビット B 0 の反転サブフレームデータの保持期間は、時刻 T 4 から図 5 ( B ) に示すように次の“ H ” レベルの正転トリガパルスが入力される時刻 T 5 までの 1 サブフレーム期間である。ここで、ビット B 1 の反転サブフレームデータはビット B 1 の正転サブフレームデータと常に逆論理値の関係にある。

#### 【 0 0 7 1 】

一方、共通電極電圧 V com は、反転サブフレームデータが反射電極 P E に印加されるサブフレーム期間は、図 5 ( D ) に示すように  $3.3V$  よりも液晶の閾値電圧  $V_{tt}$  だけ高い電圧に設定される。従って、ビット B 1 の反転サブフレームデータが反射電極 P E に印加される時刻 T 4 ~ T 5 の 1 サブフレーム期間では、液晶 L C M の印加電圧は、サブフレームデータのビット値が「 1 」のときは  $-V_{tt}$  ( $= 3.3V - (3.3V + V_{tt})$ ) となり、サブフレームデータのビット値が「 0 」のときは  $-3.3V - V_{tt}$  ( $= 0V - (3.3V + V_{tt})$ ) となる。

20

#### 【 0 0 7 2 】

これにより、画素 1 2 A は図 5 ( E ) に示すように、時刻 T 3 ~ 時刻 T 5 までの 2 サブフレーム期間はビット B 1 とビット B 1 の相補ビット B 1 b とで同じ階調を表示すると共に、液晶 L C M の電位方向がサブフレーム毎に反転する交流駆動が行われるため、液晶 L C M の焼き付きを防止することができる。以下、上記と同様の動作が繰り返され、本実施の形態の画素 1 2 A を有する液晶表示装置によれば、複数のサブフレームの組み合わせによって階調表示を行うことができる。

30

#### 【 0 0 7 3 】

なお、ビット B 0 と相補ビット B 0 b の各表示期間は同じ第 1 のサブフレーム期間であり、また、ビット B 1 と相補ビット B 1 b の各表示期間も同じ第 2 のサブフレーム期間であるが、第 1 のサブフレーム期間と第 2 のサブフレーム期間とは同一であるとは限らない。ここでは、一例として第 2 のサブフレーム期間は第 1 のサブフレーム期間の 2 倍に設定されている。また、図 5 ( E ) に示すように、ビット B 2 と相補ビット B 2 b の各表示期間である第 3 のサブフレーム期間は、第 2 のサブフレーム期間の 2 倍に設定されている。他のサブフレーム期間についても同様であり、システムに従って各サブフレーム期間の長さが所定の長さに決められ、またサブフレーム数も任意の数に決定される。

40

#### 【 0 0 7 4 】

次に、本発明の要部の画素の他の実施の形態について説明する。

#### 【 0 0 7 5 】

第 1 の実施の形態の画素 1 2 A は、列データ線 d を介して供給されるサブフレームデータをサンプリングして記憶する第 1 の信号保持手段を S R A M 2 0 1 で構成する S M 1 2 1 とし、第 1 の信号保持手段から供給されるサブフレームデータを所定期間保持して反射電極に印加する第 2 の信号保持手段を D R A M 2 0 2 で構成する D M 1 2 2 とすることで

50

、画素の小型化等を実現した。これに対し、以下説明する画素の第2及び第3の実施の形態は、第1及び第2の信号保持手段を前記特許文献1に記載の画素と同様に、いずれもS R A Mとしたものである。ただし、本発明の要部の画素の第2及び第3の実施の形態では、S R A Mを所定の構成とすることで特許文献1記載の画素に比べて動作の安定化を実現している。

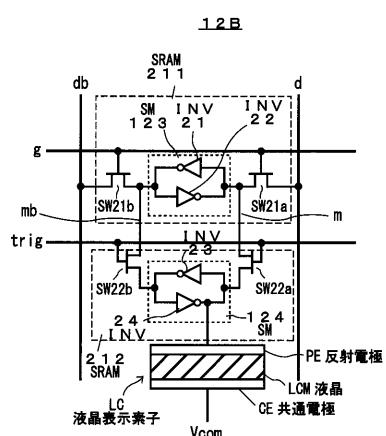

#### 【0076】

図7は、本発明になる液晶表示装置の要部である画素の第2の実施の形態の回路図を示す。同図中、図2と同一構成部分には同一符号を付し、その説明を省略する。図7において、第2の実施の形態の画素12Bは、図1中のレベルシフタ／画素ドライバ163に一端が接続されて列方向(Y方向)に延在する正転データ用列データ線d<sub>j</sub>と反転データ用列データ線d<sub>bj</sub>とを一組とする、全部でn組の列データ線のうちの、任意の一組の正転データ用列データ線d及び反転データ用列データ線d<sub>b</sub>と、垂直シフトレジスタ14に一端が接続されて行方向(X方向)に延在する任意の1本の行走査線gとの交差部に設けられた画素で、第1のスタティック・ランダム・アクセス・メモリ(S R A M)211と、第2のスタティック・ランダム・アクセス・メモリ(S R A M)212と、液晶表示素子L Cとより構成されている。第1のS R A M211は、第1及び第2のスイッチング手段を構成するスイッチSW21a及びSW21bと、第1の信号保持手段(S M)123により構成される。また、第2のS R A M212は、第3及び第4のスイッチング手段を構成するスイッチSW22a及びSW22bと、第2の信号保持手段(S M)124により構成される。

10

20

#### 【0077】

スイッチSW21aは、ゲートが行走査線gに接続され、ドレインが列データ線dに接続され、ソースがS M123の一方の入力端子に接続されているN M O Sトランジスタにより構成されている。スイッチSW21bは、ゲートが行走査線gに接続され、ドレインが列データ線d<sub>b</sub>に接続され、ソースがS M123の他方の入力端子に接続されているN M O Sトランジスタにより構成されている。

#### 【0078】

S M123は、一方の出力端子が他方の入力端子に接続された2つのインバータI N V 21及びI N V 22からなる自己保持型メモリである。インバータI N V 21は、その入力端子がインバータI N V 22の出力端子とSW21aを構成するN M O SトランジスタのソースヒスイッチSW22aとに接続されている。インバータI N V 22は、その入力端子がインバータI N V 21の出力端子とSW21bを構成するN M O SトランジスタのソースヒスイッチSW22bとに接続されている。インバータI N V 21及びI N V 22は、いずれも図3に示すような公知のC M O Sインバータの構成である。

30

#### 【0079】

また、スイッチSW22aは、ゲートがトリガ線trigに接続され、ドレインがS M123とスイッチSW21aとの接続点に接続され、ソースがS M124の一方の入力端子に接続されているN M O Sトランジスタにより構成されている。スイッチSW22bは、ゲートがトリガ線trigに接続され、ドレインがS M123とスイッチSW21bとの接続点に接続され、ソースがS M124の他方の入力端子に接続されているN M O Sトランジスタにより構成されている。

40

#### 【0080】

また、S M124は、一方の出力端子が他方の入力端子に接続された2つのインバータI N V 23及びI N V 24からなる自己保持型メモリである。インバータI N V 23は、その入力端子がインバータI N V 24の出力端子とSW22aを構成するN M O SトランジスタのソースヒスイッチSW22bとに接続されている。インバータI N V 24は、その入力端子がインバータI N V 23の出力端子とSW22bを構成するN M O SトランジスタのソースヒスイッチSW22aとに接続されている。インバータI N V 23及びI N V 24は、インバータI N V 21及びI N V 22と同様にいずれも図3に示すような公知のC M O Sインバータの構成である。

50

## 【0081】

本実施の形態の画素12Bは、図5のタイミングチャートと共に説明した動作と同様の動作を行う。画素12Bは行走検信号により選択されると、スイッチSW21a及びSW21bがオンとされる。スイッチSW21a及びSW21bには列データ線dと列データ線dbを介して互いに逆論理値の1ビットの正転サブフレームデータと1ビットの反転サブフレームデータとが供給されている。ここで、スイッチSW21a及びSW21bはNMOSトランジスタで構成されており、正転サブフレームデータ及び反転サブフレームデータがVDD側の電圧（“H”）のときには、NMOSトランジスタの閾値電圧Vthにより入力されず、VDDからVth分低い電圧しか入力されない。しかも、この電圧では電流が殆ど流れなくなる。このため、スイッチSW21a又はSW21bによりサンプリングされたGND電位（“L”）になる正転サブフレームデータ又は反転サブフレームデータが、SM123に書き込まれる。

10

## 【0082】

SM124へのデータ書き込みは、トリガ線trigを介して供給されるトリガパルスにより制御されるスイッチSW22a及びSW22bにより行われる。SM123とスイッチSW21aとの接続点から配線mを介してスイッチSW22aに供給されるデータと、SM123とスイッチSW21bとの接続点から配線mbを介してスイッチSW22bに供給されるデータとは、互いに逆論理値の関係にある。スイッチSW22a及びSW22bは、NMOSトランジスタで構成されており、VDD側の電圧（“H”レベル）はNMOSトランジスタのVthにより入力されず、VDDからVth分低い電圧しか入力さない。しかもこの電圧ではNMOSトランジスタのVth近辺で駆動することになるため、電流が殆ど流れなくなる。このため、GND電位（“L”レベル）になる配線m又は配線mbのデータがSM124に書き込まれる。

20

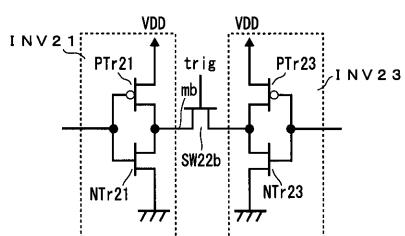

## 【0083】

ここで、画像表示部11を構成する全ての画素12BのSM123にサブフレームデータが書き込まれた直後に、トリガ線trigを介して“H”レベルのトリガパルスが入力されたとき、SM124のデータをSM123の記憶データに書き換える必要がある。つまり、SM124に記憶されているデータでSM123のデータが書き換わってはならない。このため、SM124を構成するインバータの駆動力は、SM123を構成するインバータの駆動力よりも小さくする必要がある。つまり、SM123とSM124の記憶データが異なっていた場合、“H”レベルのトリガパルスが入力された時にインバータINV21の出力データとインバータINV23の出力データとが衝突することになり、インバータINV21の出力データがインバータINV24のデータを確実に書き換えるように、インバータINV21の駆動力はインバータINV23の駆動力よりも大きくする必要がある。また、インバータINV22とインバータINV24との関係では、インバータINV22の出力データがインバータINV23のデータを確実に書き換えるように、インバータINV22の駆動力はインバータINV24の駆動力よりも大きくする必要がある。

30

## 【0084】

このことについて図8を用いて更に説明する。インバータINV21とインバータINV23の関係を簡単に説明すると、配線mbにおけるSM123の出力データが“H”レベルの場合、インバータINV21を構成するPMOSトランジスタPTr21がオンしている状態である。それに対し、SM124の配線mb側の出力データが既に“L”レベルであった場合、インバータINV23を構成するNMOSトランジスタNTr23がオンしている状態である。

40

## 【0085】

このときトリガパルス線trigの“H”レベルのトリガパルスによりスイッチSW22bを構成するNMOSトランジスタがオンし、インバータINV21とインバータINV23の出力同士が導通した場合、電流はインバータINV21のPMOSトランジスタPTr21とインバータINV23のNMOSトランジスタNTr23を通してVDDからGN

50

Dで流れる。このとき配線m bの電圧はPMOSトランジスタP Tr21とNMOSトランジスタN Tr23のオン抵抗の比によって決まる。

#### 【0086】

逆に、配線m bにおけるSM123の出力データが“L”レベルで、SM124の配線m b側の出力データが既に“H”レベルであった場合、スイッチSW22bを構成するNMOSトランジスタがトリガパルス線trigの“H”レベルのトリガパルスによりオンし、インバータINV21とインバータINV23の出力同士が導通した場合、電流はインバータINV23のPMOSトランジスタP Tr23とインバータINV21のNMOSトランジスタN Tr21を通してVDDからGNDで流れる。このとき配線m bの電圧はPMOSトランジスタP Tr23とNMOSトランジスタN Tr21のオン抵抗の比によって決まる。10

#### 【0087】

また、配線m bには図示しないインバータINV24の入力ゲートが接続されており、インバータINV24は配線m bの電圧レベルの入力によって出力データが“L”レベルか“H”レベルに確定される。つまり、SM124の出力データは配線m bの電圧レベルによって決定されるため、SM123の出力データによってSM124のデータを書き換えるためには、インバータINV21、インバータINV22のトランジスタのオン抵抗がインバータINV23、インバータINV24のトランジスタのオン抵抗よりも低い必要がある。インバータINV21、インバータINV22のトランジスタのオン抵抗が低いことにより、SM123の出力データはSM124のデータレベルによらず、確実にSM124のデータを書き換えることができる。20

#### 【0088】

オン抵抗が低いトランジスタを使用するということは、駆動力が高いトランジスタを使用するということで実現でき、ゲート長を小さくしたり、ゲート幅を大きくしたりすることで実現できる。

#### 【0089】

全画素12BのSM124にSM123に記憶されていた1ビットのデータが一斉に書き込まれると、トリガパルス線trigのトリガパルスが“L”レベルとなり、スイッチSW22a及びSW22bがそれぞれオフとなる。このため、SM124は書き込んだ1ビットのデータを保持し、任意の時間（ここでは、1サブフレーム期間）、反射電極PEの電位を上記保持データに応じた電位に固定することができる。30

#### 【0090】

SM124に書き込まれるデータは、図5(C)に示した1サブフレーム毎に切り替わる正転データと反転データであり、一方、共通電極電位Vcomも図5(D)に示したように、上記の書き込みと同期して1サブフレーム毎に所定電位に交互に切り替わるため、本実施の形態の画素12Bを用いた液晶表示装置によれば、第1の実施の形態の画素12Aを用いた液晶表示装置と同様に、サブフレーム毎に反転する交流駆動が行われるため、液晶LCMの焼き付きを防止した表示を行うことができる。更に、本実施の形態の画素12Bを用いた液晶表示装置によれば、SM123を構成するインバータINV21及びINV22と、SM124を構成するインバータINV23及びINV24の各駆動力と、スイッチSW21a、SW21b、SW22a及びSW22bを構成する各トランジスタの駆動力をそれぞれ所定の関係に設定したため、安定かつ正確な階調表示ができる。40

#### 【0091】

なお、スイッチSW21a、21b、22a及び22bはPMOSトランジスタにより構成してもよく、その場合は上記の説明とは逆極性として考えればよいため、詳細は割愛する。

#### 【0092】

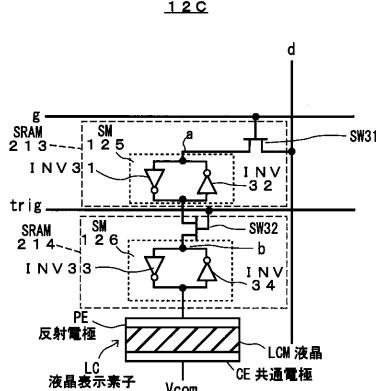

次に、本発明になる液晶表示装置の要部の画素の第3の実施の形態について説明する。図9は、本発明になる液晶表示装置の要部である画素の第3の実施の形態の回路図を示す。同図中、図7と同一構成部分には同一符号を付し、その説明を省略する。50

## 【0093】

図9において、第3の実施の形態の画素12Cは、図1中のレベルシフタ／画素ドライバ163に一端が接続されて列方向(Y方向)に延在する列データ線d1～dnのうちの、任意の1本の列データ線dと、垂直シフトレジスタ14に一端が接続されて行方向(X方向)に延在する任意の1本の行走査線gとの交差部に設けられた画素で、第1のスタティック・ランダム・アクセス・メモリ(SRAM)213と、第2のスタティック・ランダム・アクセス・メモリ(SRAM)214と、液晶表示素子LCとより構成されている。第1のSRAM213は、第1のスイッチング手段を構成するスイッチSW31と、第1の信号保持手段(SM)125により構成される。また、第2のSRAM214は、第2のスイッチング手段を構成するスイッチSW32と、第2の信号保持手段(SM)126により構成される。本実施の形態の画素12Cは、前記画素12Bと同様にSRAM2段で構成しているが、SRAM213内のSM125、SRAM214内のSM126への書き込みはそれぞれ1スイッチSW31、SW32で行う点に特徴がある。10

## 【0094】

スイッチSW31は、ゲートが行走査線gに接続され、ドレインが列データ線dに接続され、ソースがSM125の一方の入力端子に接続されているN MOSトランジスタにより構成されている。SM125は、一方の出力端子が他方の入力端子に接続された2つのインバータINV31及びINV32からなる自己保持型メモリである。インバータINV31は、その入力端子がインバータINV32の出力端子とSW31を構成するN MOSトランジスタのソースに接続されている。インバータINV32は、その入力端子がインバータINV31の出力端子とSW32を構成するN MOSトランジスタのドレインとに接続されている。インバータINV31及びINV32は、いずれも図3に示すような公知のCMOSインバータの構成である。20

## 【0095】

また、スイッチSW32は、ゲートがトリガ線trigに接続され、ドレインがSM125の出力端子に接続され、ソースがSM126の入力端子に接続されているN MOSトランジスタにより構成されている。また、SM126は、一方の出力端子が他方の入力端子に接続された2つのインバータINV33及びINV34からなる自己保持型メモリである。インバータINV33は、その入力端子がインバータINV34の出力端子と反射電極PEとに接続されている。インバータINV34は、その入力端子がインバータINV33の出力端子とSW32を構成するN MOSトランジスタのソースとに接続されている。インバータINV33及びINV34は、インバータINV31及びINV32と同様にいずれも図3に示すような公知のCMOSインバータの構成である。30

## 【0096】

本実施の形態の画素12Cは、図5のタイミングチャートと共に説明した動作と同様の動作を行う。画素12Cは行走査信号により選択されると、スイッチSW31がオンとされ、その時列データ線dに出力される正転サブフレームデータが、スイッチSW31によりサンプリングされて画素12CのSM125に書き込まれる。以下、同様にして、画像表示部11を構成する全ての画素12CのSM125に正転サブフレームデータの書き込みが行われ、その書き込み動作が終了した後に“H”レベルのトリガパルスが画像表示部11を構成する全ての画素12Cに同時に供給される。これにより、全ての画素12CのスイッチSW32がオンとされるため、SM125に記憶されている正転サブフレームデータがスイッチSW32を通してDRAM126に一斉に転送されて保持されると共に、反射電極PEに印加される。SM126の正転サブフレームデータの保持期間は、次の“H”的トリガパルスがトリガ線trigに入力されるまでの1サブフレーム期間である。40

## 【0097】

続いて、画像表示部11内の各画素12Cは上記と同様にして行走査信号により行単位で選択されて、各画素毎に直前の正転サブフレームデータと逆論理値の反転サブフレームデータがSM125に書き込まれる。画像表示部11を構成する全ての画素12CのSM125への反転サブフレームデータの書き込みが終了すると、“H”レベルのトリガパル50

スが画像表示部 11 を構成する全ての画素 12C に同時に供給される。これにより、全ての画素 12C のスイッチ SW32 がオンとされるため、SM125 に記憶されている反転サブフレームデータがスイッチ SW32 を通してDRAM126 に一斉に転送されて保持されると共に、反射電極 PE に印加される。SM126 の反転サブフレームデータの保持期間は、次の“H”のトリガパルスがトリガ線 trig に入力されるまでの 1 サブフレーム期間である。

#### 【0098】

SM125 へのデータ書き込みは、上記のように 1 個のスイッチ SW31 からの入力で行われる。この場合、スイッチ SW31 から見て SM125 を構成している入力側のインバータ INV31 内のトランジスタは、スイッチ SW31 から見て SM125 を構成している出力側のインバータ INV32 内のトランジスタに比較して、駆動力の大きいトランジスタを用いている。さらにスイッチ SW31 を構成している NMOS トランジスタの駆動力は、インバータ INV32 を構成している NMOS トランジスタの駆動力よりも大きいトランジスタで構成されている。これは、前述した画素 12A のインバータ INV121 及び INV122 とスイッチ SW11 との駆動力の関係と同様の理由によるので、その説明は省略する。

#### 【0099】

また、SM126 へのデータ書き込みは 1 個のスイッチ SW32 を通して行われる。この場合、スイッチ SW32 から見て SM126 を構成している入力側のインバータ INV33 内のトランジスタは、駆動力が大きいトランジスタを用い、スイッチ SW32 から見て SM126 を構成している出力側のインバータ INV34 内のトランジスタは、駆動力の小さいトランジスタを用いている。

#### 【0100】

こうすることによって、トリガパルスが“H”レベルとなってスイッチ SW32 がオンした場合において、SM125 と SM126 の記憶データが異なる場合、インバータ INV31 の出力データとインバータ INV34 の出力データとが衝突することになるが、インバータ INV31 の駆動力はインバータ INV34 の駆動力よりも大きいため、SM125 のデータが SM126 のデータに書き換わることなく、SM126 のデータが SM125 のデータに書き換えることができる。

#### 【0101】

更に、スイッチ SW32 を構成している NMOS トランジスタの駆動力は、インバータ INV34 を構成している NMOS トランジスタの駆動力よりも大きいトランジスタで構成されている。これは、SM126 のデータを書き換える場合、特に SM126 のスイッチ SW32 側の入力側電圧 b が“L”レベルで、SM125 のデータが“H”レベルの場合、インバータ INV33 が反転する閾値電圧よりも電圧 b を高くする必要があるからである。

#### 【0102】

すなわち、電圧 b はインバータ INV34 を構成する NMOS トランジスタの電流とスイッチ SW32 の電流との比によって決まる。このとき、スイッチ SW32 は NMOS トランジスタであるため、VDD 側の電圧は NMOS トランジスタの閾値 Vth により入力されず、“H”レベルの電圧は VDD から Vth 分低い電圧になる。しかも、この電圧では NMOS トランジスタの Vth 近辺で駆動することになるため、電流が殆ど流れなくなる。つまり、入力スイッチ SW32 を導通する電圧 b が高くなるほど、スイッチ SW32 で流す電流は少なくなる。つまり、電圧 b が SM126 の入力側インバータ INV33 が“H”レベルに反転する閾値電圧以上に達するためには、スイッチ SW32 に流れる電流が、インバータ INV34 を構成する NMOS トランジスタを流れる電流より大きい必要がある。この駆動力の比を考慮して、スイッチ SW32 のトランジスタサイズと、インバータ INV34 を構成する NMOS トランジスタのトランジスタサイズを決める必要がある。

#### 【0103】

全画素 12C の SM126 に SM125 に記憶されていた 1 ビットのデータが一斉に書

10

20

30

40

50

き込まれると、トリガパルス線trigのトリガパルスが“L”レベルとなり、スイッチSW23がオフとなる。このため、SM126は書き込んだ1ビットのデータを保持し、任意の時間（ここでは、1サブフレーム期間）、反射電極PEの電位を上記保持データに応じた電位に固定することができる。

#### 【0104】

SM126に書き込まれるデータは、図5(C)に示した1サブフレーム毎に切り替わる正転データと反転データであり、一方、共通電極電位Vcomも図5(D)に示したように、上記の書き込みと同期して1サブフレーム毎に所定電位に交互に切り替わるため、本実施の形態の画素12Cを用いた液晶表示装置によれば、上記の各実施の形態の画素12A又は12Bを用いた液晶表示装置と同様に、サブフレーム毎に反転する交流駆動が行われるため、液晶LCMの焼き付きを防止した表示を行うことができる。更に、本実施の形態の画素12Cを用いた液晶表示装置によれば、SM125を構成するインバータINV31及びINV32と、SM126を構成するインバータINV33及びINV34の各駆動力と、スイッチSW31及びSW32を構成する各トランジスタの駆動力をそれぞれ所定の関係に設定したため、安定かつ正確な階調表示ができる。

10

#### 【0105】

なお、スイッチSW31及び32はPMOSトランジスタにより構成してもよく、その場合は上記の説明とは逆極性として考えればよいため、詳細は割愛する。

#### 【0106】

なお、本発明は以上の実施の形態に限定されるものではなく、例えば画素電極は反射電極PEとして説明したが、透過電極であってもよい。

20

#### 【符号の説明】

#### 【0107】

10 液晶表示装置

11 画像表示部

12、12A、12B、12C 画素

13 タイミングジェネレータ

14 垂直シフトレジスタ

15 データラッチ回路

16 水平ドライバ

30

112 容量C1用電極

121、123、125 第1の信号保持手段(SM)

122 第2の信号保持手段(DM)

124、126 第2の信号保持手段(SM)

201、211～214 スタティック・ランダム・アクセス・メモリ(SRAM)

202 ダイナミック・ランダム・アクセス・メモリ(DRAM)

161 水平シフトレジスタ

162 ラッチ回路

163 レベルシフタ／画素ドライバ

40

d1～dn 列データ線

g1～gm 行走査線

trig トリガ線

trigb 反転トリガパルス用トリガ線

LC 液晶表示素子

LCM 液晶

PE 反射電極

CE 共通電極

C1 容量

INV11、INV12、INV21、INV22、INV31、INV32 インバータ

50

Tr1、NTr、NTr12、NTr21、NTr23 NチャネルMOS型トランジスタ (N MOSトランジスタ)

Tr2、PTr、PTr11、PTr21、PTr23 PチャネルMOS型トランジスタ (PMOSトランジスタ)

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

|                |                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2014132355A</a>                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2014-07-17 |

| 申请号            | JP2014033830                                                                                                                                                                                                                                                                                               | 申请日     | 2014-02-25 |

| [标]申请(专利权)人(译) | JVC 建伍株式会社                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | JVC建伍公司                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 岩佐 隆行                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 岩佐 隆行                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/36 G09G3/20                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/36 G09G3/20.624.B G09G3/20.621.B G09G3/20.641.E                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 5C006/AA14 5C006/AC25 5C006/AC26 5C006/AC28 5C006/BB16 5C006/BB28 5C006/BC06 5C006 /BC12 5C006/BC20 5C006/BF03 5C006/BF04 5C006/BF09 5C006/BF27 5C006/BF33 5C006/FA41 5C080/AA10 5C080/BB05 5C080/DD22 5C080/EE29 5C080/FF11 5C080/FF12 5C080/GG12 5C080 /JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

解决的问题：与在每个像素中使用两个SRAM的像素相比，减小像素的尺寸，并且即使在每个像素中准备两个SRAM的情况下，也要执行稳定的操作。在像素12A中，通过开关SW11对输出到列数据线d的数据进行采样，并将其写入SRAM 121中。数据被写入形成图像显示单元的所有像素12A的SRAM 121中。之后，所有像素12A的开关SW12通过触发脉冲而导通，并且SRAM 121的数据同时被传送并保持在形成DRAM 202的电容器C1中，并且被施加到反射电极PE。由于像素12A包括七个晶体管和一个电容器C1，因此像素可以由少量构成元件构成，并且在元件的高度方向上有效地设置了SRAM 121，DRAM 202和反射电极PE。通过布置它们，可以实现像素的尺寸减小。[选择图]图2