(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-197147

(P2016-197147A)

(43) 公開日 平成28年11月24日(2016.11.24)

|                               |                            |                                                                                                                                                                                                        |

|-------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (51) Int.Cl.                  | F 1                        | テーマコード (参考)                                                                                                                                                                                            |

| <b>G09G 3/36 (2006.01)</b>    | G09G 3/36                  | 2 H 092                                                                                                                                                                                                |

| <b>G09G 3/20 (2006.01)</b>    | G09G 3/20                  | 2 H 192                                                                                                                                                                                                |

| <b>G02F 1/133 (2006.01)</b>   | G09G 3/20                  | 2 H 193                                                                                                                                                                                                |

| <b>G02F 1/1343 (2006.01)</b>  | G09G 3/20                  | 5 C 006                                                                                                                                                                                                |

| <b>G02F 1/1368 (2006.01)</b>  | G09G 3/20                  | 5 C 080                                                                                                                                                                                                |

| 審査請求 未請求 請求項の数 9 O L (全 13 頁) |                            | 最終頁に続く                                                                                                                                                                                                 |

| (21) 出願番号                     | 特願2015-76249 (P2015-76249) | (71) 出願人 000005049<br>シャープ株式会社<br>大阪府堺市堺区匠町1番地                                                                                                                                                         |

| (22) 出願日                      | 平成27年4月2日 (2015.4.2)       | (74) 代理人 110000338<br>特許業務法人HARAKENZO WORKS PATENT & TRADEMA RK                                                                                                                                        |

|                               |                            | (72) 発明者 大橋 衛<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内<br>F ターム (参考) 2H092 GA13 GA20 JA24 JB02 JB69<br>NA01 PA06<br>2H192 AA24 BC24 DA12 GD61<br>2H193 ZA04 ZA07 ZB14 ZC04 ZC05<br>ZF11 ZP03 ZQ44<br>最終頁に続く |

(54) 【発明の名称】 液晶表示装置、液晶表示装置の駆動方法、テレビジョン受像機

## (57) 【要約】

【課題】 液晶表示装置の表示品位を高める。

【解決手段】 第1および第2画素電極を含む画素と、第1画素電極と容量を形成する第1容量配線と、第2画素電極と容量を形成する第2容量配線とを備え、第1容量配線に第1容量信号が供給されるとともに第2容量配線に第2容量信号が供給される液晶表示装置において、前記第1および第2容量信号それについて、第1電位と第1電位よりも高い第2電位とが交互に入れ替わるスイング期間と、このスイング期間に続き、第1電位および第2電位の中間となる第3電位に維持される非スイング期間とが1フレーム期間内に設けられている。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

第1および第2画素電極を含む画素と、第1画素電極と容量を形成する第1容量配線と、第2画素電極と容量を形成する第2容量配線とを備え、第1容量配線に第1容量信号が供給されるとともに第2容量配線に第2容量信号が供給される液晶表示装置であって、

前記第1および第2容量信号それぞれについて、第1電位と第1電位よりも高い第2電位とが交互に入れ替わるスイング期間と、このスイング期間に続き、第1電位および第2電位の中間となる第3電位に維持される非スイング期間とが1フレーム期間内に設けられていることを特徴とする液晶表示装置。

**【請求項 2】**

第1および第2容量信号それぞれについて、スイング期間に供給される電位の実効値が第3電位に等しいことを特徴とする請求項1記載の液晶表示装置。

**【請求項 3】**

前記第1および第2画素電極に対向する対向電極を備え、

前記第3電位は、前記対向電極に供給される電位に等しいことを特徴とする請求項1または2に記載の液晶表示装置。

**【請求項 4】**

前記非スイング期間は、垂直帰線期間と同じかそれよりも短いことを特徴とする1～3のいずれか1項に記載の請求項1記載の液晶表示装置。

**【請求項 5】**

前記スイング期間は垂直走査期間と同じかそれよりも長いことを特徴とする請求項1～4のいずれか1項に記載の液晶表示装置。

**【請求項 6】**

前記第1画素電極に接続する第1トランジスタと、第2画素電極に接続する第2トランジスタと、第1および第2トランジスタに接続する走査信号線と、第1および第2トランジスタに接続するデータ信号線とを備え、

第1垂直走査期間内の選択期間に、前記走査信号線が選択されてデータ信号線から第1および第2画素電極に第1極性の信号電位が書き込まれ、

第1垂直走査期間の選択期間終了時に1容量信号が第1電位であって、第2容量信号が第2電位であることを特徴とする請求項1～5のいずれか1項に記載の液晶表示装置。

**【請求項 7】**

第2垂直走査期間内の選択期間に、前記走査信号線が選択されてデータ信号線から第1および第2画素電極に第2極性の信号電位が書き込まれ、

第2垂直走査期間の選択期間終了時に、第1容量配線が第2電位であって、第2容量配線が第1電位であることを特徴とする請求項6記載の液晶表示装置。

**【請求項 8】**

第1および第2画素電極を含む画素と、第1画素電極と容量を形成する第1容量配線と、第2画素電極と容量を形成する第2容量配線とを備えた液晶表示装置の駆動方法であって、

第1容量配線に供給する第1容量信号および第2容量配線に供給する第2容量信号それについて、第1電位と第1電位よりも高い第2電位とが交互に入れ替わるスイング期間と、このスイング期間に続き、第1電位および第2電位の中間となる第3電位に維持される非スイング期間とを1フレーム期間内に設けることを特徴とする液晶表示装置の駆動方法。

**【請求項 9】**

請求項1～7のいずれか1項に記載の液晶表示装置と、チューナとを備えるテレビジョン受像機。

**【発明の詳細な説明】****【技術分野】****【0001】**

10

20

30

40

50

本発明は、液晶表示装置、液晶表示装置の駆動方法、テレビジョン受像機に関する。

【背景技術】

【0002】

特許文献1には、1画素に設けた第1画素電極および第2画素電極それぞれを、別々のトランジスタを介して同一データ信号線および同一走査信号線に接続とともに、第1画素電極と容量を形成する容量配線と、第2画素電極を容量を形成する容量配線とに容量信号を供給する駆動方法が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】日本国公開特許公報2004-62146(公開日:2004年2月26日)

10

【発明の概要】

【発明が解決しようとする課題】

【0004】

前記駆動方法においては、容量信号の実効値の調整等のために1フレーム期間の末尾で容量信号の周波数を上げると、帯状のスジムラが発現する現象が起りうることが見いだされた。本発明の目的の1つは、このような現象を抑えて表示品位を高めることにある。

【課題を解決するための手段】

【0005】

本液晶表示装置は、第1および第2画素電極を含む画素と、第1画素電極と容量を形成する第1容量配線と、第2画素電極と容量を形成する第2容量配線とを備え、第1容量配線に第1容量信号が供給されるとともに第2容量配線に第2容量信号が供給される液晶表示装置であって、前記第1および第2容量信号それについて、第1電位と第1電位よりも低い第2電位とが交互に入れ替わるスイング期間と、このスイング期間に続き、第1電位および第2電位の中間となる第3電位で維持される非スイング期間とが、1フレーム期間内に設けられていることを特徴とする。

20

【発明の効果】

【0006】

前記構成によれば、各容量配線の駆動負荷が軽減され、前記の現象を抑えて表示品位を高めることができる。

30

【図面の簡単な説明】

【0007】

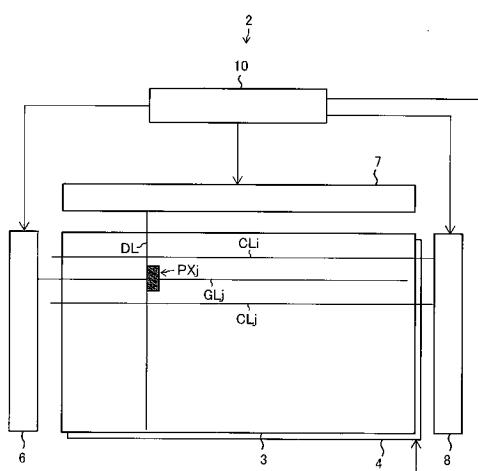

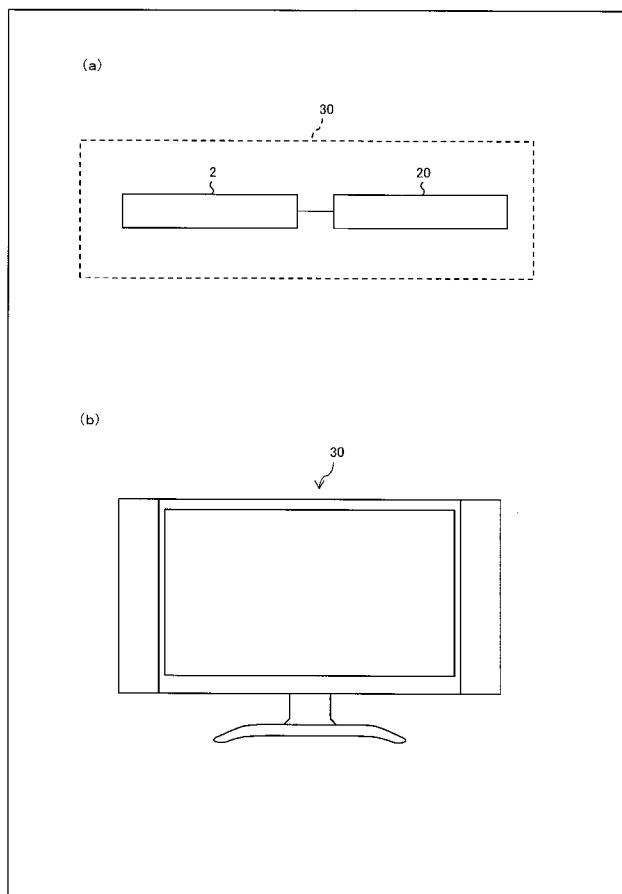

【図1】実施の形態1の液晶表示装置の構成を示す模式図である。

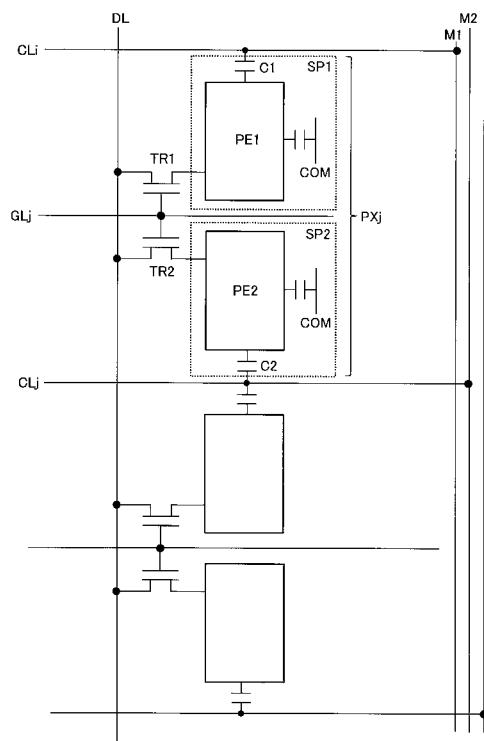

【図2】図1の液晶パネルの構成を示す回路図である。

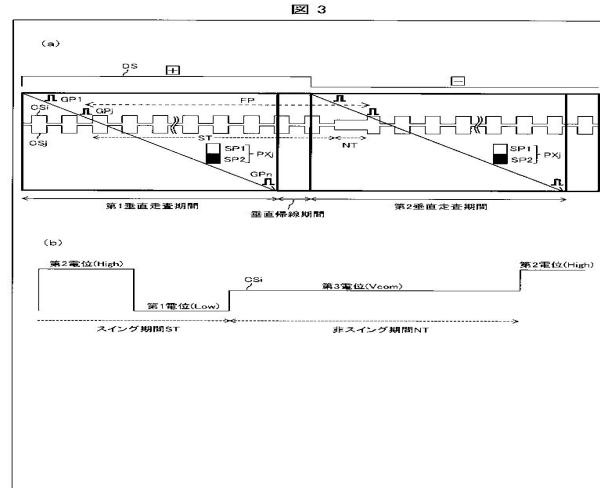

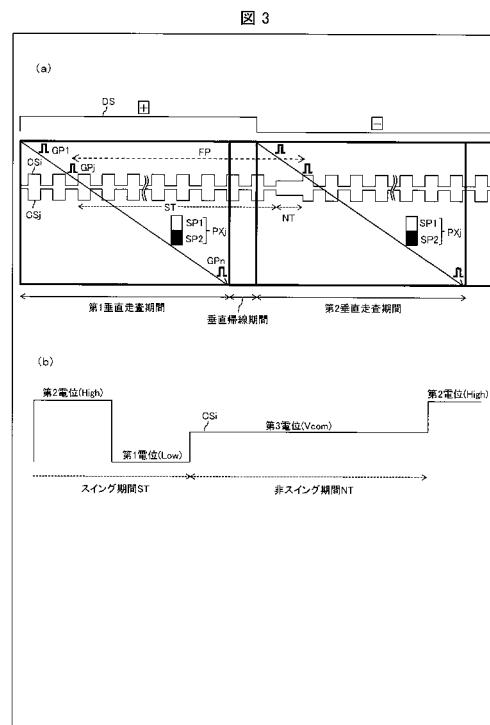

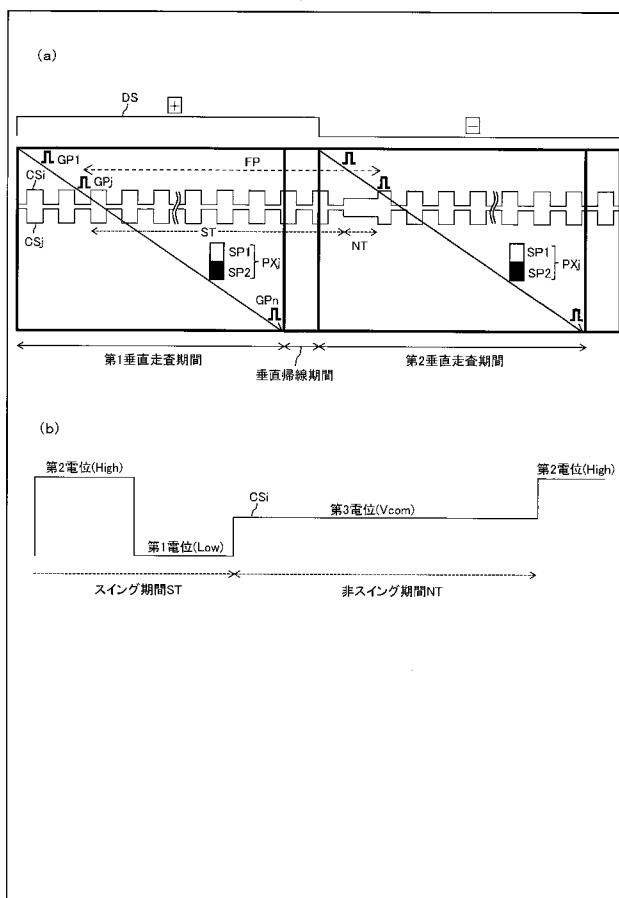

【図3】(a)・(b)は、本液晶表示装置の駆動方法を示すタイミングチャートである。

。

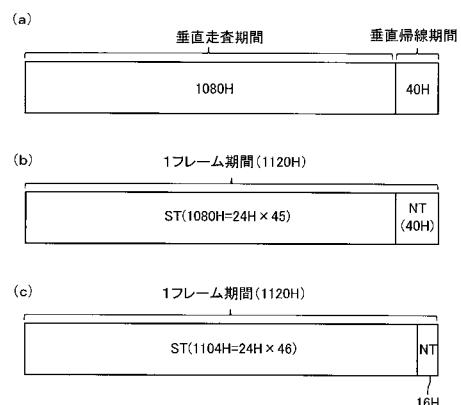

【図4】スイング期間および非スイング期間の設定方法を示す模式図である。

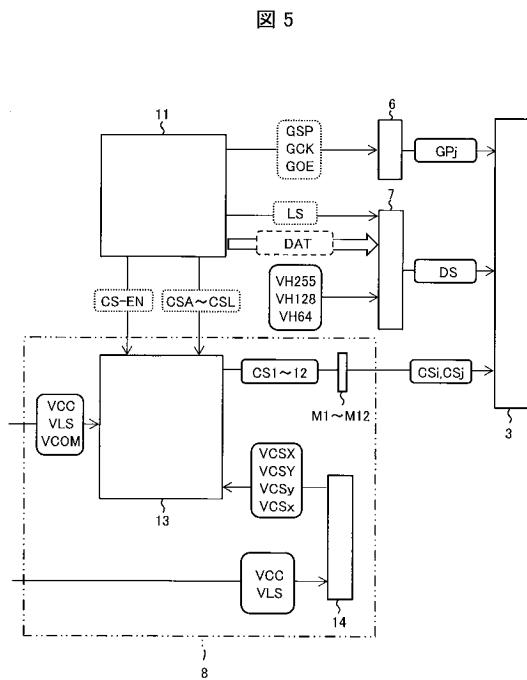

【図5】本液晶表示装置における各種信号および供給電位の流れを示すブロック図である。

40

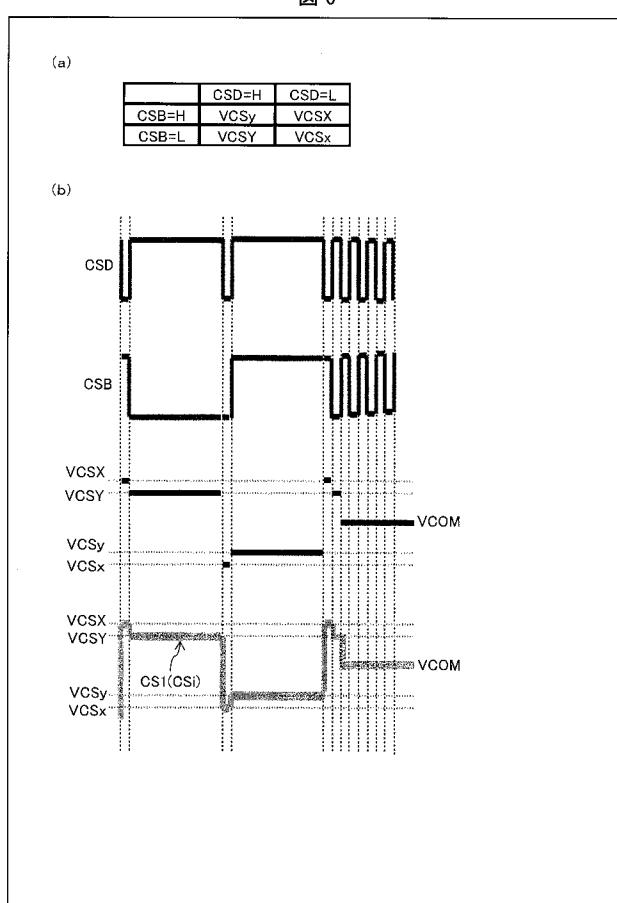

【図6】CSドライバでの容量信号の生成方法を示すタイミングチャートである。

【図7】(a)(b)は、実施の形態2の液晶TVの構成を示す模式図である。

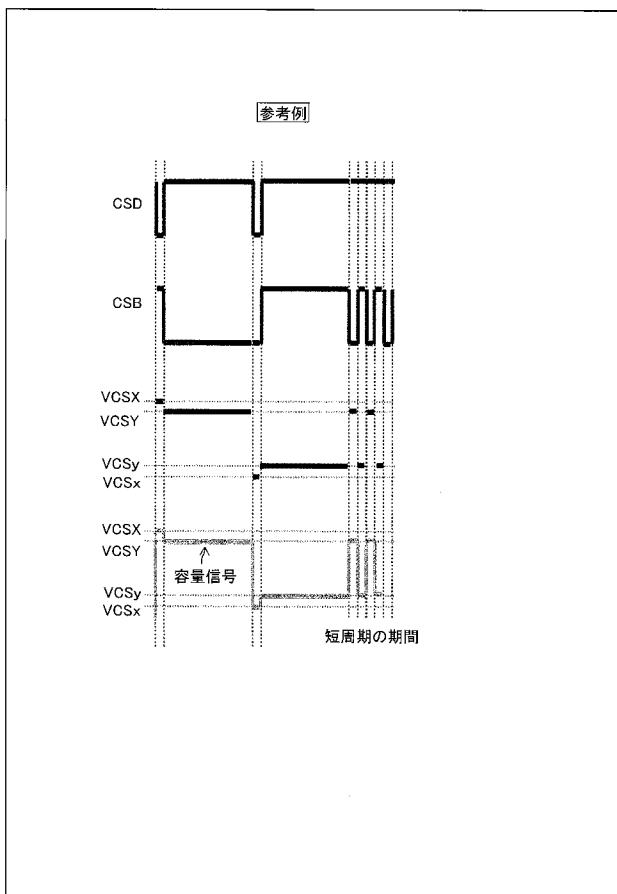

【図8】容量信号の生成方法を示す参考図である。

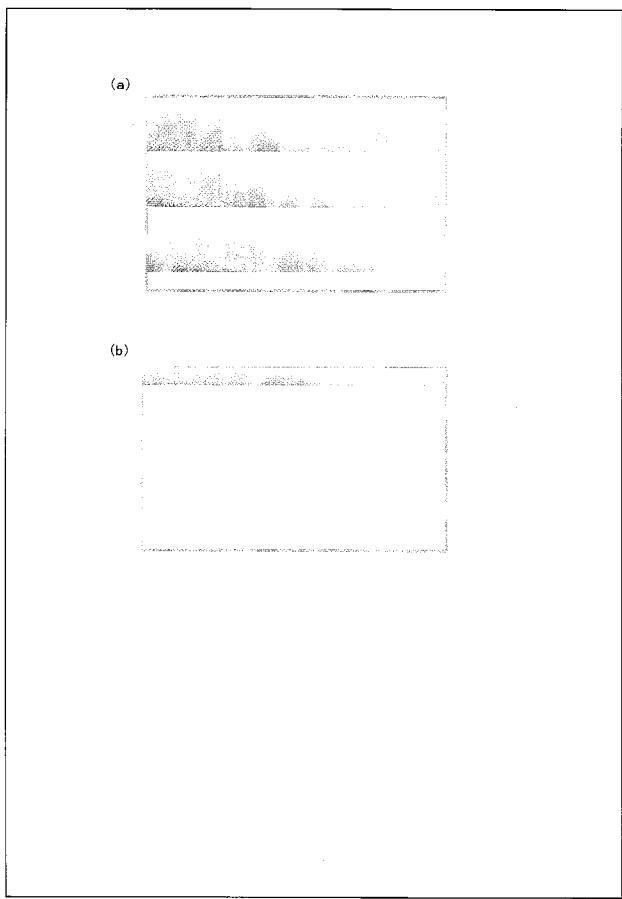

【図9】問題となる表示状態を示す模式図である。

【発明を実施するための形態】

【0008】

本発明の実施の形態を図1～図9に基づいて以下に説明する。

【0009】

〔実施の形態1〕

図1は、本液晶表示装置の構成を示す模式図である。図1に示すように、液晶表示装置

50

2は、液晶パネル3と、バックライト4と、液晶パネル3の複数の走査信号線（例えば、走査信号線G<sub>Lj</sub>）を駆動するゲートドライバ6と、液晶パネル3の複数のデータ信号線（例えば、データ信号線D<sub>L</sub>）を駆動するソースドライバ7と、液晶パネル3の複数の容量配線（例えば、容量配線C<sub>Li</sub>・C<sub>Lj</sub>）を駆動するCSドライバ8と、ゲートドライバ6およびソースドライバ7並びにCSドライバ8を制御する表示制御回路10とを備える。液晶パネル3はアクティブマトリクス基板と対向基板とこれらに挟まれた液晶層を含み、j番目の走査信号線G<sub>Lj</sub>およびデータ信号線D<sub>L</sub>の交差部分に画素P<sub>Xj</sub>が形成されている。

【0010】

図2は、図1の液晶パネル3の構成を示す回路図である。図2に示すように、画素P<sub>Xj</sub>は、第1画素電極P<sub>E1</sub>および第2画素電極P<sub>E2</sub>を含み、第1画素電極P<sub>E1</sub>および対向基板に形成された共通電極COM並びにこれらで挟まれた液晶層によってサブ画素S<sub>P1</sub>が形成され、第2画素電極P<sub>E2</sub>および対向基板に形成された共通電極COM並びにこれらで挟まれた液晶層によってサブ画素S<sub>P2</sub>が形成される。

10

【0011】

第1画素電極P<sub>E1</sub>は、トランジスタTR1を介してデータ信号線D<sub>L</sub>および走査信号線G<sub>Lj</sub>に接続され、第1画素電極P<sub>E1</sub>と容量配線C<sub>Li</sub>との間には補助容量C<sub>1</sub>が形成されている。同様に、第2画素電極P<sub>E2</sub>は、トランジスタTR2を介してデータ信号線D<sub>L</sub>および走査信号線G<sub>Lj</sub>に接続され、第2画素電極P<sub>E2</sub>と容量配線C<sub>Li</sub>との間には補助容量C<sub>2</sub>が形成されている。

20

【0012】

なお、CSドライバ8には12本の幹配線（幹配線M<sub>1</sub>・M<sub>2</sub>を含む）が設けられており、容量配線C<sub>Li</sub>はCS幹配線M<sub>1</sub>に接続され、容量配線C<sub>Lj</sub>はCS幹配線M<sub>2</sub>に接続されている。

【0013】

図3(a)は、本実施の形態の液晶表示装置の駆動方法を示すタイミングチャートである。複数の走査信号線を順次選択（走査）するゲートドライバ6は、走査信号線G<sub>Lj</sub>にゲートパルスG<sub>Pj</sub>を供給することでこれを選択する。ソースドライバ7は、データ信号線D<sub>L</sub>にデータ信号DSを供給する。CSドライバ8は、CS幹配線M<sub>1</sub>を介して容量配線C<sub>Li</sub>に第1容量信号CS<sub>i</sub>を供給するとともに、CS幹配線M<sub>2</sub>を介して容量配線C<sub>Lj</sub>に第2容量信号CS<sub>j</sub>を供給する。なお、図3(a)では垂直走査期間中はデータ信号DSの極性を同一としているが、1あるいは複数水平走査期間ごとにデータ信号DSの極性を反転させててもよい。

30

【0014】

図3(b)に示すように、パルス信号である第1容量信号CS<sub>i</sub>および第2容量信号CS<sub>j</sub>それぞれについては、第1電位（以下、適宜「Low」と記載）と第1電位よりも高い第2電位（以下、適宜「High」と記載）とが交互に入れ替わるスイング期間STと、スイング期間STに続き、第1および第2電位の中間値である第3電位が維持される非スイング期間NTとが1フレーム期間FP内に設けられている。スイング期間STの周期は、例えば24H(Highが12Hで、Lowが12H)である。なお、一水平走査期間分を1Hと記載している。スイング期間STの第1および第2容量信号CS<sub>i</sub>・CS<sub>j</sub>は、相互に位相が半周期分ずれており、両者は反転関係にある。

40

【0015】

各垂直走査期間では、ゲートパルスG<sub>Pj</sub>の供給によって走査信号線G<sub>Lj</sub>がアクティブとなり、アクティブ状態の期間（選択期間）に、データ信号線D<sub>L</sub>から第1および第2画素電極P<sub>E1</sub>・P<sub>E2</sub>にデータ信号が書き込まれる。

【0016】

図3(a)に示すように、第1垂直走査期間内の選択期間に第1容量信号CS<sub>i</sub>がLow、第2容量信号CS<sub>j</sub>がHighとなっており、この選択期間で第1および第2画素電極P<sub>E1</sub>・P<sub>E2</sub>にプラス極性のデータ信号が書き込まれた後に、第1容量信号CS<sub>i</sub>が

50

H i g h に、第 2 容量信号 C S j が L o w に反転する。

【 0 0 1 7 】

第 1 および第 2 容量信号 C S i · C S j は、第 1 垂直走査期間内の選択期間から第 2 垂直走査期間内の選択期間までの 1 フレーム期間 F P の実効電位が、第 1 電位 ( L o w ) および第 2 電位 ( H i g h ) の中間値である第 3 電位 ( 例えば、共通電極 C O M の電位である共通電位 V c o m ) である。

【 0 0 1 8 】

10 このように、1 フレーム期間 F P の第 1 容量信号 C S i の実効値が第 3 電位であり、第 1 垂直走査期間の選択期間終了時 ( トランジスタ T R 1 の O F F 時 ) の第 1 容量信号 C S i が L o w ( 第 1 電位 ) であるため、第 1 画素電極 P E 1 ( 容量配線 C L 1 と容量 C 1 を形成 ) の実効値は、第 1 垂直走査期間の選択期間終了時に書き込まれたデータ信号の電位 ( プラス ) から引き上げられる。これにより、第 1 画素電極 P E 1 を含むサブ画素 S P 1 は、データ信号の想定よりも明るい明サブ画素となる。

【 0 0 1 9 】

また、1 フレーム期間 F P の第 1 容量信号 C S j の実効値が第 3 電位であり、第 1 垂直走査期間の選択期間終了時 ( トランジスタ T R 2 の O F F 時 ) の第 2 容量信号 C S j が H i g h ( 第 2 電位 ) であるため、第 2 画素電極 P E 2 ( 容量配線 C L 2 と容量 C 2 を形成 ) の 1 フレーム期間 F P の実効値は、第 1 垂直走査期間の選択期間終了時に書き込まれたデータ信号の電位 ( プラス ) から引き下げられる。これにより、第 2 画素電極 P E 2 を含むサブ画素 S P 2 は、データ信号の想定よりも暗い暗サブ画素となる。

【 0 0 2 0 】

20 図 3 ( a ) に示すように、第 2 垂直走査期間内の選択期間に第 1 容量信号 C S i が H i g h 、第 2 容量信号 C S j が L o w となっており、この選択期間で第 1 および第 2 画素電極 P E 1 · P E 2 にマイナス極性のデータ信号が書き込まれた後に、第 1 容量信号 C S i が L o w に、第 2 容量信号 C S j が H i g h に反転する。

【 0 0 2 1 】

第 1 および第 2 容量信号 C S i · C S j は、第 2 垂直走査期間内の選択期間から次の垂直走査期間内の選択期間までの 1 フレーム期間の実効電位が、第 1 電位 ( L o w ) および第 2 電位 ( H i g h ) の中間値である第 3 電位 ( 例えば、共通電位 V c o m ) である。

【 0 0 2 2 】

30 このように、1 フレーム期間の第 1 容量信号 C S i の実効値が第 3 電位であり、第 2 垂直走査期間の選択期間終了時 ( トランジスタ T R 1 の O F F 時 ) の第 1 容量信号 C S i が H i g h ( 第 2 電位 ) であるため、第 1 画素電極 P E 1 ( 容量配線 C L 1 と容量 C 1 を形成 ) の実効値は、第 2 垂直走査期間の選択期間終了時に書き込まれたデータ信号の電位 ( マイナス ) から引き下げられる。これにより、第 1 画素電極 P E 1 を含むサブ画素 S P 1 は、データ信号の想定よりも明るい明サブ画素となる。

【 0 0 2 3 】

また、1 フレーム期間の第 1 容量信号 C S j の実効値が第 3 電位であり、第 2 垂直走査期間の選択期間終了時 ( トランジスタ T R 2 の O F F 時 ) の第 2 容量信号 C S j が L o w ( 第 1 電位 ) であるため、第 2 画素電極 P E 2 ( 容量配線 C L 2 と容量 C 2 を形成 ) の 1 フレーム期間の実効値は、第 2 垂直走査期間の選択期間終了時に書き込まれたデータ信号の電位 ( マイナス ) から引き上げられる。これにより、第 2 画素電極 P E 2 を含むサブ画素 S P 2 は、データ信号の想定よりも暗い暗サブ画素となる。

【 0 0 2 4 】

40 このように、1 画素 ( P X j ) 内に、明サブ画素 ( S P 1 ) および暗サブ画素 ( S P 2 ) を形成することで、視野角特性を高めることができる。

【 0 0 2 5 】

この駆動方法では、各フレーム期間において第 1 および第 2 容量信号 C S i · C S j それぞれの実効値を第 3 電位 ( L o w および H i g h の中間値 ) とする必要がある。例えば、図 4 ( a ) に示すように、垂直走査期間が 1 0 8 0 H 、垂直帰線期間が 4 0 H の場合 (

1 フレーム期間は  $1080\text{H} + 40\text{H} = 1120\text{H}$  )、第1および第2容量信号 C S i・C S j それぞれの周期を  $24\text{H}$  ( $12\text{H}$ ごとに反転) とすると、垂直走査期間分 ( $1080\text{H}$ ) の実効値は第3電位となる ( $24\text{H} \times 45 = 1080$ )。よって、垂直帰線期間にあたる  $40\text{H}$  分を  $1\text{H}$  反転あるいは  $2\text{H}$  反転させる (例えば図8に示すように、垂直帰線期間に相当するフレーム期間末尾を短周期の期間とする) ことで、各容量信号の実効値を第3電位とすることができますが、C S ドライバの負荷が大きくなるため、容量配線の充電不足等に起因して帯状のスジムラが発現 (図9(a)・図9(b) 参照) することが見出されている。

#### 【0026】

液晶表示装置2では、図4(b)に示すように、第1および第2容量信号 C S i・C S j それについて、垂直走査期間に相当する  $1080\text{H}$  分をスイング期間 S T とし、垂直帰線期間に相当する、フレーム期間の末尾 (例えば  $40\text{H}$  分) を、第3電位 (V c o m) が維持される非スイング期間 N T としている。これにより、C S ドライバ8の駆動負荷が軽減され、容量配線の充電不足等に起因する帯状のスジムラの発現を抑制することができる。

#### 【0027】

なお、第1および第2容量信号 C S i・C S j それぞれの周期が  $24\text{H}$  で垂直帰線期間が  $40\text{H}$  の場合、図4(c)に示すように、 $40\text{H}$  の内の  $24\text{H}$  をスイング期間 S T に付け足し (S T =  $1104\text{H}$  とする)、余った  $16\text{H}$  を非スイング期間 N T とすることもできる。

#### 【0028】

液晶表示装置2では、スイング期間 S T が垂直走査期間と同じかそれよりも長く、非スイング期間 N T が垂直帰線期間と同じかそれよりも短いため、非スイング期間 N T が表示に与える影響は実質的がないといえる。

#### 【0029】

液晶表示装置2では、第3電位を共通電極の電位である V c o m に設定しているため、第1および第2電位の中間値である第3電位を別途作成する必要がなく、C S ドライバ8の構成を簡易にことができる。

#### 【0030】

また、図8のように短周期の期間を設定する手法では、液晶パネルごとに設定を調整する必要があるが、本液晶表示装置3の構成では、この期間に自動的に V c o m が outputされるため、そのような調整工程を省くことができる。

#### 【0031】

図5は本液晶表示装置2における各種信号および供給電位の流れを示すブロック図である。図5に示すように、図1の表示制御回路10に設けられるタイミングコントローラ11は、ゲートスタートパルス信号 (G S P)、ゲートクロック信号 (G C K)、ゲートオンイネイブル信号 (G O E) をゲートドライバ6に出力し、表示データ D A T (例えば L V D S 信号) およびラッチストローブ信号 L S をソースドライバ7に供給する。また、ソースドライバ7には、階調電位 (V H 2 5 5、V H 1 2 8、V H 6 4 等) が入力される。

#### 【0032】

C S ドライバ8には、C S レベルシフタ13、D A 変換回路14、およびC S 幹配線 M 1 ~ M 1 2 が含まれる。タイミングコントローラ11は、C S 駆動のON/OFFを制御するフラグ信号 (C S - E N) およびC S タイミング信号 (C S A ~ C S L) をC S レベルシフタ13に出力する。C S レベルシフタ13には、低電位側のV C C 電位 (例えば、3.3V) および高電位側のV L S 電位 (例えば、15.6V) 並びに共通電極電位 V c o m が供給され、D A 変換回路14には、低電位側のV C C 電位 (例えば、3.3V) および高電位側のV L S 電位 (例えば、15.6V) が供給される。

#### 【0033】

D A 変換回路14は、V C C 電位およびV L S 電位からV C S X 電位、V C S Y 電位、V C S y 電位、およびV C S x 電位を作成し、これらをC S レベルシフタ13に供給する

10

20

30

40

50

。

## 【0034】

CS レベルシフタ13は、CSタイミング信号(CSA～CSL)に従い、VCSX電位、VCSY電位、VCSy電位、およびVCSx電位から容量信号CS1～CS12を生成し、これらをCS幹配線M1～M12を介して各容量配線に出力する。

## 【0035】

具体的には、CS レベルシフタ13は、例えば図6(a)に示すように、CS D = H(High)かつCS B = Hの期間はVCSy電位を出力し、CS D = HかつCS B = L(Low)の期間はVCSY電位を出力し、CS D = LかつCS B = Hの期間はVCSX電位を出力し、CS D = LかつCS B = Lの期間はVCSx電位を出力し、さらに、CS D = HかつCS B = LあるいはCS D = LかつCS B = Hの状態が3H期間以上繰り返すと、Vcomを出力する。これにより、例えば図6(b)のようなCSタイミング信号CS D・CS Bに従って、同図に示すような容量信号CS1(第1容量信号CSI)を生成し、これをCS幹配線M1を介して容量配線(例えば、CS幹配線M1に接続する容量配線CLi)に出力することができる。

## 【0036】

なお、前述した短周期の期間を設定するタイプのタイミングコントローラでは、CS DおよびCS Bが、例えば図8のように設定されているため、フレーム期間の末尾(垂直帰線期間に相当)のCS Dを図6(b)のように1H反転に変更した上で、CS D = HかつCS B = LあるいはCS D = LかつCS B = Hの状態が3H期間以上繰り返されると、Vcomを出力するようにCS レベルシフタも変更する。

## 【0037】

## 〔実施の形態2〕

図7(a)に示すように、実施の形態1の液晶表示装置2を、テレビジョン放送のチューナ装置20と組み合わせることで、例えば、図7(b)に示すような液晶テレビ30を構成することが可能である。

## 【0038】

## 〔まとめ〕

本発明の第1態様にかかる液晶表示装置は、第1および第2画素電極を含む画素と、第1画素電極と容量を形成する第1容量配線と、第2画素電極と容量を形成する第2容量配線とを備え、第1容量配線に第1容量信号が供給されるとともに第2容量配線に第2容量信号が供給される液晶表示装置であって、前記第1および第2容量信号それぞれについて、第1電位と第1電位よりも高い第2電位とが交互に入れ替わるスイング期間と、このスイング期間に続き、第1電位および第2電位の中間となる第3電位に維持される非スイング期間とが1フレーム期間内に設けられていることを特徴とする。

## 【0039】

前記構成によれば、スイング期間に続く非スイング期間において第1および第2容量信号それぞれを第3電位(第1電位および第2電位の中間の電位)に維持することで、各容量信号の実効値の調整を可能としながら各容量配線の駆動負荷を軽減することができ、前記の現象を抑えることができる。

## 【0040】

本発明の第1態様にかかる液晶表示装置は、前記第1態様において、第1および第2容量信号それぞれについて、スイング期間に供給される電位の実効値が第3電位に等しいことを特徴とする。

## 【0041】

前記構成によれば、1フレーム期間の第1および第2容量信号それぞれの実効値を第3電位とすることができます。

## 【0042】

本発明の第3態様にかかる液晶表示装置は、前記第1または第2態様において、前記第1および第2画素電極に対向する対向電極を備え、前記第3電位は、前記対向電極に供給

10

20

30

40

50

される電位に等しいことを特徴とする。

【0043】

前記構成によれば、第3電位を別途作成する必要がなくなり、容量配線の駆動回路を簡易化することができる。

【0044】

本発明の第4態様にかかる液晶表示装置は、前記第1～3態様のいずれかにおいて、前記非スイング期間は、垂直帰線期間と同じかそれよりも短いことを特徴とする。

【0045】

このように前記非スイング期間を垂直帰線期間と同じかそれよりも短くすることで、表示に対する影響を実質的に排除することができる。

10

【0046】

本発明の第5態様にかかる液晶表示装置は、前記第1～4態様のいずれかにおいて、前記スイング期間は垂直走査期間と同じかそれよりも長いことを特徴とする。

【0047】

このように前記非スイング期間を垂直走査期間と同じかそれよりも長くすることで表示に対する影響を実質的に排除することができる。

【0048】

本発明の第6態様にかかる液晶表示装置は、前記第1～5態様のいずれかにおいて、前記第1画素電極に接続する第1トランジスタと、第2画素電極に接続する第2トランジスタと、第1および第2トランジスタに接続する走査信号線と、第1および第2トランジスタに接続するデータ信号線とを備え、第1垂直走査期間内の選択期間に、前記走査信号線が選択されてデータ信号線から第1および第2画素電極に第1極性の信号電位が書き込まれ、第1垂直走査期間の選択期間終了時に1容量信号が第1電位であって、第2容量信号が第2電位であることを特徴とする。

20

【0049】

前記構成によれば、第1垂直走査期間に対応するフレーム期間に、例えば、第1画素電極に対応するサブ画素を明サブ画素、第2画素電極に対応するサブ画素を暗サブ画素とすることができる。

【0050】

本発明の第7態様にかかる液晶表示装置は、前記第6態様において、第2垂直走査期間内の選択期間に、前記走査信号線が選択されてデータ信号線から第1および第2画素電極に第2極性の信号電位が書き込まれ、第2垂直走査期間の選択期間終了時に、第1容量配線が第2電位であって、第2容量配線が第1電位である。

30

【0051】

前記構成によれば、第2垂直走査期間に対応するフレーム期間に、例えば、第1画素電極に対応するサブ画素を明サブ画素、第2画素電極に対応するサブ画素を暗サブ画素とすることができる。

【0052】

本液晶表示装置の駆動方法は、第1および第2画素電極を含む画素と、第1画素電極と容量を形成する第1容量配線と、第2画素電極と容量を形成する第2容量配線とを備えた液晶表示装置の駆動方法であって、第1容量配線に供給する第1容量信号および第2容量配線に供給する第2容量信号それぞれについて、第1電位と第1電位よりも高い第2電位とが交互に入れ替わるスイング期間と、このスイング期間に続き、第1電位および第2電位の中間となる第3電位に維持される非スイング期間とを1フレーム期間内に設けることを特徴とする。

40

【0053】

前記方法によれば、スイング期間に続く非スイング期間において第1および第2容量信号それぞれを第3電位（第1電位および第2電位の中間の電位）に維持することで、各容量信号の実効値の調整を可能としながら各容量配線の駆動負荷を軽減することができ、前記の現象を抑えることができる。

50

## 【0054】

本テレビジョン受像機は、前記第1～7態様にかかるいずれかの液晶表示装置と、チューナとを備えることを特徴とする。

## 【0055】

本発明は前記の実施の形態に限定されるものではなく、前記実施の形態を技術常識に基づいて適宜変更したものやそれらを組み合わせて得られるものも本発明の実施の形態に含まれる。

## 【産業上の利用可能性】

## 【0056】

本液晶表示装置は、液晶テレビ、液晶モニタ、テレビモニタ等に好適である。

10

## 【符号の説明】

## 【0057】

2 液晶表示装置

3 液晶パネル

4 バックライト

6 ソースドライバ

7 ゲートドライバ

8 CSドライバ

10 表示制御回路

PXj 画素

GLj 走査信号線

DL データ信号線

CLi CLj 容量配線

PE1 第1画素電極

PE2 第2画素電極

CSI 第1容量信号

CSj 第2容量信号

GPj ゲートパルス

DS データ信号

ST スイング期間

NT 非スイング期間

FP 1フレーム期間

20

30

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

四 5

【 図 6 】

図 6

( 义 7 )

〔 図 8 〕

四 7

1000

図 8

【図9】

図9

## フロントページの続き

(51) Int.CI.

F I

テーマコード(参考)

G 0 2 F 1/133 5 5 0

G 0 2 F 1/133 5 0 5

G 0 2 F 1/1343

G 0 2 F 1/1368

F ターム(参考) 5C006 AC25 AF42 AF44 AF73 BB16 BC06 FA22 FA55

5C080 AA10 BB05 DD01 DD05 EE29 FF11 FF12 JJ02 JJ04 JJ06

KK43

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置，液晶显示装置的驱动方法，电视接收机                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2016197147A</a>                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2016-11-24 |

| 申请号            | JP2015076249                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2015-04-02 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 大橋衛                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | 大橋衛                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/36 G09G3/20.642.A G09G3/20.624.D G09G3/20.612.T G09G3/20.624.E G02F1/133.550 G02F1/133.505 G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H092/GA13 2H092/GA20 2H092/JA24 2H092/JB02 2H092/JB69 2H092/NA01 2H092/PA06 2H192/AA24 2H192/BC24 2H192/DA12 2H192/GD61 2H193/ZA04 2H193/ZA07 2H193/ZB14 2H193/ZC04 2H193/ZC05 2H193/ZF11 2H193/ZP03 2H193/ZQ44 5C006/AC25 5C006/AF42 5C006/AF44 5C006/AF73 5C006/BB16 5C006/BC06 5C006/FA22 5C006/FA55 5C080/AA10 5C080/BB05 5C080/DD01 5C080/DD05 5C080/EE29 5C080/FF11 5C080/FF12 5C080/JJ02 5C080/JJ04 5C080/JJ06 5C080/KK43 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

## 摘要(译)

解决方案：提供了一种液晶显示器，包括：像素，每个像素包括第一和第二像素电极；形成所述第一像素电极的第一电容配线和电容；和形成第二像素电极的第二电容配线和电容，其中第一电容信号被提供给第一电容配线，第二电容信号被提供给第二电容配线；对于所述第一电容信号和所述第二电容信号中的每一个，将第一电位和高于所述第一电位的第二电位交替切换的摆动时段，以及在所述摆动时段之后的非摆动时段，在所述非摆动时段期间，的第一电位和第二电位被保持在一个帧周期中。选择附图：图3