(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2020-73958

(P2020-73958A)

(43) 公開日 令和2年5月14日(2020.5.14)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09F 9/30</b> (2006.01)  | G09F 9/30 | 330 2H092   |

| <b>G09F 9/00</b> (2006.01)  | G09F 9/00 | 366A 2H189  |

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2H193       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 691D 5C006  |

| <b>G06F 3/041</b> (2006.01) | G09G 3/20 | 624C 5C080  |

審査請求 有 請求項の数 11 O L (全 19 頁) 最終頁に続く

|            |                              |          |                                           |

|------------|------------------------------|----------|-------------------------------------------|

| (21) 出願番号  | 特願2019-167601 (P2019-167601) | (71) 出願人 | 502356528                                 |

| (22) 出願日   | 令和1年9月13日 (2019.9.13)        |          | 株式会社ジャパンディスプレイ                            |

| (62) 分割の表示 | 特願2017-206464 (P2017-206464) |          | 東京都港区西新橋三丁目7番1号                           |

|            | の分割                          | (74) 代理人 | 110000154                                 |

| 原出願日       | 平成24年6月8日 (2012.6.8)         |          | 特許業務法人はるか国際特許事務所                          |

|            |                              | (72) 発明者 | 松元 秀一郎                                    |

|            |                              |          | 千葉県茂原市早野3300番地 株式会社                       |

|            |                              |          | ジャパンディスプレイイースト内                           |

|            |                              |          | F ターム (参考) 2H092 GA33 GA44 GA60 GA62 JA24 |

|            |                              |          | JB14 NA27                                 |

|            |                              |          | 2H189 AA14 HA12 LA04 LA10 LA28            |

|            |                              |          | LA31                                      |

|            |                              |          | 2H193 ZA04 ZA09 ZC25 ZE09 ZF43            |

|            |                              |          | ZF51 ZF52 ZJ02                            |

最終頁に続く

## (54) 【発明の名称】表示装置

## (57) 【要約】 (修正有)

【課題】タッチパネル機能を内蔵した液晶表示装置において、液晶ドライバICの開発コストを低減し、開発期間を短縮する装置を提供する。

【解決手段】表示装置は表示パネルに信号を供給する半導体チップを有する。表示パネルは、表示部に形成された複数の映像信号線DLと、複数のタッチパネル電極CTLとを有する。半導体チップDRVはその一対の長辺のうち表示部側の一方の長辺に第1端子群を有し、第1端子群は、タッチパネル電極に接続するタッチパネル端子群A1, A2と、映像信号線に接続する映像信号端子群TADとを含む。第1端子群の中で、半導体チップの表示部側の長辺の両端部に配置される複数の端子はタッチパネル端子群であり、映像信号端子群は当該両端部に配置される複数のタッチパネル端子群に挟まれて配置される。半導体チップの長辺方向及び短辺方向それぞれにて、映像信号端子群の幅はタッチパネル端子群の幅よりも広い。

【選択図】図7

**【特許請求の範囲】****【請求項 1】**

表示パネルを備え、前記表示パネルに配置された複数の画素と、前記複数の画素で構成される表示部と、前記表示パネルに信号を供給する半導体チップとを有する表示装置であつて、

前記表示パネルは、前記表示部に形成された複数の映像信号線と、複数のタッチパネル電極とを有し、

前記タッチパネル電極は、複数のブロックに分割されており、

前記分割された各ブロックのタッチパネル電極は、連続する複数の各画素に対して共通に設けられており、

前記半導体チップは、第1方向に伸びる一対の長辺と、前記第1方向と交差する第2方向に伸びる一対の短辺を有し、前記一対の長辺のうち前記表示部側の一方の長辺に、複数の端子からなる第1端子群を有し、

前記第1端子群は、前記分割された各ブロックのタッチパネル電極に接続するタッチパネル端子と、前記映像信号線に接続する映像信号端子とを含み、

前記第1端子群の中で、前記半導体チップの前記一方の長辺の両端部に配置される複数の端子からなる端子群は、前記タッチパネル端子からなる端子群であり、

前記第1端子群の中で、前記映像信号端子からなる端子群は、前記一方の長辺の両端部に配置される複数の前記タッチパネル端子からなる端子群に挟まれて配置され、

前記映像信号端子からなる端子群の前記第1方向の幅は、前記タッチパネル端子からなる端子群の前記第1方向の幅よりも広く、

前記映像信号端子からなる端子群の前記第2方向の幅は、前記タッチパネル端子からなる端子群の前記第2方向の幅よりも広いことを特徴とする表示装置。

**【請求項 2】**

前記表示部には、複数の画素毎に画素トランジスタと、前記画素トランジスタのゲート電極にゲート信号を供給する複数のゲート線と、前記複数のゲート線に前記ゲート信号を供給するゲート線駆動回路とを有し、

前記半導体チップは、前記一対の長辺のうち他方の長辺に、複数の端子からなる第2端子群を有し、

前記第2端子群の中で、前記半導体チップの前記他方の長辺の端部に配置される複数の端子は、前記ゲート線駆動回路に制御信号を供給する制御信号端子であることを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記第2端子群の中で、外部からの入力信号が入力される端子が、複数の前記制御信号端子に挟まれて配置されることを特徴とする請求項2に記載の表示装置。

**【請求項 4】**

前記半導体チップは前記表示パネルに搭載されることを特徴とする請求項1に記載の表示装置。

**【請求項 5】**

前記タッチパネル電極には、前記ゲート信号よりもハイ電圧である期間が短いパルス波形の信号が供給されることを特徴とする請求項2に記載の表示装置。

**【請求項 6】**

前記複数の画素には前記映像信号線により映像信号が供給され、

前記画素に前記映像信号が供給される画素書き込み期間に、前記タッチパネル電極には、前記パルス波形の信号とは異なる対向電圧が供給されることを特徴とする請求項5に記載の表示装置。

**【請求項 7】**

表示パネルを備え、前記表示パネルに配置された複数の画素と、前記複数の画素で構成される表示部と、前記表示パネルに信号を供給する半導体チップとを有する表示装置であつて、

前記表示パネルは、タッチパネルとしても機能し、前記表示部に形成された複数の映像信号線と、複数のタッチパネル電極と、複数のゲート線と、前記表示部の周辺に形成され前記ゲート線にゲート信号を供給するゲート線駆動回路とを有し、

前記複数の画素の各々は画素トランジスタを有し、前記画素トランジスタのゲート電極には前記ゲート信号が供給され、

前記タッチパネル電極は、複数のブロックに分割されており、

前記分割された各ブロックのタッチパネル電極は、連続する複数の各画素に対して共通に設けられており、

前記半導体チップは、第1方向に伸びる一対の長辺と、前記第1方向と交差する第2方向に伸びる一対の短辺を有し、前記一対の長辺のうち前記表示部側の一方の長辺に、複数の端子からなる第1端子群を有し、

前記第1端子群は、前記分割された各ブロックのタッチパネル電極に接続するタッチパネル端子と、前記映像信号線に接続する映像信号端子とを含み、

前記第1端子群の中で、前記半導体チップの前記一方の長辺の両端部に配置される複数の端子からなる端子群は、前記タッチパネル端子からなる端子群であり、

前記第1端子群の中で、前記映像信号端子からなる端子群は、前記一方の長辺の両端部に配置される複数の前記タッチパネル端子からなる端子群に挟まれて配置され、

前記一対の長辺の他方の長辺には、前記ゲート線駆動回路を制御する制御信号が供給される制御信号端子が形成され、

前記映像信号端子からなる端子群の前記第1方向の幅は、前記タッチパネル端子からなる端子群の前記第1方向の幅よりも広く、

前記映像信号端子からなる端子群の前記第2方向の幅は、前記タッチパネル端子からなる端子群の前記第2方向の幅よりも広いことを特徴とする表示装置。

#### 【請求項8】

前記半導体チップは、前記一対の長辺のうち他方の長辺に、複数の端子からなる第2端子群を有し、

前記第2端子群の中で、前記半導体チップの前記他方の長辺の端部に配置される複数の端子は、前記制御信号端子で、

前記第2端子群の中で、外部からの入力信号が入力される端子が、複数の前記制御信号端子に挟まれて配置されることを特徴とする請求項7に記載の表示装置。

#### 【請求項9】

前記半導体チップは前記表示パネルに搭載されることを特徴とする請求項7に記載の表示装置。

#### 【請求項10】

前記タッチパネル電極には、前記ゲート信号よりもハイ電圧である期間が短いパルス波形の信号が供給されることを特徴とする請求項7に記載の表示装置。

#### 【請求項11】

前記複数の画素には前記映像信号線により映像信号が供給され、

前記画素に前記映像信号が供給される画素書き込み期間に、前記タッチパネル電極には、前記パルス波形の信号とは異なる対向電圧が供給されることを特徴とする請求項10に記載の表示装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、液晶表示装置に係わり、特に、タッチパネルを内蔵したインセル方式の液晶表示装置に適用して有効な技術に関する。

#### 【背景技術】

#### 【0002】

表示画面に使用者の指またはペンなどを用いてタッチ操作（接触押圧操作、以下、単にタッチと称する）して情報を入力する装置（以下、タッチセンサ又はタッチパネルとも称す

10

20

30

40

50

る)を備えた表示装置は、PDAや携帯端末などのモバイル用電子機器、各種の家電製品、現金自動預け払い機(Automated Teller Machine)等に用いられている。

このようなタッチパネルとして、タッチされた部分の容量変化を検出する静電容量方式が知られている。

この静電容量方式タッチパネルとして、下記特許文献1に示すように、タッチパネル機能を液晶表示パネルに内蔵した、所謂、インセル方式のタッチパネルを有する液晶表示装置が知られている。

インセル方式のタッチパネルでは、タッチパネルの走査電極を、液晶表示パネルを構成第1基板(TFT基板ともいう)上に形成される対向電極(コモン電極(CT)ともいう)を分割して使用している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009-258182号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

一般的に、インセル方式のタッチパネルでは、液晶表示パネルの内部に、走査線(ゲート線)を駆動する走査線駆動回路が内蔵されるのが普通である。

また、液晶表示パネルとして、半導体層にアモルファスシリコン層を使用するn型のアモルファスシリコン薄膜トランジスタで構成される駆動回路(以下、a-Si単チャンネル回路構成の駆動回路という)が内蔵されたもの、半導体層にp型あるいはn型のポリシリコン層を使用するポリシリコン薄膜トランジスタで構成される単チャンネル回路構成の駆動回路(以下、p-Si単チャンネル回路構成の駆動回路という)が内蔵されたもの、あるいは、半導体層にp型とn型のポリシリコン層を使用するp型ポリシリコン薄膜トランジスタとn型ポリシリコン薄膜トランジスタで構成されるCMOS回路構成の駆動回路(以下、CMOS回路構成の駆動回路という)が内蔵されたものがある。

そして、インセル方式のタッチパネルに対応したタッチセンス機能内蔵液晶ドライバICを開発するにあたり、a-Si単チャンネル回路構成の駆動回路を有する液晶表示パネル、p-Si単チャンネル回路構成の駆動回路を有する液晶表示パネル、および、CMOS回路構成の駆動回路を有する液晶表示パネル毎に、個別に液晶ドライバICを開発すると、開発コストと開発期間が増大してしまうという問題がある。

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、タッチパネル機能を内蔵した液晶表示装置において、液晶ドライバICの開発コストを低減し、開発期間を短縮することが可能となる技術を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

【課題を解決するための手段】

【0005】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

【0006】

(1)表示パネルを備え、前記表示パネルに配置された複数の画素と、前記複数の画素で構成される表示部と、前記表示パネルに信号を供給する半導体チップとを有する表示装置であって、前記表示パネルは、前記表示部に形成された複数の映像信号線と、複数のタッチパネル電極とを有し、前記タッチパネル電極は、複数のブロックに分割されており、前記分割された各ブロックのタッチパネル電極は、連続する複数の各画素に対して共通に設けられており、前記半導体チップは、第1方向に伸びる一対の長辺と、前記第1方向と交差する第2方向に伸びる一対の短辺を有し、前記一対の長辺のうち前記表示部側の一方の長辺に、複数の端子からなる第1端子群を有し、前記第1端子群は、前記分割された各

ロックのタッチパネル電極に接続するタッチパネル端子と、前記映像信号線に接続する映像信号端子とを含み、前記第1端子群の中で、前記半導体チップの前記一方の長辺の両端部に配置される複数の端子からなる端子群は、前記タッチパネル端子からなる端子群であり、前記第1端子群の中で、前記映像信号端子からなる端子群は、前記一方の長辺の両端部に配置される複数の前記タッチパネル端子からなる端子群に挟まれて配置され、前記映像信号端子からなる端子群の前記第1方向の幅は、前記タッチパネル端子からなる端子群の前記第1方向の幅よりも広く、前記映像信号端子からなる端子群の前記第2方向の幅は、前記タッチパネル端子からなる端子群の前記第2方向の幅よりも広い。

#### 【0007】

(2) 上記(1)において、前記表示部には、複数の画素毎に画素トランジスタと、前記画素トランジスタのゲート電極にゲート信号を供給する複数のゲート線と、前記複数のゲート線に前記ゲート信号を供給するゲート線駆動回路とを有し、前記半導体チップは、前記一対の長辺のうち他方の長辺に、複数の端子からなる第2端子群を有し、前記第2端子群の中で、前記半導体チップの前記他方の長辺の端部に配置される複数の端子は、前記ゲート線駆動回路に制御信号を供給する制御信号端子である。

(3) 上記(2)において、前記第2端子群の中で、外部からの入力信号が入力される端子が、複数の前記制御信号端子に挟まれて配置される。

(4) 上記(1)において、前記半導体チップは前記表示パネルに搭載される。

(5) 上記(2)において、前記タッチパネル電極には、前記ゲート信号よりもハイ電圧である期間が短いパルス波形の信号が供給される。

(6) 上記(5)において、前記複数の画素には前記映像信号線により映像信号が供給され、前記画素に前記映像信号が供給される画素書き込み期間に、前記タッチパネル電極には、前記パルス波形の信号とは異なる対向電圧が供給される。

#### 【0008】

(7) 表示パネルを備え、前記表示パネルに配置された複数の画素と、前記複数の画素で構成される表示部と、前記表示パネルに信号を供給する半導体チップとを有する表示装置であって、前記表示パネルは、タッチパネルとしても機能し、前記表示部に形成された複数の映像信号線と、複数のタッチパネル電極と、複数のゲート線と、前記表示部の周辺に形成され前記ゲート線にゲート信号を供給するゲート線駆動回路とを有し、前記複数の画素の各々は画素トランジスタを有し、前記画素トランジスタのゲート電極には前記ゲート信号が供給され、前記タッチパネル電極は、複数のロックに分割されており、前記分割された各ロックのタッチパネル電極は、連続する複数の各画素に対して共通に設けられており、前記半導体チップは、第1方向に伸びる一対の長辺と、前記第1方向と交差する第2方向に伸びる一対の短辺を有し、前記一対の長辺のうち前記表示部側の一方の長辺に、複数の端子からなる第1端子群を有し、前記第1端子群は、前記分割された各ロックのタッチパネル電極に接続するタッチパネル端子と、前記映像信号線に接続する映像信号端子とを含み、前記第1端子群の中で、前記半導体チップの前記一方の長辺の両端部に配置される複数の端子からなる端子群は、前記タッチパネル端子からなる端子群であり、前記第1端子群の中で、前記映像信号端子からなる端子群は、前記一方の長辺の両端部に配置される複数の前記タッチパネル端子からなる端子群に挟まれて配置され、前記一対の長辺の他方の長辺には、前記ゲート線駆動回路を制御する制御信号が供給される制御信号端子が形成され、前記映像信号端子からなる端子群の前記第1方向の幅は、前記タッチパネル端子からなる端子群の前記第2方向の幅は、前記タッチパネル端子からなる端子群の前記第2方向の幅よりも広い。

#### 【0009】

(8) 上記(7)において、前記半導体チップは、前記一対の長辺のうち他方の長辺に、複数の端子からなる第2端子群を有し、前記第2端子群の中で、前記半導体チップの前記他方の長辺の端部に配置される複数の端子は、前記制御信号端子で、前記第2端子群の中で、外部からの入力信号が入力される端子が、複数の前記制御信号端子に挟まれて配置

10

20

30

40

50

される。

(9) 上記(7)において、前記半導体チップは前記表示パネルに搭載される。

(10) 上記(7)において、前記タッチパネル電極には、前記ゲート信号よりもハイ電圧である期間が短いパルス波形の信号が供給される。

(11) 上記(10)において、前記複数の画素には前記映像信号線により映像信号が供給され、前記画素に前記映像信号が供給される画素書き込み期間に、前記タッチパネル電極には、前記パルス波形の信号とは異なる対向電圧が供給される。

#### 【発明の効果】

#### 【0010】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明のタッチパネル機能を内蔵した液晶表示装置によれば、液晶ドライバICの開発コストを低減し、開発期間を短縮することが可能となる。

#### 【図面の簡単な説明】

#### 【0011】

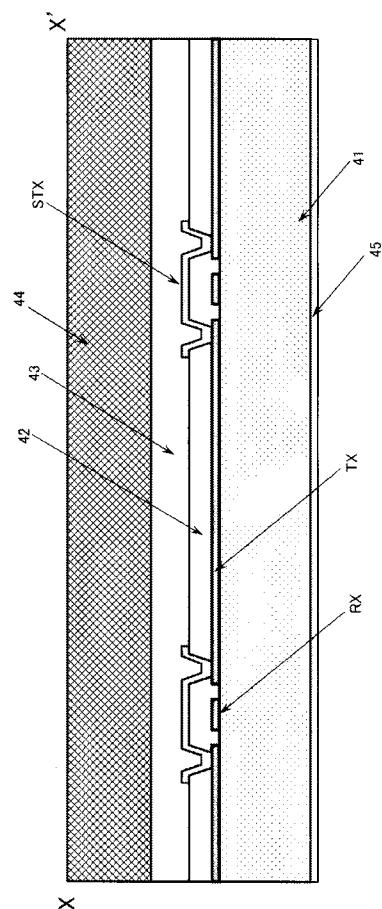

【図1】従来例のタッチパネル付き液晶表示装置の概略構成を示す分解斜視図である。

【図2】図1に示すタッチパネルの電極構成を示す平面図である。

【図3】図1に示すタッチパネルの断面構造を示す断面図である。

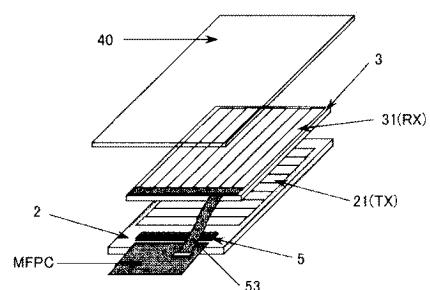

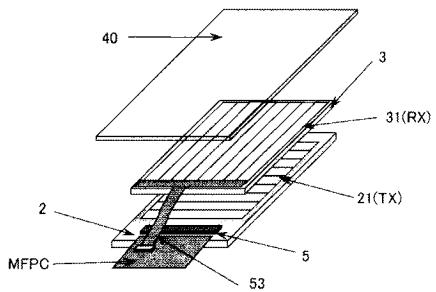

【図4】タッチパネル内蔵液晶表示装置の概略構成を示す分解斜視図である。

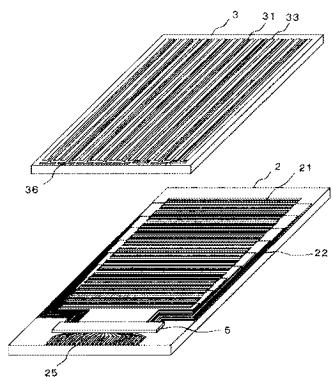

【図5】図4に示すタッチパネル内蔵液晶表示装置における、対向電極と検出電極を説明する図である。

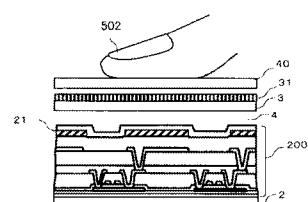

【図6】図4に示すタッチパネル内蔵液晶表示装置の表示部の断面の一部を拡大して示す概略断面図である。

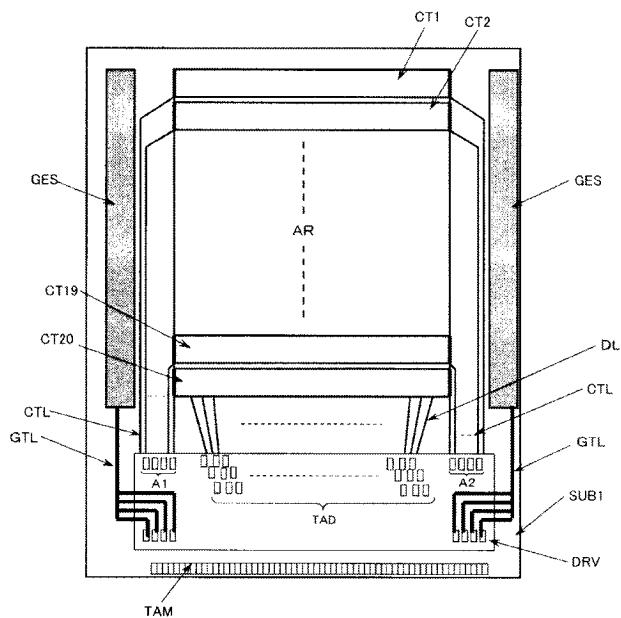

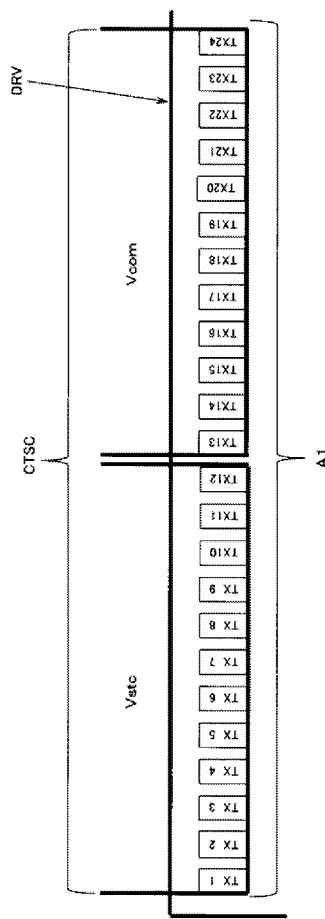

【図7】本発明が適用される液晶表示装置の一例の、複数のブロックに分割した対向電極の一例を示す平面図である。

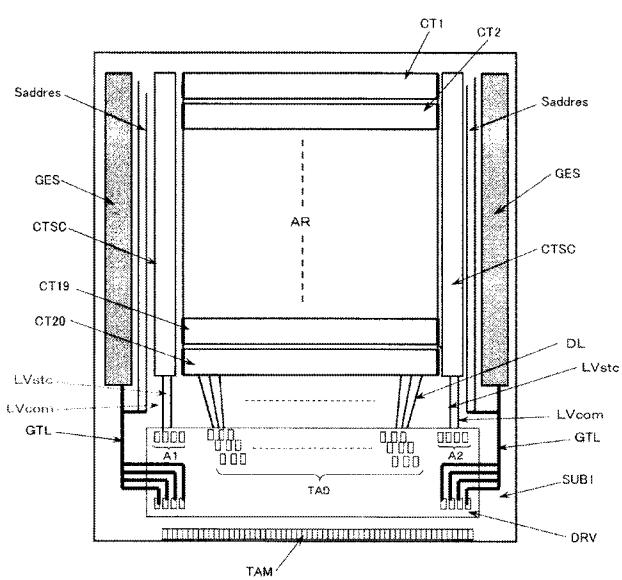

【図8】本発明が適用される液晶表示装置の他の例の、複数のブロックに分割した対向電極の駆動方法を説明するための平面図である。

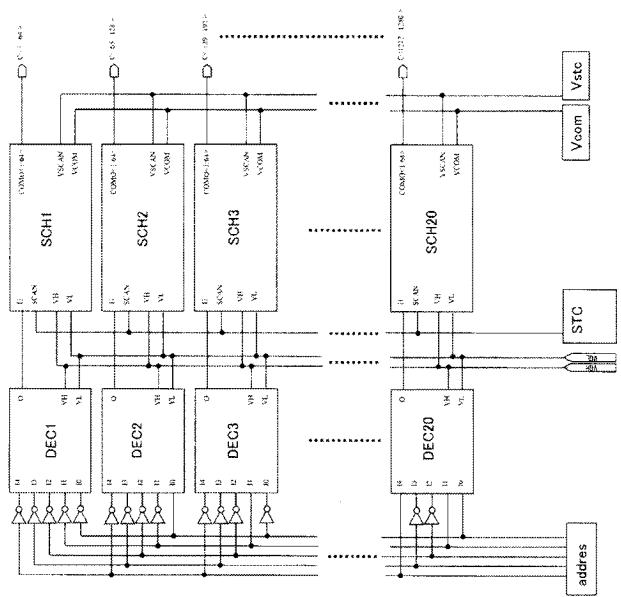

【図9】図8に示す対向電極選択回路の構成例を示すブロック図である。

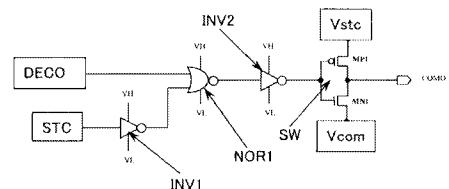

【図10】図9に示す選択回路の一例の回路構成を示す回路図である。

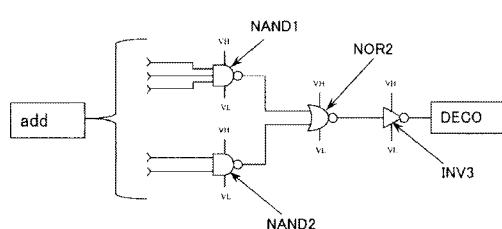

【図11】図9に示すアドレスデコーダ回路の一例の回路構成を示す回路図である。

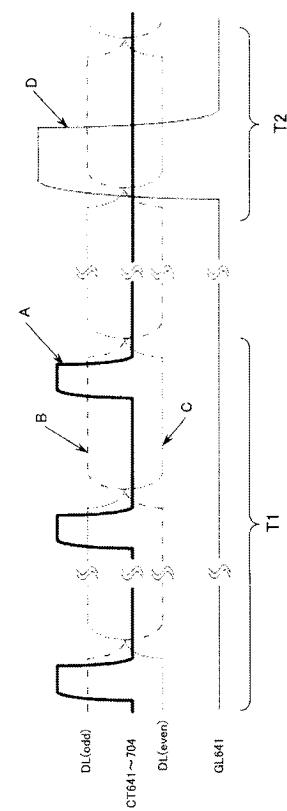

【図12】タッチパネル内蔵液晶表示装置における、タッチパネル検出時と、画素書き込み時の駆動波形を説明するための図である。

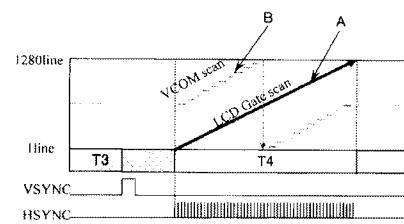

【図13】タッチパネル内蔵液晶表示装置における、タッチパネル検出時と、画素書き込み時のタイミングを説明するための図である。

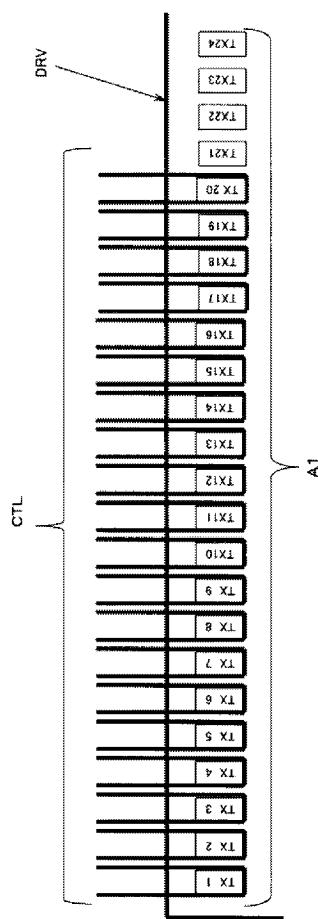

【図14】分割した対向電極を直接駆動する場合の、本発明の実施例の液晶ドライバICの端子(A1)の接続例を示す図である。

【図15】図8に示す対向電極選択回路を使用する場合の、本発明の実施例の液晶ドライバICの端子(A1)の接続例を示す図である。

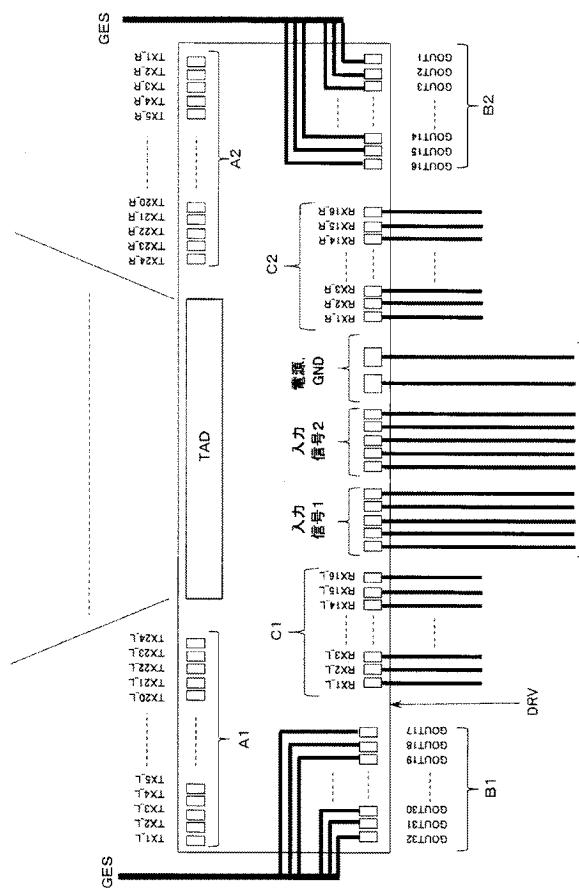

【図16】本発明の実施例の液晶ドライバICの入力側端子の接続例を示す図である。

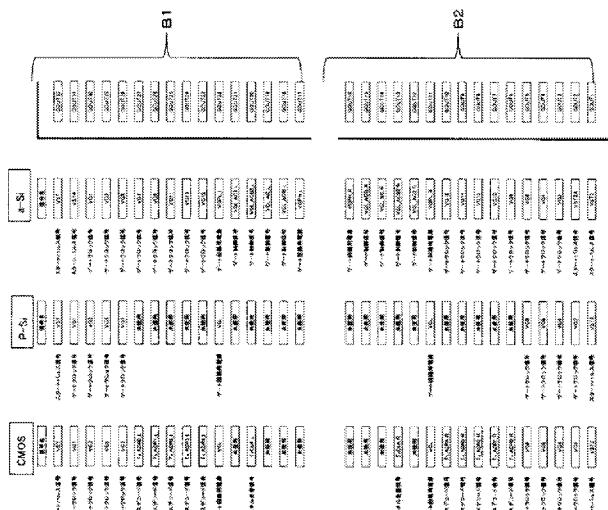

【図17】本実施例の液晶ドライバICの、入力側に配置している端子(B1, B2)の接続例を示す図である。

【図18】本実施例の液晶ドライバICにおいて、左側の端子(C1)を使用した場合の構成図である。

【図19】本実施例の液晶ドライバICにおいて、右側の端子(C2)を使用した場合の構成図である。

#### 【発明を実施するための形態】

#### 【0012】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。また、以下の実施例は、本発明の特許請求の範囲の解

10

20

30

40

50

積を限定するためのものではない。

図1は、従来例のタッチパネル付き液晶表示装置の概略構成を示す分解斜視図である。

図2は、図1に示すタッチパネルの電極構成を示す平面図である。

図3は、図1に示すタッチパネルの断面構造を示す断面図である。

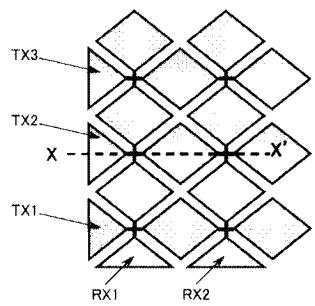

一般的に、タッチパネルは、図2に示すように、容量検出用の走査電極(TX)と、検出電極(RX)を有する。ここでは、例えば、走査電極(TX)を3本(TX1～TX3)、検出電極(RX)を2本(RX1, RX2)で図示しているが、電極数はこれに限らない。

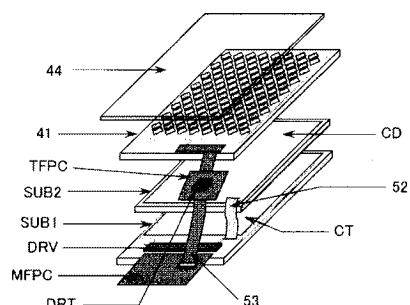

また、タッチパネルは、図1、図3に示すように、タッチパネル基板41と、タッチパネル基板41上に形成される走査電極(TX)および検出電極(RX)と、走査電極(TX)および検出電極(RX)上に形成される層間絶縁膜42と、層間絶縁膜42上に形成され、走査電極(TX)同士を電気的に接続する接続部(STX)と、前記接続部(STX)上に形成される保護膜43と、前記保護膜43上に配置されるフロントウィンドウ(又は、保護フィルム)44と、前記タッチパネル基板41の液晶表示パネル側に形成されるシールド用の透明電極(例えば、ITO(Indium Tin Oxide)膜で形成される電極)45とで構成される。

従来のタッチパネルでは、タッチパネル制御IC(DRT)により、各走査電極(TX)を5V～10V程度の電圧でパルス駆動を行い、タッチパネル制御IC(DRT)において、検出電極(RX)での電圧変化を検出し、タッチ位置の検出を行う。即ち、指等により走査電極(TX)と検出電極(RX)との間の容量値が変化し、走査電極(TX)をパルス駆動した際に、検出電極(RX)で検出される電圧変動が変化することから、検出電極(RX)の電圧を測定することによりタッチ位置を検出することができる。

#### 【0013】

タッチパネルは、液晶表示パネルの前面に設置される。従って、液晶表示パネルに表示された画像を使用者が見る場合には、表示画像がタッチパネルを透過する必要があるため、タッチパネルは光透過率が高いことが望ましい。

液晶表示パネルは、図1に示すように、第1基板(SUB1；以下、TFT基板という)、第2基板(SUB2；以下、CF基板という)と、TFT基板(SUB1)とCF基板(SUB2)との間に挟持される液晶(図示せず)とを有する。

また、TFT基板(SUB1)は、CF基板(SUB2)よりも大きな面積を有し、TFT基板(SUB1)の、CF基板(SUB2)と対向しない領域には、液晶ドライバIC(DRV)が実装され、さらに、当該領域の一辺の周辺部には、メインフレキシブル配線基板(MFPC)が実装される。

なお、図1において、CTは対向電極(共通電極ともいう)、TFPCはタッチパネル用フレキシブル配線基板、CDは裏面側透明導電膜、52は接続部材、53は接続用フレキシブル配線基板である。

IPS方式の液晶表示パネルは、TN方式の液晶表示パネルやVA方式の液晶表示パネルのように、カラーフィルタが設けられる基板上に対向電極(CT)が存在しない。そのため、表示ノイズを低減する等の理由により、カラーフィルタが設けられる基板上に、例えばITOなどの透明導電膜で構成される裏面側透明導電膜(CD)が形成されている。

#### 【0014】

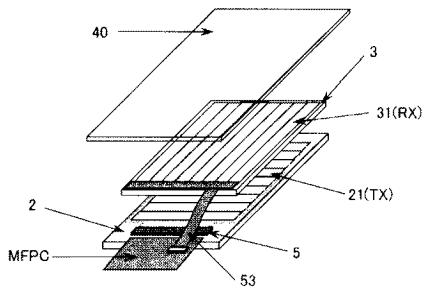

図4は、液晶表示パネルの内部にタッチパネルを内蔵したタッチパネル内蔵液晶表示装置の概略構成を示す分解斜視図である。

図4において、2はTFT基板、3はCF基板と、21は対向電極(共通電極ともいう)、5は液晶ドライバIC、MFPCはメインフレキシブル配線基板、40はフロントウィンドウ、53は接続用フレキシブル配線基板である。

図4に示す液晶表示装置では、CF基板3上の裏面側透明導電膜(CD)を、帯状のパターンに分割して、タッチパネルの検出電極(RX)31となし、TFT基板2の内部に形成される対向電極21を帯状のパターンに分割、即ち、複数のブロックに分割して、タッチパネルの走査電極(TX)として兼用することにより、タッチパネル基板(図1の4

10

20

30

40

50

1)を削減している。そのため、図4に示す液晶表示装置では、図1に示すタッチパネル制御IC(DR T)の機能が、液晶ドライバIC5の内部に設けられる。

【0015】

次に、図5を用いて、図4に示す液晶表示装置の対向電極21と検出電極31について説明する。

前述したように、対向電極21はTFT基板2上に設けられているが、複数本の(例えば20本程度)対向電極21が両端で共通に接続され、対向電極信号線22と接続されている。

図5に示す液晶表示装置では、束状の対向電極21が走査電極(TX)を兼用し、また、検出電極31が検出電極(RX)を構成する。

したがって、対向電極信号には、画像表示に用いられる対向電圧と、タッチ位置の検出に用いられるタッチパネル走査電圧とが含まれる。タッチパネル走査電圧が対向電極21に印加されると、対向電極21と一定の間隔を持って配置され容量を構成する検出電極31に検出信号が生じる。この検出信号は検出電極用端子36を介して外部に取り出される。

なお、検出電極31の両側にはダミー電極33が形成されている。検出電極31は一方の端部でダミー電極33側に向かい広がりT字状の検出電極用端子36を形成している。また、TFT基板2には対向電極信号線22以外にも駆動回路用入力端子25のような様々な配線、端子等が形成される。

【0016】

図4に示す液晶表示装置における、表示部の断面の一部を拡大した概略断面図を図6に示す。

図6に示すようにTFT基板2には画素部200が設けられており、対向電極21は画素の一部として画像表示に用いられる。また、TFT基板2とCF基板3との間には液晶組成物4が狭持されている。CF基板3に設けられた検出電極31とTFT基板に設けられた対向電極21とは容量を形成しており、対向電極21に駆動信号が印加されると検出電極31の電圧が変化する。

この時、図6に示すように、フロントウィンドウ40を介して指502等の導電体が近接または接触すると、容量に変化が生じ検出電極31に生じる電圧に、近接・接触が無い場合に比較して変化が生じる。

このように、液晶表示パネルに形成した対向電極21と検出電極31との間に生じる容量の変化を検出することで、液晶表示パネルにタッチパネルの機能を備えることが可能となる。

【0017】

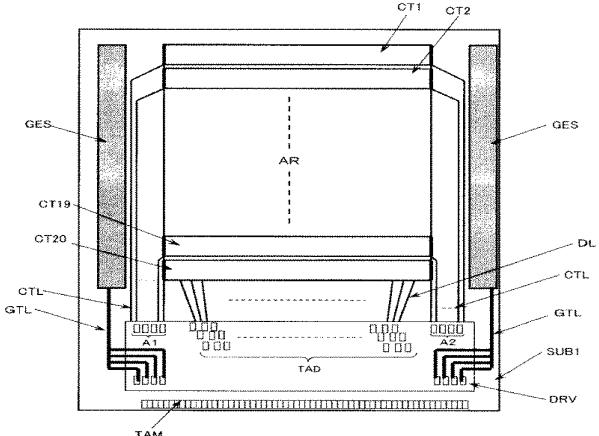

図7は、本発明が適用される液晶表示装置の一例の、複数のブロックに分割した対向電極の一例を示す平面図である。図7において、SUB1はTFT基板、DRVは液晶ドライバIC、CT1～CT20は帯状のパターンに分割された各ブロックの対向電極、DLは映像線、CTLは対向電極配線、GESは液晶表示パネルに内蔵された走査線駆動回路、GTLは走査線駆動回路信号配線、TAMはメインフレキシブル配線基板(MFPC)と接続される端子部、ARはマトリクス状に配置された複数の画素で構成される表示領域である。

図7に示す例では、走査線駆動回路(GES)として、a-Si単チャンネル回路構成の駆動回路、あるいは、半導体層にn型のポリシリコン層を使用する、p-Si単チャンネル回路構成の駆動回路が使用される。

静電容量方式のタッチパネルでは、指等による静電容量の変化を検出するため、交流駆動を行うタッチパネル用の走査電極(TX)の幅は約4～5mm程度の幅があることが望ましい。そのため、液晶表示パネルの大型化により走査電極(TX)の本数は増加する。

図7に示す例では、1280表示ラインの対向電極(CT)を、CT1～CT20の20ブロック(1ブロックは64表示ラインの対向電極で構成される)に分割しており、対向電極配線(CTL)は左右に各20本必要となる。

10

20

30

40

50

各ブロックの対向電極（C T 1 ~ C T 2 0）は、表示動作において寄生容量により電圧変動した場合は画質悪化を引き起す。そのため、各々のブロックの対向電極（C T 1 ~ C T 2 0）と、液晶ドライバIC（D R V）とを接続する対向電極配線（C T L）の抵抗値を下げる必要がある。また、走査線駆動回路（G E S）上にも配線があるため、対向電極配線（C T L）を走査線駆動回路（G E S）上に配線することはできない。

そのため、対向電極配線（C T L）は、走査線駆動回路（G E S）より対向電極（C T）側に配置する。

これに対応し、液晶ドライバIC（D R V）は、半導体チップの表示領域（A R）の中央に映像線（図示せず）に接続される映像線駆動端子（T A D）を配置し、その左右両端に、対向電極配線（C T L）に接続される端子（A 1, A 2）を配置している。 10

### 【0018】

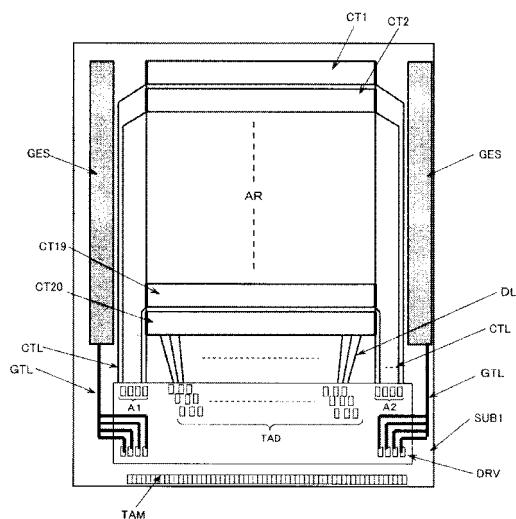

図8は、本発明が適用される液晶表示装置の他の例の、複数のブロックに分割した対向電極の駆動方法を説明するための平面図である。

図8に示す液晶表示装置は、20ブロックに分割した各々の対向電極（C T 1 ~ C T 2 0）を、アドレスデコード方式により選択する対向電極選択回路（C T S C）を、液晶表示パネルの内部に内蔵した点で、図7に示す液晶表示装置と相違する。

図8では、対向電極選択回路（C T S C）として、CMOS回路構成の駆動回路が使用される。

20ブロックに分割した対向電極（C T 1 ~ C T 2 0）の選択方法をアドレスデコード方式とすることにより、低抵抗が必要となる配線は、対向電極（C T 1 ~ C T 2 0）に供給する対向電圧（V c o m）の配線（L V c o m）と、タッチパネル走査電圧（V s t c）の配線（L V s t c）の2本となる。 20

本実施例では、タッチパネル走査電圧（V s t c）は、対向電圧（V c o m）に対して、5~10V高い電圧を直流で供給し、アドレス信号線（S a d d r e s s）を介して供給されるアドレス信号（a d d r e s s）により走査箇所の選択を行い、タッチパネル走査信号（S T C）に従い、走査電極（T X）を兼ねる、選択されたブロックの対向電極（C T）に対して、対向電圧（V c o m）、あるいは、タッチパネル走査電圧（V s t c）を切り替えて出力する。

対向電極（C T）の分割数が増加した場合でも、増加する配線は、アドレス信号線（S a d d r e s s）のみであり、液晶表示パネルの左右の額縁の増加を抑制したまま、タッチパネル走査電極として使用する対向電極の分割数を増加させることが可能となる。 30

### 【0019】

図9は、図8に示す対向電極選択回路（C T S C）の構成例を示すブロック図である。図9に示すように、対向電極選択回路（C T S C）は、D E C 1 ~ D E C 2 0のアドレスデコード回路と、S C H 1 ~ S C H 2 0の選択回路で構成されている。

図8に示す液晶表示装置では、タッチパネルの走査電極（T X）が5mmピッチとなるように、64表示ライン分の対向電極（C T）を、液晶表示パネルの内部で電気的に接続して1つのブロックとし、1280の表示ラインを20分割する。そして、当該20分割された対向電極（C T 1 ~ C T 2 0）と、アドレスデコード回路（D E C 1 ~ D E C 2 0）とを、1対1で割りつけている。分割数が、20ブロックであるため、アドレス信号線（S a d d）は5bitの5本が必要となる。 40

アドレス信号（a d d r e s s）により選択された、1ブロックの対向電極、即ち、64表示ライン分の対向電極（C T）が、タッチパネル走査信号（S T C）により交流駆動を行い、その他の対向電極（C T）は対向電圧を出力する。

### 【0020】

図10は、図9に示す選択回路（S C H 1 ~ S C H 2 0）の一例の回路構成を示す回路図である。

図10に示す選択回路は、アドレスデコード回路（D E C 1 ~ D E C 2 0）の出力（D E C O）と、インバータ（I N V 1）で反転されたタッチパネル走査信号（S T C）の反転信号とを、ノア回路（N O R 1）に入力し、当該ノア回路（N O R 1）の出力をインバ

ータ (IN V 2) で反転して、スイッチ回路 (SW) に入力することにより、タッチパネル走査電圧 (Vstc)、あるいは、対向電圧 (Vcom) を選択して各ブロックの対向電極 (CT 1 ~ CT 20) に出力する。

これにより、アドレスデコーダ回路 (DEC 1 ~ DEC 20) の一つが選択された場合、タッチパネル走査信号 (STC) に従い、各ブロックの対向電極に、タッチパネル走査電圧 (Vstc) と、対向電圧 (Vcom) とを切り替えて出力する。

即ち、図 8 に示す選択回路では、アドレスデコーダ回路 (DEC 1 ~ DEC 20) の出力 (DEC0) が、Low レベル (以下、L レベル)、および、タッチパネル走査信号 (STC) が High レベル (以下、H レベル) のときに、ノア回路 (NOR1) の出力が H レベルとなるので、スイッチ回路 (SW) は、タッチパネル走査電圧 (Vstc) を選択し、タッチパネル走査信号 (STC) が L レベル、あるいは、アドレスデコーダ回路 (DEC 1 ~ DEC 20) の出力 (DEC0) が、H レベルのときに、ノア回路 (NOR1) の出力が L レベルとなるので、スイッチ回路 (SW) は、対向電圧 (Vcom) を選択する。

#### 【0021】

図 11 は、図 7 に示すアドレスデコーダ回路 (DEC 1 ~ DEC 20) の一例の回路構成を示す回路図である。

図 11 に示すように、アドレスデコーダ回路 (DEC 1 ~ DEC 20) には、5 個のアドレス信号 (address) の各々について、アドレス信号、あるいは、アドレス信号をインバータ (INV) で反転した反転信号が入力され、5 個のアドレス信号 (address) と 5 個のアドレス信号 (address) の反転信号の組み合わせに基づきデコードする。

図 11 に示すアドレスデコーダ回路では、アドレスデコーダ回路に入力された 5 個のアドレス信号 (address) と 5 個のアドレス信号 (address) の反転信号の中の所定の組み合わせのアドレス信号 (add) を NAND 回路 (NAND1, NAND2) に入力し、当該 NAND 回路 (NAND1, NAND2) の出力を、ノア回路 (NOR2) に入力し、当該ノア回路 (NOR2) の出力をインバータ (INV3) で反転して、アドレスデコーダ回路の出力 (DEC0) としている。したがって、図 11 に示すアドレスデコーダ回路では、アドレス信号の組み合わせが、自アドレスデコーダ回路に設定されたアドレス信号の組み合わせと一致するときに、L レベルの電圧が、アドレスデコーダ回路の出力 (DEC0) として出力され、アドレス信号の組み合わせが、自アドレスデコーダ回路に設定されたアドレス信号の組み合わせと一致しないときに、H レベルの電圧が、アドレスデコーダ回路の出力 (DEC0) として出力される。

#### 【0022】

図 12 は、タッチパネル内蔵液晶表示装置における、タッチパネル検出時と、画素書き込み時の駆動波形を説明するための図である。

図 12 の A は、20 ブロックに分割された対向電極のうち、11 番目のブロックとなる 641 ~ 704 表示ラインの対向電極 (CT 11) に供給されるタッチパネル走査電圧 (Vstc) の電圧波形を示している。また、図 12 の B は、奇数列の映像線 (DL) に供給される映像電圧の波形を、図 12 の C は、偶数列の映像線 (DL) に供給される映像電圧の波形を、図 12 の D は、641 番目の走査線 (GL) を介して、641 表示ラインの薄膜トランジスタのゲート電極に供給されるゲート信号を示している。さらに、T1 は、タッチ位置検出期間、T2 は画素書き込み期間を示している。

タッチ位置検出期間 (T1) は、表示への影響を防止するため、画素書き込み期間 (T2) 以外の期間に設定される。また、タッチ位置検出期間 (T1) において、検出感度を増加させるために、同一箇所の走査電極 (TX) で複数回のスキャン、即ち、図 12 では、11 番目のブロックの対向電極 (CT 11) に、複数回タッチパネル走査電圧 (Vstc) が供給される。また、画素書き込み期間 (T2) 内には、11 番目のブロックの対向電極 (CT 11) には、タッチパネル走査電圧 (Vstc) が供給されず、対向電圧 (Vcom) が供給される。

10

20

30

40

50

## 【0023】

図13は、タッチパネル内蔵液晶表示装置における、タッチパネル検出時と、画素書き込み時のタイミングを説明するための図である。

図13のAは、1フレームの画素書き込み期間( $T_4$ )に、1番目の表示ラインから1280表示ラインまでの画素書き込みタイミングを示し、図13のBが、20ブロックに分割された各ブロックの対向電極( $C_{T1} \sim C_{T20}$ )におけるタッチパネル検出タイミングを示す。

図13に示すように、任意の表示ラインの対向電極を走査電極( $T_X$ )として機能させ、タッチパネル検出時のスキャン動作は、画素書き込みを行うゲートスキャンとは異なる箇所で行う。なお、図13において、 $T_3$ は帰線期間、 $VSYNC$ は垂直同期信号、 $HSYNC$ は水平同期信号を示す。

## 【0024】

本実施例の液晶ドライバIC( $DRV$ )では、半導体チップの表示領域( $AR$ )の一辺に配置される端子群の中で、中央に映像線( $DL$ )に接続される映像線端子( $TAD$ )を配置し、その左右端に、対向電極配線( $CTL$ )に接続される端子( $A_1, A_2$ )を配置する。

静電容量方式タッチパネルでは、指等による静電容量の変化を検出するため、交流駆動を行う走査電極の幅は約4~5mm程度の幅があることが望ましいため、液晶表示パネルの大型化により走査電極の本数は増加する。

現在携帯モバイル向けの液晶表示パネルでは、5.5インチの表示領域の要求もあり縦方向の寸法は120mmになるため、5mm幅で対向電極( $CT$ )を分割すると24本になる。一方、現行のスマートフォン向けには、4インチクラスのWVGA(480RGB × 800)が一般的で縦方向の寸法は90mmになるので、5mm幅で対向電極( $CT$ )を分割すると18本になる。

そこで、本実施例の液晶ドライバIC( $DRV$ )では、5.5インチの液晶表示パネルまで対応できるように、対向電極配線( $CTL$ )に接続される端子( $A_1, A_2$ )を24端子としている。

また、本実施例の液晶ドライバIC( $DRV$ )では、様々な対向電極本数の液晶表示パネルに対応できるように、対向電極配線( $CTL$ )に接続するために使用する使用端子数を、1本から24本まで切り替えられるようになっている。

また、前述したように画質劣化防止のため、対向電極配線( $CTL$ )は低抵抗にする必要がある。そのため、本実施例の液晶ドライバIC( $DRV$ )では、半導体チップの出力端子の左右両端に同じ機能を持つ、 $A_1, A_2$ の端子を設けて、対向電極( $CT$ )に対して両側から給電できるようにしている。

## 【0025】

図14に、分割した対向電極( $CT$ )を直接駆動する場合の、本実施例の液晶ドライバIC( $DRV$ )の端子( $A_1$ )の接続例を示す。

なお、図14は、本実施例の液晶ドライバIC( $DRV$ )を構成する半導体チップの表示領域( $AR$ )側の辺に形成されている端子群の中の左側の複数の端子( $A_1$ の端子)を図示している。

前述したように、本実施例の液晶ドライバIC( $DRV$ )では、対向電極配線( $CTL$ )に接続するために使用する使用端子数を、 $TX_1 \sim TX_{24}$ の1本から24本まで切り替えられるようになっているが、図14では、 $TX_1 \sim TX_{20}$ の20本の端子を使用している。なお、本実施例の液晶ドライバIC( $DRV$ )を構成する半導体チップの表示領域( $AR$ )側の辺に形成されている端子群の中の右側も同様な構成となっている。

図14では、 $TX_1 \sim TX_{20}$ の端子の各々に、 $CT_1 \sim CT_{20}$ の対向電極に接続される対向電極配線( $CTL$ )が接続される。

タッチ位置検出を行う端子は、例えば、図12、図13に示すタイミングで、タッチパネル走査電圧( $V_{stc}$ )を出力し、その他の端子は、対向電圧( $V_{com}$ )を出力する。

10

20

30

40

50

図15に、図8に示す対向電極選択回路(CTSC)を使用する場合の、本実施例の液晶ドライバIC(DRV)の端子(A1)の接続例を示す。

本実施例の液晶ドライバIC(DRV)では、内部のレジスタのデータ値を切り替えることにより、TX1～TX12の端子を、タッチパネル走査電圧(Vstc)を出力する端子に、TX13からTX24の端子を、対向電圧(Vcom)を出力する端子に固定して、図8に示す対向電極選択回路(CTSC)に出力する。

図15の場合、本実施例の液晶ドライバIC(DRV)の各出力端子の出力インピーダンスは100ため12本ずつ並列に接続することにより、タッチパネル走査電圧(Vstc)および対向電圧(Vcom)を出力する端子の出力インピーダンスを $100 \div 12 = 8.3$ に低減することができる。

#### 【0026】

従来の液晶ドライバIC(DRV)では、走査線駆動回路(GES)を駆動するための制御信号を出力する端子を、液晶ドライバIC(DRV)を構成する半導体チップの表示領域(AR)側(以下、出力側という)の辺に形成されている端子群の中に配置している。

しかし、対向電極配線(CTL)は、低抵抗にする必要があるため、対向電極配線(CTL)に接続される端子(A1, A2)は、液晶ドライバIC(DRV)を構成する半導体チップの出力側の辺に配置する必要がある。

これに加えて、走査線駆動回路(GES)を駆動するための制御信号を出力する端子を、液晶ドライバIC(DRV)を構成する半導体チップの出力側の辺に配置するとチップサイズが増大し、チップコストの増加につながる。

そこで、本実施例では、走査線駆動回路(GES)を駆動するための制御信号を出力する端子(B1, B2)を、液晶ドライバIC(DRV)を構成する半導体チップの表示領域(AR)と反対側(以下、入力側という)に配置している。

図16に、本実施例の液晶ドライバIC(DRV)の、入力側の端子の接続例を示す。

図16において、TADは映像線端子、A1, A2は対向電極配線(CTL)に接続される端子、B1, B2は走査線駆動回路(GES)を駆動するための制御信号を出力する端子、C1, C2はタッチパネルの検出電極(RX)で検出された検出信号が入力される端子、Dは外部からの入力信号、電源電圧が入力される端子である。

#### 【0027】

図17に、本実施例の液晶ドライバIC(DRV)の、入力側に配置している端子(B1, B2)の接続例を示す。

各画素の薄膜トランジスタ(TFT)の、ゲート選択電圧をVGH、ゲート非選択電圧をVGLとすると、a-Si単チャンネル回路構成の駆動回路、あるいは、p-Si単チャンネル回路構成の駆動回路からなる走査線駆動回路(GES)では、(VGH - VGL)振幅の駆動信号を入力しゲートスキャン動作を行っている。

同じく、CMOS回路構成の駆動回路からなる対向電極選択回路(CTSC)のアドレス信号(address)も(VGH - VGL)振幅の信号である。

しかし、半導体層にアモルファスシリコンを使用するアモルファスシリコン薄膜トランジスタ(a-Si TFT)に必要な電圧レベルは、例えばVGH = 16V, VGL = -13Vであり、半導体層にn型ポリシリコンを使用するポリシリコン薄膜トランジスタ(p-Si TFT)に必要な電圧レベルは、例えばVGH = 11V, VGL = -8Vであり、両者は異なっている。

また、a-Si単チャンネル回路構成の駆動回路、p-Si単チャンネル回路構成の駆動回路、および、CMOS回路構成の駆動回路は、その回路構成からそれぞれ異なる駆動波形が必要であり、それぞれの駆動波形を個別の出力端子で出力すると端子数の増加によりチップサイズが大きくなってしまう。

#### 【0028】

そこで、本実施例の液晶ドライバIC(DRV)では、液晶表示パネルに内蔵される、a-Si単チャンネル回路構成の駆動回路、p-Si単チャンネル回路構成の駆動回路、

10

20

30

40

50

および、C M O S回路構成の駆動回路の各々の駆動信号を、同じ共通端子を使用して、レジスタに書き込むデータ値により、各端子から出力される信号、あるいは、波形を切り替えられるようにしている。

また、V G H , V G Lの電圧レベルも、レジスタに書き込むデータ値により切替られるようにして、1つの共通端子で、a - S i 単チャンネル回路構成の駆動回路、p - S i 単チャンネル回路構成の駆動回路、および、C M O S回路構成の駆動回路に対応できるようにしている。

例えは、図17では、液晶ドライバI C ( D R V )の右側の端子 ( B 2 )のG O U T 7の端子では、内蔵回路がa - S i 単チャンネル回路構成の駆動回路 ( 図17のa - S i )の場合、「ゲートクロック信号 ( V G 1 0 )」であり、内蔵回路がp - S i 単チャンネル回路構成の駆動回路 ( 図17のp - S i )の場合、「未使用」であり、内蔵回路がC M O S回路構成の駆動回路 ( 図17のC M O S )の場合、「アドレスデコード信号 ( T x \_ A D R 1 \_ R )」となっている。

#### 【0029】

本実施例のインセル方式のタッチパネルでは、各走査電極 ( T X )を4 V ~ 6 V程度の電圧でパルス駆動を行い、検出電極 ( R X )での電圧変化を検出している。

指等により、走査電極 ( T X )と検出電極 ( R X )との間の寄生容量が変化し、走査電極 ( T X )を4 V ~ 6 V程度の電圧でパルス駆動を行った際の、検出電極 ( R X )の電圧変動が変化することから、検出電極 ( R X )の電圧を測定することによりタッチ位置を検出することができる。

そのため、メインフレキシブル配線基板 ( M F P C )上の検出電極 ( R X )用の配線は、外来ノイズの影響を受けないように配線の上下配線層や両隣りの配線を、接地電圧 ( G N D )でシールドしている。

本実施例の液晶ドライバI C ( D R V )では、タッチセンス機能を内蔵するにあたり、検出電極 ( R X )で検出された検出信号の入力端子位置が課題となる。

本実施例の液晶ドライバI C ( D R V )では、入力端子 ( D )に入力される信号・電圧は、入力信号1、入力信号2、電源、G N Dがある。入力信号1と入力信号2は、それぞれ異なるインターフェースの信号であり、2つの信号が同時に使用されることなく、本体側の構成により、いずれか一方の系統が使用される。

さらに、インセル方式のタッチパネルでは、検出電極 ( R X )用の配線は、C F基板 ( 3 , S U B 2 )側の基板 ( 例えは、ガラス基板 )にF O G ( F i l m O n G l a s s )で接続された接続用フレキシブル配線基板53からT F T基板 ( 2 , S U B 1 )のメインフレキシブル配線基板 ( M F P C )に接続するため、メインフレキシブル配線基板 ( M F P C )を含めた製品の外形要求に対して自由にレイアウトできなければならない。

そこで、本実施例の液晶ドライバI C ( D R V )では、検出電極 ( R X )で検出された検出信号の入力端子 ( C 1 , C 2 )を、入力端子 ( D )の両隣りに1セットずつ設けている。

検出電極 ( R X )で検出された検出信号の入力端子 ( C 1 , C 2 )を、図16に示すように、配置することにより、液晶表示パネル側へ配線する走査線駆動回路信号配線 ( G T L )とも交差せずノイズの影響を受けない。

さらに、同じ機能を持つ端子を左右に配置することによって、製品の外形要求に合わせて使用端子を選択することができる。なお、検出電極 ( R X )で検出された検出信号の入力端子 ( C 1 , C 2 )は、製品によりどちらかの端子のみを使用する。

図18に、検出電極 ( R X )で検出された検出信号の入力端子として、左側の端子 ( C 1 )を使用する場合の構成を、図19に、検出電極 ( R X )で検出された検出信号の入力端子として、右側の端子 ( C 2 )を使用する場合の構成を示す。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

#### 【符号の説明】

10

20

30

40

50

## 【 0 0 3 0 】

|                                               |                                     |    |

|-----------------------------------------------|-------------------------------------|----|

| 2 , S U B 1                                   | 第 1 基板                              |    |

| 3 , S U B 2                                   | 第 2 基板                              |    |

| 4 液晶組成物                                       |                                     |    |

| 5 , D R V                                     | 液晶ドライバ I C                          |    |

| 2 1 , C T , C T 1 ~ C T 2 0                   | 対向電極                                |    |

| 2 2                                           | 対向電極信号線                             |    |

| 2 5                                           | 駆動回路用入力端子                           |    |

| 3 1                                           | 検出電極                                | 10 |

| 3 3                                           | ダミー電極                               |    |

| 3 6                                           | 検出電極用端子                             |    |

| 4 0 , 4 4                                     | フロントウィンドウ ( 又は、保護フィルム )             |    |

| 4 1                                           | タッチパネル基板                            |    |

| 4 2 , P A S 1 , P A S 2                       | 層間絶縁膜                               |    |

| 4 3                                           | 保護膜                                 |    |

| 4 5                                           | シールド用の透明電極                          |    |

| 5 2                                           | 接続部材                                |    |

| 5 3                                           | 接続用フレキシブル配線基板                       |    |

| 2 0 0                                         | 画素部                                 |    |

| 5 0 2                                         | 指                                   | 20 |

| T A D , A 1 , A 2 , B 1 , B 2 , C 1 , C 2 , D | 端子                                  |    |

| T X                                           | タッチパネルの走査電極                         |    |

| R X                                           | タッチパネルの検出電極                         |    |

| A R                                           | 表示領域                                |    |

| D R T                                         | タッチパネル制御 I C                        |    |

| M F P C                                       | メインフレキシブル配線基板                       |    |

| T F P C                                       | タッチパネル用フレキシブル配線基板                   |    |

| G E S                                         | 走査線駆動回路                             |    |

| C T S C                                       | 対向電極選択回路                            |    |

| C T L                                         | 対向電極配線                              | 30 |

| L V c o m , L V s t c                         | 配線                                  |    |

| C D                                           | 裏面側透明導電膜                            |    |

| D E C 1 ~ D E C 2 0                           | アドレスデコーダ回路                          |    |

| S C H 1 ~ S C H 2 0                           | 選択回路                                |    |

| I N V 1 ~ I N V 3                             | インバータ                               |    |

| N O R 1 , N O R 2                             | ノア回路                                |    |

| N A N D 1 , N A N D 2                         | NAND 回路                             |    |

| S W                                           | スイッチ回路                              |    |

| S T X                                         | 接続部                                 |    |

| T A M                                         | メインフレキシブル配線基板 ( M F P C ) と接続される端子部 | 40 |

| G T L                                         | 走査線駆動回路信号配線                         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【 図 1 6 】

【 図 1 7 】

【 図 1 8 】

【 図 1 9 】

## フロントページの続き

| (51) Int.CI.   |               | F I              |         |        | テーマコード(参考) |           |

|----------------|---------------|------------------|---------|--------|------------|-----------|

| <b>G 0 6 F</b> | <b>3/044</b>  | <b>(2006.01)</b> | G 0 9 G | 3/20   | 6 2 2 A    | 5 C 0 9 4 |

| <b>G 0 2 F</b> | <b>1/1345</b> | <b>(2006.01)</b> | G 0 9 G | 3/20   | 6 2 1 M    | 5 G 4 3 5 |

| <b>G 0 2 F</b> | <b>1/1343</b> | <b>(2006.01)</b> | G 0 9 G | 3/20   | 6 1 1 F    |           |

| <b>G 0 2 F</b> | <b>1/1333</b> | <b>(2006.01)</b> | G 0 9 G | 3/20   | 6 7 0 F    |           |

| <b>G 0 2 F</b> | <b>1/133</b>  | <b>(2006.01)</b> | G 0 9 G | 3/20   | 6 8 0 G    |           |

|                |               |                  | G 0 6 F | 3/041  | 4 1 2      |           |

|                |               |                  | G 0 6 F | 3/041  | 4 3 0      |           |

|                |               |                  | G 0 6 F | 3/044  | 1 2 8      |           |

|                |               |                  | G 0 2 F | 1/1345 |            |           |

|                |               |                  | G 0 2 F | 1/1343 |            |           |

|                |               |                  | G 0 2 F | 1/1333 |            |           |

|                |               |                  | G 0 2 F | 1/133  | 5 3 0      |           |

F ターム(参考) 5C006 AA21 AC25 AF44 AF71 AF73 BB16 BC03 BC11 BC20 BF38

EC02 EC05 FA31 FA37 FA51

5C080 AA10 BB05 CC03 DD27 EE30 FF11 JJ02 JJ03 JJ04 JJ06

KK07

5C094 AA44 BA03 BA43 CA19 DB01 DB03 FA01

5G435 AA17 BB12 CC09 EE37 EE49

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2020073958A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2020-05-14 |

| 申请号            | JP2019167601                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2019-09-13 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 松元秀一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 松元秀一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09F9/30 G09F9/00 G09G3/36 G09G3/20 G06F3/041 G06F3/044 G02F1/1345 G02F1/1343 G02F1/1333 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09F9/30.330 G09F9/00.366.A G09G3/36 G09G3/20.691.D G09G3/20.624.C G09G3/20.622.A G09G3/20.621.M G09G3/20.611.F G09G3/20.670.F G09G3/20.680.G G06F3/041.412 G06F3/041.430 G06F3/044.128 G02F1/1345 G02F1/1343 G02F1/1333 G02F1/133.530                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H092/GA33 2H092/GA44 2H092/GA60 2H092/GA62 2H092/JA24 2H092/JB14 2H092/NA27 2H189/AA14 2H189/HA12 2H189/LA04 2H189/LA10 2H189/LA28 2H189/LA31 2H193/ZA04 2H193/ZA09 2H193/ZC25 2H193/ZE09 2H193/ZF43 2H193/ZF51 2H193/ZF52 2H193/ZJ02 5C006/AA21 5C006/AC25 5C006/AF44 5C006/AF71 5C006/AF73 5C006/BB16 5C006/BC03 5C006/BC11 5C006/BC20 5C006/BF38 5C006/EC02 5C006/EC05 5C006/FA31 5C006/FA37 5C006/FA51 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD27 5C080/EE30 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C080/KK07 5C094/AA44 5C094/BA03 5C094/BA43 5C094/CA19 5C094/DB01 5C094/DB03 5C094/FA01 5G435/AA17 5G435/BB12 5G435/CC09 5G435/EE37 5G435/EE49 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

### 摘要(译)

解决的问题：提供一种具有内置的触摸面板功能的液晶显示装置，该液晶显示装置降低了液晶驱动器IC的开发成本并缩短了开发周期。显示装置包括将信号提供给显示面板的半导体芯片。显示面板具有形成在显示部分中的多个视频信号线DL和多个触摸面板电极CTL。半导体芯片DRV在一对长边中的显示单元侧的一个长边上具有第一端子组，并且第一端子组包括连接至触摸板电极和视频信号线的触摸板端子组A1和A2。与视频信号端子组TAD相连。在第一端子组中，布置在半导体芯片的显示侧上的长边的两端处的多个端子是触摸板端子组，并且视频信号端子组是布置在两端处的多个触摸板端子。它们放置在组之间。视频信号端子组的宽度在半导体芯片的长边方向和短边方向上均比触摸面板端子组的宽度宽。[选择图]图7