(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-114877

(P2016-114877A)

(43) 公開日 平成28年6月23日(2016.6.23)

|                              |           |             |

|------------------------------|-----------|-------------|

| (51) Int.Cl.                 | F 1       | テーマコード (参考) |

| <b>G09G 3/36 (2006.01)</b>   | G09G 3/36 | 2 H 1 9 2   |

| <b>G09G 3/20 (2006.01)</b>   | G09G 3/20 | 6 1 1 C     |

| <b>G02F 1/133 (2006.01)</b>  | G09G 3/20 | 6 1 1 A     |

| <b>G02F 1/1368 (2006.01)</b> | G09G 3/20 | 5 C 0 0 6   |

|                              | G09G 3/20 | 6 2 3 A     |

|                              | G09G 3/20 | 5 C 0 8 0   |

|                              | G09G 3/20 | 6 2 3 V     |

審査請求 未請求 請求項の数 6 O L (全 21 頁) 最終頁に続く

|           |                              |          |                                                                                |

|-----------|------------------------------|----------|--------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2014-254927 (P2014-254927) | (71) 出願人 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号                                     |

| (22) 出願日  | 平成26年12月17日 (2014.12.17)     | (74) 代理人 | 100088672<br>弁理士 吉竹 英俊                                                         |

|           |                              | (74) 代理人 | 100088845<br>弁理士 有田 貴弘                                                         |

|           |                              | (72) 発明者 | 南 昭宏<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内                                            |

|           |                              |          | F ターム (参考) 2H192 AA24 CC24 CC62<br>2H193 ZA04 ZA08 ZF12 ZF16 ZF32<br>ZF33 ZF34 |

最終頁に続く

(54) 【発明の名称】 液晶表示装置および半導体装置

## (57) 【要約】

【課題】画像信号をタイミングコントローラから画像信号線駆動回路に伝送するための伝送線路において、消費電力および電磁波として放射されるノイズの発生を抑制した液晶表示装置を提供する。

【解決手段】水平方向に配列された複数の画素について、画像信号を少なくとも画素1つ置きで与えて駆動する画像信号線駆動回路と、それを制御するタイミングコントローラとを有した液晶表示装置であって、タイミングコントローラは、画像信号を少なくとも画素1つ置きで与える方に合わせて、1水平ライン分の画像信号を、画像信号線駆動回路に与える順に分割する分割回路と、前後の関係にある画像信号を比較する比較回路と、比較回路での比較結果を受け、前後の関係にある画像信号が一致する場合は、後の画像信号を画像信号線駆動回路に与えることを停止する比較結果反映回路とを備えている。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

マトリクス状に配置された複数の画素と、

前記複数の画素を水平方向および垂直方向にそれぞれ駆動する画像信号線および走査線と、を有したマトリクス表示部と、

前記画像信号線に画像信号を与える画像信号線駆動回路と、

前記走査線に走査信号を与える走査線駆動回路と、

前記画像信号線駆動回路に前記画像信号を与えると共に、前記画像信号線駆動回路を制御するタイミングコントローラと、を有した液晶表示装置であって、

前記画像信号線駆動回路は、

水平方向に配列された前記複数の画素について、前記画像信号を少なくとも画素1つ置きで与えて駆動し、

前記タイミングコントローラは、

前記画像信号を少なくとも画素1つ置きで与える方式に合わせて、1水平ライン分の画像信号を、前記画像信号線駆動回路に与える順に分割する分割回路と、

前記分割回路で分割された前記1水平ライン分の画像信号を受け、前後の関係にある画像信号を比較する比較回路と、

前記後の画像信号を前記画像信号線駆動回路に与える際に、前記比較回路での比較結果を受け、前記前後の関係にある画像信号が一致する場合は、前記後の画像信号を前記画像信号線駆動回路に与えることを停止する比較結果反映回路と、を備え、

前記画像信号線駆動回路は、先の画像信号を前記マトリクス表示部に出力した後、前記後の画像信号が前記タイミングコントローラから与えられない場合は、先の画像信号を前記後の画像信号の代わりに前記マトリクス表示部に出力する、液晶表示装置。

**【請求項 2】**

前記画像信号線駆動回路は、

前記タイミングコントローラから、前記先の画像信号の始まりのタイミングを示すスタートパルスおよび前記後の画像信号の始まりのタイミングを示すスタートパルスを受けることで、前記先の画像信号および前記後の画像信号の取り込みを始め、

前記タイミングコントローラは、

前記前後の関係にある画像信号が一致する場合は、後の画像信号を前記画像信号線駆動回路に与えることを停止すると共に、前記後の画像信号の始まりのタイミングを示す前記スタートパルスを出力せず、前記画像信号線駆動回路は、前記先の画像信号を保持し続ける、請求項1記載の液晶表示装置。

**【請求項 3】**

マトリクス状に配置された複数の画素と、

前記複数の画素を水平方向および垂直方向にそれぞれ駆動する画像信号線および走査線と、を有したマトリクス表示部と、

前記画像信号線に画像信号を与える画像信号線駆動回路と、

前記走査線に走査信号を与える走査線駆動回路と、

前記画像信号線駆動回路に前記画像信号を与えると共に、前記画像信号線駆動回路を制御するタイミングコントローラと、を有した液晶表示装置であって、

前記画像信号線駆動回路は、

水平方向に配列された前記複数の画素について、前記画像信号を少なくとも画素1つで与えて駆動し、

前記タイミングコントローラは、

前記画像信号を少なくとも画素1つ置きで与える方式に合わせて、1水平ライン分の画像信号を、前記画像信号線駆動回路に与える順に分割する分割回路と、

前記分割回路で分割された前記1水平ライン分の画像信号を受け、前後の関係にある画像信号の差分を取った差分データを生成する差分回路と、

前記差分回路から前記差分データを受け、前記差分データの全ビットのうち時間的に隣

10

20

30

40

50

り合うビット間でデータが変化している変化ビットの数をカウントする第1のカウンタと、

前記分割回路から後の画像信号を受け、後の画像信号の全ビットのうち時間的に隣り合うビット間でデータが変化している変化ビットの数をカウントする第2のカウンタと、

前記第1のカウンタでのカウント値と前記第2のカウンタでのカウント値を比較する比較回路と、

前記後の画像信号を前記画像信号線駆動回路に与える際に、

前記比較回路での比較結果を受け、前記差分データおよび前記後の画像信号のうち、カウント値の少ない方を選択して前記画像信号線駆動回路に与える比較結果反映回路と、を備える、液晶表示装置。

10

#### 【請求項4】

前記タイミングコントローラは、

前記差分データおよび前記後の画像信号のうち選択した方を前記画像信号線駆動回路に与えると共に、どちらを送ったかを伝える信号種類判別信号を与える、請求項3記載の液晶表示装置。

#### 【請求項5】

請求項1記載のタイミングコントローラが実装された半導体装置。

#### 【請求項6】

請求項3記載のタイミングコントローラが実装された半導体装置。

20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は液晶表示装置に関し、特に、水平方向1ラインに対して、画像信号線駆動回路および走査線駆動回路を複数回駆動させる方式の液晶表示装置に関する。

##### 【背景技術】

##### 【0002】

液晶表示装置において、画素がマトリクス状に配置されたマトリクス表示部の水平方向に配列されたR、G、Bの画素について、画像信号を、画素1つ置き、もしくはそれ以上の間隔で画素に与えて駆動させるために、水平方向1ラインに対して、画像信号線駆動回路および走査線駆動回路を複数回駆動させる表示方式が提案されている。

30

##### 【0003】

この方式のうち、水平方向1ラインに対して、画像信号線駆動回路および走査線駆動回路を2回駆動させる表示方式は、デュアル(Dual)ゲート方式と呼称されており、例えば特許文献1にその一例が開示されている。

##### 【0004】

デュアルゲート方式では、画像信号線(ソース線)の本数が通常方式の半分で済むため画像信号線駆動回路の出力ノードの本数も半分で済み、液晶表示装置の製造コストを低減する効果が高い。

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

【特許文献1】特開平10-73843号公報公報

40

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0006】

特許文献1に開示されるようなデュアルゲート方式の液晶表示装置に限らず、従来の液晶表示装置では、R、G、Bの画像信号をタイミングコントローラから画像信号線駆動回路に伝送するための伝送線路においては、画像信号データの伝送量が多いため、消費電力および電磁波として放射されるノイズが多いという問題があった。

##### 【0007】

50

本発明は上記のような問題を解決するためになされたものであり、画像信号をタイミングコントローラから画像信号線駆動回路に伝送するための伝送線路において、消費電力および電磁波として放射されるノイズの発生を抑制した液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明に係る液晶表示装置の態様は、マトリクス状に配置された複数の画素と、前記複数の画素を水平方向および垂直方向にそれぞれ駆動する画像信号線および走査線と、を有したマトリクス表示部と、前記画像信号線に画像信号を与える画像信号線駆動回路と、前記走査線に走査信号を与える走査線駆動回路と、前記画像信号線駆動回路に前記画像信号を与えると共に、前記画像信号線駆動回路を制御するタイミングコントローラと、を有した液晶表示装置であって、前記画像信号線駆動回路は、水平方向に配列された前記複数の画素について、前記画像信号を少なくとも画素1つ置きで与えて駆動し、前記タイミングコントローラは、前記画像信号を少なくとも画素1つ置きで与える方式に合わせて、1水平ライン分の画像信号を、前記画像信号線駆動回路に与える順に分割する分割回路と、前記分割回路で分割された前記1水平ライン分の画像信号を受け、前後の関係にある画像信号を比較する比較回路と、前記後の画像信号を前記画像信号線駆動回路に与える際に、前記比較回路での比較結果を受け、前記前後の関係にある画像信号が一致する場合は、前記後の画像信号を前記画像信号線駆動回路に与えることを停止する比較結果反映回路と、を備え、前記画像信号線駆動回路は、先の画像信号を前記マトリクス表示部に出力した後、前記後の画像信号が前記タイミングコントローラから与えられない場合は、先の画像信号を前記後の画像信号の代わりに前記マトリクス表示部に出力する。

10

20

20

【発明の効果】

【0009】

本発明に係る液晶表示装置によれば、画像信号線駆動回路に伝送するデータのHigh/Lowの繰り返しを抑制し、消費電力および電磁波として放射されるノイズの発生を抑制することができる。

【図面の簡単な説明】

【0010】

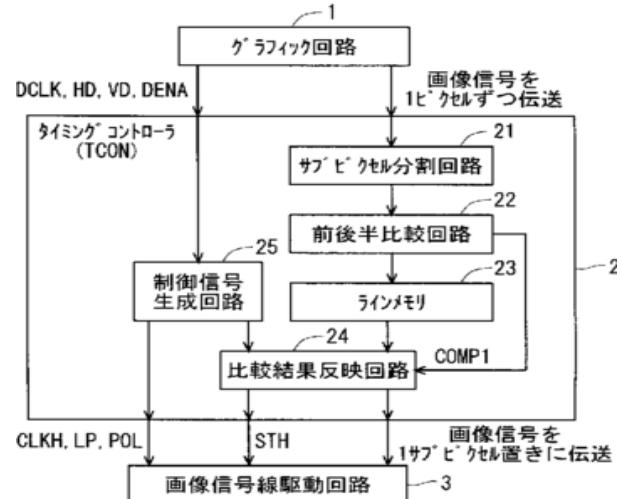

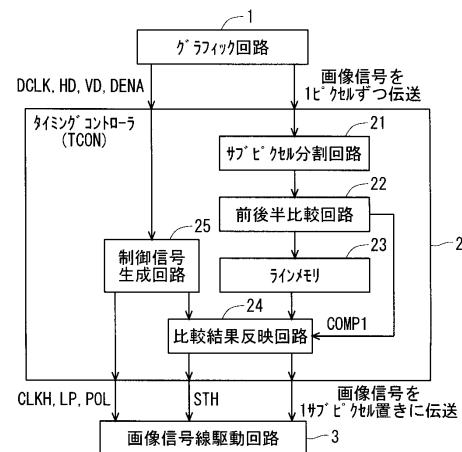

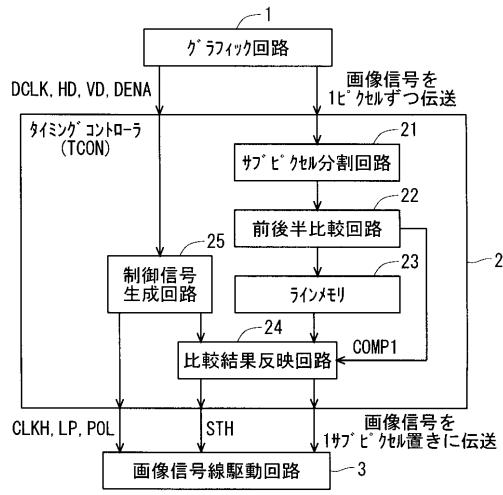

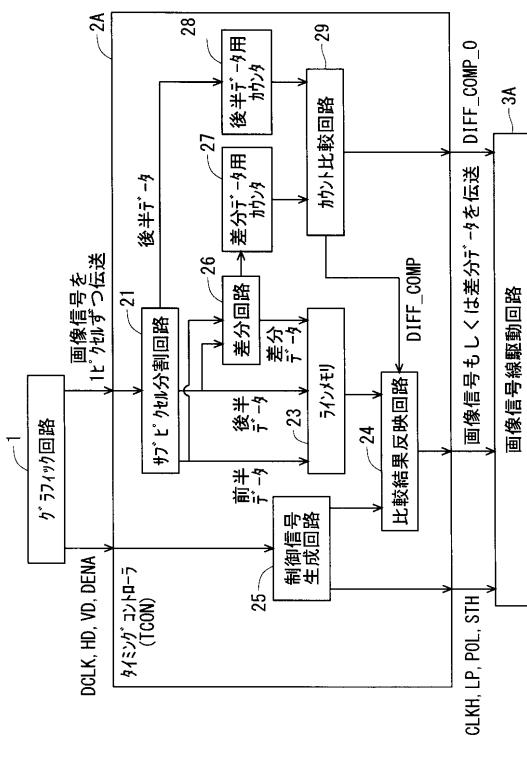

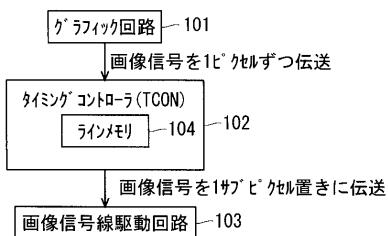

【図1】本発明に係る実施の形態1の液晶表示装置が有するタイミングコントローラの構成を示すブロック図である。

30

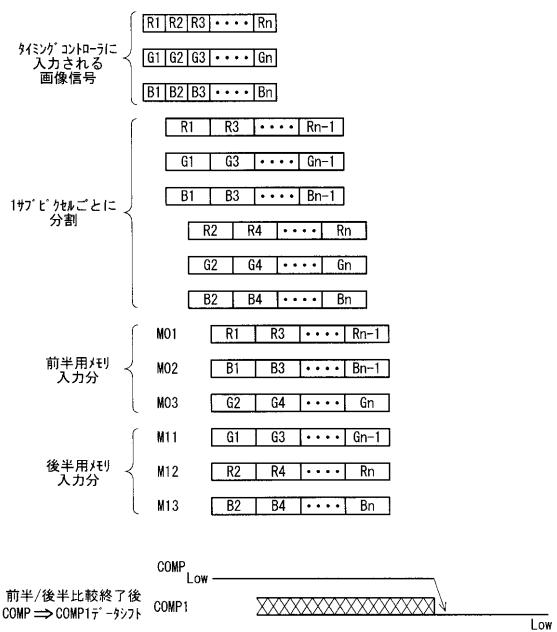

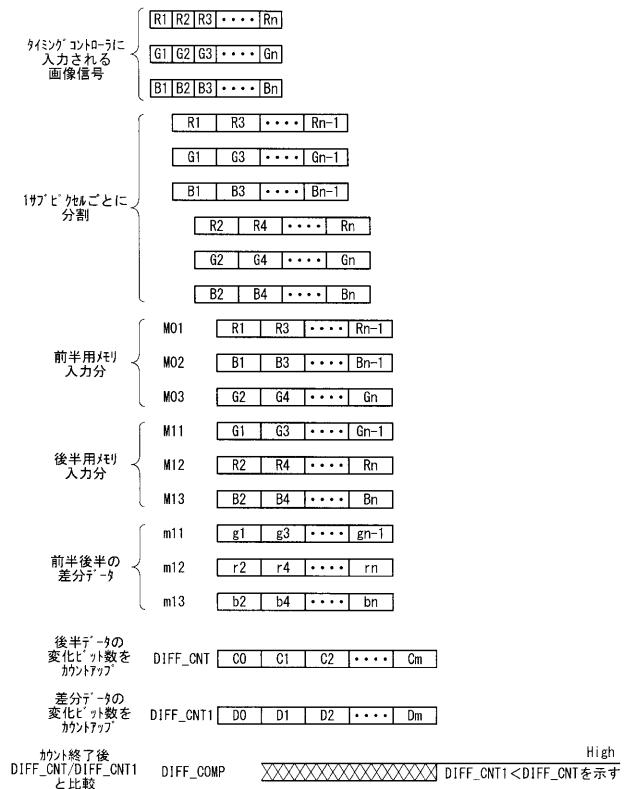

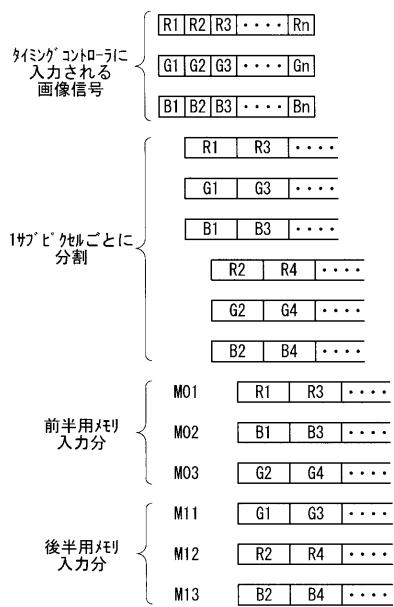

【図2】本発明に係る実施の形態1の液晶表示装置が有するタイミングコントローラにおいて、画像信号がタイミングコントローラ内のラインメモリに入力するまでの信号の流れを示すタイミングチャートである。

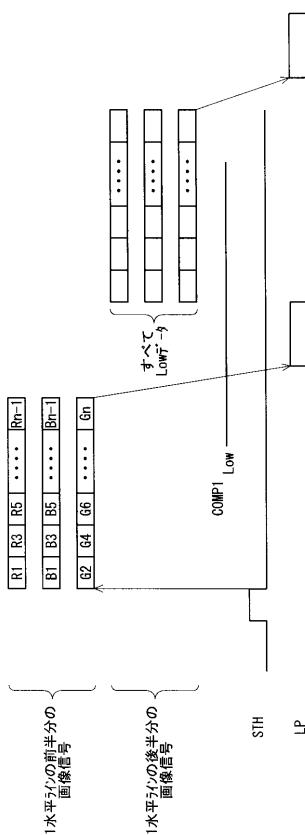

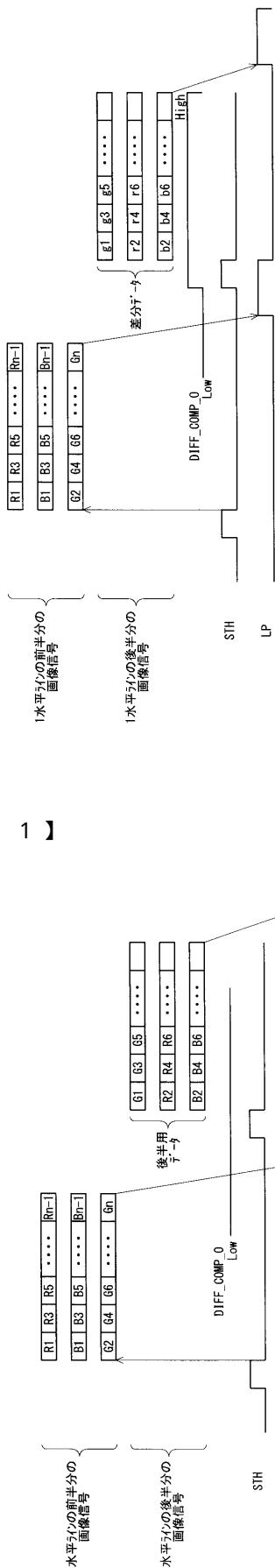

【図3】比較結果反映回路の動作を示すタイミングチャートである。

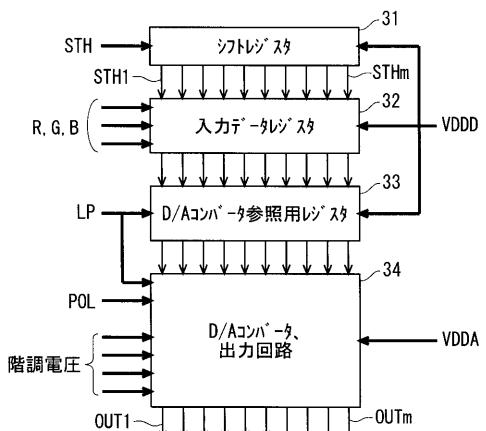

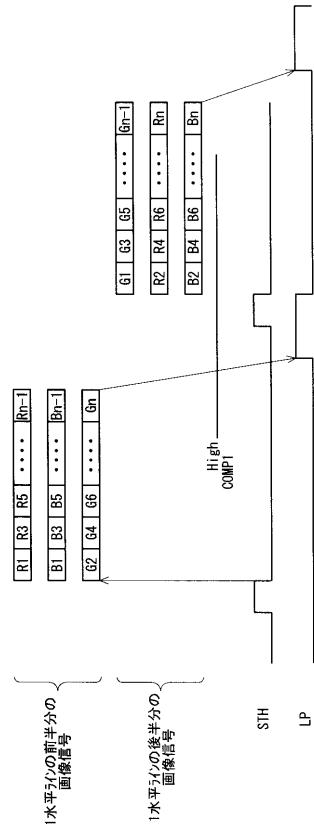

【図4】画像信号線駆動回路の構成を示すブロック図である。

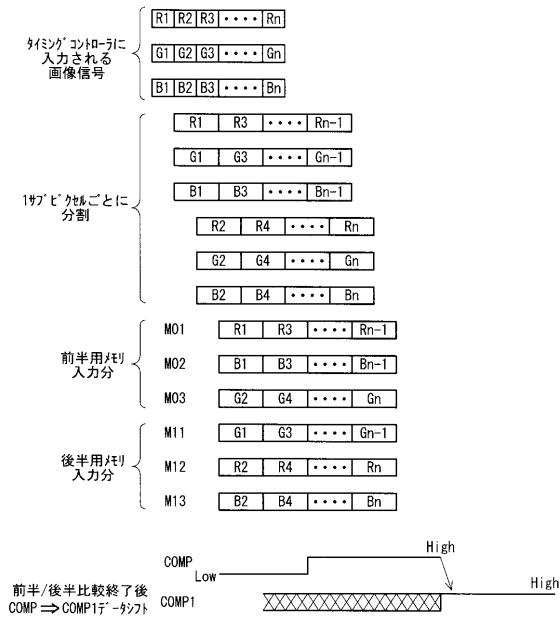

【図5】本発明に係る実施の形態1の液晶表示装置が有するタイミングコントローラにおいて、画像信号がタイミングコントローラ内のラインメモリに入力するまでの信号の流れを示すタイミングチャートである。

40

【図6】比較結果反映回路の動作を示すタイミングチャートである。

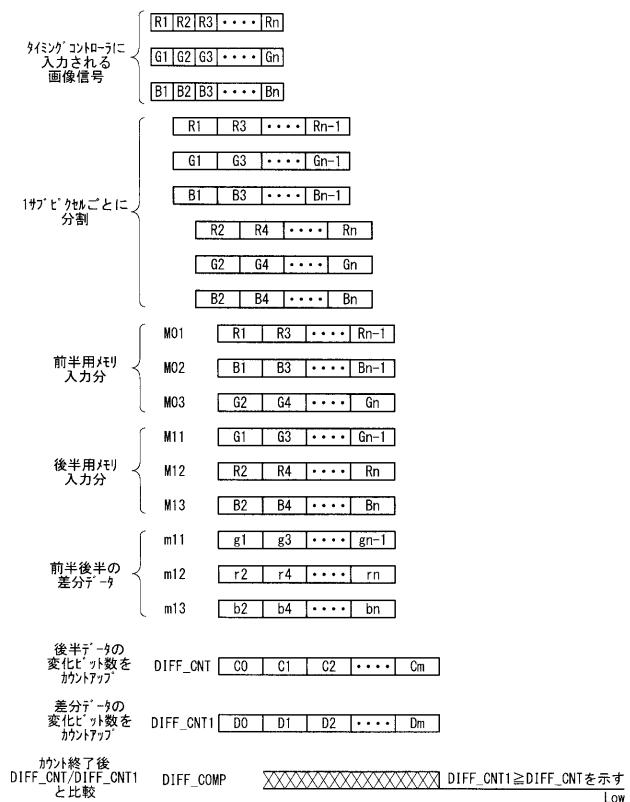

【図7】本発明に係る実施の形態2の液晶表示装置が有するタイミングコントローラの構成を示すブロック図である。

【図8】本発明に係る実施の形態2の液晶表示装置が有するタイミングコントローラにおいて、画像信号がタイミングコントローラ内のラインメモリに入力するまでの信号の流れを示すタイミングチャートである。

【図9】比較結果反映回路の動作を示すタイミングチャートである。

【図10】本発明に係る実施の形態2の液晶表示装置が有するタイミングコントローラにおいて、画像信号がタイミングコントローラ内のラインメモリに入力するまでの信号の流れを示すタイミングチャートである。

【図11】比較結果反映回路の動作を示すタイミングチャートである。

50

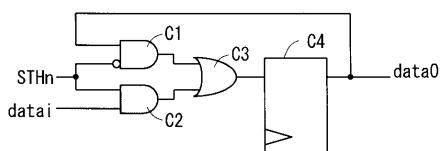

【図12】画像信号線駆動回路が備える入力データレジスタを構成する一般的な単位入力データレジスタを示す論理回路図である。

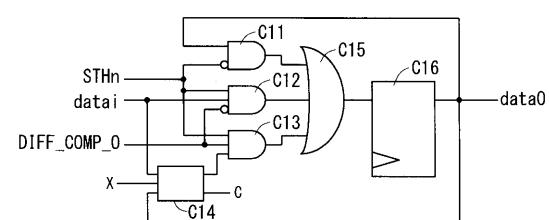

【図13】本発明に係る実施の形態2の液晶表示装置が有する画像信号線駆動回路の入力データレジスタを構成する単位入力データレジスタを示す論理回路図である。

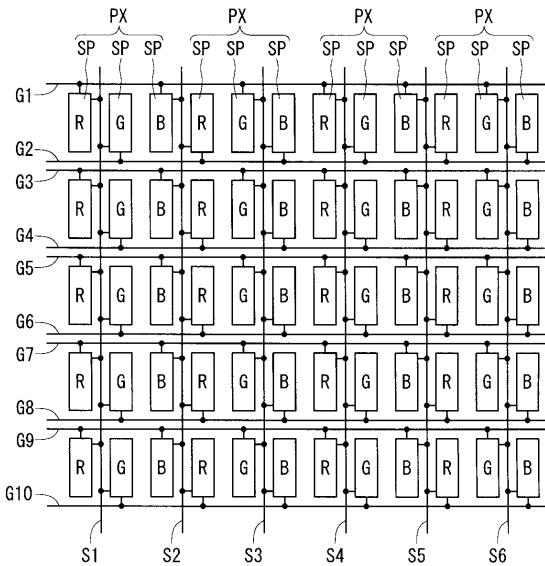

【図14】デュアルゲート方式の液晶表示装置におけるマトリクス表示部の概略構成を示す平面図である。

【図15】タイミングコントローラの構成を示すブロック図である。

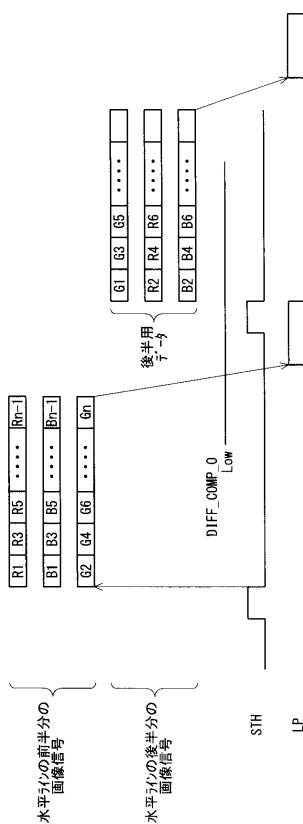

【図16】画像信号がタイミングコントローラ内のラインメモリに入力されるまでの信号の流れを示すタイミングチャートである。

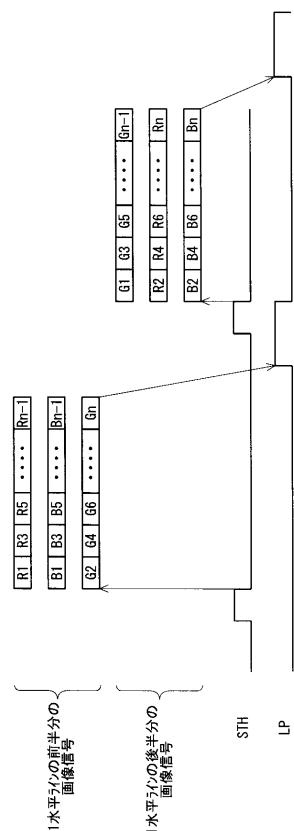

【図17】タイミングコントローラから出力される画像信号と制御信号を示すタイミングチャートである。 10

#### 【発明を実施するための形態】

##### 【0011】

<はじめに>

発明の実施の形態の説明に先立ってデュアルゲート方式の液晶表示装置の基本的な動作について図14～図17を用いて説明する。

##### 【0012】

図14は、デュアルゲート方式の液晶表示装置におけるマトリクス表示部の概略構成を示す平面図である。なお、図14においては、画像信号線（ソース線）および走査線（ゲート線）と画素との接続関係のみを記載し、その他の図示は省略している。また、本願においては、R、G、Bの画素の1つ1つをサブピクセルと呼称し、R、G、Bの3つのサブピクセルの組み合わせをピクセルと呼称する。 20

##### 【0013】

図14に示すように、デュアルゲート方式のマトリクス表示部は、マトリクス状に配置されたR、G、BのサブピクセルSPのうち、水平方向に配列されたサブピクセルSPにおいては、一本のゲート線にはサブピクセルが1つ置きに接続されている。

##### 【0014】

例えば、ゲート線G<sub>1</sub>には、水平方向にR、G、Bの順で繰り返して配列されたサブピクセルSPが、R、B、Gの繰り返しとなるように接続されており、ゲート線G<sub>2</sub>には、G、R、Bの繰り返しとなるように接続され、以下のゲート線で同じ繰り返しとなるように接続されている。 30

##### 【0015】

また、水平方向に配列されたサブピクセルSPのうち、隣り合うサブピクセルSPが一本のソース線に接続されている。

##### 【0016】

例えば、ソース線S<sub>1</sub>には、RとGのサブピクセルSPが接続され、ソース線S<sub>2</sub>には、BとRのサブピクセルSPが接続され、ソース線S<sub>3</sub>には、GとBのサブピクセルSPが接続され、以下のソース線で同じ繰り返しとなるように接続されている。

##### 【0017】

上述したデュアルゲート方式のマトリクス表示部において、サブピクセルSPの配列を垂直方向に駆動する走査信号は走査線駆動回路（図示せず）から走査線に与えられ、サブピクセルSPの配列を水平方向に駆動する画像信号は、画像信号線駆動回路（図示せず）から画像信号線に与えられる。 40

##### 【0018】

ここで、図15を用いて、画像信号線駆動回路に画像信号を与えると共に、画像信号線駆動回路を制御するタイミングコントローラの構成について説明する。図15に示すように、画像信号を生成するグラフィック回路101から、タイミングコントローラ（TCO N）102に対してR、G、Bの画像信号が1ピクセルずつ順次に与えられる。

##### 【0019】

タイミングコントローラ102では、デュアルゲート方式のマトリクス表示部に対応す 50

るため、水平方向に R、G、B の順に並んだサブピクセルに対して、1 サブピクセル置きとなるように画像信号を並べ変えて画像信号線駆動回路 103 に出力する。

#### 【0020】

このように、タイミングコントローラ 102 では、グラフィック回路 101 から入力される画像信号と、画像信号線駆動回路 103 に出力する画像信号とで画像信号の順序が違うので、内部にラインメモリ 104 を備え、画像信号の並べ替えを行うことで、画像信号線駆動回路 103 の要求するサブピクセルの配列に従った画像信号の伝送を実現する。

#### 【0021】

図 16 には、R、G、B の画像信号をタイミングコントローラ 102 に入力し、タイミングコントローラ 102 内のラインメモリ 104 に入力するまでの信号の流れをタイミングチャートで示している。10

#### 【0022】

図 16 に示すように、タイミングコントローラ 102 に入力される R、G、B の画像信号は、例えば、R1、G1、B1 のように 1 ピクセル分のサブピクセルの画像信号が同時に入力され、次のタイミングでは R2、G2、B2 のサブピクセルの画像信号が入力される。

#### 【0023】

タイミングコントローラ 102 では、入力された画像信号を 1 サブピクセルごとに分割し、次のピクセルの画像信号が入力されるタイミングでラインメモリ 104 に与える。

#### 【0024】

例えば、R1、G1、B1 の画像信号は、R2、G2、B2 の画像信号がタイミングコントローラ 102 に入力されるタイミングで 1 サブピクセルごとに分割され、R2、G2、B2 の画像信号は、R3、G3、B3 の画像信号がタイミングコントローラ 102 に入力されるタイミングで 1 サブピクセルごとに分割される。そして、1 水平ライン分の画像信号のうち、先に駆動するゲート線（他追えばゲート線 G<sub>1</sub>）に接続されるサブピクセルに与えられる画像信号（1 水平ラインの前半分の画像信号と呼称）と、次に駆動するゲート線（ゲート線 G<sub>2</sub>）に接続されるサブピクセルに与えられる画像信号（1 水平ラインの後半分の画像信号と呼称）に分けられる。20

#### 【0025】

ラインメモリ 104 は、1 水平ラインの前半分の画像信号を格納する前半用メモリと、1 水平ラインの後半分の画像信号を格納する後半用メモリとを有し、それぞれ R、G、B の 3 色分のデータを格納できる構成となっている。30

#### 【0026】

図 16 に示すように、前半用メモリには、例えば、R1、B1、G2 の画像信号が格納され、後半用メモリには、例えば、G1、R1、B2 の画像信号が格納される。この格納の仕方は、図 14 を用いて説明したように、例えばゲート線 G<sub>1</sub> には、R、B、G の繰り返しとなるようにサブピクセルが接続され、例えばゲート線 G<sub>2</sub> には G、R、B の繰り返しとなるようにサブピクセルが接続されている構成に対応したものである。

#### 【0027】

タイミングコントローラ 102 は、このような格納の仕方で画像信号が格納されたラインメモリ 104 から、画像信号を読み出して画像信号線駆動回路 103 に伝送する。40

#### 【0028】

図 17 は、タイミングコントローラ 102 から出力される画像信号と、画像信号の水平方向の始まりのタイミングを画像信号線駆動回路 103 に示すスタートパルス (STH) および画像信号を画像信号線駆動回路 103 からマトリクス表示部に出力させるタイミングを示すラッチパルス (LP) を示すタイミングチャートである。

#### 【0029】

図 17 に示すように、画像信号線駆動回路 103 は、最初のスタートパルスの立ち下がりのタイミングで R1、B1、G2 などの 1 水平ラインの前半分の画像信号を取り込み始め、前半分の画像信号を全て取り込むと、ラッチパルスの立ち上がりのタイミングで 1 水50

平ラインの前半分の画像信号の出力を始める。

**【0030】**

同様に、画像信号線駆動回路103は、次のスタートパルスの立ち下がりのタイミングでG1、R2、B2などの1水平ラインの後半分の画像信号を取り込み始め、後半分の画像信号を全て取り込むと、ラッチパルスの立ち上がりのタイミングで1水平ラインの後半分の画像信号の出力を始める。

**【0031】**

<実施の形態1>

以下、図1～図6を用いて、本発明に係る実施の形態1の液晶表示装置について説明する。

10

**【0032】**

<装置構成>

図1は、実施の形態1の液晶表示装置が有するタイミングコントローラの構成を示すブロック図である。

**【0033】**

図1に示すように、グラフィック回路1は、タイミングコントローラ(TCON)2に対してR、G、Bの画像信号を1ピクセルずつ順次に伝送すると共に、ドットクロック(DCLK)、水平同期信号(HD)、垂直同期信号(VD)およびデータイネーブル信号(DENA)を与える。

20

**【0034】**

タイミングコントローラ2は、デュアルゲート方式のマトリクス表示部に対応するため、水平方向にR、G、Bの順に並んだサブピクセルに対して、1サブピクセル置きとなるように画像信号を並べ変えて画像信号線駆動回路3に出力すると共に、基準クロック(CLKH)、液晶駆動の極性を反転するための極性反転信号(POL)、ラッチパルス(LP)およびスタートパルス(STH)を出力する。

**【0035】**

タイミングコントローラ2は、グラフィック回路1から1ピクセルずつ入力された画像信号を1サブピクセルごとに分割する、サブピクセル分割回路21を有し、サブピクセル分割回路21で1サブピクセルごとに分割された画像信号は、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とに分けられる。

30

**【0036】**

1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号は、両画像信号を比較する前後半比較回路22(比較回路)に与えられる。

**【0037】**

前後半比較回路22は、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とを比較した後は、両画像信号を順次ラインメモリ23に出力すると共に、比較結果を比較結果報告信号COMP1として、ラインメモリ23の出力を受ける比較結果反映回路24に与える。

**【0038】**

比較結果反映回路24は、1水平ラインの後半分の画像信号を画像信号線駆動回路3に出力する際に、前後半比較回路22での比較結果が、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号と同じであるとの結果を示す場合は、1水平ラインの後半分の画像信号をすべてLOWデータに固定して出力する機能を有している。なお、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とが同じでない場合は、ラインメモリ23から与えられた1水平ラインの後半分の画像信号を、加工せずに画像信号線駆動回路3に出力する。

40

**【0039】**

また、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とが同じである場合は、画像信号線駆動回路3内に残っている1水平ラインの前半分の画像信号を再利用するので、比較結果反映回路24は、1水平ラインの後半分の画像信号に同期するS

50

T H は出力しない。

【0040】

また、タイミングコントローラ2内には、グラフィック回路1から与えられるドットクロック(DCLK)、水平同期信号(HD)、垂直同期信号(VD)およびデータイネーブル信号(ENA)に基づいて、基準クロック(CLKH)、ラッチパルス(LP)、極性反転信号(POL)およびスタートパルス(STH)などの画像信号線駆動回路3を制御する制御信号を生成する制御信号生成回路25を有している。

【0041】

なお、制御信号生成回路25で生成されたCLKH、LPおよびPOLは、直接、画像信号線駆動回路3に与えられるが、STHは、比較結果反映回路24を介して与えられる構成となっている。なお、図1においては、制御信号は本発明の実施に必要な構成や信号のみを開示しており、本発明との関係が薄い構成や制御信号などは省略している。

10

【0042】

<動作>

次に、上述したタイミングコントローラ2の動作について、図2～図6を用いて説明する。

【0043】

図2は、R、G、Bの画像信号をタイミングコントローラ2に入力し、タイミングコントローラ2内のラインメモリ23に入力するまでの信号の流れを示すタイミングチャートであり、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とでデータが一致する場合を示している。

20

【0044】

図2に示すように、タイミングコントローラ2に入力されるR、G、Bの画像信号は、例えば、R1、G1、B1のように1ピクセル分のサブピクセルの画像信号が同時に投入され、次のタイミングではR2、G2、B2のサブピクセルの画像信号が投入される。

【0045】

タイミングコントローラ2では、投入された画像信号をサブピクセル分割回路21で1サブピクセルごとに分割し、次のピクセルの画像信号が投入されるタイミングで前後半比較回路22に与える。

30

【0046】

図2に示されるように、R1、G1、B1の画像信号は、R2、G2、B2の画像信号がタイミングコントローラ2に入力されるタイミングでサブピクセル分割回路21から出力され、R2、G2、B2の画像信号は、R3、G3、B3の画像信号がタイミングコントローラ2に入力されるタイミングでサブピクセル分割回路21から出力されてそれぞれ前後半比較回路22に与えられる。

【0047】

ラインメモリ23は、1水平ラインの前半分の画像信号を格納する前半用メモリと、1水平ラインの後半分の画像信号を格納する後半用メモリとを有し、それぞれR、G、Bの3色分のデータを格納できる構成となっている。

40

【0048】

図2には、ラインメモリ23の前半用メモリに、例えば、R1、B1、G2の画像信号が格納され、後半用メモリには、例えば、G1、R1、B2の画像信号が格納されることが示されている。この格納の仕方は、図14を用いて説明したように、例えばゲート線G<sub>1</sub>には、R、B、Gの繰り返しとなるようにサブピクセルが接続され、例えばゲート線G<sub>2</sub>にはG、R、Bの繰り返しとなるようにサブピクセルが接続されている構成に対応したものである。

【0049】

なお、R(赤色)用の前半用メモリには、R1、R3のように奇数番のRのデータが格納され、図2においてはこれらをデータ群M01としている。同様に、B(青色)用の前半用メモリには、B1、B3のように奇数番のBのデータが格納され、これらをデータ群

50

M02とし、G(緑色)用の前半用メモリには、G2、G4のように偶数番のGのデータが格納され、これらをデータ群M03としている。

#### 【0050】

また、G用の後半用メモリには、G1、G3のように奇数番のGのデータが格納され、図2においてはこれらをデータ群M11としている。同様に、R用の後半用メモリには、R2、R4のように偶数番のRのデータが格納され、これらをデータ群M12とし、B用の後半用メモリには、B2、B4のように偶数番のBのデータが格納され、これらをデータ群M13としている。なお、上記におけるRのデータ、GのデータおよびBのデータのそれぞれは、例えば8ビットのデジタルデータであり、Rのデータは(R[7]～R[0])、Gのデータは(G[7]～G[0])、Bのデータは(B[7]～B[0])の8ビットのデータを含んでいる。10

#### 【0051】

前後半比較回路22では、上記のようにサブピクセル分割回路21から出力された1サブピクセルごとに分割された画像信号を受け、それらを上述したラインメモリ23での格納形式に合わせて、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とに並べ変えて両者の比較を行う。この場合、上述した8ビットのデジタルデータを1ビット単位で比較することになる。

#### 【0052】

ここで、前後半比較回路22では、1水平ラインの前半分の画像信号と、1水平ラインの後半分の画像信号との比較結果を比較結果信号COMPで示すが、その定常値はLOW信号である。20

#### 【0053】

そして、画像信号の比較中に1ビットでも異なるデータがあれば、その時点で比較結果信号COMPをHIGH信号とし、比較が終了するまでHIGH信号を維持し続ける。一方、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号が全く同じであればLOW信号を維持する。

#### 【0054】

図2においては、前後半比較回路22での比較結果が、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とで同じであった場合を示しており、比較結果信号COMPはLOW信号を維持しており、前後半比較回路22からは比較結果報告信号COMP1として、比較結果信号COMPの値(Low)が出力されることを示している。30

#### 【0055】

図3は、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とでデータが一致する場合の、比較結果反映回路24の動作を示すタイミングチャートであり、タイミングコントローラ2の出力として画像信号線駆動回路3に入力される画像信号および制御信号を示している。

#### 【0056】

図3に示されるように、比較結果反映回路24では、1水平ラインの後半分の画像信号を出力する前に、比較結果報告信号COMP1の信号状態を確認し、比較結果報告信号COMP1がLOW信号である場合は、1水平ラインの後半分の画像信号を全てLOWデータとし、タイミングコントローラ2から画像信号線駆動回路3に画像信号が伝送されることを停止すると共に、1水平ラインの後半分の画像信号の始まりのタイミングを示すSTHも出力しない。40

#### 【0057】

画像信号線駆動回路3では、1水平ラインの後半分の画像信号の取り込みタイミングになつても1水平ラインの後半分の画像信号を受けることができず、また、1水平ラインの後半分の画像信号の始まりのタイミングを示すSTHも受けることができない。

#### 【0058】

ここで、画像信号線駆動回路3は、STHでデータの取り込みを始め、LPでマトリクス表示部に出力するので、次のSTHが来ない限り、画像信号線駆動回路3内のレジスタ

のデータは更新されない。そのため、画像信号線駆動回路3内のレジスタには、1水平ラインの前半分の画像信号のデータが蓄積されたままにできる。

【0059】

ただし、図3に示されるように、STH以外の制御信号は出力されるので、画像信号線駆動回路3内のレジスタに蓄積されている1水平ラインの前半分の画像信号のデータ各ピクセルに書き込まれることになる。

【0060】

図4は、OUT1～OUTmで示したm本の駆動出力を持つ画像信号線駆動回路3の構成を示すブロック図である。図4に示すように画像信号線駆動回路3は、STHを受けて、R、G、Bのデータの取り込みタイミングを示すラッチパルスSTH1～STHmを入力データレジスタ32に出力するシフトレジスタ31と、ラッチパルスSTH1～STHmを入力して、R、G、Bのデータを受ける入力データレジスタ32と、LPを受けるD/Aコンバータ参照用レジスタ33と、D/Aコンバータおよび出力回路を有し、LPおよびPOLと階調電圧を受けるD/A変換部34とを備えている。なお、シフトレジスタ31、入力データレジスタ32およびD/Aコンバータ参照用レジスタ33、制御回路電源VDDDから電力が供給され、D/A変換部34は出力回路電源VDDAから電力が供給される。

10

【0061】

入力データレジスタ32は、シフトレジスタ31からのラッチパルスSTH1～STHmを入力して、R、G、Bのデータの取り込みを行い、取り込んだデータはD/Aコンバータ参照用レジスタ33に与えられる。D/Aコンバータ参照用レジスタ33は、LPが与えられることでR、G、BのデータをD/A変換部34に出力し、D/A変換部34ではLPが与えられることでD/Aコンバータでデジタル-アナログ変換を行う。アナログ変換され、階調電圧によって階調を有することとなったアナログ信号は出力OUT1～OUTmに対応した出力回路を介してマトリクス表示部に与えられる。

20

【0062】

図5は、R、G、Bの画像信号をタイミングコントローラ2に入力し、タイミングコントローラ2内のラインメモリ23に入力するまでの信号の流れを示すタイミングチャートであり、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とでデータが一致しない合を示している。

30

【0063】

図5に示すように、タイミングコントローラ2に入力されるR、G、Bの画像信号は、例えば、R1、G1、B1のように1ピクセル分のサブピクセルの画像信号が同時に入力され、次のタイミングではR2、G2、B2のサブピクセルの画像信号が入力される。

【0064】

タイミングコントローラ2では、入力された画像信号をサブピクセル分割回路21で1サブピクセルごとに分割し、次のピクセルの画像信号が入力されるタイミングで前後半比較回路22に与える。

【0065】

図5に示されるように、R1、G1、B1の画像信号は、R2、G2、B2の画像信号がタイミングコントローラ2に入力されるタイミングでサブピクセル分割回路21から出力され、R2、G2、B2の画像信号は、R3、G3、B3の画像信号がタイミングコントローラ2に入力されるタイミングでサブピクセル分割回路21から出力されてそれぞれ前後半比較回路22に与えられる。

40

【0066】

図5には、ラインメモリ23の前半用メモリに、例えば、R1、B1、G2の画像信号が格納され、後半用メモリには、例えば、G1、R1、B2の画像信号が格納されることが示されている。

【0067】

前後半比較回路22では、1水平ラインの前半分の画像信号と、1水平ラインの後半分

50

の画像信号との比較結果を比較結果信号 C O M P で示すが、その定常値は L o w 信号である。

#### 【 0 0 6 8 】

図 5においては、前後半比較回路 2 2での比較結果が、1 水平ラインの前半分の画像信号と1 水平ラインの後半分の画像信号とで異なった場合を示しており、比較結果信号 C O M P は L o w 信号から H i g h 信号に変わっている。前後半比較回路 2 2 からは比較終了後に比較結果報告信号 C O M P 1として、比較結果信号 C O M P の値 ( H i g h ) が出力されることを示している。

#### 【 0 0 6 9 】

図 6 は、1 水平ラインの前半分の画像信号と1 水平ラインの後半分の画像信号とでデータが一致しない場合の、比較結果反映回路 2 4 の動作を示すタイミングチャートであり、タイミングコントローラ 2 の出力として画像信号線駆動回路 3 に入力される画像信号および制御信号を示している。

#### 【 0 0 7 0 】

図 6 に示されるように、比較結果反映回路 2 4 では、1 水平ラインの後半分の画像信号を出力する前に、比較結果報告信号 C O M P 1 の信号状態を確認し、比較結果報告信号 C O M P 1 が H i g h 信号である場合は、1 水平ラインの後半分の画像信号がそのまま画像信号線駆動回路 3 に伝送されると共に、1 水平ラインの後半分の画像信号の始まりのタイミングを示す S T H も出力されることを示している。

#### 【 0 0 7 1 】

以上説明したように、本発明に係る実施の形態 1 の液晶表示装置においては、1 水平ラインの前半分の画像信号と1 水平ラインの後半分の画像信号とが一致している場合は、タイミングコントローラ 2 から画像信号線駆動回路 3 に対して、1 水平ラインの後半分の画像信号を伝送しないので、データの H i g h / L o w の繰り返しを抑制し、消費電力および電磁波として放射されるノイズの発生を抑制することができる。

#### 【 0 0 7 2 】

##### < 変形例 >

なお、以上説明した実施の形態 1 では、本発明をデュアルゲート方式の液晶表示装置に適用した構成について説明したが、本発明は、1 水平ラインを 3 分割して駆動させるトリプル (Triple) ゲート方式や、4 分割以上に分割して駆動する方式にも適用可能である。この場合も、先に書き込まれる画像信号と後に書き込まれる画像信号とを比較して、画像信号が一致している場合は後に書き込まれる画像信号を画像信号線駆動回路に伝送しないようにすることで、消費電力および電磁波として放射されるノイズの発生を抑制することができる。

#### 【 0 0 7 3 】

また、説明を簡素化するために、タイミングコントローラ 2 から画像信号線駆動回路 3 に伝送する R G B 信号は、通常のデジタル信号として説明を行ったが、この間の伝送方式については m i n i L V D S ( Low Voltage Differential Signaling ) や R S D S ( reduced swing differential signaling ) などの伝送技術を用いても構わない。なお、R S D S は登録商標である。

#### 【 0 0 7 4 】

また、これらは、タイミングコントローラとして 1 つの半導体デバイスに実装することも可能であるし、タイミングコントローラ自身を画像信号線駆動回路と同じ半導体デバイスに実装することも可能である。

#### 【 0 0 7 5 】

##### < 実施の形態 2 >

次に、図 7 ~ 図 1 3 を用いて、本発明に係る実施の形態 2 の液晶表示装置について説明する。

#### 【 0 0 7 6 】

##### < 装置構成 >

10

20

30

40

50

図7は、実施の形態2の液晶表示装置が有するタイミングコントローラの構成を示すブロック図である。

【0077】

図7に示すように、グラフィック回路1は、タイミングコントローラ2Aに対してR、G、Bの画像信号を1ピクセルずつ順次に伝送すると共に、DCLK、HD、VDおよびDENAを与える。

【0078】

タイミングコントローラ2Aは、デュアルゲート方式のマトリクス表示部に対応するため、水平方向にR、G、Bの順に並んだサブピクセルに対して、1サブピクセル置きとなるように画像信号を並べ変えて画像信号線駆動回路3Aに出力すると共に、CLKH、POL、LP、STHおよび信号種類判別信号DIFFCOMP\_Oを出力する。

10

【0079】

タイミングコントローラ2Aは、グラフィック回路1から1ピクセルずつ入力された画像信号を1サブピクセルごとに分割する、サブピクセル分割回路21を有し、サブピクセル分割回路21で1サブピクセルごとに分割された画像信号は、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号とに分けられて、ラインメモリ23に出力されると共に、両画像信号の差分を取る差分回路26にも与えられる。

【0080】

ラインメモリ23は、1水平ラインの前半分の画像信号（前半データ）を格納する前半用メモリと、1水平ラインの後半分の画像信号（後半データ）を格納する後半用メモリと、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号の差分を取った差分データを格納する差分データ用メモリを有し、それぞれR、G、Bの3色分のデータを格納できる構成となっている。

20

【0081】

また、サブピクセル分割回路21は、1水平ラインの後半分の画像信号を後半データ用カウンタ28（第2のカウンタ）にも与え、後半データ用カウンタ28では、1水平ラインの後半分の画像信号の全ビットの変化ビットの数をカウントする。

【0082】

差分回路26は、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号の差分を取った差分データをラインメモリ23に与えると共に、差分データ用カウンタ27（第1のカウンタ）にも与える。差分データ用カウンタ27では、差分データの全ビットの変化ビットの数をカウントする。

30

【0083】

ここで、変化ビットとは、先に説明したように、R、G、Bの画像信号はそれぞれ8ビットのデータを含んでいる。このデータにおいて時間的に隣り合うビットどうしを比較し、ビット間で0から1に、あるいは1から0に変化しているビットのことを指す。ここで、時間的に隣り合うとは、R1とR2などのような数字の並びで隣り合っていることではなく、R1とR3などのようにデータが与えられる順で隣り合っていることを意味する。なお、比較に際してはビット列の最上位ビットから順に比較しても良いし、最下位ビットから順に比較しても良い。これは差分データの変化ビット数をカウントする場合も同じである。

40

【0084】

例えば、1水平ラインの前半分の画像信号と1水平ラインの後半分の画像信号の差分を取る場合、両者が全く同じであれば差分データは全て0となり、変化ビット数は0となる。

【0085】

差分データ用カウンタ27でのカウント値(DIFF\_CNT1)と後半データ用カウンタ28(DIFF\_CNT)でのカウント値は、カウント比較回路29(比較回路)に与えられる。カウント比較回路29では、両カウント値を比較して比較結果を比較結果信号DIFFCOMPとして、ラインメモリ23の出力を受ける比較結果反映回路24に

50

与えると共に、画像信号線駆動回路 3 A に対して、タイミングコントローラ 2 A からの出力信号が差動データであるか実画像信号であるかを報告する信号種類判別信号 D I F F\_C O M P\_O を出力する。

#### 【0086】

比較結果反映回路 2 4 は、1 水平ラインの後半分の画像信号を画像信号線駆動回路 3 に出力する際に、カウント比較回路 2 9 での比較結果を受け、カウント値の少ない方のデータ群を選択して画像信号線駆動回路 3 に出力する。すなわち、1 水平ラインの後半分の画像信号の方がカウント値が少ない場合には、当該画像信号を実画像信号として出力し、1 水平ラインの前半分の画像信号と 1 水平ラインの後半分の画像信号との差分データの方がカウント値が少ない場合には、当該差分データを出力する。なお、実画像信号または差分データの出力と同期して、信号種類判別信号 D I F F\_C O M P\_O も出力される。10

#### 【0087】

また、タイミングコントローラ 2 A 内には、D C L K、H D、V D および D E N A に基づいて、C L K H、L P、P O L および S T H などの画像信号線駆動回路 3 A を制御する制御信号を生成する制御信号生成回路 2 5 を有している。制御信号生成回路 2 5 で生成された C L K H、L P、P O L および S T H は画像信号線駆動回路 3 A に与えられる。

#### 【0088】

なお、図 7においては、制御信号は本発明の実施に必要な構成や信号のみを開示しており、本発明との関係が薄い構成や制御信号などは省略している。

#### 【0089】

<動作>

次に、上述したタイミングコントローラ 2 A の動作について、図 8～図 11 を用いて説明する。

#### 【0090】

図 8 は、R、G、B の画像信号をタイミングコントローラ 2 A に入力し、タイミングコントローラ 2 A 内のラインメモリ 2 3 に入力するまでの信号の流れを示すタイミングチャートであり、1 水平ラインの後半分の画像信号の変化ビット数と差分データの変化ビット数とを比較した結果、差分データの変化ビット数の方が少なかった場合を示している。

#### 【0091】

図 8 に示すように、タイミングコントローラ 2 に入力される R、G、B の画像信号は、例えば、R 1、G 1、B 1 のように 1 ピクセル分のサブピクセルの画像信号が同時に入力され、次のタイミングでは R 2、G 2、B 2 のサブピクセルの画像信号が入力される。30

#### 【0092】

タイミングコントローラ 2 A では、入力された画像信号をサブピクセル分割回路 2 1 で 1 サブピクセルごとに分割し、次のピクセルの画像信号が入力されるタイミングでラインメモリ 2 3、差分回路 2 6 および後半データ用カウンタ 2 8 に与える。

#### 【0093】

図 8においては、ラインメモリ 2 3 の前半用メモリに入力されるデータ群 M 0 1、M 0 2 および M 0 3、前半用メモリに入力されるデータ群 M 1 1、M 1 2 および M 1 3 に加えて、データ群 M 0 1～M 0 3 とデータ群 M 1 1～M 1 3 とのそれぞれの差分データ群 m 1 1、m 1 2 および m 1 3 を前半と後半の差分データとして示している。40

#### 【0094】

差分データ群 m 1 1 は、g 1、g 3 のように奇数番で表され、差分データ群 m 1 2 は、r 2、r 4 のように偶数番で表され、差分データ群 m 1 3 は、b 2、b 4 のように偶数番で表される。

#### 【0095】

また、図 8においては、後半データ用カウンタ 2 8 での、1 水平ラインの後半分の画像信号の変化ビット数のカウントアップのタイミングを C 0、C 1、C 2 のように表し、差分データ用カウンタ 2 7 での、差分データの変化ビット数のカウントアップのタイミングを D 0、D 1、D 2 のように表している。50

## 【0096】

ここで、カウント比較回路29では、差分データ用カウンタ27でのカウント値DIF\_CNT1と後半データ用カウンタ28でのカウント値DIFF\_CNTとの比較結果を比較結果信号DIFF\_COMPで示すが、DIFF\_CNT1がDIFF\_CNTより小さい場合は、比較結果信号DIFF\_COMPはHigh信号として出力される。

## 【0097】

図8においては、カウント比較回路29での比較結果が、DIFF\_CNT1がDIF\_CNTより小かった場合を示しており、カウント終了後に比較結果信号DIFF\_COMPがHigh信号として出力されることを示している。

## 【0098】

図9は、1水平ラインの後半分の画像信号の変化ビット数と差分データの変化ビット数とを比較した結果、差分データの変化ビット数の方が少なかった場合の、比較結果反映回路24の動作を示すタイミングチャートであり、タイミングコントローラ2Aの出力として画像信号線駆動回路3Aに入力される差分データおよび制御信号を示している。

10

## 【0099】

図9に示されるように、比較結果反映回路24では、1水平ラインの後半分の画像信号を出力する前に、比較結果報告信号DIFF\_COMPの信号状態を確認し、比較結果報告信号DIFF\_COMPがHigh信号である場合は、1水平ラインの後半分の画像信号の代わりに差分データをタイミングコントローラ2Aから画像信号線駆動回路3Aに伝送すると共に、信号種類判別信号DIFF\_COMP\_OをHigh信号として画像信号線駆動回路3Aに与え、1水平ラインの後半分の画像信号の代わりに差分データを送ったことを伝える。

20

## 【0100】

画像信号線駆動回路3Aは、最初のSTHの立ち下がりのタイミングでR1、B1、G2などの1水平ラインの前半分の画像信号を取り込み始め、前半分の画像信号を全て取り込むと、LPの立ち上がりのタイミングで1水平ラインの前半分の画像信号の出力を始める。

30

## 【0101】

また、次のSTHの立ち下がりのタイミングでg1、r2、b2などの差分データを取り込み始め、信号種類判別信号DIFF\_COMP\_OがHigh信号となっている期間に差分データを全て取り込むことができる。そして、LPの立ち上がりのタイミングで、差分データの出力を始める。

## 【0102】

図10は、R、G、Bの画像信号をタイミングコントローラ2Aに入力し、タイミングコントローラ2Aのラインメモリ23に入力するまでの信号の流れを示すタイミングチャートであり、1水平ラインの後半分の画像信号の変化ビット数と差分データの変化ビット数とを比較した結果、差分データの変化ビット数の方が多いか等価であった場合を示しており、カウント終了後に比較結果信号DIFF\_COMPがLow信号として出力されることを示している。

40

## 【0103】

図11は、1水平ラインの後半分の画像信号の変化ビット数と差分データの変化ビット数とを比較した結果、差分データの変化ビット数の方が多いか等価であった場合の、比較結果反映回路24の動作を示すタイミングチャートであり、タイミングコントローラ2Aの出力として画像信号線駆動回路3Aに入力される差分データおよび制御信号を示している。

## 【0104】

図11に示されるように、比較結果反映回路24では、1水平ラインの後半分の画像信号を出力する前に、比較結果報告信号DIFF\_COMPの信号状態を確認し、比較結果報告信号DIFF\_COMPがLow信号である場合は、1水平ラインの後半分の画像信号をタイミングコントローラ2Aから画像信号線駆動回路3Aに伝送すると共に、信号種

50

類判別信号 D I F F \_ C O M P \_ O を L o w 信号として画像信号線駆動回路 3 A に与え、1 水平ラインの後半分の画像信号を送ったことを伝える。

#### 【 0 1 0 5 】

画像信号線駆動回路 3 A は、最初の S T H の立ち下がりのタイミングで R 1、B 1、G 2 などの 1 水平ラインの前半分の画像信号を取り込み、前半分の画像信号を全て取り込むと、L P の立ち上がりのタイミングで 1 水平ラインの前半分の画像信号の出力を始める。

#### 【 0 1 0 6 】

また、次の S T H の立ち下がりのタイミングで G 1、R 2、B 2 などの 1 水平ラインの後半分の画像信号を取り込み、後半分の画像信号を全て取り込むと、L P の立ち上がりのタイミングで、1 水平ラインの後半分の画像信号の出力を始める。

10

#### 【 0 1 0 7 】

図 1 2 は、画像信号線駆動回路 3 が備える入力データレジスタ 3 2 ( 図 4 ) を構成する一般的な単位入力データレジスタの構成を示す論理回路図である。

#### 【 0 1 0 8 】

図 1 2 に示す、入力データレジスタ 3 2 を構成する m 個の入力データレジスタ中の n 番目の単位入力データレジスタは、A N D 回路 C 1 の反転入力部と A N D 回路 C 2 の入力部にシフトレジスタ 3 1 ( 図 4 ) からラッチパルス S T H n が入力され、A N D 回路 C 2 のもう 1 つの入力部には新たなデータ d a t a i が入力される構成となっている。

#### 【 0 1 0 9 】

そして、A N D 回路 C 1 および C 2 の出力は O R 回路 C 3 に入力され、O R 回路 C 3 の出力はクロック同期式のラッチ回路 C 4 に入力され、ラッチ回路 C 4 からラッチされたデータ d a t a O が output される構成となっている。なお、データ d a t a O は A N D 回路 C 1 のもう 1 つの入力部に与えられる。図 1 2 の単位データレジスタは、上記構成になっているので、ラッチパルス S T H n が入力するとラッチ回路 C 4 にラッチされているデータ d a t a O に関わらず A N D 回路 C 1 の出力が L o w となり、同時に d a t a i の入力がそのまま A N D 回路 C 2 から出力されるので、その値が O R 回路 C 3 の出力となり、ラッチ回路 C 4 でラッチされる。S T H n が L o w の場合 ( 非選択時 ) は、A N D 回路 C 2 が L o w となり、A N D 回路 C 1 の出力すなわち d a t a O が O R 回路 C 3 から出力され再ラッチされる。

20

#### 【 0 1 1 0 】

このような構成の単位入力データレジスタを必要数 ( 出力数 × データのビット数 × 色数 ) だけ配列することで、サブピクセルごとに必要とするデジタルデータを入力データレジスタ 3 2 ( 図 4 ) に蓄積しているが、画像信号線駆動回路 3 A では、単位入力データレジスタを図 1 3 に示すような構成とすることで、与えられたデータが、差分データである場合に、前半データに差分データを加えることで、後半データを作成することができる。

30

#### 【 0 1 1 1 】

すなわち、図 1 3 に示す単位入力データレジスタは、A N D 回路 C 1 1 の反転入力部、3 入力 A N D 回路 C 1 2 および C 1 3 の入力部にスタートパルス S T H n が入力され、3 A N D 回路 C 1 2 の 1 つの入力部と全加算器 C 1 4 の入力部には新たなデータ d a t a i が入力される構成となっている。また、3 入力 A N D 回路 C 1 2 の反転入力部と 3 入力 A N D 回路 C 1 3 の入力部には信号種類判別信号 D I F F \_ C O M P \_ O が入力され、全加算器 C 1 4 の出力は 3 入力 A N D 回路 C 1 3 の入力部に与えられる構成となっている。

40

#### 【 0 1 1 2 】

そして、A N D 回路 C 1 1 、3 入力 A N D 回路 C 1 2 および C 1 3 の出力は O R 回路 C 1 5 に入力され、O R 回路 C 1 5 の出力はクロック同期式のラッチ回路 C 1 6 に入力され、ラッチ回路 C 1 6 からラッチされたデータ d a t a O が output される構成となっている。なお、データ d a t a O は A N D 回路 C 1 1 のもう 1 つの入力部および全加算器 C 1 4 の入力部に与えられる。また、全加算器 C 1 4 の残りの 2 つの入力部には前半データに基づいて下位ビットからの桁上げ分のデータ X および上位ビットへの桁上げ分のデータ C が与えられる構成となっており、信号種類判別信号 D I F F \_ C O M P \_ O が H i g h 信号の場

50

合は、データdataにデータXおよびデータCが可算されて、前半データに差分データを加えた後半データが全加算器C14から出力されることとなる。

#### 【0113】

以上説明したように、本発明に係る実施の形態2の液晶表示装置においては、差分データの変化ビット数の方が少なかった場合(DIFF\_CNT < DIFF\_CNTである場合)は、タイミングコントローラ2Aから画像信号線駆動回路3Aに対して、差分データを伝送し、差分データの変化ビット数の方が多いか等価である場合(DIFF\_CNT1 DIFF\_CNT)である場合は、タイミングコントローラ2Aから画像信号線駆動回路3Aに対して、1水平ラインの後半分の画像信号を伝送するので、変化量の少ない方の伝送形態を選択することとなりデータのHigh/Lowの繰り返しを抑制し、消費電力および電磁波として放射されるノイズの発生を抑制することができる。10

#### 【0114】

##### <変形例>

なお、以上説明した実施の形態2では、本発明をデュアルゲート方式の液晶表示装置に適用した構成について説明したが、本発明は、1水平ラインを3分割して駆動させるトリプル(Triple)ゲート方式や、4分割以上に分割して駆動する表示方式にも適用可能である。この場合も、先に書き込まれる画像信号と後に書き込まれる画像信号との差分データの変化ビット数と、1水平ラインの後半分の画像信号の変ビット化数を比較して、変化量の少ない方の伝送形態を選択することにより、消費電力および電磁波として放射されるノイズの発生を抑制することができる。20

#### 【0115】

また、説明を簡素化するために、タイミングコントローラ2Aから画像信号線駆動回路3Aに伝送するRGB信号は、通常のデジタル信号として説明を行ったが、この間の伝送方式についてはminilVDSやRSDSなどの伝送技術を用いても構わない。

#### 【0116】

minilVDSやRSDSなどの特別なマッピングがされる伝送方式を用いる場合は、その伝送順序に応じて、後半データ用カウンタ28での、1水平ラインの後半分の画像信号の変化ビット数のカウントアップおよび差分データ用カウンタ27での、差分データの変化ビット数のカウントアップを行い、それらの比較データから差分データの利用の有無を確定すれば良い。30

#### 【0117】

##### <半導体装置への実装>

実施の形態1および実施の形態2の液晶表示装置においては、それぞれタイミングコントローラ2および2Aを有するものとして説明したが、タイミングコントローラ2および2Aは、どちらも半導体集積回路として半導体装置(半導体チップ)内に実装された構成とすることができます。

#### 【0118】

液晶表示装置の大型化に伴い、画像信号線の本数も増え、それに伴いタイミングコントローラの個数も増えるが、タイミングコントローラを半導体装置内に実装することで、多数のタイミングコントローラを液晶表示装置に組み込む作業が容易となる。40

#### 【0119】

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

#### 【符号の説明】

#### 【0120】

2, 2A タイミングコントローラ、3, 3A 画像信号線駆動回路、21 サブピクセル分割回路、22 前後半比較回路、24 比較結果反映回路、26 差分回路、27 差分データ用カウンタ、28 後半データ用カウンタ、29 カウント比較回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

|              |         |              |

|--------------|---------|--------------|

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|              | G 0 9 G | 3/20 6 4 1 C |

|              | G 0 2 F | 1/133 5 5 0  |

|              | G 0 2 F | 1/1368       |

F ターム(参考) 5C006 AA16 AA22 AF83 BB16 BC11 BF01 BF03 BF04 BF14 BF22

FA32 FA47

5C080 AA10 BB05 CC03 DD12 DD26 EE29 EE30 FF11 FF12 JJ02

JJ03 JJ04 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置和半导体装置                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2016114877A</a>                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2016-06-23 |

| 申请号            | JP2014254927                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2014-12-17 |

| [标]申请(专利权)人(译) | 三菱电机株式会社                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 三菱电机株式会社                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 南昭宏                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 南 昭 宏                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 G02F1/1368                                                                                                                                                                                                                                                                                                                                                 |         |            |

| F1分类号          | G09G3/36 G09G3/20.611.C G09G3/20.611.A G09G3/20.623.A G09G3/20.623.V G09G3/20.641.C G02F1/133.550 G02F1/1368                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H192/AA24 2H192/CC24 2H192/CC62 2H193/ZA04 2H193/ZF12 2H193/ZF16 2H193/ZF32 2H193/ZF33 2H193/ZF34 5C006/AA16 5C006/AA22 5C006/AF83 5C006/BB16 5C006/BC11 5C006/BF01 5C006/BF03 5C006/BF04 5C006/BF14 5C006/BF22 5C006/FA32 5C006/FA47 5C080 /AA10 5C080/BB05 5C080/CC03 5C080/DD12 5C080/DD26 5C080/EE29 5C080/EE30 5C080/FF11 5C080/FF12 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

公开了一种用于从时序控制器向图像信号线驱动电路发送的图像信号，提供一种抑制发射功率消耗和电磁波噪声的发生的液晶显示装置的传输线。多个排列在水平方向上的像素，具有图像信号线驱动电路用于驱动图像信号的液晶显示装置通过至少像素每隔一个，以及用于控制一个定时控制器给定的定时控制器包括分割电路，该分割电路根据至少每隔一个像素给出图像信号的方法，按照将图像信号给予图像信号线驱动电路的顺序分割一条水平线的图像信号，用于比较信号的比较器电路，接收所述比较电路的比较结果，比较结果反映电路停止给的情况下前后的相关匹配的图像信号，图像信号线驱动电路后的图像信号它配备了一扇门。 点域1