### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2012-163696 (P2012-163696A)

(43) 公開日 平成24年8月30日(2012.8.30)

| (51) Int.Cl. |       |           | F 1    |       |        |    | テーマコー    | ド(参考)  |

|--------------|-------|-----------|--------|-------|--------|----|----------|--------|

| G09G         | 3/36  | (2006.01) | GO9G   | 3/36  |        |    | 2H193    |        |

| G02F         | 1/133 | (2006.01) | GO2F   | 1/133 | 550    |    | 5C006    |        |

| G09G         | 3/20  | (2006.01) | GO2F   | 1/133 | 535    |    | 5C080    |        |

|              |       |           | GO9G   | 3/20  | 624C   |    |          |        |

|              |       |           | GO9G   | 3/20  | 621M   |    |          |        |

|              |       |           | 審査請求 未 | 請求請   | 求項の数 6 | ΟL | (全 13 頁) | 最終頁に続く |

(21) 出願番号 (22) 出願日

特願2011-22953 (P2011-22953) 平成23年2月4日(2011.2.4)

(71) 出願人 302020207

株式会社ジャパンディスプレイセントラル

埼玉県深谷市幡羅町一丁目9番地2

(74)代理人 100108855

弁理士 蔵田 昌俊

(74)代理人 100159651

弁理士 高倉 成男

(74)代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100075672

弁理士 峰 隆司

最終頁に続く

## (54) 【発明の名称】液晶表示装置

## (57)【要約】

【課題】 消費電力を低減する液晶表示装置を提供する

【解決手段】 第1基板200と、複数の画素電極23 0のそれぞれに対向した対向電極330を備えた第2基 板300と、第1基板200と第2基板300との間に 保持された液晶層400と、備え、第1基板200は、 対向電極330に供給される電圧を制御する対向電圧生 成回路COMを備え、対向電圧生成回路COMは、対向 電極330と第1電圧源VDDとの電気的接続を切替え る第1スイッチSWAと、対向電極330と第2電圧源 VSSとの電気的接続を切替える第2スイッチSWBと 、第1スイッチSWAの開閉を制御する信号を出力する 否定論理積回路530と、第2スイッチSWBの開閉を 制御する信号を出力する否定論理和回路540と、遅延 回路520と、を備え、否定論理積回路530および否 定論理和回路540には遅延回路520の入力信号と出 力信号とが入力される。

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

複数の画素によって構成された略矩形状のアクティブエリアを備えた液晶表示装置であって、

前記画素のそれぞれに画素電極を備えた第1基板と、

前記画素電極のそれぞれに対向した対向電極を備えた第2基板と、

前記第1基板と前記第2基板との間に保持された液晶層と、を備え、

前記第1基板は、さらに、前記対向電極に供給される電圧を制御する対向電圧生成回路を備え、

前記対向電圧生成回路は、前記対向電極と第1電圧源との電気的接続を切替える第1スイッチと、前記対向電極と第2電圧源との電気的接続を切替える第2スイッチと、前記第1スイッチの開閉を制御する信号を出力する否定論理積回路と、前記第2スイッチの開閉を制御する信号を出力する否定論理和回路と、遅延回路と、を備え、

前記否定論理積回路および前記否定論理和回路には前記遅延回路の入力信号と出力信号とが入力される、液晶表示装置。

#### 【請求項2】

複数の画素によって構成された略矩形状のアクティブエリアを備えた液晶表示装置であって、

前記画素のそれぞれに画素電極を備えた第1基板と、

前記画素電極のそれぞれに対向した対向電極を備えた第2基板と、

前記第1基板と前記第2基板との間に保持された液晶層と、を備え、

前記第1基板は、さらに、前記対向電極に供給される電圧を制御する対向電圧生成回路を備え、

前記対向電圧生成回路は、前記対向電極と第1電圧源との電気的接続を切替える第1スイッチと、前記対向電極と第2電圧源との電気的接続を切替える第2スイッチと、前記第1スイッチの開閉を制御する信号を出力する否定論理積回路と、前記第2スイッチの開閉を制御する信号を出力する否定論理和回路と、前記第1論理回路の出力信号を反転して前記否定論理和回路へ出力する第1遅延回路と、前記第2論理回路の出力信号を反転して前記否定論理積回路へ出力する第2遅延回路と、を備え、

前記否定論理積回路および前記否定論理和回路には共通の制御信号がさらに入力される、液晶表示装置。

## 【請求項3】

前記第1スイッチはP型の薄膜トランジスタであり、前記第2スイッチはN型の薄膜トランジスタである請求項1又は請求項2記載の液晶表示装置。

### 【請求項4】

前記遅延回路は、直列に接続された2以上の偶数のインバート回路を備える請求項1記載の液晶表示装置。

### 【請求項5】

前記第1遅延回路および第2遅延回路のそれぞれは、直列に接続された1以上の奇数のインバート回路を備える請求項2記載の液晶表示装置。

## 【請求項6】

前記第1スイッチおよび第2スイッチは、ポリシリコンによって形成された半導体層を備えた薄膜トランジスタである請求項1又は請求項2記載の液晶表示装置。

# 【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明の実施形態は、液晶表示装置に関する。

## 【背景技術】

### [0002]

液晶表示装置は、軽量、薄型、低消費電力などの特徴を生かして、パーソナルコンピュ

10

20

30

30

40

ータやテレビなどの O A 機器などの表示装置として各種分野で利用されている。近年では、液晶表示装置は、携帯電話などの携帯端末機器や、カーナビゲーション装置、ゲーム機などの様々な電子機器の表示装置としても利用されている。

[00003]

液晶表示装置は、シール材を介して対向して貼り合わせられたアレイ基板と対向基板と の間に液晶層を保持して構成された液晶表示パネルを備えている。この液晶表示パネルは 、画像を表示する略矩形状のアクティブエリアを備えている。

[0004]

アクティブエリアにおいてアレイ基板はマトリクス状に配置された複数の画素電極を備えている。対向基板は、複数の画素電極と対向するように配置された対向電極を備えている。複数の画素電極には、駆動回路からそれぞれ対応する映像信号が印加される。対向電極には対向電圧生成回路から対向電圧が印加される。

[00005]

例えば、低温ポリシリコン技術を用いて液晶表示パネルに対向電圧生成回路を内蔵する場合、液晶表示パネルサイズやアレイ基板と対向基板との間の基板間ギャップから、液晶負荷容量を算出して対向電圧生成回路の最終段バッファ能力を調整している。対向電圧生成回路の最終段バッファは例えば2つの電圧源と対向電極との電気的接続を切替えている

【先行技術文献】

【特許文献】

[0006]

【特許文献1】特開2008-209696号公報

【発明の概要】

【発明が解決しようとする課題】

[0007]

液晶表示パネルのアクティブエリアの寸法や基板間ギャップが大きくなると液晶負荷容量が大きくなり、対向電圧生成回路の最終段バッファに入力されるゲート信号波形の立ち上がりおよび立下りに遅延が発生する。この場合、対向電極と一方の電圧源との接続を切替える第 2 スイッチとの両方が閉じて(導通して)、 2 つの電圧源間に貫通電流が流れることがあった。さらに第 1 スイッチおよび第 2 スイッチの種類の特性によっては、両方が閉じる期間が長くなり、貫通電流が大きくなることがあった。貫通電流が流れると消費電力が大きくなるため、低消費電力化を実現することが困難であった。

[0008]

本発明は上記事情を鑑みて成されたものであって、消費電力を低減する液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

[0009]

実施形態による液晶表示装置は、複数の画素によって構成された略矩形状のアクティブエリアを備えた液晶表示装置であって、前記画素のそれぞれに画素電極を備えた第1基板と、前記画素電極のそれぞれに対向した対向電極を備えた第2基板と、前記第1基板はは、さらに、前記対向電極に供給される電圧を制御する対向電圧生成回路を備え、前記対向電圧生成回路は、前記対向電圧生成回路は、前記対向電極と第1電圧源との電気的接続を切替える第1スイッチと、前記対向電極と第2電圧源との電気的接続を切替える第2スイッチと、前記第1スイッチの開閉を制御する信号を出力する否定論理和回路と、遅延回路と、を備え、前記否定論理積回路および前記否定論理和回路には前記遅延回路の入力信号と出力信号とが入力される、液晶表示装置。

【図面の簡単な説明】

[0010]

10

20

30

40

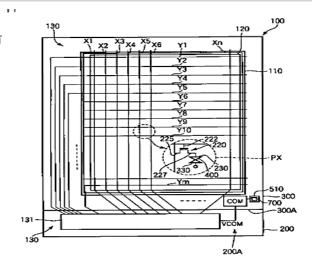

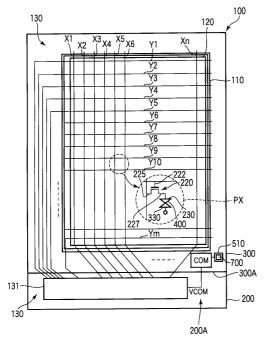

- 【 図 1 】 実 施 形 態 の 液 晶 表 示 装 置 の 一 構 成 例 を 示 す 図 で あ る 。

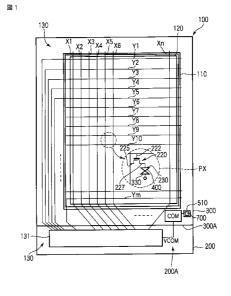

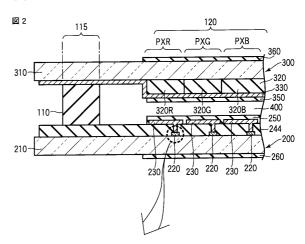

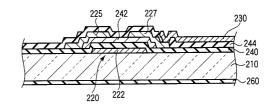

- 【図2】図1に示した液晶表示パネルの構成を概略的に示す断面図の一例である。

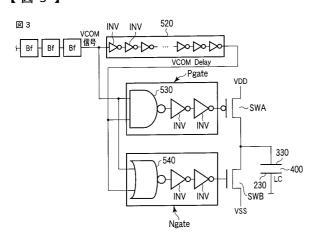

- 【図3】図1に示した対向電圧生成回路の最終段のバッファ回路の一構成例を概略的に示す図である。

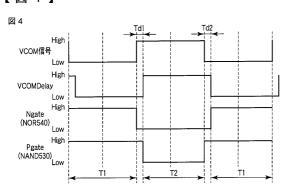

- 【図4】図3に示す最終段のバッファ回路の動作の一例を説明するためのタイミングチャートである。

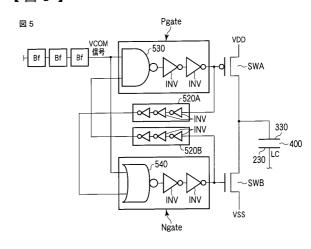

- 【 図 5 】 図 1 に示した対向電圧生成回路の最終段のバッファ回路の他の構成例を概略的に示す図である。

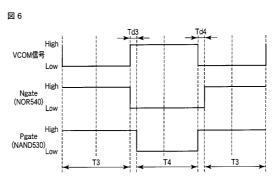

- 【図 6 】図 5 に示す最終段のバッファ回路の動作の一例を説明するためのタイミングチャートである。

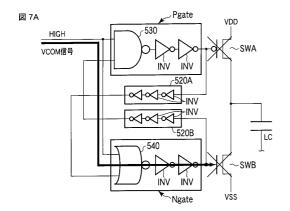

- 【図7A】図5に示す最終段のバッファ回路に入力される制御信号の立ち上がり時の動作の一例を説明するための図である。

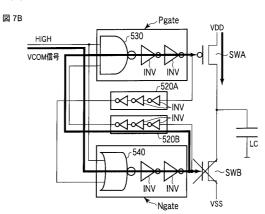

- 【図7B】図5に示す最終段のバッファ回路に入力される制御信号の立ち上がり時の動作の一例を説明するための図である。

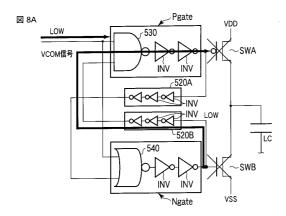

- 【図8A】図5に示す最終段のバッファ回路に入力される制御信号の立ち下がり時の動作の一例を説明するための図である。

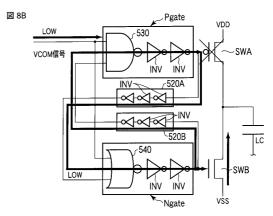

- 【図8B】図5に示す最終段のバッファ回路に入力される制御信号の立ち下がり時の動作の一例を説明するための図である。

【発明を実施するための形態】

[0011]

以下、実施形態について、図面を参照して説明する。

図1に、本実施形態に係る液晶表示装置の一構成例を示す。図1に示すように、液晶表示装置は、略矩形平板上の液晶表示パネル100を備えている。液晶表示パネル100は、一対の基板すなわちアレイ基板(第1基板)200及び対向基板(第2基板)300と、アレイ基板200と対向基板300との間に保持された液晶層400と、を備えている。アレイ基板200と対向基板300とは、シール材110によって貼り合わせられ、これらの間に液晶層400を保持するための所定のギャップを形成する。

[0012]

液晶表示パネル100は、シール材110によって囲まれた内側に、画像を表示する略矩形状のアクティブエリア120を備えている。このアクティブエリア120は、マトリクス状に配置された複数の画素 PXによって構成されている。

[0013]

アレイ基板 2 0 0 は、アクティブエリア 1 2 0 において、画素 P X の行方向に沿って延在する複数のゲート線 Y ( 1 、 2 、 3 、 ... 、 m ) と、画素 P X の列方向に沿って延在する複数のソース線 X ( 1 、 2 、 3 、 ... 、 n ) と、各画素 P X におけるソース線 X とゲート線 Y との交差部に配置されたスイッチング素子 2 2 0 と、画素 P X のそれぞれに配置されスイッチング素子 2 2 0 に接続された画素電極 2 3 0 と、を備えている。

[0014]

ゲート線 Y とソース線 X とは、絶縁層を介して互いに交差するように配置されている。 スイッチング素子 2 2 0 は、例えばポリシリコンによって形成された半導体層を備えた薄膜トランジスタ(TFT;Thin Film Transistor)によって構成されている。

[ 0 0 1 5 ]

スイッチング素子220のゲート電極222は、ゲート線Yに接続されている(あるいは、ゲート電極222は、ゲート線Yと一体的に形成されている)。スイッチング素子220のソース電極225は、ソース線Xに接続されている(あるいは、ソース225は、ソース線Xと一体的に形成されている)。スイッチング素子220のドレイン電極227は、画素電極230に接続されている。

[0016]

対向基板300は、アクティブエリア120において、複数の画素電極230のそれぞれに対向した対向電極330を備えている。

10

20

30

40

また、液晶表示パネル100は、アクティブエリア120の外側に位置する外周部13 0に配置された接続部131を備えている。この接続部131は、信号供給源として機能する駆動ICチップやフレキシブル配線基板と接続可能である。図1に示した例では、接続部131は、対向基板300の端部300Aより外方に延在したアレイ基板200の延在部200A上に形成されている。

## [0017]

アクティブエリア120に配置されたゲート線 Y (1、2、3、…、m)のそれぞれは、外周部130を経由して接続部131に接続されている。また、ソース線 X (1、2、3、…、n)のそれぞれも同様に、外周部130を経由して接続部131に接続されている。

[0018]

次に、アレイ基板200及び対向基板300の構造をより詳細に説明する。

図 2 に示すように、アレイ基板 2 0 0 は、ガラスなどの光透過性を有する絶縁基板 2 1 0 を用いて形成される。スイッチング素子 2 2 0 のゲート電極 2 2 2 は、ゲート線 Y などとともに絶縁基板 2 1 0 の上に配置されている。このゲート電極 2 2 2 は、ゲート絶縁膜 2 4 0 によって覆われている。このゲート絶縁膜 2 4 0 は、例えば、窒化シリコン ( S i 3 N 4 ) などによって形成されている。

## [0019]

スイッチング素子 2 2 0 の半導体層 2 4 2 は、ゲート絶縁膜 2 4 0 の上に配置されている。この半導体層 2 4 2 には、スイッチング素子 2 2 0 のソース電極 2 2 5 及びドレイン電極 2 2 7 がコンタクトしている。これらのソース電極 2 2 5 及びドレイン電極 2 2 7 は、パッシベーション膜 2 4 4 によって覆われている。このパッシベーション膜 2 4 4 は、例えば、窒化シリコン(Si<sub>3</sub> N 4 )などによって形成されている。

[0020]

画素電極 2 3 0 は、パッシベーション膜 2 4 4 の上において各画素 P X に対応して配置されている。この画素電極 2 3 0 は、パッシベーション膜 2 4 4 に形成されたコンタクトホールを介してスイッチング素子 2 2 0 のドレイン電極 2 2 7 と電気的に接続されている

## [0021]

バックライト光を選択的に透過して画像を表示する透過型液晶表示パネルにおいては、画素電極 2 3 0 は、例えば、インジウム・ティン・オキサイド(ITO)やインジウム・ジンク・オキサイド(IZO)などの光透過性を有する導電材料によって形成されている。また、外光を選択的に反射して画像を表示する反射型液晶表示パネルにおいては、画素電極 2 3 0 は、例えば、アルミニウム(A1)やモリブデン(Mo)などの光反射性を有する導電材料によって形成されている。

[0022]

対向基板 3 0 0 は、ガラスなどの光透過性を有する絶縁基板 3 1 0 を用いて形成される。カラー表示タイプの液晶表示装置では、液晶表示パネル 1 0 0 は、複数種類の画素、例えば赤(R)を表示する赤色画素 P X R、緑(G)を表示する緑色画素 P X G、青(B)を表示する青色画素 P X B を有している。

[ 0 0 2 3 ]

図 2 に示した実施形態においては、対向基板 3 0 0 は、アクティブエリア 1 2 0 において、絶縁基板 3 1 0 の一方の主面(液晶層と対向する面)上に、画素 P X 毎に配置されたカラーフィルタ層 3 2 0 (R、G、B) を備えている。これらのカラーフィルタ層 3 2 0 (R、G、B) は、赤色(R)、緑色(G)、及び青色(B)にそれぞれ着色された複数の着色樹脂によって形成されている。

#### [0024]

すなわち、対向基板300は、絶縁基板310上に、赤色画素PXRに対応して赤色の主波長の光を透過するように着色された樹脂からなる赤色カラーフィルタ層320Rを備え、緑色画素PXGに対応して緑色の主波長の光を透過するように着色された樹脂からな

10

20

30

40

10

20

30

40

50

る緑色カラーフィルタ層 3 2 0 G を備え、さらに、青色画素 P X B に対応して青色の主波長の光を透過するように着色された樹脂からなる青色カラーフィルタ層 3 2 0 B を備えている。

## [0025]

対向電極 3 3 0 は、アクティブエリア 1 2 0 において、複数の画素 P X に対向するようにカラーフィルタ層 3 2 0 上に配置されている。この対向電極 3 3 0 は、例えば I T O や I Z O などの光透過性を有する導電材料によって形成されている。

### [0026]

これらのアレイ基板 2 0 0 及び対向基板 3 0 0 の表面は、液晶層 4 0 0 に含まれる液晶分子の配向を制御するための配向膜 2 5 0 及び 3 5 0 によってそれぞれ覆われている。また、アレイ基板 2 0 0 及び対向基板 3 0 0 の外面には、それぞれ光学素子 2 6 0 及び 3 6 0 が設けられている。これらの光学素子 2 6 0 及び 3 6 0 は、液晶層 4 0 0 の特性に合わせて偏光方向を設定した偏光板などを含んでいる。

## [ 0 0 2 7 ]

図1に示すように、シール材110は、略矩形状のアクティブエリア120を囲むようにアレイ基板200と対向基板300との間に配置される。シール材110は、例えば熱硬化性樹脂や紫外線硬化性樹脂などの樹脂材料によって形成され、液晶表示パネル100を構成する一方の基板、例えばアレイ基板200のアクティブエリア120を囲むシール部115に塗布される。その後、他方の基板、例えば対向基板300をアレイ基板200に対向配置した状態で、一対の基板を貼り合わせる方向に加圧しながら加熱するあるいは紫外線を照射する。これにより、シール材110が硬化し、アレイ基板200と対向基板300とが貼り合わせられる。

### [0028]

次に、アレイ基板側から対向基板側への給電構造についてより詳細に説明する。

アレイ基板 2 0 0 は、対向電極 3 3 0 に対して所定の電位、例えば対向電位を供給するための対向電圧生成回路 C O M と対向電圧生成回路 C O M から出力された対向電位が印加される給電パッド 5 1 0 と、をさらに備えている。

#### [0029]

給電パッド 5 1 0 は、アクティブエリア 1 2 0 外の角部、すなわちシール材 1 1 0 が配置されるシール部 1 1 5 よりも基板端側に位置したアレイ基板 2 0 0 の角部に配置されている。この給電パッド 5 1 0 は、対向基板 3 0 0 においてシール部 1 1 5 よりも基板端側まで延在した対向電極 3 3 0 と対向している。このような給電パッド 5 1 0 は、パッシベーション膜 2 4 4 の上に配置され、画素電極 2 3 0 と同一材料によって形成されている。この給電パッド 5 1 0 は、配向膜 2 5 0 から露出している。

# [0030]

給電パッド 5 1 0 の上には、対向電極 3 3 0 にコンタクトした導電性部材 7 0 0 が配置されている。つまり、対向電圧生成回路 C O M から出力された対向電位は、給電パッド 5 1 0 を介して導電性部材 7 0 0 により対向電極 3 3 0 へ印加される。

## [0031]

対向電圧生成回路 C O M はアレイ基板 2 0 0 のアクティブエリア 1 2 0 外に形成されている。対向電圧生成回路 C O M は、例えば低温ポリシリコン技術により、スイッチング素子 2 2 0 、ゲート線 Y 、ソース線 X 等を形成する工程と同時に、アレイ基板 2 0 0 の絶縁基板 2 1 0 上に形成される。

# [0032]

図3に、対向電圧生成回路COMの最終段のバッファ回路の一構成例を示す。対向電圧生成回路COMは複数段のバッファ回路Bfを備えている。対向電圧生成回路COMの最終段のバッファ回路は、第1電圧源VDDと対向電極330との電気的接続を切替える第1スイッチSWAと、第2電圧源VSSと対向電極330との電気的接続を切替える第2スイッチSWBと、第1スイッチSWAのゲート電圧を制御する論理回路Pgateと、第2スイッチSWBのゲート電圧を制御する論理回路Ngateと、遅延回路520と、

を備えている。

### [0033]

第1スイッチSWAは、P型の薄膜トランジスタであって、ソース・ドレインパスが第1電圧源VDDと対向電極330との間に電気的に接続されている。第2スイッチSWBは、N型の薄膜トランジスタであって、ソース・ドレインパスが第2電圧源VSSと対向電極330との間に電気的に接続されている。

### [0034]

論理回路 P g a t e は、否定論理積回路 5 3 0 と、否定論理積回路 5 3 0 の後段に直列に接続された 2 つのインバート回路 I N V と、を備えている。否定論理積回路 5 3 0 の出力信号は、 2 つのインバート回路 I N V を介して第 1 スイッチ S W A のゲート電極に印加される。したがって論理回路 P g a t e の出力信号は、否定論理積回路 5 3 0 の出力信号を反転しない信号となる

論理回路Ngateは、否定論理和回路540と、否定論理和回路540の後段に直列に接続された2つのインバート回路INVと、を備えている。否定論理和回路540の出力信号は、2つのインバート回路INVを介して第2スイッチSWBのゲート電極に印加される。したがって論理回路Ngateの出力信号は、否定論理和回路540の出力信号を反転しない信号となる。

#### [0035]

遅延回路520は、直列に接続された複数のインバート回路INVを備えている。遅延回路520は、遅延回路520の入力信号と出力信号との波形が反転しないように、2以上の偶数のインバート回路INVを備えている。なお、遅延回路520のインバート回路INVの数は、液晶容量LCの大きさや配線容量、第1スイッチSWAおよび第2スイッチSWBのゲート容量に応じて調整することが望ましい。

#### [0036]

遅延回路520には、接続部131を介して信号供給源としての駆動ICチップやフレキシブル配線基板から(若しくは複数段のバッファ回路Bfを介して)VCOM信号が入力される。論理回路Pgateの否定論理積回路530にはVCOM信号(遅延回路520の入力信号)と遅延回路520の入力信号(VCOM Delay)とが入力される。論理回路Ngateの否定論理和回路540にはVCOM信号(遅延回路520の入力信号)と遅延回路520の出力信号(VCOM Delay)とが入力される。

### [0037]

図4は、図3に示すバッファ回路の動作を説明するためのタイミングチャートの一例を示す。遅延回路520から出力される出力信号(VCOM Delay)は入力されたVCOM信号に対して所定期間だけ遅延した波形となる。

### [0038]

VCOM信号がロー(Low)レベルであって、出力信号(VCOM Delay)がローレベルである期間T1では、論理回路Pgateおよび論理回路Ngateは共にハイ(High)レベルの信号を出力する。したがってこの期間T1では、第2スイッチSWBのソース・ドレインパスが導通して対向電極330には第2電圧源VSSから対向電圧が供給されている。

## [0039]

VCOM信号がローレベルからハイレベルへ変化し、出力信号(VCOM Delay)がローレベルのままである期間Td1では、論理回路Pgateはハイレベルの信号出力を維持し、論理回路Ngateはローレベルの信号を出力する。したがって、この期間Td1では、第1スイッチSWAおよび第2スイッチSWBの両方が開いた状態となる。

# [0040]

VCOM信号がハイレベルへ変化した後、所定期間が経過すると、出力信号(VCOM Delay)がハイレベルへ変化する。VCOM信号と出力信号(VCOM Delay)との両方がハイレベルである期間T2では、論理回路Pgateおよび論理回路Ngateは共にローレベルの信号を出力する。したがって、この期間T2では、第1スイッチSWAのソース・ド

10

20

30

40

レインパスが導通して対向電極330には第1電圧源VDDから対向電圧が供給される。

### [0041]

VCOM信号がハイレベルからローレベルへ変化し、出力信号(VCOM Delay)がハイレベルのままである期間Td2では、論理回路Pgateはハイレベルの信号を出力し、論理回路Ngateはローレベルの出力信号を維持する。したがって、この期間Td2では、第1スイッチSWAおよび第2スイッチSWBの両方が開いた状態となる。

#### [0042]

VCOM信号がローレベルへ変化した後、所定期間が経過すると、出力信号(VCOM Delay)がローレベルへ変化して、再びVCOM信号と出力信号(VCOM Delay)とが共にローレベルとなり、第2スイッチSWBのソース・ドレインパスが導通する。

## [0043]

上記のように、図3に示すバッファ回路では、VCOM信号が変化してから出力信号(VCOM Delay)が変化するまでの期間(期間Td1、Td2)は、第1スイッチSWAおよび第2スイッチSWBの両方が閉じた状態となり、第1スイッチSWAと第2スイッチSWBとの両方のソース・ドレインパスが導通する期間が生じない。したがって、遅延回路520による遅延期間を負荷容量の大きさに応じて調整することにより、第1電圧源VDDから第2電圧源VSSへ貫通電流が流れることを防止し、消費電力が増すことを回避することができる。

## [0044]

すなわち、本実施形態に係る液晶表示装置によれば、消費電力を低減する液晶表示装置 を提供することができる。

### [0045]

次に、第2実施形態に係る液晶表示装置について図面を参照して説明する。なお、以下の説明において上述の第1実施形態に係る液晶表示装置と同様の構成については同一の符号を付して説明を省略する。本実施形態に係る液晶表示装置は、アレイ基板200の対向電圧生成回路COMの最終段のバッファ回路の構成が上述の第1実施形態に係る液晶表示装置と異なっている。

### [0046]

図5に、本実施形態に係る液晶表示装置のアレイ基板200に設けられた対向電圧生成回路COMの最終段のバッファ回路の一構成例を示す。対向電圧生成回路COMの最終段のバッファ回路は、第1電圧源VDDと対向電極330との電気的接続を切替える第1スイッチSWAと、第2電圧源VSSと対向電極330との電気的接続を切替える第2スイッチSWBと、第1スイッチSWAのゲート電圧を制御する論理回路Pgateと、第2スイッチSWBのゲート電圧を制御する論理回路Ngateと、遅延回路520A、520Bと、を備えている。

## [0047]

第1スイッチSWAは、P型の薄膜トランジスタであって、ソース・ドレインパスが第1電圧源VDDと対向電極330との間に電気的に接続されている。第2スイッチSWBは、N型の薄膜トランジスタであって、ソース・ドレインパスが第2電圧源VSSと対向電極330との間に電気的に接続されている。

## [ 0 0 4 8 ]

論理回路Pgateは、否定論理積回路530と、否定論理積回路530の後段に直列に接続された2つのインバート回路INVと、を備えている。論理回路Pgateの出力信号は、否定論理積回路530の出力信号を反転しない信号となる。否定論理積回路530には、接続部131を介して信号供給源としての駆動ICチップやフレキシブル配線基板から(若しくは複数段のバッファ回路Bfを介して)VCOM信号と後述する遅延回路520Bの出力信号とが入力される。否定論理積回路530の出力信号は、2つのインバート回路INVを介して第1スイッチSWAのゲート電極に印加される。

### [0049]

論理回路 N g a t e は、否定論理和回路 5 4 0 と、否定論理和回路 5 4 0 の後段に直列

10

20

30

40

に接続された2つのインバート回路INVと、を備えている。論理回路Ngateの出力信号は、否定論理和回路540の出力信号を反転しない信号となる。否定論理和回路540には、接続部131を介して信号供給源としての駆動ICチップやフレキシブル配線基板から(若しくは複数段のバッファ回路Bfを介して)VCOM信号と後述する遅延回路520Aの出力信号が入力される。否定論理和回路540の出力信号は、2つのインバート回路INVを介して第2スイッチSWBのゲート電極に印加される。すなわち、否定論理積回路530と否定論理和回路540とには共通の制御信号としてVCOM信号が入力される。

# [0050]

遅延回路520Aはインバート回路INVを備えている。遅延回路520Aは、遅延回路520Aの入力信号と出力信号との波形が反転するように、直列に接続された1以上の奇数のインバート回路INVを備えている。遅延回路520Aには論理回路Ngateの出力信号が入力され、遅延回路520Aの出力信号は論理回路Pgateの否定論理積回路530に入力される。

### [0051]

同様に、遅延回路520Bはインバート回路INVを備えている。遅延回路520Bは、遅延回路520Bの入力信号と出力信号との波形が反転するように、直列に接続された1以上の奇数のインバート回路INVを備えている。遅延回路520Bには論理回路Pgateの出力信号が入力され、遅延回路520Bの出力信号は論理回路Ngateの否定論理和回路540に入力される。

### [0052]

なお、遅延回路520A、520Bのインバート回路INVの数は、液晶容量LCの大きさや配線容量、第1スイッチSWAおよび第2スイッチSWBのゲート容量に応じて調整することが望ましい。

### [ 0 0 5 3 ]

図 6 に、図 5 に示すバッファ回路の動作を説明するためのタイミングチャートの一例を示す。

VCOM信号がロー(Low)レベルである期間T3では、論理回路Pgateおよび 論理回路Ngateは共にハイレベルの信号を出力する。したがってこの期間T3では、 第2スイッチSWBのソース・ドレインパスが導通して対向電極330には第2電圧源VSSから対向電圧が供給されている。

# [0054]

図7Aおよび図7Bに、VCOM信号がローレベルからハイレベルへ変化するときのバッファ回路の動作を説明するための図を示す。VCOM信号がローレベルからハイレベルへ変化してから所定期間Td3では、まず、図6および図7Aに示すように論理回路Ngateの出力信号がローレベルとなる。このことによって、第2スイッチSWBが開いた状態となる。したがって期間Td3では第1スイッチSWAおよび第2スイッチSWBの両方が開いている。

## [0055]

VCOM信号がローレベルからハイレベルへ変化して所定期間Td3経過すると、図6および図7Bに示すように、遅延回路520Bを介して論理回路Pgateに入力される論理回路Ngateの信号がハイレベルとなり、論理回路Pgateの出力信号がハイレベルへ変化する。したがって、VCOM信号がローレベルからハイレベルへ変化して所定期間Td3経過した後の期間T4では、第1スイッチSWAのソース・ドレインパスが導通して、対向電極330には第1電圧源VDDから対向電圧が供給される。

# [0056]

図8Aおよび図8Bに、VCOM信号がハイレベルからローレベルへ変化するときのバッファ回路の動作を説明するための図を示す。VCOM信号がハイレベルからローレベルへ変化してから所定期間Td4では、まず、図6および図8Aに示すように、論理回路Pgateの出力信号がハイレベルとなる。このことによって、第1スイッチSWAが開い

10

20

30

40

た状態となる。 したがって期間Td4では第1スイッチSWAおよび第2スイッチSWB の両方が開いている。

## [0057]

VCOM信号がハイレベルからローレベルへ変化して所定期間Td4経過すると、図6および図8Bに示すように、遅延回路520Aを介して論理回路Ngateに入力される論理回路Pgateの信号がローレベルとなり、論理回路Ngateの出力信号がハイレベルとなる。したがって、VCOM信号がハイレベルからローレベルへ変化して所定期間Td4経過した後の期間T3では、第2スイッチSWBのソース・ドレインパスが導通して、対向電極330には第2電圧源VSSから対向電圧が供給される。

#### [0058]

上記のように、図5に示すバッファ回路では、VCOM信号が変化してから遅延回路520A、520Bの出力信号が変化するまでの期間(期間Td3、Td4)は、第1スイッチSWAおよび第2スイッチSWBの両方が閉じた状態となり、第1スイッチSWAと第2スイッチSWBとの両方のソース・ドレインパスが導通する期間が生じない。したがって、遅延回路520A、520Bによる遅延期間を負荷容量の大きさに応じて調整することにより、第1電圧源VDDから第2電圧源VSSへ貫通電流が流れることを防止し、消費電力が増すことを回避することができる。

## [0059]

すなわち、本実施形態に係る液晶表示装置によれば、消費電力を低減する液晶表示装置 を提供することができる。

### [0060]

以上で説明したように、上述の第1実施形態および第2実施形態によれば、アレイ基板 200内に対向電圧生成回路COMを内蔵し、低消費電電力を実現する表示装置を提供す ることが可能である。

## [0061]

なお、対向電圧生成回路 C O M は、アレイ基板 2 0 0 を形成する低温ポリシリコン製造工程において、アクティブエリア 1 2 0 に配置されたスイッチング素子 2 2 0 、ゲート線 Y 、ソース線 X 等を形成する工程と同時に、アレイ基板 2 0 0 の絶縁基板 2 1 0 上に形成されるため製造工程も増加せず、したがって上記実施形態によれば製造コストを増大させることもなく上記効果を得ることが可能である。

### [0062]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる

### 【符号の説明】

## [0063]

PX…画素、COM…対向電圧生成回路、VDD…第1電圧源、SWA…第1スイッチ、VSS…第2電圧源、SWB…第2スイッチ、Pgate…第1論理回路、Ngate…第2論理回路、INV…インバート回路、100…液晶表示パネル、120…アクティブエリア、130…外周部、200…アレイ基板、230…画素電極、300…対向基板、330…対向電極、400…液晶層、520…遅延回路、520A…第1遅延回路、520B…第2遅延回路、530…否定論理積回路、540…否定論理和回路、700…導電性部材。

10

20

30

# 【図1】

図 1

# 【図2】

【図3】

【図5】

【図4】

【図6】

# 【図7A】

# 【図7B】

# 【図8A】

# 【図8B】

## フロントページの続き

(51) Int.CI. F I テーマコード (参考)

G 0 9 G 3/20 6 1 1 A

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72) 発明者 丸山 哲

埼玉県深谷市幡羅町一丁目9番地2 東芝モバイルディスプレイ株式会社内

(72)発明者 原田 賢治

埼玉県深谷市幡羅町一丁目9番地2 東芝モバイルディスプレイ株式会社内

F ターム(参考) 2H193 ZA04 ZF02 ZF59 ZG03

5C006 AA16 AA22 AC11 AC25 AC26 AF50 AF52 AF71 BB16 BC20 BF07 BF25 BF26 BF27 BF33 BF34 BF42 EB05 FA16 FA36

FA37 FA47 FA51

5C080 AA10 BB05 CC03 DD24 DD25 DD26 DD27 FF03 FF11 JJ02

JJ03 JJ04 KK03 KK07 KK20 KK23

| 专利名称(译)     | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号     | JP2012163696A                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2012-08-30 |  |  |  |

| 申请号         | JP2011022953                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2011-02-04 |  |  |  |

| 申请(专利权)人(译) | 有限公司日本展示中心                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |  |

| [标]发明人      | 丸山哲<br>原田賢治                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |

| 发明人         | 丸山 哲<br>原田 賢治                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |

| IPC分类号      | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |

| FI分类号       | G09G3/36 G02F1/133.550 G02F1/133.535 G09G3/20.624.C G09G3/20.621.M G09G3/20.611.A                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |  |  |

| F-TERM分类号   | 2H193/ZA04 2H193/ZF02 2H193/ZF59 2H193/ZG03 5C006/AA16 5C006/AA22 5C006/AC11 5C006 /AC25 5C006/AC26 5C006/AF50 5C006/AF52 5C006/AF71 5C006/BB16 5C006/BC20 5C006/BF07 5C006/BF25 5C006/BF26 5C006/BF27 5C006/BF33 5C006/BF34 5C006/BF42 5C006/EB05 5C006 /FA16 5C006/FA36 5C006/FA37 5C006/FA47 5C006/FA51 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD24 5C080/DD25 5C080/DD26 5C080/DD27 5C080/FF03 5C080/FF11 5C080/JJ02 5C080 /JJ03 5C080/JJ04 5C080/KK03 5C080/KK07 5C080/KK20 5C080/KK23 |         |            |  |  |  |

| 代理人(译)      | 河野 哲<br>中村诚<br>河野直树<br>冈田隆                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |  |

| 外部链接        | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |  |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |  |

## 摘要(译)

提供一种降低功耗的液晶显示装置。 和第一基板200,第二基板300具有面向每个所述多个像素电极230,第一基板200和第二基板之间夹持的液晶层的对置电极330 300 400,包括第一基板200包括计数器电压产生电路COM,其控制提供给公共电极330的电压,对电极电压产生电路COM电对置电极330和第一电压源VDD之间第一开关SWA的切换连接,第二开关SWB用于切换对置电极330和第二电压源VSS之间的电连接,以及用于控制所述第一开关SWA的开闭输出信号的NAND电路530一NOR为用于控制第二开关SWB,延迟电路520,提供时,NAND电路530的开闭输出信号电路540和NOR电路540和延迟电路的输入信号520个输出信号输入。 点域1