(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-87895

(P2018-87895A)

(43) 公開日 平成30年6月7日(2018.6.7)

| (51) Int.Cl.                 | F 1             | テーマコード (参考) |

|------------------------------|-----------------|-------------|

| <b>G02F 1/1368 (2006.01)</b> | GO2F 1/1368     | 2H092       |

| <b>G02F 1/1333 (2006.01)</b> | GO2F 1/1333     | 2H189       |

| <b>G02F 1/1343 (2006.01)</b> | GO2F 1/1343     | 2H192       |

| <b>G02F 1/1335 (2006.01)</b> | GO2F 1/1335 505 | 2H291       |

審査請求 未請求 請求項の数 15 O L (全 51 頁)

|           |                              |          |                                                                                                                                                                                                                                               |

|-----------|------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2016-230912 (P2016-230912) | (71) 出願人 | 506087819<br>パナソニック液晶ディスプレイ株式会社<br>兵庫県姫路市飾磨区妻鹿日田町1-6                                                                                                                                                                                          |

| (22) 出願日  | 平成28年11月29日 (2016.11.29)     | (74) 代理人 | 110000154<br>特許業務法人はるか国際特許事務所                                                                                                                                                                                                                 |

|           |                              | (72) 発明者 | 小野 記久雄<br>兵庫県姫路市飾磨区妻鹿日田町1-6 パ<br>ナソニック液晶ディスプレイ株式会社内<br>F ターム (参考) 2H092 GA14 GA22 GA23 GA51 GA60<br>JA26 JA46 JB03 JB04 JB06<br>JB23 JB32 JB57 JB58 NA01<br>PA06 PA08 PA09 PA13<br>2H189 AA28 CA36 LA03 LA06 LA07<br>LA08 LA10 LA14 LA15 LA20 |

|           |                              |          |                                                                                                                                                                                                                                               |

|           |                              |          | 最終頁に続く                                                                                                                                                                                                                                        |

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】複数の表示パネルを重ね合わせて構成された液晶表示装置において、単色画像の色再現性の向上を図る。

【解決手段】液晶表示装置は、互いに重ね合わされて配置された第1表示パネル及び第2表示パネルを含み、前記第1表示パネルは、第1方向に延在する複数の第1ソース線と第2方向に延在する複数の第1ゲート線と複数の第1薄膜トランジスタと複数の第1画素電極と複数の第1画素とを含み、前記第2表示パネルは、前記第1方向に延在する複数の第2ソース線と前記第2方向に延在する複数の第2ゲート線と複数の第2薄膜トランジスタと複数の第3薄膜トランジスタと複数の第2画素電極と複数の第3画素電極と複数の第2画素と複数の第3画素とを含み、前記第2表示パネルは、さらに、平面視で、前記第2方向に隣り合って配置された前記第2画素電極と前記第3画素電極との間に前記第2ソース線が配置されていない第1領域を含む。

【選択図】図20

## 【特許請求の範囲】

## 【請求項 1】

複数の表示パネルが重ね合わされて配置され、それぞれの前記表示パネルに画像を表示する液晶表示装置であって、

互いに重ね合わされて配置された第1表示パネル及び第2表示パネルを含み、

前記第1表示パネルは、第1方向に延在する複数の第1ソース線と、前記第1方向に交差する第2方向に延在する複数の第1ゲート線と、複数の第1薄膜トランジスタと、前記各第1薄膜トランジスタに電気的に接続された複数の第1画素電極と、前記各第1画素電極の駆動領域を規定する複数の第1画素と、を含み、

前記第2表示パネルは、前記第1方向に延在する複数の第2ソース線と、前記第2方向に延在する複数の第2ゲート線と、複数の第2薄膜トランジスタと、複数の第3薄膜トランジスタと、前記各第2薄膜トランジスタに電気的に接続された複数の第2画素電極と、前記各第3薄膜トランジスタに電気的に接続された複数の第3画素電極と、前記各第2画素電極の駆動領域を規定する複数の第2画素と、前記各第3画素電極の駆動領域を規定する複数の第3画素と、を含み、

前記第2表示パネルは、さらに、平面視で、前記第2方向に隣り合って配置された前記第2画素電極と前記第3画素電極との間に前記第2ソース線が配置されていない第1領域を含む、

ことを特徴とする液晶表示装置。

## 【請求項 2】

前記第2表示パネルは、さらに、平面視で、前記第2方向に隣り合って配置された前記第2画素電極と前記第3画素電極との間に前記第2ソース線が配置された第2領域を含む、

ことを特徴とする請求項1に記載の液晶表示装置。

## 【請求項 3】

前記第2表示パネルにおいて、前記第1領域及び前記第2領域が、前記第2方向に交互に繰り返し配置されている、

ことを特徴とする請求項2に記載の液晶表示装置。

## 【請求項 4】

隣り合う2本の前記第1ソース線と、隣り合う2本の前記第1ゲート線とで囲まれた1つの領域に、1つの前記第1画素が含まれ、

隣り合う2本の前記第2ソース線と、隣り合う2本の前記第2ゲート線とで囲まれた1つの領域に、1つの前記第2画素と1つの前記第3画素とが含まれている、

ことを特徴とする請求項1に記載の液晶表示装置。

## 【請求項 5】

平面視で、前記第2画素は、1つ前記第1画素、又は、同一色に対応する複数の前記第1画素に重畳している、

ことを特徴とする請求項1に記載の液晶表示装置。

## 【請求項 6】

前記複数の第1画素は、赤色に対応する赤色画素と、緑色に対応する緑色画素と、青色に対応する青色画素と、を含み、

前記第2画素の面積と前記第3画素の面積とは互いに異なる、

ことを特徴とする請求項1に記載の液晶表示装置。

## 【請求項 7】

前記第1画素と前記第2画素とは、平面視で互いに重畳し、

前記第1画素の面積と前記第2画素の面積とは、互いに等しく、

前記第3画素の面積は、前記第1画素の面積の2倍に等しい、

ことを特徴とする請求項1に記載の液晶表示装置。

## 【請求項 8】

前記複数の第1画素は、赤色に対応する赤色画素と、緑色に対応する緑色画素と、青色

10

20

30

40

50

に対応する青色画素と、を含み、

前記第2表示パネルは、さらに、複数の第4薄膜トランジスタと、前記各第4薄膜トランジスタに電気的に接続された複数の第4画素電極と、前記各第4画素電極の駆動領域を規定する複数の第4画素を含み、

1つの前記第2領域に、1つの前記第2画素と1つの前記第3画素と1つの前記第4画素とが並んで配置されており、

平面視で、前記第2画素は前記赤色画素に重畠し、前記第3画素は前記緑色画素に重畠し、前記第4画素は前記青色画素に重畠している、

ことを特徴とする請求項1に記載の液晶表示装置。

**【請求項9】**

前記複数の第1画素は、赤色に対応する赤色画素と、緑色に対応する緑色画素と、青色に対応する青色画素と、白色に対応する白色画素と、を含み、

前記第2表示パネルは、さらに、複数の第4薄膜トランジスタと、複数の第5薄膜トランジスタと、前記各第4薄膜トランジスタに電気的に接続された複数の第4画素電極と、前記各第5薄膜トランジスタに電気的に接続された複数の第5画素電極と、前記各第4画素電極の駆動領域を規定する複数の第4画素と、前記各第5画素電極の駆動領域を規定する複数の第5画素とを含み、

1つの前記第2領域に、1つの前記第2画素と1つの前記第3画素と1つの前記第4画素と1つの前記第5画素とが並んで配置されており、

平面視で、前記第2画素は前記赤色画素に重畠し、前記第3画素は前記緑色画素に重畠し、前記第4画素は前記青色画素に重畠し、前記第5画素は前記白色画素に重畠している、

ことを特徴とする請求項1に記載の液晶表示装置。

**【請求項10】**

前記複数の第1画素は、赤色に対応する赤色画素と、緑色に対応する緑色画素と、青色に対応する青色画素と、を含み、

平面視で、前記第2画素は前記赤色画素に重畠し、前記第3画素は前記緑色画素と前記青色画素とに重畠している、

ことを特徴とする請求項1に記載の液晶表示装置。

**【請求項11】**

前記第1表示パネルはカラー画像を表示し、前記第2表示パネルは白黒画像を表示し、前記第2表示パネルは、前記第1表示パネルより観察者から遠い位置に配置され、

前記第1ブラックマトリクスは、平面視で前記複数の第1ソース線及び前記複数の第1ゲート線に重畠するように前記第1方向及び前記第2方向に延在し、格子状に形成されており、

前記第2ブラックマトリクスは、平面視で前記複数の第2ゲート線に重畠するように前記第2方向に延在し、ストライプ状に形成されている、

ことを特徴とする請求項1に記載の液晶表示装置。

**【請求項12】**

前記第1表示パネルはカラー画像を表示し、前記第2表示パネルは白黒画像を表示し、前記第1表示パネルは、前記第2表示パネルより観察者から遠い位置に配置され、

前記第1ブラックマトリクスは、平面視で前記複数の第1ゲート線に重畠するように前記第2方向に延在し、ストライプ状に形成されており、

前記第2ブラックマトリクスは、平面視で前記複数の第2ソース線及び前記複数の第2ゲート線に重畠するように前記第1方向及び前記第2方向に延在し、格子状に形成されている、

ことを特徴とする請求項1に記載の液晶表示装置。

**【請求項13】**

前記第1ブラックマトリクスは、平面視で前記複数の第1ソース線及び前記複数の第1ゲート線に重畠するように前記第1方向及び前記第2方向に延在し、格子状に形成されて

10

20

30

40

50

おり、

前記第2ブラックマトリクスは、平面視で前記複数の第2ソース線及び前記複数の第2ゲート線に重畳するように前記第1方向及び前記第2方向に延在し、格子状に形成されており、

前記第2ブラックマトリクスの前記第1方向に延在する部分の前記第2方向の長さは、前記第1ブラックマトリクスの前記第1方向に延在する部分の前記第2方向の長さより短く、かつ、

前記第2ブラックマトリクスの前記第2方向に延在する部分の前記第1方向の長さは、前記第1ブラックマトリクスの前記第2方向に延在する部分の前記第1方向の長さより短い、

10

ことを特徴とする請求項1に記載の液晶表示装置。

**【請求項14】**

前記第1表示パネルは、さらに、第1ブラックマトリクスを含み、

前記第2表示パネルは、さらに、第2ブラックマトリクスを含み、

前記第1ブラックマトリクスの前記第2方向に延在する部分の前記第1方向の長さと、前記第2ブラックマトリクスの前記第2方向に延在する部分の前記第1方向の長さとは、互いに異なる、

ことを特徴とする請求項1に記載の液晶表示装置。

**【請求項15】**

複数の表示パネルが重ね合わされて配置され、それぞれの前記表示パネルに画像を表示する液晶表示装置であって、

20

互いに重ね合わされて配置された第1表示パネル及び第2表示パネルを含み、

前記第1表示パネルは、第1方向に延在する複数の第1ソース線と、前記第1方向に交差する第2方向に延在する複数の第1ゲート線と、複数の第1薄膜トランジスタと、前記各第1薄膜トランジスタに電気的に接続された複数の第1画素電極と、前記各第1画素電極の駆動領域を規定する複数の第1画素と、を含み、

前記第2表示パネルは、前記第1方向に延在する複数の第2ソース線と、前記第2方向に延在する複数の第2ゲート線と、複数の第2薄膜トランジスタと、複数の第3薄膜トランジスタと、前記各第2薄膜トランジスタに電気的に接続された複数の第2画素電極と、前記各第3薄膜トランジスタに電気的に接続された複数の第3画素電極と、前記各第2画素電極の駆動領域を規定する複数の第2画素と、前記各第3画素電極の駆動領域を規定する複数の第3画素と、を含み、

30

隣り合う2本の前記第1ソース線と、隣り合う2本の前記第1ゲート線とで囲まれた1つの領域に、1つの前記第1画素が含まれ、

隣り合う2本の前記第2ソース線と、隣り合う2本の前記第2ゲート線とで囲まれた1つの領域に、1つの前記第2画素と1つの前記第3画素とが含まれている、

ことを特徴とする液晶表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

40

本発明は、液晶表示装置に関する。

**【背景技術】**

**【0002】**

従来、液晶表示装置のコントラストを向上させる技術として、2枚の表示パネルを重ね合わせて、入力映像信号に基づいて、それぞれの表示パネルに画像を表示させる技術が提案されている（例えば特許文献1参照）。具体的には例えば、前後に配置された2枚の表示パネルのうち前側（観察者側）の表示パネルにカラー画像を表示し、後側（バックライト側）の表示パネルに白黒画像を表示することによって、コントラストの向上を図るものである。また、上記液晶表示装置では、ソースドライバの数を削減してコスト低減を図るべく、画素の配置を、カラー画像表示パネルの3個の画素（赤色画素、緑色画素、青色画

50

素)に対して、白黒画像表示パネルの画素が1個となるように構成している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】WO2007/040127号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、カラー画像表示パネル1枚で構成された通常の液晶表示装置では、単色画像を表示させた場合に、本来の色を透過する画素とは異なる画素からの漏れ光により、色再現性が低下する問題が知られている。例えば、赤色の単色画像を表示させた場合に、オフ状態となる緑色画素及び青色画素から散乱等により一部の光が漏れ、この漏れ光が赤色光に混ざることにより、赤色画像の色再現性が低下する。特に低輝度の単色画像を表示させた場合には、上記漏れ光の影響が大きくなるため、色再現性が悪化する。この問題は、上記特許文献1に開示された液晶表示装置においても同様である。すなわち、上記液晶表示装置では、単色画像を表示する場合でも、カラー画像表示パネルの赤色画素、緑色画素及び青色画素に、白黒画像表示パネルを透過したバックライト光が均等に照射されるため、通常の液晶表示装置と同様に、光漏れによる色再現性の低下が起こり得る。

【0005】

本発明は、上記実情に鑑みてなされたものであり、その目的は、複数の表示パネルを重ね合わせて構成された液晶表示装置において、単色画像の色再現性の向上を図ることにある。

【課題を解決するための手段】

【0006】

上記課題を解決するために、本発明に係る液晶表示装置は、複数の表示パネルが重ね合わされて配置され、それぞれの前記表示パネルに画像を表示する液晶表示装置であって、互いに重ね合わされて配置された第1表示パネル及び第2表示パネルを含み、前記第1表示パネルは、第1方向に延在する複数の第1ソース線と、前記第1方向に交差する第2方向に延在する複数の第1ゲート線と、複数の第1薄膜トランジスタと、前記各第1薄膜トランジスタに電気的に接続された複数の第1画素電極と、前記各第1画素電極の駆動領域を規定する複数の第1画素と、を含み、前記第2表示パネルは、前記第1方向に延在する複数の第2ソース線と、前記第2方向に延在する複数の第2ゲート線と、複数の第2薄膜トランジスタと、複数の第3薄膜トランジスタと、前記各第2薄膜トランジスタに電気的に接続された複数の第2画素電極と、前記各第3薄膜トランジスタに電気的に接続された複数の第3画素電極と、前記各第2画素電極の駆動領域を規定する複数の第2画素と、前記各第3画素電極の駆動領域を規定する複数の第3画素と、を含み、前記第2表示パネルは、さらに、平面視で、前記第2方向に隣り合って配置された前記第2画素電極と前記第3画素電極との間に前記第2ソース線が配置されていない第1領域を含む、ことを特徴とする。

【0007】

本発明に係る液晶表示装置では、前記第2表示パネルは、さらに、平面視で、前記第2方向に隣り合って配置された前記第2画素電極と前記第3画素電極との間に前記第2ソース線が配置された第2領域を含んでもよい。

【0008】

本発明に係る液晶表示装置では、前記第2表示パネルにおいて、前記第1領域及び前記第2領域が、前記第2方向に交互に繰り返し配置されてもよい。

【0009】

本発明に係る液晶表示装置では、隣り合う2本の前記第1ソース線と、隣り合う2本の前記第1ゲート線とで囲まれた1つの領域に、1つの前記第1画素が含まれ、隣り合う2本の前記第2ソース線と、隣り合う2本の前記第2ゲート線とで囲まれた1つの領域に、

10

20

30

40

50

1つの前記第2画素と1つの前記第3画素とが含まれてもよい。

【0010】

本発明に係る液晶表示装置では、平面視で、前記第2画素は、1つ前記第1画素、又は、同一色に対応する複数の前記第1画素に重畠してもよい。

【0011】

本発明に係る液晶表示装置では、前記複数の第1画素は、赤色に対応する赤色画素と、緑色に対応する緑色画素と、青色に対応する青色画素と、を含み、前記第2画素の面積と前記第3画素の面積とは互いに異なってもよい。

【0012】

本発明に係る液晶表示装置では、前記第1画素と前記第2画素とは、平面視で互いに重畠し、前記第1画素の面積と前記第2画素の面積とは、互いに等しく、前記第3画素の面積は、前記第1画素の面積の2倍に等しくてもよい。

【0013】

本発明に係る液晶表示装置では、前記複数の第1画素は、赤色に対応する赤色画素と、緑色に対応する緑色画素と、青色に対応する青色画素と、を含み、前記第2表示パネルは、さらに、複数の第4薄膜トランジスタと、前記各第4薄膜トランジスタに電気的に接続された複数の第4画素電極と、前記各第4画素電極の駆動領域を規定する複数の第4画素を含み、1つの前記第2領域に、1つの前記第2画素と1つの前記第3画素と1つの前記第4画素とが並んで配置されており、平面視で、前記第2画素は前記赤色画素に重畠し、前記第3画素は前記緑色画素に重畠し、前記第4画素は前記青色画素に重畠してもよい。

【0014】

本発明に係る液晶表示装置では、前記複数の第1画素は、赤色に対応する赤色画素と、緑色に対応する緑色画素と、青色に対応する青色画素と、白色に対応する白色画素と、を含み、前記第2表示パネルは、さらに、複数の第4薄膜トランジスタと、複数の第5薄膜トランジスタと、前記各第4薄膜トランジスタに電気的に接続された複数の第4画素電極と、前記各第5薄膜トランジスタに電気的に接続された複数の第5画素電極と、前記各第4画素電極の駆動領域を規定する複数の第4画素と、前記各第5画素電極の駆動領域を規定する複数の第5画素とを含み、1つの前記第2領域に、1つの前記第2画素と1つの前記第3画素と1つの前記第4画素と1つの前記第5画素とが並んで配置されており、平面視で、前記第2画素は前記赤色画素に重畠し、前記第3画素は前記緑色画素に重畠し、前記第4画素は前記青色画素に重畠し、前記第5画素は前記白色画素に重畠してもよい。

【0015】

本発明に係る液晶表示装置では、前記複数の第1画素は、赤色に対応する赤色画素と、緑色に対応する緑色画素と、青色に対応する青色画素と、を含み、平面視で、前記第2画素は前記赤色画素に重畠し、前記第3画素は前記緑色画素と前記青色画素とに重畠してもよい。

【0016】

本発明に係る液晶表示装置では、前記第1表示パネルはカラー画像を表示し、前記第2表示パネルは白黒画像を表示し、前記第2表示パネルは、前記第1表示パネルより観察者から遠い位置に配置され、前記第1ブラックマトリクスは、平面視で前記複数の第1ソース線及び前記複数の第1ゲート線に重畠するように前記第1方向及び前記第2方向に延在し、格子状に形成されており、前記第2ブラックマトリクスは、平面視で前記複数の第2ゲート線に重畠するように前記第2方向に延在し、ストライプ状に形成されてもよい。

【0017】

本発明に係る液晶表示装置では、前記第1表示パネルはカラー画像を表示し、前記第2表示パネルは白黒画像を表示し、前記第1表示パネルは、前記第2表示パネルより観察者から遠い位置に配置され、前記第1ブラックマトリクスは、平面視で前記複数の第1ゲート線に重畠するように前記第2方向に延在し、ストライプ状に形成されており、前記第2ブラックマトリクスは、平面視で前記複数の第2ソース線及び前記複数の第2ゲート線に重畠するように前記第1方向及び前記第2方向に延在し、格子状に形成されてもよい。

10

20

30

40

50

## 【0018】

本発明に係る液晶表示装置では、前記第1ブラックマトリクスは、平面視で前記複数の第1ソース線及び前記複数の第1ゲート線に重畠するように前記第1方向及び前記第2方向に延在し、格子状に形成されており、前記第2ブラックマトリクスは、平面視で前記複数の第2ソース線及び前記複数の第2ゲート線に重畠するように前記第1方向及び前記第2方向に延在し、格子状に形成されており、前記第2ブラックマトリクスの前記第1方向に延在する部分の前記第2方向の長さは、前記第1ブラックマトリクスの前記第1方向に延在する部分の前記第2方向の長さより短く、かつ、前記第2ブラックマトリクスの前記第2方向に延在する部分の前記第1方向の長さは、前記第1ブラックマトリクスの前記第2方向に延在する部分の前記第1方向の長さより短くてもよい。

10

## 【0019】

本発明に係る液晶表示装置では、前記第1表示パネルは、さらに、第1ブラックマトリクスを含み、前記第2表示パネルは、さらに、第2ブラックマトリクスを含み、前記第1ブラックマトリクスの前記第2方向に延在する部分の前記第1方向の長さと、前記第2ブラックマトリクスの前記第2方向に延在する部分の前記第1方向の長さとは、互いに異なってもよい。

20

## 【0020】

また上記課題を解決するために、本発明に係る液晶表示装置は、複数の表示パネルが重ね合わされて配置され、それぞれの前記表示パネルに画像を表示する液晶表示装置であって、互いに重ね合わされて配置された第1表示パネル及び第2表示パネルを含み、前記第1表示パネルは、第1方向に延在する複数の第1ソース線と、前記第1方向に交差する第2方向に延在する複数の第1ゲート線と、複数の第1薄膜トランジスタと、前記各第1薄膜トランジスタに電気的に接続された複数の第1画素電極と、前記各第1画素電極の駆動領域を規定する複数の第1画素と、を含み、前記第2表示パネルは、前記第1方向に延在する複数の第2ソース線と、前記第2方向に延在する複数の第2ゲート線と、複数の第2薄膜トランジスタと、複数の第3薄膜トランジスタと、前記各第2薄膜トランジスタに電気的に接続された複数の第2画素電極と、前記各第3薄膜トランジスタに電気的に接続された複数の第3画素電極と、前記各第2画素電極の駆動領域を規定する複数の第2画素と、前記各第3画素電極の駆動領域を規定する複数の第3画素と、を含み、隣り合う2本の前記第1ソース線と、隣り合う2本の前記第1ゲート線とで囲まれた1つの領域に、1つの前記第1画素が含まれ、隣り合う2本の前記第2ソース線と、隣り合う2本の前記第2ゲート線とで囲まれた1つの領域に、1つの前記第2画素と1つの前記第3画素とが含まれている、ことを特徴とする。

30

## 【発明の効果】

## 【0021】

本発明に係る液晶表示装置によれば、複数の表示パネルを重ね合わせて構成された液晶表示装置において、単色画像の色再現性の向上を図ることができる。

## 【図面の簡単な説明】

## 【0022】

40

【図1】本実施形態に係る液晶表示装置の概略構成を示す斜視図である。

【図2】上記液晶表示装置の概略構成を模式的に示す図である。

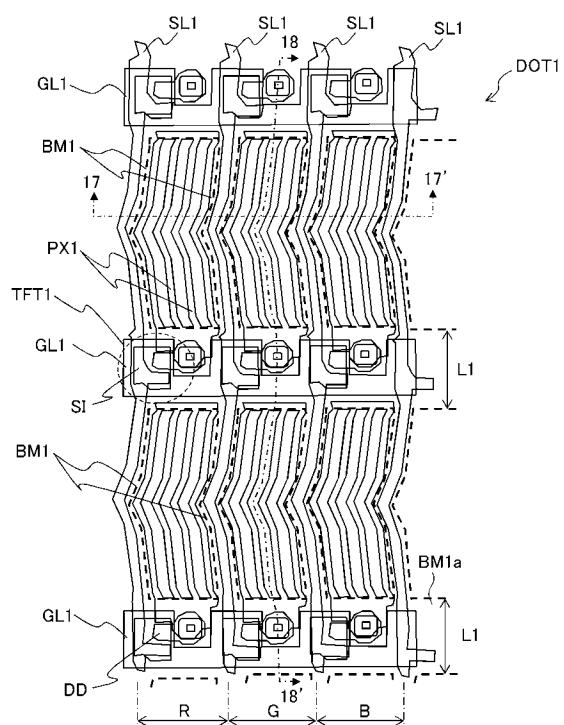

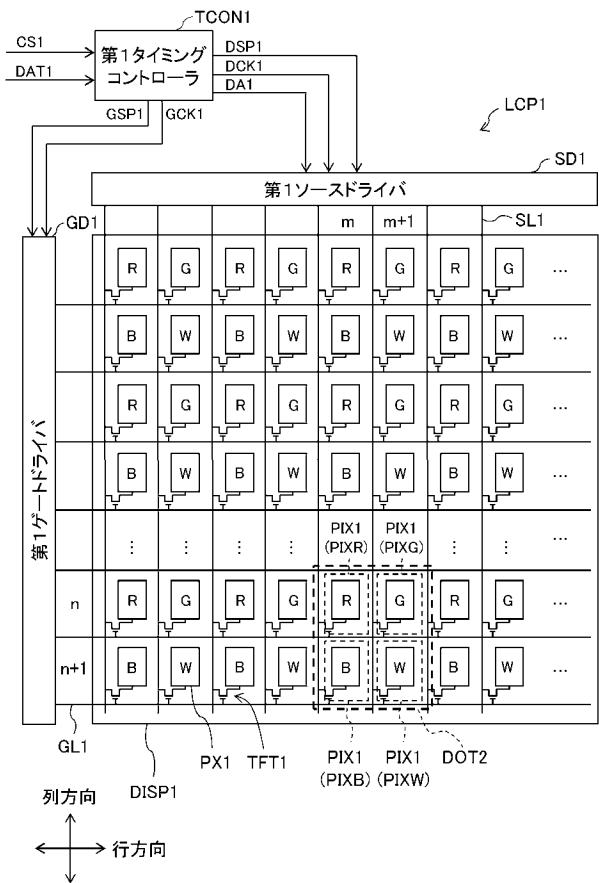

【図3】実施形態1に係る前側の表示パネルの概略構成を示す平面図である。

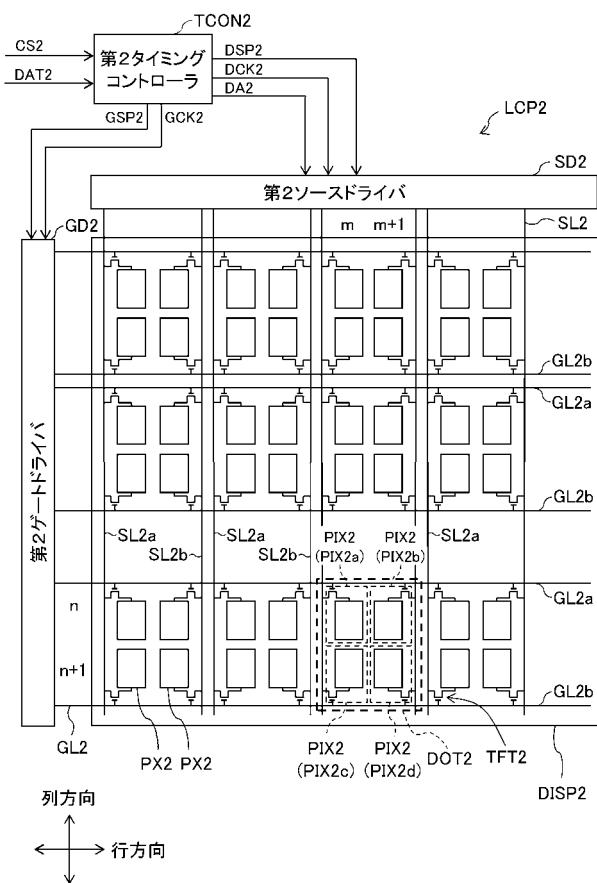

【図4】実施形態1に係る後側の表示パネルの概略構成を示す平面図である。

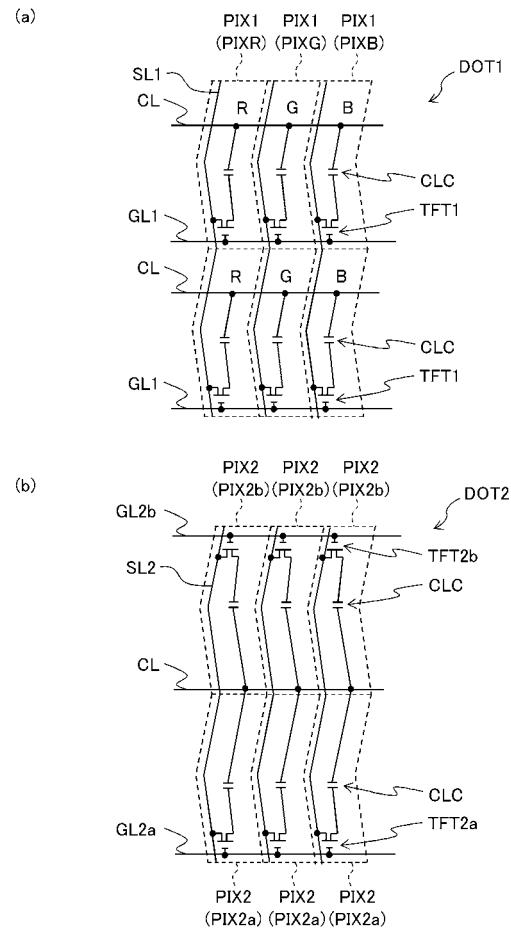

【図5】図3及び図4の5-5'断面図である。

【図6】実施形態1に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

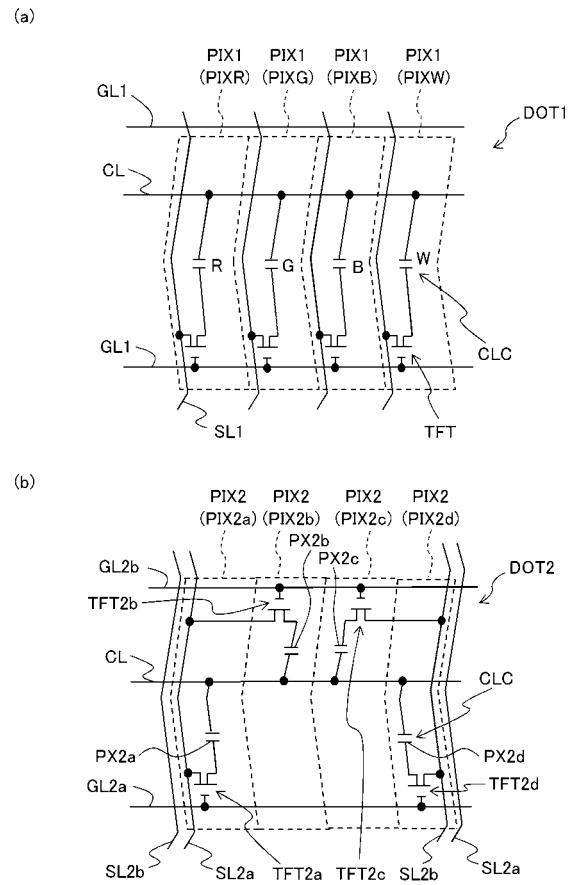

【図7】図6に対応する画素の具体的な構成を示す平面図である。

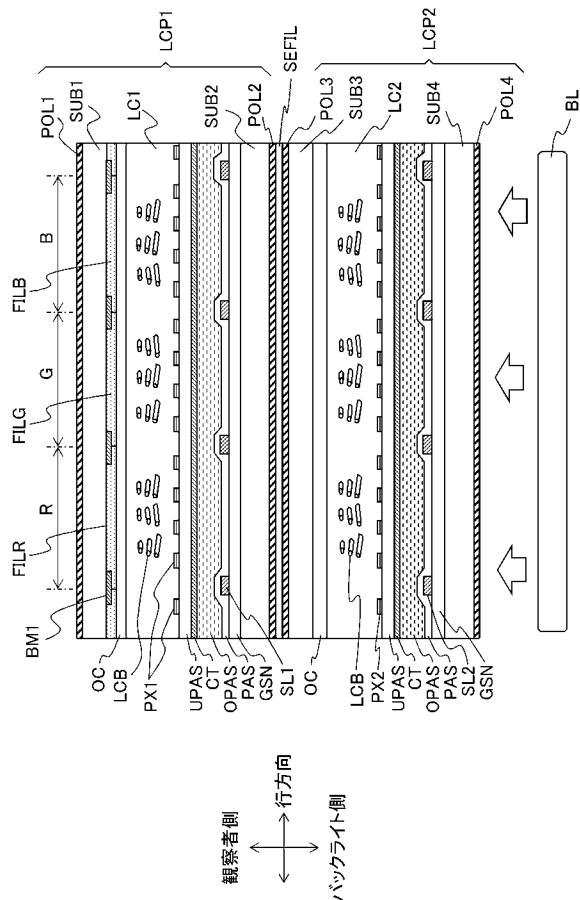

【図8】図7の8-8'切断線における断面図である。

【図9】図7の9-9'切断線における断面図である。

【図10】実施形態1に係る液晶表示装置における画像表示(黒色画像)の一例を示す模

50

式図である。

【図11】実施形態1に係る前側の表示パネル及び後側の表示パネルのドライバの構成を示す図である。

【図12】実施形態2に係る前側の表示パネルの概略構成を示す平面図である。

【図13】実施形態2に係る後側の表示パネルの概略構成を示す平面図である。

【図14】実施形態2に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

【図15】図14(a)に示す前側の表示パネルの画素の具体的な構成を示す平面図である。

【図16】図14(b)に示す後側の表示パネルの画素の具体的な構成を示す平面図である。

10

【図17】図15及び図16の17-17'切断線における断面図である。

【図18】図15及び図16の18-18'切断線における断面図である。

【図19】実施形態3に係る前側の表示パネルの概略構成を示す平面図である。

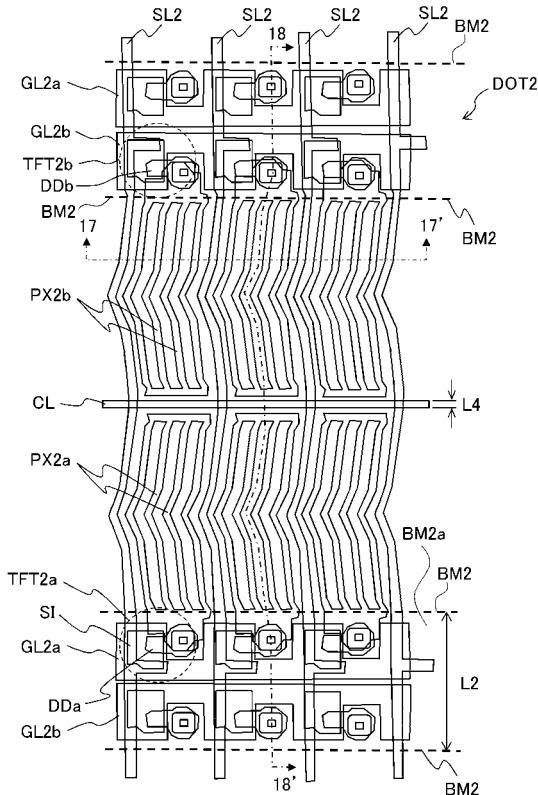

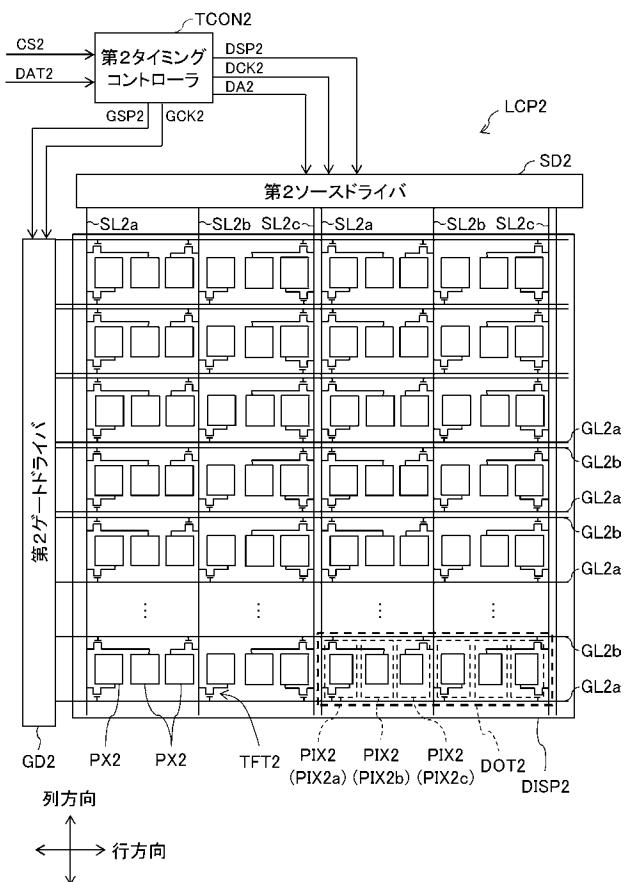

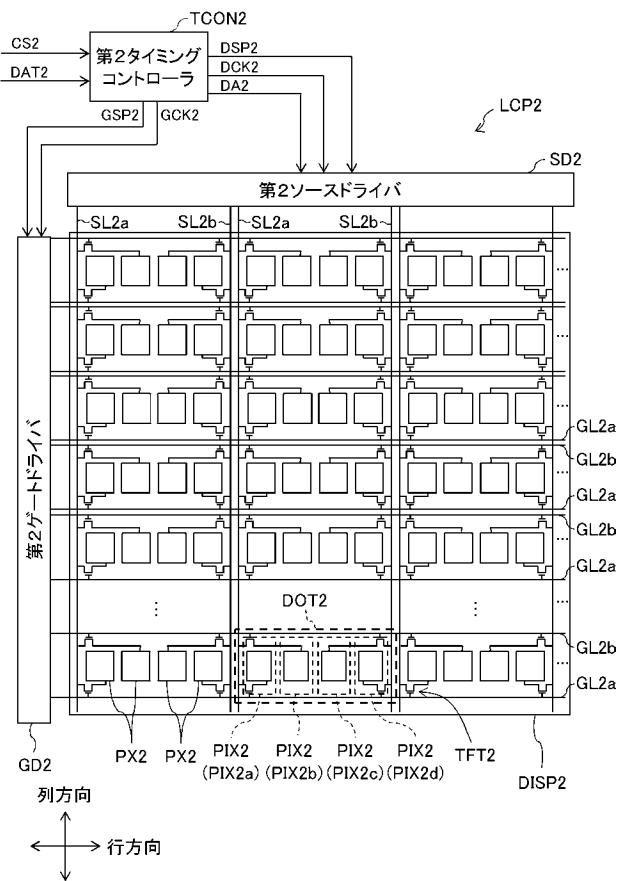

【図20】実施形態3に係る後側の表示パネルの概略構成を示す平面図である。

【図21】実施形態3に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

【図22】図21に対応する画素の具体的な構成を示す平面図である。

【図23】図22の23-23'切断線における断面図である。

【図24】図22の24-24'切断線における断面図である。

20

【図25】実施形態3に係る前側の表示パネル及び後側の表示パネルのドライバの構成を示す図である。

【図26】実施形態4に係る前側の表示パネルの概略構成を示す平面図である。

【図27】実施形態4に係る後側の表示パネルの概略構成を示す平面図である。

【図28】図26及び図27の28-28'断面図である。

【図29】実施形態4に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

【図30】図29に対応する画素の具体的な構成を示す平面図である。

【図31】図30の31-31'切断線における断面図である。

【図32】図30の32-32'切断線における断面図である。

30

【図33】実施形態4に係る前側の表示パネル及び後側の表示パネルのドライバの構成を示す図である。

【図34】実施形態5に係る前側の表示パネルの画素及び後側の表示パネルの画素の具体的な構成を示す平面図である。

【図35】図34の35-35'切断線における断面図である。

【図36】実施形態6に係る前側の表示パネルの概略構成を示す平面図である。

【図37】実施形態6に係る後側の表示パネルの概略構成を示す平面図である。

【図38】実施形態6に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

【図39】図38(a)に示す前側の表示パネルの画素の具体的な構成を示す平面図である。

40

【図40】図38(b)に示す後側の表示パネルの画素の具体的な構成を示す平面図である。

【図41】図39及び図40の41-41'切断線における断面図である。

【図42】実施形態6に係る前側の表示パネル及び後側の表示パネルのドライバの構成を示す図である。

【図43】実施形態7に係る後側の表示パネルの概略構成を示す平面図である。

【図44】実施形態7に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

【図45】図44に対応する画素の具体的な構成を示す平面図である。

50

【図46】図45の46-46'切断線における断面図である。

【図47】実施形態7に係る前側の表示パネル及び後側の表示パネルのドライバの構成を示す図である。

【図48】実施形態8に係る後側の表示パネルの概略構成を示す平面図である。

【図49】実施形態8に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

【図50】図49(b)に示す後側の表示パネルの画素の具体的な構成を示す平面図である。

【図51】実施形態8に係る前側の表示パネル及び後側の表示パネルのドライバの構成を示す図である。

【図52】実施形態9に係る前側の表示パネルの概略構成を示す平面図である。

【図53】実施形態9に係る後側の表示パネルの概略構成を示す平面図である。

【図54】実施形態9に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

【図55】実施形態9に係る前側の表示パネル及び後側の表示パネルのドライバの構成を示す図である。

【図56】実施形態10に係る前側の表示パネルの概略構成を示す平面図である。

【図57】実施形態10に係る後側の表示パネルの概略構成を示す平面図である。

【図58】実施形態10に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

【図59】実施形態11に係る前側の表示パネルの概略構成を示す平面図である。

【図60】実施形態11に係る後側の表示パネルの概略構成を示す平面図である。

【図61】実施形態11に係る前側の表示パネルの画素と後側の表示パネルの画素との関係を示す平面図である。

【図62】実施形態12に係る前側の表示パネルの画素及び後側の表示パネルの画素の具体的な構成を示す平面図である。

【図63】図62の62-62'切断線における断面図である。

【図64】他の実施形態に係る後側の表示パネルの概略構成を示す平面図である。

【図65】互いに重ね合わせて配置される2枚のパネルにおける、ブラックマトリクスと開口部との関係を模式的に示す図である。

【図66】互いに重ね合わせて配置される2枚のパネルにおける、ブラックマトリクスと開口部との関係を模式的に示す図である。

【発明を実施するための形態】

【0023】

本発明の実施形態について、図面を用いて以下に説明する。以下に示す各実施形態に係る液晶表示装置は、画像を表示する複数の表示パネルと、それぞれの表示パネルを駆動する複数の駆動回路（複数のソースドライバ、複数のゲートドライバ）と、それぞれの駆動回路を制御する複数のタイミングコントローラと、外部から入力される入力映像信号に対して画像処理を行い、それぞれのタイミングコントローラに画像データを出力する画像処理部と、複数の表示パネルに背面側から光を照射するバックライトと、を含んでいる。表示パネルの数は限定されず2枚以上であればよい。また複数の表示パネルは、観察者側から見て前後方向に互いに重ね合わせて配置されており、それぞれが画像を表示する。以下では、2枚の表示パネルを備える液晶表示装置LCDを例に挙げて説明する。

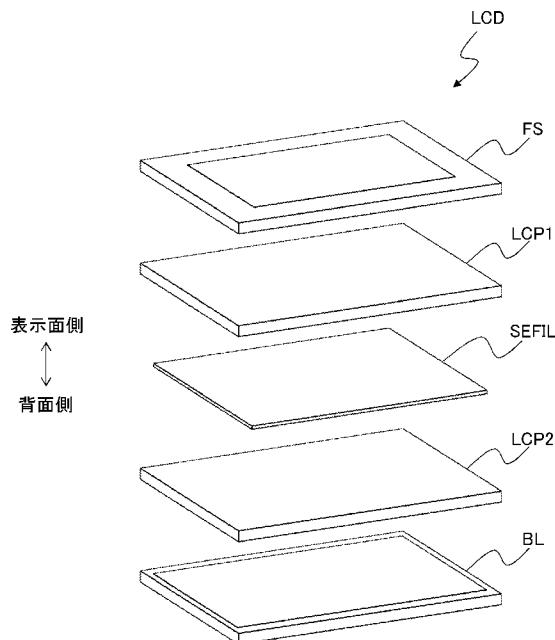

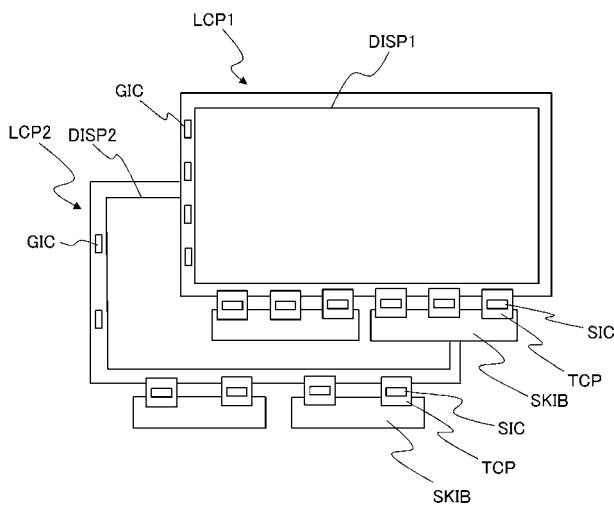

【0024】

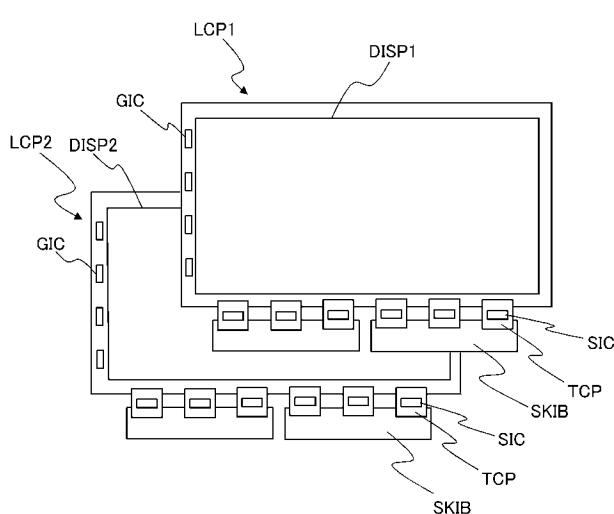

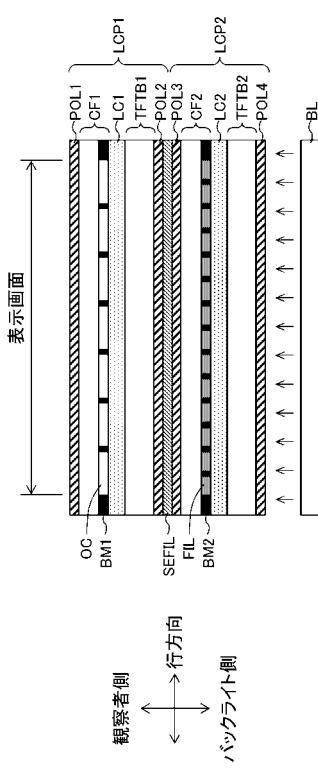

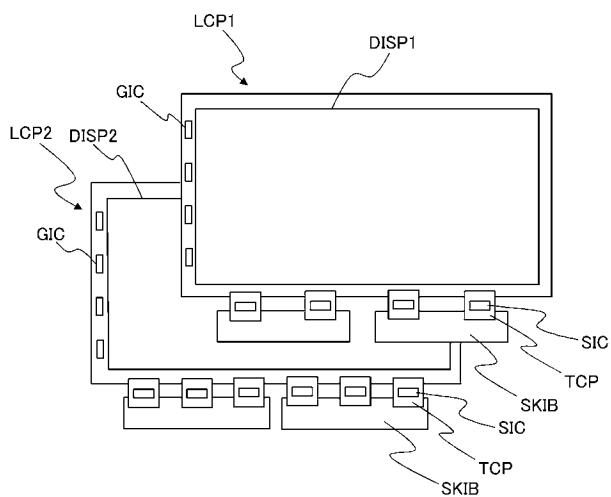

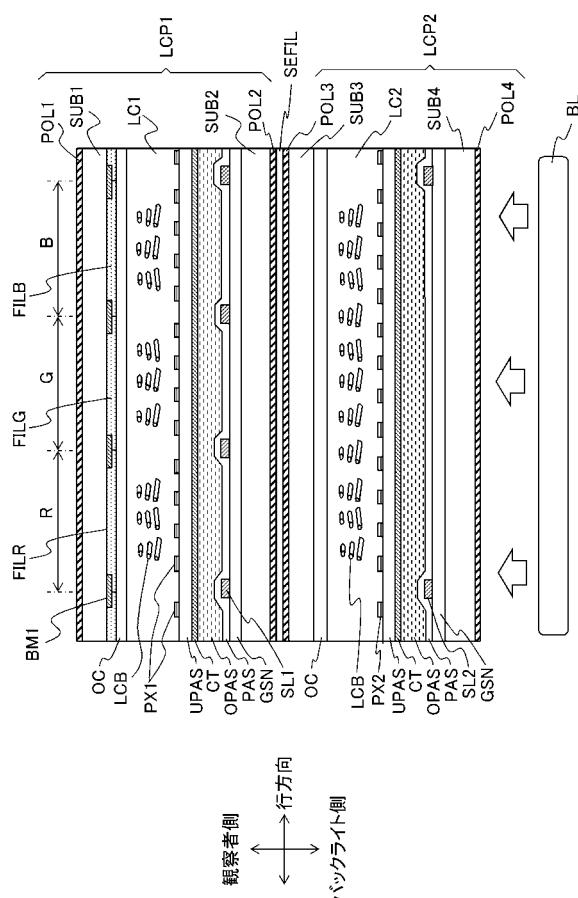

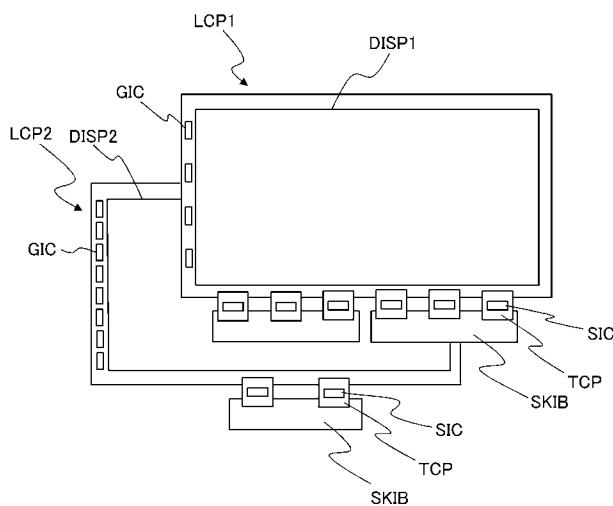

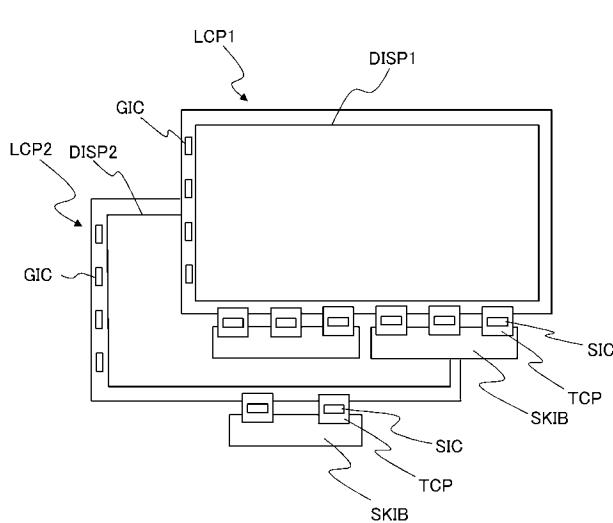

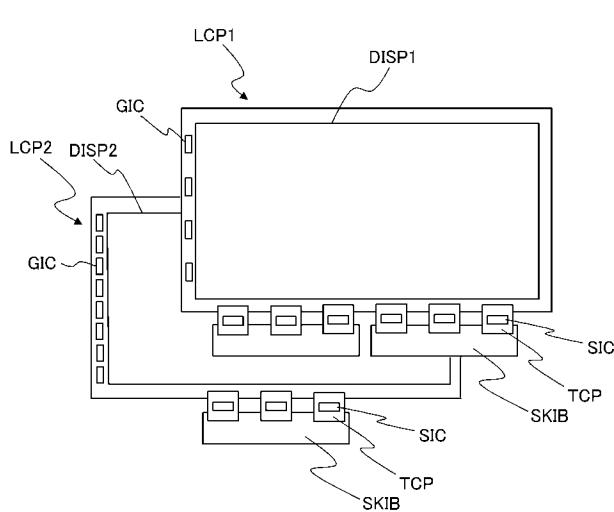

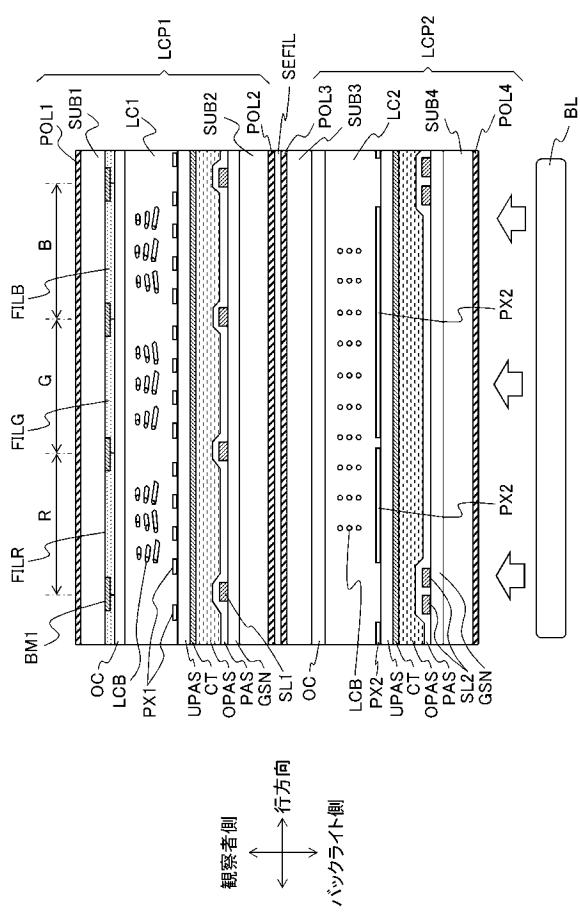

図1は、本実施形態に係る液晶表示装置LCDの概略構成を示す斜視図である。図1に示すように、液晶表示装置LCDは、観察者に近い位置（前側）に配置された表示パネルLCD1と、表示パネルLCD1より観察者から遠い位置（後側）に配置された表示パネルLCD2と、表示パネルLCD1及び表示パネルLCD2を貼り合わせる接着層SEFILと、表示パネルLCD2の背面側に配置されたバックライトBLと、表示面側から表示パネルLCD1及び表示パネルLCD2を覆うフロントシャーシFSとを含んでいる。

10

20

30

40

50

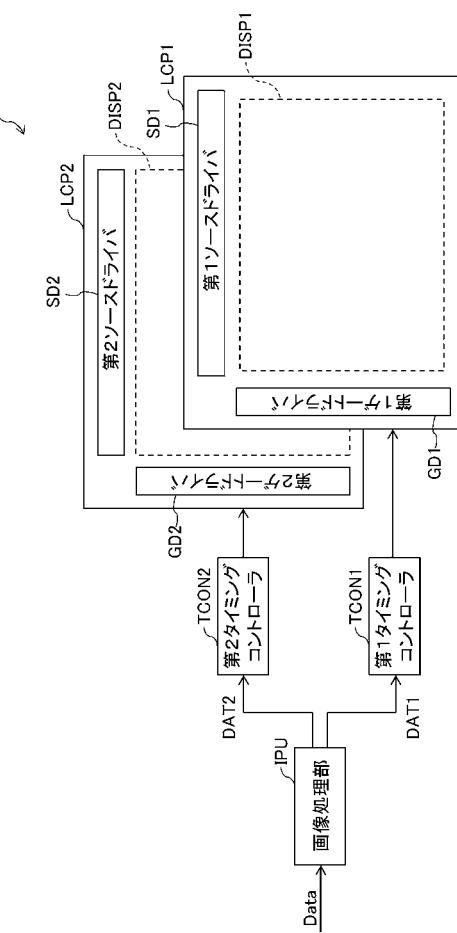

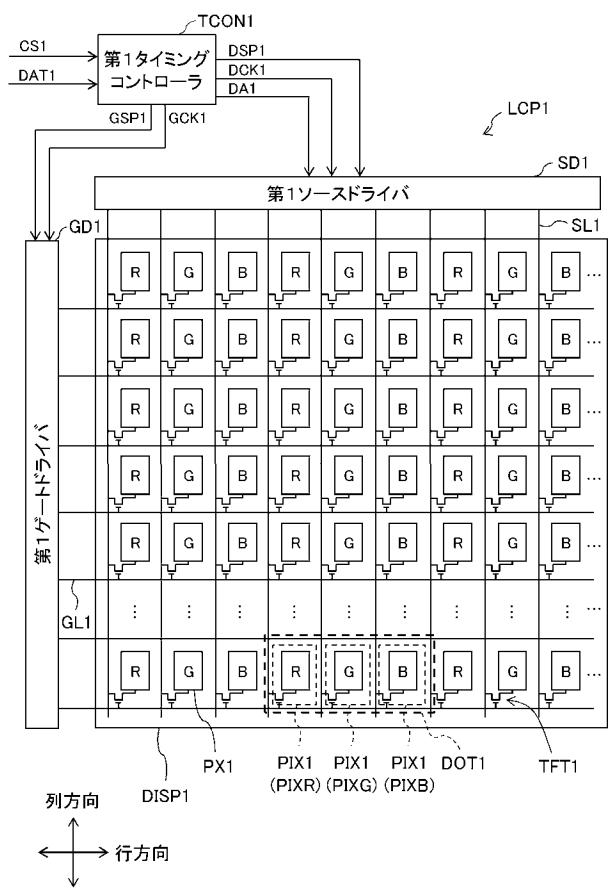

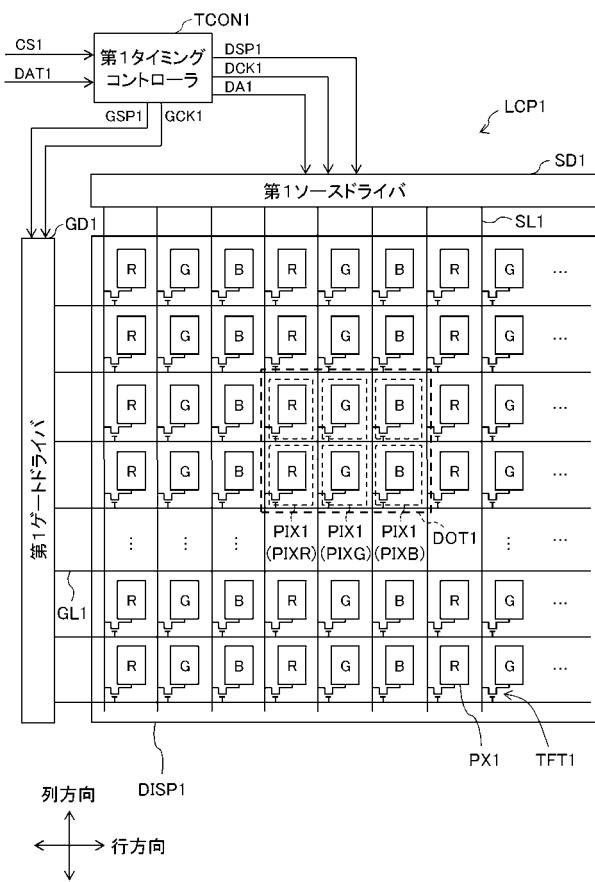

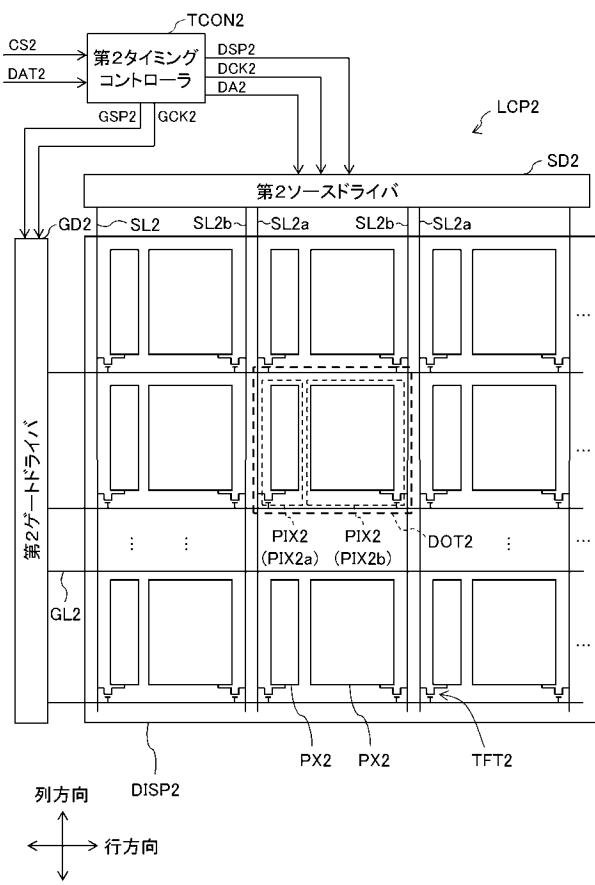

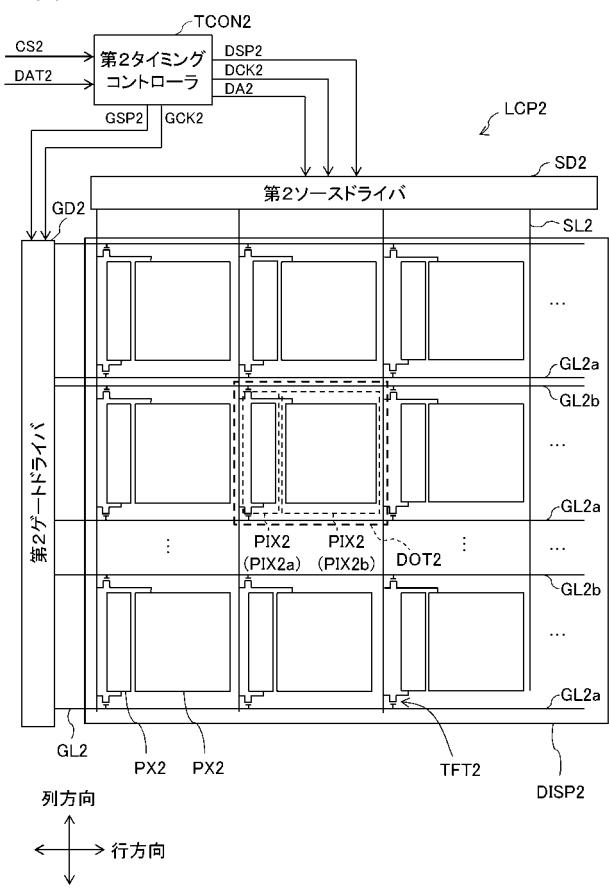

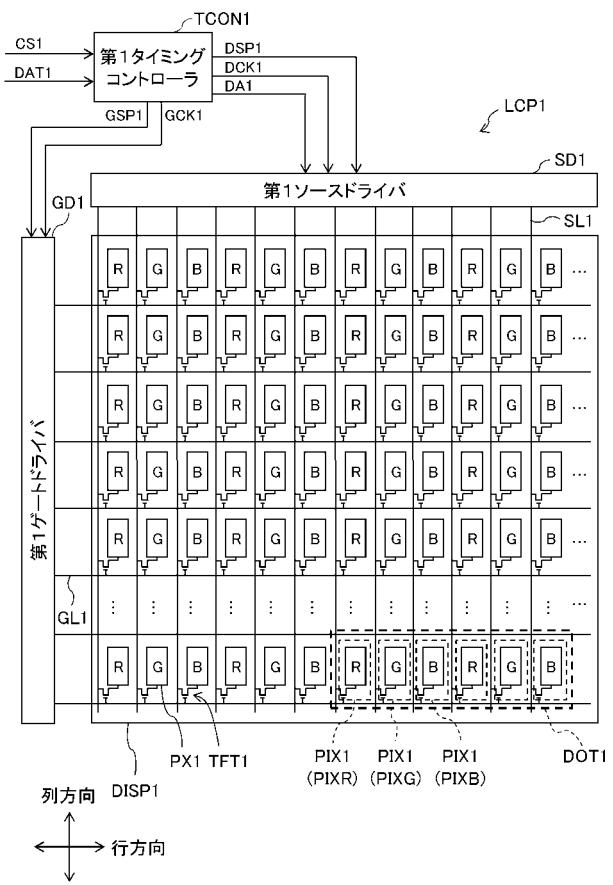

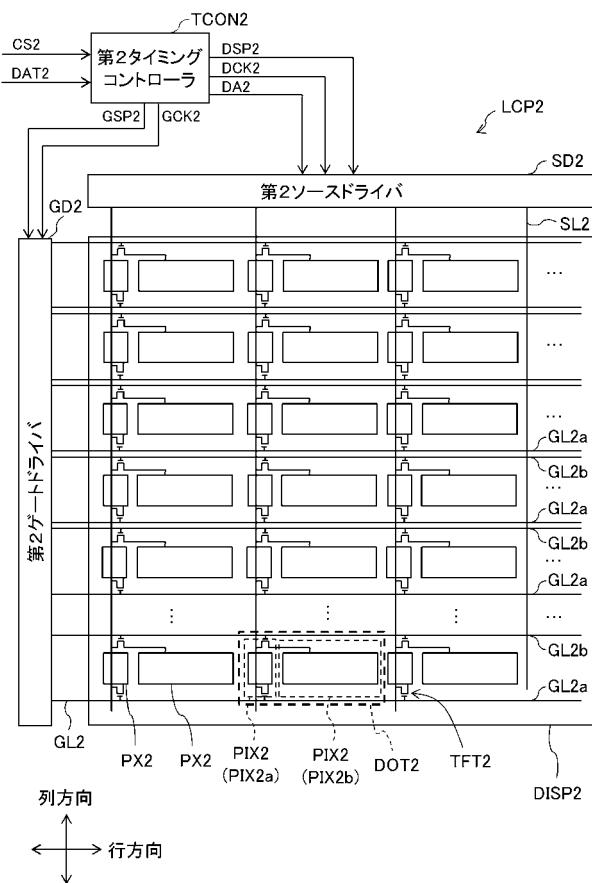

## 【0025】

図2は、本実施形態に係る液晶表示装置LCDの概略構成を模式的に示す図である。図2に示すように、表示パネルLCP1は、第1ソースドライバSD1と第1ゲートドライバGDIとを含み、表示パネルLCP2は、第2ソースドライバSD2と第2ゲートドライバGDIとを含んでいる。また液晶表示装置LCDは、第1ソースドライバSD1及び第1ゲートドライバGDIを制御する第1タイミングコントローラTCON1と、第2ソースドライバSD2及び第2ゲートドライバGDIを制御する第2タイミングコントローラTCON2と、第1タイミングコントローラTCON1及び第2タイミングコントローラTCON2に画像データを出力する画像処理部IPUと、を含んでいる。例えば、表示パネルLCP1は入力映像信号に応じたカラー画像を第1画像表示領域DISP1に表示し、表示パネルLCP2は入力映像信号に応じた白黒画像を第2画像表示領域DISP2に表示する。画像処理部IPUは、外部のシステム(図示せず)から送信された入力映像信号Dataを受信し、周知の画像処理を実行した後、第1タイミングコントローラTCON1に第1画像データDAT1を出力し、第2タイミングコントローラTCON2に第2画像データDAT2を出力する。また画像処理部IPUは、第1タイミングコントローラTCON1及び第2タイミングコントローラTCON2に同期信号等の制御信号(図2では省略)を出力する。第1画像データDAT1は例えばカラー画像表示用の画像データであり、第2画像データDAT2は例えば白黒画像表示用の画像データである。尚、液晶表示装置LCDは、表示パネルLCP1が白黒画像を第1画像表示領域DISP1に表示し、表示パネルLCP2がカラー画像を第2画像表示領域DISP2に表示する構成であってもよい。

10

20

20

## 【0026】

## [実施形態1]

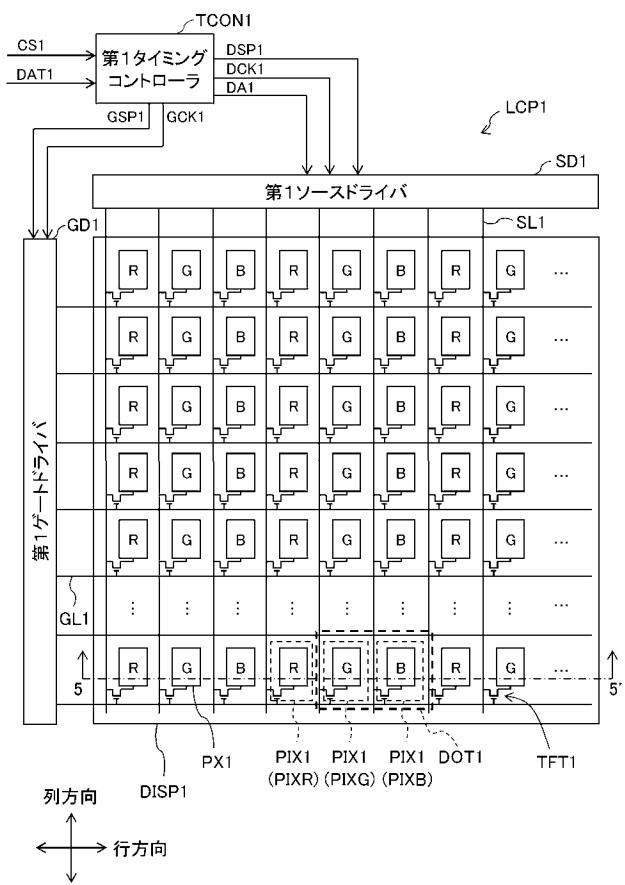

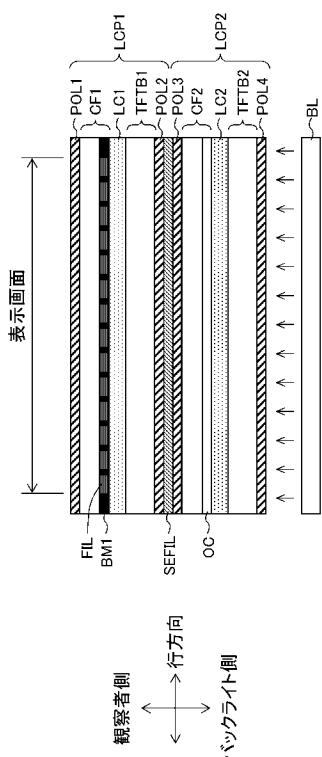

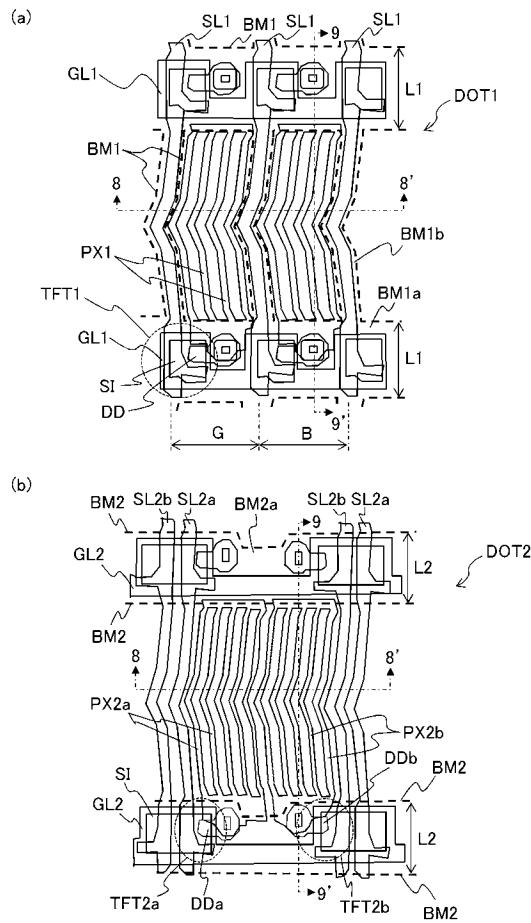

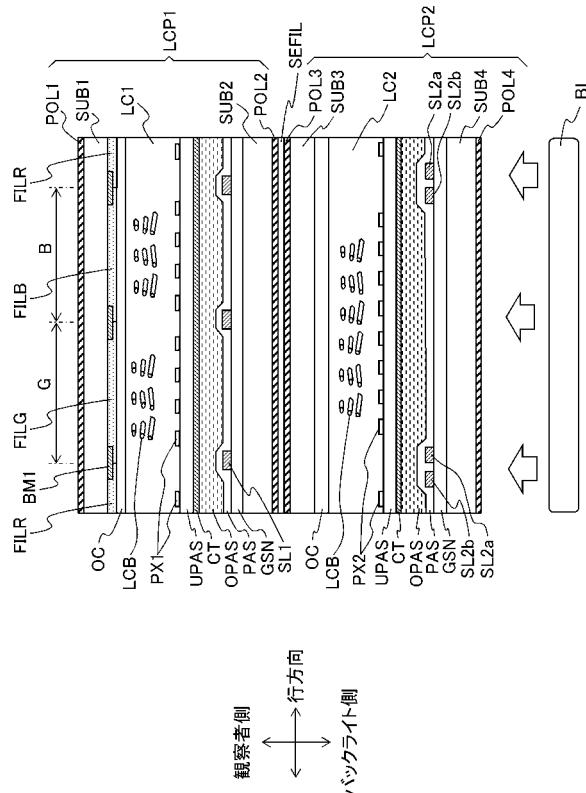

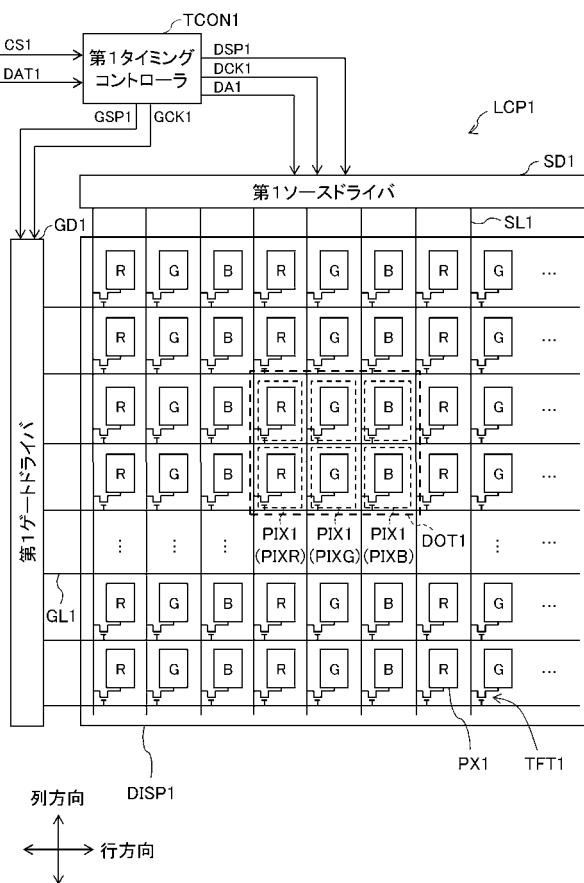

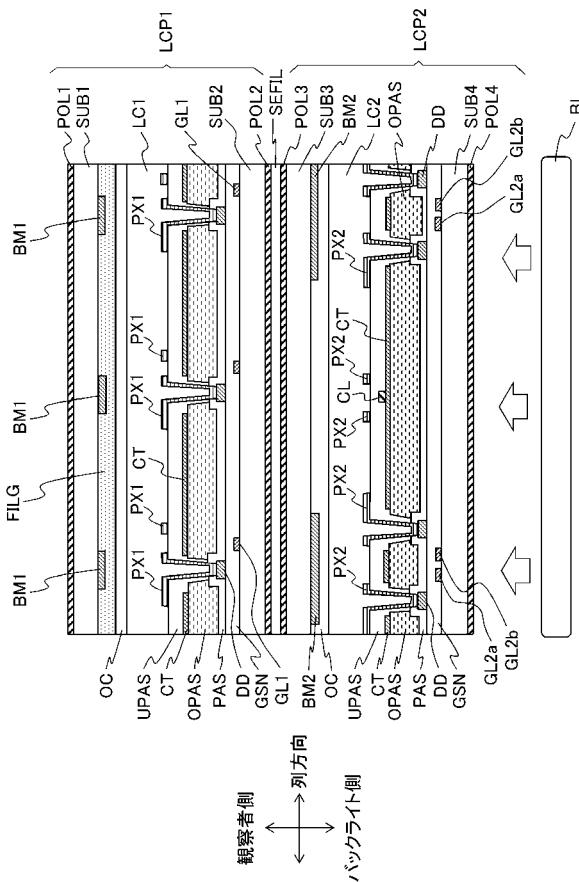

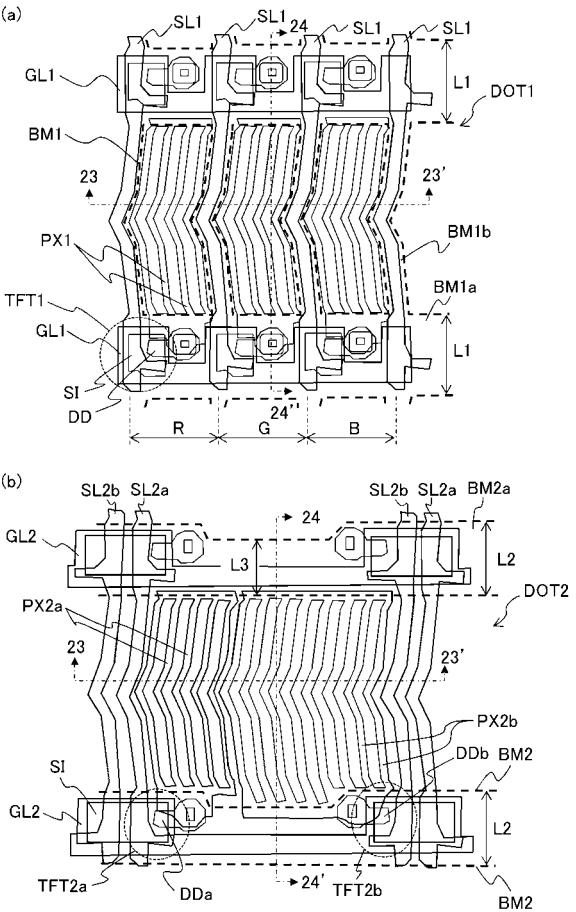

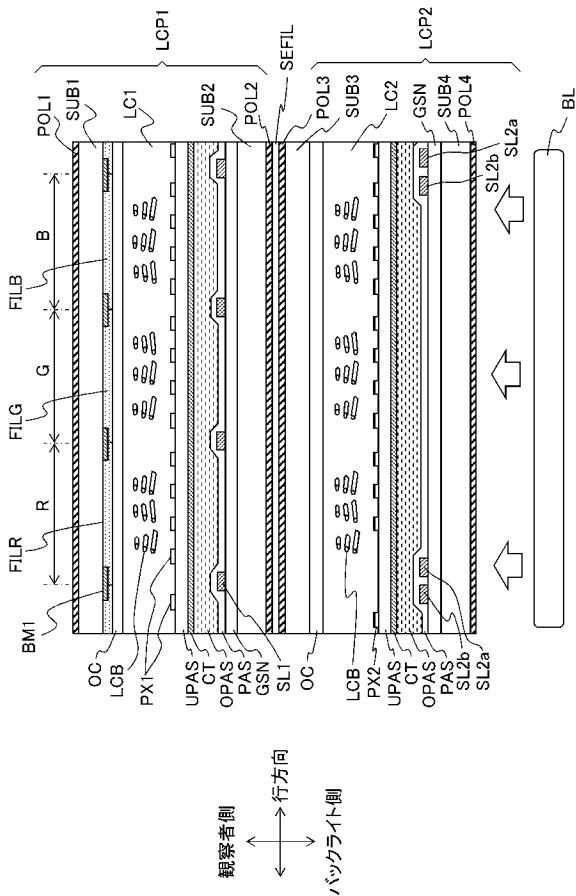

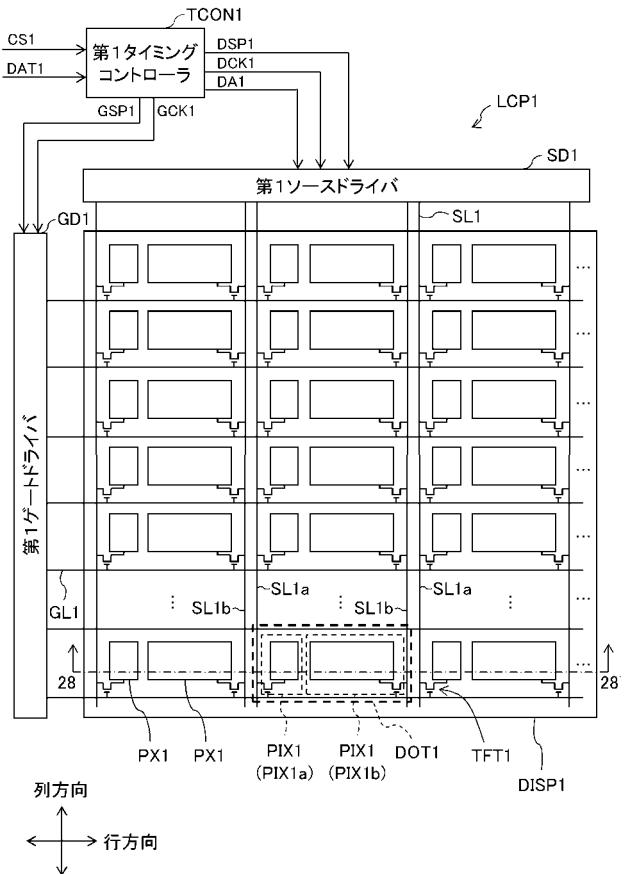

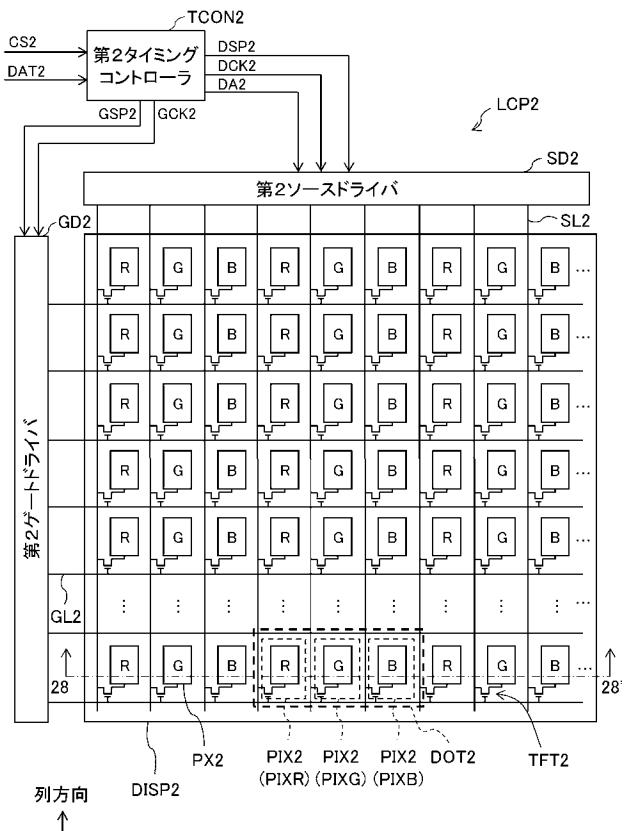

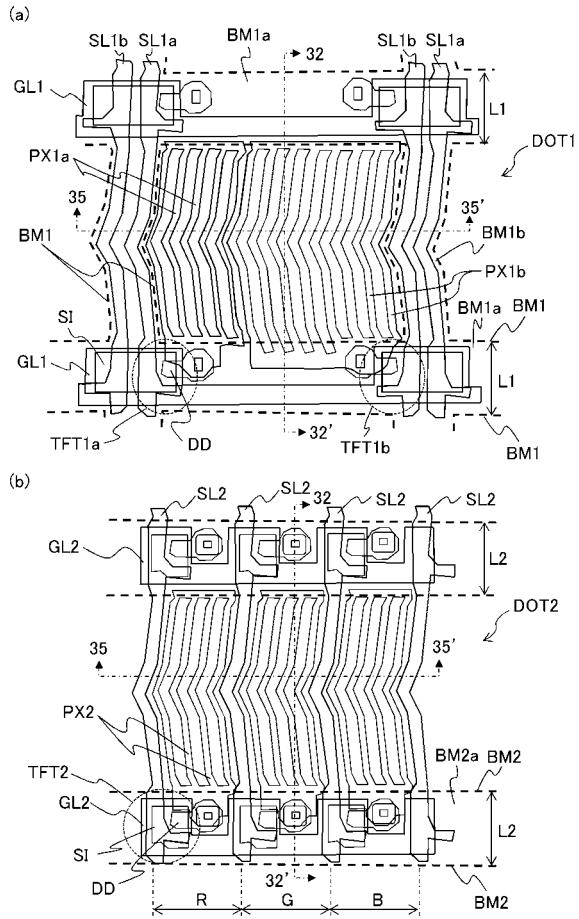

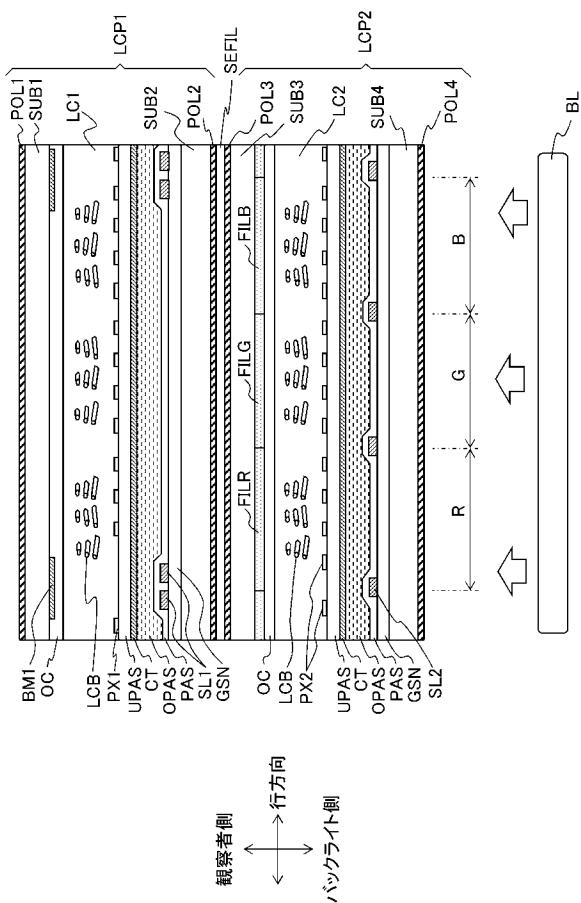

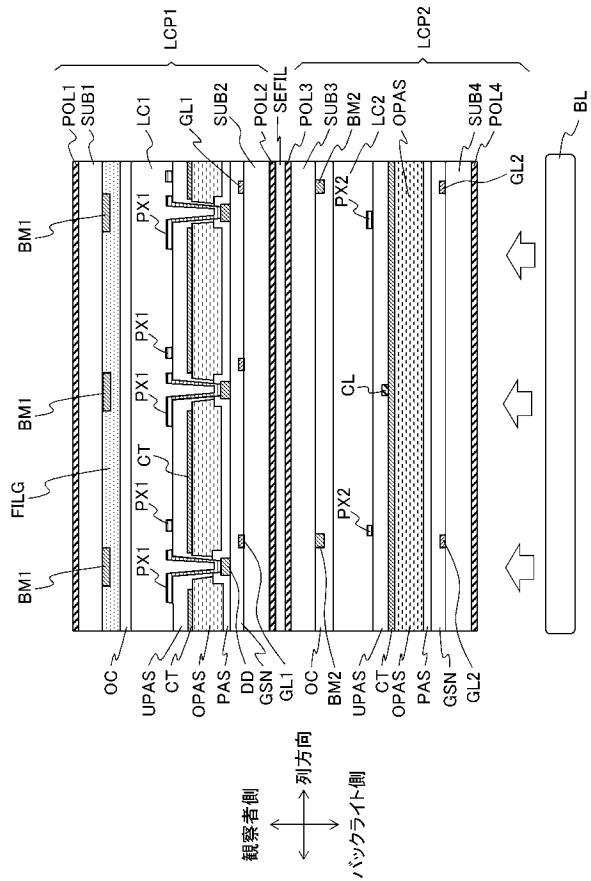

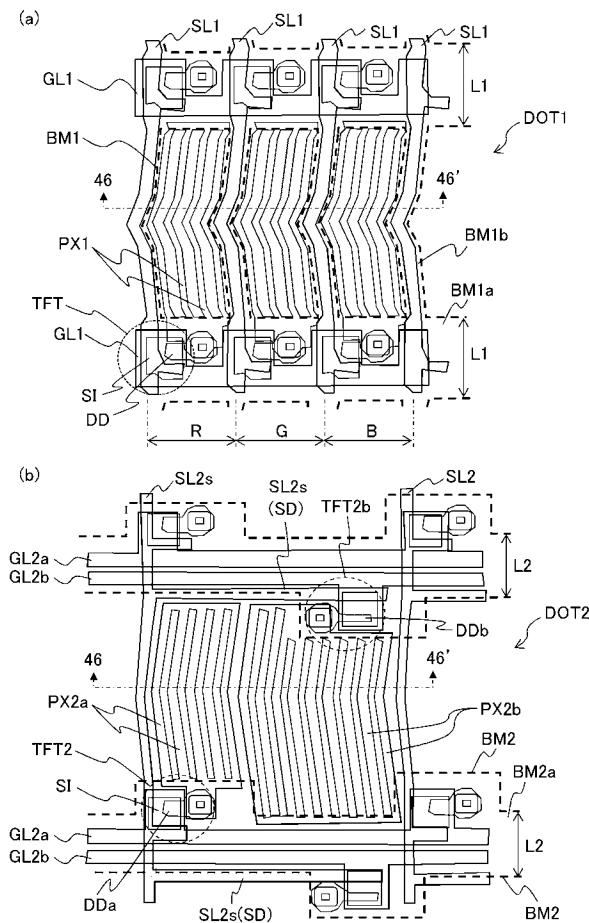

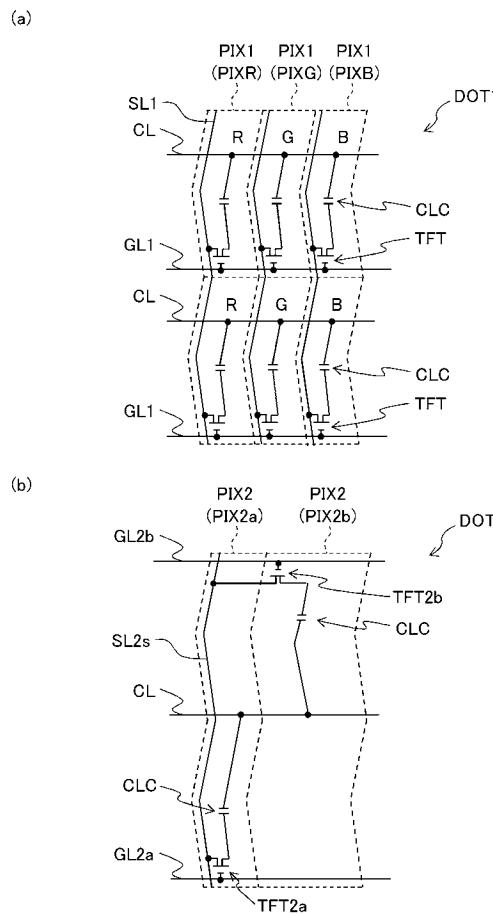

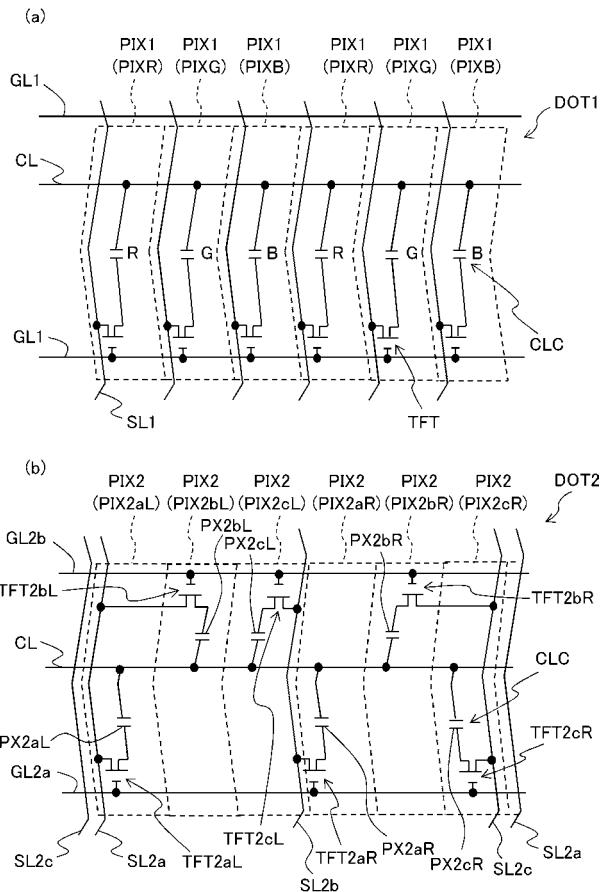

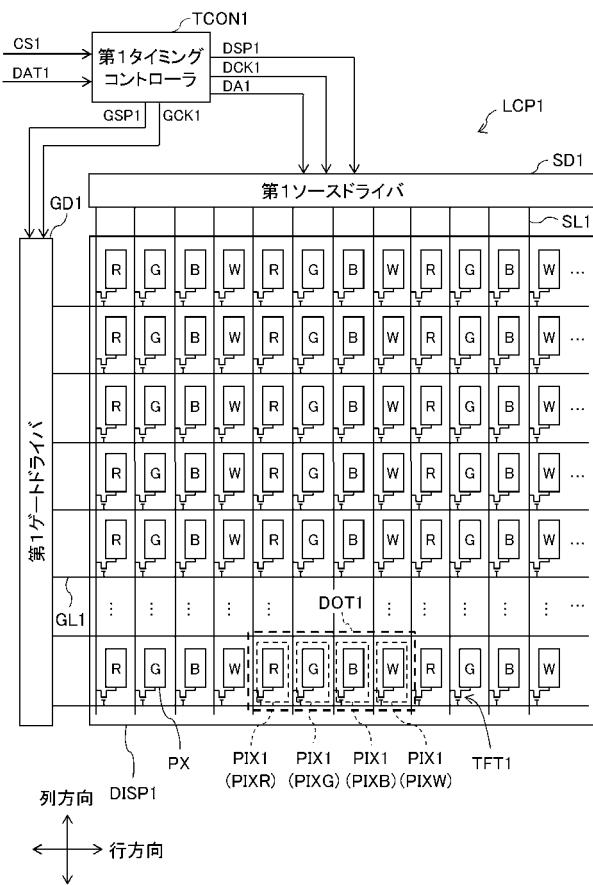

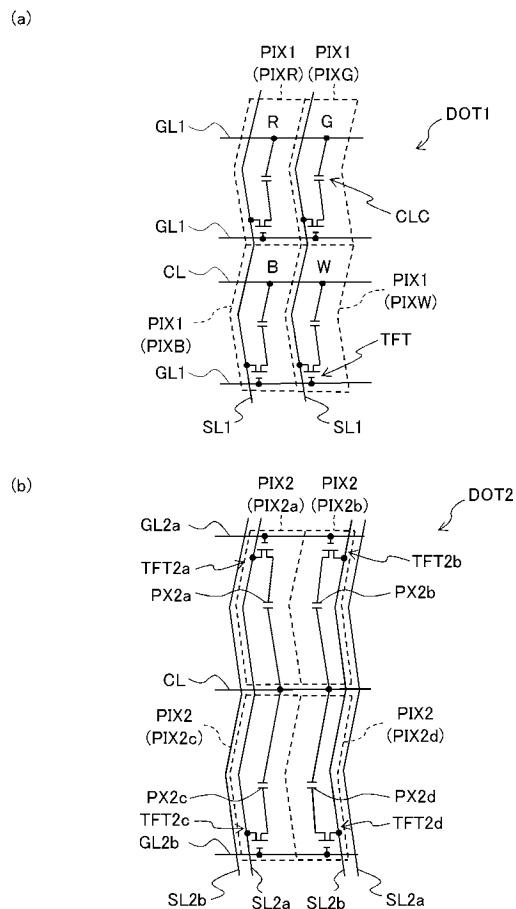

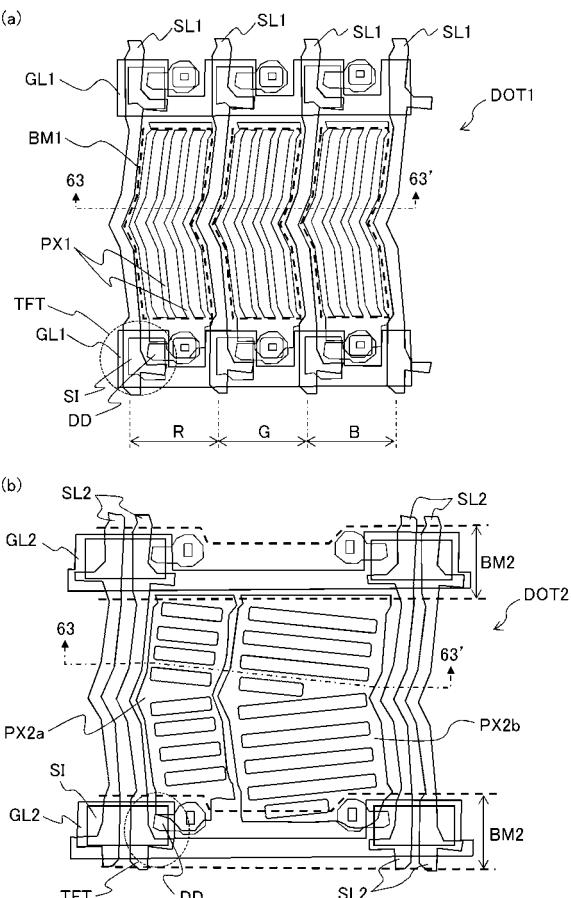

図3は実施形態1に係る表示パネルLCP1の概略構成を示す平面図であり、図4は実施形態1に係る表示パネルLCP2の概略構成を示す平面図である。図5は、図3及び図4の5-5'切断線における断面図である。

30

## 【0027】

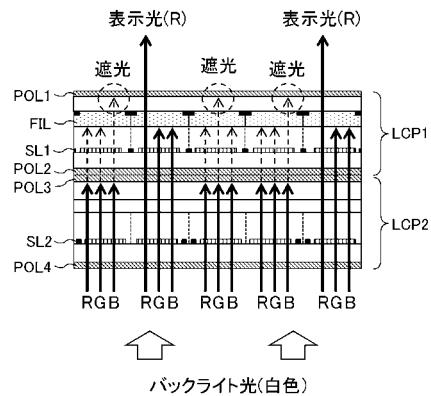

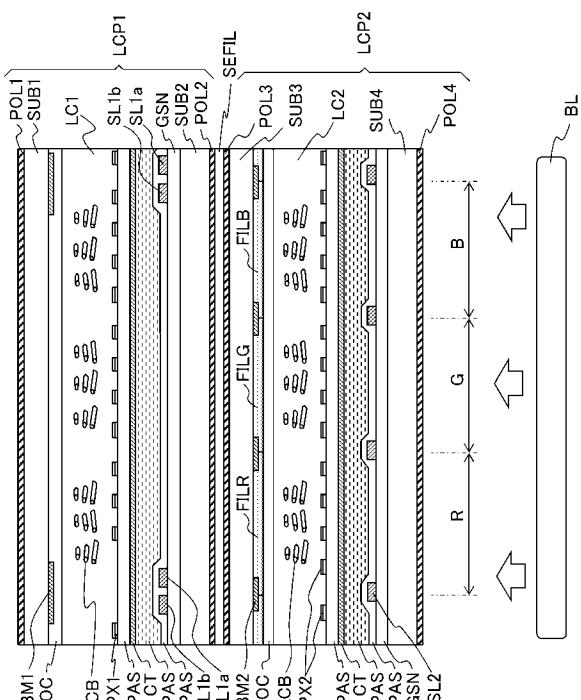

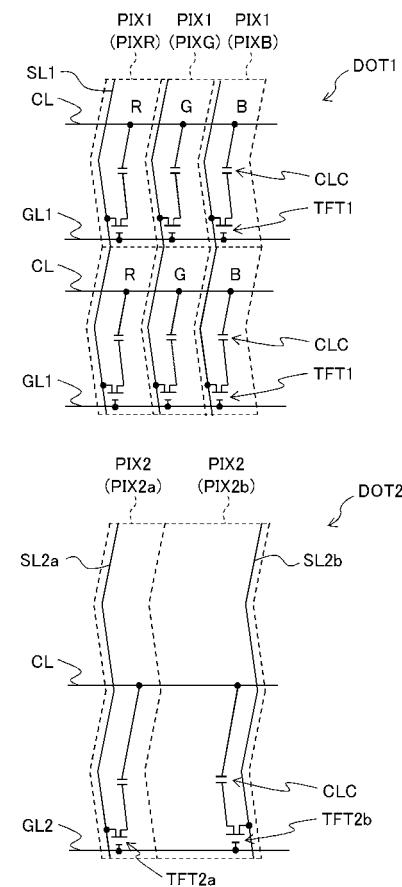

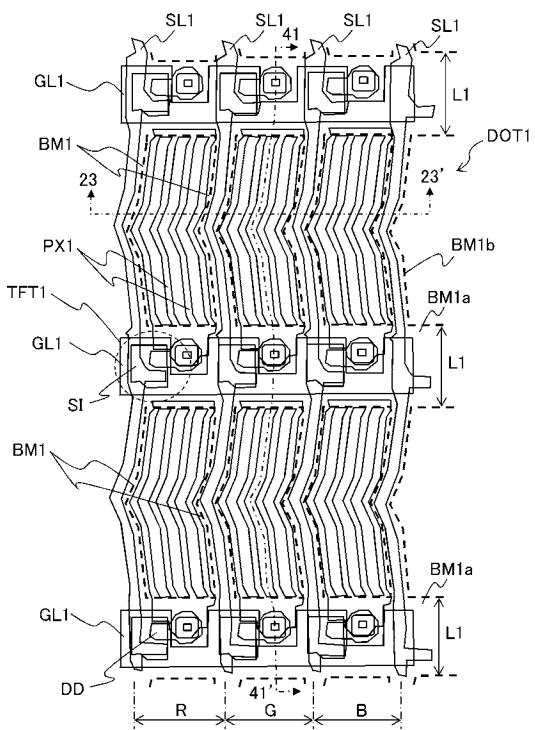

図3及び図5を用いて、表示パネルLCP1の概略構成について説明する。図5に示すように、表示パネルLCP1は、バックライトBL側に配置された薄膜トランジスタ基板TFTB1と、観察者側に配置され、薄膜トランジスタ基板TFTB1に対向する対向基板CF1と、薄膜トランジスタ基板TFTB1及び対向基板CF1の間に配置された液晶層LC1と、を含んでいる。表示パネルLCP1のバックライトBL側には偏光板POL2が配置されており、観察者側には偏光板POL1が配置されている。

40

## 【0028】

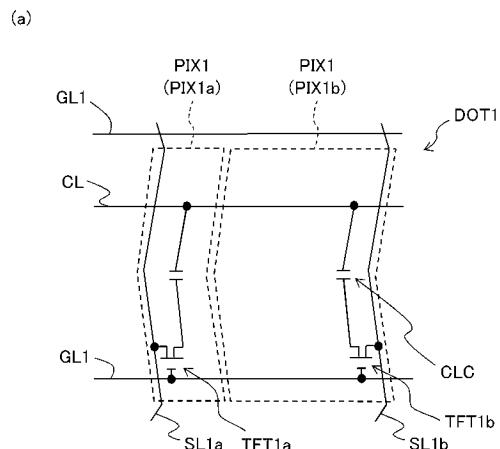

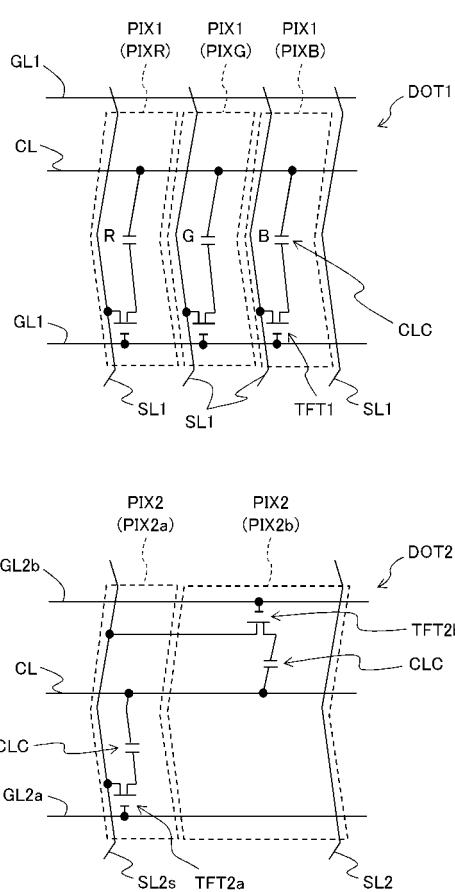

薄膜トランジスタ基板TFTB1には、図3に示すように、第1方向(例えば列方向)に延在する複数のソース線SL1と、第1方向に交差する第2方向(例えば行方向)に延在する複数のゲート線GL1とが形成され、複数のソース線SL1と複数のゲート線GL1とのそれぞれの交差部近傍に薄膜トランジスタTFT1が形成されている。表示パネルLCP1において、表示の最小単位(ドット)、すなわち薄膜トランジスタTFT1に電気的に接続された画素電極PIX1の駆動領域(ドット表示領域)が、1個の画素PIX1として規定され、該画素PIX1がマトリクス状(行方向及び列方向)に複数配置されている。複数のソース線SL1は、行方向に等間隔で配置されており、複数のゲート線GL1は、列方向に等間隔で配置されている。薄膜トランジスタ基板TFTB1(図5参照)には、画素PIX1ごとに画素電極PIX1が形成されており、複数の画素PIX1に共通する1個の共通電極CT(図8参照)が形成されている。薄膜トランジスタTFT1を構成するソース電極はソース線SL1に電気的に接続され、ドレイン電極DD(図7(a)参照)はコンタクトホールを介して画素電極PIX1に電気的に接続され、ゲート電極はゲート線GL1に電気的に接続されている。

## 【0029】

図5に示すように、対向基板CF1には、光を透過する光透過部と、光の透過を遮断す

50

るブラックマトリクスBM1(遮光部)とが形成されている。光透過部には、各画素PIX1に対応して複数のカラーフィルタFIL(着色層)が形成されている。光透過部は、ブラックマトリクスBM1で囲まれており、例えば矩形状に形成されている。詳細は後述するが、複数のカラーフィルタFILは、赤色(R色)の材料で形成され、赤色の光を透過する赤色カラーフィルタFILR(赤色層)と、緑色(G色)の材料で形成され、緑色の光を透過する緑色カラーフィルタFILG(緑色層)と、青色(B色)の材料で形成され、青色の光を透過する青色カラーフィルタFILB(青色層)と、を含んでいる。赤色カラーフィルタFILR、緑色カラーフィルタFILG、及び青色カラーフィルタFILBは、行方向にこの順に繰り返し配列され、同一色のカラーフィルタFILが列方向に配列され、行方向及び列方向に隣り合うカラーフィルタFILの境界部分にブラックマトリクスBM1が形成されている。各カラーフィルタFILに対応して、複数の画素PIX1は、図3に示すように、赤色カラーフィルタFILRに対応する赤色画素PIXRと、緑色カラーフィルタFILGに対応する緑色画素PIXGと、青色カラーフィルタFILBに対応する青色画素PIXBと、を含んでいる。表示パネルLCP1では、赤色画素PIXR、緑色画素PIXG、及び青色画素PIXBが行方向にこの順に繰り返し配列されており、列方向には同一色の画素PIX1が配列されている。

10

20

30

40

50

## 【0030】

第1タイミングコントローラTCON1は、周知の構成を備えている。例えば第1タイミングコントローラTCON1は、画像処理部IPUから出力される第1画像データDA1と第1制御信号CS1(クロック信号、垂直同期信号、水平同期信号等)に基づいて、第1画像データDA1と、第1ソースドライバSD1及び第1ゲートドライバGD1の駆動を制御するための各種タイミング信号(データスタートパルスDSP1、データクロックDCK1、ゲートスタートパルスGSP1、ゲートクロックGCK1)とを生成する(図3参照)。第1タイミングコントローラTCON1は、第1画像データDA1と、データスタートパルスDSP1と、データクロックDCK1とを第1ソースドライバSD1に出力し、ゲートスタートパルスGSP1とゲートクロックGCK1とを第1ゲートドライバGD1に出力する。

## 【0031】

第1ソースドライバSD1は、データスタートパルスDSP1及びデータクロックDCK1に基づいて、第1画像データDA1に応じたデータ信号(データ電圧)をソース線SL1に出力する。第1ゲートドライバGD1は、ゲートスタートパルスGSP1及びゲートクロックGCK1に基づいて、ゲート信号(ゲート電圧)をゲート線GL1に出力する。

## 【0032】

各ソース線SL1には、第1ソースドライバSD1からデータ電圧が供給され、各ゲート線GL1には、第1ゲートドライバGD1からゲート電圧が供給される。共通電極CTには、コモンドライバ(図示せず)から共通電圧Vcomが供給される。ゲート電圧(ゲートオン電圧)がゲート線GL1に供給されると、ゲート線GL1に接続された薄膜トランジスタTFT1がオンし、薄膜トランジスタTFT1に接続されたソース線SLを介して、データ電圧が画素電極PX1に供給される。画素電極PX1に供給されたデータ電圧と、共通電極CTに供給された共通電圧Vcomとの差により電界が生じる。この電界により液晶を駆動してバックライトBLの光の透過率を制御することによって画像表示を行う。表示パネルLCP1では、赤色画素PIXR、緑色画素PIXG、及び青色画素PIXBそれぞれの画素電極PX1に接続されたソース線SL1に、所望のデータ電圧を供給することにより、カラー画像表示が行われる。

## 【0033】

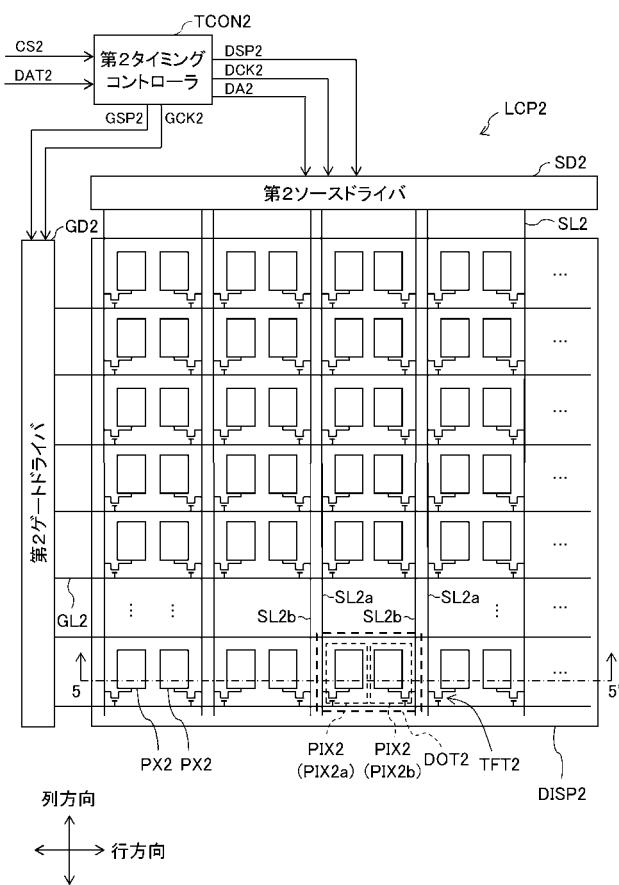

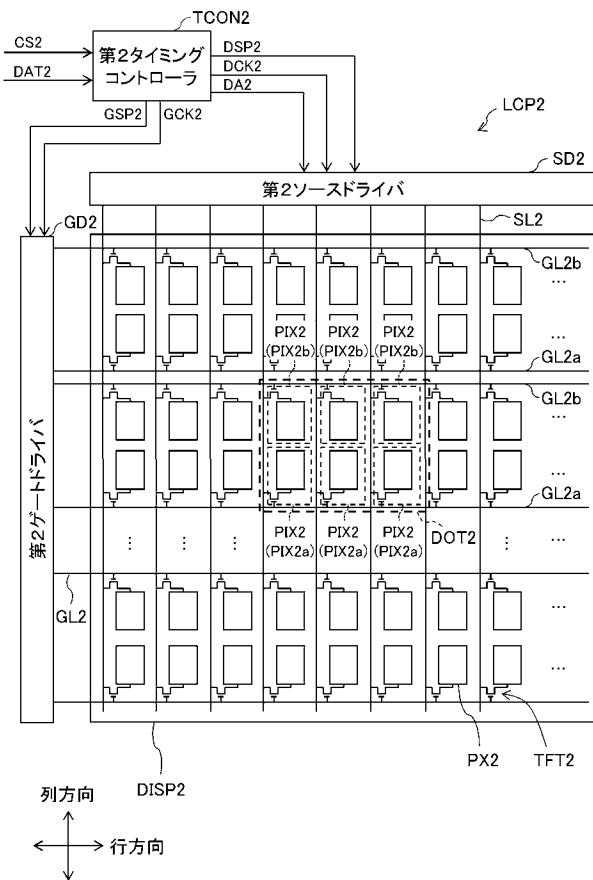

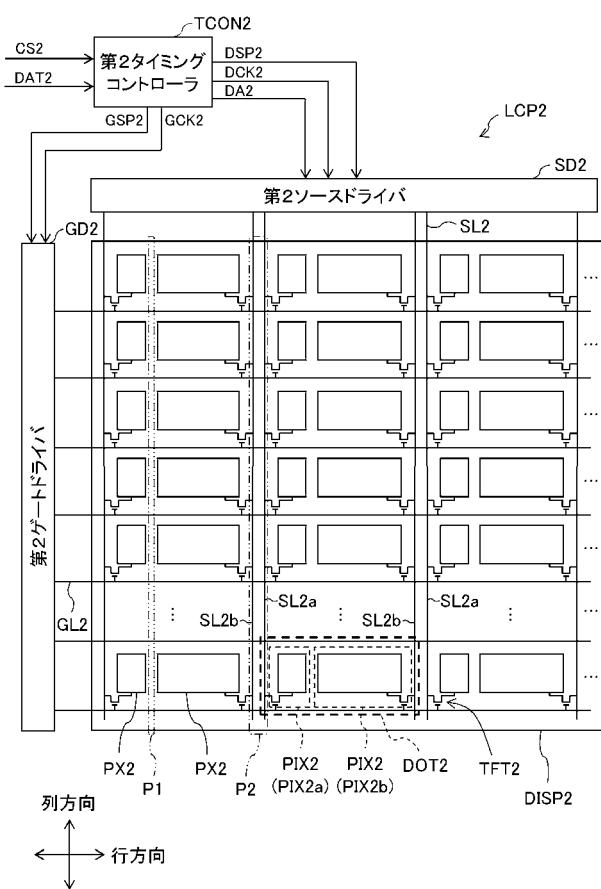

次に、図4及び図5を用いて、表示パネルLCP2の構成について説明する。図5に示すように、表示パネルLCP2は、バックライトBL側に配置された薄膜トランジスタ基板TFTB2と、観察者側に配置され、薄膜トランジスタ基板TFTB2に対向する対向基板CF2と、薄膜トランジスタ基板TFTB2及び対向基板CF2の間に配置された液

晶層 L C 2 と、を含んでいる。表示パネル L C P 2 のバックライト BL 側には偏光板 P O L 4 が配置されており、観察者側には偏光板 P O L 3 が配置されている。表示パネル L C P 1 の偏光板 P O L 2 と、表示パネル L C P 2 の偏光板 P O L 3 との間には、接着層 S E F I L が配置されている。

【 0 0 3 4 】

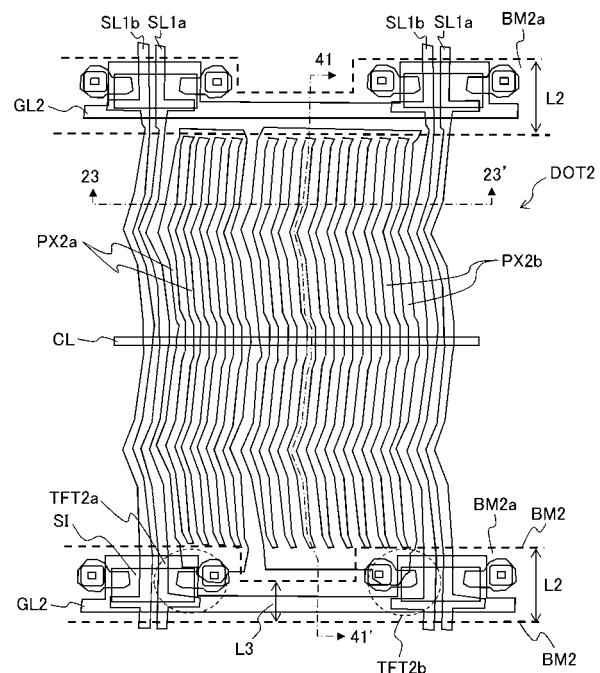

薄膜トランジスタ基板 T F T B 2 には、図 4 に示すように、列方向に延在する複数のソース線 S L 2 と、行方向に延在する複数のゲート線 G L 2 とが形成され、複数のソース線 S L 2 と複数のゲート線 G L 2 とのそれぞれの交差部近傍に薄膜トランジスタ T F T 2 が形成されている。複数のソース線 S L 2 は、複数のソース線 S L 2 a と、複数のソース線 S L 2 b とを含んでいる。複数のソース線 S L 2 a は、行方向に等間隔で配置されており、複数のソース線 S L 2 b は、行方向に等間隔で配置されている。ソース線 S L 2 a 及びソース線 S L 2 b は、行方向に交互に配置されている。表示パネル L C P 2 において、表示の最小単位（ドット）、すなわち薄膜トランジスタ T F T 2 に電気的に接続された画素電極 P X 2 の駆動領域（ドット表示領域）が、1 個の画素 P I X 2 として規定される。図 4 に示す例では、表示パネル L C P 2 を平面的に見て、隣り合うソース線 S L 2 a , S L 2 b と隣り合う 2 本のゲート線 G L 2 とにより囲まれた領域（画素領域）に、2 個の画素 P I X 2 ( P I X 2 a , P I X 2 b ) が行方向に並んで配置されている。複数の画素 P I X 2 は、マトリクス状（行方向及び列方向）に配置されている。ソース線 S L 2 a と、該ソース線 S L 2 a から離間して配置されたソース線 S L 2 b との間には、画素領域が形成されて 2 個の画素 P I X 2 ( P I X 2 a , P I X 2 b ) が配置されている。一方、ソース線 S L 2 a と、該ソース線 S L 2 a に近接して配置されたソース線 S L 2 b との間には、画素領域が形成されていない。すなわち、ソース線 S L 2 a に隣り合う 2 本のソース線 S L 2 b のうち、ソース線 S L 2 a から離間して配置されたソース線 S L 2 b と、ソース線 S L 2 a と、の間には、画素領域が形成されて 2 個の画素 P I X 2 ( P I X 2 a , P I X 2 b ) ( 画素電極 P X 2 ) が配置されている。また、ソース線 S L 2 a に隣り合う 2 つのソース線 S L 2 b のうち、ソース線 S L 2 a に近接して配置されたソース線 S L 2 b と、ソース線 S L 2 a と、の間には、画素領域が形成されていない。複数のゲート線 G L 2 は、列方向に等間隔で配置されている。薄膜トランジスタ基板 T F T B 2 ( 図 5 参照 ) には、画素 P I X 2 ごとに画素電極 P X 2 が形成されており、複数の画素 P I X 2 に共通する 1 個の共通電極 C T ( 図 8 参照 ) が形成されている。薄膜トランジスタ T F T 2 を構成するソース電極はソース線 S L 2 に電気的に接続され、ドレイン電極 D D ( 図 7 ( b ) 参照 ) はコンタクトホールを介して画素電極 P X 2 に電気的に接続され、ゲート電極はゲート線 G L 2 に電気的に接続されている。

【 0 0 3 5 】

対向基板 C F 2 ( 図 5 参照 ) には、光を透過する光透過部と、光の透過を遮断するブラックマトリクス B M 1 ( 遮光部 ) ( 図 9 参照 ) とが形成されている。光透過部には、カラーフィルタ F I L ( 着色層 ) が形成されておらず、例えばオーバーコート膜 O C が形成されている。

【 0 0 3 6 】

第 2 タイミングコントローラ T C O N 2 は、周知の構成を備えている。例えば第 2 タイミングコントローラ T C O N 2 は、画像処理部 I P U から出力される第 2 画像データ D A T 2 と第 2 制御信号 C S 2 ( クロック信号、垂直同期信号、水平同期信号等 ) とに基づいて、第 2 画像データ D A 2 と、第 2 ソースドライバ S D 2 及び第 2 ゲートドライバ G D 2 の駆動を制御するための各種タイミング信号 ( データスタートパルス D S P 2 、データクロック D C K 2 、ゲートスタートパルス G S P 2 、ゲートクロック G C K 2 ) とを生成する ( 図 4 参照 )。第 2 タイミングコントローラ T C O N 2 は、第 2 画像データ D A 2 と、データスタートパルス D S P 2 と、データクロック D C K 2 とを第 2 ソースドライバ S D 2 に出力し、ゲートスタートパルス G S P 2 とゲートクロック G C K 2 とを第 2 ゲートドライバ G D 2 に出力する。

【 0 0 3 7 】

10

20

30

40

50

第2ソースドライバSD2は、データスタートパルスDSP2及びデータクロックDCK2に基づいて、第2画像データDA2に応じたデータ電圧をソース線SL2に出力する。第2ゲートドライバGD2は、ゲートスタートパルスGSP2及びゲートクロックGCK2に基づいて、ゲート電圧をゲート線GL2に出力する。

【0038】

各ソース線SL2には、第2ソースドライバSD2からデータ電圧が供給され、各ゲート線GL2には、第2ゲートドライバGD2からゲート電圧が供給される。共通電極CTには、コモンドライバから共通電圧Vcomが供給される。ゲート電圧(ゲートオン電圧)がゲート線GLに供給されると、ゲート線GL2に接続された薄膜トランジスタTFT2がオンし、薄膜トランジスタTFT2に接続されたソース線SL2を介して、データ電圧が画素電極PX2に供給される。画素電極PX2に供給されたデータ電圧と、共通電極CTに供給された共通電圧Vcomとの差により電界が生じる。この電界により液晶を駆動してバックライトBLの光の透過率を制御することによって画像表示を行う。表示パネルLCP2では、各画素PIX2の画素電極PX2に接続されたソース線SL2に、所望のデータ電圧を供給することにより、白黒画像表示が行われる。

10

【0039】

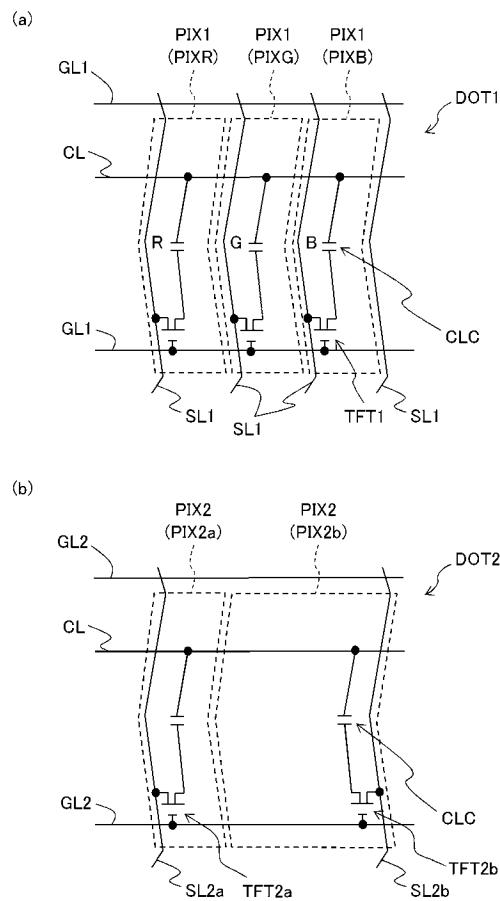

液晶表示装置LCDでは、表示パネルLCP1の単位面積当たりの画素PIX1の数と、表示パネルLCP2の単位面積当たりの画素PIX2の数とが等しくなっており、表示パネルLCP1及び表示パネルLCP2は互いに同一の解像度を有している。表示パネルLCP1の画素PIX1と、表示パネルLCP2の画素PIX2とは、平面視で互いに重畠するように配置されている。

20

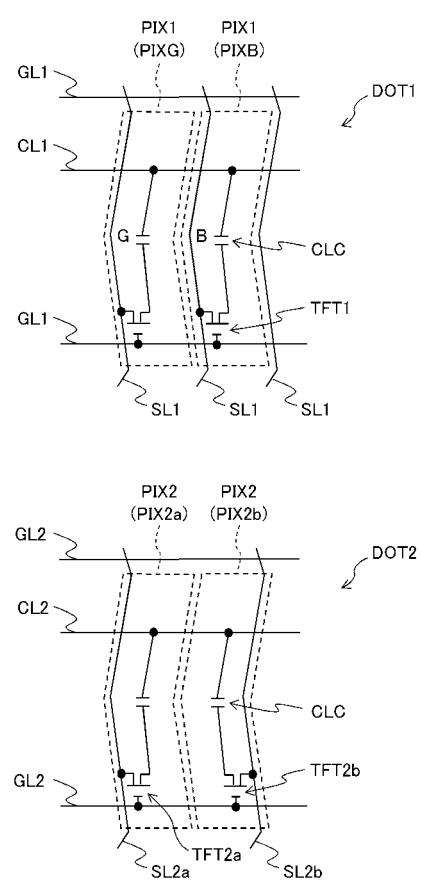

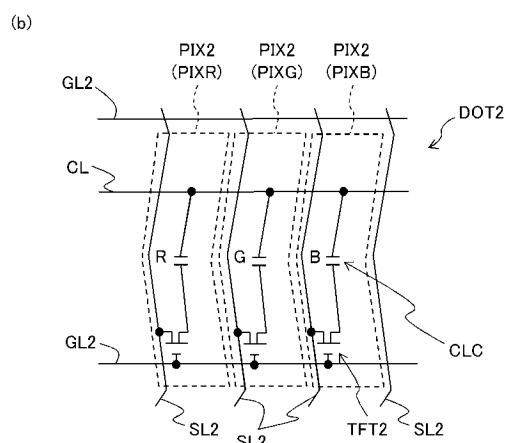

【0040】

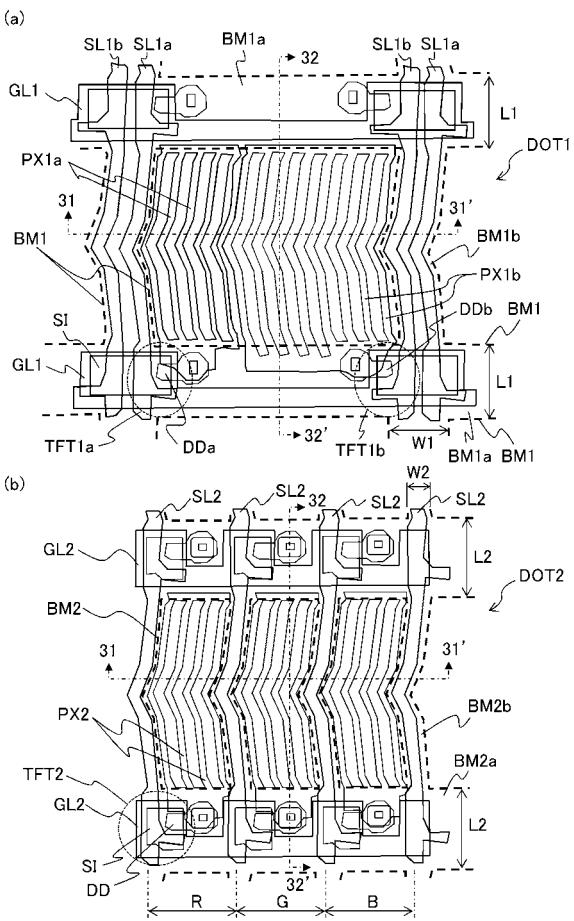

図6は、平面視で互いに重なり合う、表示パネルLCP1の画素グループDOT1と、表示パネルLCP2の画素グループDOT2との関係を示す平面図であり、図7は、図6に対応する画素グループDOT1, DOT2の画素PIX1, PIX2の具体的な構成を示す平面図である。画素グループDOT1は、表示パネルLCP1の2個の画素PIX1(図6に示す例では、1個の緑色画素PIXG及び1個の青色画素PIXB)から成り、画素グループDOT2は、表示パネルLCP2の1個の画素PIX2a及び1個の画素PIX2bから成る。尚、図6には、共通電極CT(図8参照)に接続される共通配線CL1, CL2と、液晶容量CLCとを示している。図7には、薄膜トランジスタTFT1, TFT2を構成する半導体層SI(チャネル)とドレイン電極DDとを示している。画素電極PX1, PX2にスリットが形成されてもよい。

30

【0041】

図6(a)に示すように、各画素PIX1では、ソース線SL1が薄膜トランジスタTFT1のソース電極に接続されており、ゲート線GL1が薄膜トランジスタTFT1のゲート電極に接続されており、画素電極PX1(図7(a)参照)が薄膜トランジスタTFT1のドレイン電極DD(図7(a)参照)に接続されている。一方、図6(b)に示すように、画素PIX2aでは、ソース線SL2aが薄膜トランジスタTFT2aのソース電極に接続されており、ゲート線GL2が薄膜トランジスタTFT2aのゲート電極に接続されており、画素電極PX2a(図7(b)参照)が薄膜トランジスタTFT2aのドレイン電極DDa(図7(b)参照)に接続されている。また画素PIX2bでは、ソース線SL2bが薄膜トランジスタTFT2bのソース電極に接続されており、ゲート線GL2が薄膜トランジスタTFT2bのゲート電極に接続されており、画素電極が薄膜トランジスタTFT2bのドレイン電極DDb(図7参照)に接続されている。

40

【0042】

図7に示すように、表示パネルLCP1のブラックマトリクスBM1は、平面視でゲート線GL1及びソース線SL1の両方に重なるように行方向及び列方向に延在しており、格子状に形成されている。すなわち、表示パネルLCP1のブラックマトリクスBM1は、平面視で、表示パネルLCP1の複数のゲート線GL1の各々に重なる複数の行ストライプ部分BM1aと、平面視で、表示パネルLCP1の複数のソース線SL1の各々に重

50

なる複数の列ストライプ部分 B M 1 b を含んでいる。また行ストライプ部分 B M 1 a はゲート線 G L 1 の列方向の長さより長く、列ストライプ部分 B M 1 b はソース線 S L 1 の行方向の長さより長くなっている。一方、表示パネル L C P 2 のブラックマトリクス B M 2 は、ゲート線 G L 2 に重なるように行方向に延在しており、ストライプ状に形成されている。すなわち、表示パネル L C P 2 のブラックマトリクス B M 2 は、平面視で、表示パネル L C P 2 の複数のゲート線 G L 2 の各々に重なる複数の行ストライプ部分 B M 2 a を含んでいる。ブラックマトリクス B M 2 は、平面視でソース線 S L 2 全体を覆うような列方向に延在する部分を含まない。行ストライプ部分 B M 2 a は、ゲート線 G L 2 の列方向の長さより長くなっている。また、図 7 に示すように、ブラックマトリクス B M 2 の行ストライプ部分 B M 2 a の列方向の長さ L 2 は、ブラックマトリクス B M 1 の行ストライプ部分 B M 1 a の列方向の長さ L 1 より短くなっている。

10

## 【 0 0 4 3 】

図 8 は、図 7 の 8 - 8' 切断線における断面図であり、図 9 は、図 7 の 9 - 9' 切断線における断面図である。図 8 及び図 9 を用いて画素 P I X 1, P I X 2 の断面構造について説明する。

## 【 0 0 4 4 】

表示パネル L C P 1 の画素 P I X 1 を構成する薄膜トランジスタ基板 T F T B 1 ( 図 5 参照 ) では、透明基板 S U B 2 ( ガラス基板 ) 上にゲート線 G L 1 ( 図 9 参照 ) が形成されており、ゲート線 G L 1 を覆うようにゲート絶縁膜 G S N が形成されている。ゲート絶縁膜 G S N 上にソース線 S L 1 ( 図 8 参照 ) が形成されており、ソース線 S L 1 を覆うように保護膜 P A S 及び有機膜 O P A S が形成されており、有機膜 O P A S 上に共通電極 C T が形成されており、共通電極 C T を覆うように保護膜 U P A S が形成されている。保護膜 U P A S 上に画素電極 P X 1 が形成されており、画素電極 P X 1 を覆うように配向膜 ( 図示せず ) が形成されている。画素電極 P X 1 は、コンタクトホールを介してドレイン電極 D D ( 図 9 参照 ) に電気的に接続されている。ソース線 S L 1 は行方向に等間隔に配置されており、ゲート線 G L 1 は列方向に等間隔に配置されている。対向基板 C F 1 ( 図 5 参照 ) では、透明基板 S U B 1 ( ガラス基板 ) 上に、格子状のブラックマトリクス B M 1 と、カラーフィルタ F I L ( 赤色カラーフィルタ F I L R, 緑色カラーフィルタ F I L G 、及び青色カラーフィルタ F I L B ) が形成されている。カラーフィルタ F I L の表面にはオーバーコート膜 O C が被覆されており、オーバーコート膜 O C 上に配向膜 ( 図示せず ) が形成されている。各カラーフィルタ F I L は、平面視で、隣り合うカラーフィルタ F I L の境界部分がソース線 S L 1 に重なるように配置されている。

20

## 【 0 0 4 5 】

表示パネル L C P 2 の画素 P I X 2 を構成する薄膜トランジスタ基板 T F T B 2 ( 図 5 参照 ) では、透明基板 S U B 4 上にゲート線 G L 2 ( 図 9 参照 ) が形成されており、ゲート線 G L 2 を覆うようにゲート絶縁膜 G S N が形成されている。ゲート絶縁膜 G S N 上にソース線 S L 2 a, S L 2 b ( 図 8 参照 ) が形成されており、ソース線 S L 2 a, S L 2 b を覆うように保護膜 P A S 及び有機膜 O P A S が形成されており、有機膜 O P A S 上に共通電極 C T が形成されており、共通電極 C T を覆うように保護膜 U P A S が形成されている。保護膜 U P A S 上に画素電極 P X 2 が形成されており、画素電極 P X 2 を覆うように配向膜 ( 図示せず ) が形成されている。画素電極 P X 2 は、コンタクトホールを介してドレイン電極 D D ( 図 9 参照 ) に電気的に接続されている。図 8 において左側のソース線 S L 2 b と右側のソース線 S L 2 a とは行方向に近接して配置されており、ゲート線 G L 2 は列方向に等間隔に配置されている。対向基板 C F 2 ( 図 5 参照 ) では、透明基板 S U B 3 上に、ストライプ状のブラックマトリクス B M 2 ( 図 9 参照 ) が形成されており、ブラックマトリクス B M 2 の開口部 ( 光透過部 ) 及びブラックマトリクス B M 2 上にオーバーコート膜 O C が被覆されており、オーバーコート膜 O C 上に配向膜 ( 図示せず ) が形成されている。

30

## 【 0 0 4 6 】

このように、表示パネル L C P 2 では、平面視で、画素電極 P X 2 a ( 図 7 参照 ) に電

40

50

気的に接続されたソース線 S L 2 a が、該画素電極 P X 2 a の左側に配置されており、画素電極 P X 2 b ( 図 7 参照 ) に電気的に接続されたソース線 S L 2 b が、該画素電極 P X 2 b の右側に配置されている。また、画素電極 P X 2 a の右側と画素電極 P X 2 b の左側との間にはソース線 S L 2 は配置されていない。

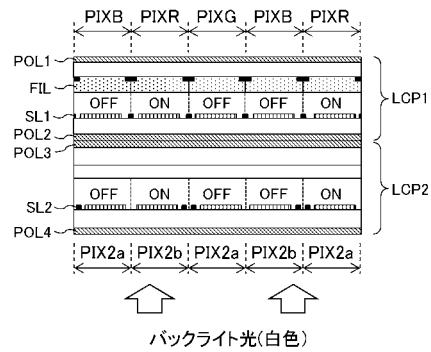

【 0 0 4 7 】

実施形態 1 に係る液晶表示装置 L C D では、表示パネル L C P 1 の各画素 P I X 1 と、表示パネル L C P 2 の各画素 P I X 2 とが重畳して配置されている。上記構成において、図 10 ( a ) に示すように例えば赤色の単色画像を表示する場合、表示パネル L C P 1 では赤色画素 P I X R をオン状態にし、緑色画素 P I X G 及び青色画素 P I X B をオフ状態にする。また、表示パネル L C P 2 では、赤色画素 P I X R に重畳する画素 P I X 2 をオン状態にし、緑色画素 P I X G 及び青色画素 P I X B に重畳する画素 P I X 2 をオフ状態にする。この状態で、R G B 成分を含むバックライト光 ( 白色 ) を照射すると、図 10 ( b ) に示すように赤色画素 P I X R からは本来の表示光 ( 赤色 ) が射出される。また、緑色画素 P I X G では、表示パネル L C P 2 の漏れ光 ( 白色 ) が表示パネル L C P 1 に入射され、この漏れ光のうち赤色成分 R 及び青色成分 B は緑色カラーフィルタ F I L G で遮光され、緑色成分 G は偏光板 P O L 1 で遮光される。また、青色画素 P I X B では、表示パネル L C P 2 の漏れ光 ( 白色 ) が表示パネル L C P 1 に入射され、この漏れ光のうち赤色成分 R 及び緑色成分 G は青色カラーフィルタ F I L B で遮光され、青色成分 B は偏光板 P O L 1 で遮光される。

【 0 0 4 8 】

このように、表示パネル L C P 1 の赤色画素 P I X R と、赤色画素 P I X R に重畳する表示パネル L C P 2 の画素 P I X 2 とが 1 対 1 の関係で配置されているため、互いに重畳する赤色画素 P I X R と画素 P I X 2 とのオン / オフを他の画素とは独立して制御することができる。このため、表示パネル L C P 2 で光漏れが生じたとしても、この漏れ光の各色成分 ( 例えば緑色成分 G 、青色成分 B ) を表示パネル L C P 1 のカラーフィルタ F I L 及び偏光板 P O L 1 で遮光することができる。これにより、従来の構成と比較して、光漏れを低減することができるため、赤色画像の色再現性を向上させることができる。尚、上記構成では、表示パネル L C P 1 の各画素 P I X 1 と表示パネル L C P 2 の各画素 P I X 2 とが 1 対 1 の関係で配置されているため、互いに重畳する各画素 P I X 1 , P I X 2 のオン / オフを独立して制御することができる。よって、赤色画像と同様に、緑色及び青色の単色画像の色再現性も向上させることができる。

【 0 0 4 9 】

ここで、上記のように各画素 P I X 1 , P I X 2 のオン / オフを独立して制御する方法として、表示パネル L C P 2 のソース線 S L 2 、ブラックマトリクス B M 2 、及び画素 P I X 2 の構成を、表示パネル L C P 1 と同一の構成とすることができる。すなわち、表示パネル L C P 2 において、平面視で、ソース線 S L 2 を隣り合う画素 P I X 2 の境界に 1 本ずつ配置し、ブラックマトリクス B M 2 を各画素 P I X 2 の周囲を囲むようにマトリクス状に形成することができる。

【 0 0 5 0 】

しかし、この構成 ( 以下、比較例とする。 ) では、局所的な輝度ムラあるいはモアレが発生し易くなるおそれがある。例えば、輝度ムラやモアレは、表示パネル L C P 1 と表示パネル L C P 2 とを貼り合わせる際に、互いに位置ずれが生じた場合に視認され易くなる。図 6 5 及び図 6 6 は、互いに重ね合わせて配置される 2 枚のパネル A , B における、ブラックマトリクスと開口部との関係を模式的に示す図である。例えば、上記比較例に対応する構成例 1 ( 図 6 5 参照 ) では、パネル A とパネル B とに位置ずれが生じた場合に、各画素において、パネル A 及びパネル B それぞれのブラックマトリクスの位置が、左右方向、上下方向、又は回転方向に互いにずれることにより、画素の開口率が表示面内で不均一になり輝度ムラが視認され易くなる。また表示画面を斜め方向から視た場合に、上下のブラックマトリクスが幅広く見え、これにより周期的な輝度の明暗すなわちモアレが視認され易くなる。一方、構成例 2 ( 図 6 5 参照 ) では、パネル A とパネル B とに位置ずれが生

10

20

30

40

50

じた場合に、特に赤色画素及び青色画素において、パネルA及びパネルBそれぞれのブラックマトリクスの位置が互いにずれることにより、赤色及び青色の単色画像を表示する際に輝度ムラは視認されるが、パネルBでは、緑色画素及び赤色画素の境界と、緑色画素及び青色画素の境界に重なる部分にブラックマトリクスが形成されていないため、緑色画素については、輝度ムラあるいはモアレは軽減される。

#### 【0051】

これに対して、実施形態1に係る液晶表示装置LCDに対応する構成例4(図66参照)では、表示パネルLCP2(図66のパネルBに対応)のブラックマトリクスBM2が、行方向に延在する部分から成り、ストライプ状に形成されており、列方向に延在する部分が省略されている。また、行方向に延在するブラックマトリクスBM2(行ストライプ部分BM2a)の列方向の長さ(図7(b)に示すL2)が、ブラックマトリクスBM1の行ストライプ部分BM1aの列方向の長さ(図7(a)に示すL1)より短くなっている。このため、表示パネルLCP1と表示パネルLCP2とに位置ずれが生じた場合でも、ブラックマトリクスBM1, BM2の位置ずれによる影響が小さいため、輝度ムラ及びモアレが生じ難くなる。また、図65の構成例1では各画素の開口率が低下するが、本実施形態1(図66の構成例4)では、画素の開口率の低下を抑えることもできる。尚、本実施形態では、ブラックマトリクスBM2が、ブラックマトリクスBM1の列ストライプ部分BM1bより行方向の長さが短い列ストライプ部分を含んでもよい。この構成でも、図65に示す構成例3と同様に、輝度ムラ及びモアレが生じ難くなる。

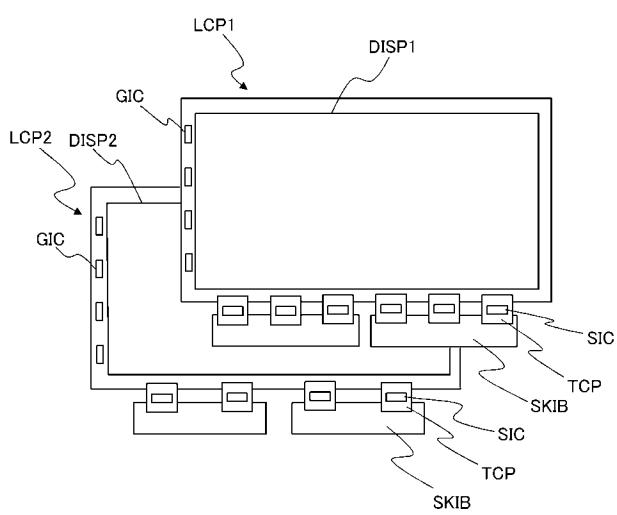

#### 【0052】

図11は、表示パネルLCP1及び表示パネルLCP2のドライバの構成を示す図である。表示パネルLCP1には、それぞれにソースドライバIC(SIC)が実装された6個のTCP(Tape Carrier Package)が接続されており、各TCPがソースプリント基板SKIBに接続されている。また表示パネルLCP1には、4個のゲートドライバIC(GIC)が実装されている。同様に、表示パネルLCP2には、それぞれにソースドライバIC(SIC)が実装された6個のTCPが接続されており、各TCPがソースプリント基板SKIBに接続されている。また表示パネルLCP2には、4個のゲートドライバIC(GIC)が実装されている。

#### 【0053】

##### [実施形態2]

本発明の実施形態2について、図面を用いて以下に説明する。なお、説明の便宜上、実施形態1において示した構成要素と構成要素には同一の符号を付し、その説明を省略する。また、実施形態1において定義した用語については特に断らない限り本実施形態においてもその定義に則って用いるものとする。なお、後述の各実施形態についても同様である。

#### 【0054】

図12は実施形態2に係る表示パネルLCP1の概略構成を示す平面図であり、図13は実施形態2に係る表示パネルLCP2の概略構成を示す平面図である。実施形態2に係る表示パネルLCP1の構成は、実施形態1に係る表示パネルLCP1の構成と同一である。

#### 【0055】

実施形態2に係る表示パネルLCP2では、図13に示すように、複数のゲート線GL2は、複数のゲート線GL2aと、複数のゲート線GL2bとを含んでいる、複数のゲート線GL2aは、列方向に等間隔で配置されており、複数のゲート線GL2bは、列方向に等間隔で配置されている。ゲート線GL2a及びゲート線GL2bは、列方向に交互に配置されている。表示パネルLCP2を平面的に見て、隣り合うゲート線GL2a, GL2bと、隣り合う2本のソース線SL2とにより囲まれた領域(画素領域)に2個の画素PIX2(PIX2a, PIX2b)が列方向に並んで配置されている。複数の画素PIX2は、マトリクス状(行方向及び列方向)に配置されている。ゲート線GL2aと、該ゲート線GL2aから離間して配置されたゲート線GL2bとの間には、画素領域が形成

10

20

30

40

50

されて2個の画素PIX2(PIX2a, PIX2b)が配置されている。一方、ゲート線GL2aと、該ゲート線GL2aに近接して配置されたゲート線GL2bとの間には、画素領域が形成されていない。すなわち、ゲート線GL2aに隣り合う2本のゲート線GL2bのうち、ゲート線GL2aから離間して配置されたゲート線GL2bと、ゲート線GL2aと、の間には、画素領域が形成されて2個の画素PIX2(PIX2a, PIX2b)(画素電極PX2)が配置されている。また、ゲート線GL2aに隣り合う2本のゲート線GL2bのうち、ゲート線GL2aに近接して配置されたゲート線GL2bと、ゲート線GL2aと、の間には、画素領域が形成されていない。複数のソース線SL2は、行方向に等間隔で配置されている。

【0056】

10

図14は、平面視で互いに重なり合う、表示パネルLCP1の画素グループDOT1と、表示パネルLCP2の画素グループDOT2との関係を示す平面図であり、図15は、図14(a)に対応する画素グループDOT1の画素PIX1の具体的な構成を示す平面図である。図16は、図14(b)に対応する画素グループDOT2の画素PIX2の具体的な構成を示す平面図である。画素グループDOT1は、表示パネルLCP1の2個の赤色画素PIXR、2個の緑色画素PIXG及び2個の青色画素PIXBから成り、画素グループDOT2は、表示パネルLCP2の3個の画素PIX2a及び3個の画素PIX2bから成る。

【0057】

20

図14(b)に示すように、画素PIX2aでは、ソース線SL2が薄膜トランジスタTFT2aのソース電極に接続されており、ゲート線GL2aが薄膜トランジスタTFT2aのゲート電極に接続されており、画素電極PX2a(図16参照)が薄膜トランジスタTFT2aのドレイン電極DDa(図16参照)に接続されている。また画素PIX2bでは、ソース線SL2が薄膜トランジスタTFT2bのソース電極に接続されており、ゲート線GL2bが薄膜トランジスタTFT2bのゲート電極に接続されており、画素電極PX2b(図16参照)が薄膜トランジスタTFT2bのドレイン電極DDb(図16参照)に接続されている。

【0058】

30

図16に示すように、表示パネルLCP2のブラックマトリクスBM2は、ゲート線GL2に重なるように行方向に延在しており、ストライプ状に形成されている。すなわち、表示パネルLCP2のブラックマトリクスBM2は、平面視で、表示パネルLCP2のゲート線GL2に重なる複数の行ストライプ部分BM2aを含んでいる。ブラックマトリクスBM2は、平面視でソース線SL2全体を覆うような列方向に延在する部分を含まない。また、図16に示すように、ブラックマトリクスBM2の行ストライプ部分BM2aの列方向の長さL2は、ゲート線GL2aの列方向の長さとゲート線GL2bの列方向の長さとを合計した長さ(2本分のゲート線GL2の列方向の長さ)より長くなっている。また、ブラックマトリクスBM2の行ストライプ部分BM2aの列方向の長さL2は、ブラックマトリクスBM1の行ストライプ部分BM1aの列方向の長さL1より長くなっている。

【0059】

40

図17は、図15及び図16の17-17'切断線における断面図であり、図18は、図15及び図16の18-18'切断線における断面図である。図17及び図18を用いて画素PIX1, PIX2の断面構造について説明する。

【0060】

50

図17に示すように、ソース線SL1, SL2はそれぞれ行方向に等間隔に配置されており、平面視で、ソース線SL1, SL2は互いに重疊するように配置されている。図18に示すように、透明基板SUB4上にゲート線GL2a, GL2bが形成されている。ゲート線GL2a, GL2bは近接して配置されており、一組のゲート線GL2a, GL2bは、平面視で、ブラックマトリクスBM2の1本の行ストライプ部分BM2aに重疊するように配置されている。表示パネルLCP2では、共通電極CT上に共通配線CLが

形成されている。共通配線 C L は、平面視で、行方向に延在し、ブラックマトリクス B M 1 に重畠するように配置されている。尚、ブラックマトリクス B M 1 の行ストライプ部分 B M 1 a の列方向の長さ L 1 (図 15 参照) は、共通配線 C L の列方向の長さ L 4 (図 16 参照) よりも長くなっている。

【0061】

このように、表示パネル L C P 2 では、平面視で、画素電極 P X 2 a (図 16 参照) に電気的に接続されたゲート線 G L 2 a が、該画素電極 P X 2 a の下側に配置されており、画素電極 P X 2 b (図 16 参照) に電気的に接続されたゲート線 G L 2 b が、該画素電極 P X 2 b の上側に配置されている。また、画素電極 P X 2 a の上側と画素電極 P X 2 b の下側との間にはゲート線 G L 2 は配置されていない。

10

【0062】

実施形態 2 の構成によれば、実施形態 1 の構成と同様に、表示パネル L C P 1 の各画素 P I X 1 と表示パネル L C P 2 の各画素 P I X 2 とが 1 対 1 の関係で配置されているため、各画素 P I X 1, P I X 2 のオン / オフを独立して制御することができる。このため、従来の構成と比較して、光漏れを低減することができるため、各色の単色画像の色再現性を向上させることができる。また、輝度ムラの発生及び画素の開口率の低下を抑えることもできる。

【0063】

表示パネル L C P 1 及び表示パネル L C P 2 のドライバの構成は、図 11 に示す構成と同一である。

20

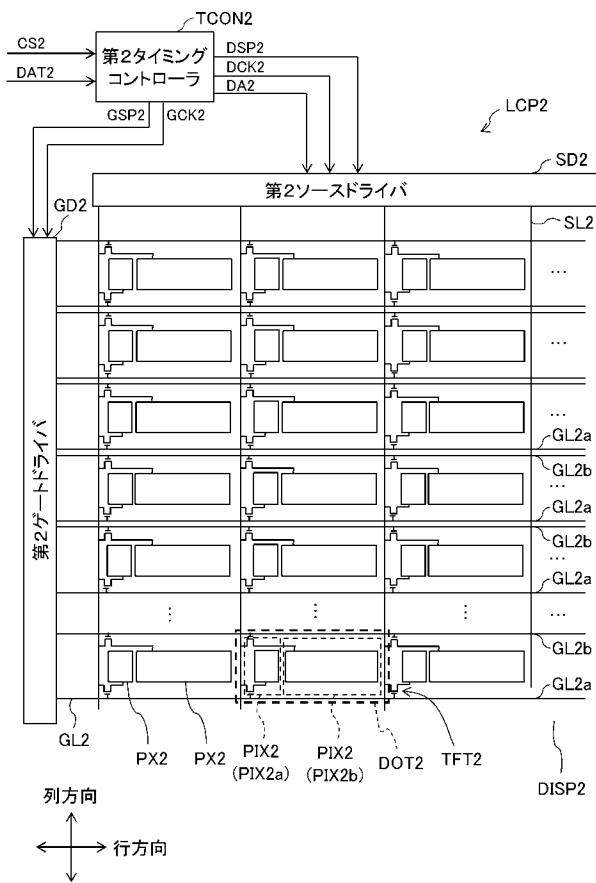

【0064】

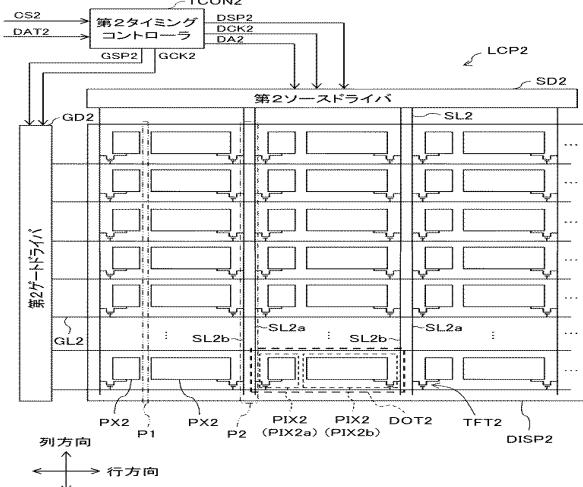

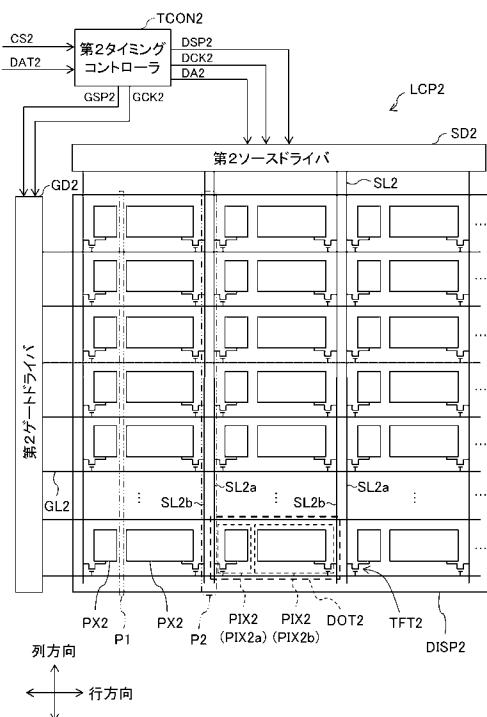

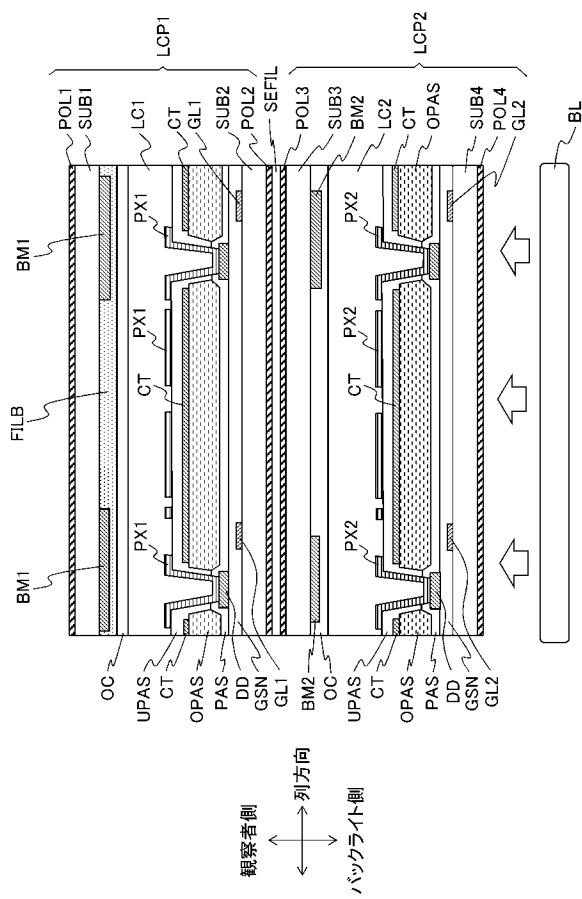

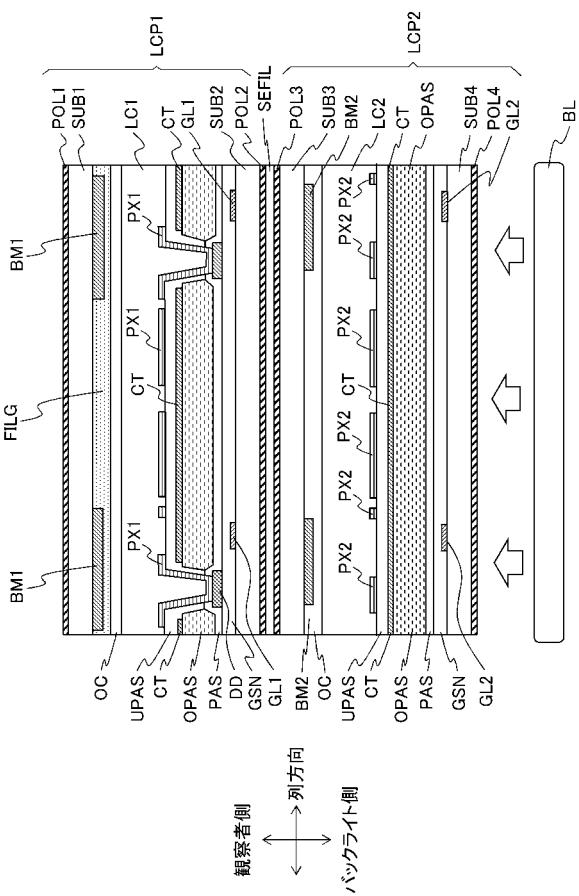

【実施形態 3】

図 19 は実施形態 3 に係る表示パネル L C P 1 の概略構成を示す平面図であり、図 20 は実施形態 3 に係る表示パネル L C P 2 の概略構成を示す平面図である。実施形態 3 に係る表示パネル L C P 1 の構成は、実施形態 1 に係る表示パネル L C P 1 の構成と同一である。

【0065】

実施形態 3 に係る表示パネル L C P 2 は、概略的には、実施形態 1 に係る表示パネル L C P 2 と比較して、画素 P I X 2 b の大きさが異なっており、その他の構成は同一である。

30

【0066】

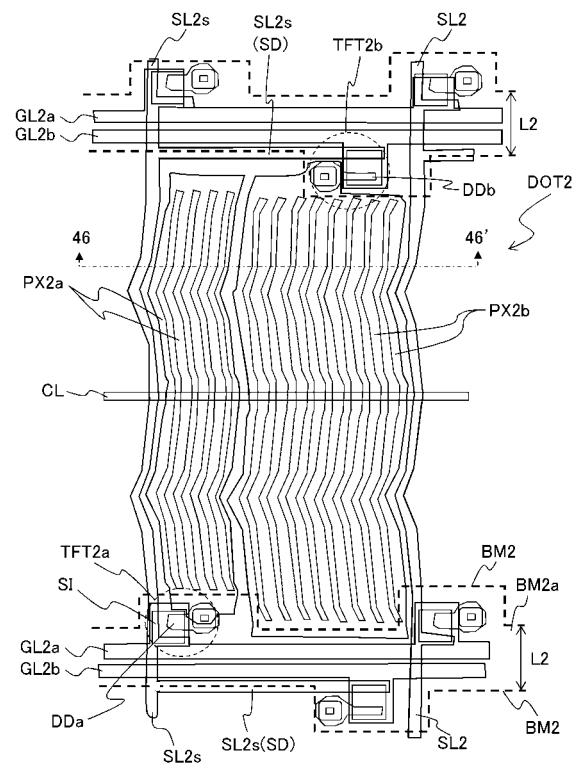

図 21 は、平面視で互いに重なり合う、表示パネル L C P 1 の画素グループ D O T 1 と、表示パネル L C P 2 の画素グループ D O T 2 との関係を示す平面図であり、図 22 は、図 21 に対応する画素グループ D O T 1, D O T 2 の画素 P I X 1, P I X 2 の具体的な構成を示す平面図である。画素グループ D O T 1 は、表示パネル L C P 1 の 1 個の赤色画素 P I X R、1 個の緑色画素 P I X G 及び 1 個の青色画素 P I X B から成り、画素グループ D O T 2 は、表示パネル L C P 2 の 1 個の画素 P I X 2 a 及び 1 個の画素 P I X 2 b から成る。

【0067】

実施形態 3 に係る表示パネル L C P 2 は、単位面積当たりの画素 P I X 2 の数が、表示パネル L C P 1 の単位面積当たりの画素 P I X 1 の数より少なくなるように構成されている。具体的には、図 21 及び図 22 に示すように、表示パネル L C P 1 の 1 個の画素 P I X 1 (1 個の赤色画素 P I X R) と、表示パネル L C P 2 の 1 個の画素 P I X 2 a とが、平面視で互いに重畠し、表示パネル L C P 1 の 2 個の画素 P I X 1 (1 個の緑色画素 P I X G 及び 1 個の青色画素 P I X B) と、表示パネル L C P 2 の 1 個の画素 P I X 2 b とが、平面視で互いに重畠するように構成されている。表示パネル L C P 1 の各画素 P I X 1 の面積 (大きさ) が互いに等しい場合、表示パネル L C P 2 の画素 P I X 2 a の面積は、表示パネル L C P 1 の 1 個の画素 P I X 1 の面積と等しく、表示パネル L C P 2 の画素 P I X 2 b の面積は、表示パネル L C P 1 の 1 個の画素 P I X 1 の面積の 2 倍となっている。また 1 個の画素 P I X 2 b の面積は、1 個の緑色画素 P I X G の面積と 1 個の青色画素

40

50

P IX B の面積とを合計した面積に等しくなっている。

【0068】

図21(b)に示すように、画素P IX 2 aでは、ソース線S L 2 aが薄膜トランジスタTFT 2 aのソース電極に接続されており、ゲート線G L 2が薄膜トランジスタTFT 2 aのゲート電極に接続されており、画素電極P X 2 a(図22(b)参照)が薄膜トランジスタTFT 2 aのドレイン電極D D a(図22(b)参照)に接続されている。また画素P IX 2 bでは、ソース線S L 2 bが薄膜トランジスタTFT 2 bのソース電極に接続されており、ゲート線G L 2が薄膜トランジスタTFT 2 bのゲート電極に接続されており、画素電極P X 2 b(図22(b)参照)が薄膜トランジスタTFT 2 bのドレイン電極D D b(図22(b)参照)に接続されている。また、図22に示すように、ブラックマトリクスBM2の行ストライプ部分BM2 aの列方向の長さL 2は、ブラックマトリクスBM1の行ストライプ部分BM1 aの列方向の長さL 1より短くなっている。また、行ストライプ部分BM2 aにおける、薄膜トランジスタTFT 2 a, TFT 2 bの間の領域(中央部分)の列方向の長さL 3は、薄膜トランジスタTFT 2 a, TFT 2 bを覆う部分の列方向の長さL 2より短くなっている。

10

【0069】

図23は、図22の23-23'切断線における断面図であり、図24は、図22の24-24'切断線における断面図である。図23及び図24を用いて画素P IX 1, P IX 2の断面構造について説明する。

20

【0070】

図23に示すように、透明基板SUB4のゲート絶縁膜GSN上にソース線S L 2 a, S L 2 bが形成されている。ソース線S L 2 a, S L 2 bは近接して配置されており、一組のソース線S L 2 a, S L 2 bの一部は、平面視で、ブラックマトリクスBM1の1本の列ストライプ部分BM2 b(図22(a)参照)に重畠するように配置されている。

30

【0071】

実施形態3の構成によれば、表示パネルLCP1の赤色画素P IX Rと表示パネルLCP2の画素P IX 2 aとが1対1の関係で配置されているため、互いに重畠する赤色画素P IX Rと画素P IX 2 aのオン/オフを他の画素とは独立して制御することができる。このため、赤色の単色画像を表示する際に、緑色成分G及び青色成分Bの光漏れを抑えることができる。よって、従来の構成と比較して、赤色画像の色再現性を向上させることができる。また、実施形態1と同様に、輝度ムラの発生及び画素の開口率の低下を抑えることもできる。

30

【0072】

図25は、表示パネルLCP1及び表示パネルLCP2のドライバの構成を示す図である。表示パネルLCP1には、それぞれにソースドライバIC(SIC)が実装された6個のTCPが接続されており、各TCPがソースプリント基板SKIBに接続されている。これに対して、表示パネルLCP2には、それぞれにソースドライバIC(SIC)が実装された4個のTCPが接続されており、各TCPがソースプリント基板SKIBに接続されている。このように、表示パネルLCP1と比較して、表示パネルLCP2のソースドライバICの数を削減することができるため、液晶表示装置LCDのコストを低減することができる。

40

【0073】

実施形態3に係る表示パネルLCP1は、白色画素を含んでもよい。この場合、表示パネルLCP2の1個の画素P IX 2 bが、平面視で、1個の緑色画素P IX Gと1個の青色画素P IX Bと1個の白色画素とに重畠してもよい。

【0074】

[実施形態4]

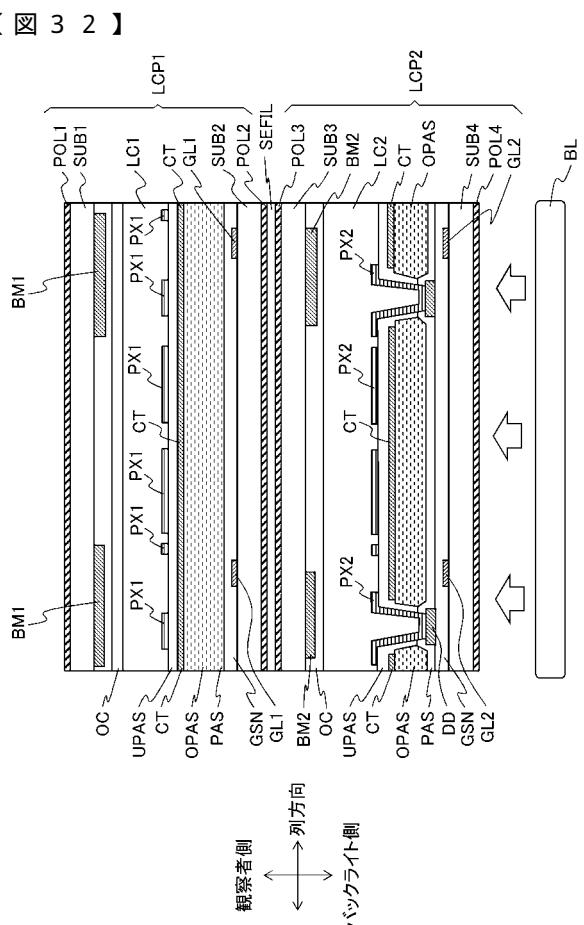

図26は実施形態4に係る表示パネルLCP1の概略構成を示す平面図であり、図27は実施形態4に係る表示パネルLCP2の概略構成を示す平面図である。概略的には、実施形態4に係る表示パネルLCP1の構成は、実施形態3に係る表示パネルLCP2の構

50

成（図20参照）と同一であり、実施形態4に係る表示パネルLCP2の構成は、実施形態3に係る表示パネルLCP1の構成（図19参照）と同一である。すなわち、実施形態4に係る液晶表示装置LCDでは、表示パネルLCP1が白黒画像を表示し、表示パネルLCP2がカラー画像を表示する。

【0075】

実施形態4に係る表示パネルLCP1では、図26に示すように、平面的に見て、複数のソース線SL1は、複数のソース線SL1aと、複数のソース線SL1bとを含んでいる。複数のソース線SL1aは、行方向に等間隔で配置されており、複数のソース線SL1bは、行方向に等間隔で配置されている。ソース線SL1a及びソース線SL1bは、行方向に交互に配置されている。表示パネルLCP1を平面的に見て、隣り合うソース線SL1a, SL1bと隣り合う2本のゲート線GL1とにより囲まれた領域（画素領域）に、2個の画素PIX1（PIX1a, PIX1b）が行方向に並んで配置されている。複数の画素PIX1は、マトリクス状（行方向及び列方向）に配置されている。ソース線SL1aと、該ソース線SL1aから離間して配置されたソース線SL1bとの間には、画素領域が形成されて2個の画素PIX1（PIX1a, PIX1b）が配置されている。一方、ソース線SL1aと、該ソース線SL1aに近接して配置されたソース線SL1bとの間には、画素領域が形成されていない。複数のゲート線GL1は、列方向に等間隔で配置されている。

10

【0076】

図28に示すように、表示パネルLCP1の対向基板CF1には、光を透過する光透過部と、光の透過を遮断するブラックマトリクスBM1とが形成されている。光透過部には、カラーフィルタFILが形成されておらず、例えばオーバーコート膜OCが形成されている。また、表示パネルLCP2の対向基板CF2には、光透過部と、ブラックマトリクスBM2とが形成されており、光透過部には、各画素PIX1に対応して複数のカラーフィルタFILが形成されている。

20

【0077】

図29は、平面視で互いに重なり合う、表示パネルLCP1の画素グループDOT1と、表示パネルLCP2の画素グループDOT2との関係を示す平面図であり、図30は、図29に対応する画素グループDOT1, DOT2の画素PIX1, PIX2の具体的な構成を示す平面図である。画素グループDOT1は、表示パネルLCP1の1個の画素PIX1a及び1個の画素PIX1bから成り、画素グループDOT2は、表示パネルLCP2の1個の赤色画素PIXR、1個の緑色画素PIXG及び1個の青色画素PIXBから成る。

30

【0078】

実施形態4に係る表示パネルLCP1は、単位面積当たりの画素PIX1の数が、表示パネルLCP2の単位面積当たりの画素PIX2の数より少なくなるように構成されている。具体的には、図29及び図30に示すように、表示パネルLCP1の1個の画素PIX1aと、表示パネルLCP2の1個の画素PIX2（1個の赤色画素PIXR）とが、平面視で互いに重畠し、表示パネルLCP1の1個の画素PIX1bと、表示パネルLCP2の2個の画素PIX2（1個の緑色画素PIXG及び1個の青色画素PIXB）とが、平面視で互いに重畠するように構成されている。表示パネルLCP2の各画素PIX2の面積（大きさ）が互いに等しい場合、表示パネルLCP1の画素PIX1aの面積は、表示パネルLCP2の1個の画素PIX2の面積と等しく、表示パネルLCP1の画素PIX1bの面積は、表示パネルLCP2の1個の画素PIX2の面積の2倍となっている。また1個の画素PIX1bの面積は、1個の緑色画素PIXGの面積と1個の青色画素PIXBの面積とを合計した面積に等しくなっている。

40

【0079】

図29（a）に示すように、画素PIX1aでは、ソース線SL1aが薄膜トランジスタTFT1aのソース電極に接続されており、ゲート線GL1が薄膜トランジスタTFT1aのゲート電極に接続されており、画素電極PX1a（図30（a）参照）が薄膜ト

50

ンジスタ TFT 1 a のドレイン電極 D D a ( 図 3 0 ( a ) 参照 ) に接続されている。また画素 PIX 1 b では、ソース線 S L 1 b が薄膜トランジスタ TFT 1 b のソース電極に接続されており、ゲート線 G L 1 が薄膜トランジスタ TFT 1 b のゲート電極に接続されており、画素電極 P X 1 b ( 図 3 0 ( a ) 参照 ) が薄膜トランジスタ TFT 1 b のドレイン電極 D D b ( 図 3 0 ( a ) 参照 ) に接続されている。また、表示パネル L C P 1 のブラックマトリクス B M 1 は、平面視で、表示パネル L C P 1 の複数のゲート線 G L 1 の各々に重なる複数の行ストライプ部分 B M 1 a と、平面視で、表示パネル L C P 1 のソース線 S L 1 , S L 2 に重なる複数の列ストライプ部分 B M 1 b とを含んでいる。図 3 0 に示すように、ブラックマトリクス B M 1 の行ストライプ部分 B M 1 a の列方向の長さ L 1 は、ブラックマトリクス B M 2 の行ストライプ部分 B M 2 a の列方向の長さ L 2 より長くなっている。またブラックマトリクス B M 1 の列ストライプ部分 B M 1 b の行方向の長さ W 1 は、ブラックマトリクス B M 2 の列ストライプ部分 B M 2 b の行方向の長さ W 2 より長くなっている。

10

## 【 0 0 8 0 】

図 3 1 は、図 3 0 の 3 1 - 3 1 ' 切断線における断面図であり、図 3 2 は、図 3 0 の 3 2 - 3 2 ' 切断線における断面図である。図 3 1 及び図 3 2 を用いて画素 PIX 1 , PIX 2 の断面構造について説明する。

## 【 0 0 8 1 】

図 3 1 に示すように、透明基板 S U B 2 のゲート絶縁膜 G S N 上にソース線 S L 1 a , S L 1 b が形成されている。ソース線 S L 1 a , S L 1 b は近接して配置されており、一組のソース線 S L 1 a , S L 1 b は、平面視で、ブラックマトリクス B M 1 の 1 本の列ストライプ部分 B M 1 b ( 図 3 0 ( a ) 参照 ) に重畳するように配置されている。

20

## 【 0 0 8 2 】

実施形態 4 の構成によれば、実施形態 3 の構成と同様に、表示パネル L C P 1 の画素 PIX 1 a と表示パネル L C P 2 の赤色画素 PIX R とが 1 対 1 の関係で配置されているため、互いに重畳する画素 PIX 1 a と赤色画素 PIX R のオン / オフを他の画素とは独立して制御することができる。このため、赤色の単色画像を表示する際に、緑色成分 G 及び青色成分 B の光漏れを抑えることができる。よって、従来の構成と比較して、赤色画像の色再現性を向上させることができる。

30

## 【 0 0 8 3 】

また、実施形態 4 に係る液晶表示装置 L C D では、表示パネル L C P 2 のブラックマトリクス B M 2 の行ストライプ部分 B M 2 a の列方向の長さ L 2 ( 図 3 0 参照 ) が、ブラックマトリクス B M 1 の行ストライプ部分 B M 1 a の列方向の長さ L 1 ( 図 3 0 参照 ) より短くなっている。また、ブラックマトリクス B M 2 の列ストライプ部分 B M 2 b の行方向の長さ W 2 ( 図 3 0 参照 ) が、ブラックマトリクス B M 1 の列ストライプ部分 B M 1 b の行方向の長さ W 1 ( 図 3 0 参照 ) より短くなっている。実施形態 4 に係る表示パネル L C P 1 は、図 6 6 の構成例 5 のパネル B に対応し、実施形態 4 に係る表示パネル L C P 2 は、図 6 6 の構成例 5 のパネル A に対応する。上記構成によれば、構成例 5 に示すように、表示パネル L C P 1 と表示パネル L C P 2 とに位置ずれが生じた場合でも、ブラックマトリクス B M 1 , B M 2 の位置ずれによる影響が小さいため、輝度ムラ及びモアレが生じ難くなる。よって、モアレの発生及び画素の開口率の低下を抑えることができる。

40

## 【 0 0 8 4 】

図 3 3 は、表示パネル L C P 1 及び表示パネル L C P 2 のドライバの構成を示す図である。表示パネル L C P 1 には、それぞれにソースドライバ I C ( S I C ) が実装された 4 個の T C P が接続されており、各 T C P がソースプリント基板 S K I B に接続されている。これに対して、表示パネル L C P 2 には、それぞれにソースドライバ I C ( S I C ) が実装された 6 個の T C P が接続されており、各 T C P がソースプリント基板 S K I B に接続されている。このように、表示パネル L C P 2 と比較して、表示パネル L C P 1 のソースドライバ I C の数を削減することができるため、液晶表示装置 L C D のコストを低減することができる。

50

## 【0085】

## [実施形態5]

実施形態5に係る表示パネルLCP1の構成は、実施形態4に係る表示パネルLCP1の構成と同一である。実施形態5に係る表示パネルLCP2の構成は、実施形態4に係る表示パネルLCP2の構成と比較すると、ブラックマトリクスBM2の構成が異なっており、それ以外の構成は同一である。

## 【0086】

図34は、実施形態5に係る液晶表示装置LCDにおいて、平面視で互いに重なり合う、表示パネルLCP1の画素グループDOT1の画素PIX1と、表示パネルLCP2の画素グループDOT2の画素PIX2との具体的な構成を示す平面図である。図35は、図34の35-35'切断線における断面図である。図34の32-32'切断線における断面構成は、図32に示す断面構成と同一である。

10

## 【0087】

実施形態5に係る表示パネルLCP2のブラックマトリクスBM2は、図34に示すように、ゲート線GL2に重なるように行方向に延在しており、ストライプ状に形成されている。すなわち、表示パネルLCP2のブラックマトリクスBM2は、平面視で、表示パネルLCP2の複数のゲート線GL2の各々に重なる複数の行ストライプ部分BM2aを含み、ソース線SL2全体を覆うような列方向に延在する部分を含まない。またブラックマトリクスBM2の行ストライプ部分BM2aの列方向の長さL2は、ブラックマトリクスBM1の行ストライプ部分BM1aの列方向の長さL1より短くなっている。

20

## 【0088】

実施形態5の構成によれば、実施形態4と同様の効果を得ることができる。また、実施形態5の構成では、表示パネルLCP2のブラックマトリクスBM2が列方向に形成されていないため、図66の構成例4と同様に、輝度ムラ及びモアレの発生、及び、画素の開口率の低下を抑えることができる。

30

## 【0089】

## [実施形態6]

図36は実施形態6に係る表示パネルLCP1の概略構成を示す平面図であり、図37は実施形態6に係る表示パネルLCP2の概略構成を示す平面図である。実施形態6に係る表示パネルLCP1の構成は、実施形態1に係る表示パネルLCP1の構成と同一である。

30

## 【0090】

実施形態6に係る表示パネルLCP2では、図37に示すように、平面的に見て、複数のソース線SL2は、複数のソース線SL2aと、複数のソース線SL2bとを含んでいる。複数のソース線SL2aは、行方向に等間隔で配置されており、複数のソース線SL2bは、行方向に等間隔で配置されている。ソース線SL2a及びソース線SL2bは、行方向に交互に配置されている。表示パネルLCP2を平面的に見て、隣り合うソース線SL2a, SL2bと隣り合う2本のゲート線GL2とにより囲まれた領域(画素領域)に、2個の画素PIX2(PIX2a, PIX2b)が行方向に並んで配置されている。複数の画素PIX2は、マトリクス状(行方向及び列方向)に配置されている。ソース線SL2aと、該ソース線SL2aから離間して配置されたソース線SL2bとの間には、画素領域が形成されて2個の画素PIX2(PIX2a, PIX2b)が配置されている。一方、ソース線SL2aと、該ソース線SL2aに近接して配置されたソース線SL2bとの間には、画素領域が形成されていない。複数のゲート線GL2は、列方向に等間隔で配置されている。表示パネルLCP2のゲート線GL2の本数は、表示パネルLCP1のゲート線GL1の本数の半分になっている。

40

## 【0091】

図38は、平面視で互いに重なり合う、表示パネルLCP1の画素グループDOT1と、表示パネルLCP2の画素グループDOT2との関係を示す平面図である。図39は、図38(a)に対応する画素グループDOT1の画素PIX1の具体的な構成を示す平面

50

図であり、図40は、図38(b)に対応する画素グループDOT2の画素PIX2の具体的な構成を示す平面図である。画素グループDOT1は、表示パネルLCP1の2個の赤色画素PIXR、2個の緑色画素PIXG及び2個の青色画素PIXBから成り、画素グループDOT2は、表示パネルLCP2の1個の画素PIX2a及び1個の画素PIX2bから成る。

#### 【0092】

実施形態6に係る表示パネルLCP2は、単位面積当たりの画素PIX2の数が、表示パネルLCP1の単位面積当たりの画素PIX1の数より少なくなるように構成されている。具体的には、図38及び図39に示すように、表示パネルLCP1の2個の画素PIX1(2個の赤色画素PIXR)と、表示パネルLCP2の1個の画素PIX2aとが、平面視で互いに重畠し、表示パネルLCP1の4個の画素PIX1(2個の緑色画素PIXG及び2個の青色画素PIXB)と、表示パネルLCP2の1個の画素PIX2bとが、平面視で互いに重畠するように構成されている。表示パネルLCP1の各画素PIX1の面積(大きさ)が互いに等しい場合、表示パネルLCP2の画素PIX2aの面積は、表示パネルLCP1の1個の画素PIX1の面積の2倍と等しく、表示パネルLCP2の画素PIX2bの面積は、表示パネルLCP2の1個の画素PIX1の面積の4倍と等しい。

10

#### 【0093】

図39及び図40に示すように、ブラックマトリクスBM2の行ストライプ部分BM2aの列方向の長さL2は、ブラックマトリクスBM1の行ストライプ部分BM1aの列方向の長さL1より短くなっている。また、行ストライプ部分BM2aにおける、薄膜トランジスタTFT2a, TFT2bの間の領域(中央部分)の列方向の長さL3は、薄膜トランジスタTFT2a, TFT2bを覆う部分の列方向の長さL2より短くなっている。

20

#### 【0094】

図41は、図39及び図40の41-41'切断線における断面図である。図39及び図40の23-23'切断線における断面構成は、図23に示す断面構成と同一である。図41に示すように、ゲート線GL2は、平面視でゲート線GL1に重畠するように配置され、共通配線CLは、行方向に延在し、ブラックマトリクスBM1に重畠するように配置されている。

30

#### 【0095】

実施形態6の構成によれば、表示パネルLCP1の2個の赤色画素PIXRと表示パネルLCP2の1個の画素PIX2aとが1対1の関係で配置されているため、互いに重畠する赤色画素PIXRと画素PIX2aのオン/オフを他の画素とは独立して制御することができる。このため、赤色の単色画像を表示する際に、緑色成分G及び青色成分Bの光漏れを抑えることができる。よって、従来の構成と比較して、赤色画像の色再現性を向上させることができる。また、実施形態3の構成と比較して、ブラックマトリクスBM2の行ストライプ部分BM2aの本数が少ないため、輝度ムラ及びモアレの発生、及び、画素の開口率の低下をさらに抑えることができる。

#### 【0096】

図42は、表示パネルLCP1及び表示パネルLCP2のドライバの構成を示す図である。表示パネルLCP1には、それぞれにソースドライバIC(SIC)が実装された6個のTCPが接続されており、各TCPがソースプリント基板SKIBに接続されている。これに対して、表示パネルLCP2には、それぞれにソースドライバIC(SIC)が実装された4個のTCPが接続されており、各TCPがソースプリント基板SKIBに接続されている。また表示パネルLCP1には、4個のゲートドライバIC(GIC)が実装されているのに対して、表示パネルLCP2には、2個のゲートドライバIC(GIC)が実装されている。このように、表示パネルLCP1と比較して、表示パネルLCP2のソースドライバIC及びゲートドライバICの数を削減することができるため、液晶表示装置LCDのコストを低減することができる。

40

#### 【0097】

50

## [実施形態7]

図43は実施形態7に係る表示パネルLCP2の概略構成を示す平面図である。実施形態7に係る表示パネルLCP1の構成は、実施形態3に係る表示パネルLCP1の構成(図19参照)と同一である。

## 【0098】

実施形態7に係る表示パネルLCP2では、図43に示すように、複数のゲート線GL2は、複数のゲート線GL2aと、複数のゲート線GL2bとを含んでいる。複数のゲート線GL2aは、列方向に等間隔で配置されており、複数のゲート線GL2bは、列方向に等間隔で配置されている。ゲート線GL2a及びゲート線GL2bは、列方向に交互に配置されている。表示パネルLCP2を平面的に見て、隣り合うゲート線GL2a, GL2bと、隣り合う2本のソース線SL2とにより囲まれた領域(画素領域)に、2個の画素PIX2(PIX2a, PIX2b)が行方向に並んで配置されている。複数の画素PIX2は、マトリクス状(行方向及び列方向)に配置されている。ゲート線GL2aと、該ゲート線GL2aから離間して配置されたゲート線GL2bとの間には、画素領域が形成されて2個の画素PIX2(PIX2a, PIX2b)が配置されている。一方、ゲート線GL2aと、該ゲート線GL2aに近接して配置されたゲート線GL2bとの間には、画素領域が形成されていない。また、表示パネルLCP2のゲート線GL2の本数は、表示パネルLCP1のゲート線GL1の本数の2倍になっている。また、表示パネルLCP1のゲート線GL1と、表示パネルLCP2のゲート線GL2とは、平面視で互いに重畠するように配置されている。尚、表示パネルLCP1のゲート線GL1は、平面視で、表示パネルLCP2のゲート線GL2aに重畠してもよいし、表示パネルLCP2のゲート線GL2bに重畠してもよいし、ゲート線GL2a, GL2bの間の領域に重畠してもよい。複数のソース線SL2は、行方向に等間隔で配置されている。

## 【0099】

図44は、平面視で互いに重なり合う、表示パネルLCP1の画素グループDOT1と、表示パネルLCP2の画素グループDOT2との関係を示す平面図であり、図45は、図44に対応する画素グループDOT1, DOT2の画素PIX1, PIX2の具体的な構成を示す平面図である。画素グループDOT1は、表示パネルLCP1の1個の赤色画素PIXR、1個の緑色画素PIXG及び1個の青色画素PIXBから成り、画素グループDOT2は、表示パネルLCP2の1個の画素PIX2a及び1個の画素PIX2bから成る。

## 【0100】

平面視で、表示パネルLCP2の画素PIX2aは、表示パネルLCP1の赤色画素PIXRに重畠し、表示パネルLCP2の画素PIX2bは、表示パネルLCP1の緑色画素PIXG及び青色画素PIXBに重畠している。

## 【0101】

図44(b)に示すように、画素PIX2aでは、ソース線SL2(ここでは、ソース線SL2sとする。)が薄膜トランジスタTFT2aのソース電極に接続されており、ゲート線GL2aが薄膜トランジスタTFT2aのゲート電極に接続されており、画素電極PX2a(図45(b)参照)が薄膜トランジスタTFT2aのドレイン電極DDa(図45(b)参照)に接続されている。また画素PIX2bでは、ソース線SL2sの延伸部SD(図45(b)参照)が薄膜トランジスタTFT2bのソース電極に接続されており、ゲート線GL2bが薄膜トランジスタTFT2bのゲート電極に接続されており、画素電極PX2b(図45(b)参照)が薄膜トランジスタTFT2bのドレイン電極DDb(図45(b)参照)に接続されている。

## 【0102】

図45に示すように、表示パネルLCP2のブラックマトリクスBM2は、ゲート線GL2に重なるように行方向に延在しており、ストライプ状に形成されている。すなわち、表示パネルLCP2のブラックマトリクスBM2は、平面視で、表示パネルLCP2のゲート線GL2に重なる複数の行ストライプ部分BM2aを含んでいる。ブラックマトリク

10

20

30

40

50

ス B M 2 は、平面視でソース線 S L 2 全体を覆うような列方向に延在する部分を含まない。また、図 4 5 に示すように、ブラックマトリクス B M 2 の行ストライプ部分 B M 2 a の列方向の長さ L 2 は、ゲート線 G L 2 a の列方向の長さとゲート線 G L 2 b の列方向の長さとを合計した長さ（2 本分のゲート線 G L 2 の列方向の長さ）より長くなっている。また、ブラックマトリクス B M 2 の行ストライプ部分 B M 2 a の列方向の長さ L 2 は、ブラックマトリクス B M 1 の行ストライプ部分 B M 1 a の列方向の長さ L 1 より長くなっている。

#### 【 0 1 0 3 】

図 4 6 は、図 4 5 の 4 6 - 4 6 ' 切断線における断面図である。図 4 6 に示すように、ソース線 S L 1 , S L 2 はそれぞれ行方向に等間隔に配置されている。また平面視で、ソース線 S L 2 は、青色画素 P I X B と赤色画素 P I X R との境界部分に配置されている。

10

#### 【 0 1 0 4 】

このように、表示パネル L C P 2 では、平面視で、画素電極 P X 2 a (図 4 5 (b) 参照) に電気的に接続されたゲート線 G L 2 a が、該画素電極 P X 2 a の下側に配置されており、画素電極 P X 2 b (図 4 5 (b) 参照) に電気的に接続されたゲート線 G L 2 b が、該画素電極 P X 2 b の上側に配置されている。また画素電極 P X 2 a , P X 2 b は、同一のソース線 S L 2 (図 4 5 (b) ではソース線 S L 2 s ) に電気的に接続されている。上記構成では、表示パネル L C P 2 は、表示パネル L C P 1 におけるフレーム周波数（例えば 60 Hz）の 2 倍のフレーム周波数（例えば 120 Hz）で駆動（2 倍速駆動）を行う。

20

#### 【 0 1 0 5 】

実施形態 7 の構成によれば、実施形態 3 の構成と同様に、表示パネル L C P 1 の赤色画素 P I X R と表示パネル L C P 2 の画素 P I X 2 a とが 1 対 1 の関係で配置されているため、互いに重畠する赤色画素 P I X R と画素 P I X 2 a とのオン / オフを他の画素とは独立して制御することができる。このため、赤色の単色画像を表示する際に、緑色成分 G 及び青色成分 B の光漏れを抑えることができる。よって、従来の構成と比較して、赤色画像の色再現性を向上させることができる。また、輝度ムラ及びモアレの発生、及び、画素の開口率の低下を抑えることもできる。

#### 【 0 1 0 6 】

図 4 7 は、表示パネル L C P 1 及び表示パネル L C P 2 のドライバの構成を示す図である。表示パネル L C P 1 には、それぞれにソースドライバ I C (S I C) が実装された 6 個の T C P が接続されており、各 T C P がソースプリント基板 S K I B に接続されている。これに対して、表示パネル L C P 2 には、それぞれにソースドライバ I C (S I C) が実装された 2 個の T C P が接続されており、各 T C P がソースプリント基板 S K I B に接続されている。また表示パネル L C P 1 には、4 個のゲートドライバ I C (G I C) が実装されているのに対して、表示パネル L C P 2 には、8 個のゲートドライバ I C (G I C) が実装されている。

30

#### 【 0 1 0 7 】

#### [ 実施形態 8 ]

図 4 8 は実施形態 8 に係る表示パネル L C P 2 の概略構成を示す平面図である。実施形態 8 に係る表示パネル L C P 1 の構成は、実施形態 6 に係る表示パネル L C P 1 の構成（図 3 6 参照）と同一である。

40

#### 【 0 1 0 8 】

実施形態 8 に係る表示パネル L C P 2 では、図 4 8 に示すように、複数のゲート線 G L 2 は、複数のゲート線 G L 2 a と、複数のゲート線 G L 2 b とを含んでいる。複数のゲート線 G L 2 a は、列方向に等間隔で配置されており、複数のゲート線 G L 2 b は、列方向に等間隔で配置されている。ゲート線 G L 2 a 及びゲート線 G L 2 b は、列方向に交互に配置されている。表示パネル L C P 2 を平面的に見て、隣り合うゲート線 G L 2 a , G L 2 b と、隣り合う 2 本のソース線 S L 2 とにより囲まれた領域（画素領域）に、2 個の画素 P I X 2 (P I X 2 a , P I X 2 b) が行方向に並んで配置されている。複数の画素 P

50

I X 2 は、マトリクス状（行方向及び列方向）に配置されている。ゲート線 G L 2 a と、該ゲート線 G L 2 a から離間して配置されたゲート線 G L 2 b との間には、画素領域が形成されて 2 個の画素 P I X 2 ( P I X 2 a , P I X 2 b ) が配置されている。一方、ゲート線 G L 2 a と、該ゲート線 G L 2 a に近接して配置されたゲート線 G L 2 b との間には、画素領域が形成されていない。複数のソース線 S L 2 は、行方向に等間隔で配置されている。

【 0 1 0 9 】

図 4 9 は、平面視で互いに重なり合う、表示パネル L C P 1 の画素グループ D O T 1 と、表示パネル L C P 2 の画素グループ D O T 2 との関係を示す平面図であり、図 5 0 は、図 4 9 ( b ) に対応する画素グループ D O T 2 の画素 P I X 2 の具体的な構成を示す平面図である。尚、図 4 9 ( a ) に対応する画素グループ D O T 1 の画素 P I X 1 の具体的な構成は、図 3 9 に示す構成と同一である。画素グループ D O T 1 は、表示パネル L C P 1 の 2 個の赤色画素 P I X R 、 2 個の緑色画素 P I X G 及び 2 個の青色画素 P I X B から成り、画素グループ D O T 2 は、表示パネル L C P 2 の 1 個の画素 P I X 2 a 及び 1 個の画素 P I X 2 b から成る。

10

【 0 1 1 0 】

平面視で、表示パネル L C P 2 の画素 P I X 2 a は、表示パネル L C P 1 の 2 個の画素 P I X 1 ( 2 個の赤色画素 P I X R ) に重畠し、表示パネル L C P 2 の画素 P I X 2 b は、表示パネル L C P 1 の 4 個の画素 P I X 1 ( 2 個の緑色画素 P I X G 及び 2 個の青色画素 P I X B ) に重畠している。

20

【 0 1 1 1 】

図 4 9 ( b ) に示すように、画素 P I X 2 a では、ソース線 S L 2 ( ここでは、ソース線 S L 2 s とする。 ) が薄膜トランジスタ T F T 2 a のソース電極に接続されており、ゲート線 G L 2 a が薄膜トランジスタ T F T 2 a のゲート電極に接続されており、画素電極 P X 2 a ( 図 5 0 参照 ) が薄膜トランジスタ T F T 2 a のドレイン電極 D D a ( 図 5 0 参照 ) に接続されている。また画素 P I X 2 b では、ソース線 S L 2 s の延伸部 S D ( 図 5 0 参照 ) が薄膜トランジスタ T F T 2 b のソース電極に接続されており、ゲート線 G L 2 b が薄膜トランジスタ T F T 2 b のゲート電極に接続されており、画素電極 P X 2 b ( 図 5 0 参照 ) が薄膜トランジスタ T F T 2 b のドレイン電極 D D b ( 図 5 0 参照 ) に接続されている。

30

【 0 1 1 2 】

図 5 0 に示すように、表示パネル L C P 2 のブラックマトリクス B M 2 は、ゲート線 G L 2 に重なるように行方向に延在しており、ストライプ状に形成されている。すなわち、表示パネル L C P 2 のブラックマトリクス B M 2 は、平面視で、表示パネル L C P 2 のゲート線 G L 2 に重なる複数の行ストライプ部分 B M 2 a を含んでいる。ブラックマトリクス B M 2 は、平面視でソース線 S L 2 全体を覆うような列方向に延在する部分を含まない。また、図 5 0 に示すように、ブラックマトリクス B M 2 の行ストライプ部分 B M 2 a の列方向の長さ L 2 は、ゲート線 G L 2 a の列方向の長さとゲート線 G L 2 b の列方向の長さとを合計した長さ ( 2 本分のゲート線 G L 2 の列方向の長さ ) より長くなっている。また、ブラックマトリクス B M 2 の行ストライプ部分 B M 2 a の列方向の長さ L 2 は、ブラックマトリクス B M 1 の行ストライプ部分 B M 1 a の列方向の長さ L 1 ( 図 3 9 参照 ) より長くなっている。

40

【 0 1 1 3 】

図 5 0 の 4 6 - 4 6 ' 切断線における断面構成は、図 4 6 に示す構成と同一である。

【 0 1 1 4 】

このように、表示パネル L C P 2 では、平面視で、画素電極 P X 2 a ( 図 5 0 参照 ) に電気的に接続されたゲート線 G L 2 a が、該画素電極 P X 2 a の下側に配置されており、画素電極 P X 2 b ( 図 5 0 参照 ) に電気的に接続されたゲート線 G L 2 b が、該画素電極 P X 2 b の上側に配置されている。また画素電極 P X 2 a , P X 2 b は、同一のソース線 S L 2 ( 図 5 0 ではソース線 S L 2 s ) に電気的に接続されている。上記構成では、表示

50

パネル L C P 2 は、表示パネル L C P 1 におけるフレーム周波数（例えば 60 Hz）の 2 倍のフレーム周波数（例えば 120 Hz）で駆動（2 倍速駆動）を行う。また、表示パネル L C P 2 は、各ゲート線 G L 2 の選択時間（書き込み時間）を、表示パネル L C P 1 における各ゲート線 G L 1 の選択時間（1 水平期間）の 2 倍（2 H）とする。

【0115】

実施形態 8 の構成によれば、実施形態 6 の構成と同様に、表示パネル L C P 1 の 2 個の赤色画素 P IX R と表示パネル L C P 2 の 1 個の画素 P IX 2 a とが 1 対 1 の関係で配置されているため、互いに重畠する赤色画素 P IX R と画素 P IX 2 a のオン／オフを他の画素とは独立して制御することができる。このため、赤色の単色画像を表示する際に、緑色成分 G 及び青色成分 B の光漏れを抑えることができる。よって、従来の構成と比較して、赤色画像の色再現性を向上させることができる。また、実施形態 6 の構成と同様に、輝度ムラ及びモアレの発生、及び、画素の開口率の低下を抑えることができる。

10

【0116】

図 51 は、表示パネル L C P 1 及び表示パネル L C P 2 のドライバの構成を示す図である。表示パネル L C P 1 には、それぞれにソースドライバ IC (S I C) が実装された 6 個の T C P が接続されており、各 T C P がソースプリント基板 S K I B に接続されている。これに対して、表示パネル L C P 2 には、それぞれにソースドライバ IC (S I C) が実装された 2 個の T C P が接続されており、各 T C P がソースプリント基板 S K I B に接続されている。このように、表示パネル L C P 1 と比較して、表示パネル L C P 2 のソースドライバ IC の数を削減することができるため、液晶表示装置 LCD のコストを低減することができる。

20

【0117】

[実施形態 9]

図 52 は実施形態 9 に係る表示パネル L C P 1 の概略構成を示す平面図であり、図 53 は実施形態 9 に係る表示パネル L C P 2 の概略構成を示す平面図である。実施形態 9 に係る表示パネル L C P 1 の構成は、実施形態 1 に係る表示パネル L C P 1 の構成と同一である。

【0118】

実施形態 9 に係る表示パネル L C P 2 では、図 53 に示すように、複数のゲート線 G L 2 は、複数のゲート線 G L 2 a と、複数のゲート線 G L 2 b とを含んでいる。複数のゲート線 G L 2 a は、列方向に等間隔で配置されており、複数のゲート線 G L 2 b は、列方向に等間隔で配置されている。ゲート線 G L 2 a 及びゲート線 G L 2 b は、列方向に交互に配置されている。複数のソース線 S L 2 は、複数のソース線 S L 2 a と、複数のソース線 S L 2 b と、複数のソース線 S L 2 c とを含んでいる。ソース線 S L 2 a, S L 2 b, S L 2 c は、行方向にこの順に繰り返し配置されている。また、表示パネル L C P 2 を平面的に見て、隣り合うゲート線 G L 2 a, G L 2 b と、隣り合うソース線 S L 2 a, S L 2 b とにより囲まれた領域（画素領域）に、3 個の画素 P IX 2 (P IX 2 a, P IX 2 b, P IX 2 c) が行方向に並んで配置されている。同様に、表示パネル L C P 2 を平面的に見て、隣り合うゲート線 G L 2 a, G L 2 b と、隣り合うソース線 S L 2 b, S L 2 c とにより囲まれた領域（画素領域）に、3 個の画素 P IX 2 (P IX 2 a, P IX 2 b, P IX 2 c) が行方向に並んで配置されている。また、複数の画素 P IX 2 は、マトリクス状（行方向及び列方向）に配置されている。ゲート線 G L 2 a と、該ゲート線 G L 2 a から離間して配置されたゲート線 G L 2 b との間には、画素領域が形成されて 3 個の画素 P IX 2 (P IX 2 a, P IX 2 b, P IX 2 c) が配置されている。一方、ゲート線 G L 2 a と、該ゲート線 G L 2 a に近接して配置されたゲート線 G L 2 b との間には、画素領域が形成されていない。また、ソース線 S L 2 a と、該ソース線 S L 2 a から離間して配置されたソース線 S L 2 b との間には、画素領域が形成されて 3 個の画素 P IX 2 (P IX 2 a, P IX 2 b, P IX 2 c) が配置され、同様に、ソース線 S L 2 b と、該ソース線 S L 2 b から離間して配置されたソース線 S L 2 c との間には、画素領域が形成されて 3 個の画素 P IX 2 (P IX 2 a, P IX 2 b, P IX 2 c) が配置されている。一方

30

40

50

、ソース線 S L 2 a と、該ソース線 S L 2 a に近接して配置されたソース線 S L 2 c との間には、画素領域が形成されていない。また、表示パネル L C P 2 のゲート線 G L 2 の本数は、表示パネル L C P 1 のゲート線 G L 1 の本数の 2 倍になっている。また、表示パネル L C P 1 のゲート線 G L 1 と、表示パネル L C P 2 のゲート線 G L 2 とは、平面視で互いに重畠するように配置されている。尚、表示パネル L C P 1 のゲート線 G L 1 は、平面視で、表示パネル L C P 2 のゲート線 G L 2 a に重畠してもよいし、表示パネル L C P 2 のゲート線 G L 2 b に重畠してもよいし、ゲート線 G L 2 a , G L 2 b の間の領域に重畠してもよい。

#### 【 0 1 1 9 】

図 5 4 は、平面視で互いに重なり合う、表示パネル L C P 1 の画素グループ D O T 1 と、表示パネル L C P 2 の画素グループ D O T 2 との関係を示す平面図である。画素グループ D O T 1 は、表示パネル L C P 1 の 2 個の赤色画素 P I X R 、 2 個の緑色画素 P I X G 及び 2 個の青色画素 P I X B から成り、画素グループ D O T 2 は、表示パネル L C P 2 の 2 個の画素 P I X 2 a 、 2 個の画素 P I X 2 b 及び 2 個の画素 P I X 2 c から成る。以下では、説明の便宜上、図 5 4 に示すように、画素グループ D O T 2 のうちソース線 S L 2 a , S L 2 b の間に配置された左側の 3 個の画素 P I X 2 をそれぞれ、画素 P I X 2 a L , 画素 P I X 2 b L , 及び画素 P I X 2 c L と称し、ソース線 S L 2 b , S L 2 c の間に配置された右側の 3 個の画素 P I X 2 をそれぞれ、画素 P I X 2 a R , 画素 P I X 2 b R , 及び画素 P I X 2 c R と称す。

#### 【 0 1 2 0 】

平面視で、表示パネル L C P 2 の画素 P I X 2 a ( 画素 P I X 2 a L , P I X 2 a R ) は、表示パネル L C P 1 の赤色画素 P I X R に重畠し、表示パネル L C P 2 の画素 P I X 2 b ( 画素 P I X 2 b L , P I X 2 b R ) は、表示パネル L C P 1 の緑色画素 P I X G に重畠し、表示パネル L C P 2 の画素 P I X 2 c ( 画素 P I X 2 c L , P I X 2 c R ) は、表示パネル L C P 1 の青色画素 P I X B に重畠している。

#### 【 0 1 2 1 】

図 5 4 ( b ) に示すように、画素 P I X 2 a L では、ソース線 S L 2 a が薄膜トランジスタ T F T 2 a L のソース電極に接続されており、ゲート線 G L 2 a が薄膜トランジスタ T F T 2 a L のゲート電極に接続されており、画素電極 P X 2 a L が薄膜トランジスタ T F T 2 a L のドレイン電極に接続されている。画素 P I X 2 b L では、ソース線 S L 2 a が薄膜トランジスタ T F T 2 b L のソース電極に接続されており、ゲート線 G L 2 b が薄膜トランジスタ T F T 2 b L のゲート電極に接続されており、画素電極 P X 2 b L が薄膜トランジスタ T F T 2 b L のドレイン電極に接続されている。画素 P I X 2 c L では、ソース線 S L 2 b が薄膜トランジスタ T F T 2 c L のソース電極に接続されており、ゲート線 G L 2 b が薄膜トランジスタ T F T 2 c L のゲート電極に接続されており、画素電極 P X 2 c L が薄膜トランジスタ T F T 2 c L のドレイン電極に接続されている。

#### 【 0 1 2 2 】

画素 P I X 2 a R では、ソース線 S L 2 b が薄膜トランジスタ T F T 2 a R のソース電極に接続されており、ゲート線 G L 2 a が薄膜トランジスタ T F T 2 a R のゲート電極に接続されており、画素電極 P X 2 a R が薄膜トランジスタ T F T 2 a R のドレイン電極に接続されている。画素 P I X 2 b R では、ソース線 S L 2 c が薄膜トランジスタ T F T 2 b R のソース電極に接続されており、ゲート線 G L 2 b が薄膜トランジスタ T F T 2 b R のゲート電極に接続されており、画素電極 P X 2 b R が薄膜トランジスタ T F T 2 b R のドレイン電極に接続されている。画素 P I X 2 c R では、ソース線 S L 2 c が薄膜トランジスタ T F T 2 c R のソース電極に接続されており、ゲート線 G L 2 a が薄膜トランジスタ T F T 2 c R のゲート電極に接続されており、画素電極 P X 2 c R が薄膜トランジスタ T F T 2 c R のドレイン電極に接続されている。表示パネル L C P 2 では、画素グループ D O T 2 がマトリクス状 ( 行方向及び列方向 ) に複数配置されている。

#### 【 0 1 2 3 】

表示パネル L C P 2 のブラックマトリクス B M 2 は、実施形態 7 の構成 ( 図 4 5 ( b ) )

10

20

30

40

50

参照)と同様に、ゲート線 G L 2 に重なるように行方向に延在しており、ストライプ状に形成されている。上記構成では、表示パネル L C P 2 は、表示パネル L C P 1 におけるフレーム周波数(例えば 60 Hz)の 2 倍のフレーム周波数(例えば 120 Hz)で駆動(2 倍速駆動)を行う。

#### 【0124】

実施形態 9 の構成によれば、実施形態 1 の構成と同様に、表示パネル L C P 1 の各画素 P I X 1 と表示パネル L C P 2 の各画素 P I X 2 とが 1 対 1 の関係で配置されているため、互いに重畠する各画素 P I X 1, P I X 2 のオン/オフを独立して制御することができる。このため、従来の構成と比較して、光漏れを低減することができるため、各色の単色画像の色再現性を向上させることができる。また、輝度ムラ及びモアレの発生、及び、画素の開口率の低下を抑えることもできる。

10

#### 【0125】

図 5 5 は、表示パネル L C P 1 及び表示パネル L C P 2 のドライバの構成を示す図である。表示パネル L C P 1 には、それぞれにソースドライバ I C (S I C) が実装された 6 個の T C P が接続されており、各 T C P がソースプリント基板 S K I B に接続されている。これに対して、表示パネル L C P 2 には、それぞれにソースドライバ I C (S I C) が実装された 3 個の T C P が接続されており、各 T C P がソースプリント基板 S K I B に接続されている。また表示パネル L C P 1 には、4 個のゲートドライバ I C (G I C) が実装されているのに対して、表示パネル L C P 2 には、8 個のゲートドライバ I C (G I C) が実装されている。

20

#### 【0126】

##### 【実施形態 10】

図 5 6 は実施形態 10 に係る表示パネル L C P 1 の概略構成を示す平面図であり、図 5 7 は実施形態 10 に係る表示パネル L C P 2 の概略構成を示す平面図である。実施形態 10 に係る液晶表示装置 L C D では、概略的には、表示パネル L C P 1 は、実施形態 9 に係る表示パネル L C P 1(図 5 2 参照)において、青色画素 P I X B と赤色画素 P I X R との間に白色画素 P I X W が追加された構成を有し、表示パネル C L P 2 は、実施形態 9 に係る表示パネル L C P 2(図 5 3 参照)において、白色画素 P I X W に重畠する画素 P I X 2 d が追加された構成を有している。

30

#### 【0127】

また、実施形態 10 に係る表示パネル L C P 2 では、複数のソース線 S L 2 は、複数のソース線 S L 2 a と、複数のソース線 S L 2 b とを含んでいる。複数のソース線 S L 2 a は、行方向に等間隔で配置されており、複数のソース線 S L 2 b は、行方向に等間隔で配置されている。ソース線 S L 2 a, S L 2 b は、行方向に交互に配置されている。表示パネル L C P 2 を平面的に見て、隣り合うゲート線 G L 2 a, G L 2 b と、隣り合うソース線 S L 2 a, S L 2 b とにより囲まれた領域(画素領域)に、4 個の画素 P I X 2 (P I X 2 a, P I X 2 b, P I X 2 c, P I X 2 d) が行方向に並んで配置されている。複数の画素 P I X 2 は、マトリクス状(行方向及び列方向)に配置されている。ゲート線 G L 2 a と、該ゲート線 G L 2 a から離間して配置されたゲート線 G L 2 b との間には、画素領域が形成されて 4 個の画素 P I X 2 (P I X 2 a, P I X 2 b, P I X 2 c, P I X 2 d) が配置されている。一方、ゲート線 G L 2 a と、該ゲート線 G L 2 a に近接して配置されたゲート線 G L 2 b との間には、画素領域が形成されていない。また、ソース線 S L 2 a と、該ソース線 S L 2 a から離間して配置されたソース線 S L 2 b との間には、画素領域が形成されて 4 個の画素 P I X 2 (P I X 2 a, P I X 2 b, P I X 2 c, P I X 2 d) が配置されている。一方、ソース線 S L 2 a と、該ソース線 S L 2 a に近接して配置されたソース線 S L 2 b との間には、画素領域が形成されていない。

40

#### 【0128】

図 5 8 は、平面視で互いに重なり合う、表示パネル L C P 1 の画素グループ D O T 1 と、表示パネル L C P 2 の画素グループ D O T 2 との関係を示す平面図である。画素グループ D O T 1 は、表示パネル L C P 1 の 1 個の赤色画素 P I X R、1 個の緑色画素 P I X G

50

、1個の青色画素PIXB、及び1個の白色画素PIXWから成り、画素グループDOT2は、表示パネルLCP2の1個の画素PIX2a、1個の画素PIX2b、1個の画素PIX2c、及び1個の画素PIX2dから成る。

【0129】

平面視で、表示パネルLCP2の画素PIX2aは、表示パネルLCP1の赤色画素PIXRに重畠し、表示パネルLCP2の画素PIX2bは、表示パネルLCP1の緑色画素PIXGに重畠し、表示パネルLCP2の画素PIX2cは、表示パネルLCP1の青色画素PIXBに重畠し、表示パネルLCP2の画素PIX2dは、表示パネルLCP1の白色画素PIXWに重畠している。

【0130】

図58(b)に示すように、画素PIX2aでは、ソース線SL2aが薄膜トランジスタTFT2aのソース電極に接続されており、ゲート線GL2aが薄膜トランジスタTFT2aのゲート電極に接続されており、画素電極PX2aが薄膜トランジスタTFT2aのドレイン電極に接続されている。画素PIX2bでは、ソース線SL2aが薄膜トランジスタTFT2bのソース電極に接続されており、ゲート線GL2bが薄膜トランジスタTFT2bのゲート電極に接続されており、画素電極PX2bが薄膜トランジスタTFT2bのドレイン電極に接続されている。画素PIX2cでは、ソース線SL2bが薄膜トランジスタTFT2cのソース電極に接続されており、ゲート線GL2bが薄膜トランジスタTFT2cのゲート電極に接続されており、画素電極PX2cが薄膜トランジスタTFT2cのドレイン電極に接続されている。画素PIX2dでは、ソース線SL2bが薄膜トランジスタTFT2dのソース電極に接続されており、ゲート線GL2aが薄膜トランジスタTFT2dのゲート電極に接続されており、画素電極PX2dが薄膜トランジスタTFT2dのドレイン電極に接続されている。

【0131】

表示パネルLCP2のブラックマトリクスBM2は、実施形態7の構成(図45(b)参照)と同様に、ゲート線GL2に重なるように行方向に延在しており、ストライプ状に形成されている。上記構成では、表示パネルLCP2は、表示パネルLCP1におけるフレーム周波数(例えば60Hz)の2倍のフレーム周波数(例えば120Hz)で駆動(2倍速駆動)を行う。

【0132】

実施形態10の構成によれば、実施形態1の構成と同様に、表示パネルLCP1の各画素PIX1と表示パネルLCP2の各画素PIX2とが1対1の関係で配置されているため、互いに重畠する各画素PIX1, PIX2のオン/オフを独立して制御することができる。このため、従来の構成と比較して、光漏れを低減することができるため、各色の単色画像の色再現性を向上させることができる。また、輝度ムラ及びモアレの発生、及び、画素の開口率の低下を抑えることもできる。

【0133】

表示パネルLCP1及び表示パネルLCP2のドライバの構成は、図55に示す構成と同一である。

【0134】

[実施形態11]

図59は実施形態11に係る表示パネルLCP1の概略構成を示す平面図であり、図60は実施形態11に係る表示パネルLCP2の概略構成を示す平面図である。

【0135】

図59に示すように、実施形態11に係る表示パネルLCP1は、複数の赤色画素PIXRと、複数の緑色画素PIXGと、複数の青色画素PIXBと、複数の白色画素PIXWとを含んでいる。例えば、第n行目には、行方向に赤色画素PIXRと緑色画素PIXGとが交互に並んで配置されており、第(n+1)行目には、行方向に青色画素PIXBと白色画素PIXWとが交互に並んで配置されている。また第m列目には、列方向に赤色画素PIXRと青色画素PIXBとが交互に並んで配置されており、第(m+1)列目に

10

20

30

40

50

は、列方向に緑色画素 P IX G と白色画素 P IX W とが交互に並んで配置されている。

【 0 1 3 6 】

図 6 0 に示すように、実施形態 1 1 に係る表示パネル L C P 2 は、複数の画素 P IX 2 a と、複数の画素 P IX 2 b と、複数の画素 P IX 2 c と、複数の画素 P IX 2 d とを含んでいる。例えば、第 n 行目には、行方向に画素 P IX 2 a と画素 P IX 2 b とが交互に並んで配置されており、第 ( n + 1 ) 行目には、行方向に画素 P IX 2 c と画素 P IX 2 d とが交互に並んで配置されている。また第 m 列目には、列方向に画素 P IX 2 a と画素 P IX 2 c とが交互に並んで配置されており、第 ( m + 1 ) 列目には、列方向に画素 P IX 2 b と画素 P IX 2 d とが交互に並んで配置されている。

【 0 1 3 7 】

実施形態 1 1 に係る表示パネル L C P 2 では、複数のゲート線 G L 2 は、複数のゲート線 G L 2 a と、複数のゲート線 G L 2 b とを含んでいる。複数のゲート線 G L 2 a は、列方向に等間隔で配置されており、複数のゲート線 G L 2 b は、列方向に等間隔で配置されている。ゲート線 G L 2 a 及びゲート線 G L 2 b は、列方向に交互に配置されている。複数のソース線 S L 2 は、複数のソース線 S L 2 a と、複数のソース線 S L 2 b とを含んでいる。複数のソース線 S L 2 a は、行方向に等間隔で配置されており、複数のソース線 S L 2 b は、行方向に等間隔で配置されている。ソース線 S L 2 a , S L 2 b は、行方向に交互に配置されている。表示パネル L C P 2 を平面的に見て、隣り合うゲート線 G L 2 a , G L 2 b と、隣り合うソース線 S L 2 a , S L 2 b とにより囲まれた領域（画素領域）に、4 個の画素 P IX 2 ( P IX 2 a , P IX 2 b , P IX 2 c , P IX 2 d ) がマトリクス状に並んで配置されている。ゲート線 G L 2 a と、該ゲート線 G L 2 a から離間して配置されたゲート線 G L 2 b との間には、画素領域が形成されて 4 個の画素 P IX 2 ( P IX 2 a , P IX 2 b , P IX 2 c , P IX 2 d ) が配置されている。一方、ゲート線 G L 2 a と、該ゲート線 G L 2 a に近接して配置されたゲート線 G L 2 b との間には、画素領域が形成されていない。また、ソース線 S L 2 a と、該ソース線 S L 2 a から離間して配置されたソース線 S L 2 b との間には、画素領域が形成されて 4 個の画素 P IX 2 ( P IX 2 a , P IX 2 b , P IX 2 c , P IX 2 d ) が配置されている。一方、ソース線 S L 2 a と、該ソース線 S L 2 a に近接して配置されたソース線 S L 2 b との間には、画素領域が形成されていない。

【 0 1 3 8 】

図 6 1 は、平面視で互いに重なり合う、表示パネル L C P 1 の画素グループ D O T 1 と、表示パネル L C P 2 の画素グループ D O T 2 との関係を示す平面図である。画素グループ D O T 1 は、表示パネル L C P 1 の 1 個の赤色画素 P IX R 、 1 個の緑色画素 P IX G 、 1 個の青色画素 P IX B 、及び 1 個の白色画素 P IX W から成り、画素グループ D O T 2 は、表示パネル L C P 2 の 1 個の画素 P IX 2 a 、 1 個の画素 P IX 2 b 、 1 個の画素 P IX 2 c 、及び 1 個の画素 P IX 2 d から成る。

【 0 1 3 9 】

平面視で、表示パネル L C P 2 の画素 P IX 2 a は、表示パネル L C P 1 の赤色画素 P IX R に重畠し、表示パネル L C P 2 の画素 P IX 2 b は、表示パネル L C P 1 の緑色画素 P IX G に重畠し、表示パネル L C P 2 の画素 P IX 2 c は、表示パネル L C P 1 の青色画素 P IX B に重畠し、表示パネル L C P 2 の画素 P IX 2 d は、表示パネル L C P 1 の白色画素 P IX W に重畠している。

【 0 1 4 0 】

図 6 1 ( b ) に示すように、画素 P IX 2 a では、ソース線 S L 2 a が薄膜トランジスタ T F T 2 a のソース電極に接続されており、ゲート線 G L 2 a が薄膜トランジスタ T F T 2 a のゲート電極に接続されており、画素電極 P X 2 a が薄膜トランジスタ T F T 2 a のドレイン電極に接続されている。画素 P IX 2 b では、ソース線 S L 2 b が薄膜トランジスタ T F T 2 b のソース電極に接続されており、ゲート線 G L 2 a が薄膜トランジスタ T F T 2 b のゲート電極に接続されており、画素電極 P X 2 b が薄膜トランジスタ T F T 2 b のドレイン電極に接続されている。画素 P IX 2 c では、ソース線 S L 2 a が薄膜ト

10

20

30

40

50

ランジスタ TFT 2 c のソース電極に接続されており、ゲート線 GL 2 b が薄膜トランジスタ TFT 2 c のゲート電極に接続されており、画素電極 PX 2 c が薄膜トランジスタ TFT 2 c のドレイン電極に接続されている。画素 PIX 2 d では、ソース線 SL 2 b が薄膜トランジスタ TFT 2 d のソース電極に接続されており、ゲート線 GL 2 b が薄膜トランジスタ TFT 2 d のゲート電極に接続されており、画素電極 PX 2 d が薄膜トランジスタ TFT 2 d のドレイン電極に接続されている。

【 0 1 4 1 】

表示パネル LCP 2 のブラックマトリクス BM 2 は、実施形態 8 の構成（図 50 参照）と同様に、ゲート線 GL 2 に重なるように行方向に延在しており、ストライプ状に形成されている。

10

【 0 1 4 2 】

実施形態 1 1 の構成によれば、実施形態 1 の構成と同様に、表示パネル LCP 1 の各画素 PIX 1 と表示パネル LCP 2 の各画素 PIX 2 とが 1 対 1 の関係で配置されているため、互いに重畳する各画素 PIX 1, PIX 2 のオン / オフを独立して制御することができる。このため、従来の構成と比較して、光漏れを低減することができるため、各色の単色画像の色再現性を向上させることができる。また、輝度ムラ及びモアレの発生、及び、画素の開口率の低下を抑えることもできる。

【 0 1 4 3 】

表示パネル LCP 1 及び表示パネル LCP 2 のドライバの構成は、図 1 1 に示す構成と同一である。

20

【 0 1 4 4 】

〔 実施形態 1 2 〕

実施形態 1 2 に係る表示パネル LCP 1 の構成は、実施形態 3 に係る表示パネル LCP 1 の構成（図 19 参照）と同一である。実施形態 1 2 に係る表示パネル LCP 2 の構成は、実施形態 3 に係る表示パネル LCP 2 の構成（図 20 参照）と比較すると、液晶 LCB の材料が異なっており、それ以外の構成は同一である。

【 0 1 4 5 】

図 6 2 は、実施形態 1 2 に係る液晶表示装置 LCD において、平面視で互いに重なり合う、表示パネル LCP 1 の画素グループ DOT 1 の画素 PIX 1 と、表示パネル LCP 2 の画素グループ DOT 2 の画素 PIX 2 との具体的な構成を示す平面図である。図 6 3 は、図 6 2 の 6 3 - 6 3 ' 切断線における断面図である。

30

【 0 1 4 6 】

実施形態 1 2 に係る表示パネル LCP 1 では、液晶 LCB が、誘電率異方性が正の液晶（ポジ型液晶）で構成されており、表示パネル LCP 2 では、液晶 LCB が、誘電率異方性が負の液晶（ネガ型液晶）で構成されている。また、図 6 2 及び図 6 3 に示すように、表示パネル LCP 1 の画素電極 PX 1 には、略列方向に延在するスリットが形成されており、表示パネル LCP 2 の画素電極 PX 2 (PX 2 a, PX 2 b) には、略行方向に延在するスリットが形成されている。すなわち、画素電極 PX 1 及び画素電極 PX 2 は、平面視で互いに略直交するように形成されている。

【 0 1 4 7 】

本発明の液晶表示装置 LCD は上記各実施形態の構成に限定されない。例えば、ストライプ状のブラックマトリクス BM は、平面視で薄膜トランジスタ TFT に重なる位置に島状パターンに形成されてもよい。また、白色画素 PIX W の代わりに、黄色画素が配置されていてもよい。

40

【 0 1 4 8 】

また、例えば実施形態 3 では、表示パネル LCP 2 において、平面視で、画素電極 PX 2 a (図 22 参照) に電気的に接続されたソース線 SL 2 a は、該画素電極 PX 2 a の左側に配置されており、画素電極 PX 2 b (図 22 参照) に電気的に接続されたソース線 SL 2 b は、該画素電極 PX 2 b の右側に配置されている。本発明の液晶表示装置 LCD は、上記構成に限定されず、例えば、画素電極 PX 2 a に電気的に接続されたソース線 SL

50

2 a が、平面視で該画素電極 P X 2 a に重なるように配置されてもよいし、画素電極 P X 2 b に電気的に接続されたソース線 S L 2 b が、平面視で該画素電極 P X 2 b に重なるように配置されてもよい。また、図 6 4 に示すように、画素電極 P X 2 a , P X 2 b の両方に電気的に接続されたソース線 S L 2 が、平面視で該画素電極 P X 2 a ( 又は、画素電極 P X 2 b ) に重なるように配置されてもよい。これらの構成を考慮すると、表示パネル L C P 2 は、画素電極 P X 2 a と画素電極 P X 2 b との間にソース線 S L 2 が配置されていない第 1 領域 P 1 ( 図 2 0 参照 ) を含んでいることが好ましい。また表示パネル L C P 2 は、画素電極 P X 2 a と画素電極 P X 2 b との間にソース線 S L 2 が配置された第 2 領域 P 2 ( 図 2 0 参照 ) を含んでもよい。さらに、図 2 0 に示すように、第 1 領域 P 1 及び第 2 領域 P 2 が、行方向に交互に繰り返し配置されてもよい。

10

#### 【 0 1 4 9 】

以上、本発明の実施形態について説明したが、本発明は上記各実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内で上記各実施形態から当業者が適宜変更した形態も本発明の技術的範囲に含まれることは言うまでもない。

#### 【 符号の説明 】

#### 【 0 1 5 0 】

L C D 液晶表示装置、L C P 1 表示パネル、S D 1 第 1 ソースドライバ、G D 1 第 1 ゲートドライバ、T C O N 1 第 1 タイミングコントローラ、L C P 2 表示パネル、S D 2 第 2 ソースドライバ、S I C ソースドライバ I C 、G I C ゲートドライバ I C 、G D 2 第 2 ゲートドライバ、T C O N 2 第 2 タイミングコントローラ、I P U 画像処理部、S L ソース線、G L 1 , G L 2 ゲート線、P O L 1 ~ P O L 4 偏光板、B M 1 , B M 2 ブラックマトリクス、B M 1 a ( ブラックマトリクス B M 1 の行方向に延在する ) 部分、B M 1 b ( ブラックマトリクス B M 1 の列方向に延在する ) 部分、B M 2 a ( ブラックマトリクス B M 2 の行方向に延在する ) 部分、B M 2 b ( ブラックマトリクス B M 2 の列方向に延在する ) 部分、F I L カラーフィルタ、P I X 1 , P I X 2 画素、P I X R 赤色画素、P I X G 緑色画素、P I X B 青色画素、P I X W 白色画素、D O T 1 , D O T 2 画素グループ、P X 1 , P X 2 画素電極、P 1 第 1 領域、P 2 第 2 領域。

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

(a)

(b)

【図11】

【図12】

【 図 1 3 】

〔 15 〕

### 【図14】

【 16 】

【図17】

【図18】

【図19】

【図20】

【 図 2 1 】

【 図 2 2 】

【 図 2 3 】

【 図 2 4 】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

観察者側

←→行方向

←→パックライト側

観察者側

←→行方向

←→パックライト側

【図33】

【図34】

【図35】

【図36】

【図37】

【 図 3 8 】

【図39】

【 図 4 0 】

【 図 4 1 】

【図42】

【 図 4 3 】

【 図 4 4 】

【図45】

【図46】

【図47】

【図48】

【図 49】

【図 50】

【図 51】

【図 52】

【図53】

【図54】

【図55】

【図56】

【図57】

【図58】

【図59】

【図60】

【 図 6 1 】

【図62】

【 図 6 3 】

【図64】

【図65】

|       | 構成例1 | 構成例2 | 構成例3 |

|-------|------|------|------|

| パネルA  |      |      |      |

| パネルB  |      |      |      |

| 位置ずれ無 |      |      |      |

| 位置ずれ有 |      |      |      |

【図66】

|       | 構成例4 | 構成例5 |

|-------|------|------|

| パネルA  |      |      |

| パネルB  |      |      |

| 位置ずれ無 |      |      |

| 位置ずれ有 |      |      |

---

フロントページの続き

F ターム(参考) 2H192 AA24 AA43 AA62 BB13 BB53 BC02 BC31 CB05 CC24 CC55

CC64 CC66 EA22 EA43 EA54 FB22 GD61 JA33

2H291 FA09Y FA14Y FA81Z FD07 FD22 FD26 GA04 GA10 GA17 GA19

HA15 LA03

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号     | <a href="#">JP2018087895A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2018-06-07 |

| 申请号         | JP2016230912                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2016-11-29 |

| 申请(专利权)人(译) | 松下液晶显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人      | 小野記久雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人         | 小野 記久雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号      | G02F1/1368 G02F1/1333 G02F1/1343 G02F1/1335                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| F1分类号       | G02F1/1368 G02F1/1333 G02F1/1343 G02F1/1335.505                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号   | 2H092/GA14 2H092/GA22 2H092/GA23 2H092/GA51 2H092/GA60 2H092/JA26 2H092/JA46 2H092/JB03 2H092/JB04 2H092/JB06 2H092/JB23 2H092/JB32 2H092/JB57 2H092/JB58 2H092/NA01 2H092/PA06 2H092/PA08 2H092/PA09 2H092/PA13 2H189/AA28 2H189/CA36 2H189/LA03 2H189/LA06 2H189/LA07 2H189/LA08 2H189/LA10 2H189/LA14 2H189/LA15 2H189/LA20 2H192/AA24 2H192/AA43 2H192/AA62 2H192/BB13 2H192/BB53 2H192/BC02 2H192/BC31 2H192/CB05 2H192/CC24 2H192/CC55 2H192/CC64 2H192/CC66 2H192/EA22 2H192/EA43 2H192/EA54 2H192/FB22 2H192/GD61 2H192/JA33 2H291/FA09Y 2H291/FA14Y 2H291/FA81Z 2H291/FD07 2H291/FD22 2H291/FD26 2H291/GA04 2H291/GA10 2H291/GA17 2H291/GA19 2H291/HA15 2H291/LA03 |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

## 摘要(译)

要解决的问题：改善通过叠加多个显示面板而构成的液晶显示装置中的单色图像的颜色再现性。第一显示面板包括沿第一方向延伸的多条第一源极线和沿第二方向延伸的多条第二源极线，沿两个方向延伸的多条第一栅极线，多个第一薄膜晶体管，多个第一像素电极以及多个第一像素。第二显示面板包括沿第一方向延伸的多条第二源极线，沿第二方向延伸的多条第二栅极线，多个第二薄膜晶体管，多个第三薄膜晶体管，多个第二像素电极，多个第三像素电极，多个第二像素和多个第三像素，并且第二显示面板并且还包括第一区域和第二区域，在所述第一区域中，所述第二源极线未被布置在所述第二像素电极和所述第三像素电极之间，所述第二像素电极和所述第三像素电极在平面图中在所述第二方向上彼此相邻布置。