(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-235413

(P2014-235413A)

(43) 公開日 平成26年12月15日(2014.12.15)

| (51) Int.Cl.               | F 1       | テーマコード (参考) |

|----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01) | GO9G 3/36 | 5C006       |

| <b>G09G 3/20</b> (2006.01) | GO9G 3/20 | 611C        |

|                            | GO9G 3/20 | 622C        |

|                            | GO9G 3/20 | 623C        |

|                            | GO9G 3/20 | 611A        |

審査請求 未請求 請求項の数 2 O L (全 10 頁) 最終頁に続く

|           |                              |          |                                                |

|-----------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号 | 特願2013-119059 (P2013-119059) | (71) 出願人 | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号 |

| (22) 出願日  | 平成25年6月5日 (2013.6.5)         | (74) 代理人 | 110001737<br>特許業務法人スズエ国際特許事務所                  |

|          |                        |

|----------|------------------------|

| (74) 代理人 | 100108855<br>弁理士 蔵田 昌俊 |

| (74) 代理人 | 100109830<br>弁理士 福原 淑弘 |

| (74) 代理人 | 100088683<br>弁理士 中村 誠  |

| (74) 代理人 | 100103034<br>弁理士 野河 信久 |

| (74) 代理人 | 100095441<br>弁理士 白根 俊郎 |

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】表示品位の良好な液晶表示装置を提供する。

【解決手段】マトリクス状に配列した画素電極 P E と、画素電極 P E が配列した行に沿って延びたゲート配線 G と、画素電極 P E が配列した列に沿って延びたソース配線 S と、ゲート配線 G とソース配線 S とが交差した位置近傍に配置されたスイッチング素子 S W と、ゲート配線 G を駆動するゲートドライバ G D と、ソース配線 S を駆動するソースドライバ S D と、ソース配線 S とソースドライバ S Dとの間に配置されソース配線 S とソースドライバ S D の出力端子との接続を切り替えるスイッチを含むスイッチ回路 A SW と、スイッチ回路 A SW の動作を制御する信号をスイッチ回路 A SW へ供給する配線に介在したトランスマッテラ T G と、を備えたアレイ基板 A R と、アレイ基板 A R と対向して配置された対向基板 C T と、アレイ基板 A R と対向基板 C Tとの間に保持された液晶層 L Q と、を備えた液晶表示装置。

【選択図】図 1

## 【特許請求の範囲】

## 【請求項 1】

マトリクス状に配列した画素電極と、前記画素電極が配列した行に沿って延びたゲート配線と、前記画素電極が配列した列に沿って延びたソース配線と、前記ゲート配線と前記ソース配線とが交差した位置近傍に配置されたスイッチング素子と、前記ゲート配線を駆動するゲートドライバと、前記ソース配線を駆動するソースドライバと、前記ソース配線と前記ソースドライバとの間に配置され前記ソース配線と前記ソースドライバの出力端子との接続を切り替えるスイッチを含むスイッチ回路と、前記スイッチ回路の動作を制御する信号を前記スイッチ回路へ供給する配線に介在したトランスマルチプレクタと、を備えたアレイ基板と、

10

前記アレイ基板と対向して配置された対向基板と、

前記アレイ基板と前記対向基板との間に保持された液晶層と、を備えた液晶表示装置。

## 【請求項 2】

マトリクス状に配列した画素電極と、前記画素電極が配列した行に沿って延びたゲート配線と、前記画素電極が配列した列に沿って延びたソース配線と、前記ゲート配線と前記ソース配線とが交差した位置近傍に配置されたスイッチング素子と、前記ゲート配線を駆動するゲートドライバと、前記ソース配線を駆動するソースドライバと、前記ソース配線と前記ソースドライバとの間に配置され前記ソース配線と前記ソースドライバの出力端子との接続を切り替えるスイッチを含むスイッチ回路と、前記スイッチ回路の動作を制御する信号を前記スイッチ回路へ供給する配線に介在した抵抗器と、を備えたアレイ基板と、

20

前記アレイ基板と対向して配置された対向基板と、

前記アレイ基板と前記対向基板との間に保持された液晶層と、を備えた液晶表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明の実施形態は、液晶表示装置に関する。

## 【背景技術】

## 【0002】

液晶表示装置は、軽量、薄型等の特徴により様々な電子機器に搭載されている。液晶表示装置には、例えば、アクティブマトリクス型の液晶表示パネルが用いられている。液晶表示パネルは、アレイ基板と、対向基板と、アレイ基板及び対向基板間に挟持された液晶層とを備えている。アレイ基板は、互いに交差するように配線された複数本のゲート配線と複数本のソース配線と、これらゲート配線及びソース配線により区画された各画素領域に形成されたスイッチング素子としての薄膜トランジスタ(Thin Film Transistor: TFT)と、を備えている。

30

## 【0003】

ソース配線はスイッチング素子を介してソースドライバと接続されている。スイッチング素子を切り替えることによりソースドライバから出力された映像信号は、選択的にソース配線へ出力される。

40

## 【先行技術文献】

## 【特許文献】

## 【0004】

## 【特許文献1】特開2006-267999号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

本発明の実施形態は、表示品位の良好な液晶表示装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0006】

実施形態によれば、マトリクス状に配列した画素電極と、前記画素電極が配列した行に

50

沿って延びたゲート配線と、前記画素電極が配列した列に沿って延びたソース配線と、前記ゲート配線と前記ソース配線とが交差した位置近傍に配置されたスイッチング素子と、前記ゲート配線を駆動するゲートドライバと、前記ソース配線を駆動するソースドライバと、前記ソース配線と前記ソースドライバとの間に配置され前記ソース配線と前記ソースドライバの出力端子との接続を切り替えるスイッチを含むスイッチ回路と、前記スイッチ回路の動作を制御する信号を前記スイッチ回路へ供給する配線に介在したトランスマルチплексором и, включенным в цепь управления переключателем, и в цепь управления транзистором, включенным в цепь истока.

#### 【図面の簡単な説明】

10

#### 【0007】

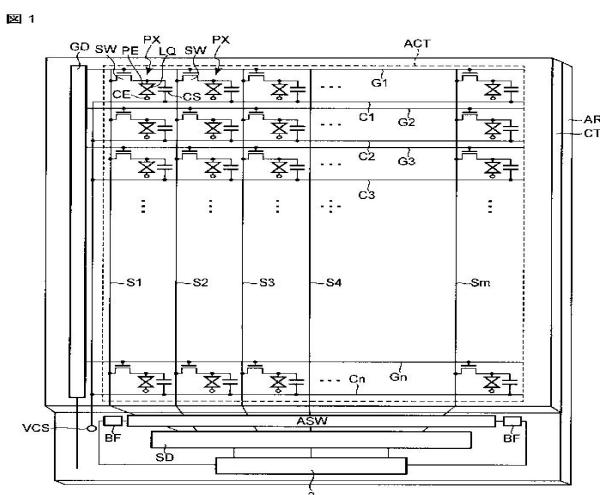

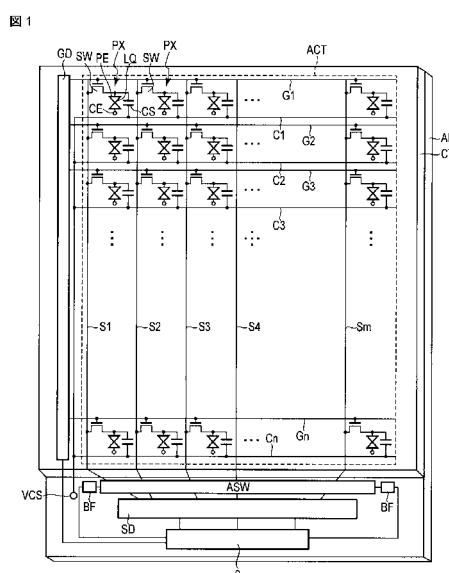

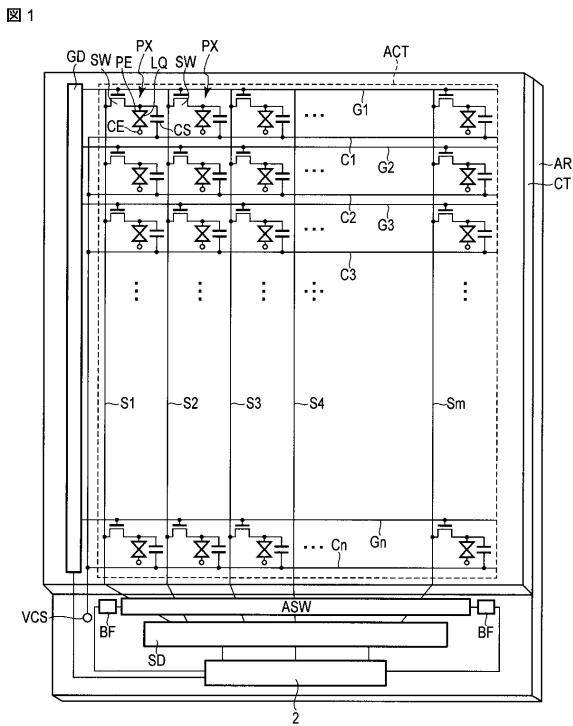

【図1】図1は、一実施形態の液晶表示装置の構成を概略的に示す図である。

【図2】図2は、図1に示す液晶表示装置のバッファの一例を示す回路図である。

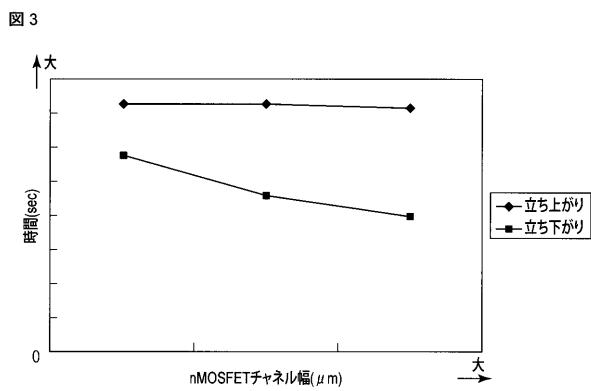

【図3】図3は、nMOSFETのチャネル幅を調整したときの出力信号波形の立ち上がり時間と立下り時間との一例を示す図である。

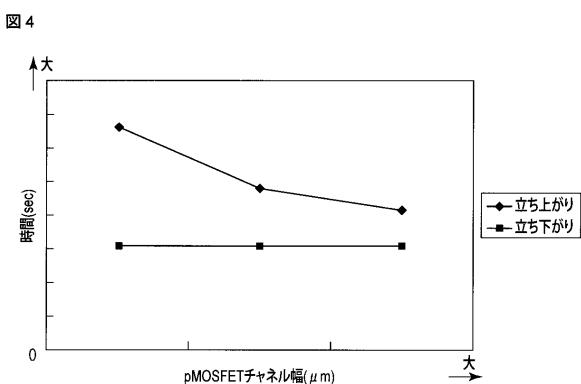

【図4】図4は、pMOSFETのチャネル幅を調整したときの出力信号の立ち上がり時間と立下り時間との一例を示す図である。

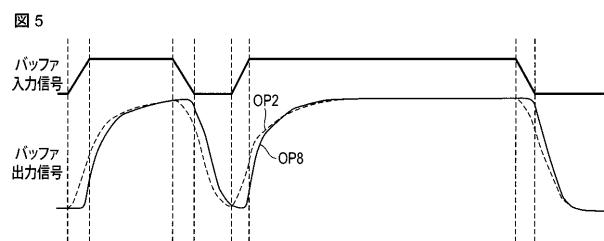

【図5】図5は、バッファの入力信号波形と図2に示すバッファの出力信号波形と図8に示すバッファの出力信号波形との一例を示す図である。

20

【図6】図6は、図1に示す液晶表示装置のバッファの他の例を示す回路図である。

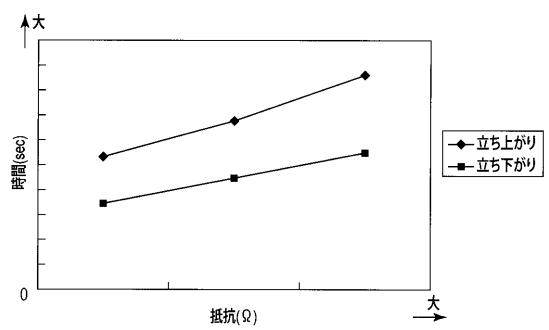

【図7】図7は、抵抗器の大きさを調整したときの出力信号波形の立ち上がり時間と立下り時間との一例を示す図である。

【図8】図8は、比較例の液晶表示装置のバッファの一例を示す回路図である。

#### 【発明を実施するための形態】

#### 【0008】

以下、実施形態の液晶表示装置について、図面を参照して説明する。

図1は、一実施形態の液晶表示装置の構成を概略的に示す図である。

#### 【0009】

本実施形態の液晶表示装置は、アクティブマトリクスタイプの液晶表示パネルLPNを備えている。液晶表示パネルLPNは、第1基板であるアレイ基板ARと、アレイ基板ARに対向して配置された第2基板である対向基板CTと、これらのアレイ基板ARと対向基板CTとの間に保持された液晶層LQと、を備えている。このような液晶表示パネルLPNは、画像を表示するアクティブエリアACTを備えている。このアクティブエリアACTは、m×n個のマトリクス状に配置された複数の画素PXによって構成されている（但し、m及びnは正の整数である）。

30

#### 【0010】

液晶表示パネルLPNは、アクティブエリアACTにおいて、n本のゲート配線G（G<sub>1</sub>～G<sub>n</sub>）、m本のソース配線S（S<sub>1</sub>～S<sub>m</sub>）などを備えている。ゲート配線G及び補助容量線Cは、例えば、第1方向Xに沿って略直線的に延出している。これらのゲート配線G及び補助容量線Cは、第1方向Xに交差する第2方向Yに沿って交互に並列配置されている。ここでは、第1方向Xと第2方向Yとは互いに略直交している。ソース配線Sは、ゲート配線G及び補助容量線Cと交差している。ソース配線Sは、第2方向Yに沿って略直線的に延出している。なお、ゲート配線G、補助容量線C、及び、ソース配線Sは、必ずしも直線的に延出していなくても良く、それらの一部が屈曲していてもよい。

40

#### 【0011】

各ゲート配線Gは、アクティブエリアACTの外側に引き出され、ゲートドライバGDに接続されている。各ソース配線Sは、アクティブエリアACTの外側に引き出され、スイッチ回路ASWを介してソースドライバSDに接続されている。これらのゲートドライバGD及びソースドライバSDの少なくとも一部は、例えば、アレイ基板ARに形成され、コントローラを内蔵した駆動ICチップ2と接続されている。

50

## 【0012】

各画素 P X は、スイッチング素子 S W、画素電極 P E、共通電極 C Eなどを備えている。保持容量 C s は、例えば補助容量線 C と画素電極 P Eとの間に形成される。補助容量線 C は、補助容量電圧が印加される電圧印加部 V C S と電気的に接続されている。

## 【0013】

画素電極 P E は、各画素 P X に配置され、スイッチング素子 S W に電気的に接続されている。共通電極 C E は、液晶層 L Q を介して複数の画素 P X の画素電極 P E に対して共通に配置されている。このような画素電極 P E 及び共通電極 C E は、例えば、インジウム・ティン・オキサイド (ITO) やインジウム・ジンク・オキサイド (IZO) などの光透過性を有する導電材料によって形成されている。10

## 【0014】

スイッチング素子 S W は、例えば、n チャネル薄膜トランジスタ (TFT) によって構成されている。スイッチング素子 S W は、ゲート配線 G 及びソース配線 S と電気的に接続されている。このようなスイッチング素子 S W は、トップゲート型あるいはボトムゲート型のいずれであっても良い。また、スイッチング素子 S W の半導体層は、例えば、ポリシリコンによって形成されているが、アモルファスシリコンによって形成されていても良い。10

## 【0015】

スイッチング素子 S W のゲート電極は、対応するゲート配線 G と電気的に接続している（あるいは一体に形成されている）。スイッチング素子 S W のソース電極は、対応するソース配線 S と電気的に接続している（あるいは一体に形成されている）。スイッチング素子 S W のドレイン電極は、対応する画素電極 P E と電気的に接続している（あるいは一体に形成されている）20。

## 【0016】

アレイ基板 A R は、共通電極 C E に電圧を印加するための給電部（図示せず）を備えている。この給電部は、例えば、アクティブエリア A C T の外側に形成されている。共通電極 C E は、アクティブエリア A C T の外側に引き出され、図示しない導電部材を介して、給電部と電気的に接続されている。

## 【0017】

スイッチ回路 A S W は、アクティブエリア A C T とソースドライバ S Dとの間に配置されている。スイッチ回路 A S W はソースドライバ S D の出力ラインとソース配線 Sとの接続を切り替えるアナログスイッチを複数備えている。アナログスイッチを切り替える制御信号は、駆動 I C チップ 2 からバッファ B F を介してスイッチ回路 A S W へ入力される。30

## 【0018】

バッファ B F は、スイッチ回路 A S W の動作を制御する信号をスイッチ回路 A S W へ供給する駆動 I C チップ 2 とスイッチ回路 A S Wとの間に延びた配線に介在している。バッファ B F は、スイッチ回路 A S W に入力される制御信号を鈍らせるために設けられている。アナログスイッチを切り替える制御信号の波形の立ち上がりおよび立下りが急であると、アナログスイッチが切り替わるタイミングでノイズ (EMI : electromagnetic interference) が発生して、映像信号にノイズが重畠してしまうことがあり、このノイズの発生を改善するためにバッファ B F を設けている。40

## 【0019】

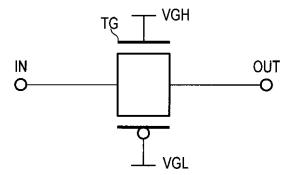

図 2 は、図 1 に示す液晶表示装置のバッファ B F の一例を示す回路図である。

この例では、バッファ B F は、トランスマニアゲート T G を備えている。トランスマニアゲート T G は、切替信号 V G H、V G L によりその動作を制御される。トランスマニアゲート T G は、例えば n MOSFET と p MOSFET とを組み合わせて構成された CMOS トランスマニアゲート T G である。トランスマニアゲート T G は、例えば、切替信号 V G H がハイ (H) レベルであって切替信号 V G L がロー (L) レベルであるときに入力端子 (IN) と出力端子 (OUT) とが導通し、切替信号 V G H がロー レベルであって切替信号 V G L がハイ レベルであるときに入力端子 (IN) と出力端子 (OUT) とが絶縁する。切替

信号 VGH、VGL は、例えば駆動 IC2 から供給される。トランスマルチゲート TG の入力端子 (IN) には駆動 IC チップ 2 からスイッチ回路 ASW の制御信号が入力される。

#### 【0020】

トランスマルチゲート TG は、nMOSFET のチャネル幅と pMOSFET のチャネル幅とを調整することにより、出力信号波形の形状を制御することが可能である。

#### 【0021】

図 3 は、nMOSFET のチャネル幅を調整したときの出力信号波形の立ち上がり時間と立下り時間との一例を示す図である。

図示した例では、nMOSFET のチャネル幅を大きくするとトランスマルチゲート TG の出力信号波形の立下り時間が小さくなり、nMOSFET のチャネル幅を小さくするとトランスマルチゲート TG の出力信号波形の立下り時間が大きくなる傾向が得られた。また、トランスマルチゲート TG の出力信号波形の立ち上がり時間は nMOSFET のチャネル幅を調整しても略一定であった。

#### 【0022】

なお、出力信号波形の立ち上がり時間は、例えば、出力信号波形がハイレベルのときを 100% としローレベルのときを 0% とし、出力信号波形が 10% に到達した時点から 90% に到達した時点までの時間である。出力信号波形の立下り時間は、例えば、出力信号波形が 90% に到達した時点から 10% に到達した時点までの時間である。

#### 【0023】

図 4 は、pMOSFET のチャネル幅を調整したときの出力信号の立ち上がり時間と立下り時間との一例を示す図である。

#### 【0024】

図示した例では、pMOSFET のチャネル幅を大きくするとトランスマルチゲート TG の出力信号波形の立ち上がり時間が小さくなり、pMOSFET のチャネル幅を小さくするとトランスマルチゲート TG の出力信号波形の立ち上がり時間が大きくなる傾向が得られた。また、トランスマルチゲート TG の出力信号波形の立下り時間は pMOSFET のチャネル幅を調整しても略一定であった。

#### 【0025】

上記のように nMOSFET のチャネル幅と pMOSFET のチャネル幅とを調整することにより、出力信号波形の立ち上がり形状と立下り形状とを独立に制御することが可能である。

#### 【0026】

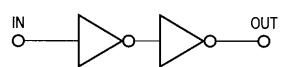

図 8 は、比較例の液晶表示装置のバッファ BF の一例を示す回路図である。

図示した比較例では、バッファ BF が例えれば直列に接続した 2 つの否定 (NOT) 回路で構成されている。NOT 回路は入力信号がハイレベルであればローレベルの信号を出力し、入力信号がローレベルであればハイレベルの信号を出力する。NOT 回路は、例えは、ハイレベルの電流源 (VGH) とローレベルの電流源 (VGL) とに接続され、入力信号に応じてこれらの電流源 (VGH, VGL) と出力端子との接続を切り替えるように構成される。

#### 【0027】

図 5 は、バッファ BF の入力信号波形と図 2 に示すバッファ BF の出力信号波形 OP2 と図 8 に示すバッファ BF の出力信号波形 OP8 との一例を示す図である。

#### 【0028】

図 5 を参照すると、2 つの NOT 回路で構成されたバッファ BF の出力信号の立ち上がり開始タイミングおよび立下り開始タイミングは入力信号よりも遅延する。これに対し、トランスマルチゲート TG で構成されたバッファ BF の出力信号は、その立ち上がり開始タイミングと立下り開始タイミングとは入力信号と略同時である。

#### 【0029】

したがって、トランスマルチゲート TG の nMOSFET のチャネル幅と pMOSFET のチャネル幅とを調整することにより、容易にバッファ BF の出力信号波形の立ち上がり

10

20

30

40

50

の傾きと立下りの傾きとのそれぞれを調整することが可能である。

【0030】

すなわち、本実施形態では、スイッチ回路A S Wのアナログスイッチを切り替える際に、ノイズが発生することを抑制することができ、表示品位の良好な液晶表示装置を提供することができる。

【0031】

また、バッファB FをトランスファゲートT Gで構成すると、N O T回路で構成する場合よりも液晶表示パネルL P Nの消費電力を低く抑えることが可能である。すなわち、N O T回路は、入力端子(I N)に供給される信号に応じて制御信号V G H、V G Lを出力する。したがって、N O T回路に入力される制御信号V G H、V G Lは、トランスファゲートT Gに入力する制御信号V G H、V G Lよりも大きくなる。10

【0032】

また、バッファB FをトランスファゲートT Gで構成すると、バッファB Fによる電流消費が略ゼロになり、トランスファゲートT Gで構成したバッファB Fの消費電流はバッファB FをN O T回路で構成するときの約1/5となる。

【0033】

さらに、バッファB FをトランスファゲートT Gで構成すると、バッファB Fにおける貫通電流が略なくなるため、液晶表示パネルL P Nとしての消費電流も低く抑えることができる。

【0034】

また、バッファB FをトランスファゲートT Gで構成すると、N O T回路で構成した場合よりも静電気に対する耐性が増し、製造歩留りを向上することが可能である。20

【0035】

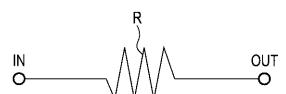

図6は、図1に示す液晶表示装置のバッファB Fの他の例を示す回路図である。

この例では、バッファB Fは、抵抗器Rを備えている。抵抗器Rは、入力端子(I N)と出力端子(O U T)とに直列に接続している。

【0036】

抵抗器Rは、その大きさを調整することによりバッファB Fの出力信号波形を制御することができる。

【0037】

図7は、抵抗器Rの大きさを調整したときの出力信号波形の立ち上がり時間と立下り時間との一例を示す図である。

図示した例では、抵抗器Rの抵抗値を大きくするとバッファB Fの出力信号波形の立ち上がり時間および立下り時間が大きくなり、抵抗器Rの抵抗値を小さくするとバッファB Fの出力信号波形の立ち上がり時間および立下り時間が小さくなる傾向が得られた。30

【0038】

抵抗器Rで構成されたバッファB Fの出力信号は、その立ち上がり開始タイミングと立下り開始タイミングとは入力信号と略同時である。したがって、抵抗器Rの抵抗値を調整することにより、容易にバッファB Fの出力信号波形の立ち上がりおよび立下りの傾きを小さくすることが可能である。40

【0039】

したがって、図6に示すように抵抗器RでバッファB Fを構成したときにも、スイッチ回路A S Wのアナログスイッチを切り替える際に、ノイズが発生することを抑制することができ、表示品位の良好な液晶表示装置を提供することができる。

【0040】

また、バッファB Fを抵抗器Rで構成すると、トランスファゲートT Gで構成した場合と同様に、N O T回路で構成する場合よりも液晶表示パネルL P Nの消費電力を低く抑えることが可能である。また、バッファB Fを抵抗器Rで構成すると、バッファB Fによる電流消費が略ゼロとなり、抵抗器Rで構成したバッファB Fの消費電流はバッファB FをN O T回路で構成するときの約1/5となる。50

**【 0 0 4 1 】**

さらに、バッファBFを抵抗器Rで構成すると、バッファBFにおける貫通電流が略なくなるため、液晶表示パネルLPNとしての消費電流も低く抑えることができる。

**【 0 0 4 2 】**

さらに、バッファBFを抵抗器Rで構成すると、NOT回路で構成した場合よりもバッファBFのレイアウトに必要な領域が大きくならず、レイアウトの設計が容易であるとともに、液晶表示パネルLPNの小型化の実現が容易となる。

**【 0 0 4 3 】**

また、バッファBFを抵抗器Rで構成すると、NOT回路で構成した場合よりも静電気に対する耐性が増し、製造歩留りを向上することが可能である。

10

**【 0 0 4 4 】**

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

**【 0 0 4 5 】**

なお、上記の説明では、表示パネルとして液晶表示パネルを備えた構成について説明したが、有機エレクトロルミネッセンス表示パネルなど他の表示パネルを備えた構成であっても良い。

20

**【 0 0 4 6 】**

また、液晶表示パネルは、画素電極PE及び共通電極CEの双方がアレイ基板ARに備えられた構成、すなわち、IPS(In-Plane Switching)モードやFFS(Fringe Field Switching)モードなどの主として横電界(フリンジ電界も含む)を利用する構成であってもよい。少なくとも画素電極PEはアレイ基板ARに備えられ、共通電極CEはアレイ基板AR及び対向基板CTのいずれに備えられていても良い。TN(Twisted Nematic)モード、OCB(Optically Compensated Bend)モード、VA(Vertical Aligned)モードなどの主として縦電界を利用する構成の場合、共通電極CEは対向基板CTに備えられる。つまり、共通電極CEが配置される位置は、アレイ基板ARを構成する絶縁基板と対向基板CTを構成する絶縁基板との間であれば良い。

30

**【 符号の説明 】****【 0 0 4 7 】**

LPN...液晶表示パネル、AR...アレイ基板、CT...対向基板、LQ...液晶層、ACT...アクティブエリア、PX...画素、G...ゲート配線、S...ソース配線、C...補助容量線、X...第1方向、Y...第2方向、GD...ゲートドライバ、SD...ソースドライバ、ASW...スイッチ回路、SW...スイッチング素子、PE...画素電極、CE...共通電極、Cs...保持容量、VCS...電圧印加部、BF...バッファ、TG...トランスマジックゲート、R...抵抗器、2...駆動ICチップ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

図7

【図8】

図8

## フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

G 0 9 G 3/20 6 2 1 J

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100172580

弁理士 赤穂 隆雄

(74)代理人 100179062

弁理士 井上 正

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72)発明者 宮永 直季

東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

F ターム(参考) 5C006 AC11 AC24 BB16 BF27 BF32 BF34 FA32 FA47 FA51

5C080 AA10 BB05 DD12 DD26 DD27 FF11 JJ02 JJ03 JJ05

|                |                                                                                                                                                                                                       |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2014235413A</a>                                                                                                                                                                         | 公开(公告)日 | 2014-12-15 |

| 申请号            | JP2013119059                                                                                                                                                                                          | 申请日     | 2013-06-05 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                             |         |            |

| [标]发明人         | 宫永直季                                                                                                                                                                                                  |         |            |

| 发明人            | 宫永 直季                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/36 G09G3/20                                                                                                                                                                                     |         |            |

| FI分类号          | G09G3/36 G09G3/20.611.C G09G3/20.622.C G09G3/20.623.C G09G3/20.611.A G09G3/20.621.J                                                                                                                   |         |            |

| F-TERM分类号      | 5C006/AC11 5C006/AC24 5C006/BB16 5C006/BF27 5C006/BF32 5C006/BF34 5C006/FA32 5C006/FA47 5C006/FA51 5C080/AA10 5C080/BB05 5C080/DD12 5C080/DD26 5C080/DD27 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ05 |         |            |

| 代理人(译)         | 中村诚<br>河野直树<br>井上 正<br>冈田隆                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                             |         |            |

### 摘要(译)

解决的问题：提供一种具有良好的显示质量的液晶显示装置。以矩阵形式布置的像素电极PE，沿着布置有像素电极PE的行延伸的栅极布线G，沿着布置有像素电极PE的列延伸的源极布线S和栅极布线。布置在G和源极布线S相交的位置附近的开关元件SW，驱动栅极布线G的栅极驱动器GD，驱动源极布线S的源极驱动器SD，源极布线S和源极驱动器SD，在源极布线S和源极驱动器SD的输出端子之间，该源极驱动器SD设置在包括开关的开关电路ASW和插入在该布线中的传输门之间，用于向开关电路ASW提供用于控制开关电路ASW的操作的信号 液晶，包括：具有TG的阵列基板AR，与该阵列基板AR相对配置的对置基板CT，以及保持在该阵列基板AR与对置基板CT之间的液晶层LQ。显示装置。

[选型图]图1