(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-66029

(P2016-66029A)

(43) 公開日 平成28年4月28日(2016.4.28)

| (51) Int.Cl.               | F 1       | テーマコード (参考) |

|----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01) | G09G 3/36 | 5C006       |

| <b>G09G 3/20</b> (2006.01) | G09G 3/20 | 624B        |

|                            | G09G 3/20 | 624D        |

|                            | G09G 3/20 | 622C        |

|                            | G09G 3/20 | 623C        |

審査請求 未請求 請求項の数 12 O L (全 21 頁) 最終頁に続く

|           |                              |          |                                                |

|-----------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号 | 特願2014-196075 (P2014-196075) | (71) 出願人 | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号 |

| (22) 出願日  | 平成26年9月26日 (2014. 9. 26)     | (74) 代理人 | 110001737<br>特許業務法人スズエ国際特許事務所                  |

|           |                              | (74) 代理人 | 100091351<br>弁理士 河野 哲                          |

|           |                              | (74) 代理人 | 100084618<br>弁理士 村松 貞男                         |

|           |                              | (74) 代理人 | 100087653<br>弁理士 鈴江 正二                         |

|           |                              | (72) 発明者 | 中村 阜<br>東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内        |

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその駆動方法

## (57) 【要約】

【課題】低消費電力化を図ることのできる液晶表示装置及び液晶表示装置の駆動方法を提供する。又は、表示品位に優れた液晶表示装置及び液晶表示装置の駆動方法を提供する。

【解決手段】液晶表示装置の駆動部は、第1画素電極と第1対向電極との間に第1電位差を、第2画素電極と第2対向電極との間に第2電位差を、それぞれ与え保持する際、まず、書き込み期間に、第1対向電極に第1対向電圧  $V_{comH}$  を与え、第2対向電極に第2対向電圧  $V_{comL}$  を与え、制御信号 SG の電圧値を第1電圧値  $V_1$  に設定する。特定書き込み期間に、制御信号 SG の電圧値を第2電圧値  $V_2$  に一時的に設定し、第1画像信号  $V_{sig1L}$  を第1信号線に与え、第2画像信号  $V_{sig2H}$  を第2信号線に与える。保持期間に、第1対向電極に第1対向電圧  $V_{comH}$  を与えた状態に維持し、第2対向電極に第2対向電圧  $V_{comL}$  を与えた状態に維持し、制御信号 SG の電圧値を第3電圧値  $V_3$  に設定する。

【選択図】図 7

## 【特許請求の範囲】

## 【請求項 1】

走査線と、第1信号線と、前記走査線及び第1信号線に電気的に接続されたnチャネル型の第1薄膜トランジスタと、前記第1薄膜トランジスタに電気的に接続された第1画素電極と、前記第1薄膜トランジスタ及び第1画素電極とともに第1画素を形成する第1対向電極と、第2信号線と、前記走査線及び第2信号線に電気的に接続されたnチャネル型の第2薄膜トランジスタと、前記第2薄膜トランジスタに電気的に接続された第2画素電極と、前記第2薄膜トランジスタ及び第2画素電極とともに、前記第1画素に隣合う第2画素を形成する第2対向電極と、前記走査線、第1信号線、第2信号線、第1対向電極及び第2対向電極に電気的に接続された駆動部と、を備え、

前記駆動部は、前記第1画素電極と前記第1対向電極との間に第1電位差を、前記第2画素電極と前記第2対向電極との間に第2電位差を、それぞれ与え保持する際、

書込み期間に、前記第1対向電極に第1対向電圧を与える、前記第2対向電極に前記第1対向電圧よりロウレベルの第2対向電圧を与える、前記走査線に与える制御信号の電圧値を前記第2対向電圧よりロウレベルの第1電圧値に設定する書込みであって、前記第1対向電圧と前記第1電圧値との差は前記第1対向電圧と前記第2対向電圧との差の2倍以上である、前記書込みと、

前記書込み期間のうちの第1画像信号及び第2画像信号の特定書込み期間に、前記走査線に与える前記制御信号の電圧値を前記第1薄膜トランジスタの閾値電圧及び前記第2薄膜トランジスタの閾値電圧と同一レベル又はそれよりハイレベルの第2電圧値に一時的に設定し、前記第1画像信号を前記第1信号線に与え前記第1画素電極に書き込み、前記第2画像信号を前記第2信号線に与え前記第2画素電極に書き込み、前記第1電位差及び第2電位差を生じさせる、前記第1画像信号及び第2画像信号の特定書込みと、

前記書込み期間に続き、前記書込み期間より長い保持期間に、前記第1対向電極に前記第1対向電圧を与えた状態に維持し、前記第2対向電極に前記第2対向電圧を与えた状態に維持し、前記走査線に与える前記制御信号の電圧値を前記第2対向電圧よりロウレベルであり前記第1電圧値よりハイレベルである第3電圧値に設定し、前記第1電位差及び第2電位差を保持する、保持と、

を行うように構成されている液晶表示装置。

## 【請求項 2】

走査線と、第1信号線と、前記走査線及び第1信号線に電気的に接続されたpチャネル型の第1薄膜トランジスタと、前記第1薄膜トランジスタに電気的に接続された第1画素電極と、前記第1薄膜トランジスタ及び第1画素電極とともに第1画素を形成する第1対向電極と、第2信号線と、前記走査線及び第2信号線に電気的に接続されたpチャネル型の第2薄膜トランジスタと、前記第2薄膜トランジスタに電気的に接続された第2画素電極と、前記第2薄膜トランジスタ及び第2画素電極とともに、前記第1画素に隣合う第2画素を形成する第2対向電極と、前記走査線、第1信号線、第2信号線、第1対向電極及び第2対向電極に電気的に接続された駆動部と、を備え、

前記駆動部は、前記第1画素電極と前記第1対向電極との間に第1電位差を、前記第2画素電極と前記第2対向電極との間に第2電位差を、それぞれ与え保持する際、

書込み期間に、前記第1対向電極に第1対向電圧を与える、前記第2対向電極に前記第1対向電圧よりハイレベルの第2対向電圧を与える、前記走査線に与える制御信号の電圧値を前記第2対向電圧よりハイレベルの第1電圧値に設定する書込みであって、前記第1対向電圧と前記第1電圧値との差は前記第1対向電圧と前記第2対向電圧との差の2倍以上である、前記書込みと、

前記書込み期間のうちの第1画像信号及び第2画像信号の特定書込み期間に、前記走査線に与える前記制御信号の電圧値を前記第1薄膜トランジスタの閾値電圧及び前記第2薄膜トランジスタの閾値電圧と同一レベル又はそれよりロウレベルの第2電圧値に一時的に設定し、前記第1画像信号を前記第1信号線に与え前記第1画素電極に書き込み、前記第2画像信号を前記第2信号線に与え前記第2画素電極に書き込み、前記第1電位差及び第2電

位差を生じさせる、前記第1画像信号及び第2画像信号の特定書き込みと、

前記書き込み期間に続き、前記書き込み期間より長い保持期間に、前記第1対向電極に前記第1対向電圧を与えた状態に維持し、前記第2対向電極に前記第2対向電圧を与えた状態に維持し、前記走査線に与える前記制御信号の電圧値を前記第2対向電圧よりハイレベルであり前記第1電圧値よりロウレベルである第3電圧値に設定し、前記第1電位差及び第2電位差を保持する、保持と、

を行うように構成されている液晶表示装置。

【請求項3】

前記駆動部は、前記保持期間に、前記第1対向電圧と前記第2対向電圧との中間の電圧レベルの調整信号を前記第1信号線及び第2信号線にそれぞれ与えるように構成されている請求項1又は2に記載の液晶表示装置。 10

【請求項4】

前記駆動部は、

前記保持期間に続く他の書き込み期間に、前記第1対向電極に前記第2対向電圧を与え、前記前記第2対向電極に前記第1対向電圧を与え、前記走査線に与える前記制御信号の電圧値を前記第1電圧値に設定する他の書き込みと、

前記他の書き込み期間のうちの前記第1画像信号及び第2画像信号の他の特定書き込み期間に、前記走査線に与える前記制御信号の電圧値を前記第2電圧値に一時的に設定し、前記第1画像信号を前記第1信号線に与え前記第1画素電極に書き込み、前記第2画像信号を前記第2信号線に与え前記第2画素電極に書き込み、前記第1電位差及び第2電位差を生じさせる、前記第1画像信号及び第2画像信号の他の特定書き込みと、 20

前記他の書き込み期間に続き、前記他の書き込み期間より長い他の保持期間に、前記第1対向電極に前記第2対向電圧を与えた状態に維持し、前記第2対向電極に前記第1対向電圧を与えた状態に維持し、前記走査線に与える前記制御信号の電圧値を前記第3電圧値に設定し、前記第1電位差及び第2電位差を保持する、他の保持と、

をさらにを行うように構成されている請求項1又は2に記載の液晶表示装置。

【請求項5】

前記駆動部は、前記他の保持期間に、前記第1対向電圧と前記第2対向電圧との中間の電圧レベルの調整信号を前記第1信号線及び第2信号線にそれぞれ与えるように構成されている請求項4に記載の液晶表示装置。 30

【請求項6】

前記駆動部は、前記特定書き込みを含む前記書き込みと、前記保持と、前記他の特定書き込みを含む前記他の書き込みと、前記他の保持と、を繰り返し、前記第1電位差及び第2電位差を保持するように構成されている請求項4に記載の液晶表示装置。

【請求項7】

前記駆動部は、前記第1画素電極に前記第1画像信号を60Hzのフレームレートで書き込み、前記第2画素電極に前記第2画像信号を60Hzのフレームレートで書込むように構成され、

前記書き込み期間は1フレーム期間であり、

前記保持期間は、59フレーム期間である請求項1又は2に記載の液晶表示装置。 40

【請求項8】

前記第1画素電極に電気的に接続され前記第1画素を形成する第1補助容量素子と、

前記第2画素電極に電気的に接続され前記第2画素を形成する第2補助容量素子と、

をさらに備えている請求項1乃至7の何れか1項に記載の液晶表示装置。

【請求項9】

前記第1画素及び第2画素は、それぞれ光反射型の画素である請求項1乃至8の何れか1項に記載の液晶表示装置。

【請求項10】

前記第1画素電極及び第2画素電極は、それぞれ光反射型の電極である請求項9に記載の液晶表示装置。 50

**【請求項 1 1】**

ツイステッドネマティック方式を採用している請求項 1 乃至 10 の何れか 1 項に記載の液晶表示装置。

**【請求項 1 2】**

走査線と、第 1 信号線と、前記走査線及び第 1 信号線に電気的に接続された  $n$  チャネル型の第 1 薄膜トランジスタと、前記第 1 薄膜トランジスタに電気的に接続された第 1 画素電極と、前記第 1 薄膜トランジスタ及び第 1 画素電極とともに第 1 画素を形成する第 1 対向電極と、第 2 信号線と、前記走査線及び第 2 信号線に電気的に接続された  $n$  チャネル型の第 2 薄膜トランジスタと、前記第 2 薄膜トランジスタに電気的に接続された第 2 画素電極と、前記第 2 薄膜トランジスタ及び第 2 画素電極とともに、前記第 1 画素に隣合う第 2 画素を形成する第 2 対向電極と、を備えた液晶表示装置の駆動方法において、

前記第 1 画素電極と前記第 1 対向電極との間に第 1 電位差を、前記第 2 画素電極と前記第 2 対向電極との間に第 2 電位差を、それぞれ与え保持する際、

書き込み期間に、前記第 1 対向電極に第 1 対向電圧を与え、前記第 2 対向電極に前記第 1 対向電圧よりロウレベルの第 2 対向電圧を与え、前記走査線に与える制御信号の電圧値を前記第 2 対向電圧よりロウレベルの第 1 電圧値に設定し、

前記書き込み期間のうちの第 1 画像信号及び第 2 画像信号の特定書き込み期間に、前記走査線に与える前記制御信号の電圧値を前記第 1 薄膜トランジスタの閾値電圧及び前記第 2 薄膜トランジスタの閾値電圧と同一レベル又はそれよりハイレベルの第 2 電圧値に一時的に設定し、前記第 1 画像信号を前記第 1 信号線に与え前記第 1 画素電極に書き込み、前記第 2 画像信号を前記第 2 信号線に与え前記第 2 画素電極に書き込み、前記第 1 電位差及び第 2 電位差を生じさせ、

前記書き込み期間に続き、前記書き込み期間より長い保持期間に、前記第 1 対向電極に前記第 1 対向電圧を与えた状態に維持し、前記第 2 対向電極に前記第 2 対向電圧を与えた状態に維持し、前記走査線に与える前記制御信号の電圧値を前記第 2 対向電圧よりロウレベルであり前記第 1 電圧値よりハイレベルである第 3 電圧値に設定し、前記第 1 電位差及び第 2 電位差を保持し、

前記第 1 対向電圧と前記第 1 電圧値との差は前記第 1 対向電圧と前記第 2 対向電圧との差の 2 倍以上である、

液晶表示装置の駆動方法。

10

20

30

40

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明の実施形態は、液晶表示装置及び液晶表示装置の駆動方法に関する。

**【背景技術】****【0 0 0 2】**

一般に、液晶表示装置は、アレイ基板と、対向基板と、これら両基板間に挟持された液晶層と、アレイ基板及び対向基板のいずれか一方に形成されたカラーフィルタと、を有している。アレイ基板及び対向基板間の隙間は、スペーサにより一定に保持されている。液晶表示装置の表示方式としては、T N (Twisted Nematic) 方式等の各種の方式が用いられている。各画素は、薄膜トランジスタ (thin film transistor : TFT) を有している。

**【0 0 0 3】**

液晶表示装置は、60 Hz のフレームレートで駆動されることが多いが、フレームレートを低減することにより、低消費電力化を図ることができる。しかしながら、薄膜トランジスタのリーク電流のために、画素電極の電圧が変化してしまい、画像表示の際にフリッカが生じる問題がある。

**【先行技術文献】****【特許文献】****【0 0 0 4】**

50

【特許文献 1】国際公開第 2013 / 035594 号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の実施形態は、低消費電力化を図ることのできる液晶表示装置及び液晶表示装置の駆動方法を提供する。又は、本発明の実施形態は、表示品位に優れた液晶表示装置及び液晶表示装置の駆動方法を提供する。

【課題を解決するための手段】

【0006】

一実施形態に係る液晶表示装置は、

走査線と、第 1 信号線と、前記走査線及び第 1 信号線に電気的に接続された n チャネル型の第 1 薄膜トランジスタと、前記第 1 薄膜トランジスタに電気的に接続された第 1 画素電極と、前記第 1 薄膜トランジスタ及び第 1 画素電極とともに第 1 画素を形成する第 1 対向電極と、第 2 信号線と、前記走査線及び第 2 信号線に電気的に接続された n チャネル型の第 2 薄膜トランジスタと、前記第 2 薄膜トランジスタに電気的に接続された第 2 画素電極と、前記第 2 薄膜トランジスタ及び第 2 画素電極とともに、前記第 1 画素に隣合う第 2 画素を形成する第 2 対向電極と、前記走査線、第 1 信号線、第 2 信号線、第 1 対向電極及び第 2 対向電極に電気的に接続された駆動部と、を備え、

前記駆動部は、前記第 1 画素電極と前記第 1 対向電極との間に第 1 電位差を、前記第 2 画素電極と前記第 2 対向電極との間に第 2 電位差を、それぞれ与え保持する際、

書込み期間に、前記第 1 対向電極に第 1 対向電圧を与え、前記第 2 対向電極に前記第 1 対向電圧よりロウレベルの第 2 対向電圧を与え、前記走査線に与える制御信号の電圧値を前記第 2 対向電圧よりロウレベルの第 1 電圧値に設定する書込みであって、前記第 1 対向電圧と前記第 1 電圧値との差は前記第 1 対向電圧と前記第 2 対向電圧との差の 2 倍以上である、前記書込みと、

前記書込み期間のうちの第 1 画像信号及び第 2 画像信号の特定書込み期間に、前記走査線に与える前記制御信号の電圧値を前記第 1 薄膜トランジスタの閾値電圧及び前記第 2 薄膜トランジスタの閾値電圧と同一レベル又はそれよりハイレベルの第 2 電圧値に一時的に設定し、前記第 1 画像信号を前記第 1 信号線に与え前記第 1 画素電極に書込み、前記第 2 画像信号を前記第 2 信号線に与え前記第 2 画素電極に書込み、前記第 1 電位差及び第 2 電位差を生じさせる、前記第 1 画像信号及び第 2 画像信号の特定書込みと、

前記書込み期間に続き、前記書込み期間より長い保持期間に、前記第 1 対向電極に前記第 1 対向電圧を与えた状態に維持し、前記第 2 対向電極に前記第 2 対向電圧を与えた状態に維持し、前記走査線に与える前記制御信号の電圧値を前記第 2 対向電圧よりロウレベルであり前記第 1 電圧値よりハイレベルである第 3 電圧値に設定し、前記第 1 電位差及び第 2 電位差を保持する、保持と、

を行うように構成されている。

【0007】

また、一実施形態に係る液晶表示装置は、

走査線と、第 1 信号線と、前記走査線及び第 1 信号線に電気的に接続された p チャネル型の第 1 薄膜トランジスタと、前記第 1 薄膜トランジスタに電気的に接続された第 1 画素電極と、前記第 1 薄膜トランジスタ及び第 1 画素電極とともに第 1 画素を形成する第 1 対向電極と、第 2 信号線と、前記走査線及び第 2 信号線に電気的に接続された p チャネル型の第 2 薄膜トランジスタと、前記第 2 薄膜トランジスタに電気的に接続された第 2 画素電極と、前記第 2 薄膜トランジスタ及び第 2 画素電極とともに、前記第 1 画素に隣合う第 2 画素を形成する第 2 対向電極と、前記走査線、第 1 信号線、第 2 信号線、第 1 対向電極及び第 2 対向電極に電気的に接続された駆動部と、を備え、

前記駆動部は、前記第 1 画素電極と前記第 1 対向電極との間に第 1 電位差を、前記第 2 画素電極と前記第 2 対向電極との間に第 2 電位差を、それぞれ与え保持する際、

書込み期間に、前記第 1 対向電極に第 1 対向電圧を与え、前記第 2 対向電極に前記第 1

10

20

30

40

50

対向電圧よりハイレベルの第2対向電圧を与え、前記走査線に与える制御信号の電圧値を前記第2対向電圧よりハイレベルの第1電圧値に設定する書込みであって、前記第1対向電圧と前記第1電圧値との差は前記第1対向電圧と前記第2対向電圧との差の2倍以上である、前記書込みと、

前記書込み期間のうちの第1画像信号及び第2画像信号の特定書込み期間に、前記走査線に与える前記制御信号の電圧値を前記第1薄膜トランジスタの閾値電圧及び前記第2薄膜トランジスタの閾値電圧と同一レベル又はそれよりロウレベルの第2電圧値に一時的に設定し、前記第1画像信号を前記第1信号線に与え前記第1画素電極に書込み、前記第2画像信号を前記第2信号線に与え前記第2画素電極に書込み、前記第1電位差及び第2電位差を生じさせる、前記第1画像信号及び第2画像信号の特定書込みと、

前記書込み期間に続き、前記書込み期間より長い保持期間に、前記第1対向電極に前記第1対向電圧を与えた状態に維持し、前記第2対向電極に前記第2対向電圧を与えた状態に維持し、前記走査線に与える前記制御信号の電圧値を前記第2対向電圧よりハイレベルであり前記第1電圧値よりロウレベルである第3電圧値に設定し、前記第1電位差及び第2電位差を保持する、保持と、

を行うように構成されている。

#### 【0008】

また、一実施形態に係る液晶表示装置の駆動方法は、

走査線と、第1信号線と、前記走査線及び第1信号線に電気的に接続されたnチャネル型の第1薄膜トランジスタと、前記第1薄膜トランジスタに電気的に接続された第1画素電極と、前記第1薄膜トランジスタ及び第1画素電極とともに第1画素を形成する第1対向電極と、第2信号線と、前記走査線及び第2信号線に電気的に接続されたnチャネル型の第2薄膜トランジスタと、前記第2薄膜トランジスタに電気的に接続された第2画素電極と、前記第2薄膜トランジスタ及び第2画素電極とともに、前記第1画素に隣合う第2画素を形成する第2対向電極と、を備えた液晶表示装置の駆動方法において、

前記第1画素電極と前記第1対向電極との間に第1電位差を、前記第2画素電極と前記第2対向電極との間に第2電位差を、それぞれ与え保持する際、

書込み期間に、前記第1対向電極に第1対向電圧を与え、前記第2対向電極に前記第1対向電圧よりロウレベルの第2対向電圧を与え、前記走査線に与える制御信号の電圧値を前記第2対向電圧よりロウレベルの第1電圧値に設定し、

前記書込み期間のうちの第1画像信号及び第2画像信号の特定書込み期間に、前記走査線に与える前記制御信号の電圧値を前記第1薄膜トランジスタの閾値電圧及び前記第2薄膜トランジスタの閾値電圧と同一レベル又はそれよりハイレベルの第2電圧値に一時的に設定し、前記第1画像信号を前記第1信号線に与え前記第1画素電極に書込み、前記第2画像信号を前記第2信号線に与え前記第2画素電極に書込み、前記第1電位差及び第2電位差を生じさせ、

前記書込み期間に続き、前記書込み期間より長い保持期間に、前記第1対向電極に前記第1対向電圧を与えた状態に維持し、前記第2対向電極に前記第2対向電圧を与えた状態に維持し、前記走査線に与える前記制御信号の電圧値を前記第2対向電圧よりロウレベルであり前記第1電圧値よりハイレベルである第3電圧値に設定し、前記第1電位差及び第2電位差を保持し、

前記第1対向電圧と前記第1電圧値との差は前記第1対向電圧と前記第2対向電圧との差の2倍以上である。

#### 【図面の簡単な説明】

#### 【0009】

【図1】図1は、一実施形態に係る液晶表示装置を示す概略構成図である。

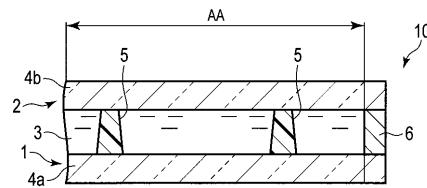

【図2】図2は、図1に示した液晶表示パネルの周縁部を示す概略断面図である。

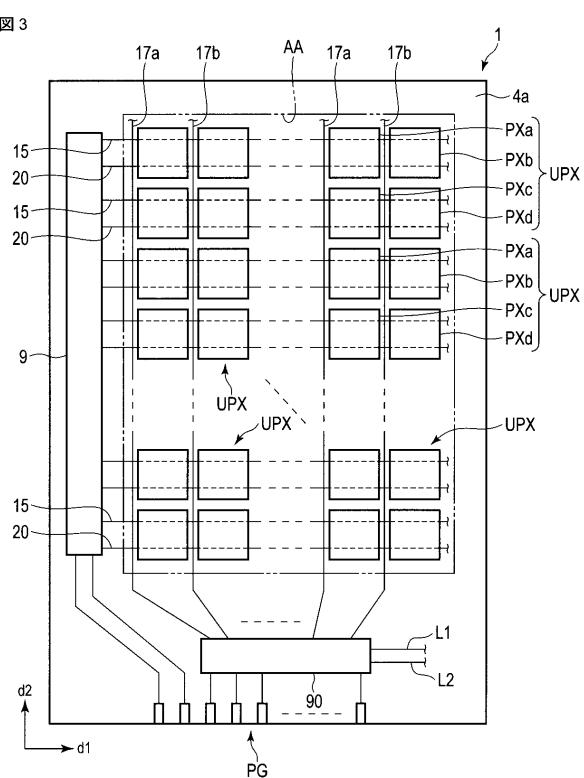

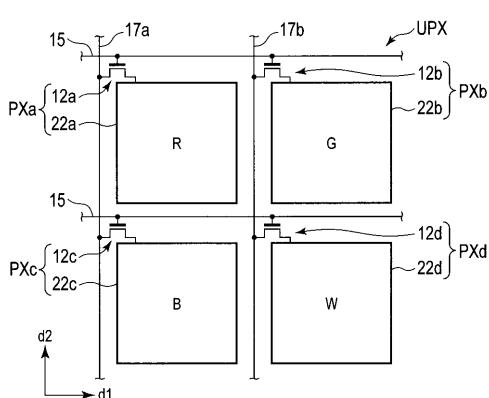

【図3】図3は、図1及び図2に示したアレイ基板の概略構成を示す平面図である。

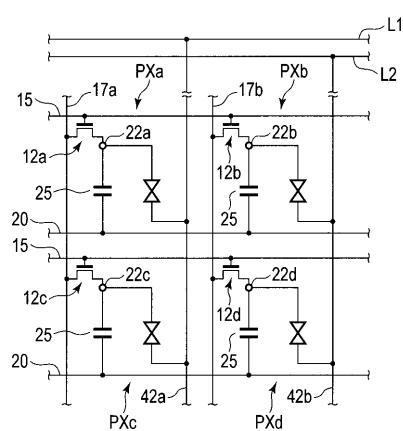

【図4】図4は、図3に示した単位画素を概略的に示す回路図である。

【図5】図5は、上記単位画素を示す等価回路である。

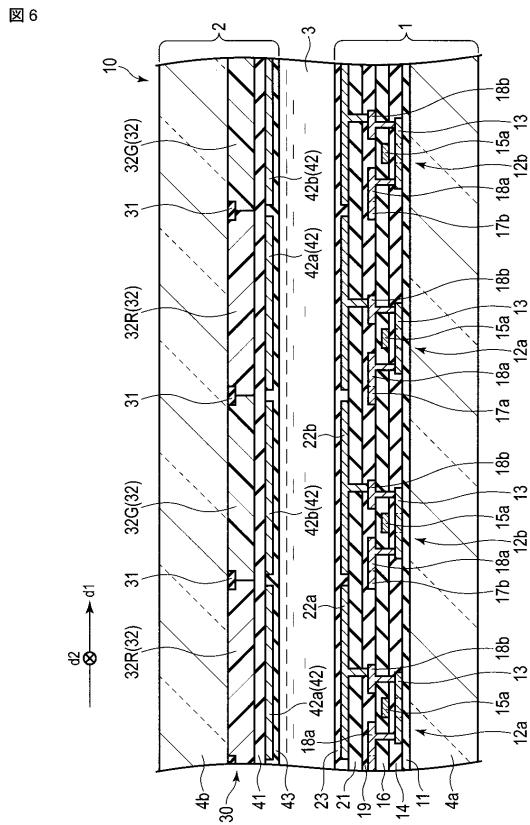

【図6】図6は、上記液晶表示パネルの一部を示す断面図であり、4個の画素を示す図である。

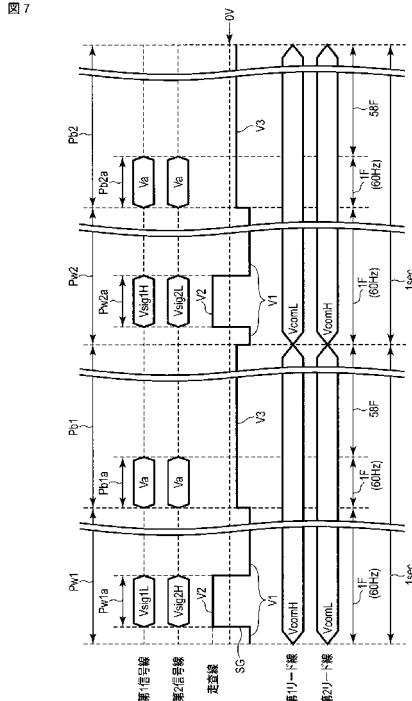

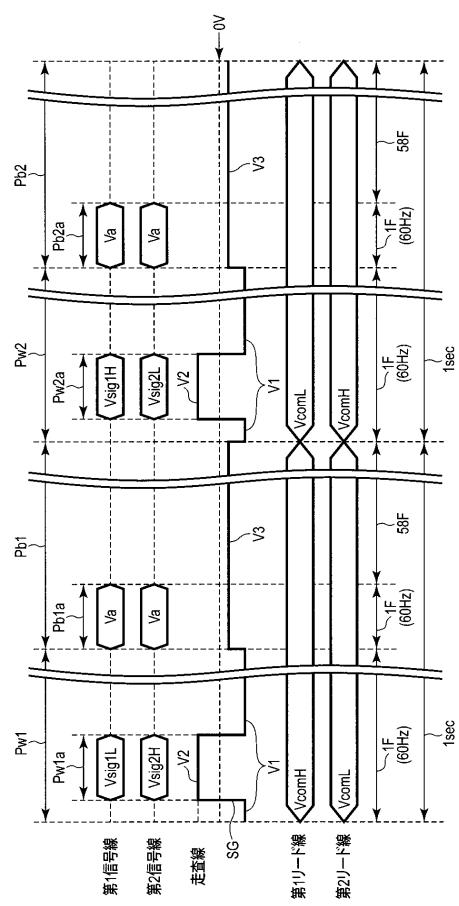

【図7】図7は、上記液晶表示装置の駆動方法を説明するためのタイミングチャートであり、(1)第1信号線を駆動する信号、(2)第2信号線を駆動する信号、(3)走査線を駆動する制御信号、(4)第1リード線を駆動する第1対向電圧、(5)第2リード線を駆動する第2対向電圧、を示す図である。

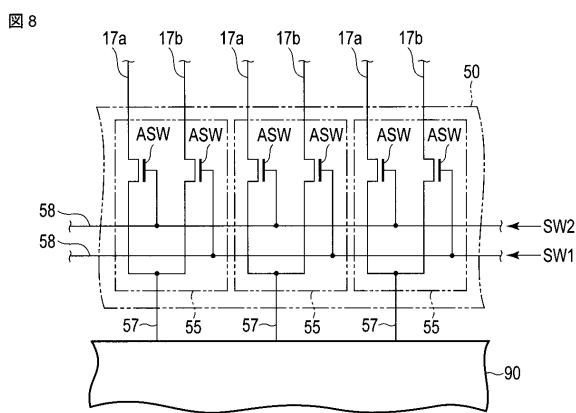

【図8】図8は、上記実施形態に係る液晶表示装置の変形例のアレイ基板の表示領域の外側を拡大して示す平面図であり、切替え回路を示す図である。

【発明を実施するための形態】

【0010】

以下に、本発明の各実施の形態について、図面を参照しつつ説明する。なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の様子に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。

【0011】

以下、図面を参照しながら一実施形態に係る液晶表示装置及び液晶表示装置の駆動方法について詳細に説明する。まず、液晶表示装置の構成について説明する。

図1及び図2に示すように、液晶表示装置は、液晶表示パネル10を備えている。本実施形態において、液晶表示パネル10は、TN(Twisted Nematic)方式を採用している。液晶表示パネル10は、アレイ基板1と、アレイ基板に所定の隙間を置いて対向配置された対向基板2と、これら両基板間に挟持された液晶層3とを備えている。その他、液晶表示装置は、画像信号出力部としての駆動回路90(信号線駆動回路)と、制御部100と、接続部110とを備えている。駆動回路90は、静止画を表示するための画像信号や、動画を表示するための画像信号(映像信号)を出力する。接続部110としては、FPC(flexible printed circuit)又はTCP(tape carrier package)を利用することができます。液晶表示パネル10は、表示領域AAを有している。表示領域AAは非表示領域で囲まれている。

【0012】

図1乃至図5に示すように、アレイ基板1は、透明な絶縁性の基板として、例えばガラス基板4aを備えている。表示領域AAにおいて、ガラス基板4a上にはマトリクス状に配置された複数の単位画素UPXが形成されている。単位画素UPXは、第1方向d1にm個並べられ、第1方向d1に直交した第2方向d2にn個並べられている。

【0013】

各単位画素UPXは、複数の画素PXを備えている。ここでは、各単位画素UPXは、第1乃至第4画素PXa乃至PXdを備えている。第2画素PXbは、第1画素PXaに第1方向d1に隣合って位置している。第3画素PXcは、第1画素PXaに第2方向d2に隣合って位置している。第4画素PXdは、第2画素PXbに第2方向d2に隣合いで第3画素PXcに第1方向d1に隣合って位置している。

【0014】

ここで、単位画素UPXの単位ではなく画素PXの単位に着目すると、複数の画素PXは、第1方向d1に $2 \times m$ 個並べられ、第2方向d2に $2 \times n$ 個並べられている。奇数行において、第1画素PXa及び第2画素PXbが第1方向d1に交互に並べられている。偶数行において、第3画素PXc及び第4画素PXdが第1方向d1に交互に並べられている。奇数列において、第1画素PXa及び第3画素PXcが第2方向d2に交互に並べられている。偶数列において、第2画素PXb及び第4画素PXdが第2方向d2に交互に並べられている。

なお、上記単位画素UPXを絵素と言い換えることができる。又は、単位画素UPXを

10

20

30

40

50

画素と言い換えることができ、この場合、上記画素 P X を副画素と言い換えることができる。

#### 【0015】

表示領域 A A の外側において、ガラス基板 4 a の上方に、駆動回路 9 及びアウタリードポンディング (outer lead bonding) のパッド群（以下、OLB パッド群と称する）PG が形成されている。本実施形態において、駆動回路 9 は、走査線駆動回路及び補助容量線駆動回路として利用される。なお、上記走査線駆動回路及び補助容量線駆動回路は、互いに分離して設けられてもよい。例えば図 3 を参照すると、非表示領域のうち、左側領域に走査線駆動回路が設けられ、右側領域に補助容量線駆動回路が設けられてもよい。

#### 【0016】

表示領域 A A において、ガラス基板 4 a の上方には、複数本 ( $2 \times m$  本) の信号線 17 及び複数本 ( $2 \times n$  本) の走査線 15 及び複数本 ( $2 \times n$  本) の補助容量線 20 が配置されている。

信号線 17 は、駆動回路 9 0 (信号線駆動回路) に接続されている。信号線 17 は、第 2 方向 d 2 に延在し第 1 方向 d 1 に互いに間隔を置いて設けられている。信号線 17 は、それぞれ一列の複数の画素 P X に電気的に接続されている。

#### 【0017】

走査線 15 は、駆動回路 9 (走査線駆動回路) に接続されている。走査線 15 は、第 1 方向 d 1 に延出し、第 2 方向 d 2 に互いに間隔を置いて設けられている。走査線 15 は、それぞれ一行の複数の画素 P X に電気的に接続されている。

補助容量線 20 は、駆動回路 9 (補助容量線駆動回路) に接続されている。補助容量線 20 は、第 1 方向 d 1 に延在し第 2 方向 d 2 に互いに間隔を置いて設けられている。補助容量線 20 は、それぞれ一行の複数の画素 P X に電気的に接続されている。

#### 【0018】

次に、単位画素 U P X を 1 つ取り出して説明する。

図 3 乃至図 5 に示すように、第 1 乃至第 4 画素 P X a 乃至 P X d は、互いに異なる色の画像を表示するように構成された画素である。この実施形態において、第 1 乃至第 4 画素 P X a 乃至 P X d は、赤色 (R)、緑色 (G)、青色 (B) 及び白色 (W) の画像を表示するように構成された画素である。単位画素 U P X は、いわゆる RGBW 正方画素 (RGBW の 4 個の正方形の画素が正方配列化された画素) で構成されている。

#### 【0019】

第 1 画素 P X a は、第 1 画素電極 2 2 a と、第 1 スイッチング素子 1 2 a と、補助容量素子 2 5 と、を有し、赤色 (R) の画像を表示するように構成されている。この実施形態において、第 1 スイッチング素子 1 2 a は、n チャネル型の薄膜トランジスタ (thin film transistor : TFT) で形成されている。第 1 スイッチング素子 1 2 a は、走査線 15 に電気的に接続された第 1 電極と、信号線 17 (17 a) に電気的に接続された第 2 電極と、第 1 画素電極 2 2 a に電気的に接続された第 3 電極と、を有している。第 1 画素電極 2 2 a は、第 1 対向電極 4 2 a との間に液晶容量を形成している。なお、各第 1 対向電極 4 2 a は、第 1 リード線 L 1 に接続され、第 1 リード線 L 1 等を介して駆動回路 9 0 (リード線駆動回路) に接続されている。

#### 【0020】

ここで、第 1 スイッチング素子 1 2 a において、上記第 1 電極がゲート電極として機能し、第 2 及び第 3 電極の一方がソース電極として機能し、第 2 及び第 3 電極の他方がドレイン電極として機能する。なお、これら第 1 乃至第 3 電極の機能に関しては、後述する第 2 乃至第 4 スイッチング素子 1 2 b 乃至 1 2 d においても同様である。

#### 【0021】

補助容量素子 2 5 は、第 1 画素電極 2 2 a に電気的に接続されている。この実施形態において、補助容量素子 2 5 は、第 1 画素電極 2 2 a と補助容量線 20 との間に形成されている。補助容量素子 2 5 の一方の電極は、第 1 画素電極 2 2 a 又は第 1 画素電極 2 2 a に接続された電極で形成されている。補助容量素子 2 5 の他方の電極は、対応する補助容量

10

20

30

40

50

線 2 0 の一部又は上記補助容量線 2 0 に接続された電極で形成されている。補助容量線 2 0 は、駆動回路 9 (補助容量線駆動回路) により駆動されている。なお、補助容量線 2 0 を駆動する必要が無い場合は、補助容量線駆動回路は特に必要でなく、各補助容量線 2 0 は何らかの定電位電源に接続されていてもよい。

#### 【 0 0 2 2 】

第 2 画素 P X b は、第 2 画素電極 2 2 b と、第 2 スイッチング素子 1 2 b と、補助容量素子 2 5 と、を有し、緑色 (G) の画像を表示するように構成されている。この実施形態において、第 2 スイッチング素子 1 2 b は、n チャネル型の TFT で形成されている。第 2 スイッチング素子 1 2 b は、走査線 1 5 に電気的に接続された第 1 電極と、信号線 1 7 (1 7 b) に電気的に接続された第 2 電極と、第 2 画素電極 2 2 b に電気的に接続された第 3 電極と、を有している。第 2 画素 P X b は、第 1 画素 P X a とともに同一の走査線 1 5 に接続されている。第 2 画素電極 2 2 b は、第 2 対向電極 4 2 b との間に液晶容量を形成している。なお、各第 2 対向電極 4 2 b は、第 2 リード線 L 2 に接続され、第 2 リード線 L 2 等を介して駆動回路 9 0 (リード線駆動回路) に接続されている。

10

#### 【 0 0 2 3 】

第 3 画素 P X c は、第 3 画素電極 2 2 c と、第 3 スイッチング素子 1 2 c と、補助容量素子 2 5 と、を有し、青色 (B) の画像を表示するように構成されている。この実施形態において、第 3 スイッチング素子 1 2 c は、n チャネル型の TFT で形成されている。第 3 スイッチング素子 1 2 c は、走査線 1 5 に電気的に接続された第 1 電極と、信号線 1 7 (1 7 a) に電気的に接続された第 2 電極と、第 3 画素電極 2 2 c に電気的に接続された第 3 電極と、を有している。第 3 画素 P X c は、第 1 画素 P X a とともに同一の第 1 信号線 1 7 a に接続されている。第 3 画素電極 2 2 c は、第 1 対向電極 4 2 a との間に液晶容量を形成している。

20

#### 【 0 0 2 4 】

第 4 画素 P X d は、第 4 画素電極 2 2 d と、第 4 スイッチング素子 1 2 d と、補助容量素子 2 5 と、を有し、白色 (W) の画像を表示するように構成されている。この実施形態において、第 4 スイッチング素子 1 2 d は、n チャネル型の TFT で形成されている。第 4 スイッチング素子 1 2 d は、走査線 1 5 に電気的に接続された第 1 電極と、信号線 1 7 (1 7 b) に電気的に接続された第 2 電極と、第 4 画素電極 2 2 d に電気的に接続された第 3 電極と、を有している。第 4 画素 P X d は、第 3 画素 P X c とともに同一の走査線 1 5 に接続され、第 2 画素 P X b とともに同一の第 2 信号線 1 7 b に接続されている。第 4 画素電極 2 2 d は、第 2 対向電極 4 2 b との間に液晶容量を形成している。

30

#### 【 0 0 2 5 】

上記のように、本実施形態において、各単位画素 U P X には、2 本の信号線 1 7 と 2 本の走査線 1 5 と、2 本の補助容量線 2 0 と、が接続されている。但し、信号線及び走査線に着目すると、各単位画素 U P X には、4 本の信号線 1 7 と 1 本の走査線 1 5 とが接続されてもよい。この場合、単位画素 U P X の第 1 乃至第 4 画素 P X a 乃至 P X d は、同一の走査線 1 5 に電気的に接続されている。そして、単位画素 U P X の第 1 乃至第 4 画素 P X a 乃至 P X d は、互いに異なる信号線 1 7 に電気的に接続されている。

40

#### 【 0 0 2 6 】

次に、液晶表示パネル 1 0 の断面構造について説明する。

図 4 乃至図 6 に示すように、ガラス基板 4 a 上にはアンダーコート膜 (絶縁膜) 1 1 が形成されている。アンダーコート膜 1 1 の上方に、複数のスイッチング素子 1 2 (1 2 a 乃至 1 2 d) が形成されている。詳しくは、アンダーコート膜 1 1 上に半導体層 1 3 が形成されている。

#### 【 0 0 2 7 】

半導体層 1 3 は、アモルファスシリコン、ポリシリコン、有機物半導体、酸化物半導体等の半導体で形成されている。本実施形態において、半導体層 1 3 は、酸化物半導体で形成された酸化物半導体層である。このような酸化物半導体としては、インジウム、ガリウム及び亜鉛の少なくとも 1 つを含む酸化物が好適に用いられる。酸化物半導体の体表的な

50

例としては、例えば、酸化インジウムガリウム亜鉛（IGZO）、酸化インジウムガリウム（IGO）、インジウム亜鉛酸化物（IZO）、亜鉛スズ酸化物（ZnSnO）、亜鉛酸化物（ZnO）及び透明アモルファス酸化物半導体（TAOS）などが挙げられる。

このような酸化物半導体から成る半導体層13は、アモルファスシリコンからなる半導体層と比較して高移動度を実現できる。また、このような酸化物半導体からなる半導体層13は、ポリシリコンからなる半導体層と比較して、低温で大面積に亘って均一に成膜することができ、製造コストの低減を図ることができる。

#### 【0028】

アンダーコート膜11及び半導体層13上に、ゲート絶縁膜14が形成されている。ゲート絶縁膜14上には、複数の走査線15が形成されている。走査線15は、半導体層13の第1領域（チャネル領域）と対向した複数の第1電極（ゲート電極）15aを有している。ゲート絶縁膜14及び走査線15（第1電極15a）上に、第1層間絶縁膜16が形成されている。10

#### 【0029】

第1層間絶縁膜16上に、複数の信号線17、複数の第2電極18a及び複数の第3電極18bが形成されている。信号線17、第2電極18a及び第3電極18bは、同一材料を利用し、同時に形成されている。信号線17は、第2電極18aと一緒に形成されている。第2電極18aは、ゲート絶縁膜14及び第1層間絶縁膜16に形成されたコンタクトホールを通り半導体層13の第2領域にコンタクトしている。第3電極18bは、ゲート絶縁膜14及び第1層間絶縁膜16に形成された他のコンタクトホールを通り半導体層13の第3領域にコンタクトしている。なお、第2及び第3領域の一方がソース領域として機能し、第2及び第3領域の他方がドレイン領域として機能する。上記のように、スイッチング素子12が形成されている。20

#### 【0030】

第1層間絶縁膜16、信号線17、第2電極18a及び第3電極18b上に、第2層間絶縁膜19が形成されている。第2層間絶縁膜19上に、絶縁膜21が形成されている。絶縁膜21は、平坦化膜としても機能し得る。絶縁膜21が平坦化膜として機能することにより、アレイ基板1の表面の凹凸を低減することができる。

絶縁膜21上に、複数の画素電極22（22a乃至22d）が形成されている。本実施形態において、画素電極22は、光反射導電層、透明導電層、又はこれらの積層体で形成されている。光反射導電層は、アルミニウム（aluminum：A1）等の金属材料を利用して形成することができる。透明導電層は、インジウム錫酸化物（indium tin oxide：ITO）、インジウム亜鉛酸化物（indium zinc oxide：IZO）等の透明な導電材料を利用して形成することができる。30

#### 【0031】

この実施形態において、画素電極22は、光反射導電層と透明導電層との積層体で形成された光反射型の画素電極である。液晶表示パネル10は光反射型の液晶表示パネルである。画素電極22は、光反射性を有し、表示面（対向基板2の外面）側から入射された光を上記表示面側に反射することができる。40

#### 【0032】

例えば、透明導電層は画素電極22の最上層に位置している。透明導電層のサイズは光反射導電層のサイズと同一であり、透明導電層は光反射導電層に完全に重なって形成されていてもよい。この場合、1回のフォトリソグラフィ工程で、積層された光反射導電膜及び透明導電膜にパターニングを施すことにより、光反射導電層及び透明導電層を同時に形成することができる。

なお、液晶表示パネル10は光透過型の液晶表示パネルであってもよい。この場合、画素電極22は、透明導電層のみで形成された光透過型の画素電極である。画素電極22は、光透過性を有し、アレイ基板1側から入射された光を対向基板2側に透過させることができる。50

## 【0033】

絶縁膜21及び画素電極22上には、柱状スペーサ5(図2)が形成されている。絶縁膜21、画素電極22及び柱状スペーサ5上には配向膜23が設けられている。配向膜23は液晶層3に接している。この実施形態において、配向膜23は水平配向膜であり、ラビング等の配向処理が施されている。これにより、配向膜23は、液晶層3の液晶分子を初期配向させることができる。

上記のように、アレイ基板1が形成されている。

## 【0034】

図6に示すように、一方、対向基板2は、透明な絶縁基板として、例えばガラス基板4bを備えている。ガラス基板4b上には、カラーフィルタ30が設けられている。カラーフィルタ30は、ブラックマトリクス31と、複数色の着色層(又は無着色層)32とを有している。ブラックマトリクス31は、複数の画素PXを区画するように格子状に形成されている。

10

## 【0035】

この実施形態において、カラーフィルタ30は、第1画素PXaを形成する赤色の着色層32(32R)、第2画素PXbを形成する緑色の着色層32(32G)、第3画素PXcを形成する青色の着色層32、及び第4画素PXdを形成する透明な無着色層32を有している。なお、上記カラーフィルタ30は、無着色層32無しに形成することができ得る。

20

## 【0036】

また、この実施形態において、カラーフィルタ30上にオーバーコート膜41が設けられている。オーバーコート膜41は、対向基板2の表面の凹凸を低減する機能を有している。なお、オーバーコート膜41は必要に応じて設けられていればよい。オーバーコート膜41上には、対向電極(共通電極)42及び配向膜43が順に設けられている。

20

## 【0037】

この実施形態において、対向電極42は、ITO、IZO等の透明な導電材料を利用して形成されている。また、対向電極42は、複数の第1対向電極42aと、複数の第2対向電極42bと、を有している。第1対向電極42a及び第2対向電極42bは、それぞれ帯状に形成され、第2方向d2に延在し、第1方向d1に間隔を置いて交互に並べられている。各第1対向電極42aは、奇数列のうちの任意の一列の全ての画素PXの画素電極22と対向している。各第2対向電極42bは、偶数列のうちの任意の一列の全ての画素PXの画素電極22と対向している。

30

このため、第1対向電極42a及び第2対向電極42bは、それぞれ複数の画素PXの形成に寄与している。また、第1対向電極42a及び第2対向電極42bは、それぞれ複数の画素PXで共用される共通電極である。

## 【0038】

本実施形態において、液晶表示装置はカラム反転駆動法を利用し、かつ、信号線17を駆動する電圧を半減するため、対向電極42は、帯状の第1対向電極42a及び第2対向電極42bを有している。列単位及びフレーム単位で、第1対向電極42a及び第2対向電極42bの電位も変動させることにより、液晶層3を交流駆動することができる。

40

このため、動画を表示する際の任意のN番目の1フレーム期間内に、画素電極22に画像信号が与えられると、奇数列の画素PXの画素電極22の電位は第1対向電極42aの電位と同一かそれより高くなり、偶数列の画素PXの画素電極22の電位は第2対向電極42bの電位と同一かそれより低くなる。そして、N+1番目の1フレーム期間内に、画素電極22に画像信号が与えられると、奇数列の画素PXの画素電極22の電位は第1対向電極42aの電位と同一かそれより低くなり、偶数列の画素PXの画素電極22の電位は第2対向電極42bの電位と同一かそれより高くなる。

すなわち、N番目の1フレーム期間内に、奇数列では、画素電極22が正極性の電極、第1対向電極42aが負極性の電極となり、偶数列では、画素電極22が負極性の電極、第2対向電極42bが正極性の電極となる。N+1番目の1フレーム期間内に、奇数列で

50

は、画素電極 22 が負極性の電極、第 1 対向電極 42a が正極性の電極となり、偶数列では、画素電極 22 が正極性の電極、第 2 対向電極 42b が負極性の電極となる。

#### 【0039】

配向膜 43 は液晶層 3 に接している。配向膜 43 は、水平配向膜であり、ラビング等の配向処理が施されている。これにより、配向膜 43 は、液晶層 3 の液晶分子を初期配向させることができる。

上記のように、対向基板 2 が形成されている。

#### 【0040】

図 2 に示すように、アレイ基板 1 及び対向基板 2 間の所定の隙間は柱状スペーサ 5 により保持されている。アレイ基板 1 及び対向基板 2 は、これら両基板の周縁部に配置されたシール材 6 により接合されている。液晶層 3 は、アレイ基板 1、対向基板 2 及びシール材 6 で囲まれた空間に形成されている。本実施形態において、液晶層 3 は、ポジ型の液晶材料で形成されている。

10

上記のように液晶表示装置が形成されている。

#### 【0041】

次に、上記のように構成された液晶表示装置の駆動方法について説明する。

駆動部（駆動回路 9 及び駆動回路 90 等）は、走査線 15、補助容量線 20 及び信号線 17 を駆動し、画素電極 22 に画像信号を書込んでいる。液晶表示装置が動画や静止画を表示する場合、駆動部は走査線 15 及び信号線 17 を毎フレーム駆動する。但し、液晶表示装置が静止画を表示する場合、駆動部は走査線 15 及び信号線 17 を数フレーム置きに駆動（間欠駆動）することもできる。

20

#### 【0042】

図 4 及び図 5 に示した第 1 画素 P X a 及び第 2 画素 P X b に着目すると、本実施形態において、駆動部は、第 1 画素電極 22a と第 1 対向電極 42aとの間に第 1 電位差を、第 2 画素電極 22b と第 2 対向電極 42b との間に第 2 電位差を、それぞれ与え保持する際、すなわち、静止画を表示する際、次のように走査線 15 及び信号線 17 等を駆動する。

#### 【0043】

書き込み期間に、駆動部は、第 1 対向電極 42a に第 1 対向電圧を与え、第 2 対向電極 42b に第 1 対向電圧よりロウレベルの第 2 対向電圧を与え、走査線 15 に与える制御信号の電圧値を第 2 対向電圧よりロウレベルの第 1 電圧値に設定する書き込みを行う。

30

ここで、ロウレベルとは、相対的に負であることを言う。例えば、第 2 対向電圧は、第 1 対向電圧より相対的に負の電圧である。また、第 1 対向電圧と第 1 電圧値との差は、第 1 対向電圧と第 2 対向電圧との差の 2 倍以上である。

#### 【0044】

上記書き込み期間のうちの第 1 画像信号及び第 2 画像信号の特定書き込み期間に、駆動部は、第 1 画像信号及び第 2 画像信号の特定書き込みを行う。詳しくは、駆動部は、走査線 15 に与える制御信号の電圧値を第 1 スイッチング素子 12a の閾値電圧及び第 2 スイッチング素子 12b の閾値電圧と同一レベル又はそれよりハイレベルの第 2 電圧値に一時的に設定し、第 1 画像信号を第 1 信号線 17a に与え第 1 画素電極 22a に書き込み、第 2 画像信号を第 2 信号線 17b に与え第 2 画素電極 22b に書き込む。これにより、上記第 1 電位差及び第 2 電位差を生じさせる。

40

ここで、ハイレベルとは、相対的に正であることを言う。例えば、第 2 電圧値は、第 1 スイッチング素子 12a の閾値電圧及び第 2 スイッチング素子 12b の閾値電圧と同一レベル又はそれより相対的に正の電圧値である。

#### 【0045】

上記書き込み期間に続き、上記書き込み期間より長い保持期間に、駆動部は、上記第 1 電位差及び第 2 電位差を保持する、保持を行う。詳しくは、駆動部は、第 1 対向電極 42a に第 1 対向電圧を与えた状態に維持し、第 2 対向電極 42b に第 2 対向電圧を与えた状態に維持し、走査線 15 に与える制御信号の電圧値を第 2 対向電圧よりロウレベルであり第 1 電圧値よりハイレベルである第 3 電圧値に設定する。

50

## 【0046】

次に、液晶表示装置の駆動方法の実施例について説明する。ここでは、図4及び図5に示した第1画素P X a及び第2画素P X bに着目し、第1画素電極2 2 aと第1対向電極4 2 aとの間に第1電位差を、第2画素電極2 2 bと第2対向電極4 2 bとの間に第2電位差を、それぞれ与え保持し、静止画を表示する場合について説明する。なお、静止画を表示する期間も補助容量線2 0は定電位に固定されている。

## 【0047】

図7、及び図3乃至図5に示すように、第1書き込み期間P w 1及び第1保持期間P b 1の和は1秒間に相当し、第2書き込み期間P w 2及び第2保持期間P b 2の和は1秒間に相当する。第1書き込み期間P w 1は1フレーム期間(1/60秒)である。第1書き込み期間P w 1に、駆動部は60Hzのフレームレートで書き込み動作を行う。

10

## 【0048】

まず、第1書き込み期間P w 1に、駆動回路9 0は、第1対向電極4 2 aに第1対向電圧V c o m Hを与える、第2対向電極4 2 bに第1対向電圧V c o m Hよりロウレベルの第2対向電圧V c o m Lを与える。駆動回路9は、走査線1 5に与える制御信号S Gの電圧値を第2対向電圧V c o m Lよりロウレベルの第1電圧値V 1に設定する。第1対向電圧V c o m Hと第1電圧値V 1との差は第1対向電圧V c o m Hと第2対向電圧V c o m Lとの差の2倍以上である。この実施形態において、電圧値を例示すると、第1対向電圧V c o m Hは+4.0V(ボルト)、第2対向電圧V c o m Lは+0.2V、第1電圧値V 1は-6.0Vである。

20

上記のように、第1対向電圧V c o m Hと第1電圧値V 1との差を第1対向電圧V c o m Hと第2対向電圧V c o m Lとの差の2倍以上にすることにより、走査線1 5(第1電極1 5 a)の電位が第1画素電極2 2 aの電位又は第2画素電極2 2 bの電位より不所望に高くなる事態を回避することができる。

## 【0049】

第1書き込み期間P w 1のうちの第1画像信号及び第2画像信号の第1特定書き込み期間P w 1 aは、ここでは、一水平走査期間に相当する。第1特定書き込み期間P w 1 aに、駆動部は、第1画像信号V s i g 1 L及び第2画像信号V s i g 2 Hの第1特定書き込みを行う。第1特定書き込み期間P w 1 aに、駆動回路9は、走査線1 5に与える制御信号S Gの電圧値を第1スイッチング素子1 2 aの閾値電圧及び第2スイッチング素子1 2 bの閾値電圧と同一レベル又はそれよりハイレベルの第2電圧値V 2に一時的に設定し、駆動回路9 0は、第1画像信号V s i g 1 Lを第1信号線1 7 aに与え第1画素電極2 2 aに書き込み、第2画像信号V s i g 2 Hを第2信号線1 7 bに与え第2画素電極2 2 bに書き込む。これにより、上記第1電位差及び第2電位差を生じさせることができる。

30

ここで、第1画像信号V s i g 1 Lは、第1対向電圧V c o m Hと第2対向電圧V c o m Lとの間の電圧値を有し、ロウレベルの第1画像信号である。このため、第1画素電極2 2 aが負極性の電極、第1対向電極4 2 aが正極性の電極となる。一方、第2画像信号V s i g 2 Hは、第1対向電圧V c o m Hと第2対向電圧V c o m Lとの間の電圧値を有し、ハイレベルの第2画像信号である。このため、第2画素電極2 2 bが正極性の電極、第2対向電極4 2 bが負極性の電極となる。

40

この実施形態において、電圧値を例示すると、第2電圧値V 2は+10Vである。

## 【0050】

第1書き込み期間P w 1に続き、第1書き込み期間P w 1より長い第1保持期間P b 1に、駆動部は、上記第1電位差及び第2電位差の保持を行う。この実施形態において、第1保持期間P b 1は、59フレーム期間(59/60秒)である。第1保持期間P b 1に、駆動回路9 0は、第1対向電極4 2 aに第1対向電圧V c o m Hを与えた状態に維持し、第2対向電極4 2 bに第2対向電圧V c o m Lを与えた状態に維持し、駆動回路9は、走査線1 5に与える制御信号S Gの電圧値を第2対向電圧V c o m Lよりロウレベルであり第1電圧値V 1よりハイレベルである第3電圧値V 3に設定する。

制御信号S Gの電圧値を第1電圧値V 1に設定した場合より第3電圧値V 3に設定した

50

場合の方が、走査線 15（第1電極 15a）の電位と第1画素電極 22a の電位との差や、走査線 15（第1電極 15a）の電位と第2画素電極 22b の電位との差を小さくすることができる。第1スイッチング素子 12a や第2スイッチング素子 12b にかかるバイアス電圧を小さくすることができるため、半導体層 13（第1スイッチング素子 12a, 第2スイッチング素子 12b）に生じるリーク電流の低減に寄与することができる。これにより、上記第1電位差及び第2電位差を良好に保持することができる。

そして、上記のように第1保持期間 P<sub>b</sub>1 を設けることにより、液晶表示装置の低消費電力化に寄与することができる。

#### 【0051】

さらに本実施形態において、駆動回路 90（駆動部）は、第1保持期間 P<sub>b</sub>1 に、第1対向電圧 V<sub>c o m H</sub> と第2対向電圧 V<sub>c o m L</sub> との中間の電圧レベルの調整信号 V<sub>a</sub> を第1信号線 17a 及び第2信号線 17b にそれぞれ与えるように構成されている。この実施形態において、電圧値を例示すると、調整信号 V<sub>a</sub> の電圧値は +2.1V である。

また、この例では、第1保持期間 P<sub>b</sub>1 のうちの第1電圧調整期間 P<sub>b</sub>1a に、調整信号 V<sub>a</sub> が第1信号線 17a 及び第2信号線 17b にそれぞれ与えられている。第1電圧調整期間 P<sub>b</sub>1a は、第1保持期間 P<sub>b</sub>1 の最初の1フレーム期間である。しかしながら、第1電圧調整期間 P<sub>b</sub>1a の長さは、種々変形可能であり、1フレーム期間未満であったり、1フレーム期間を超えたとしてもよい。例えば、第1電圧調整期間 P<sub>b</sub>1a の長さと第1保持期間 P<sub>b</sub>1 の長さとが一致してもよい。信号線に第2電圧を書き込んだのち、信号線をハイインピーダンス状態において（信号線に電気的な書き込みがされないようにする）、保持させておくのでも良い。

#### 【0052】

このように、第1保持期間 P<sub>b</sub>1 に、第1信号線 17a 及び第2信号線 17b の電圧値を調整信号 V<sub>a</sub> の電圧値に設定した方が、第1信号線 17a の電位と第1画素電極 22a の電位との差や、第2信号線 17b の電位と第2画素電極 22b の電位との差を小さくすることができる。第1スイッチング素子 12a や第2スイッチング素子 12b にかかるバイアス電圧を小さくすることができるため、半導体層 13（第1スイッチング素子 12a, 第2スイッチング素子 12b）に生じるリーク電流の低減に寄与することができる。特に、第1画像信号 V<sub>s i g 1 L</sub> の電圧値や第2画像信号 V<sub>s i g 2 H</sub> の電圧値が、第1対向電圧 V<sub>c o m H</sub> と第2対向電圧 V<sub>c o m L</sub> との中間の電圧レベルに近い程、半導体層 13 に生じるリーク電流を低減することができる。これにより、上記第1電位差及び第2電位差を良好に保持することができる。

#### 【0053】

第1保持期間 P<sub>b</sub>1 に続く第2書き込み期間 P<sub>w</sub>2 に、駆動回路 90 は、第1対向電極 42a に第2対向電圧 V<sub>c o m L</sub> を与え、第2対向電極 42b に第1対向電圧 V<sub>c o m H</sub> を与え、駆動回路 9 は、走査線 15 に与える制御信号 SG の電圧値を第1電圧値 V<sub>1</sub> に設定する。

ここでも、第1対向電圧 V<sub>c o m H</sub> と第1電圧値 V<sub>1</sub> との差を第1対向電圧 V<sub>c o m H</sub> と第2対向電圧 V<sub>c o m L</sub> との差の2倍以上にすることにより、走査線 15（第1電極 15a）の電位が第1画素電極 22a の電位又は第2画素電極 22b の電位より不所望に高くなる事態を回避することができる。

#### 【0054】

第2書き込み期間 P<sub>w</sub>2 のうちの第1画像信号及び第2画像信号の第2特定書き込み期間 P<sub>w</sub>2a は、ここでは、一水平走査期間に相当する。第2特定書き込み期間 P<sub>w</sub>2a に、駆動部は、第1画像信号 V<sub>s i g 1 H</sub> 及び第2画像信号 V<sub>s i g 2 L</sub> の第2特定書き込みを行う。第2特定書き込み期間 P<sub>w</sub>2a に、駆動回路 9 は、走査線 15 に与える制御信号 SG の電圧値を第2電圧値 V<sub>2</sub> に一時的に設定し、駆動回路 9 0 は、第1画像信号 V<sub>s i g 1 H</sub> を第1信号線 17a に与え第1画素電極 22a に書き込み、第2画像信号 V<sub>s i g 2 L</sub> を第2信号線 17b に与え第2画素電極 22b に書き込む。これにより、上記第1電位差及び第2電位差を生じさせることができる。

10

20

30

40

50

なお、第1画素電極22aの電位と第1対向電極42aの電位との差の絶対値は、第1特定書き込み期間Pw1aと第2特定書き込み期間Pw2aとで同一である。同様に、第2画素電極22bの電位と第2対向電極42bの電位との差の絶対値は、第1特定書き込み期間Pw1aと第2特定書き込み期間Pw2aとで同一である。

#### 【0055】

ここで、第1画像信号Vsig1Hは、第1対向電圧VcomHと第2対向電圧VcomLとの間の電圧値を有し、ハイレベルの第1画像信号である。このため、第1画素電極22aが正極性の電極、第1対向電極42aが負極性の電極となる。一方、第2画像信号Vsig2Lは、第1対向電圧VcomHと第2対向電圧VcomLとの間の電圧値を有し、ロウレベルの第2画像信号である。このため、第2画素電極22bが負極性の電極、第2対向電極42bが正極性の電極となる。

10

#### 【0056】

このため、このように静止画を表示する際は、1秒単位でいわゆるカラムコモン反転駆動を行うことができる。これにより、1秒毎に、第1画素電極22aの電位と第1対向電極42aの電位との関係が反転し、同様に、第2画素電極22bの電位と第2対向電極42bの電位との関係が反転する。液晶層3に交流電圧を印加することができるため、液晶材料の劣化を抑制することができる。

#### 【0057】

第2書き込み期間Pw2に続き、第2書き込み期間Pw2より長い第2保持期間Pb2に、駆動部は、上記第1電位差及び第2電位差の保持を行う。この実施形態において、第2保持期間Pb2は、59フレーム期間(59/60秒)である。第2保持期間Pb2に、駆動回路90は、第1対向電極42aに第2対向電圧VcomLを与えた状態に維持し、第2対向電極42bに第1対向電圧VcomHを与えた状態に維持し、駆動回路9は、走査線15に与える制御信号SGの電圧値を第3電圧値V3に設定する。

20

この場合も、制御信号SGの電圧値を第1電圧値V1に設定した場合より第3電圧値V3に設定した場合の方が、半導体層13(第1スイッチング素子12a, 第2スイッチング素子12b)に生じるリーク電流の低減に寄与することができる。これにより、上記第1電位差及び第2電位差を良好に保持することができる。

そして、上記のように第2保持期間Pb2を設けることにより、液晶表示装置の低消費電力化に寄与することができる。

30

#### 【0058】

さらに本実施形態において、駆動回路90(駆動部)は、第2保持期間Pb2に、調整信号Vaを第1信号線17a及び第2信号線17bにそれぞれ与えるように構成されている。

また、この例では、第2保持期間Pb2のうちの第2電圧調整期間Pb2aに、調整信号Vaが第1信号線17a及び第2信号線17bにそれぞれ与えられている。第2電圧調整期間Pb2aは、第2保持期間Pb2の最初の1フレーム期間である。しかしながら、第2電圧調整期間Pb2aの長さは、種々変形可能であり、1フレーム期間未満であったり、1フレーム期間を超えたとしてもよい。例えば、第2電圧調整期間Pb2aの長さと第2保持期間Pb2の長さとが一致してもよい。信号線に第2電圧を書き込んだのち、信号線をハイインピーダンス状態において(信号線に電気的な書き込みがされないようにする)、保持させておくのでも良い。

40

#### 【0059】

このように、第2保持期間Pb2に、第1信号線17a及び第2信号線17bの電圧値を調整信号Vaの電圧値に設定した方が、半導体層13(第1スイッチング素子12a, 第2スイッチング素子12b)に生じるリーク電流の低減に寄与することができる。特に、第1画像信号Vsig1Hの電圧値や第2画像信号Vsig2Lの電圧値が、第1対向電圧VcomHと第2対向電圧VcomLとの中間の電圧レベルに近い程、半導体層13に生じるリーク電流を低減することができる。これにより、上記第1電位差及び第2電位差を良好に保持することができる。

50

## 【0060】

上記第2保持期間Pb2の後、駆動部は、第1特定書き込みを含む第1書き込み期間Pw1の書き込みと、第1保持期間Pb1の保持と、第2特定書き込みを含む第2書き込み期間Pw2の書き込みと、第2保持期間Pb2の保持と、を繰り返し、上記第1電位差及び第2電位差を保持するように構成されていてもよい。これにより、静止画を表示する時間を調整することができ、低消費電力化に寄与することができ、表示品位に優れた画像の表示を保持することができる。

## 【0061】

上記のように構成された一実施形態に係る液晶表示装置及び液晶表示装置の駆動方法によれば、液晶表示装置は、走査線15と、第1信号線17aと、第1スイッチング素子12aと、第1画素電極22aと、第1対向電極42aと、第2信号線17bと、第2スイッチング素子12bと、第2画素電極22bと、第2対向電極42bと、駆動部(駆動回路9,90)と、を備えている。第1スイッチング素子12a及び第2スイッチング素子12bは、nチャネル型のTFTで形成されている。第1スイッチング素子12a、第1画素電極22a及び第1対向電極42aは、とともに第1画素PXaを形成している。第2スイッチング素子12b、第2画素電極22b及び第2対向電極42bは、とともに第2画素PXbを形成している。

10

## 【0062】

駆動部は、第1画素電極22aと第1対向電極42aとの間に第1電位差を、第2画素電極22bと第2対向電極42bとの間に第2電位差を、それぞれ与え保持する際、書き込みと、保持と、を行うように構成されている。

20

## 【0063】

上記書き込みでは、第1書き込み期間Pw1に、駆動部は、第1対向電極42aに第1対向電圧VcomHを与え、第2対向電極42bに第2対向電圧VcomLを与え、走査線15に与える制御信号SGの電圧値を第1電圧値V1に設定する。第1対向電圧VcomHと第1電圧値V1との差は第1対向電圧VcomHと第2対向電圧VcomLとの差の2倍以上である。これにより、走査線15(第1電極15a)の電位が第1画素電極22aの電位又は第2画素電極22bの電位より不所望に高くなる事態を回避することができる。

30

## 【0064】

第1書き込み期間Pw1のうちの第1画像信号及び第2画像信号の第1特定書き込み期間Pw1aに、駆動部は、走査線15に与える制御信号SGの電圧値を第2電圧値V2に一時的に設定し、第1画像信号Vsig1Lを第1信号線17aに与え第1画素電極22aに書き込み、第2画像信号Vsig2Hを第2信号線17bに与え第2画素電極22bに書き込んでいる。これにより、上記第1電位差及び第2電位差を生じさせることができる。

## 【0065】

第1書き込み期間Pw1に続き、第1書き込み期間Pw1より長い第1保持期間Pb1に、駆動部は、第1対向電極42aに第1対向電圧VcomHを与えた状態に維持し、第2対向電極42bに第2対向電圧VcomLを与えた状態に維持し、走査線15に与える制御信号SGの電圧値を第3電圧値V3に設定している。

40

## 【0066】

制御信号SGの電圧値を第3電圧値V3に設定することにより、走査線15(第1電極15a)の電位と第1画素電極22aの電位との差や、走査線15(第1電極15a)の電位と第2画素電極22bの電位との差を小さくすることができる。第1スイッチング素子12aや第2スイッチング素子12bにかかるバイアス電圧を小さくすることができるため、半導体層13(第1スイッチング素子12a, 第2スイッチング素子12b)に生じるリーク電流の低減に寄与することができる。これにより、上記第1電位差及び第2電位差を良好に保持することができる。

画素電極22(例えば第1画素電極22a又は第2画素電極22b)の電位の変化を抑制することができるため、フリッカの発生を抑制することができる。そして、上記のよう

50

に第1保持期間Pb1を設けることにより、液晶表示装置の低消費電力化に寄与することができる。

上記のことから、低消費電力化を図ることのできる液晶表示装置及び液晶表示装置の駆動方法を得ることができる。又は、表示品位に優れた液晶表示装置及び液晶表示装置の駆動方法を得ることができる。

#### 【0067】

次に、上記実施形態に係る液晶表示装置の変形例について説明する。

図8に示すように、液晶表示装置は、切替え回路50をさらに備えていてもよい。この場合も、上述した実施形態と同様の効果を得ることができる。

切替え回路50は、複数の切替え素子群55を有し、切替え素子群55はそれぞれ複数の切替え素子ASWを有している。この実施の形態において、切替え素子群55はそれぞれ2個の切替え素子ASWを有している。切替え回路50は、1/2マルチプレクサ回路である。切替え素子ASWとしては、例えばTFTであり、上記スイッチング素子12と同様に形成することができ得る。

10

#### 【0068】

切替え回路50は、複数の信号線17(17a, 17b)に接続されている。また、切替え回路50は、接続配線57を介して駆動回路90に接続されている。ここでは、接続配線57の本数は、信号線17の本数の1/2である。

駆動回路90の出力(接続配線57)1個当たり2本の信号線17を時分割駆動するよう、切替え素子(アナログスイッチ)ASWは、制御信号SW1及びSW2により、オン/オフが切替えられる。これら制御信号SW1及びSW2は、制御部100から、OLBパッド群pG(図3)、複数の制御配線58を介して切替え素子ASWにそれぞれ与えられる。

20

上記の変形例によれば、信号線17は時分割駆動されている。このため、信号線17を駆動するために駆動回路90及び制御部100等によって生成される画像信号の数を半分にすることができる。これにより、上述した実施形態と同様に、外部ソースI/C(駆動回路90及び制御部100)の消費電力の増大を抑制することができる。

30

#### 【0069】

本発明の実施形態を説明したが、上記実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

30

#### 【0070】

例えば、スイッチング素子12(12a, 12b, 12c, 12d)は、pチャネル型のTFTで形成されていてもよい。この場合も、上述した実施形態と同様の効果を得ることができ。但し、この場合、次の点で上述した実施形態と相違する。第2対向電圧VcomLは第1対向電圧VcomHよりハイレベルの電圧となる。第1電圧値V1は第2対向電圧VcomLよりハイレベルの電圧となる。第2電圧値V2は、第1スイッチング素子12aの閾値電圧及び第2スイッチング素子12bの閾値電圧と同一レベル又はそれよりロウレベルの電圧値となる。第3電圧値V3は、第2対向電圧VcomLよりハイレベルであり、第1電圧値V1よりロウレベルとなる。

40

#### 【0071】

画素電極22(22a, 22b, 22c, 22d)の形状は、正方形に限定されるものではなく、種々変形可能であり、長方形であってもよい。画素電極22の形状は、矩形状以外の形状であってもよい。これらの場合であっても、上述した実施形態の効果と同様の効果を得ることができます。

単位画素UPXは、RGBW正方画素に限らず、種々変形可能であり、例えば、いわゆるRGBW縦ストライプ画素(RGBWの4個の長方形の画素(画素電極)がストライプ状に配列された画素)で構成されていてもよい。

50

また、単位画素 U P X は、いわゆる R G B 縱ストライプ画素（一般的な 3 原色である R G B の 3 個の長方形の画素（画素電極）がストライプ状に配列された画素）で構成されていてもよい。単位画素 U P X は、さらに、Y（黄色）画素や、W 画素及び Y 画素の両方を備えた 4 色以上の画素で構成されていてもよい。

#### 【0072】

上述した実施形態では、液晶表示パネル 10 は、TN (Twisted Nematic) 方式を採用している。しかしながら、これに限定されるものではなく、液晶表示パネルは、TN 方式以外の表示方式を採用してもよい。例えば、液晶表示パネルは、FFS (Fringe Field Switching) 方式等の主として基板正面に略平行な横電界を利用する IPS (In-Plane Switching) 方式を採用していてもよい。そして、液晶表示パネルは、補助容量素子 25 無しに形成されていてもよい。10

また、液晶表示装置は、光反射型の液晶表示装置に限定されるものではなく、種々変形可能であり、光透過型の液晶表示装置であってもよい。

上述した実施形態は、上述した液晶表示装置及びその駆動方法に限定されるものではなく、各種の液晶表示装置及びその駆動方法に適用可能である。

#### 【符号の説明】

#### 【0073】

1 ... アレイ基板、2 ... 対向基板、3 ... 液晶層、9, 90 ... 駆動回路、10 ... 液晶表示パネル、12, 12a, 12b, 12c, 12d ... スイッチング素子、13 ... 半導体層、15 ... 走査線、17, 17a, 17b ... 信号線、22, 22a, 22b, 22c, 22d ... 画素電極、25 ... 補助容量素子、42, 42a, 42b ... 対向電極、P X, P X a, P X b, P X c, P X d ... 画素、L 1, L 2 ... リード線、P w 1 ... 第 1 書込み期間、P w 1 a ... 第 1 特定書込み期間、P b 1 ... 第 1 保持期間、P b 1 a ... 第 1 電圧調整期間、P w 2 ... 第 2 書込み期間、P w 2 a ... 第 2 特定書込み期間、P b 2 ... 第 2 保持期間、P b 2 a ... 第 2 電圧調整期間、V sig 1 L, V sig 1 H ... 第 1 画像信号、V sig 2 H, V sig 2 L ... 第 2 画像信号、V com H ... 第 1 対向電圧、V com L ... 第 2 対向電圧、V 1, V 2, V 3 ... 電圧値。20

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【 四 6 】

【 四 7 】

( 8 )

---

フロントページの続き

|              |         |              |

|--------------|---------|--------------|

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|              | G 0 9 G | 3/20 6 2 3 D |

|              | G 0 9 G | 3/20 6 1 1 A |

|              | G 0 9 G | 3/20 6 1 1 E |

(72)発明者 木村 裕之

東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

(72)発明者 多田 正浩

東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

(72)発明者 綱島 貴徳

東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

F ターム(参考) 5C006 AA02 AA22 AC25 AC27 BB16 BB28 BC03 BC06 BC11 FA23

FA47 FA48

5C080 AA10 BB05 CC03 DD06 DD26 FF11 JJ01 JJ02 JJ03 JJ04

JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2016066029A</a>                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2016-04-28 |

| 申请号            | JP2014196075                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2014-09-26 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 中村卓<br>木村裕之<br>多田正浩<br>綱島貴徳                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 中村 卓<br>木村 裕之<br>多田 正浩<br>綱島 貴徳                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/36 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F1分类号          | G09G3/36 G09G3/20.624.B G09G3/20.624.D G09G3/20.622.C G09G3/20.623.C G09G3/20.623.D<br>G09G3/20.611.A G09G3/20.611.E                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 5C006/AA02 5C006/AA22 5C006/AC25 5C006/AC27 5C006/BB16 5C006/BB28 5C006/BC03 5C006/<br>/BC06 5C006/BC11 5C006/FA23 5C006/FA47 5C006/FA48 5C080/AA10 5C080/BB05 5C080/CC03<br>5C080/DD06 5C080/DD26 5C080/FF11 5C080/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06                                                                                                                                   |         |            |

| 代理人(译)         | 河野 哲                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 摘要(译)          | <p>解决的问题：提供一种能够实现低功耗的液晶显示装置及其驱动方法。可替代地，提供了一种具有优异的显示质量的液晶显示装置以及用于驱动该液晶显示装置的方法。液晶显示装置的驱动单元分别在第一像素电极和第一对电极之间施加第一电势差，并且在第二像素电极和第二对电极之间施加第二电势差。当保持时，首先，在写入时段中，将第一对向电压VcomH施加至第一对向电极，将第二对向电压VcomL施加至第二对向电极，并且将控制信号SG的电压值设置为第一电压值V1。要做。在特定写入时段期间，控制信号SG的电压值被临时设置为第二电压值V2，第一图像信号VsigtL被提供给第一信号线，并且第二图像信号VsigtH被提供给第二信号线。在保持期间中，第一对置电极维持在第一对置电压VcomH，第二对置电极维持在第二对置电压VcomL，控制信号SG的电压值被设定为第三电压。设置为值V3。[选择图]图7</p> |         |            |

| (21)出願番号       | 特願2014-196075 (P2014-196075)                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| (22)出願日        | 平成26年9月26日 (2014.9.26)                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| (71)出願人        | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号                                                                                                                                                                                                                                                                                                                                                         |         |            |

| (74)代理人        | 110001737<br>特許業務法人スズエ国際特許事務所                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| (74)代理人        | 100091351<br>弁理士 河野 哲                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| (74)代理人        | 100084618<br>弁理士 村松 貞男                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| (74)代理人        | 100087653<br>弁理士 鈴江 正二                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| (72)発明者        | 中村 卓<br>東京都港区西新橋三丁目7番1号 株式会<br>社ジャパンディスプレイ内                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 最終頁に続く         |                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |