(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-246250

(P2013-246250A)

(43) 公開日 平成25年12月9日(2013.12.9)

(51) Int.Cl.

G02F 1/1368 (2006.01)

F 1

G02F 1/1368

テーマコード(参考)

2H092

審査請求 未請求 請求項の数 5 O L (全 10 頁)

(21) 出願番号

特願2012-118839 (P2012-118839)

(22) 出願日

平成24年5月24日 (2012.5.24)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100113077

弁理士 高橋 省吾

(74) 代理人 100112210

弁理士 稲葉 忠彦

(74) 代理人 100108431

弁理士 村上 加奈子

(72) 発明者 横溝 政幸

熊本県合志市御代志997番地 メルコ・

ディスプレイ・テクノロジー株式会社内

F ターム(参考) 2H092 GA14 JA26 JA46 JB13 JB22

JB33 JB42 JB69 NA04 NA29

QA06

(54) 【発明の名称】 TFTアレイ基板およびそれを備える液晶パネル

## (57) 【要約】

**【課題】** 画素電極および共通電極以外の電界が液晶に影響を与えることを防止する構成を備える横電界方式の液晶表示装置であって、製造工程中での線欠陥不良の発生を防止できるとともに、製品の使用中に線欠陥が発生することを防止できるTFTアレイ基板を用いた横電界方式の液晶パネルを得ることを目的とする。

**【解決手段】** 本発明の横電界方式の液晶パネルに用いられるTFTアレイ基板100は、ソース配線2の上に、第2の共通電極7が上記第1の共通電極6とは別に設けられている。第2の共通電極7は、ソース配線2上に基板保護膜95を介し、ソース配線2に沿って、かつ、画素領域に対応して独立して設けられている。また、第2の共通電極7は、画素電極5の駆動に用いられる第1のTFT3とは別のTFTである。第1のTFT3を構成するゲート配線1上に設けられた第2のTFT10に接続される。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

基板上にマトリクス状に配置されるソース配線およびゲート配線、

前記ソース配線とゲート配線の交差部に形成される第1のTFT (Thin Film Transistor: 薄膜トランジスタ)、

前記第1のTFTに接続され、前記ソース配線と前記ゲート配線により囲まれる画素領域内に配置される画素電極、

前記画素電極と所定の間隔を保って配置され、前記画素電極とともに前記基板に対し平行な電界を印加する第1の共通電極、

前記ソース配線上に沿って形成される第2の共通電極、を備え、

前記第2の共通電極は、前記ゲート配線上に設けられた第2のTFTに接続されている、

TFTアレイ基板。

10

**【請求項 2】**

基板上にマトリクス状に配置されるソース配線およびゲート配線、

前記ソース配線とゲート配線の交差部に形成される第1のTFT (Thin Film Transistor: 薄膜トランジスタ)、

前記第1のTFTに接続され、前記ソース配線と前記ゲート配線により囲まれる画素領域内に配置される画素電極、

前記画素電極に対向する位置に絶縁膜を介して配置される第1の共通電極、

前記第1の共通電極は、前記画素電極とともに前記基板に対し平行な電界が印加されており、

前記ソース配線上に沿って形成される第2の共通電極、を備え、

前記第2の共通電極は、前記ゲート配線上に設けられた第2のTFTに接続されている、

TFTアレイ基板。

20

**【請求項 3】**

前記第2の共通電極は、前記画素領域毎に対応して独立して設けられていることを特徴とする請求項1または2記載のTFTアレイ基板。

**【請求項 4】**

前記第2の共通電極は、前記第1の共通電極と同層で形成されることを特徴とする請求項1乃至3のいずれか1項に記載のTFTアレイ基板。

30

**【請求項 5】**

請求項1乃至4のいずれか1項に記載のTFTアレイ基板と、

前記TFTアレイ基板と対向配置される対向基板と、

前記両基板間に配置される液晶と、を備え、

前記両基板と平行な方向に電界が印加されることで画像を表示する横電界方式の液晶パネル。

**【発明の詳細な説明】****【技術分野】****【0001】**

この発明は、横電界方式の液晶パネルに形成された液晶を駆動するスイッチング素子であるTFT (薄膜トランジスタ: Thin Film Transistor 以下、TFTと称する)アレイ基板および該TFTアレイ基板を用いた液晶パネルに関するものである。

40

**【背景技術】****【0002】**

横電界方式の液晶パネルを搭載した液晶表示装置は、従来のTN (Twisted Nematic) 方式の液晶表示装置と比較し視野角が広い特徴を有しており、TFTアレイ基板の構造からIPS (インプレーンスイッチング: In-Plane Switching 以下、IPSと称する) 方式やFFS (フリンジフィールドスイッチング: Fringe Field Switching 以下、FFSと称する) 方式の開発がな

50

されている。

【0003】

横電界方式の液晶表示装置のうち、たとえばIPS方式の液晶表示装置は、TFTアレイ基板の画素領域に櫛歯状に形成された画素電極および対向電極となる共通電極の間の液晶に電界が加わることで、液晶の配向を制御し、液晶パネルの透過率をコントロールしている。

【0004】

したがって、TFTアレイ基板の構造として、画素電極と共に電極以外の電界が、液晶に影響を与えない構造が提案されている。

【0005】

特許文献1に開示された液晶表示装置は、ドレイン信号線DLの形成領域上においてドレイン信号線DLよりも幅広の第1の導電層CND1が形成され、ドレイン信号線DLを覆う構成が開示されている。これにより、電界による光漏れを遮光する構成となっている。

【先行技術文献】

【特許文献】

【0006】

特開2002-131767号公報（第7ページ、第3図）

【発明の概要】

【発明が解決しようとする課題】

【0007】

特許文献1に開示された横電界方式のTFTアレイ基板は、第1の導電層CND1でドレイン信号線DLを覆う構成となっているため、TFTアレイ製造工程で発生した異物等が、ドレイン信号線DLと第1の導電層CND1の間に混入すると、ドレイン信号線DLと第1の導電層CND1間の絶縁膜に欠損が生じ、両電極間の絶縁が保たれず、ドレイン信号線DLと第1の導電層CND1がショートするということがあった。

【0008】

すなわち、ドレイン信号線DL形成後に配線上に異物等が付着した場合に、その後形成する絶縁膜に異物の存在により、ドレイン信号線DL上を十分覆うことができず、絶縁膜が形成されない部分が発生する。その上に第1の導電層CND1が形成されると、異物部分では絶縁膜が形成されない部分が発生しているので、各ドレイン信号線DL配線が露出され、ドレイン信号線DLと第1の導電層CND1が直接接触する部分が発生してしまう。その結果、ドレイン信号線DLと第1の導電層CND1間のショートを引き起こすこととなる。

【0009】

ドレイン信号線DLと第1の導電層CND1がショートした場合、ドレイン信号線DLの電位は、ほぼ第1の導電層CND1の電位となり、正常なドレイン信号を供給できなくなる。その結果、ドレイン信号線DLに沿った画素が全て表示しなくなる。特にIPS方式の場合は信号OFFで黒くなるノーマリーブラックモードとなっているので、ドレイン信号線DLに沿って黒い線欠陥として視認されてしまう。

【0010】

配線のオープン不良欠陥の場合は、電気的な検査や点灯表示検査によって、欠陥位置を特定することが可能なため、リペア配線と呼ばれる冗長配線を用いて、レーザーリペア等により配線の修正を行い、歩留を向上させることができあるが、上記のようにショートした場合は電気的にも、表示状態でも欠陥位置を検出することが難しいため、その液晶パネルは廃却処置となり、歩留の低下を招いていた。

【0011】

さらに、ショート欠陥が微小なリーケの場合は、製造時に検出できず、出荷後に、通電することでリーケ量が徐々に大きくなり、線欠陥不良が製品の使用中に発生し、品質問題を発生させるという、不具合があった。

10

20

30

40

50

## 【0012】

この発明は画素電極および共通電極以外の電界が液晶に影響を与えることを防止する構成を備える横電界方式の液晶表示装置であって、上記のような問題点を解消するためになされたものであり、製造工程中での線欠陥不良の発生を防止できるとともに、製品の使用中に線欠陥が発生することを防止できるTFTアレイ基板を用いた横電界方式の液晶パネルを得ることを目的とする。

## 【課題を解決するための手段】

## 【0013】

本発明におけるTFTアレイ基板および液晶パネルは、基板上にマトリクス状に配置されるソース配線およびゲート配線、ソース配線とゲート配線の交差部に形成される第1のTFT (Thin Film Transistor: 薄膜トランジスタ)、第1のTFTに接続され、ソース配線とゲート配線により囲まれる画素領域内に配置される画素電極、画素電極と所定の間隔を保って配置され、画素電極とともに基板に対し平行な電界を印加する第1の共通電極、ソース配線上に沿って形成される第2の共通電極をさらに備え、第2の共通電極は、ゲート配線上を延在し、ゲート配線上に設けられた第2のTFTに接続されていることを特徴とする。

10

## 【発明の効果】

## 【0014】

本発明の横電界方式のTFTアレイ基板を用いた液晶パネルによれば、画素電極および共通電極以外の電界が液晶に影響を与えることを防止する構成を備えるとともに、製造工程中での線欠陥不良の発生を防止できるとともに、製品の使用中に線欠陥が発生することを低減できる。

20

## 【図面の簡単な説明】

## 【0015】

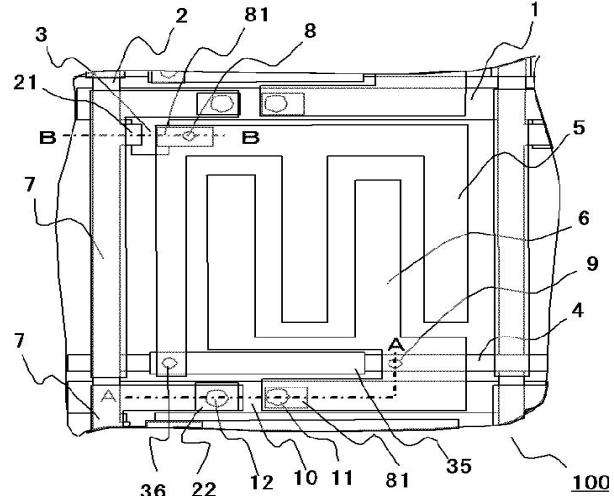

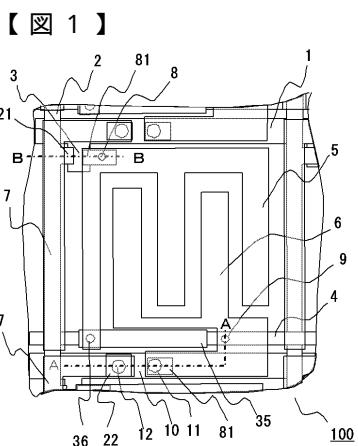

【図1】本発明の液晶パネルを構成するTFTアレイ基板上の1画素の構成を示す平面図である。

30

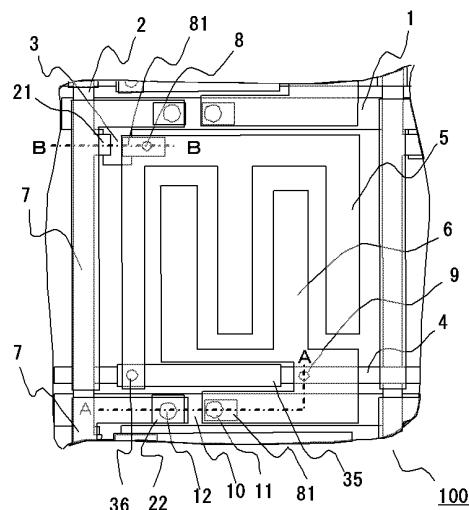

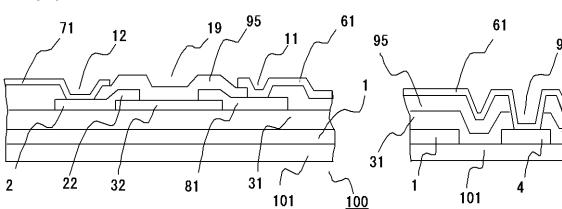

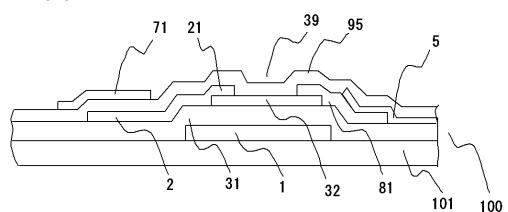

【図2】図1のA-A断面図である。

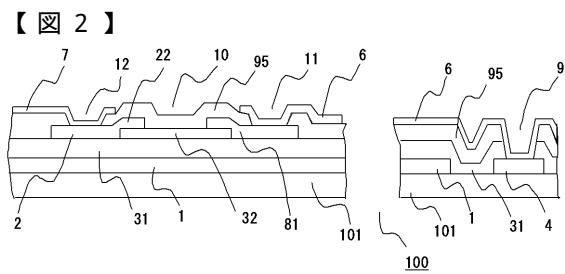

【図3】図1のB-B断面図である。

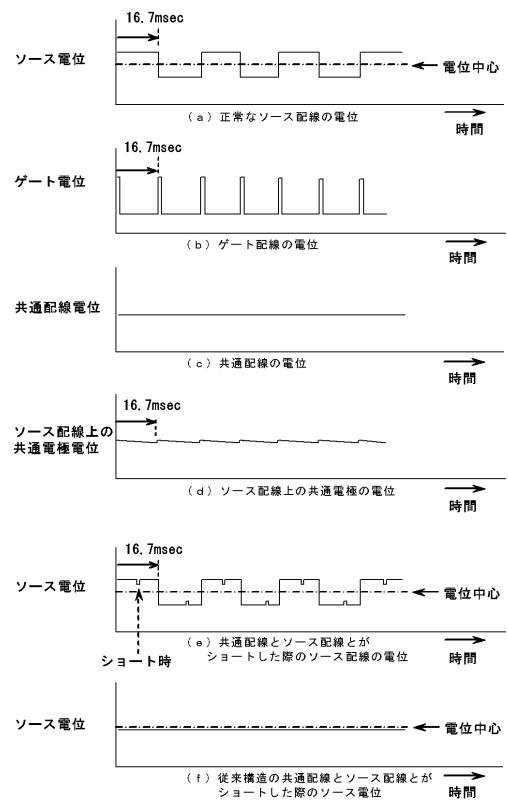

【図4】本発明における液晶パネルの電位を示す図である。

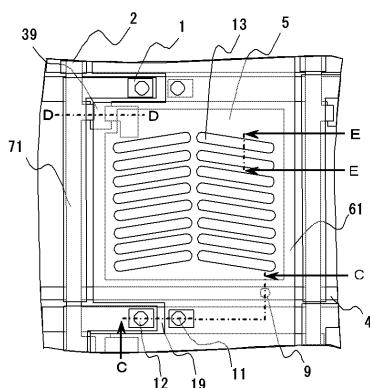

【図5】本発明の液晶パネルを構成するTFTアレイ基板上の1画素の構成を示す平面図である。

40

【図6】図5のC-C断面図である。

【図7】図5のD-D断面図である。

【図8】図5のE-E断面図である。

## 【発明を実施するための形態】

## 【0016】

実施の形態1.

以下、本発明に係るTFTアレイ基板および液晶パネルの実施形態を図面に基づいて説明する。各図において同一の符号を付されたものは、実質的に同様の構成要素を示す。

## 【0017】

図1は、本発明の液晶パネルを構成するTFTアレイ基板上の画素領域である1画素の構成を示す平面図、図2は図1のA-A断面図、図3はB-B断面図である。

## 【0018】

図1乃至図3に示すように、本発明のIPS方式の液晶パネルを構成するTFTアレイ基板100は、ガラス等の絶縁性基板101上に形成されたゲート配線1、ゲート配線1とともに形成された共通配線4、ゲート配線1および共通配線4とマトリクス状に交差するようゲート絶縁膜31を介して形成されたソース配線2を備えている。また、ゲート配線1とソース配線2の交点には、液晶パネルのスイッチング素子である第1のTFT3が形成されている。第1のTFT3は、ゲート配線1の上に形成されたゲート絶縁膜31、a-Si等の半導体層32、半導体層32上であって、ソース配線2より延在したソース

50

電極 21 およびドレイン電極 81 で構成され、基板保護膜 95 が積層されている。基板保護膜 95 上の画素領域には、画素電極 5 および第 1 の共通電極 6 が形成されている。

#### 【0019】

画素電極 5 はドレイン 81 上の基板保護膜 95 に形成されたコンタクトホール 8 を介して、第 1 の TFT3 に接続されている。また、第 1 の共通電極 6 は共通配線 4 上のゲート絶縁膜 31、基板保護膜 95 に形成されたコンタクトホール 9 を介して共通配線 4 に接続されている。画素電極 5 および第 1 の共通電極 6 は数  $\mu\text{m}$  幅の電極であり、1 画素の画素領域内に数  $\mu\text{m}$  ~ 数十  $\mu\text{m}$  間隔で互いに平行であって、対向する櫛歯状となるよう同層に配置されている。また、共通配線 4 の上には電圧を保持する保持容量電極が、ゲート絶縁膜 31 を介して形成され、保持容量電極 35 上に設けられたコンタクトホール 36 を介して画素電極 5 と接続されている。

#### 【0020】

このように形成された TFT アレイ基板 100 は、カラーフィルタやブラックマトリックスを形成した対向基板（図示せず）と所定の間隔で貼りあわせ、両基板の間に液晶を封入、表面にそれぞれ偏光板（図示せず）を貼付けることで、液晶パネルが完成する。さらに、この液晶パネルに駆動 IC（図示せず）や、バックライト（図示せず）等を実装することで液晶表示装置が完成する。

#### 【0021】

本発明の横電界方式の液晶パネルは、画素電極 5 と第 1 の共通電極 6 が櫛歯状に形成され、対向配置されているため、画素電極 5 と第 1 の共通電極 6 との間に配置する液晶（図示せず）に電界が加わる。よって、画素領域全域に絶縁性基板 101 と平行となる方向に電界が発生させ、液晶の配向を制御し、液晶パネルの透過率をコントロールしている。また、共通配線 4 上に形成された保持容量電極 35 により、画素電極 5 に印加された電圧を保持している。

#### 【0022】

また、図 1、図 3 に示すように、本発明の TFT アレイ基板 100 においては、ソース配線 2 の上に、第 2 の共通電極 7 が上記第 1 の共通電極 6 とは別に設けられている。第 2 の共通電極 7 は、ソース配線 2 上に基板保護膜 95 を介し、ソース配線 2 に沿って、かつ、画素領域に対応して独立して設けられている。また、第 2 の共通電極 7 は、画素電極 5 の駆動に用いられる第 1 の TFT3 とは別の TFT であって、第 1 の TFT3 を構成するゲート配線 1 上に設けられた第 2 の TFT10 に接続される。第 2 の TFT10 は、ゲート配線 1 上にゲート絶縁膜 31、半導体層 32 を介し、ソース配線 2 と同層で形成されるソース電極 22、ドレイン電極 81 より構成されている。また、第 2 の共通電極 7 と第 2 の TFT10 は、第 2 の TFT10 上の基板保護膜 95 に設けられたコンタクトホール 12 で接続されている。また、第 2 の TFT10 は、前段に形成される第 1 の共通電極 6 と第 2 の TFT10 上の基板保護膜 95 に設けられたコンタクトホール 11 を介して接続されている。

#### 【0023】

次に、図 1 乃至図 3 を用いて、液晶パネルを構成する TFT アレイ基板 100 の製造方法について説明する。

#### 【0024】

TFT アレイ基板 100 はガラス等の絶縁性基板 101 上に、Cr や Al 等の金属を成膜し、パターニングすることで、ゲート配線 1 および共通配線 4 を形成する。次に、絶縁膜である SiN 等や、半導体である a-Si (i, n 層) 等を順次成膜し、a-Si (i, n 層) 等を第 1 の TFT3 および第 2 の TFT10 が形成される領域に、島状にパターニングすることで、ゲート絶縁膜 31 および半導体層 32 を形成する。

#### 【0025】

次いで、Cr や Al 等の金属を成膜し、パターニングすることで、ソース配線 2、ソース電極 21、ドレイン電極 81、ソース電極 22、保持容量電極 35 を形成する。その後、第 1 の TFT3 および第 2 の TFT10 の位置に形成した島状の半導体層 32 において

10

20

30

40

50

、ソース2、ドレイン電極81で覆われていない半導体層32の表面を前記ソース配線2(ソース電極21)、ドレイン電極81のパターンをマスクとし、表面の導電率が高いn層をエッチングすることで、TFT(薄膜トランジスタ)のチャネル領域が形成され、第1のTFT3、第2のTFT10が同時に完成する。

#### 【0026】

その後、SiN等を成膜、パターニングし、基板保護膜95を形成する。次に、基板保護膜95に、第1のTFT3のドレイン電極81上のコンタクトホール8、共通配線4上のコンタクトホール9、第2のTFT10と第1の共通電極6とを接続するコンタクトホール11、第2のTFT10と第2の共通電極7とを接続するコンタクトホール12、保持容量電極35に形成されたコンタクトホール36を形成する。

10

#### 【0027】

その後、ITO等の透明電極を成膜、パターニングすることで、画素電極5および、画素内の第1の共通電極6、ソース配線2上の第2の共通電極7が形成される。

#### 【0028】

画素電極5は、コンタクトホール8で第1のTFT3のドレイン電極81、コンタクトホール36で保持容量電極35とそれぞれ接続される。また、第1の共通電極6は、コンタクトホール9で共通配線4、コンタクトホール11で第2のTFT10とそれぞれ接続される。第2の共通電極7は、コンタクトホール12で第2のTFT10と接続される。

#### 【0029】

このように、第2の共通電極7および第2の共通電極7と接続させる第2のTFT10は、新たな工程を追加することなく形成することが可能であり、コストを上昇させることがない。

20

#### 【0030】

本発明におけるTFTアレイ基板100を用いた液晶パネルは、ゲート配線1、共通配線4およびソース配線2に電圧が印加されると、第1のTFT3を介して画素電極5に電圧が印加される。また、第2のTFT10を介して共通電極6に電圧が印加される。画素電極5および共通電極との間の電界が液晶に加わることで、液晶の配向が制御され、液晶パネルに画像が表示される。

#### 【0031】

次に本発明における、TFTアレイ基板100を用いた液晶パネルにおける動作を説明する。

30

#### 【0032】

図4は液晶パネルに印加される電位を示す図であり、図4(a)は正常に動作している場合の任意のソース配線2に印加される電位を示す図、図4(b)は任意のゲート配線1に印加される電位を示す図、図4(c)は共通配線4に印加される電位を示す図である。また、図4(d)は任意の第2の共通電極7(ソース配線2上の共通電極)の電位を示す図、図4(e)は任意の第2の共通電極7(ソース配線2上の共通電極)とソース配線2とがショートした場合のソース配線2に印加される電位を示す図、図4(f)は従来の液晶パネルにおいて、共通電極とソース配線がショートした場合のソース配線の電位を示す図である。ここで、図4(a)～図4(f)の電位中心電圧は、図4(c)に示す、共通配線4の電位とほぼ等しい電圧に設定されている。

40

#### 【0033】

まず、ソース配線2より画素電極5に印加されるソース電圧の印加方法を説明する。正常な状態でのソース配線2は、図4(a)に示す電圧波形のソース電圧が印加されている。ゲート配線1には図4(b)に示す電圧波形のゲート電圧が印加されている。ゲート配線1は、一般的に1フレームを60Hzの周期で駆動する場合は16.7msに1回電位が印加され、ゲート電位が高くなる。また、ソース電圧は、1フレーム間(16.7ms)にゲート配線1の本数分の電圧が印加されており、ゲート電圧が高くなるタイミングで、任意のソース電圧が選択される。また、液晶の劣化を避けるため、ソース電圧は、電位中心(共通配線4の電位)を中心として1フレーム毎に交流電圧が選択される。

50

## 【0034】

ソース電圧の選択動作としては、ゲート電圧が高くなると、第1のTFT3の半導体層32にa-Siを用いた場合、チャネル抵抗（図示せず）が $10^6$ オーダーの低い抵抗値となり、ソース配線2の電圧がソース配線2から画素電極5へ供給され、保持容量電極35および画素電極5と、第1の共通電極6間の容量へ保持される。ゲート電圧が低くなると、第1のTFT3が $10^{12}$ 程度の高抵抗となるので、画素電極5に印加された電位は保持容量電極35および画素電極5と第1の共通電極6間の容量へ保持された状態を保つ。

## 【0035】

次に、第2の共通電極7への電位の印加方法について説明する。上述した画素電極5への電圧印加動作と同様、図4(b)に示すゲート配線1のゲート電圧が高くなるタイミングで、図4(d)に示す第2の共通電極7の電位は、第2のTFT10のチャネル抵抗が $10^6$ 程度の低い抵抗値となり、第2のTFT10を介して第2の共通電極7へ供給され、電位が印加される。その後、ゲート配線1のゲート電位が低くなると、第2のTFT10のチャネル抵抗が $10^{12}$ 程度と極めて高い抵抗値となるため、第2の共通電極7に印加された、共通電極電位は、図4(d)に示すように、ゲート電圧が高くなるまでの期間、保持されることとなる。この動作が液晶パネルを駆動中、継続して繰り返される。

10

## 【0036】

結果、第2の共通電極7の電位は図4(c)に示す波形となり、図4(d)に示す、共通配線4の電位とほぼ同じ電位を保つ。このような構成であるため、ソース配線2の電界の影響が画素領域内の液晶におよぶことがない、よって、画素領域内の液晶の配向が制御できるため、ソース配線2の端部の電界の乱れにより発生していた光漏れを防止することができる。

20

## 【0037】

次に、ソース配線2と第2の共通電極7がショートした場合の動作を従来構造の液晶パネルと比較しながら、説明する。

## 【0038】

図4(f)に示すとおり、従来の液晶パネルの構造で共通電極4とソース配線2がショートした場合のソース配線2の電位であるソース電位は、共通配線4の電位とほぼ同じ電位となってしまい、ソース配線2に接続された画素電極5には全て共通配線4の電圧が印加される。共通配線4の電位は、ソース電圧の電位中心とほぼ同じ電位のため、ソース配線2に接続された画素電極5は共通配線4と同じ電位となり、画素電極5の液晶に電圧が印加されなくなる。したがって、ノーマリーブラックモードの場合はソース配線2に沿った画素が全て黒点となるので、ソース配線2が形成される方向に沿った黒線として視認される。

30

## 【0039】

次に、本発明の液晶パネルの構造で、ソース配線2上の基板保護膜95に異物等による絶縁不良が発生した場合の動作を説明する。前述のとおり、第2の共通電極7への電圧の供給は第2のTFT10を介して行われるので、第2のTFT10がONして第1の共通電極6と $10^6$ 程度の低抵抗で接続されている時間は、例えば、ゲート配線の本数が480本でフレーム周波数60Hzの場合、 $60\text{Hz} (16.7\text{msec}) / 480\text{本} = 34.7\mu\text{sec}$ ときわめて短い時間となる。図4(d)に示すとおり、ソース配線2と第2の共通電極7がショートした場合、上記のきわめて短い時間しか、ソース配線2と共通電極6間が低抵抗でショートしないので、ほとんどの期間はソース配線2へのソース駆動IC（図示せず）からの出力は正常な電圧を維持するようになり、その結果、ソース配線2が共通配線4の電位の影響を受けにくくなる。したがって、ソース配線2の電位は正常な状態（図4(a)）からほぼ変化しないので、ソース配線2に接続された画素電極5へ印加される電位はショートが無い場合とほぼ変わらない電位が印加される。したがって、ソース配線2が第2の共通電極7とショートしていても、線欠陥の発生を防止することができる。

40

50

## 【0040】

上記説明したとおり、本発明のTFTアレイ基板100を用いた液晶パネルによれば、画素領域内に形成した第1の共通電極6とは独立してソース配線2上に第2の共通電極7を形成したので、画素電極および共通電極以外の電界が液晶に影響を与えることを防止できる。また、第2の共通電極7は、画素電極5を駆動する第1のTFT3とは別の第2のTFT10により駆動させるので、ソース配線2と第2の共通電極7とのショートに起因するソース配線2の線欠陥が低減される。よって、液晶表示装置の歩留が向上する。

## 【0041】

また、上述の通り、ソース配線2と第2の共通電極7のショートに起因した線欠陥が大幅に低減されるため、製品を出荷した後にソース配線2と第2共通電極7のショートに起因する線欠陥が発生することも低減することとなり、液晶表示装置の信頼性が向上する。

10

## 【0042】

実施の形態2.

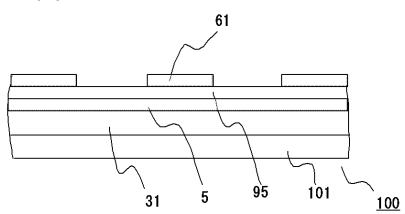

図5は本発明の実施の形態2におけるTFTアレイ基板の部分平面図、図6は図5のC-Cの断面図、図7は図5のD-Dの断面図、図8は図5のE-Eの断面図を示す。

## 【0043】

実施の形態1においては、IPS方式の液晶パネルを構成するTFTアレイ基板の構造について説明したが、本実施の形態2においては、FFS方式の液晶パネルを構成するTFTアレイ基板に本発明を適用する例を説明する。その他、実施の形態1と同様の構成および効果を奏するものは、説明を省略する。

20

## 【0044】

実施の形態1で説明したIPS方式のTFTアレイ基板は、画素電極5と第1の共通電極6が同層に構成されているが、図5乃至図8に示すように、本実施の形態2におけるFFS方式では、画素電極5は第1の共通電極61の下層に絶縁膜である基板保護膜95を介して形成されている。共通電極61には開口部13が形成されている。また、図7に示すように第1のTFT39は、ドレイン電極81の形成後に画素電極5を形成しており、コンタクトホールを介すことなく、ドレイン電極81と画素電極5が直接接続されている。

20

## 【0045】

図6に示すように、共通配線4と接続された共通電極61が第2のTFT19を介して、第2の共通電極71へ接続される構造においては、実施の形態1で説明したTFTアレイ基板と同一の構造となる。したがって、本実施の形態2に示すFFS方式においても第2の共通電極71をソース配線2に沿って独立して形成させ、第2のTFT19を介して、共通配線4と接続させる構成であるため、ソース配線2からの電界の影響を防止する構成であって、ソース2配線2上に形成した第2の共通電極71とソース配線2が異物等でショートした場合でも、線欠陥を引き起こすことが大幅に低減される。よって、実施の形態1の液晶パネルと同様、FFS方式の液晶パネルにおいても、上記実施の形態1と同様の効果を奏する。

30

## 【符号の説明】

## 【0046】

40

- 1 ゲート配線

- 2 ソース配線

- 21、22 ソース電極

- 3、39 第1のTFT

- 31 ゲート絶縁膜

- 32 半導体層

- 35 保持容量電極

- 4 共通配線

- 5 画素電極

- 6、61 第1の共通電極

50

7、71 第2の共通電極

8、9、11、12、36 コンタクトホール

81 ドレイン電極

95 基板保護膜

10、19 第2のTFT

100 TFTアレイ基板

101 絶縁性基板。

【図4】

【図5】

【図6】

【図7】

【図8】

|                |                                                                                                                                                                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | TFT阵列基板和具有该TFT阵列基板的液晶面板                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2013246250A</a>                                                                                                                                                                                               | 公开(公告)日 | 2013-12-09 |

| 申请号            | JP2012118839                                                                                                                                                                                                                | 申请日     | 2012-05-24 |

| [标]申请(专利权)人(译) | 三菱电机株式会社                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 三菱电机株式会社                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 横溝政幸                                                                                                                                                                                                                        |         |            |

| 发明人            | 横溝 政幸                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G02F1/1368                                                                                                                                                                                                                  |         |            |

| FI分类号          | G02F1/1368                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/JA26 2H092/JA46 2H092/JB13 2H092/JB22 2H092/JB33 2H092/JB42 2H092/JB69 2H092/NA04 2H092/NA29 2H092/QA06 2H192/AA24 2H192/BB03 2H192/BB12 2H192/BB53 2H192/BB91 2H192/BC31 2H192/CB05 2H192/DA32 2H192/GA03 |         |            |

| 代理人(译)         | 高桥省吾<br>稻叶忠彦<br>村上佳菜子                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                   |         |            |

## 摘要(译)

具有用于防止像素电极和公共电极之外的电场影响液晶的配置的面内切换模式液晶显示装置可以防止在制造过程中出现缺陷线缺陷，本发明的一个目的是获得一种使用TFT阵列基板的横向电场型液晶面板，其可以防止在产品使用期间发生线缺陷。用于本发明的横向电场型液晶面板的TFT阵列基板在与第一公共电极6分开的源极配线2上设置有第二公共电极。。第二公共电极7经由基板保护膜95设置在源极线2上，并且沿着源极线2独立地设置并且对应于像素区域。此外，第二公共电极7是与用于驱动像素电极5的第一TFT 3不同的TFT，第二公共电极7是设置在构成第一TFT 3的栅极布线1上的第二TFT 10。它是连接到。点域1