(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-221295

(P2011-221295A)

(43) 公開日 平成23年11月4日(2011.11.4)

(51) Int.Cl.

G02F 1/1368 (2006.01)

F 1

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

審査請求 未請求 請求項の数 9 O L (全 19 頁)

(21) 出願番号

特願2010-90516 (P2010-90516)

(22) 出願日

平成22年4月9日 (2010.4.9)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100117606

弁理士 安部 誠

(74) 代理人 100115510

弁理士 手島 勝

(74) 代理人 100121186

弁理士 山根 広昭

(74) 代理人 100136423

弁理士 大井 道子

(72) 発明者 大上 亮

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】 液晶パネル用アレイ基板と該基板を備える液晶表示装置

## (57) 【要約】

【課題】液晶が封入される一対の基板間での短絡の虞を低減させ得る構造の液晶パネルと、そのようなパネルの構築に好適な液晶パネル用アレイ基板を提供すること。

【解決手段】本発明により提供される液晶パネル用アレイ基板において、薄膜トランジスタ30は、少なくともゲート電極32とソース電極36とドレイン電極37とを備えた積層構造に形成されている。そして、基板本体(ガラス基板)12aは、少なくとも薄膜トランジスタ形成部分の一部において、該薄膜トランジスタ形成部分の周囲よりも凹んだ凹部96, 97を備えており、ソース電極およびドレイン電極は、凹部内に少なくともその一部が埋設されるようにして形成されている。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

基板本体と、複数のゲート線と、該ゲート線に交差する複数のソース線と、いずれかのゲート線及びソース線と電気的に接続する複数の薄膜トランジスタと、を備える液晶パネル用のアレイ基板であって、

前記薄膜トランジスタは、少なくともゲート電極とソース電極とドレイン電極とを備えた積層構造に形成されており、

前記基板本体は、少なくとも前記薄膜トランジスタ形成部分の一部において、該薄膜トランジスタ形成部分の周囲よりも凹んだ凹部を備えており、

前記ソース電極および前記ドレイン電極は、前記凹部内に少なくともその一部が埋設されるようにして形成されていることを特徴とする液晶パネル用アレイ基板。 10

**【請求項 2】**

前記薄膜トランジスタは、前記基板本体上に形成されるソース電極およびドレイン電極と、該ソース電極および該ドレイン電極よりも基板上方であって該ソース電極から該ドレイン電極に連続的に形成される半導体膜と、該半導体膜よりも基板上方に形成される絶縁膜と、該絶縁膜よりも基板上方に形成されるゲート電極と、を含む積層構造をしていることを特徴とする請求項 1 に記載の液晶パネル用アレイ基板。

**【請求項 3】**

前記アレイ基板は、マトリクス状に設けられた複数の画素電極をさらに備えており、

前記基板本体における前記ドレイン電極と前記画素電極とが重なっている部位は、該重なり部位に隣接する部位よりも凹んだ凹部となるように形成されており、 20

前記ドレイン電極は、前記凹部内に少なくともその一部が埋設されるようにして形成されており、

ここで、前記画素電極の一部は、前記ドレイン電極と前記凹部上で接触していることを特徴とする請求項 1 または 2 に記載の液晶パネル用アレイ基板。

**【請求項 4】**

前記ドレイン電極は、前記基板本体上に形成される A1 から成る金属膜層と、該金属膜層の上方に形成される Ti から成る金属膜層と、を含む積層構造をしていることを特徴とする請求項 3 に記載の液晶パネル用アレイ基板。 30

**【請求項 5】**

前記基板本体における少なくとも該基板本体上に配線されている前記ゲート線と前記ソース線とが交差する部位は、該交差部位に隣接する非交差部位よりも凹んだ凹部となるように形成されており、

前記ソース線の少なくとも一部は、前記凹部内に埋設されるようにして形成されて、該凹部上で前記ソース線と前記ゲート線とが交差するように配線されていることを特徴とする請求項 1 から 4 のいずれかに記載の液晶パネル用アレイ基板。 40

**【請求項 6】**

前記アレイ基板は、前記ソース線と交差する複数の補助容量線をさらに備えており、

前記基板本体における少なくとも該基板本体上に配線されている前記補助容量線と前記ソース線とが交差する部位は、該交差部位に隣接する非交差部位よりも凹んだ凹部となるように形成されており、

前記ソース線の少なくとも一部は、前記凹部内に埋設されるようにして形成されて、該凹部上で前記ソース線と前記補助容量線とが交差するように配線されていることを特徴とする請求項 1 から 5 のいずれかに記載の液晶パネル用アレイ基板。

**【請求項 7】**

前記凹部は、前記基板本体上に配線されている前記ソース線の下方に、該ソース線に沿って連続的に形成されていることを特徴とする請求項 6 に記載の液晶パネル用アレイ基板。

**【請求項 8】**

請求項 1 から 7 のいずれかに記載の液晶パネル用アレイ基板を備える液晶パネル。 50

**【請求項 9】**

請求項 8 に記載の液晶パネルを備える液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置及び該表示装置に装備される液晶表示パネルを構築するのに用いられる液晶パネル用アレイ基板に関する。 10

**【0002】**

テレビ、パソコン等の画像表示装置（ディスプレイ）として、液晶パネルを備えた液晶表示装置が広く用いられている。

液晶パネルは、一対の基板（即ちアレイ基板及び該アレイ基板に対向するように配置される対向基板）と、該一対の基板間に挟持された液晶層とを備えており、アレイ基板と対向基板との間に画素毎に選択的に電圧を印加することで液晶層中の液晶分子が制御されて画像の表示が行われる。ここで、例えば、アクティブマトリクス型の液晶表示パネルでは、アレイ基板に、複数のゲート線（走査線配線）とソース線（信号線配線）とが互いに直交して形成されており、ゲート線とソース線との各交点にスイッチング素子としての薄膜トランジスタ（TFT）を備える画素が形成されている。この種の先行技術に関する技術文献として、特許文献1が挙げられる。特許文献1には、TFT形成領域において層間絶縁膜に凹部を設けて平坦にし得る技術が記載されている。 20

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】特開平11-218781号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

ところで、液晶パネルの組立工程の際に、アレイ基板と対向基板（カラーフィルタ基板）との間の液晶層に異物が混入する場合がある。このとき、アレイ基板に形成されたゲート線とソース線とが直交して交差する部位や、アレイ基板上のTFTが形成された部位等は、アレイ基板に対向して配置されるカラーフィルタ基板との間隔が狭くなるため（距離が小さくなる）、該部位に異物が混入すると短絡（リーク）が発生する虞が高くなる。このような不良が発生すると、両基板間に正常な電圧が印加されなくなり、液晶表示装置において画素表示不良（点欠陥、線欠陥）となって現れ、製造歩留まりの低下の要因となる。特にTFTが形成された部位は、複数の材料から構成される積層構造であるため、TFTが形成されていない部位と比べてカラーフィルタ基板との間隔が狭くなる傾向にある。基板間の間隔を広げる（例えば、スペーサ部材の厚さを大きくする。）と、液晶パネルの厚みが増してしまい液晶パネルの薄型化という要求にこたえることができないだけでなく、応答時間やコントラスト比が低下する虞がある。また、配線の厚みを薄くすることによって十分な間隔を確保しようとすると、配線抵抗が大きくなり信号遅延が発生する虞が高まる。なお、上記特許文献1に記載の技術は、上記問題点を解決するものではない。 30

**【0005】**

そこで、本発明は、上述した課題を解決すべく創出された発明であり、その目的は、配線抵抗を増加させることなく、基板間に異物が混入した際に短絡の虞を低減させうる構造の液晶パネル用アレイ基板を提供することである。また、他の目的は、上記液晶パネル用アレイ基板を備える液晶パネルおよび該液晶パネルを備える液晶表示装置を提供することである。 40

**【課題を解決するための手段】****【0006】**

10

20

30

40

50

上記目的を実現するべく、本発明により、基板本体と、複数のゲート線と、該ゲート線に交差する複数のソース線と、いずれかのゲート線及びソース線と電気的に接続する複数の薄膜トランジスタと、を備える液晶パネル用のアレイ基板が提供される。ここで開示される液晶パネル用のアレイ基板において、上記薄膜トランジスタは、少なくともゲート電極とソース電極とドレイン電極とを備えた積層構造に形成されている。そして、上記基板本体は、少なくとも上記薄膜トランジスタ形成部分の一部において、該薄膜トランジスタ形成部分の周囲よりも凹んだ凹部を備えている。ここで、上記ソース電極および上記ドレイン電極は、上記凹部内に少なくともその一部が埋設されるようにして形成されている。

#### 【0007】

本発明によって提供される液晶パネル用のアレイ基板では、基板本体（典型的にはガラス基板）における薄膜トランジスタ（TFT）形成部分に凹部が形成されているため、薄膜トランジスタを形成する際にソース電極およびドレイン電極をその電極の少なくとも一部が該凹部内に埋設するようにして形成することができる。これにより、凹部内に埋設された電極（ソース電極およびドレイン電極）の厚さ分だけ TFT 形成部位の厚みが薄くなり、アレイ基板の TFT 形成部位（典型的にはゲート電極）とカラーフィルタ基板との間隔が大きくなるため、該部位に異物が混入することに起因する上記基板間の短絡発生の虞を低減することができる。また、本発明に係る液晶パネル用のアレイ基板では、上述のように基板本体に凹部を形成しており、上記電極（配線）の厚みを薄くしていないため配線抵抗を増大させることなく TFT 形成部位における上記基板間の間隔を大きくすることができる。

従って、かかる液晶パネル用のアレイ基板によると、配線抵抗を増大させることなく、基板間に異物が混入した場合であっても基板間での短絡の虞を低減することができる。

#### 【0008】

ここで開示される液晶パネル用アレイ基板の好適な一態様では、上記薄膜トランジスタは、上記基板本体上に形成されるソース電極およびドレイン電極と、該ソース電極および該ドレイン電極よりも基板上方であって該ソース電極から該ドレイン電極に連続的に形成される半導体膜と、該半導体膜よりも基板上方に形成される絶縁膜と、該絶縁膜よりも基板上方に形成されるゲート電極と、を含む積層構造をしている。かかる積層構造の薄膜トランジスタによると本発明は、よりいっそうの効果を奏することができる。

#### 【0009】

ここで開示される液晶パネル用アレイ基板の好適な一態様では、上記アレイ基板は、マトリクス状に設けられた複数の画素電極をさらに備えており、上記基板本体における上記ドレイン電極と上記画素電極とが重なっている部位は、該重なり部位に隣接する部位よりも凹んだ凹部となるように形成されている。上記ドレイン電極は、上記凹部内に少なくともその一部が埋設するようにして形成されている。ここで、上記画素電極の一部は、上記ドレイン電極と上記凹部上で接触している。特に、上記ドレイン電極は、上記基板本体上に形成される Al から成る金属膜層と、該金属膜層の上方に形成される Ti から成る金属膜層と、を含む積層構造をしていることが好ましい。

かかる構成の液晶パネル用アレイ基板では、ドレイン電極の Ti から成る金属膜層と画素電極とを直接接觸させて電気的に接続することができるため、ドレイン電極にエッティング処理を施す必要がなく構造がより簡易となる。

#### 【0010】

ここで開示される液晶パネル用アレイ基板の好適な一態様では、上記基板本体における少なくとも該基板本体上に配線されている上記ゲート線と上記ソース線とが交差する部位は、該交差部位に隣接する非交差部位よりも凹んだ凹部となるように形成されている。そして、上記ソース線の少なくとも一部は、上記凹部内に埋設されるようにして形成されて、該凹部上で上記ソース線と上記ゲート線とが交差するように配線されている。

かかる構成の液晶パネル用アレイ基板では、基板本体においてゲート線とソース線とが交差する部位が凹むように形成されており、ソース線の少なくとも一部はかかる凹部内に埋設されるように形成されて、当該凹部上でゲート線とソース線とが交差するように形成

10

20

30

40

50

されている。このため、凹部を有しない場合と比べて、凹部内に埋設されているソース線の厚さ（高さ）だけ該交差部位の厚さが薄くなる。このようなアレイ基板を用いて液晶パネルを構築すると、上記交差部位とカラーフィルタ基板との間隔が大きくなるため、該部位に異物が混入することに起因する上記基板間の短絡発生の虞を低減することができる。

#### 【0011】

ここで開示される液晶パネル用アレイ基板の好適な一態様では、上記アレイ基板は、上記ソース線と交差する複数の補助容量線をさらに備えており、上記基板本体における少なくとも該基板本体上に配線されている上記補助容量線と上記ソース線とが交差する部位は、該交差部位に隣接する非交差部位よりも凹んだ凹部となるように形成されており、上記ソース線の少なくとも一部は、上記凹部内に埋設されるようにして形成されて、該凹部上で上記ソース線と上記補助容量線とが交差するように配線されている。10

かかる構成の液晶パネル用アレイ基板では、基板本体における補助容量線とソース線とが交差する部位が凹むように形成されており、ソース線の少なくとも一部はかかる凹部内に埋設されるように形成されて、当該凹部上で補助容量線とソース線とが交差するように形成されている。このため、凹部を有しない場合と比べて、凹部内に埋設されているソース線の厚さ（高さ）だけ該交差部位の厚さが薄くなる。このようなアレイ基板を用いて液晶パネルを構築すると、上記交差部位とカラーフィルタ基板との間隔が大きくなるため、該部位に異物が混入することに起因する上記基板間の短絡発生の虞を低減することができる。

#### 【0012】

ここで開示される液晶パネル用アレイ基板の好適な一態様では、上記凹部は、上記基板本体上に配線されている上記ソース線の下方に、該ソース線に沿って連続的に形成されている。20

かかる構成の液晶パネル用アレイ基板では、基板本体上に配線されているソース線（ソース電極およびドレイン電極を含む）の下方の基板本体に凹部が連続的に形成されているため、平坦なソース線の形成を実現することができる。これにより、ソース線とゲート線とが交差する部位、ソース線と補助容量線とが交差する部位及びTFT形成部位において、アレイ基板とカラーフィルタ基板との間隔を大きくすることができるので、両基板間での短絡の虞を減少することができる。

#### 【0013】

また、本発明は、他の側面として、ここで開示されるアレイ基板を備える液晶パネルを提供する。30

本発明の液晶パネルによると、上記液晶パネル用アレイ基板を備えているので、配線抵抗の増大を抑えると共に、両基板間での短絡の虞を低減することを実現することができる。また、本発明は、このような液晶パネルを備える液晶表示装置を提供する。

#### 【図面の簡単な説明】

#### 【0014】

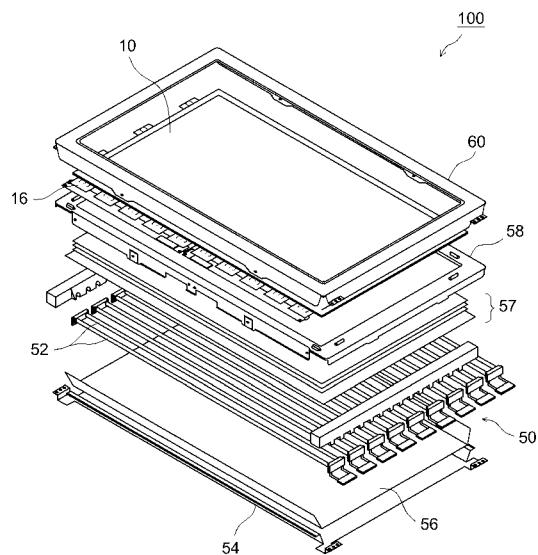

【図1】本発明の一実施形態に係る液晶表示装置の構成を模式的に示す分解斜視図である。40

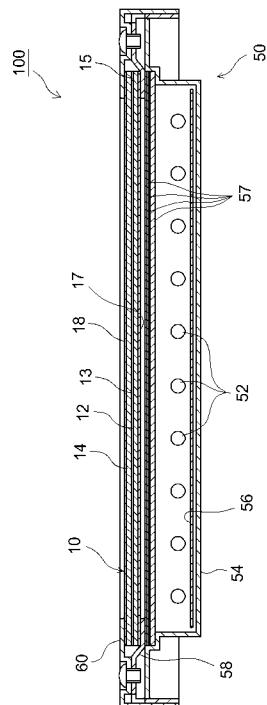

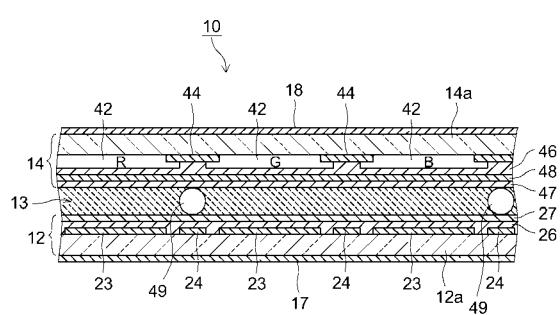

【図2】本発明の一実施形態に係る液晶表示装置の構成を模式的に示す断面図である。

【図3】本発明の一実施形態に係る液晶パネルの構成を模式的に示す部分断面図である。

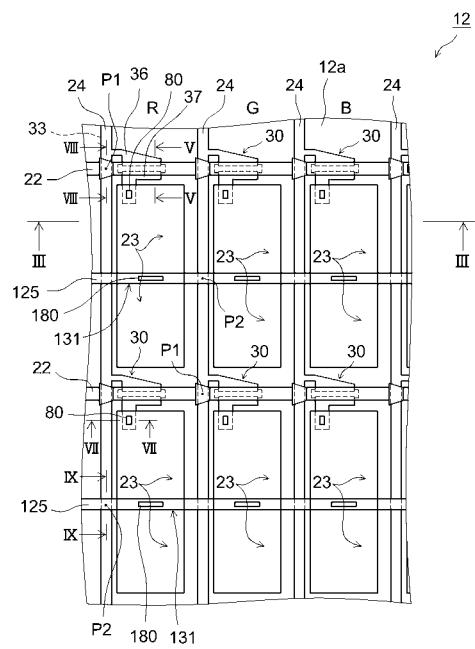

【図4】本発明の一実施形態に係る液晶パネルのアレイ基板の画素領域を示す部分平面図である。

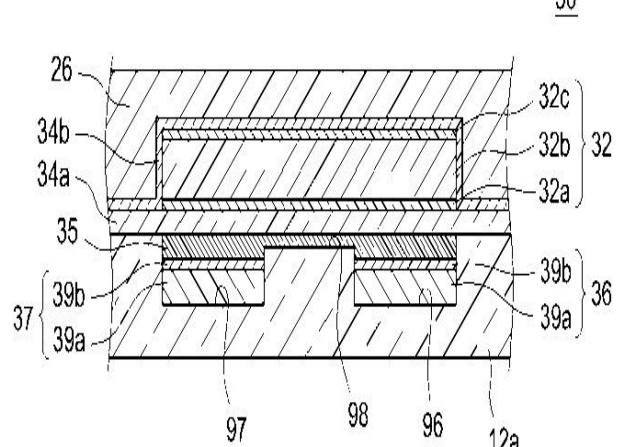

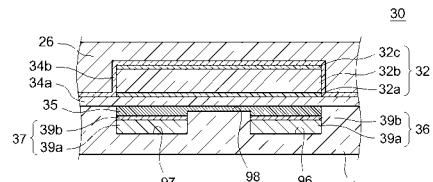

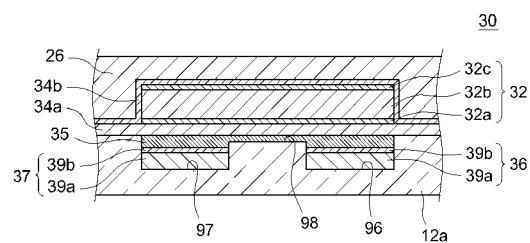

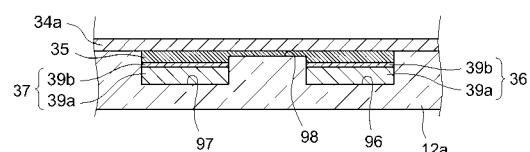

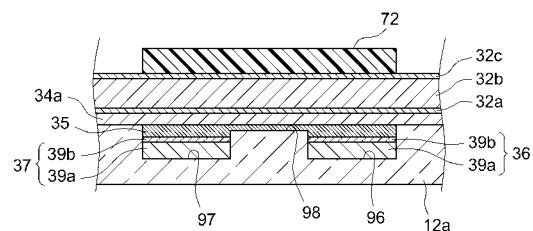

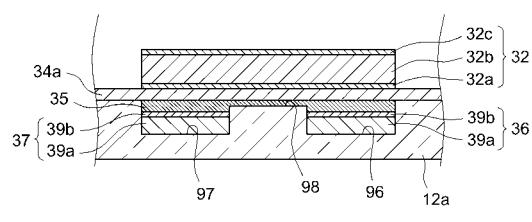

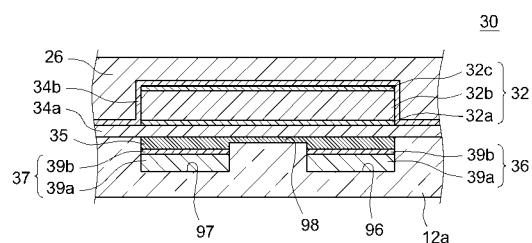

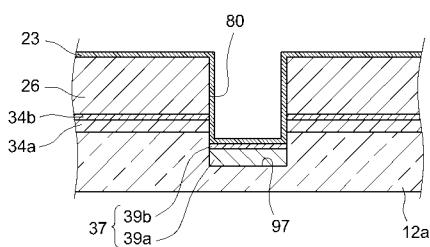

【図5】図4中のV-V線に沿う断面図であって、薄膜トランジスタ（TFT）の積層構造を模式的に示す断面図である。

【図6A】本発明の一実施形態に係るアレイ基板において、アレイ基板を構成するガラス基板本体の上にレジスト膜が所定位置に形成された状態を模式的に示す断面図である。

【図6B】フォトリソグラフィ実施後にガラス基板がパターン形成された状態を模式的に示す断面図である。

【図6C】パターン形成されたガラス基板の上にソース電極及びドレイン電極を構成する50

下層と上層とが積層された状態を模式的に示す断面図である。

【図6D】ソース電極及びドレイン電極の上層の上に半導体層が積層された状態を模式的に示す断面図である。

【図6E】半導体層上に第1の絶縁層が積層された状態を模式的に示す断面図である。

【図6F】第1の絶縁層の上にゲート電極を構成する下層と中層と上層とが積層された状態を模式的に示す断面図である。

【図6G】ゲート電極の上層の上にレジスト膜が所定位置に形成された状態を模式的に示す断面図である。

【図6H】フォトリソグラフィ実施後にゲート電極の下層と中層と上層とがパターン形成された状態を模式的に示す断面図である。

【図6I】積層されたゲート電極上に第2の絶縁層及び平坦化層が積層された状態を模式的に示す断面図である。

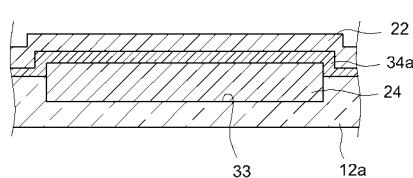

【図7】図4中のVII-VII線に沿う断面図であって、ドレイン電極と画素電極との接続部位を模式的に示す断面図である。

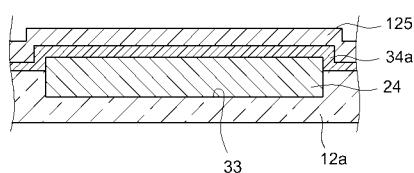

【図8】図4中のVII-II-VII-I線に沿う断面図であって、ソース線とゲート線とが交差する部位を模式的に示す断面図である。

【図9】図4中のIX-IX線に沿う断面図であって、ソース線と補助容量線とが交差する部位を模式的に示す断面図である。

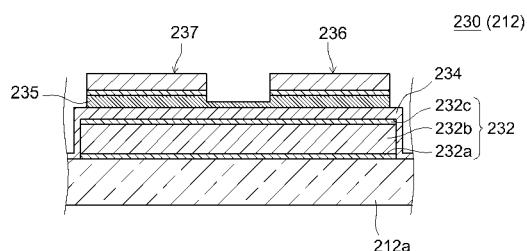

【図10】従来のアレイ基板におけるTFTの積層構造を模式的に示す断面図である。

【発明を実施するための形態】

#### 【0015】

以下、図面を参照しながら、本発明の好適な実施形態を説明する。なお、本明細書において特に言及している事項（例えば、アレイ基板の構成や製造方法）以外の事柄であって本発明の実施に必要な事柄（例えば、液晶表示装置に装備される光源の構成や該光源の駆動方式に係る電気回路等）は、当該分野における従来技術に基づく当業者の設計事項として把握され得る。本発明は、本明細書及び図面によって開示されている内容と当該分野における技術常識とに基づいて実施することができる。

#### 【0016】

以下、図1から図4を参照しながら、本発明の好ましい一実施形態に係る液晶パネル用アレイ基板12を備える液晶パネル10、及び該液晶パネル10を備えたアクティブマトリクス方式（TFT型）の液晶表示装置100について説明する。図1は、本実施形態に係る液晶表示装置100の構成を模式的に示す分解斜視図である。図2は、本実施形態に係る液晶表示装置100の構成を模式的に示す断面図である。図3は、上記液晶パネル10の構成を模式的に示す断面図である。図4は、本実施形態に係る液晶パネル用アレイ基板12を模式的に示す平面図である。

なお、以下の図面において、同じ作用を奏する部材、部位には同じ符号を付し、重複する説明は省略又は簡略化することがある。また、各図における寸法関係（長さ、幅、厚さ等）は、必ずしも実際の寸法関係を正確に反映するものではない。また、以下の説明において、「上方」又は「表側」とは液晶表示装置100における視聴者に面する側（すなわち液晶パネル側）をいい、「下方」又は「裏側」とは液晶表示装置100における視聴者に面しない側（すなわちバックライト装置側）をいうこととする。

#### 【0017】

図1及び図2を参照しつつ、液晶表示装置100の構成について説明する。液晶表示装置100は、図1に示されるように、液晶パネル10と、該液晶パネル10の裏側（図1における下側）に配置された外部光源であるバックライト装置50とを備えており、これらはベゼル（枠体）60等により組み付けられることで一体的に保持されている。

#### 【0018】

図1から図4を参照しつつ、液晶パネル10について説明する。

図1から図3に示されるように、液晶パネル10は、概して、全体として矩形の形状を有しており、その中央領域に画素が形成されている画素形成領域（有効表示領域、あるいは

はアクティブエリアともいう)を有している。また、この液晶パネル10は、互いに対向する一対の透光性のガラス製の基板12, 14と、その間に封入された液晶層13とから構成されるサンドイッチ構造を有している。かかる基板12, 14には、製造工程でそれぞれマザーガラスと称される大型の母材から切り出されたものが使用されている。上記一対の基板12, 14のうち、表側がカラーフィルタ基板(CF基板)14であり、裏側がアレイ基板12である。アレイ基板12及びCF基板14の周縁部(液晶パネル10における周縁部)には、シール材15が設けられており、液晶層13を封止している。液晶層13は、液晶分子を含む液晶材料から構成される。かかる液晶材料は、基板12, 14の間の電圧印加に伴って液晶分子の配向が操作され光学特性が変化する。両基板12, 14における対向しない側(外側)の面には、それぞれ偏光板17及び18が貼り付けられている。

10

#### 【0019】

図3及び図4に示されるように、ここで開示される液晶パネル10において、アレイ基板12を構成するガラス製の基板本体12aの表側(液晶層13に臨む側)には、表示させるための画素(詳細にはサブ画素)が配列しており、各画素を駆動するための複数のゲート線(走査線配線)22及びソース線(信号線配線)24が格子状のパターンをなすように形成されている。また、基板本体12aには、ゲート線22と平行な状態で独立配線された補助容量線(蓄積容量線、Csラインともいう。)125が別途設けられている。基板本体12aには、ソース線24の配線方向(図では水平方向)に沿って凹部33が連続的に形成されている。また、後述する薄膜トランジスタの形成部位には、ドレイン電極用凹部97(図5参照)とソース電極用凹部96(図5参照)が形成されている。

20

図4に示されるように、かかるゲート線22及びソース線24に囲まれた各格子領域には、画素電極23及びスイッチング素子である薄膜トランジスタ(以下、単に「TFT」ということもある。)30が設けられており、さらに画素電極23の電位を安定させる補助容量(蓄積容量、Csともいう。)131が形成されている。画素電極23は、典型的には透明な導電材料であるITO(インジウム酸化スズ)からなり、TFT30を構成するドレイン電極37とコンタクトホール80(図7参照)を介して電気的に接続している。これらの画素電極23には、画像に応じた電圧が上記ゲート線22、ソース線24及び薄膜トランジスタ30を介して所定のタイミングで供給される。補助容量131は、補助容量線125と、絶縁膜を挟んで補助容量線125と対向する位置に形成された図示しない補助容量電極(蓄積容量電極、Cs電極ともいう。)とを含んでいる。絶縁膜に形成されたコンタクトホール180を介して補助容量電極と画素電極23とが電気的に接続している。

30

上記ゲート線22及びソース線24は、図1に示されるように、典型的には液晶パネル10の周辺に設けられた外部駆動回路(ドライバIC)16であって、画像信号等を供給可能な外部駆動回路16に接続されている。また、補助容量線125は図示しない補助容量線駆動回路に接続されている。

40

なお、本実施形態では凹部33をソース線24に沿って連続的に形成しているが、少なくともソース線24とゲート線22の交差部位(TFT30の形成部位を含む)において凹部を形成すればよい。

#### 【0020】

図3に示されるように、画素電極23、ゲート線(図4参照)及びソース線24は、絶縁材料から成る平坦化層(オーバーコート層ともいう)26によって覆われている。平坦化層26の上には、ポリイミド等から成る配向膜27が形成されている。この配向膜27の表面には、電圧を印加していないときの液晶分子の配向方向を決定するために、配向処理が施されている。配向処理としては、ラビング処理を行う方法、光配向処理を行う方法等が挙げられる。

#### 【0021】

一方、図3に示されるように、CF基板14を構成するガラス製の基板本体(ガラス基板)14aの裏側(液晶層13に臨む側)には、アレイ基板12の各画素電極23に対応

50

する位置にカラーフィルタ42と、該各色のフィルタ42を区画するブラックマトリクス(遮光膜)44が形成されている。図3に示されるように、カラーフィルタ42には赤(R)、緑(G)、青(B)の3色があり、アレイ基板12の1つの画素電極23に対してR・G・Bいずれか1つのカラーフィルタ42が対向している。ブラックマトリクス44はサブ画素間の領域を光が透過しないようにするために、Cr(クロム)等の金属により形成されている。平坦化層46は、図3に示されるように、カラーフィルタ42及びブラックマトリクス44を覆うように形成されており、この平坦化層46の表面にはITOから成る対向電極(共通電極)48が形成されている。また、対向電極48のさらに表面には配向膜47が形成されている。この配向膜47の表面にも配向処理(上記配向膜27と同様の方法)が施されている。なお、本実施形態アレイ基板12の配向膜27の配向方向と、CF基板14の配向膜47の配向方向とは90°異なる。

10

## 【0022】

上記アレイ基板12及びCF基板14との間隙(ギャップ)には、図3に示されるように、球形又は円柱形状で複数個のスペーサ49(図3では、球形)が挟まれるように分散配置されている。スペーサ49は、例えば、弾性変形可能な樹脂材料により形成されている。このことにより、上記基板12, 14の間隙は、上述したシール材15(図2参照)及びスペーサ49によって保持され、液晶層13が一定の厚みに維持されている。

また、図2及び図3に示されるように、上記基板12, 14の互いに対向しない側の面にはそれぞれ偏光板17, 18が貼り付けられている。

20

## 【0023】

上記液晶パネル10の表側には、図1及び図2に示されるように、ベゼル60が装着されている。また、液晶パネル10の裏側には、フレーム58が装着されている。そして、ベゼル60及びフレーム58は、液晶パネル10を挟んだ状態で互いに固定される。さらに、フレーム58は、液晶パネル10の中央部分における有効表示領域に相当する部分が開口している。液晶パネル10の裏側(ベゼル60の裏側)には、ケース54に収容されたバックライト装置50が装着されている。

30

## 【0024】

バックライト装置50は、図1に示されるように、複数本の線状の光源(典型的には冷陰極管、発光ダイオード等)52と、光源52を収納するケース(シャーシ)54とから構成されている。ケース54は、表側に向けて開口した箱形形状を有しており、ケース54内には、光源52が平行に配列されており、ケース54と光源52との間には、光源52の光を効率的に視聴者側に反射させるための反射部材56が配置されている。

30

## 【0025】

また、ケース54の開口部には、複数のシート状の光学部材57が積層されて該開口部を覆うように配置されている。光学部材57の構成としては、例えば、バックライト装置0側から順に、拡散板、拡散シート、レンズシート、及び輝度上昇シートから構成されているが、この組合せ及び順序に限定されない。さらに、光学部材57をケース54に挟んで保持するために、ケース54には、略枠状の上記フレーム58が設けられている。

40

ケース54の裏側には、インバータ回路を搭載するための図示しないインバータ回路基板と、各光源52に電力を供給する昇圧回路としての図示しないインバータトランジスタが設けられているが、本発明を特徴付けるものではないため説明は省略する

## 【0026】

以上のような構成の液晶表示装置100は、アレイ基板12とCF基板14との間に制御された電圧を印加することによって液晶層13中の液晶分子を操作して、バックライト装置50からの光を液晶パネル10において通過又は遮断させる。また、かかる液晶表示装置100は、バックライト装置50の輝度等も制御しつつ、所望の画像を上記液晶パネル10の有効表示領域に表示させる。

## 【0027】

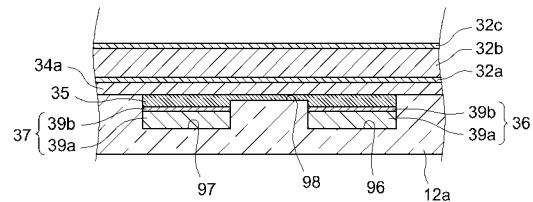

次に、図5から図6Iを参照しつつ、本実施形態に係るアレイ基板12におけるTFT30についてさらに詳細に説明する。図5は、図4中のV-V線に沿う断面図であって、

50

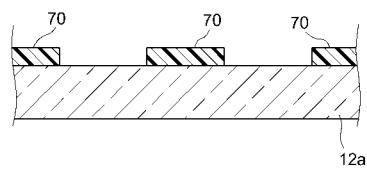

TFTの積層構造を模式的に示す断面図である。図6Aから図6Iは、TFT30の積層構造を形成する工程を順に模式的に示す断面図である。図6Aは、アレイ基板12を構成するガラス基板12aの上にレジスト膜70が所定位置に形成された状態を模式的に示す断面図である。図6Bは、フォトリソグラフィ実施後にガラス基板12aがパターン形成された状態を模式的に示す断面図である。図6Cは、パターン形成されたガラス基板12aの上にソース電極36及びドレイン電極37を構成する金属膜層の下層39aと上層39bとが積層された状態を模式的に示す断面図である。図6Dは、ソース電極36及びドレイン電極37の上層39bの上に半導体層35が積層された状態を模式的に示す断面図である。図6Eは、半導体層35上に第1の絶縁層34aが積層された状態を模式的に示す断面図である。図6Fは、第1の絶縁層34a上にゲート電極を構成する下層32aと中層32bと上層32cとが積層された状態を模式的に示す断面図である。図6Gは、ゲート電極の上層32cの上にレジスト膜72が所定位置に形成された状態を模式的に示す断面図である。図6Hは、フォトリソグラフィ実施後にゲート電極32がパターン形成された状態を模式的に示す断面図である。図6Iは、積層されたゲート電極32上に第2の絶縁層34b及び平坦化層26が積層された状態を模式的に示す断面図である。なお、図5及び図6Aから図6Iは模式的な断面図であるため、図4に係る模式的な平面図とは厳密には一致していない。

10

## 【0028】

図4に示されるように、本実施形態に係る液晶パネル10のアレイ基板12は、ガラス製のガラス基板(基板本体)12aと、複数のゲート線22と、該ゲート線22に直角に交差する複数のソース線24と、いずれかのゲート線22及びソース線24と電気的に接続する複数のTFT30とを備えている。本実施形態に係るアレイ基板12では、画素の開口率を大きくするためにTFT30がソース線24上(詳細にはゲート線22との交差部位P1(図4参照)の近傍におけるソース線24上)に配置されている。

20

かかるアレイ基板12において上記TFT30は、図5に示されるように、ガラス基板12a上に形成されたソース電極36及びドレイン電極37と、該電極36,37の上方に形成(積層)された半導体(膜)層35と、該半導体層35の上方に形成された第1の絶縁(膜)層34aと、該絶縁層34aの上方に形成されたゲート電極32と、該ゲート電極32の上方に形成された第2の絶縁(膜)層34bと、該絶縁層34bの上方に形成された平坦化層26とを含む積層構造を有している。ゲート電極32はゲート線22(図4参照)に、ソース電極36はソース線24(図4参照)に、そしてドレイン電極37はコンタクトホール80を介して画素電極23(図4参照)にそれぞれ電気的に接続されている。

30

## 【0029】

本実施形態に係るガラス基板12aのTFT30形成部分には、図5に示されるように、その周辺部位(領域)よりも所定の深さで凹んだソース電極用凹部96及びドレイン電極用凹部97が形成されている。ソース電極用凹部96の上方にはソース電極36が形成されており、ドレイン電極用凹部97の上方にはドレイン電極37が形成されている。かかる電極36,37は、いずれも二層構造の金属膜層から形成されており、該金属膜層は、A1から成る下層39aとTiから成る上層39bとから構成される。

40

上記各電極36,37の上層39bの上方には、ソース電極36からドレイン電極37に連続的に半導体(膜)層35が形成され、該半導体層35の上方には第1の絶縁層34aが形成されている。かかる第1の絶縁層34aの上方にはゲート電極32が形成されている。なお、本実施形態では、ソース電極36及びドレイン電極37さらには半導体層35の全てがそれに対応する上記凹部96,97に埋設されるように形成されているが、少なくともソース電極36及びドレイン電極37の一部が上記凹部96,97にそれぞれ埋設されればよい。

## 【0030】

上記二層構造のソース電極36及びドレイン電極37の上層39b,39b上に形成されている半導体層35は、TFT30のスイッチとして機能するアモルファスシリコン(

50

- S i ) 層と、該 - S i 層の下方に積層された  $n^+$  アモルファスシリコン ( $n^+ - S i$ ) 層とから構成される。かかる  $n^+ - S i$  層は、上記 - S i 層とソース電極 3 6 及びドレイン電極 3 7との間に良好なオーミックコンタクトをとるために設けられており、不純物としてリン (P) がドープされた - S i から成る。ここで、上記 - S i 層と  $n^+ - S i$  層との間に、チャネル保護膜 (i ストップ膜) として機能する絶縁層であつて Si Nx から成る絶縁層が介在していてもよい。

#### 【0031】

上記第1の絶縁層 3 4 a は、ゲート絶縁膜として機能しており、従来の TFT におけるゲート絶縁膜と同様に、シリコン (S i) の窒化物 (Si Nx) 及び / 又は酸化物 (Si O x) 等から構成されている。かかる第1の絶縁層 3 4 a は、多層構造 (例えば二層構造) であつてもよい。10

#### 【0032】

上記第1の絶縁層 3 4 a の上には、ゲート電極 3 2 が形成されている。かかるゲート電極 3 2 は、二層のチタン (Ti) 層の間に一層のアルミニウム (Al) 層が挟まれた態様の三層構造を有する。すなわち、かかる三層構造は、第1の絶縁層 3 4 a の上方に Ti からなる下層 3 2 a が積層されており、下層 3 2 a の上に積層された Al からなる中層 3 2 b と、該中層 3 2 b 上に積層された Ti からなる上層 3 2 c とから構成される。

以上のような構成により、本実施形態に係る TFT 3 0 は、ソース電極 3 6 及びドレイン電極 3 7 の少なくとも一部がガラス基板 1 2 a の凹部 9 6 , 9 7 内に埋設されてなる積層構造を備えている。20

#### 【0033】

次に、図 6 A から図 6 I を参照しつつアレイ基板 1 2 、該アレイ基板 1 2 を備えた液晶パネル 1 0 の製造方法の一例について TFT 3 0 の領域を中心として説明する。なお、本実施形態に係るアレイ基板 1 2 の製造工程において、該製造に採用されるフォトリソグラフィにより積層される薄膜の種類 (膜材料) 等は、従来のアレイ基板と同様でよく、特に制限はない。以下、大まかな製造工程を説明するがこれに限定されるものではない。

#### 【0034】

まず、マザーガラスから切り出されたガラス基板 1 2 a を用意する。そして、ガラス基板 1 2 a 上に紫外線感光樹脂から成るレジスト膜 7 0 を塗布する (レジスト塗布工程)。プリベーク (予備乾燥) により該レジスト膜 (例えばポジレジスト膜 7 0 ) を硬化させる (プリベーク工程)。次いで、かかる硬化したレジスト膜 7 0 上にパターニングされたマスクを載せて、該マスクの上から所定波長の紫外線 (例えば波長 3 6 5 nm の i 線) を照射して露光する (露光工程)。かかる露光後のガラス基板 1 2 a を現像液に浸漬し、その後純水 rinsing を行うことにより、ポジレジスト膜 7 0 の露光部分を溶解除去する (現像工程)。この後、ポストベークを実施する (ポストベーク工程)。これにより、図 6 A に示されるように、上記ガラス基板 1 2 a の上に上記マスクのパターンが転写されたレジスト膜 7 0 (ポジレジスト膜の未露光部分) が形成される。30

#### 【0035】

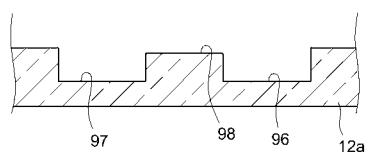

次に、エッティング処理を実施して、上記ガラス基板 1 2 a における上記レジスト膜 7 0 が形成されていない所定の部分に所定の深さのソース電極用凹部 9 6 及びドレイン電極用凹部 9 7 を形成する (エッティング工程)。かかるエッティング処理としては、ドライエッティング及びウェットエッティングが挙げられる。例えば、プラズマにより生じるガスラジカルを利用したドライエッティング等を好ましく用いることができる。ここで、凹部 9 6 , 9 7 の深さは、上記エッティング処理条件 (例えばエッティングレート) を適宜調整することにより設定される。凹部 9 6 , 9 7 の深さとしては 5 0 0 nm ~ 7 0 0 nm 程度 (例えば 5 2 5 nm ~ 6 8 5 nm) が適当である (本実施形態では 5 9 5 nm である。)。最後に、例えば、酸素ガスプラズマ等によって上記レジスト膜 7 0 をガラス基板 1 2 a から剥離する (レジスト剥離工程)。なお、本実施形態において、凹部 9 6 , 9 7 の間には、ガラス基板 1 2 a の表面から後退した凸部 9 8 が上記エッティング処理により形成されている。

以上により、図 6 B に示されるように、ガラス基板 1 2 a の上面に凹部 9 6 , 9 7 が形40

10

20

30

40

50

成される。

**【0036】**

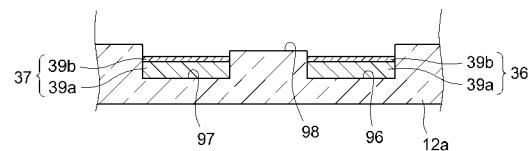

次いで、凹部96, 97が形成されたガラス基板12aを洗浄する（洗浄工程）。そして、図6Cに示されるように、ガラス基板12a上に、ソース電極36及びドレイン電極37を構成する上記A1から成る下層39aとTiから成る上層39bとをスパッタリングにより堆積（蒸着）させる（膜形成工程）。これにより、ガラス基板12aに形成された凹部96, 97内に、ソース電極36及びドレイン電極37の少なくとも一部（本実施形態ではソース電極36及びドレイン電極37の全部）が埋め込まれるように形成される。

上記下層39aの膜厚としては230nm～310nmが適当であり（本実施形態では270nmである。）、上記上層39bの膜厚としては30nm～40nmが適当である（本実施形態では35nmである。）。

**【0037】**

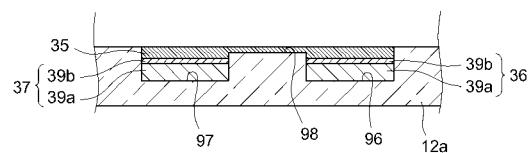

次いで、図6D及び図6Eに示されるように、膜形成工程において、上記ソース電極36及びドレイン電極37の上に、半導体層35、及び第1の絶縁層（ゲート絶縁膜）34aを順に形成する。ここで、-Si層及びn<sup>+</sup>-Si層の二層構造の半導体層35と、該二層構造の半導体層35の各層の間に介在し得るチャネル保護膜層と、SiNx等から成る第1の絶縁層34aとは、プラズマCVDにて四層続けて積層することができる。本実施形態では、半導体層35の一部は上記凹部96, 97内の上層39b, 39bに積層されており、凸部98上に形成されているため、半導体層35はガラス基板12aから上方へ突出していない。これにより、ガラス基板12aの表面は平坦な構造となっている。半導体層35における-Si層の膜厚としては190nm～280nmが適当であり（本実施形態では230nmである。）、n<sup>+</sup>-Si層の膜厚としては44nm～66nmが適当であり（本実施形態では55nmである。）、及びチャネル保護膜の膜厚としては210nm～320nmが適当であり（本実施形態では260nmである。）、第1の絶縁層34aの膜厚としては330nm～500nmが適当である（本実施形態では410nmである。）。

**【0038】**

次いで、図6Fに示されるように、上記と同様にして、上記第1の絶縁層34aの上に、ゲート電極32となる三層構造の金属膜層、即ちTiから成る下層32aとAlから成る中層32bとTiから成る上層32cとをスパッタリングにより堆積させる。ここで、上記下層32aの膜厚としては60nm～160nmが適当であり（本実施形態では110nmである。）、上記中層32bの膜厚としては310nm～410nmが適当であり（本実施形態では360nmである。）、上記上層32cの膜厚としては30nm～40nmが適当である（本実施形態では35nmである。）。

また、図6Gに示されるように、かかる膜形成工程で積層された上記ゲート電極32となる金属膜層の上層32cには、レジスト塗布工程でレジスト膜72が塗布され、プリベーク、露光、現像、ポストベーク、エッチング、及びレジスト剥離の一連の工程を経てパターニングされたゲート電極32（図6H参照）が形成される。

**【0039】**

次に、図6Iに示されるように、上記のように形成されたゲート電極32の上方に該ゲート電極32を覆うように第2の絶縁層34bを上記第1の絶縁層34aと同様にして形成する。次いで平坦化層26（図3参照）を所定の方法（例えばフォトリソグラフィ）により形成する。なお、本実施形態では第1の絶縁層34aと平坦化層26を形成しているが、少なくともいずれかの層を形成すればよい。

**【0040】**

次いで、例えばインクジェット方式により上記平坦化層26上に配向膜構成材料（例えばポリイミド材料）を塗布し、その後、液晶分子の配向を制御するためのラビング処理（例えばラビング布で所定方向に沿って膜の表面を擦る処理）を行って、配向膜27を形成する。

10

20

30

40

50

以上のようにして、アレイ基板12を製造する。

#### 【0041】

次に、CF基板14を製造する。かかるCF基板14の製造方法は、従来の方法と同様でよい。好適な一方法として、アレイ基板12と同様に、フォトリソグラフィを採用することができる。かかる方法では、まずガラス基板14a上に、各色のカラーフィルタ42を囲む枠となるブラックマトリクス44を、典型的にはフォトリソグラフィにより格子状に形成する。その後、例えばR(赤)の顔料分散レジスト(赤色の顔料を透明樹脂中に分散して得られるレジスト材料)を上記ブラックマトリクス44が形成されているガラス基板14a上に均一に塗布し、その後、マスク合わせをして露光することによりRのカラーフィルタのパターンを焼き付ける。次いで、現像を行ってRのサブ画素(カラーフィルタ)を所定パターンで形成する。G(緑)及びB(青)のカラーフィルタについても同様にして形成する。その後、平坦化層46及び対向電極48となる透明なITO導電膜を、例えばスパッタリングあるいはフォトリソグラフィ等で上記カラーフィルタ42及びブラックマトリクス44上に形成する。上記対向電極48上に配向膜47を形成する方法は、上記アレイ基板12に配向膜27を形成する方法と同様でよい。

10

以上のようにして、CF基板14を作製する。

#### 【0042】

上記のようにして得られたアレイ基板12及びCF基板14を用いて液晶パネル10を以下のようにして製造する。上記アレイ基板12とCF基板14とを貼り合わせる(図2及び図3参照)。すなわち、まず上記アレイ基板12の周縁部を囲むようにシール材料(例えば熱硬化性樹脂や紫外線硬化性樹脂から成るシール接着剤)を付与してシール材15を形成する。次に、アレイ基板12とCF基板14との間隙(ギャップ)を作るために、アレイ基板12上にスペーサ49を散布する。この後、上記アレイ基板12上にCF基板14を互いの配向膜27, 47が形成されている側同士が対向するように重ねて貼り合わせる。

20

#### 【0043】

次いで、上記貼り合わせた一対の上記基板12, 14を真空に保ち毛細管現象により液晶材を上記基板間のギャップに注入する(ディップ方式)。そして、該ギャップ内に液晶材を充填した後に注入口を封止する(例えば紫外線硬化型接着剤を用いて注入口を塞ぐ)。最後に、両基板12, 14の対向しない側の各面(即ち配向膜27, 47が形成されていない面)に偏光板17, 18を貼る。このようにして液晶パネル10が完成する。

30

#### 【0044】

上記完成した液晶パネル10の表側及び裏側に、それぞれベゼル60及びフレーム58を配置することにより該液晶パネル10を支持し、フレーム58の裏側に光学部材57及びケース54に収容されたバックライト装置50を装着する。このようにして液晶表示装置100を構築する。

30

#### 【0045】

ここで、上記のようにして製造したアレイ基板12と従来のアレイ基板212との相違を、図10を参考しつつTFT230の構造を例にして説明する。図10は、従来のアレイ基板212におけるTFT230の積層構造を模式的に示す断面図である。

40

従来のアレイ基板212のTFT230の積層構造は、図10に示されるように、ガラス基板212aの上に、ゲート電極232を構成する下層232a、中層232b及び上層232cが形成され、さらに絶縁層(ゲート絶縁膜)234、その上に半導体層235が積層されている。そして、かかる半導体層235の上にソース電極236及びドレイン電極237がそれぞれ形成されており、かかる電極236, 237に挟まれる部位(チャネル)には、半導体層235における-Si層がチャネル保護膜により覆われた状態で現われている。ここで、従来のアレイ基板212のTFT230形成部分では、平坦なガラス基板212a上にゲート電極232が形成されており、該ゲート電極よりも上方にソース電極236およびドレイン電極237が形成された積層構造であるため、TFT230の周辺部分の上面部に比べて突出した形態となっている。このような形態のアレイ基板

50

212を液晶パネルとして採用した場合には、対向配置されるCF基板との基板間の距離(間隔)が、ソース電極236及びドレイン電極237の位置する部位において小さくなる(狭くなる)。このため、両基板間に配置される液晶層の中に不純物(異物)が混入し、かかる不純物が両基板同士の間隔の小さい部位に介在した際には、該間隔の大きな部位に介在する場合に比べて、高い確率で両基板間での好ましくない短絡が発生する虞がある。

#### 【0046】

一方、図5及び図6Iに示されるように、本実施形態に係るアレイ基板12では、ガラス基板12aにソース電極用凹部96及びドレイン電極用凹部97が形成されており、該凹部96, 97内にソース電極36及びドレイン電極37が埋設されるようにして形成されている(本実施形態では半導体層35の一部も凹部96, 97に埋設されるように形成されている)。このため、TFT30形成部分の厚みは、ソース電極36及びドレイン電極37がガラス基板12aに埋設している部分の厚みだけ小さくなる(薄くなる)。従って、かかるアレイ基板12とCF基板14とが対向配置されて成る液晶パネル10(図3参照)において、ゲート電極32の位置する部位(即ちTFT30形成部分)における上記両基板12, 14間の間隔は、従来のアレイ基板212に比べて大きくなる。以上より、本実施形態に係る液晶パネル10によって、上記アレイ基板12, CF基板14間での短絡の発生を低減することができる液晶パネルが実現される。

#### 【0047】

次に、アレイ基板12において、ドレイン電極37と画素電極23との接続部位の構造について説明する。図7は、図4中のVII-VIII線に沿う断面図であって、ドレイン電極37と画素電極23とがコンタクトホール80を介して接続している状態を模式的に示す断面図である。

図7に示すように、ガラス基板12aにおいてドレイン電極37と画素電極23とが重なっている部位には、該重なり部位に隣接する部位よりも凹んだドレイン電極用凹部97が形成されている。該凹部97の上方にはA1から成る下層39aとTiから成る上層39bとから構成されるドレイン電極37が該凹部97に少なくともその一部が埋設されるように形成されている。ドレイン電極37と画素電極23とを電気的に接続するためにドレイン電極37の上方に形成された第1の絶縁膜34aと第2の絶縁膜34bと平坦化層26とをエッチング処理によって除去することによってコンタクトホール80が形成されている。これによりコンタクトホール80においてドレイン電極37の上層39bが露出する。そして透明な導電材料であるITOをスパッタリングにより堆積させて画素電極23を形成することで、画素電極23はコンタクトホール80を介してドレイン電極37(上層39b)と接触(電気的に接続)する。

従来のアレイ基板のように、ゲート電極の上方に絶縁膜と半導体膜を介してTiから成る金属膜とA1から成る金属膜とをこの順に形成したドレイン電極では、ITOをA1から成る金属膜の上方に直接堆積させると表面が酸化して酸化アルミニウムが形成され不具合が発生する虞がある。このためA1から成る金属膜をエッチングしITOとA1膜とが直接接触しないようにして、ITOとTiから成る金属膜を接触(接続)させる必要があるが、本実施形態では上層39bがTiから成る金属膜層であるためA1膜を除去することなく画素電極23を構成するITOを上層39bに直接積層させて電気的に接続することが実現される。

#### 【0048】

次に、アレイ基板12において、ソース線24とゲート線22との交差部位の構造について説明する。図8は、図4中のVII-II-VIII-I线に沿う断面図であって、ソース線とゲート線22とが交差する部位を模式的に示す断面図である。本実施形態に係るアレイ基板12は、図4に示されるように、画素領域において、TFT30のオン・オフ信号を供給するゲート線22とTFT30に表示信号(信号電圧)を供給するソース線24とが交差する部位P1を複数備えている。

図8に示されるように、ガラス基板12aには、少なくともゲート線22とソース線2

10

20

30

40

50

4との交差部位P1において、該交差部位P1に隣接する周辺の非交差部位よりも凹んだ凹部33が形成されている。そして、ソース線24の少なくとも一部は、かかる凹部33内に配線されて該凹部33上でゲート線22と交差している。このように、ガラス基板12aにおいて上記交差部位P1が凹んでいるため、かかる凹部33上にソース線24を配線して、該ソース線24上にゲート線22を交差するように配置すると、従来のアレイ基板(凹部が形成されていないアレイ基板)212と比べて、交差部位P1の厚みが小さく(薄く)なる。従って、該交差部位P1において、アレイ基板12とCF基板14との間隔は、従来のアレイ基板212と比較して大きくなる。なお、本実施形態に係るアレイ基板12では、上記凹部33は、ソース線24の下方に、該ソース線24に沿って連続的に形成されているが、少なくともソース線24とゲート線22とが交差する部位において形成されればよい。

10

#### 【0049】

次に、アレイ基板12において、ソース線24と補助容量線125との交差部位の構造について説明する。図9は、図4中のIX-IX線に沿う断面図であって、ソース線24と補助容量線125とが交差する部位を模式的に示す断面図である。本実施形態に係るアレイ基板12は、図4に示されるように、画素領域において、補助容量131に所定の電圧を供給する補助容量線125とソース線24とが交差する部位P2を複数備えている。

20

図9に示されるように、ガラス基板12aには、少なくとも補助容量線125とソース線24との交差部位P2において、該交差部位P2に隣接する周辺の非交差部位よりも凹んだ凹部33が形成されている。そして、ソース線24は、かかる凹部33内に配線されて該凹部33上で補助容量線125と交差している。かかる様により、従来のアレイ基板212と比べて、交差部位P2の厚みが小さくなり、該交差部位P2において、アレイ基板12とCF基板14間の間隔は、従来のアレイ基板212と比較して大きくなる。

#### 【0050】

以上、本発明の好適な一実施形態について図面を参照しつつ説明したが本発明の液晶パネル用アレイ基板は、かかる実施形態に限られない。例えば、凹部の形状(凹み形状)は、上述した本発明の目的が実現する限りにおいて特に限定されない。例えば、上述のような断面長方形の形状に限らず、台形状のものであってもよい。

30

また、基板はガラス基板に限られずその他の材料(合成樹脂等)からなる基板であってもよい。

#### 【産業上の利用可能性】

#### 【0051】

本発明によって提供される液晶パネル用アレイ基板を使用することにより、薄型であって基板間で短絡が生じにくい液晶パネルを構築して、該パネルを備えた信頼性の高い液晶表示装置を提供することができる。

#### 【符号の説明】

#### 【0052】

10 液晶パネル

40

12 アレイ基板

12a ガラス基板(基板本体)

13 液晶層

14 カラーフィルタ(CF)基板

14a ガラス基板

15 シール材

16 外部駆動回路(ドライバIC)

17, 18 偏光板

22 ゲート線

23 画素電極

24 ソース線

26 平坦化層(オーバーコート層)

50

|           |                  |    |

|-----------|------------------|----|

| 2 7       | 配向膜              |    |

| 3 0       | 薄膜トランジスタ ( TFT ) |    |

| 3 2       | ゲート電極            |    |

| 3 2 a     | 下層               |    |

| 3 2 b     | 中層               |    |

| 3 2 c     | 上層               |    |

| 3 3       | 凹部               |    |

| 3 4 a     | 第 1 の絶縁層         |    |

| 3 4 b     | 第 2 の絶縁層         |    |

| 3 5       | 半導体層             | 10 |

| 3 6       | ソース電極            |    |

| 3 7       | ドレイン電極           |    |

| 3 9 a     | 下層               |    |

| 3 9 b     | 上層               |    |

| 4 2       | カラーフィルタ          |    |

| 4 4       | ブラックマトリクス        |    |

| 4 6       | 平坦化層             |    |

| 4 7       | 配向膜              |    |

| 4 8       | 対向電極             |    |

| 4 9       | スペーサ             | 20 |

| 5 0       | バックライト装置         |    |

| 5 2       | 光源               |    |

| 5 4       | ケース              |    |

| 5 6       | 反射部材             |    |

| 5 7       | 光学部材             |    |

| 5 8       | フレーム             |    |

| 6 0       | ベゼル ( 枠体 )       |    |

| 7 0 , 7 2 | レジスト膜            |    |

| 8 0       | コンタクトホール         |    |

| 9 6       | ソース電極用凹部         | 30 |

| 9 7       | ドレイン電極用凹部        |    |

| 9 8       | 凸部               |    |

| 1 0 0     | 液晶表示装置           |    |

| 1 2 5     | 補助容量線            |    |

| 1 3 1     | 補助容量             |    |

| 1 8 0     | コンタクトホール         |    |

| 2 1 2     | アレイ基板            |    |

| 2 1 2 a   | ガラス基板            |    |

| 2 3 0     | TFT              |    |

| 2 3 2     | ゲート電極            | 40 |

| 2 3 2 a   | 下層               |    |

| 2 3 2 b   | 中層               |    |

| 2 3 2 c   | 上層               |    |

| 2 3 4     | 絶縁層              |    |

| 2 3 5     | 半導体層             |    |

| 2 3 6     | ソース電極            |    |

| 2 3 7     | ドレイン電極           |    |

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6 A】

【図6 B】

【図6 C】

【図6 D】

【図6 F】

【図6 E】

【図6 G】

【図 6 H】

【図 6 I】

【図 7】

【図 8】

【図 9】

【図 10】

---

フロントページの続き

(72)発明者 伊藤 貴昭

大阪府大阪市阿倍野区長池町 22番22号 シャープ株式会社内

Fターム(参考) 2H092 JA25 JA36 JA44 JB32 JB33 JB56 NA16 PA01 PA06 PA08

PA13

|                |                                                                                                                                                                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶面板的阵列基板和具有该基板的液晶显示装置                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2011221295A</a>                                                                                                                                                                                                                                  | 公开(公告)日 | 2011-11-04 |

| 申请号            | JP2010090516                                                                                                                                                                                                                                                   | 申请日     | 2010-04-09 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 大上亮<br>伊藤貴昭                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 大上 亮<br>伊藤 貴昭                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G02F1/1368                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G02F1/1368                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 2H092/JA25 2H092/JA36 2H092/JA44 2H092/JB32 2H092/JB33 2H092/JB56 2H092/NA16 2H092 /PA01 2H092/PA06 2H092/PA08 2H092/PA13 2H192/AA24 2H192/BC31 2H192/CB03 2H192/CB71 2H192/CC32 2H192/CC72 2H192/DA12 2H192/DA42 2H192/EA22 2H192/EA43 2H192/EA67 2H192 /GD02 |         |            |

| 代理人(译)         | 安倍晋三诚                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                      |         |            |

### 摘要(译)

要解决的问题：提供一种液晶面板，其具有能够减少封闭液晶的一对基板之间短路的可能性的结构，并提供适合于构造这种面板的液晶面板的阵列基板。解决方案：薄膜晶体管30包括层叠结构，该层叠结构至少在用于液晶面板的阵列基板中具有栅电极32，源电极36和漏电极37。在构成薄膜晶体管的部分的至少一部分中，与构成薄膜晶体管的部分的周边相比，基板主体（玻璃基板）12a包括凹陷部分96和97。至少部分源电极和漏电极嵌入凹陷部分中。