(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3609977号 (P3609977)

(45) 発行日 平成17年1月12日(2005.1.12)

(24) 登録日 平成16年10月22日 (2004.10.22)

(51) Int. C1. <sup>7</sup> F 1

HO3K 19/0185 HO3K 19/00 1 O 1 D GO9G 3/20 GO9G 3/20 62 1 L

**GO9G 3/36** GO9G 3/36

請求項の数 9 (全 21 頁)

(21) 出願番号 特願2000-92725 (P2000-92725) (22) 出願日 平成12年3月30日 (2000.3.30) (65) 公開番号 特開2001-85990 (P2001-85990A) (43) 公開日 平成13年3月30日 (2001.3.30) 審查請求日 平成14年7月12日 (2002.7.12) (31) 優先権主張番号 特願平11-201100 平成11年7月15日 (1999.7.15) (33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

||(74) 代理人 100103296

弁理士 小池 隆彌

(74) 代理人 100073667

弁理士 木下 雅晴

|(72)発明者 佐々木 修

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 小川 康行

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】レベルシフト回路および画像表示装置

# (57)【特許請求の範囲】

### 【請求項1】

入力部に設けられる容量手段と、前記容量手段により容量結合された入力信号の直流電圧 レベルを設定するためのバイアス電圧設定手段と、直流電圧レベルを設定された入力信号 の振幅レベルを増幅するためのアンプ手段とを備えたレベルシフト回路において、

前記バイアス電圧設定手段が正電源電圧と負電源電圧との間に分圧手段を設けることで構成されると共に、前記アンプ手段への入力信号線が1本であり、

前記バイアス設定手段は、第1の p チャネルのトランジスタのソースが正電源電圧に接続され、第1の n チャネルのトランジスタのソースが負電源電圧に接続され、第2の p チャネルのトランジスタのゲートとドレインと第2の n チャネルのトランジスタのゲートとドレインと第2の n チャネルのトランジスタのゲートとドレインとがアンプ手段の入力端子に接続されることを特徴とするレベルシフト回路。

【請求項2】

前記アンプ手段が C M O S インバータ回路であることを特徴とする請求項 1 記載のレベルシフト回路。

# 【請求項3】

前記バイアス電圧設定手段で設定された直流電圧レベルをクランプするための電圧クランプ手段を備えることを特徴とする請求1乃至2記載のレベルシフト回路。

### 【請求項4】

前記バイアス電圧設定手段で設定された直流電圧レベルが前記電圧クランプ手段によりクランプするときに、電圧降下した電圧を補償する手段を備えることを特徴とする請求項3

記載のレベルシフト回路。

### 【請求項5】

入力部に設けられる容量手段と、前記容量手段により容量結合された入力信号の直流電圧 レベルを設定するためのバイアス電圧設定手段と、直流電圧レベルを設定された入力信号 の振幅レベルを増幅するためのアンプ手段とを備えたレベルシフト回路を用いた画像表示 装置において、

前記バイアス電圧設定手段が正電源電圧と負電源電圧との間に分圧手段を設けることで構成されると共に、前記アンプ手段への入力信号線が1本であり、

前記バイアス設定手段は、第1の p チャネルのトランジスタのソースが正電源電圧に接続され、第1の n チャネルのトランジスタのソースが負電源電圧に接続され、第2の p チャネルのトランジスタのゲートとドレインと第2の n チャネルのトランジスタのゲートとドレインと第2の n チャネルのトランジスタのゲートとドレインとがアンプ手段の入力端子に接続されることを特徴とする画像表示装置。

### 【請求項6】

前記アンプ手段がCMOSインバータ回路であることを特徴とする請求項<u>5</u>記載の画像表示装置。

### 【請求項7】

前記バイアス電圧設定手段で設定された直流電圧レベルをクランプするための電圧クランプ手段を備えることを特徴とする請求 5 乃至 6 記載の画像表示装置。

### 【請求項8】

<u>入力部に設けられる容量手段と、前記容量手段により容量結合された入力信号の直流電</u> <u>圧レベルを設定するためのバイアス電圧設定手段と、直流電圧レベルを設定された入力信</u> 号の振幅レベルを増幅するためのアンプ手段とを備えたレベルシフト回路において、

前記バイアス電圧設定手段が正電源電圧と負電源電圧との間に分圧手段を設けることで構成されると共に、前記アンプ手段への入力信号線が1本であり、

<u>前記分圧手段として複数個の p チャネルのトランジスタと複数個の n チャネルのトランジ</u>スタとが用いられ、

各前記 p チャネルのトランジスタは、隣接するもの同士でソースとドレインとが接続されることにより直列に接続され、

各前記pチャネルのトランジスタのゲートは負電源電圧に接続され、

端に位置する前記pチャネルのトランジスタのソースは正電源電圧に接続され、

各前記 n チャネルのトランジスタは、隣接するもの同士でソースとドレインとが接続され て直列に接続され、

端に位置するnチャネルのトランジスタのソースは負電源電圧に接続され、

各前記 n チャネルのトランジスタのゲートは正電源電圧に接続されていることを特徴とするレベルシフト回路。

### 【請求項9】

入力部に設けられる容量手段と、前記容量手段により容量結合された入力信号の直流電圧 レベルを設定するためのバイアス電圧設定手段と、直流電圧レベルを設定された入力信号 の振幅レベルを増幅するためのアンプ手段とを備えたレベルシフト回路を用いた画像表示 装置において、

<u>前記バイアス電圧設定手段が正電源電圧と負電源電圧との間に分圧手段を設けることで構</u>成されると共に、前記アンプ手段への入力信号線が1本であり、

<u>前記分圧手段として複数個の p チャネルのトランジスタと複数個の n チャネルのトランジスタとが用いられ、</u>

各前記 p チャネルのトランジスタは、隣接するもの同士でソースとドレインとが接続されることにより直列に接続され、

各前記pチャネルのトランジスタのゲートは負電源電圧に接続され、

端に位置する前記pチャネルのトランジスタのソースは正電源電圧に接続され、

各前記 n チャネルのトランジスタは、隣接するもの同士でソースとドレインとが接続され て直列に接続され、 10

20

30

端に位置するnチャネルのトランジスタのソースは負電源電圧に接続され、 各前記nチャネルのトランジスタのゲートは正電源電圧に接続されていることを特徴とする画像表示装置。

# 【発明の詳細な説明】

### [0001]

### 【発明の属する技術分野】

本発明は、レベルシフト回路およびそれを用いた画像表示装置に関し、特にドライバモノリシック型(駆動回路一体型)の画像表示装置に内蔵され、低振幅(ロジックレベル)の 入力信号を増幅するためのレベルシフト回路および画像表示装置に関する。

### [0002]

### 【従来の技術】

近年、液晶を用いた表示装置の研究および開発が著しく進んでおり、特に多結晶シリコンを用いたTFT(薄膜トランジスタ:Thin Film Transistor)液晶表示装置について、今後の高い需要が見込まれている。多結晶シリコンを用いたTFT液晶表示装置は、アモルファスシリコンを用いたものと比較して、電子および正孔の移動度が2桁高く、nチャネルTFTとpチャネルTFTとを組み合わせたCMOS構成が可能である。そのため、アモルファスシリコンを用いたTFT液晶表示装置が駆動回路を液晶セル用の画素TFTの基板の外部で、例えば単結晶シリコンを用いて形成しなければならないのに対し、多結晶シリコンを用いて液晶セル用の画素TFTと同一基板上に駆動回路を形成することができる、すなわちドライバモノリシック型のTFT液晶表示装置を形成することができるので、小形化、高機能化および低コスト化の実現が可能となる。

### [0003]

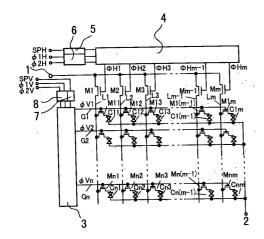

図11は、ドライバモノリシック型のTFT液晶表示装置の構成を示す。図11において、1は外部よりビデオ信号を入力するためのビデオ信号端子、2は対向電極へ電圧を入力するための対向電圧端子、3はn(nはn>1の整数)段のゲートバスライン駆動用のシフトレジスタ、4はm(mはm>1の整数)段のソースバスライン駆動用のシフトレジスタ、5~8は入力制御信号の振幅レベルを増幅するためのレベルシフト回路、SPVははフトレジスタ3へ入力されるスタートパルス、1Vおよび、2Vは水平期間と同じカラレジスタ3より出力される駆動パルス、G1~Gnはゲートバスライン、SPHはシフトレジスタ4へ入力されるスタートパルス、1Hおよび、2Hは水平期間のm倍の周波数であるクロック信号、 H1~ Hmはシフトレジスタ4より出力されるサンプリングするためのサンプリングスイッチ、Lnとゲートバスライン、M1~Mnmはビデオ信号をサンプリングするためのサンプリングスイッチ、L1~Lmはソースバスライン、M11~Mnmは接続された画素電極と対向電極の間に存在する液晶セルである。

# [0004]

図11では、レベルシフト回路5~8として、スタートパルスSPVおよびSPH並びにクロック信号 1 V、 2 V、 1 Hおよび 2 Hの振幅レベルを増幅するための回路を設けている。ドライバモノリシック型のTFT液晶表示装置では、多結晶シリコンを用いて駆動回路を形成しているが、単結晶シリコンを用いて駆動回路を形成しているものと比べてトランジスタのしきい値電圧が高くなる。そこで、スタートパルスSPVおよびSPH並びにクロック信号 1 V、 2 V、 1 Hおよび 2 Hの振幅レベルは、ロジックレベルの電源電圧3 V、3 . 3 Vおよび5 Vなどの電圧では十分高いとは言えず、例えば12~15 Vまで高くする必要があり、そのためにレベルシフト回路5~8 を設けている。

# [0005]

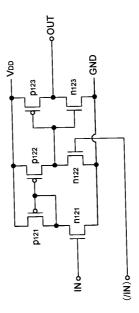

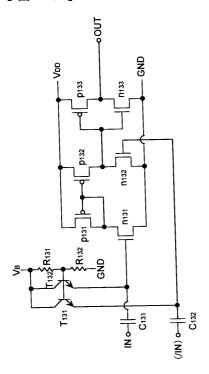

図12は、従来のレベルシフト回路を示す。図12において、VDDは正電源電圧、GNDは負電源電圧、INは入力信号、(/IN)は入力信号INと電圧レベルが反転した関係にある入力信号、OUTは出力信号、p121、p122およびp123はpチャネルTFT、n121、n122およびn123はnチャネルTFTである。

10

20

30

40

20

30

40

50

### [0006]

図12では、入力信号INはnチャネルTFTn121のゲートへ入力され、入力信号(/IN)はnチャネルTFTn122のゲートへ入力される。nチャネルTFTn121のドレインはpチャネルTFTp121のドレインおよびゲート並びにpチャネルTFTp122のゲートと接続され、nチャネルTFTn122のドレインはpチャネルTFTp122のドレインおよびpチャネルTFTp123とnチャネルTFTn123とからなるインバータ回路部の入力端子と接続される。また、pチャネルTFTp121のソースおよびpチャネルTFTp122のソースは正電源電圧VDDと接続され、nチャネルTFTn121のソースおよびnチャネルTFTn122のソースは負電源電圧GNDと接続される。

[0007]

図12に示す従来のレベルシフト回路の動作について説明する。入力信号INがハイレベ ル、入力信号(/IN)がローレベルのとき、nチャネルTFTn121はオンとなり、 n チャネルTFT n 1 2 2 はオフとなる。そうすると、負電源電圧 G N D が p チャネルT FTp121のゲートおよびpチャネルTFTp122のゲートへ入力され、pチャネル TFTp121は抵抗成分とみなされ、正電源電圧VDDおよび負電源電圧GND間で電 流が流れる。一方、pチャネルTFTp122はオンとなり、pチャネルTFTp122 のドレインおよびpチャネルTFTp123とnチャネルTFTn123とからなるイン バータ回路部の入力端子は正電源電圧 V D D に充電され、インバータ回路部の出力端子か らは負電源電圧GNDが出力される。入力信号INがローレベル、入力信号(/IN)が ハイレベルに反転すると、nチャネルTFTn121はオフとなり、nチャネルTFTn 122はオンとなる。そうすると、pチャネルTFTp123とnチャネルTFTn12 3とからなるインバータ回路部の入力端子は負電源電圧GNDに放電され、インバータ回 路部の出力端子からは正電源電圧VDDが出力される。すなわち、入力信号INの振幅レ ベルは、図12に示す従来のレベルシフト回路により増幅されている。(但し、正電源電 圧 V D D と負電源電圧 G N D との電位差は、入力信号 I N の振幅レベルより高く設定され る。)

[00008]

# 【発明が解決しようとする課題】

ここで、図12に示す従来のレベルシフト回路を他の駆動回路と同じように多結晶シリコンを用いて形成する場合、トランジスタのしきい値電圧は単結晶シリコンを用いて形成したものと比べて高くなる。また、トランジスタを形成するプロセスの途上で、しきい値電圧のばらつきが大きくなることがある。トランジスタのしきい値電圧が高くなることはトランジスタのオン抵抗が高くなることに繋がり、pチャネルTFTp121およびp122並びにnチャネルTFTn121およびn122のオン抵抗が高くなると、pチャネルTFTp123とnチャネルTFTn123とからなるインバータ回路部の入力端子を充放電する時定数も高くなることになる。それに対して、スタートパルスSPVおよびSPH並びにクロック信号 1V、 2V、 1Hおよび 2Hの振幅レベルは、ロジックレベルの電源電圧3V、3.3Vおよび5Vなどの電圧では十分高いとは言えず、レベルシフト回路から出力される波形は訛ったもの、または歪んだものになるという問題点があった。

[0009]

そこで、その時定数を小さくするためにトランジスタのチャネル幅を大きくすることが考えられるが、トランジスタのチャネル幅を大きくすればレベルシフト回路の面積の増大に繋がる。また、トランジスタのチャネル幅を大きくすると、そのトランジスタ自身の容量も同時に大きくなるため、トランジスタのチャネル幅を大きくしても、時定数の低減効果はトランジスタのチャネル幅の大きさには比例しないことになる。

### [0010]

このような問題点を解決するための技術としては、例えば、特開平4-242317号公報などが提案されている。図13は、この特開平4-242317号公報で開示されてい

30

40

50

る従来のレベルシフト回路を示す。図13において、VBは正電源電圧、R131およびR132は抵抗、C131およびC132はコンデンサ、T131およびT132はnpn型バイポーラトランジスタ、p131、p132およびp133はpチャネルTFT、n131、n132およびn133はnチャネルTFT、他の構成要素は図12と同様である。

### [0011]

図13では、正電源電圧 V B、負電源電圧 G N D、抵抗 R 1 3 1 および R 1 3 2、 n p n 型バイポーラトランジスタT131およびT132からなる電圧クランプ回路部と、正電源電圧 V D D、負電源電圧 G N D、 p チャネルTFTp131、 p 1 3 2 および p 1 3 3、 n チャネルTFT n 1 3 1、 n 1 3 2 および n 1 3 3 からなるレベルシフト回路部とから構成される。電圧クランプ回路部では、正電源電圧 V B と負電源電圧 G N D とを抵抗 R 1 3 1 および R 1 3 2 で分圧した電圧(この電圧を V B 'と定義する)が n p n 型バイポーラトランジスタT 1 3 1 のベースおよびT 1 3 2 のベースへ入力される。 n p n 型バイポーラトランジスタT 1 3 1 の エミッタはコンデンサ C 1 3 1 の一方の電極および n チャネルTFT n 1 3 2 のゲートと接続され、 n p n 型バイポーラトランジスタT 1 3 2 のゲートと接続される。また、 n p n 型バイポーラトランジスタT 1 3 1 のコレクタおよび T 1 3 2 のコレクタは正電源電圧 V B と接続される。尚、レベルシフト回路部は、図 1 2 に示す従来のレベルシフト回路と同じ構成である。

### [0012]

図13に示す従来のレベルシフト回路の動作について説明する。入力信号INはコンデンサС131により容量結合されてnチャネルTFTn131のゲートへ入力され、入力信号(/IN)はコンデンサС132により容量結合されてnチャネルTFTn132のゲートへ入力される。ここで、電圧クランプ回路部からの電圧により、入力信号INおよび(/IN)の振幅レベルは変わらないが、そのローレベルは電圧VB'から順方向電圧だけ電圧降下した電圧にシフトされる。つまり、レベルシフト回路部を構成するトランジスタのしきい値電圧が高くなった場合においても、入力信号INおよび(/IN)のハイレベルをしきい値電圧より高く設定することが可能となり、トランジスタのオンおよびオフの動作を正常に行うことができる。そして、レベルシフト回路部では、図12に示す従来のレベルシフト回路と同じように、入力信号INの振幅レベルを増幅している。

### [0013]

しかしながら、上記のレベルシフト回路では、電圧レベルが反転した関係にある入力信号INおよび(/IN)の2つの入力信号が必要であるという問題点があった。つまり、図11に示すドライバモノリシック型のTFT液晶表示装置に上記のレベルシフト回路を内蔵する場合、スタートパルスSPVおよびSPHは、シフトレジスタ3および4を駆動するという目的からみると各々の入力制御信号の電圧レベルが反転した関係にある信号は必要ないが、レベルシフト回路では各々の入力制御信号と各々の入力制御信号の電圧レベルが反転した関係にある信号との2つの信号を必要としている。このことは、ドライバモノリシック型のTFT液晶表示装置を形成する場合に外部からの入力信号数が増加するため、外部信号との接続端子数の増加を招くことになる。

# [0014]

また、上記のレベルシフト回路では、電圧クランプ回路部が n p n 型バイポーラトランジスタT131およびT132で構成されており、駆動回路と同一基板上に多結晶シリコンでモノリシックに形成することは困難であるという問題点があった。すなわち、電圧クランプ回路部は外部に用意する必要があり、部品点数の増加をもたらすことになる。

# [0015]

さらに、上記のレベルシフト回路では、レベルシフト回路部を構成する p チャネルTFT p 1 3 1、 p 1 3 2 および p 1 3 3 並びに n チャネルTFT n 1 3 1、 n 1 3 2 および n 1 3 3 のしきい値電圧が変動した場合、トランジスタのしきい値電圧に応じて電圧 V B 'を調整する必要があるという問題点があった。すなわち、トランジスタのしきい値電圧に

合わせて、正電源電圧 V B または抵抗 R 1 3 1 および R 1 3 2 の値を調整しなければならない。一般に、多結晶シリコンを用いて形成されるトランジスタのしきい値電圧のばらつきは単結晶シリコンで形成されるものと比べて大きく、量産化を行う場合、各液晶表示装置毎に電圧 V B 'を調整することは非常に効率が悪くなる。

### [0016]

本発明は、上記問題点を解決するためになされたものであり、1つの入力信号のみで動作し、レベルシフト回路全体を駆動回路と同一基板上に多結晶シリコンを用いてモノリシックに形成することを可能とし、各液晶表示装置毎に電源電圧および抵抗の値を調整する必要がないレベルシフト回路および画像表示装置を提供するものである。

### [0017]

【課題を解決するための手段】

本発明のレベルシフト回路は、入力部に設けられる容量手段と、前記容量手段により容量結合された入力信号の直流電圧レベルを設定するためのバイアス電圧設定手段と、直流電圧レベルを設定された入力信号の振幅レベルを増幅するためのアンプ手段とを備えたレベルシフト回路において、前記バイアス電圧設定手段が正電源電圧と負電源電圧との間に分圧手段を設けることで構成されると共に、前記アンプ手段への入力信号線が1本であり、前記バイアス設定手段は、第1のpチャネルのトランジスタのソースが正電源電圧に接続され、第1のnチャネルのトランジスタのソースが負電源電圧に接続され、第2のpチャネルのトランジスタのゲートとドレインと第2のnチャネルのトランジスタのゲートとドレインと第2のnチャネルのトランジスタのゲートとドレインと第2のnチャネルのトランジスタのゲートとドレインと第2のnチャネルのトランジスタのゲートとドレインとがアンプ手段の入力端子に接続されることを特徴としている。

### [0018]

本発明のレベルシフト回路は、前記アンプ手段がCMOSインバータ回路であることを特徴としている。

### [0020]

本発明のレベルシフト回路は、前記分圧手段として、容量を用いることを特徴としている

# [0025]

本発明のレベルシフト回路は、前記バイアス電圧設定手段で設定された直流電圧レベルをクランプするための電圧クランプ手段を備えることを特徴としている。

### [0026]

本発明のレベルシフト回路は、前記バイアス電圧設定手段で設定された直流電圧レベルが 前記電圧クランプ手段によりクランプするときに、電圧降下した電圧を補償する手段を備 えることを特徴としている。

# [0027]

本発明の画像処理装置は、入力部に設けられる容量手段と、前記容量手段により容量結合された入力信号の直流電圧レベルを設定するためのバイアス電圧設定手段と、直流電圧レベルを設定された入力信号の振幅レベルを増幅するためのアンプ手段とを備えたレベルシフト回路を用いた画像表示装置において、前記バイアス電圧設定手段が正電源電圧と負電源電圧との間に分圧手段を設けることで構成されると共に、前記アンプ手段への入力信号線が1本であり、前記バイアス設定手段は、第1のpチャネルのトランジスタのソースが正電源電圧に接続され、第1のnチャネルのトランジスタのソースが負電源電圧に接続され、第2のpチャネルのトランジスタのゲートとドレインと第2のnチャネルのトランジスタのゲートとドレインとがアンプ手段の入力端子に接続されることを特徴としている。

### [0028]

本発明の画像表示装置は、前記アンプ手段がCMOSインバータ回路であることを特徴としている。

### [0032]

本発明の画像表示装置は、前記バイアス電圧設定手段で設定された直流電圧レベルをクランプするための電圧クランプ手段を備えることを特徴としている。

本発明のレベルシフト回路は、入力部に設けられる容量手段と、前記容量手段により容量

20

10

30

30

40

50

結合された入力信号の直流電圧レベルを設定するためのバイアス電圧設定手段と、直流電圧レベルを設定された入力信号の振幅レベルを増幅するためのアンプ手段とを備えたレベルシフト回路において、前記バイアス電圧設定手段が正電源電圧と負電源電圧との間に分圧手段を設けることで構成されると共に、前記アンプ手段への入力信号線が1本であり、前記分圧手段として複数個の p チャネルのトランジスタと複数個の n チャネルのトランジスタとが用いられ、各前記 p チャネルのトランジスタは、隣接するもの同土でソースとドレインとが接続されることにより直列に接続され、各前記 p チャネルのトランジスタのゲートは負電源電圧に接続され、端に位置する前記 p チャネルのトランジスタのソースは正電源電圧に接続され、各前記 n チャネルのトランジスタは、隣接するもの同土でソースとドレインとが接続されて直列に接続され、端に位置する n チャネルのトランジスタのソースは負電源電圧に接続され、各前記 n チャネルのトランジスタのゲートは正電源電圧に接続されて1000とを特徴としている。

### [0033]

以下、上記構成による作用を説明する。

### [0034]

本発明のレベルシフト回路および画像表示装置は、バイアス電圧設定手段が正電源電圧と負電源電圧との間に分圧手段を設けることで構成されるため、簡単な回路構成でバイアス電圧設定手段を実現することができると共に、入力信号の直流電圧レベルを容易にアンプ手段の動作点の範囲にシフトすることができる。また、アンプ手段の入力端子が1つの端子から構成されるため、レベルシフト回路への入力信号線数が少なくてすむと共に、簡単な回路構成でアンプ手段を実現することができる。

# [0035]

本発明のレベルシフト回路および画像表示装置は、アンプ手段がCMOSインバータ回路であるため、pチャネルのトランジスタとnチャネルのトランジスタを用いた簡単な構成でアンプ手段を実現することができる。

# [0036]

本発明のレベルシフト回路および画像表示装置は、分圧手段として p チャネルのトランジスタと n チャネルのトランジスタを用いるため、入力信号の直流電圧レベルをトランジスタのオン抵抗比により容易に設定することができる。また、単結晶シリコンと比べてしきい値電圧にばらつきのある多結晶シリコンでレベルシフト回路全体を同一基板上に形成することができる。つまり、レベルシフト回路を含めたドライバモノリシック型の画像表示装置を実現することが可能となる。

# [0037]

本発明のレベルシフト回路および画像表示装置は、分圧手段として容量を用いるため、入力信号の直流電圧レベルを容量の面積比により容易に設定することができる。容量は多結晶シリコン上にも簡単に構成できるため、レベルシフト回路全体を同一基板上に形成することができる。つまり、レベルシフト回路を含めたドライバモノリシック型の画像表示装

置を実現することが可能となる。

### [0038]

本発明のレベルシフト回路および画像表示装置は、分圧手段として抵抗体を用いるため、 入力信号の直流電圧レベルを抵抗比により容易に設定することができると共に、レベルシ フト回路全体を同一基板上に形成することができる。つまり、レベルシフト回路を含めた ドライバモノリシック型の画像表示装置を実現することが可能となる。

### [0039]

本発明のレベルシフト回路および画像表示装置は、バイアス電圧設定手段の構成として、 pチャネルのトランジスタのソースとnチャネルのトランジスタのゲートとが正電源電圧 に接続され、pチャネルのトランジスタのゲートとnチャネルのトランジスタのソースと が負電源電圧に接続され、pチャネルのトランジスタのドレインとnチャネルのトランジ スタのドレインとがアンプ手段の入力端子に接続されるため、レベルシフト回路を構成す るトランジスタのしきい値電圧が変動してアンプ手段の動作点がシフトしても、それに追 従して入力信号の直流電圧レベルを自動的に設定することができる。

### [0040]

本発明のレベルシフト回路および画像表示装置は、バイアス電圧設定手段の構成として、 pチャネルのトランジスタのソースが正電源電圧に接続され、nチャネルのトランジスタ のソースが負電源電圧に接続され、pチャネルのトランジスタのゲートとドレインとnチャネルのトランジスタのゲートとドレインとがアンプ手段の入力端子に接続されるため、 レベルシフト回路を構成するトランジスタのしきい値電圧が変動してアンプ手段の動作点 がシフトしても、入力信号の直流電圧レベルの設定を容易に行うことができる。

### [0041]

本発明のレベルシフト回路および画像表示装置は、pチャネルのトランジスタとnチャネルのトランジスタは各々複数個を用いて前記分圧手段を構成するため、各々のトランジスタのソース・ドレイン端子間にかかる電界によるストレスを低減することができる。また、トランジスタの数により入力信号の直流電圧レベルを決められるので、設定の自由度を高くすることができる。

### [0042]

本発明のレベルシフト回路および画像表示装置は、バイアス電圧設定手段で設定された直流電圧レベルをクランプするための電圧クランプ手段を備えるため、入力信号の周波数、バイアス電圧設定手段を構成するトランジスタおよび入力部に設けられる容量手段に関わらず、入力信号の波形の歪みを防ぐことができる。そのため、設計の自由度を高くすることも可能である。

# [0043]

本発明のレベルシフト回路および画像表示装置は、バイアス電圧設定手段で設定された直流電圧レベルが前記電圧クランプ手段によりクランプするときに、電圧降下した電圧を補償する手段を備えるため、入力信号の直流電圧レベルをバイアス電圧設定手段で容易に設定することができる。

# [0044]

### 【発明の実施の形態】

本発明の実施の形態について以下に説明する。

### [0045]

### (実施の形態1)

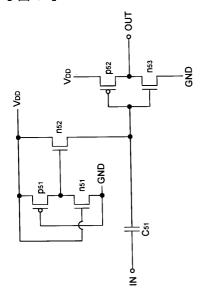

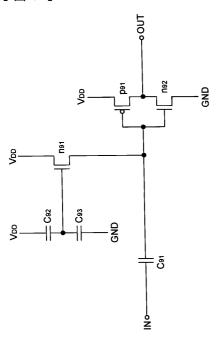

図1は、本発明の実施の形態1における画像表示装置に用いるレベルシフト回路を示す。 図1において、VDDは正電源電圧、GNDは負電源電圧、INは入力信号、OUTは出力信号、C11はコンデンサ、p11およびp12はpチャネルTFT、n11およびn 12はnチャネルTFTである。

### [0046]

図 1 では、正電源電圧 V D D 、 負電源電圧 G N D 、 p チャネル T F T p 1 1 、 n チャネル T F T n 1 1 からなるバイアス電圧設定部と、正電源電圧 V D D 、 負電源電圧 G N D 、 p

10

20

\_\_

30

40

20

30

40

50

チャネルTFTp12、nチャネルTFTn12からなるアンプ回路部とから構成される。バイアス電圧設定部では、pチャネルTFTp11のドレインとnチャネルTFTn11のドレインとが接続されると共にコンデンサC11の一方の電極と接続され、pチャネルTFTp11のソースおよびnチャネルTFTn11のゲートは正電源電圧VDDと接続され、pチャネルTFTn11のソースは負電源電圧GNDと接続される。アンプ回路部では、pチャネルTFTp12のゲートとnチャネルTFTn12のゲートとが接続されると共にコンデンサC11の一方の電極と接続され(アンプ回路部の入力端子となる)、pチャネルTFTp12のドレインとnチャネルTFTn12のドレインとが接続され(アンプ回路部の出力端子となる)、pチャネルTFTn12のソースは正電源電圧VDDと接続され、nチャネルTFTn12のソースは負電源電圧GNDと接続される。

### [0047]

図1に示す本発明の実施の形態1におけるレベルシフト回路の動作について説明する。入力信号INはコンデンサC11により容量結合されてアンプ回路部の入力端子へ入力によって決定されるバイアス電圧(この電圧をVbと定義する)により、入力信号INの比にはして決定されるバイアス電圧(この電圧をVbと定義する)により、入力信号INの比に幅レベルは変わらないが、その振幅レベルの中心電圧はバイアス電圧Vbにシフトされる。つまり、そのバイアス電圧Vbを正しく設定することにより、アンプ回路部の動作を正常に行うことができる。そして、アンプ回路部では、入力信号INがハイレベルのとき、ウチャネルTFTp12はオフとなり、nチャネルTFTn12はオンとなり、アンプ回路部の出力端子からは負電源GNDが出力される。入力信号INがローレベルのとき、pチャネルTFTp12はオンとなり、nチャネルTFTn12はオフとなり、アンプ回路の出力端子からは正電源VDDが出力される。すなわち、入力信号INの振幅レベルはの出力に示す本発明の実施の形態1におけるレベルシフト回路により増幅されている。(但し、正電源電圧VDDと負電源電圧GNDとの電位差は、入力信号INの振幅レベルより高く設定される。)

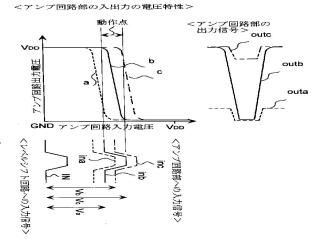

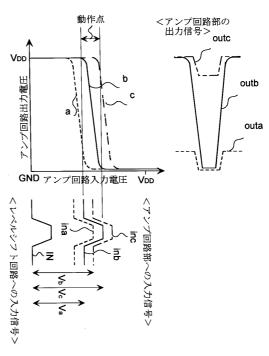

図2は、本発明の実施の形態1におけるレベルシフト回路の入出力の関係を示す。入力信号INの振幅レベルの中心電圧はバイアス電圧Vbにシフトされ、信号inbとなり、アンプ回路部の入力端子へ入力される。そして、アンプ回路部の入出力の電圧特性が波形bのような特性で、信号inbの振幅レベルがアンプ回路部の出力電圧を正電源電圧VDDから負電源電圧GNDへ反転するような入力電圧の動作点の範囲となれば、アンプ回路部の出力端子からは信号outbが出力される。

### [0048]

ここで、レベルシフト回路を構成する p チャネル T F T のしきい値電圧の絶対値が n チャネル T F T のしきい値電圧の絶対値に対して小さくなった場合、アンプ回路部の入出力の電圧特性は波形 c のような特性になり、動作点が正電源電圧 V D D 側にシフトされる。その場合でも、アンプ回路部の入力端子へ入力される信号が信号 i n b のままであれば、アンプ回路部の出力端子からは信号 o u t c が出力され、振幅レベルの十分な変換が行われないことになる。しかしながら、 p チャネル T F T のしきい値電圧の絶対値が n チャネル T F T のしきい値電圧の絶対値に対して小さくなった場合、 p チャネル T F T p 1 1 のオン抵抗は n チャネル T F T n 1 1 のオン抵抗より値が低くなるため、バイアス電圧設定部により決定されるバイアス電圧は V b より正電源電圧 V D D 側にシフトされ V c となり、アンプ回路部の入力端子へ入力される信号が信号 i n c となる。その結果、アンプ回路の出力端子からは信号 o u t b が出力される。

### [0049]

上述とは逆に、レベルシフト回路を構成する p チャネルTFTのしきい値電圧の絶対値が n チャネルTFTのしきい値電圧の絶対値に対して大きくなった場合、アンプ回路部の入出力の電圧特性は波形 a のような特性になり、動作点が負電源電圧 G N D 側にシフトされる。その場合は、 p チャネルTFT p 1 1 のオン抵抗は n チャネルTFT n 1 1 のオン抵抗より値が高くなるため、バイアス電圧設定部により決定されるバイアス電圧は V b より

20

50

負電源電圧GND側にシフトされVaとなり、アンプ回路部の入力端子へ入力される信号が信号inaとなる。その結果、アンプ回路の出力端子からは、信号outaではなく信号outbが出力される。

[0050]

つまり、本発明の実施の形態 1 におけるレベルシフト回路では、レベルシフト回路を構成するトランジスタのしきい値電圧が変動してアンプ回路部の動作点がシフトしても、それに追従してバイアス電圧がバイアス電圧設定部で自動的に設定されることになる。

[0051]

尚、図1に示す本発明の実施の形態1におけるレベルシフト回路では、pチャネルTFTおよびnチャネルTFTを各々1つずつでバイアス電圧設定部を構成しているが、pチャネルTFTおよびnチャネルTFTを両方またはいずれか一方を2つ以上で構成しても良い。

[0052]

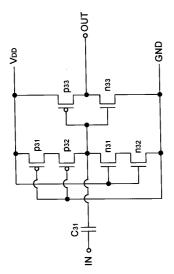

図 3 は、本発明の実施の形態 1 におけるレベルシフト回路の別の例を示す。図 3 において、 C 3 1 はコンデンサ、 p 3 1 、 p 3 2 および p 3 3 は p チャネル T F T 、 n 3 1 、 n 3 2 および n 3 3 は n チャネル T F T 、他の構成要素は図 1 と同様である。

[0053]

図3では、図1に示す本発明の実施の形態1におけるレベルシフト回路と比べて、バイアス電圧設定部が各々2つのpチャネルTFTおよびnチャネルTFTから構成される点が異なる。このようにすることで、各トランジスタの端子間にかかる電圧を低減できるため、トランジスタのソース・ドレイン端子間にかかる電界によるストレス低減効果が期待できる。また、pチャネルTFTおよびnチャネルTFTの個数の比でもバイアス電圧を決めることが可能となり、バイアス電圧の設定の自由度が増すことになる。

[0054]

(実施の形態2)

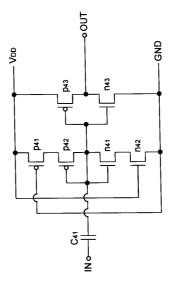

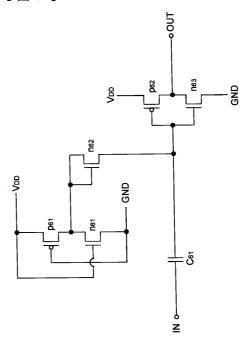

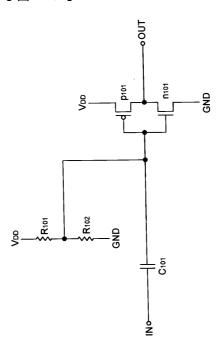

図 4 は、本発明の実施の形態 2 における画像表示装置に用いるレベルシフト回路を示す。 図 4 において、 C 4 1 はコンデンサ、 p 4 1 、 p 4 2 および p 4 3 は p チャネル T F T 、 n 4 1 、 n 4 2 および n 4 3 は n チャネル T F T 、他の構成要素は図 1 と同様である。

[0055]

図4では、図3に示す本発明の実施の形態1におけるレベルシフト回路と比べて、バイアス電圧設定部を構成する p チャネルTFT p 4 2 のゲートと n チャネルTFT n 4 1 のドレインおよび n チャネルTFT n 4 1 のドレインと接続される点が異なる。

[0056]

ここで、図2および図3に示す実施の形態1におけるレベルシフト回路では、トランジスタのしきい値電圧の変動によるアンプ回路部の動作点のシフト量およびバイアス電圧設定部からのバイアス電圧のシフト方向は一致するが、一般的にバイアス電圧のシフト量がアンプ回路部の動作点よりも大きくなる。そのため、バイアス電圧のシフト量が大きくなりすぎると、入力信号INの振幅レベルがアンプ回路部の動作点の範囲とずれる可能性がある。一方、図4に示す本発明の実施の形態2におけるレベルシフト回路では、バイアス電圧設定部からのバイアス電圧がpチャネルTFTp42のゲートおよびnチャネルTFTn41のゲートにフィードバックされ、トランジスタのしきい値電圧の変動によるバイアス電圧のシフト量を補償することができる。

[0057]

その補償効果について詳しく説明する。レベルシフト回路を構成する p チャネルTFTのしきい値電圧の絶対値が n チャネルTFTのしきい値電圧の絶対値に対して小さくなった場合、 p チャネルTFT p 4 1 および p 4 2 のオン抵抗は n チャネルTFT n 4 1 および n 4 2 のオン抵抗より値が低くなるため、バイアス電圧は正電源電圧 V D D 側にシフトされる。しかしながら、バイアス電圧設定部からのバイアス電圧は、 p チャネルTFT p 4 2 のゲートおよび n チャネルTFT n 4 1 のゲートにフィードバックされるため、正電源

30

40

50

電圧 VDD側にシフトされたバイアス電圧により n チャネルTFT n 4 1 のオン抵抗の値が低くなるように働く。その結果、バイアス電圧のシフト量は、図 2 および図 3 に示す実施の形態 1 におけるレベルシフト回路と比べて小さくなる。上述とは逆に、レベルシフト回路を構成する p チャネルTFTのしきい値電圧の絶対値が n チャネルTFTのしきい値電圧の絶対値に対して大きくなった場合、バイアス電圧は負電源電圧 G N D 側にシフトされるが、 p チャネルTFT p 4 2 オン抵抗の値が低くなるように働く。その結果、上述と同様に、バイアス電圧のシフト量は、図 2 および図 3 に示す実施の形態 1 におけるレベルシフト回路と比べて小さくなる。

### [0058]

つまり、本発明の実施の形態 2 におけるレベルシフト回路では、レベルシフト回路を構成するトランジスタのしきい値電圧が変動してアンプ回路部の動作点がシフトする場合、バイアス電圧設定部からのバイアス電圧をアンプ回路部のシフト量に合わせて設定することが容易になる。

# [0059]

尚、図4に示す本発明の実施の形態2におけるレベルシフト回路では、pチャネルTFTおよびnチャネルTFTを各々2つずつでバイアス電圧設定部を構成しているが、pチャネルTFTおよびnチャネルTFTを両方またはいずれか一方を3つ以上で構成しても良い。また、pチャネルTFTおよびnチャネルTFTを両方またはいずれか一方を1つで構成しても良い。すなわち、図4に示す本発明の実施の形態2におけるレベルシフト回路からpチャネルTFTp41またはnチャネルTFTn42を取り除いた構成としても良い。

### [0060]

# (実施の形態3)

図 5 は、本発明の実施の形態 3 における画像表示装置に用いるレベルシフト回路を示す。図 5 において、C 5 1 はコンデンサ、p 5 1 およびp 5 2 はp チャネルTFT、n 5 1 、n 5 2 およびn 5 3 はn チャネルTFT、他の構成要素は図 1 と同様である。

# [0061]

図5では、図1に示す本発明の実施の形態1におけるレベルシフト回路と比べて、バイアス電圧設定部の出力端子とアンプ回路部の入力端子との間に電圧クランプ用のnチャネルTFTn52が設けられている点が異なる。nチャネルTFTn52のドレインは、アンプ回路部の入力端子となるpチャネルTFTp52のゲートとnチャネルTFTn53のゲートと接続されると共にコンデンサC51の一方の電極と接続される。また、nチャネルTFTn52のゲートはバイアス電圧設定部の出力端子となるpチャネルTFTp51のドレインおよびnチャネルTFTn51のドレインおよびnチャネルTFTn52のソースは正電源電圧VDDと接続される。

### [0062]

の関係式が成り立つようにしなければならない。そうでないと、アンプ回路部の入力端子 で信号波形が歪んだものとなり、レベルシフト回路が正常に動作しなくなる。

### [0063]

尚、入力信号 I N の周波数 f H z から f / 1 0 H z になった場合、上式を満たすためには、コンデンサ C 1 1 の値を 1 0 倍、または p チャネル T F T p 1 1 のオン抵抗 R p 1 1 および n チャネル T F T n 1 1 のオン抵抗 R n 1 1 の値を 1 0 倍にする必要がある。すなわ

ち、入力信号 INの周波数におけるコンデンサ C11のインピーダンス Zc11とバイアス電圧設定部のトランジスタのオン抵抗との比を十分に大きくするために、コンデンサのサイズを大きくして容量を増やすか、またはバイアス電圧設定部を構成するトランジスタの数を多くしてトランジスタのオン抵抗を高くしなければならない。しかしながら、コンデンサのサイズを大きくしたり、トランジスタの数を増やすことは、レベルシフト回路の規模の増大につながるため必ずしも好ましくない。また、pチャネル TFTp11のオン抵抗 Rp11および nチャネル TFTn11のオン抵抗 Rn11の値を高くするため、トランジスタのサイズを調整する方法も考えられるが、トランジスタの設計ルールを考慮すると、トランジスタのオン抵抗の値を一定以上にすることは困難である。

### [0064]

一方、図5に示す本発明の実施の形態3におけるレベルシフト回路では、入力信号INのローレベルがpチャネルTFTp51のオン抵抗とnチャネルTFTn51のオン抵抗との比で設定された電圧から、nチャネルTFTn52のしきい値電圧だけ電圧降下した電圧V'にシフトされる。もし、入力信号INのローレベルが電圧V'よりも低くなる方向で動作しても、nチャネルTFTn52を介して、アンプ回路部を構成するpチャネルTFTp52のゲートおよびnチャネルTFTn53のゲート並びにコンデンサC51を充電することになり、常に電圧V'より低くなることはなく、電圧V'にクランプされる。そして、入力信号INの振幅レベルがアンプ回路部の動作点の範囲となるように、入力信号のローレベル、すなわち電圧V'を設定すれば良い。

### [0065]

つまり、本発明の実施の形態3におけるレベルシフト回路では、入力信号のローレベルを電圧クランプすることにより、入力信号の波形が歪むことなくアンプ回路部へ入力されるため、バイアス電圧設定部を構成するpチャネルTFTおよびnチャネルTFTのオン抵抗の値、コンデンサの容量の調整が不要となり、設計時の自由度が増すことになる。

### [0066]

図 6 は、本発明の実施の形態 3 におけるレベルシフト回路の別の例を示す。図 6 において、 C 6 1 はコンデンサ、 p 6 1 および p 6 2 は p チャネルTFT、 n 6 1 、 n 6 2 および n 6 3 は n チャネルTFT、他の構成要素は図 1 と同様である。

# [0067]

図6では、図5に示す本発明の実施の形態3におけるレベルシフト回路と比べて、バイアス電圧設定部の出力端子とアンプ回路部の入力端子との間に設けられる電圧クランプ用の n チャネルTFT n 6 2 のゲートとソースとが接続される点が異なる。このようにすることで、 n チャネルTFT n 6 2 はダイオードとして機能し、入力信号INのローレベルが p チャネルTFT p 6 1 のオン抵抗と n チャネルTFT n 6 1 のオン抵抗との比で設定された電圧から、 n チャネルTFT n 6 2 のしきい値電圧だけ電圧降下した電圧にシフトされる。

# [0068]

尚、本発明の実施の形態3におけるレベルシフト回路では、pチャネルTFTおよびnチャネルTFTを各々1つずつでバイアス電圧設定部を構成しているが、pチャネルTFTおよびnチャネルTFTを両方またはいずれか一方を2つ以上で構成しても良い。

# [0069]

また、本発明の実施の形態3におけるレベルシフト回路では、電圧クランプ用としてnチャネルTFTを用いているが、pチャネルTFTを用いても良い。

# [0070]

### (実施の形態4)

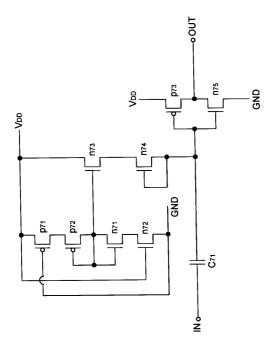

図 7 は、本発明の実施の形態 4 における画像表示装置に用いるレベルシフト回路を示す。図 7 において、C 7 1 はコンデンサ、p 7 1、p 7 2 およびp 7 3 はp チャネルTFT、n 7 1、n 7 2、n 7 3、n 7 4 およびn 7 5 はn チャネルTFT、他の構成要素は図 1 と同様である。

# [0071]

40

10

20

20

30

40

50

図 7 では、図 4 に示す本発明の実施の形態 2 におけるレベルシフト回路と比べて、バイアス電圧設定部の出力端子とアンプ回路部の入力端子との間に電圧クランプ用の n チャネルTFT n 7 3 および n チャネルTFT n 7 4 が設けられている点が異なる。 n チャネルTFT n 7 3 のドレインと n チャネルTFT n 7 4 のソースとが接続され、 n チャネルTFT n 7 2 のゲートは、 p チャネルTFT p 7 2 のゲートおよび n チャネルTFT n 7 2 のドレインと接続されると共に p チャネルTFT p 7 2 のドレインおよび n チャネルTFT n 7 2 のドレインと接続される。また、 n チャネルTFT n 7 3 のソースは正電源電圧 V D Dと接続され、 n チャネルTFT n 7 4 のゲートとドレインとが接続されると共に、 アンプ回路部の入力端子となる p チャネルTFT p 7 3 のゲートおよび n チャネルTFT n 7 5 のゲート並びにコンデンサ C 7 1 の一方の電極と接続される。

[0072]

ここで、図7に示す本発明の実施の形態4におけるレベルシフト回路の電圧クランプのレベルについて考える。バイアス電圧設定部からのバイアス電圧は、nチャネルTFTn73のしきい値電圧だけ電圧降下した電圧がnチャネルTFTn73のドレインより出力される。そして、nチャネルTFTn74のゲートとドレインとが接続されるため、nチャネルTFTn73のドレインより出力される電圧は、nチャネルTFTn74のしきい値電圧だけ高くなる。

[0073]

つまり、本発明の実施の形態 4 におけるレベルシフト回路では、電圧クランプ用のトランジスタを 2 つ設け、最初のトランジスタのしきい値電圧だけ電圧降下した電圧を次のトランジスタで補償することにより、バイアス電圧設定部で設定された電圧で入力信号のローレベルを電圧クランプすることができるため、バイアス電圧の設定が容易になる。

[0074]

尚、本発明の実施の形態 4 におけるレベルシフト回路では、バイアス電圧設定部を本発明の実施の形態 2 におけるレベルシフト回路のバイアス電圧設定部と同じ構成としているが、本発明の実施の形態 1 におけるレベルシフト回路のバイアス電圧設定部と同じ構成としても良い。

[0075]

また、本発明の実施の形態4におけるレベルシフト回路では、pチャネルTFTおよびnチャネルTFTを各々2つずつでバイアス電圧設定部を構成しているが、pチャネルTFTおよびnチャネルTFTを両方またはいずれか一方を3つ以上で構成しても良い。

[0076]

さらに、本発明の実施の形態4におけるレベルシフト回路では、電圧クランプ用としてn チャネルTFTを用いているが、pチャネルTFTを用いても良い。

[0077]

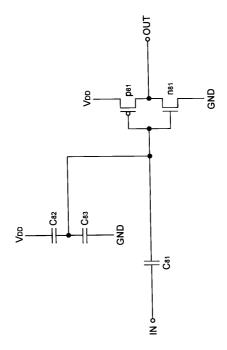

(実施の形態5)

図8~図10は、本発明の実施の形態5における画像表示装置に用いるレベルシフト回路を示す。レベルシフト回路を構成するpチャネルTFTおよびnチャネルTFTのしきい値電圧の変動が小さく、アンプ回路部の動作点の範囲の変動が小さい場合、バイアス電圧設定部からのバイアス電圧をトランジスタのしきい値電圧に合わせる必要はなく、固定することが可能である。従って、図8~図10に示す本発明の実施の形態5におけるレベルシフト回路が考えられる。

[0078]

図8において、C81、C82およびC83はコンデンサ、p81はpチャネルTFT、n81はnチャネルTFT、他の構成要素は図1と同様である。図8では、図1に示す本発明の実施の形態1におけるレベルシフト回路と比べて、トランジスタを容量に置き換えた点が異なる。バイアス電圧はコンデンサC82とコンデンサC83との容量比に応じて設定される。

[0079]

図9において、С91、С92およびС93はコンデンサ、р91はpチャネルTFT、

20

30

40

50

n91およびn92はnチャネルTFT、他の構成要素は図1と同様である。図9では、図5に示す本発明の実施の形態3におけるレベルシフト回路と比べて、トランジスタを容量に置き換える点が異なる。コンデンサC92とコンデンサC93との容量比に応じて設定されるバイアス電圧は、nチャネルTFTn91のしきい値電圧だけ電圧降下した電圧により電圧クランプされる。

### [0800]

図10において、C101はコンデンサ、R101、R102は抵抗、p101はpチャネルTFT、n101はnチャネルTFT、他の構成要素は図1と同様である。図10では、図1に示す本発明の実施の形態1におけるレベルシフト回路と比べて、トランジスタを抵抗に置き換える点が異なる。バイアス電圧は抵抗R101と抵抗102との抵抗比に応じて設定される。

### [0081]

図8~図10に示す本発明の実施の形態5におけるレベルシフト回路では、コンデンサまたは抵抗を用いてバイアス電圧設定部を構成しているため、トランジスタの特性による影響を受けずにバイアス電圧を安定にかつ容易に設定できる。

### [0082]

尚、本発明の実施の形態 5 におけるレベルシフト回路では、コンデンサを用いたバイアス電圧設定部とアンプ回路部との間に電圧クランプ用のトランジスタを設けているが、抵抗を用いたバイアス電圧設定部とアンプ回路部との間に電圧クランプ用のトランジスタを設けても良いし、本発明の実施の形態 4 におけるレベルシフト回路のように電圧クランプ用のトランジスタを 2 つ設けても良い。

### [0083]

また、本発明の実施の形態 5 におけるレベルシフト回路では、コンデンサまたは抵抗を正電源電圧側と負電源電圧側とに各々 1 つずつでバイアス電圧設定部を構成しているが、正電源電圧側と負電源電圧側との両方またはいずれか一方を 2 つ以上で構成しても良い。

### [0084]

本発明の実施の形態におけるレベルシフト回路では、多結晶シリコンとして、連続粒界結晶性シリコンを用いても良い。

# [0085]

また、本発明の実施の形態におけるレベルシフト回路では、入力信号の振幅レベルの増幅 手段であるアンプ回路部として、入力信号に対して反転した信号を出力するためのCMO Sインバータ回路を用いているが、入力信号に対して反転しない信号を出力する回路手段 を用いても良い。

# [0086]

### 【発明の効果】

以上説明したように、本発明のレベルシフト回路および画像表示装置においては、以下のような効果を奏する。

### [0087]

本発明のレベルシフト回路および画像表示装置には、バイアス電圧設定手段が正電源電圧と負電源電圧との間に分圧手段を設けることで構成されるため、簡単な回路構成でバイアス電圧設定手段を実現することができると共に、入力信号の直流電圧レベルを容易にアンプ手段の動作点の範囲にシフトすることができる。また、アンプ手段の入力端子が1つの端子から構成されるため、レベルシフト回路への入力信号線数が少なくてすむと共に、簡単な回路構成でアンプ手段を実現することができる。

# [0088]

本発明のレベルシフト回路および画像表示装置には、アンプ手段がCMOSインバータ回路であるため、pチャネルのトランジスタとnチャネルのトランジスタを用いた簡単な構成でアンプ手段を実現することができる。

### [0089]

本発明のレベルシフト回路および画像表示装置には、分圧手段としてpチャネルのトラン

ジスタとn チャネルのトランジスタを用いるため、入力信号の直流電圧レベルをトランジスタのオン抵抗比により容易に設定することができる。また、単結晶シリコンに比べて V t h ばらつきのある多結晶シリコンでレベルシフト回路全体を同一基板上に形成することができる。つまり、レベルシフト回路を含めたドライバモノリシック型の画像表示装置を実現することが可能となる。

### [0090]

本発明のレベルシフト回路および画像表示装置は、分圧手段として容量を用いるため、入力信号の直流電圧レベルを容量の面積比により容易に設定することができる。容量は多結晶シリコン上にも簡単に構成できるため、レベルシフト回路全体を同一基板上に形成することができる。つまり、レベルシフト回路を含めたドライバモノリシック型の画像表示装置を実現することが可能となる。

### [0091]

本発明のレベルシフト回路および画像表示装置は、分圧手段として抵抗体を用いるため、 入力信号の直流電圧レベルを抵抗比により容易に設定することができると共に、レベルシ フト回路全体を同一基板上に形成することができる。つまり、レベルシフト回路を含めた ドライバモノリシック型の画像表示装置を実現することが可能となる。

### [0092]

本発明のレベルシフト回路および画像表示装置は、バイアス電圧設定手段の構成として、 p チャネルのトランジスタのソースと n チャネルのトランジスタのゲートとが正電源電圧 に接続され、 p チャネルのトランジスタのゲートと n チャネルのトランジスタのソースと が負電源電圧に接続され、 p チャネルのトランジスタのドレインと n チャネルのトランジスタのドレインとがアンプ手段の入力端子に接続されるため、レベルシフト回路を構成するトランジスタのしきい値電圧が変動してアンプ手段の動作点がシフトしても、それに追従して入力信号の直流電圧レベルを自動的に設定することができる。

# [0093]

本発明のレベルシフト回路および画像表示装置は、バイアス電圧設定手段の構成として、 pチャネルのトランジスタのソースが正電源電圧に接続され、nチャネルのトランジスタ のソースが負電源電圧に接続され、pチャネルのトランジスタのゲートとドレインとnチャネルのトランジスタのゲートとドレインとがアンプ手段の入力端子に接続されるため、 レベルシフト回路を構成するトランジスタのしきい値電圧が変動してアンプ手段の動作点 がシフトしても、入力信号の直流電圧レベルの設定を容易に行うことができる。

# [0094]

本発明のレベルシフト回路および画像表示装置は、pチャネルのトランジスタとnチャネルのトランジスタは各々複数個を用いて前記分圧手段を構成するため、各々のトランジスタのソース・ドレイン端子間にかかる電界によるストレスを低減することができる。また、トランジスタの数により入力信号の直流電圧レベルを決められるので、設定の自由度を高くすることができる。

### [0095]

本発明のレベルシフト回路および画像表示装置は、バイアス電圧設定手段で設定された直流電圧レベルをクランプするための電圧クランプ手段を備えるため、入力信号の周波数、バイアス電圧設定手段を構成するトランジスタおよび入力部に設けられる容量手段に関わらず、入力信号の波形の歪みを防ぐことができる。そのため、設計の自由度を高くすることも可能である。

# [0096]

本発明のレベルシフト回路および画像表示装置は、バイアス電圧設定手段で設定された直流電圧レベルが前記電圧クランプ手段によりクランプするときに、電圧降下した電圧を補償する手段を備えるため、入力信号の直流電圧レベルをバイアス電圧設定手段で容易に設定することができる。

### 【図面の簡単な説明】

【図1】本発明の実施の形態1におけるレベルシフト回路を示す図である。

20

10

30

40

- 【図2】本発明の実施の形態1におけるレベルシフト回路の入出力の関係を示す図である

- 【図3】本発明の実施の形態1におけるレベルシフト回路の別の例を示す図である。

- 【図4】本発明の実施の形態2におけるレベルシフト回路を示す図である。

- 【図5】本発明の実施の形態3におけるレベルシフト回路を示す図である。

- 【図6】本発明の実施の形態3におけるレベルシフト回路の別の例を示す図である。

- 【図7】本発明の実施の形態4におけるレベルシフト回路を示す図である。

- 【図8】本発明の実施の形態5におけるレベルシフト回路を示す図である。

- 【図9】本発明の実施の形態5におけるレベルシフト回路の別の例を示す図である。

- 【図10】本発明の実施の形態5におけるレベルシフト回路の別の例を示す図である。

- 【図11】ドライバモノリシック型のTFT液晶表示装置の構成を示す図である。

- 【図12】従来のレベルシフト回路を示す図である。

- 【図13】特開平4-242317号公報に開示されている、従来のレベルシフト回路を 示す図である。

### 【符号の説明】

- ビデオ信号端子

- 2 対向電圧端子

- n 段のシフトレジスタ

- 4 m段のシフトレジスタ

- 5~8 レベルシフト回路

- SPV ゲート用のスタートパルス

- 2 V 水平周波数のクロック信号

- Vn ゲートバスラインの駆動パルス

- G1~Gn ゲートバスライン

- SPH ソース用のスタートパルス

- 2 H 水平周波数のm倍の周波数のクロック信号

- H1~ Hm サンプリングパルス

- M1~Mm サンプリングスイッチ

- L1~Lm ソースバスライン

- M 1 1 ~ M n m T F T 素子

- C11~Cnm 液晶セル

- VDD、VB 正電源電圧

- GND 負電源電圧

- IN 入力信号

- (/IN) 入力信号INと電圧レベルが反転した関係にある入力信号

- OUT 出力信号

- p 1 1 、p 1 2 、p 3 1 ~ p 3 3 、p 4 1 ~ p 4 3 、p 5 1 、p 5 2 、p 6 1 、p 6 2 、

- p71~p73、p81、p91、p101、p121~p123、p131~p133 pチャネルTFT

- n 1 1 、 n 1 2 、 n 3 1 、 n 3 2 、 n 3 3 、 n 4 1 、 n 4 2 、 n 4 3 、 n 5 1 、 n 5 2 、 40

- n 5 3 、 n 6 1 ~ n 6 3 、 n 7 1 ~ n 7 5 、 n 8 1 、 n 9 1 、 n 9 2 、 n 1 0 1 、 n 1 2

- 1~n123、n131~n133 nチャネルTFT

- R 1 0 1、R 1 0 2、R 1 3 1、R 1 3 2 抵抗

- C 1 1、C 3 1、C 4 1、C 5 1、C 6 1、C 7 1、C 8 1 ~ C 8 3、C 9 1 ~ C 9 3、

- C 1 0 1、C 1 3 1、C 1 3 2 コンデンサ

- T 1 3 1、T 1 3 2 npn型バイポーラトランジスタ

- VB' 分圧した電圧

- Va、Vb、Vc バイアス電圧

- ina、inb、inc アンプ回路部の入力信号

- a、b、c アンプ回路部の入出力の電圧波形

20

10

outa、outb、outcアンプ回路部の出力信号Rp11pチャネルTFTp11のオン抵抗

R n 1 1 n チャネル T F T n 1 1 のオン抵抗

Z c 1 1 コンデンサ C 1 1 のインピーダンス

# C<sub>11</sub> V<sub>DD</sub> V<sub>DD</sub> C<sub>111</sub> C<sub>111</sub> C<sub>DD</sub> C<sub>DD</sub>

【図2】

<アンプ回路部の入出力の電圧特性>

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

# フロントページの続き

# (72)発明者 高藤裕

大阪府大阪市阿倍野区長池町22番22号シャープ株式会社内

# 審査官 彦田 克文

(56)参考文献 特開平07-170167(JP,A)

特開平02-216911(JP,A)

特開平04-175011(JP,A)

特開昭60-105320(JP,A)

(58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H03K 19/0185

G09G 3/20 621

G09G 3/36

| 专利名称(译)        | 电平移位电路和图像显示装置                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | JP3609977B2                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2005-01-12 |

| 申请号            | JP2000092725                                                                                                                                                                                                                                                                                              | 申请日     | 2000-03-30 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 佐々木修<br>小川康行<br>高藤裕                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 佐々木 修<br>小川 康行<br>▲高▼藤 裕                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G09G3/36 G09G3/20 H03K19/0185                                                                                                                                                                                                                                                                             |         |            |

| CPC分类号         | H03K19/018585 G09G3/3648 G09G2300/0408                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | H03K19/00.101.D G09G3/20.621.L G09G3/36 H03K19/0185.230                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 5C006/BB11 5C006/BC20 5C006/BF25 5C006/BF37 5C006/BF46 5C006/EB05 5C006/FA42 5C080 /AA10 5C080/BB05 5C080/DD23 5C080/DD25 5C080/JJ02 5C080/JJ03 5C080/JJ05 5J056/AA32 5J056/BB53 5J056/BB58 5J056/BB59 5J056/CC21 5J056/DD29 5J056/DD51 5J056/EE03 5J056/EE11 5J056/FF08 5J056/GG06 5J056/GG09 5J056/KK03 |         |            |

| 优先权            | 1999201100 1999-07-15 JP                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | JP2001085990A                                                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                          |         |            |

|                |                                                                                                                                                                                                                                                                                                           |         |            |

# 摘要(译)

要解决的问题:通过在正电源电压和负电源电压之间提供分压装置并设置偏置电压来不必调整每个液晶显示装置中的电源电压和电阻值。解决方案:输入信号IN与电容器C11进行电容耦合,并输入到放大器电路的输入端。这里,信号IN的幅度电平的中心电压通过由p沟道TFT p11和n沟道TFT的导通电阻之比决定的偏置电压(定义为Vb)移位到偏置电压Vb。N11。然后,在放大器电路中,当信号IN处于高电平时,p沟道TFT p12截止,n沟道TFT n12导通,而负电源GND从放大器的输出端输出。电路。当信号IN处于低电平时,TFT p12导通并且TFT n12截止,并且正电源VDD从放大器电路的输出端输出。

# 【図2】