(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-102218

(P2008-102218A)

(43) 公開日 平成20年5月1日(2008.5.1)

| (51) Int.CI.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2H093       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 5C006       |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20 | 5C058       |

| <b>H04N 5/66</b> (2006.01)  | G09G 3/20 | 5C080       |

|                             | G09G 3/20 | 612U        |

審査請求 未請求 請求項の数 7 O L (全 15 頁) 最終頁に続く

|           |                              |          |                                              |

|-----------|------------------------------|----------|----------------------------------------------|

| (21) 出願番号 | 特願2006-283127 (P2006-283127) | (71) 出願人 | 000005049<br>シャープ株式会社<br>大阪府大阪市阿倍野区長池町22番22号 |

| (22) 出願日  | 平成18年10月17日 (2006.10.17)     | (74) 代理人 | 110000338<br>特許業務法人原謙三国際特許事務所                |

|           |                              | (72) 発明者 | 清水 将樹<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内    |

|           |                              | (72) 発明者 | 内山 正勝<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内    |

|           |                              |          | F ターム (参考) 2H093 NA16 NA33 NC34 NC35         |

最終頁に続く

## (54) 【発明の名称】 映像表示装置

## (57) 【要約】

【課題】動画ボケを抑制しつつフリッカ現象の発生を抑えて動画像表示の表示品位を向上させることが可能な映像表示装置を実現する。

【解決手段】本発明の映像表示装置は、複数の画素からなる、複数の水平ラインで構成されるLCDパネル11と、前記LCDパネル11の各水平ラインに対し、入力された映像情報を映像情報表示期間内に表示する第一表示処理と、非映像信号を非映像表示期間内に前記映像情報と異なる階調数で表示する第二表示処理とを所定の周期で繰り返し行うゲートドライバ13と、前記所定の周期に対する前記非映像表示期間の時間比率に応じて、第二表示処理における前記階調数を制御する制御回路15とを備える。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

複数の画素からなる、複数の水平ラインで構成される表示手段と、

前記表示手段の各水平ラインに対し、入力された映像情報を映像情報表示期間内に表示する第一表示処理と、非映像信号を非映像表示期間内に前記映像情報と異なる階調数で表示する第二表示処理とを所定の周期で繰り返し行う表示処理手段と、

前記所定の周期に対する前記非映像表示期間の時間比率に応じて、第二表示処理における前記階調数を制御する表示制御手段を備えたことを特徴とする映像表示装置。

**【請求項 2】**

前記表示処理手段は、

入力された映像情報を映像情報表示期間内に表示するために、水平同期信号が入力される度にいずれかの前記水平ラインを選択する第一走査手段と、

前記第一走査手段によって選択された水平ラインに対し第一表示処理をするために前記1水平ライン分の映像情報を保持する第一保持手段と、

非映像情報を非映像表示期間内に前記映像情報と異なる階調数で表示するために、前記水平同期信号が入力される際に前記第一走査手段によって選択された水平ラインとは異なる水平ラインを選択する第二走査手段とを有し、

前記表示制御手段は、

第一走査手段と第二走査手段で同一水平期間内に選択された各水平ラインの間のライン数に応じて、前記第二走査手段によって選択された水平ラインに対する第二表示処理の前記階調数を制御することを特徴とする請求項1に記載の映像表示装置。

**【請求項 3】**

前記第一表示処理は、同一水平ライン中の隣接画素間に對し極性反転したデータ電圧を入力する表示処理であり、

前記第二表示処理は、水平ラインを構成する各画素間に印加されたデータ電圧を放電させる処理を伴う表示処理であることを特徴とする請求項1又は2のいずれかに記載の映像表示装置。

**【請求項 4】**

前記第二表示処理は、各垂直期間内に複数回行われ、

前記表示制御手段は、前記時間比率に応じて、当該第二表示処理の回数を制御することを特徴とする請求項1乃至3のいずれかに記載の映像表示装置。

**【請求項 5】**

前記第二表示処理は、各垂直期間内に複数回行われ、

前記表示制御手段は、前記時間比率の増加に応じて、当該第二表示処理の回数を減少させることを特徴とする請求項1乃至3のいずれかに記載の映像表示装置。

**【請求項 6】**

各水平期間毎に行われる前記第二表示処理における各水平ラインへの放電処理は、同一水平期間中に行われる前記第一表示処理におけるデータ電圧を印加するタイミングに対し異なるタイミングで行われることを特徴とする請求項1乃至5のいずれかに記載の映像表示装置。

**【請求項 7】**

各水平期間毎に行われる前記第二表示処理における各水平ラインへの放電処理は、同一水平期間中に行われる前記第一表示処理において水平ライン選択開始時から当該水平ラインに対するデータ電圧入力時までの期間内に行われることを特徴とする請求項1乃至5のいずれかに記載の映像表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、動画ボケを抑制するために1フレーム期間中に非画像信号を挿入する期間を設けた映像表示装置に関するものである。

10

20

30

40

50

**【背景技術】****【0002】**

C R T (Cathode Ray Tube : 陰極線管) のようなインパルス型の表示装置においては、個々の画素に着目すると、画像が表示される点灯期間と画像が表示されない消灯期間とが交互に繰り返される。例えば動画の表示が行われた場合にも、1画面分の画像の書き換えが行われる際に消灯期間が挿入されるため、人間の視覚に動いている物体の残像が生じることがない。このため、背景と物体とが明瞭に見分けられ、違和感なく動画が視認される。

**【0003】**

これに対し、T F T (Thin Film Transistor : 薄膜トランジスタ) を使用した液晶表示装置のようなホールド型の表示装置では、個々の画素の輝度は各画素容量に保持される電圧によって決まり、画素容量における保持電圧は、一旦書き換えられると1フレーム期間維持される。このようにホールド型の表示装置では、画素データとして画素容量に保持すべき電圧は、一旦書き込まれると次に書き換えられるまで保持されるので、各フレームの画像は、その1フレーム前の画像と時間的に近接することになる。これにより、動画が表示される場合に、人間の視覚には動いている物体の残像が生じる。

**【0004】**

このような残像を低減させる方法として、液晶表示装置のようなホールド型の表示装置において、1フレーム期間中に黒表示（非画像表示）を行う期間を挿入すること（以下、黒挿入と称する）により該液晶表示装置における表示を（擬似的に）インパルス化するという方法が知られている（例えば特許文献1）。

**【0005】**

しかしながら、上述のような擬似的なインパルス駆動の場合、1フレーム期間中に画像表示期間と非画像表示（黒表示）期間とが混在し、1フレーム期間中の画像表示期間と非画像表示期間との比率（表示時間比率）によっては、動画像を表示する際、残像に起因する動画ボケが生じる虞がある。

**【0006】**

そこで、例えば、特許文献2には、1フレーム期間中の画像表示期間と非画像表示期間との表示時間比率を、動画像中の画像の動き量に応じて調整することで、動画像表示における残像に起因する動画ボケを低減させる技術が開示されている。

**【特許文献1】**特開2003-066918号公報（平成15（2003）年03月05日公開）

**【特許文献2】**特開2002-323876号公報（平成14（2002）年11月08日公開）

**【発明の開示】****【発明が解決しようとする課題】****【0007】**

ところで、上記特許文献2では、動画像中の画像の動き量が増大、すなわち動きが速くなれば、非画像表示期間の時間比率を上げて残像を低減させて動画ボケを改善している。

**【0008】**

しかしながら、動画像表示において、非画像表示期間の時間比率を高くした場合、動きが速い動画像に対して残像を低減して動画ボケを改善できるものの、フリック現象が生じ、動画像表示における表示品位を低下させるという問題が生じる。

**【0009】**

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、動画ボケを抑制しつつフリック現象の発生を抑えて動画像表示の表示品位を向上させることができ可能な映像表示装置を実現することにある。

**【課題を解決するための手段】****【0010】**

本発明の映像表示装置は、上記の課題を解決するために、複数の画素からなる、複数の

10

20

30

40

50

水平ラインで構成される表示手段と、前記表示手段の各水平ラインに対し、入力された映像情報を映像情報表示期間内に表示する第一表示処理と、非映像信号を非映像表示期間内に前記映像情報と異なる階調数で表示する第二表示処理とを所定の周期で繰り返し行う表示処理手段と、前記所定の周期に対する前記非映像表示期間の時間比率に応じて、第二表示処理における前記階調数を制御する表示制御手段を備えたことを特徴としている。

## 【0011】

上記構成によれば、表示制御手段が、所定の周期に対する前記非映像表示期間の時間比率に応じて、第二表示処理における前記階調数を制御することで、当該所定の周期における最大輝度と最小輝度との差分が制御されることになる。

## 【0012】

これにより、所定の周期における最大輝度と最小輝度との差分を、表示手段における輝度で除したときの割合、すなわちフリッカ率を、所定の周期に対する前記非映像情報表示期間の時間比率に応じて変えることができる。

10

## 【0013】

例えば、所定の周期に対する前記非映像情報表示期間の時間比率が多くなるとき、すなわち映像情報に含まれる動き量が多くなるときには、所定の周期における最大輝度と最小輝度との差分が小さくなるように、非映像の階調数を上げるように制御すればよい。この場合には、フリッカ率を求める式の分子が小さくなるので、フリッカ率が小さくなり、映像情報に含まれる動き量が多くなり、動画ボケを抑制するために、非映像情報表示期間の時間比率が増加しても、フリッカの発生を抑制することが可能となる。つまり、フリッカ現象が生じやすい非映像表示期間が長い場合、すなわち映像における動画速度が速い場合であっても、動画ボケを抑制しつつフリッカの発生を抑制が可能な映像表示装置を提供することができる。

20

## 【0014】

前記表示処理手段は、入力された映像情報を映像情報表示期間内に表示するために、水平同期信号が入力される度にいずれかの前記水平ラインを選択する第一走査手段と、前記第一走査手段によって選択された水平ラインに対し第一表示処理をするために前記1水平ライン分の映像情報を保持する第一保持手段と、非映像情報を非映像表示期間内に前記映像情報と異なる階調数で表示するために、前記水平同期信号が入力される際に前記第一走査手段によって選択された水平ラインとは異なる水平ラインを選択する第二走査手段とを有し、前記表示制御手段は、第一走査手段と第二走査手段で同一水平期間内に選択された各水平ラインの間のライン数に応じて、前記第二走査手段によって選択された水平ラインに対する第二表示処理の前記階調数を制御するようにしてよい。

30

## 【0015】

ここで、第一走査手段と第二走査手段とで同一水平期間内に選択された各水平ラインの間のライン数が小さくなることは、第二走査手段によって選択される水平ライン数が多くなることを示す。つまり、第一走査手段と第二走査手段とで同一水平期間内に選択された各水平ラインの間のライン数が小さくなることは、水平期間内に非映像情報を挿入する割合が多くなることを示す。

40

## 【0016】

したがって、上記構成のように、映像情報から得た所定の情報に応じて、第一走査手段と第二走査手段で同一水平期間内に選択された各水平ラインの間のライン数を制御することにより前記時間比率を制御すると共に、該時間比率に応じて、前記第二保持手段に保持された非映像情報の階調数を制御することで、1水平期間内の非映像情報を挿入する割合に応じた該非映像情報の階調数に設定することが可能となる。

## 【0017】

また、前記第一表示処理は、同一水平ライン中の隣接画素間に對し極性反転したデータ電圧を入力する表示処理であり、前記第二表示処理は、水平ラインを構成する各画素間に印加されたデータ電圧を放電させる処理を伴う表示処理であってもよい。

## 【0018】

50

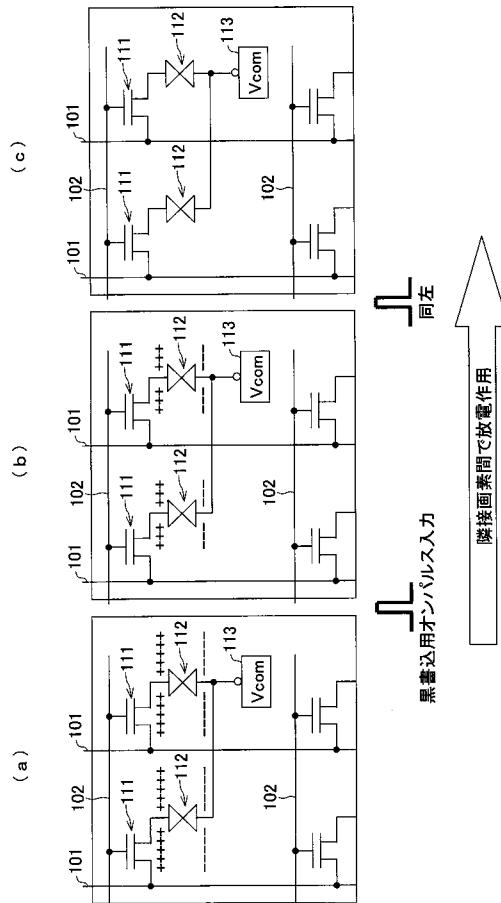

この場合、映像情報の表示期間に、同一水平ラインの隣接画素間で印加されるデータ電圧の極性が反転しているので、非映像情報の表示期間に、各画素に印加されたデータ電圧を放電させることで、隣接画素間で電荷の共有、すなわちチャージシェアリングが行われることになる。

【0019】

これにより、画素に蓄積された電荷を、第二表示処理が行われる都度、減少させることができるとなる。このように、隣接画素間でのチャージシェアの結果、所定の階調数と同程度のドレン電圧にすることができるので、フリッカ率を求めるための分子である最大輝度と最小輝度との差分（AC成分）を小さくできる。これにより、フリッカ現象の発生を抑制することができる。

10

【0020】

具体的な表示処理の回数の制御については、以下に示すような処理が好ましい。

【0021】

そして、前記第二表示処理は、各垂直期間内に複数回行われ、前記表示制御手段は、前記時間比率に応じて、当該第二表示処理の回数を制御するようにしてもよい。

【0022】

さらに、前記第二表示処理は、各垂直期間内に複数回行われ、前記表示制御手段は、前記時間比率の増加に応じて、当該第二表示処理の回数を減少させるようにしてもよい。

20

【0023】

各水平期間毎に行われる前記第二表示処理における各水平ラインへの放電処理は、同一水平期間中に行われる前記第一表示処理におけるデータ電圧を印加するタイミングに対し異なるタイミングで行われるのが好ましい。

【0024】

各水平期間毎に行われる前記第二表示処理における各水平ラインへの放電処理は、同一水平期間中に行われる前記第一表示処理において水平ライン選択開始時から当該水平ラインに対するデータ電圧入力時までの期間内に行われるのが好ましい。

30

【0025】

以上のように、第二表示処理における各水平ラインへの放電処理は、同一水平期間中に行われる前記第一表示処理におけるデータ電圧を印加するタイミングで行われることで、2種類の放電のためのオノパルス信号を印加するための走査信号線が1本ですむので、画面の輝度低下を伴うことなく、動画ボケの抑制とフリッカ現象の発生を抑制できる。

【発明の効果】

【0026】

本発明に係る映像表示装置は、以上のように、複数の画素からなる、複数の水平ラインで構成される表示手段と、前記表示手段の各水平ラインに対し、入力された映像情報を映像情報表示期間内に表示する第一表示処理と、非映像信号を非映像表示期間内に前記映像情報と異なる階調数で表示する第二表示処理とを所定の周期で繰り返し行う表示処理手段と、前記所定の周期に対する前記非映像表示期間の時間比率に応じて、第二表示処理における前記階調数を制御する表示制御手段を備えたことで、動画ボケを抑制しつつフリッカの発生を抑制が可能な映像表示装置を提供することができるという効果を奏する。

40

【発明を実施するための最良の形態】

【0027】

本発明の一実施の形態について説明すれば、以下の通りです。なお、本実施の形態では、映像表示装置の一例として、液晶表示装置について説明する。

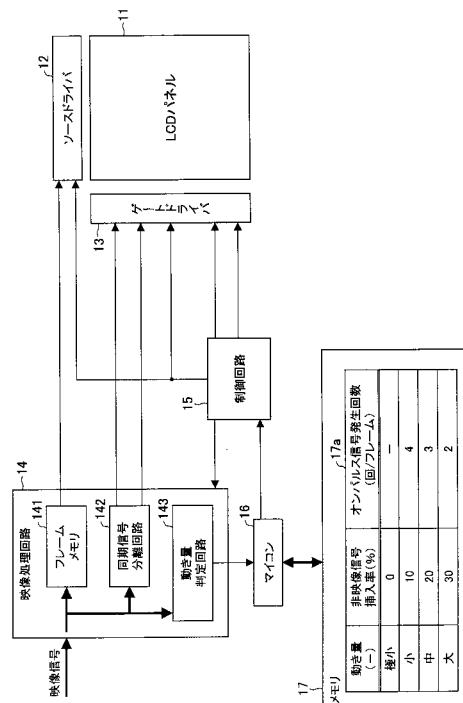

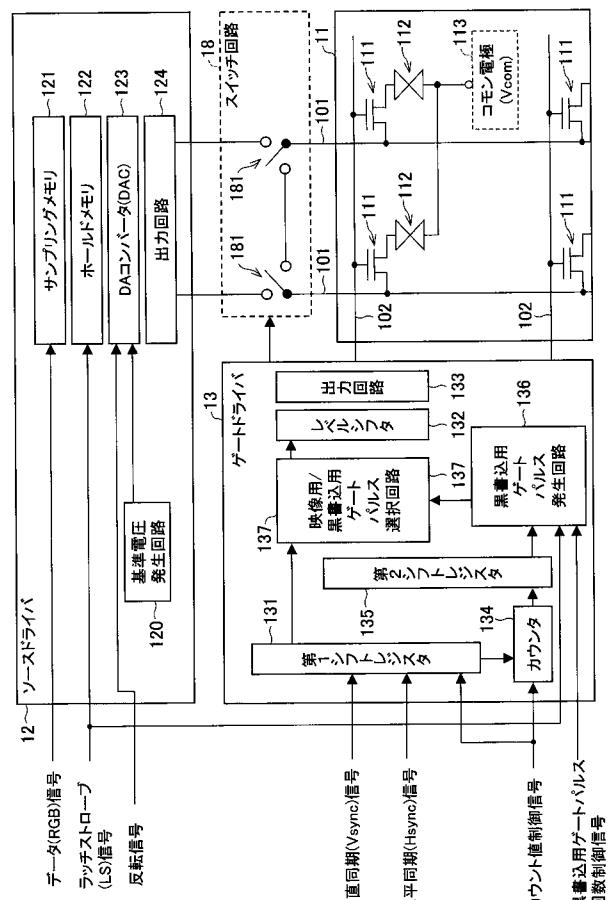

【0028】

本実施の形態に係る液晶表示装置は、図1に示すように、LCD (Liquid Crystal Display) パネル（表示手段）11、ソース駆動回路としてのソースドライバ12、ゲート駆動回路としてのゲートドライバ13を備えており、さらに、上記ソースドライバ12に対して、外部から入力される映像信号および非映像信号をフレーム単位で供給すると共に、上記ゲートドライバ13に対して水平同期信号および垂直同期信号を供給する映像処理回

50

路 14 と、上記の各ドライバにスタートパルス信号などの制御信号を供給する制御回路 15 と、1 フレーム期間中に非映像信号を挿入する割合および該非映像信号の階調数を設定するためのマイコン 16 と、該マイコン 16 で使用するデータを格納するメモリ 17 とを備えている。

【 0029 】

上記LCDパネル 11 は、複数の絵素又は画素からなる、複数の水平ラインで構成されており、上記映像処理回路 14 から送られる映像信号を表示するようになっている。

【 0030 】

また、ソース駆動回路およびゲート駆動回路は、上記LCDパネル 11 の各水平ラインに対し、上記映像処理回路 14 から入力された映像情報を映像情報表示期間内に表示する表示処理と、非映像信号を非映像表示期間内に前記映像情報と異なる階調数で表示する表示処理とを所定の周期で繰り返し行う表示処理手段とて機能している。

10

【 0031 】

上記映像処理回路 14 は、チューナ（図示せず）から 1 フレームごとに順次入力される映像信号をフレーム単位で格納するフレームメモリ 141、上記映像信号から水平同期信号と垂直同期信号とを分離する同期信号分離回路 142、1 フレームごとに順次入力された映像信号から、該映像信号に含まれる動画像の動き量を判定する動き量判定回路 143 を含んでいる。

20

【 0032 】

上記動き量判定回路 143 は、チューナ等を介して 1 フレームごとに順次入力された映像信号から、連続する 2 つ以上のフレーム間における動きの差分を比較して、動き量を判定する回路である。

【 0033 】

上記動き量判定回路 143 では、例えば以下のような演算によって動き量を判定する。すなわち、連続して送られる複数フレームのうち各フレーム内に存在する画素から任意に選択された画素番号を  $i$  とし、 $m$  番目のフレームに含まれる  $i$  個目の画素の階調数を  $P_{m i}$  とし、 $m + 1$  番目のフレームに含まれる  $i$  個目の画素の階調数を  $P(m + 1) i$  としたとき、この  $P_{m i}$  と  $P(m + 1) i$  の差分の大きさを  $i$  の最小値から最大値（0 ~ MAX）までを積算した積算値（ $|P_{m i} - P(m + 1) i|$ ）から動き量を判定している。具体的には、上記積算値がある一定の値の範囲内であるか否かを判断し、範囲内であると判断されたときに、該範囲に応じて動き量を判定している。ここでは、動き量を、極小、小、中、大の 4 段階に分類するために、4 種類の範囲を用意しておく。

30

【 0034 】

上記動き量判定回路 143 は、上記のようにして判定した動き量（極小、小、中、大の 4 段階）のデータをマイコン 16 に送る。

【 0035 】

上記マイコン 16 は、送られた動き量のデータから、上記メモリ 17 に格納されている動き量に対応付けられた発生回数のオンパルス信号をゲートバスラインに出力するよう、上記制御回路 15 に指示する。

40

【 0036 】

上記メモリ 17 には、動き量に対して、所定値の非映像信号挿入率と所定値のオンパルス信号発生回数を一組とするメモリ - 領域を、分類分けした動き量の数だけメモリマップ 17a として保存しておく。このメモリマップ 17a に、動き量の大きい時ほど非映像信号挿入率が高く、また、1 フレーム期間における 1 画素毎に入力されるオンパルス信号の発生回数が少なくなるように設定値を保存しておく。

【 0037 】

ここで、非映像信号挿入率とは、1 フレーム期間のうち、非映像表示を行う時間比率を示す。つまり、非映像信号挿入率が 0 とは、1 フレーム期間中に非映像表示を行う期間が無いことを示している。従って、非映像信号挿入率が 0 の場合、オンパルス信号の発生回数を設定しない。

50

## 【0038】

上記制御回路15は、上記ソースドライバ12にラッチストローブL/S信号を、上記ゲートドライバ13にカウント値制御信号を供給するようになっている。これにより、上記ソースドライバ12からは、1フレーム期間の映像表示期間に映像信号が所定のタイミングでLCDパネル11の目的とする画素に書き込まれる。

## 【0039】

また、上記制御回路15は、前記LCDパネル11の各水平ラインに対し、入力された映像情報を映像情報表示期間内に表示する第一表示処理と、非映像信号を非映像表示期間内に前記映像情報と異なる階調数で表示する第二表示処理とを繰り返し行う周期（詳細は後述する）に対する前記非映像表示期間の時間比率に応じて、第二表示処理における前記階調数を制御する機能を有している。そして、上記制御回路15は、上記マイコン16からの指示に基づいて、非映像信号として出力される信号の階調数を設定するための制御信号を上記ソースドライバ12に供給するようになっている。これにより、上記ソースドライバ12からは、1フレーム期間の非映像表示期間に非映像信号が所定のタイミングでLCDパネル11の目的とする画素に書き込まれる。

10

## 【0040】

上記構成の液晶表示装置について、さらに、詳細に説明すれば、以下の通りである。

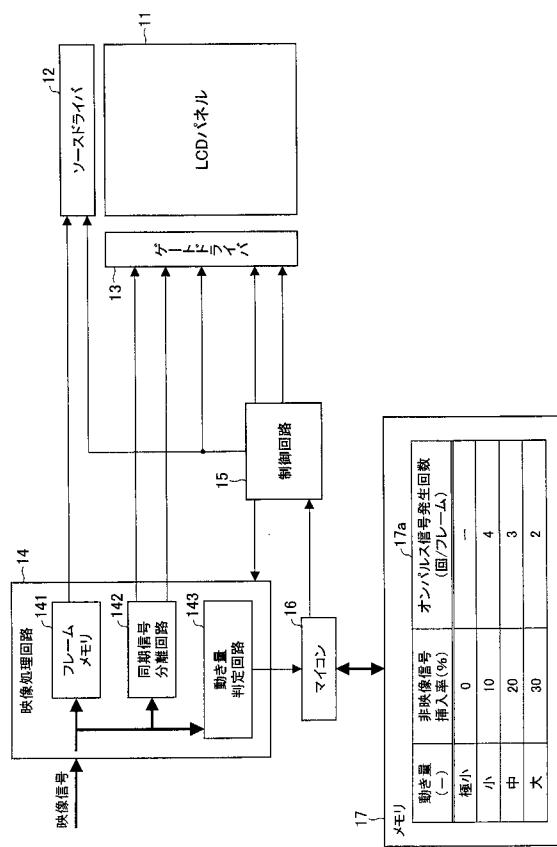

## 【0041】

上記LCDパネル11は、図2に示すように、上記ソースドライバ12に、スイッチ回路18を介して接続された複数のソースバスライン101・・・と、上記ゲートドライバ13に接続された複数のゲートバスライン102・・・とが直交するように配され、ソースバスライン101とゲートバスライン102との交差部には、スイッチング素子としてのTFT111が設けられている。

20

## 【0042】

上記TFT111のドレイン電極には、画素容量112が接続されている。本実施の形態では、隣接された画素の画素容量112同士は、ひとつのコモン電極113を共有している。

## 【0043】

上記スイッチ回路18は、ゲートドライバ13から出力された黒挿入処理（後述）のためのオンパルス信号が出力される度に、あるいはラッチストローブ信号がON状態になる度に、同一ゲートバスライン102上の画素間でショート状態を形成させるために各ソースバスライン101が互いに導通状態になるように接続されるショート（短絡）ラインを構成するためのスイッチング素子181を備えた構成となっている。そして、ゲートドライバ13からのオンパルス信号の発生した期間で隣接するソースバスライン101同士のショート状態を形成する。この構成によって、ラッチストローブ信号において、それまでの映像信号表示処理で互いに反転した電荷を蓄えた隣接画素間の放電現象がオンパルス信号を契機に作用し、それまでの各画素への印加電圧を低減させて、徐々に黒書き込み処理を施すようになる。

30

## 【0044】

上記ソースドライバ12は、図2に示すように、基準電圧発生回路120、サンプリングメモリ121、ホールドメモリ122、DAコンバータ（DAC）123、出力回路124を含んだ構成となっている。

40

## 【0045】

上記基準電圧発生回路120は、データ信号として表現されたRGBの各階調数のうち適当な階調数に対し相応しいアナログ電圧値を出力するための基準電圧を生成する回路であり、生成した基準電圧は上記DAコンバータ123に供給される。例えば、ドット反転やライン反転などの表示処理を行う際は、1ライン毎に発生する反転信号に従って各階調数毎に正負両方のアナログ階調電圧を出力できるように電圧データを保持しておく。例えば、256階調の場合には、256×2個の電圧データが保持される。

## 【0046】

50

上記サンプリングメモリ（第一保持手段）121は、映像処理回路14（図1）から送られた映像データ（RGB）信号のうち1ライン分をLCDパネル11に書込む前に読み込み保存するためのメモリである。つまり、前記第1ゲートドライバ13aによって選択された水平ラインに対し第一表示処理（映像表示処理）をするために前記1水平ライン分の映像情報を保持するメモリである。

#### 【0047】

上記ホールドメモリ122は、上記サンプリングメモリ121に1ライン分のデータ信号が書込まれた後で同じデータを書き込むためのメモリである。このホールドメモリ122によるDAコンバータ123へのデータの書き込みのタイミングは、ラッチストローブLS信号によって制御されている。

10

#### 【0048】

上記DAコンバータ123は、入力された電圧信号を、上記ホールドメモリ122にデジタル形式で保存された1ライン分のデータ信号を基準電圧発生回路120から出力された階調毎の電圧値に従ってアナログ電圧値に変換する回路である。

#### 【0049】

上記出力回路124は、上記DAコンバータ123によって変換されたアナログ電圧値の信号を各ソースバスライン101に出力する回路である。

#### 【0050】

上記ゲートドライバ13は、前記LCDパネル11の各水平ラインに対し、入力された映像情報を映像情報表示期間内に表示する第一表示処理と、非映像信号を非映像表示期間内に前記映像情報と異なる階調数で表示する第二表示処理とを所定の周期で繰り返し行わせる表示処理手段としての機能を有し、さらに、ゲートドライバ13は、入力された映像情報を映像情報表示期間内に表示するために、水平同期信号が入力される度にいずれかの前記水平ラインを選択する第一走査手段と、非映像情報を非映像表示期間内に前記映像情報と異なる階調数で表示するために、前記水平同期信号が入力される際に前記第一走査手段によって選択された水平ラインとは異なる水平ラインを選択する第二走査手段との機能を有している。具板的には、ゲートドライバ13は、図2に示すように、第1シフトレジスタ131、レベルシフタ132、出力回路133を含み、さらに、カウンタ134、第2シフトレジスタ135、黒書き用ゲートパルス発生回路136、映像用／黒書き用ゲートパルス選択回路137を含んだ構成となっている。

20

30

#### 【0051】

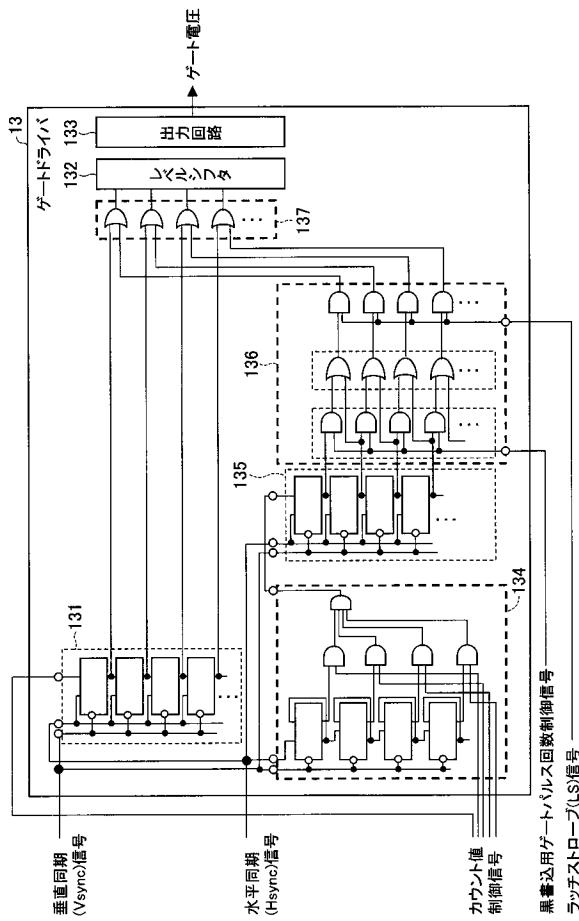

上記ゲートドライバ13の具体的な回路構成の一例を、図3に示す。

#### 【0052】

上記第1シフトレジスタ131は、水平同期信号(Hsync)が入力されるたびに、LCDパネル11が構成する複数本のゲートバスライン102を順次切替えて選択することにより、ソースドライバ12に保存された1ライン分のデータ信号を順次書き込むことを可能にする回路である。

40

#### 【0053】

上記カウンタ134は、一度選択されたあるゲートラインに対して、数十～数百ライン分遅れて黒書き用のゲートパルスを発生させるために、数十～数百ライン分の水平同期信号を計測することを目的とする回路。更に、マイコン等から送られたカウント値制御信号に含まれるカウント上限データ（デジタル形式）とカウンタで計測したカウント数とを比較する構成を加えることにより、黒書き用ゲートパルスのタイミングを1水平期間単位で調整され、これにより1垂直期間において出力された映像信号と非映像信号（例えば黒信号）との表示期間比率（非映像信号插入率）を制御することができる。

#### 【0054】

上記第2シフトレジスタ135は、上記第1シフトレジスタ132に対してカウンタ134で計数した数十～数百ライン分だけ遅れて黒書き用のゲートバスライン102を選択するための回路である。

#### 【0055】

50

さらに、上記第2シフトレジスタ135において、OR回路等の論理回路を各フリップフロップの出力を入力端子に接続することにより、1回の水平同期期間内において複数本のゲートバスライン102を同時に選択することが可能である。

#### 【0056】

また、黒書き込み用ゲートパルス発生回数制御信号の情報によって、同一水平期間に黒書き込み処理のために選択されるゲートバスライン102の本数を適宜調整することが可能になる。

#### 【0057】

本願発明では、上記カウンタ134に入力されるカウント上限データの値を少なくして非映像信号挿入率を向上させる時にはそれまで選択していたゲートライン数をより少なくなるように制御することにより、非映像信号挿入率が向上することによって著しく発生するフリッカ現象を緩和させることができ、動画ボケをより押さえながらもフリッカが発生し難い表示処理が可能になる。

10

#### 【0058】

つまり、ライン数mの値に応じて前記非映像信号挿入率を制御、さらに、該非映像信号挿入率に応じて、非映像信号の階調数を制御することで、例えば、ライン数mが小さくなり非映像信号挿入率が向上してフリッカが生じ易い条件になっても、非映像信号の階調数を上げて、最大輝度と最小輝度との差分を小さくすることで、フリッカを防止することが可能になる。

20

#### 【0059】

上記黒書き込み用ゲートパルス発生回路136は、上記第2シフトレジスタ135で複数本選択されたゲートバスライン102に対して、ラッチストローブ信号がオン状態になった時に黒書き込み用のゲートパルス信号を発生させる。このゲートパルス信号をラッチストローブ期間に発生させることにより、他のラインにおける(映像)データ信号の書き込み処理をタイミング的に阻害することなく所望のゲートラインの黒書き込み処理を適当に行うことが可能になる。

30

#### 【0060】

上記黒書き込み用ゲートパルス発生回路136は、図3に示すように、主にAND回路若しくはトランジスタ素子を各ライン毎に設けることで構成される。

#### 【0061】

上記映像用／黒書き込み用ゲートパルス選択回路137は、1垂直期間内において、任意のゲートバスライン102に対して、第1シフトレジスタ131で発生した映像用ゲートパルスと第2シフトレジスタ135を介して黒書き込み用ゲートパルス発生回路136で発生した黒書き込み用ゲートパルスとを組合わせて発生させるための回路である。

#### 【0062】

上記映像用／黒書き込み用ゲートパルス選択回路137は、図3に示すように、主に上記2つのゲートパルスのラインを入力してLCDパネル11のゲートバスライン102へ出力するOR回路をゲートバスライン102に対して並列に設けて構成される。

40

#### 【0063】

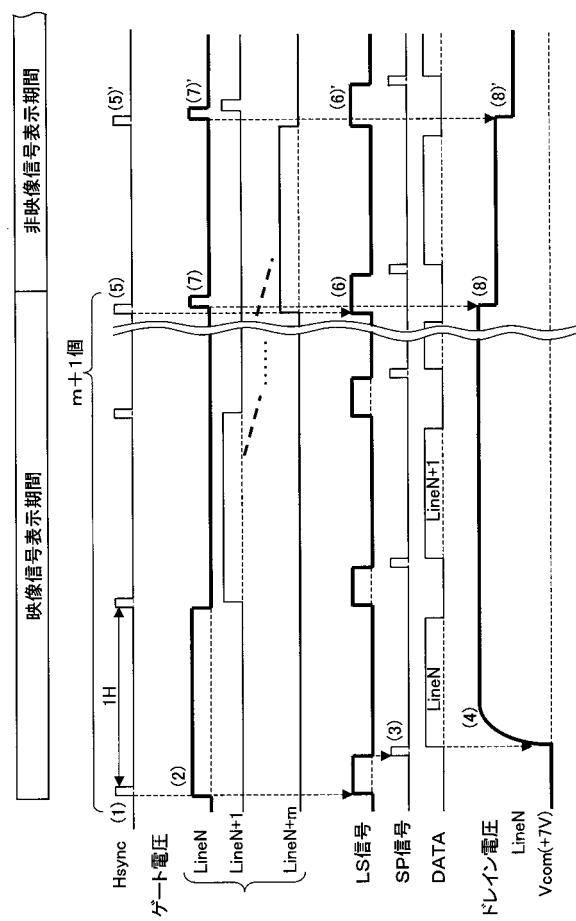

上記構成の各ドライバの動作について、図2～図4を参照しながら以下に説明する。

#### 【0064】

ここでは、1フレーム期間が、映像信号表示期間と非映像信号表示期間とで構成されている場合について説明する。

#### 【0065】

はじめに、通常時、すなわち映像信号表示期間におけるデータ信号走査処理の流れについて説明する。

(1)：まず水平同期信号(Hsync)がゲートドライバに入力される。

(2)：第1シフトレジスタ131ではHsyncの入力によりN番ライン(Line N)のゲートパルスが次のHsync信号が入力されるまでの間だけ立上り、同時にラッチストローブ(LS)信号が上記ゲートパルスよりも比較的短い期間立上る。

50

(3) : 上記(2)でLS信号がオフ状態になるとスタートパルス(SP)信号が立上る。

(4) : 上記(3)のSP信号の立上りによりN番ラインの各画素の TFT 素子がON状態になり、そのドレイン電圧にはソースドライバで所望の階調数のデータ信号をアナログ変換した電圧値が供給される。

#### 【0066】

次に、非映像信号期間(黒書き込み期間)におけるデータ信号走査処理の流れについて説明する。

(5) : ここでは、N番ラインに対して更にMラインだけ先行したゲートライン((N+m)番ライン)を選択するためのHsync信号が入力される。

(6) : これにより(N+m)番ラインのゲートラインが選択されるとほぼ同時に、ラッチストローブ信号が立ち上がる。 10

(7) : そして、このラッチストローブ信号の立上りを検出したことを契機に第2シフトレジスタ135で選択されたN番ラインへ1H期間に対し十分短いオンパルス信号を出力する。

(8) : 上記(7)のパルス信号が立ち上がることにより、N番ラインのドレイン端子に印加された映像信号の各階調電圧は、LS信号が立上った期間のデータ信号電圧(例えば0V)を一瞬だけ導通した結果立下り現象を起こし(若しくは、ドット反転駆動の場合は隣接画素同士のコモン電極から互いの液晶層に係った電荷量が放電しあうことによって減圧し(下図参照))、各画素の明るさが落とし込まれる。

#### 【0067】

(5)' ~ (8)': このオンパルス信号出力処理をLS信号が入力されるたびに行い、一定回数以上(例えば4回等)オンパルス信号を繰り返し発生させることによって、液晶層への印加電圧をコモン電圧(Vcom)と同等にでき、結果、非映像信号表示期間内の複数の水平期間をかけて黒書き込み処理が段階的に行われる。 20

#### 【0068】

ここで、黒書き込み処理を段階的に行って、目的とする階調数のドレイン電圧にするための原理について説明すれば、以下の通りである。

#### 【0069】

図4に示す非映像信号表示期間において、(6)(6)'に示すラッチストローブ信号LSがハイレベル、すなわちON状態にある間に、(8)(8)'に示すように、N番目のラインへ短いパルス信号(黒書き込み用オンパルス信号)を送ることにより隣接画素間で放電作用が働き、N番目のラインの画素に印加された階調電圧が低下する。これを1水平期間毎に複数回繰り返すことでパネル階調数をゼロに落とすことが可能になる。この場合、図6に示すように、隣接する2つの画素同士が黒書き込み用オンパルス信号の入力により、導通状態となり、黒書き込み用オンパルス信号がON状態の期間、チャージシェアリングが行われる。 30

#### 【0070】

本発明では、前述のような構成をしているため、例えば動画ボケを抑制しようとして非映像信号挿入率を向上させた結果生じ易くなるフリッカを極力抑制または解消させることができ可能になる。つまり、動画ボケを押さえながらフリッカも生じ難い高画質な映像を視聴者に提供することが可能になる。 40

#### 【0071】

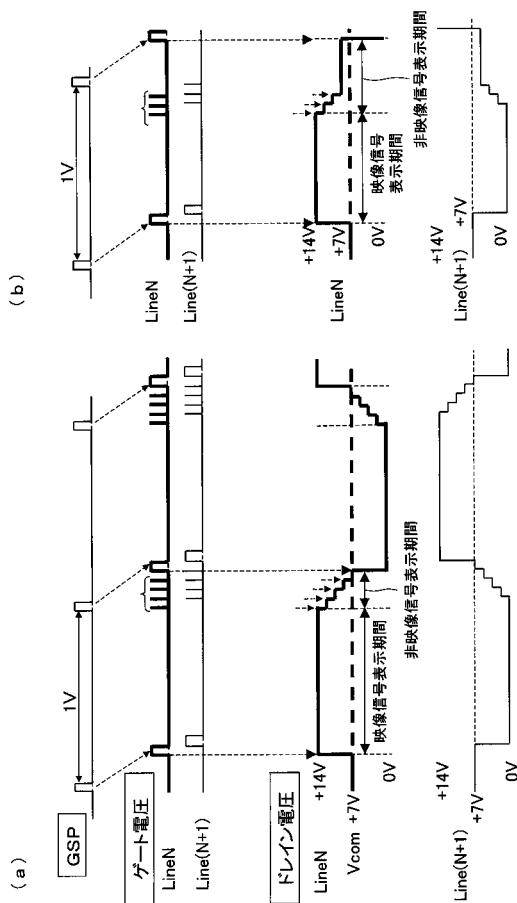

したがって例えば図5(a)(b)を参照して本発明の効果について説明する。

#### 【0072】

図5(a)は、1フレーム期間(1V期間)における非映像表示期間の時間比率(非映像信号挿入率)が20%のときの駆動制御例を示す図である。

#### 【0073】

この場合には、オンパルス信号を1垂直期間(1V)に4回挿入することにより、LCDパネル11における液晶層への印加電圧であるドレイン電圧を制御してゼロ階調に段階的にシフトさせて非映像信号(黒信号)を書き込んでいる。 50

## 【0074】

図5(a)では、非映像信号挿入率が20%の例について示したが、さらに、動き量が多くなり、非映像信号挿入率が40%になった場合には、図5(b)に示すように、オンパルス信号を1垂直期間(1V)に3回挿入(図5(a)に示す場合より1回少ない)することによりLCDパネル11の液晶層への印加電圧であるドレイン電圧をゼロ階調ではない低階調数に対応する電圧に留めた書き込み処理を行っている。

## 【0075】

これにより、1フレーム期間内の画面輝度の急激な落としこみを抑制することが可能になり、結果フリッカ率を向上させることなく動画ボケをより抑制するという効果をもたらす。

10

## 【0076】

つまり、1フレーム期間の非映像表示期間において、動画像の動き量に応じてオンパルス信号の回数と最終的なドレイン電圧を調整することで、フリッカ率を求める式の分子であるAC成分の値を、階調数0の場合の $14V - 7V = 7V$ よりも小さくすることができる。これにより、フリッカ率を、階調数0の場合よりも小さくすることができるので、フリッカの発生を抑制できる。

## 【0077】

したがって、非映像信号挿入率を維持したまま、フリッカ率を低減できるので、動画ボケおよびフリッカの無い表示品位の高い動画像を表示することができる。

20

## 【0078】

本発明は上述した実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能である。すなわち、請求項に示した範囲で適宜変更した技術的手段を組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

## 【産業上の利用可能性】

## 【0079】

本発明は、動画ボケを抑制するために1フレーム期間中に非画像信号を挿入する期間を設けた液晶表示装置に関するものであるが、表示素子の応答性に有る程度の遅延が生じる素子であれば同様の効果をなしうるものであり、ホールド型の表示装置であれば本発明の技術的範囲であるものとする。

30

## 【図面の簡単な説明】

## 【0080】

【図1】本発明の実施形態を示すものであり、液晶表示装置の要部構成を示すブロック図である。

【図2】図1に示す液晶表示装置の各ドライバの要部構成を示すブロック図である。

【図3】図2に示すゲートドライバの一例を示す回路図である。

【図4】図1に示す液晶表示装置の各ドライバの出力信号の波形図である。

【図5】(a)は、非映像信号挿入率が20%の場合の図2に示す各ドライバの出力信号の波形図であり、(b)は、非映像信号挿入率が30%の場合の図2に示す各ドライバの出力信号の波形図である。

40

【図6】チャージシェアリングの原理を示す説明図である。

## 【符号の説明】

## 【0081】

1 1 LCDパネル(表示手段)

1 2 ソースドライバ(表示処理手段)

1 3 ゲートドライバ(表示処理手段、第一走査手段、第二走査手段)

1 1 LCDパネル

1 2 ソースドライバ

1 3 ゲートドライバ

1 4 映像処理回路

1 5 制御回路

50

1 6 マイコン

1 7 メモリ

1 7 a メモリマップ

1 8 スイッチ回路

1 0 1 ソースバスライン

1 0 2 ゲートバスライン

1 1 1 T F T

1 1 2 画素容量

1 1 3 コモン電極

1 2 0 基準電圧発生回路 10

1 2 1 サンプリングメモリ(第一保持手段)

1 2 2 ホールドメモリ

1 2 3 D A コンバータ

1 2 4 出力回路

1 3 1 第1シフトレジスタ

1 3 2 レベルシシフタ

1 3 2 第1シフトレジスタ

1 3 3 出力回路

1 3 4 カウンタ

1 3 5 第2シフトレジスタ 20

1 3 6 黒書込用ゲートパルス発生回路

1 3 7 映像用 / 黒書込用ゲートパルス選択回路

1 4 1 フレームメモリ

1 4 2 同期信号分離回路

1 4 3 動き量判定回路

1 8 1 スイッチング素子

L S ラッチストローブ信号

〔 図 1 〕

【図3】

【 四 2 】

【 図 4 】

【図5】

【図6】

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 2 1 B

G 0 9 G 3/20 6 4 1 P

G 0 2 F 1/133 5 5 0

H 0 4 N 5/66 1 0 2 B

F ターム(参考) 5C006 AA01 AA14 AC27 AC28 AF01 AF44 AF45 AF46 AF51 AF52

AF53 AF61 AF71 BB16 BC03 BC11 BF02 BF05 BF14 BF24

FA18 FA23 FA29

5C058 AA06 BA01 BA09 BA25 BB12

5C080 AA05 AA06 AA10 BB05 DD04 DD05 DD06 EE19 EE29 FF11

JJ02 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 映像表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2008102218A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2008-05-01 |

| 申请号            | JP2006283127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2006-10-17 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 清水将樹<br>内山正勝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 清水 将樹<br>内山 正勝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 H04N5/66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| FI分类号          | G09G3/36 G09G3/20.632.C G09G3/20.641.R G09G3/20.611.E G09G3/20.612.U G09G3/20.621.B<br>G09G3/20.641.P G02F1/133.550 H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA33 2H093/NC34 2H093/NC35 5C006/AA01 5C006/AA14 5C006/AC27 5C006<br>/AC28 5C006/AF01 5C006/AF44 5C006/AF45 5C006/AF46 5C006/AF51 5C006/AF52 5C006/AF53<br>5C006/AF61 5C006/AF71 5C006/BB16 5C006/BC03 5C006/BC11 5C006/BF02 5C006/BF05 5C006<br>/BF14 5C006/BF24 5C006/FA18 5C006/FA23 5C006/FA29 5C058/AA06 5C058/BA01 5C058/BA09<br>5C058/BA25 5C058/BB12 5C080/AA05 5C080/AA06 5C080/AA10 5C080/BB05 5C080/DD04 5C080<br>/DD05 5C080/DD06 5C080/EE19 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ04 2H193/ZA04<br>2H193/ZC15 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

## 摘要(译)

要解决的问题：实现能够在抑制运动模糊的同时抑制闪烁现象的发生并且改善运动图像显示的显示质量的图像显示装置。根据本发明的图像显示装置包括：LCD面板11，由多个像素组成并由多条水平线组成；以及图像显示单元，用于在LCD面板11的每条水平线上显示输入图像信息作为视频信息。栅极驱动器13，其以预定周期在非视频显示时段内重复执行用于在显示时段内显示的第一显示处理和用于在视频信息中显示具有不同灰度数的非视频信号的第二显示处理，并且控制电路15用于根据非视频显示时段与预定时段的时间比控制第二显示处理中的灰度数。点域1