## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-267560 (P2006-267560A)

(43) 公開日 平成18年10月5日(2006.10.5)

長野県諏訪市大和3丁目3番5号 セイコ

最終頁に続く

ーエプソン株式会社内 Fターム(参考) 2H093 NA10 ND39 ND41 NF28

| (51) Int.C1.<br>G09G<br>G02F<br>G09G | 3/36<br>1/133<br>3/20 | (2006. 01)<br>(2006. 01)<br>(2006. 01) | F I<br>G09G<br>G02F<br>G09G<br>G09G | 3/36<br>1/133<br>3/20<br>3/20<br>3/20 | 560<br>611A<br>611G<br>612U                                        | テーマコー<br>2H093<br>5C006<br>5C080 |            |

|--------------------------------------|-----------------------|----------------------------------------|-------------------------------------|---------------------------------------|--------------------------------------------------------------------|----------------------------------|------------|

|                                      |                       |                                        | 審査請求 未                              | 請求 請決                                 | 求項の数 6 OⅠ                                                          | . (全 15 頁)                       | 最終頁に続く<br> |

| (21) 出願番号(22) 出願日                    |                       | 特願2005-85688 (P2<br>平成17年3月24日 (2      | ,                                   | (74) 代理。(74) 代理。(74) 代理。              | セイコーエ;<br>東京都新宿【<br>人 100095728<br>弁理士 上札<br>人 100107076<br>弁理士 藤様 | 岡 英吉                             | 4番1号       |

(72) 発明者 澤田 宗徳

(54) 【発明の名称】表示体駆動回路及び走査電極駆動回路

## (57)【要約】

【課題】 データ信号読み込みのためのクロック信号の 周波数を低くすること。

【解決手段】 データ信号を取り込むことを示す制御信号が入力されたドライバ9に当該データ信号が示す電圧パターンを印加させ、前記制御信号が入力されなかったドライバ9に駆動対象の走査電極に対応する画素列をNon-Selection状態とする電圧パターンを印加させるようにし、また、前記Non-Selection状態となるドライバ9に取得させるデータ信号を省略したデータ信号を用いるようにした。そのため、コレステリック液晶パネル6を適切にDDS駆動することができ、前記省略したデータ信号の分だけ、取得させるデータの数を少なくすることができ、その結果、データ信号を読み込むためのクロック信号の周波数を低くすることができる。

【選択図】 図3

### 【特許請求の範囲】

### 【請求項1】

所定の表示体の各走査電極に対応する画素列を複数の状態のいずれかとする電圧を、当該走査電極それぞれに印加することで、表示体を駆動する表示体駆動回路であって、

カスケード接続され、走査電極に所定電圧を印加する複数のドライバと、

前記画素列のうち既定の状態とする画素列を除いた画素列の状態を示すデータ信号を、前記複数のドライバに出力するデータ信号出力手段と、

その出力されたデータ信号を、当該データ信号が状態を示す画素列の走査電極に対応するドライバに入力するデータ信号入力手段と、

そのデータ信号が入力されたドライバに前記画素列を当該データ信号が示す状態とする電圧を印加させ、前記データ信号が入力されなかったドライバに前記画素列を前記既定の状態とする電圧を印加させる電圧印加手段とを備えたことを特徴とする表示体駆動回路。

### 【請求項2】

前記表示体は、コレステリック液晶パネルであり、前記データ信号出力手段は、前記コレステリック液晶パネルの D D S 駆動時にPreparation状態、Selection状態及びEvolution状態のいずれかの状態とする画素列の状態を示すデータ信号を前記複数のドライバに出力し、前記電圧印加手段は、前記データ信号出力手段から出力されるデータ信号が入力されたドライバに前記画素列を当該データ信号が示す状態とする電圧を印加させ、前記データ信号が入力されなかったドライバに前記画素列をNon-Selection状態とする電圧を印加させることを特徴とする請求項 1 に記載の表示体駆動回路。

### 【請求項3】

前記請求項1又は2に記載の表示体駆動回路におけるデータ信号入力手段と電圧印加手段とを備えたことを特徴とする走査電極駆動回路。

### 【請求項4】

前記データ信号入力手段は、前記データ信号の取得を示す制御信号が入力されたドライバに前記データ信号を入力することを特徴とする請求項3に記載の走査電極駆動回路。

### 【請求項5】

前記データ信号入力手段は、外部回路から出力される制御信号が入力されたドライバに前記データ信号を入力することを特徴とする請求項4に記載の走査電極駆動回路。

### 【請求項6】

前記データ信号入力手段は、前記制御信号が入力されたドライバへの前記データ信号の入力を開始し、また、当該ドライバの全画素列が前記既定の状態となると、当該ドライバへの前記データ信号の入力を停止し、且つ、当該ドライバに他のドライバに対して前記制御信号を入力させることを特徴とする請求項4に記載の走査電極駆動回路。

## 【発明の詳細な説明】

### 【技術分野】

### [00001]

本発明は、コレステリック液晶パネル等の表示体に配されたデータ電極を駆動する表示体駆動回路、及び当該表示体駆動回路に好適な走査電極駆動回路に関する。

### 【背景技術】

## [ 0 0 0 2 ]

従来、表示体であるコレステリック液晶の配向状態を切り替えることで白黒表示を行うコレステリック液晶パネルの高速駆動方式として、DDS駆動がある(例えば、特許文献1参照)。ここで、DDS駆動は、コレステリック液晶をPreparation状態、Selection状態、及びEvolution状態とする複数の電圧パターンを当該コレステリック液晶に印加することで、コレステリック液晶パネルの書換えを高速に実現する駆動方式である。このようなDDS駆動のための走査電極の駆動回路にあっては、一般に、所定の読込用クロック信号に従い、走査電極に印加する電圧パターンを示すデータ信号を読み込み、そのデータ信号に基づいて、コレステリック液晶をDDS駆動するようになっている。

### [0003]

20

10

30

また、 D D S 駆動方式にあっては、最適な表示を可能とするSelection期間は比較的短く、Selection期間が長くなると、表示対象画像のコントラストが低減してしまう。

【特許文献1】米国特許第5748277号明細書

【発明の開示】

【発明が解決しようとする課題】

[0004]

しかしながら、上記従来の駆動回路にあっては、DDS駆動方式におけるSelection期間(最短期間)にデータ信号を全て読み込むようになっているため、例えば、高精細ディスプレイ(例えば、4000ライン)において、Selection期間を短くしようとすると(例えば、0.1ms)、データ信号読み込みのためのクロック信号の周波数が高くなってしまい(例えば、40MHz)、その結果、消費電力が増大してしまう恐れや、安定動作が得られなくなる恐れがあった。

[00005]

本発明は、上記従来の技術の問題点を解決することを目的とするものであって、データ信号読み込みのためのクロック信号の周波数を低くすることができる表示体駆動回路、及び当該表示体駆動回路に好適な走査電極駆動回路を提供することを課題とする。

【課題を解決するための手段】

[0006]

上記課題を解決するために、本発明の表示体駆動回路は、所定の表示体の各走査電極に対応する画素列を複数の状態のいずれかとする電圧を、当該走査電極それぞれに印加することで、表示体を駆動する表示体駆動回路であって、カスケード接続され、走査電極に所定電圧を印加する複数のドライバと、前記画素列のうち既定の状態とする画素列を除いた画素列の状態を示すデータ信号を、前記複数のドライバに出力するデータ信号出力手段と、その出力されたデータ信号を、当該データ信号が状態を示す画素列の走査電極に対応するドライバに入力するデータ信号入力手段と、そのデータ信号が入力されたドライバに前記画素列を当該データ信号が示す状態とする電圧を印加させ、前記データ信号が入力されなかったドライバに前記画素列を前記既定の状態とする電圧を印加させる電圧印加手段とを備えたことを特徴とする。

[0007]

また、前記表示体は、コレステリック液晶パネルであり、前記データ信号出力手段は、前記コレステリック液晶パネルのDDS駆動時にPreparation状態、Selection状態及びEvolution状態のいずれかの状態とする画素列の状態を示すデータ信号を前記複数のドライバに出力し、前記電圧印加手段は、前記データ信号出力手段から出力されるデータ信号が入力されたドライバに前記画素列を当該データ信号が示す状態とする電圧を印加させ、前記データ信号が入力されなかったドライバに前記画素列をNon-Selection状態とする電圧を印加させるようにしてもよい。

[00008]

一方、上記課題を解決するために、本発明の走査電極駆動回路は、前記請求項1又は2 に記載の表示体駆動回路におけるデータ信号入力手段と電圧印加手段とを備えたことを特徴とする。

また、前記データ信号入力手段は、前記データ信号の取得を示す制御信号が入力されたドライバに前記データ信号を入力するようにしてもよい。

[0009]

さらに、前記データ信号入力手段は、外部回路から出力される制御信号が入力されたドライバに前記データ信号を入力するようにしてもよい。

また、前記データ信号入力手段は、前記制御信号が入力されたドライバへの前記データ信号の入力を開始し、また、当該ドライバの全画素列が前記既定の状態となると、当該ドライバへの前記データ信号の入力を停止し、且つ、当該ドライバに他のドライバに対して前記制御信号を入力させるようにしてもよい。

[0010]

10

20

30

30

40

50

このような構成によれば、全画素列が非選択状態となるドライバに取得させるデータ信号を省略し、ドライバに取得させるデータの数を少なくすることができ、その結果、データ信号を読み込むためのクロック信号の周波数を低くすることができる。

【発明を実施するための最良の形態】

### [0011]

以下、本発明に係る表示体駆動回路、及び走査電極駆動回路を電子ブックリーダに適用した実施形態を図面に基づいて説明する。

<第1実施形態>

< 電子ブックリーダの構成 >

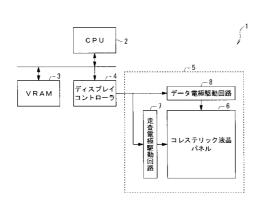

図 1 は、本発明を適用した電子ブックリーダ 1 の内部構成を示すブロック図である。この電子ブックリーダ 1 は、図 1 に示すように、 C P U (Central Processing Unit) 2 、 V R A M (Video Random Access Memory) 3 、ディスプレイコントローラ 4 、及びディスプレイ 5 を含んで構成される。

[ 0 0 1 2 ]

CPU2は、記憶装置(不図示)に格納された基本制御プログラムやアプリケーションプログラム等の各種プログラム及びデータを読み込み、それら各種プログラム及びデータをワークエリアに展開して、電子ブックリーダ 1 が備える各部 3 ~ 8 の制御を実行する。また、CPU2は、ディスプレイ 5 の表示状態の書き換え指令があると、表示対象画像のビットマップデータを生成し、そのビットマップデータをVRAM 3 に格納させる。

[0013]

VRAM3は、CPU2からビットマップデータの書き込み要求があると、そのビットマップデータを格納する。また、VRAM3は、ビットマップデータの読み出し要求があると、その要求されたビットマップデータをディスプレイコントローラ4に出力する。 ディスプレイコントローラ4は、ディスプレイ5の表示状態の書き換え指令があると、 後述するドライバ駆動許可処理を実行する。そして、ディスプレイコントローラ4は、そ

後述するドライバ駆動許可処理を実行する。そして、ディスプレイコントローラ 4 は、そのドライバ駆動許可処理が実行されると、まず、コレステリック液晶パネル 6 の全画素行(平面視横方向に伸びている行の画素群)をNon-Selection状態とする指令(以下「Non-Selection状態指令」とも呼ぶ。)をディスプレイ 5 (走査電極駆動回路 7 (後述))に出力する。走査電極ドライバ 7 は、図 3 に示すように、ドライバ 9 から構成され、内部にデータ用シフトレジスタ 1 0 、データラッチ 1 1 、データ生成回路 1 2 、及びレベルシフタ 1 3 を有する。次に、平面視上側から 1 番目と 2 番目のドライバ 9 (データ用シフトレジスタ 1 0 )にデータ信号を取り込むことを示す制御信号を出力する。また、平面視上側から 1 番目のドライバ 9 にデータ信号を取り込むことを示す制御信号を出力する(平面視上側から 1 番目のドライバ 9 にデータ信号の取り込むことを示す制御信号を出力する(平面視上側から 1 番目のドライバ 9 にデータ信号の取り込むことを示す制御信号を順次出力するようになっている。

[0014]

また、ディスプレイコントローラ4は、ディスプレイ5の表示状態の書き換え指令があると、VRAM3からビットマップデータを読み出し、そのビットマップデータを平面視上側の画素行のものから順にディスプレイ5のデータ電極駆動回路8に出力する。

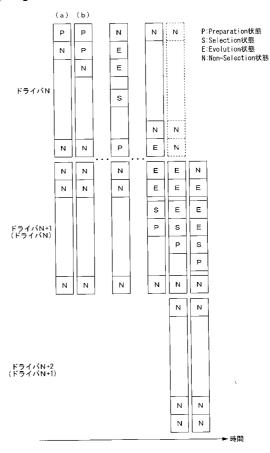

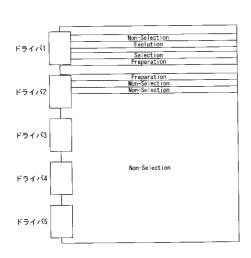

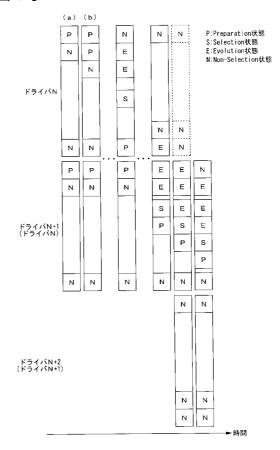

さらに、ディスプレイコントローラ 4 は、ドライバ駆動許可処理の制御信号によってデータ信号の取得が許可される互いに隣り合う 2 つのドライバ 9 の各画素行それぞれをPreparation状態、Selection状態、Evolution状態、Non-Selection状態のいずれの状態とするのかを示すデータ信号を走査電極駆動回路 7 に出力する。ここで、データ信号としては、図 2 に示すように、各画素行の状態の組み合わせからなる複数のパターンを所定の順序で繰り返し出力するようになっている。具体的には、まず、図 2 (a)に示すように、平面視上端の画素行をPreparation状態とし、その他の画素行をNon-Selection状態とするパターンを示すデータ信号を出力する。次いで、図 2 (b)に示すように、平面視上側から 1 番目と 2 番目の画素行をPreparation状態とし、その他の画素行をNon-Selection状態と

20

30

40

するパターンを示すデータ信号を出力する。そして、Preparation状態とする画素行を平面視下側へと徐々に増やしていき、所定個数(予め設定されたPreparation期間に対応する個数)となると、以下同様に、Selection状態とする画素行、Evolution状態とする画素行、Non-Selection状態とする画素行を平面視上側から平面視下側へと徐々に増やしていくパターンを示すデータ信号を順次出力する。なお、上記データ信号の出力を繰り返すうちに、前記2つのドライバ9のうち、平面視上側のドライバ9の平面視下端の画素行をEvolution状態とするパターンを示すデータ信号が出力されたときには、次いで、平面視下側のドライバ9の状態を示すパターンを平面視上側のドライバ9のパターンとし、且つ、平面視下側のドライバ9の全画素行をNon-Selection状態とするパターンを示すデータ信号を出力する。

[0015]

ディスプレイ 5 は、コレステリック液晶パネル 6 、走査電極駆動回路 7 及びデータ電極 駆動回路 8 を含んで構成される。

コレステリック液晶パネル 6 は、ディスプレイ 5 の平面視中央部に配される。そして、コレステリック液晶パネル 6 は、コレステリック液晶が封入されたコレステリック液晶層 (不図示)と、そのコレステリック液晶層の上面側で平面視横方向に伸びている複数の走 査電極 (不図示)と、コレステリック液晶層の下面側で平面視縦方向に伸びている複数のデータ電極 (不図示)とを備え、走査電極とデータ電極との交差点に画素が形成される。 【 0 0 1 6 】

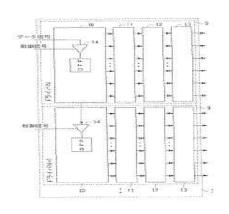

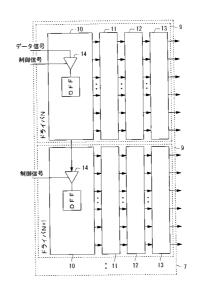

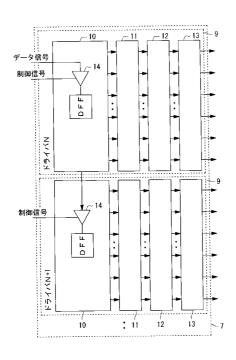

走査電極駆動回路 7 は、図 3 に示すように、コレステリック液晶パネル 6 の平面視左側に配されて互いにカスケード接続されてなる複数のドライバ 9 (ディスプレイコントローラ 4 から出力されるデータ信号を平面視上側のものから順次送っていくドライバ 9 ) を含んで構成される。これら複数のドライバ 9 は、データ用シフトレジスタ 1 0、データラッチ 1 1、データ生成回路 1 2、及びレベルシフタ 1 3 をそれぞれ含んで構成される。

[0017]

データ用シフトレジスタ10は、ディスプレイコントローラ4から出力される制御信号に基づき、ディスプレイコントローラ4から出力されるデータ信号を対応するドライバ9に取り込むか否かを切り替えるドライバデータ入力部14を備える。そして、データ用シフトレジスタ10は、データ信号を取り込むことを示す制御信号が出力されると、読込用クロック信号の有為なエッジが現れる度に、ディスプレイコントローラ4から出力されるデータ信号を平面視上側にある走査電極に対応づけられているものから順に1走査電極分ずつ取得する。即ち、データ信号を取り込むことを示す制御信号が出力されたデータ用シフトレジスタ10には、対応付けられている走査電極の新しいデータ信号が格納される。

[0018]

なお、データ用シフトレジスタ 1 0 は、データ信号を取り込むことを示す制御信号が出力されない場合には、読込用クロック信号に関わらず、ディスプレイコントローラ 4 から出力されるデータ信号を取り込まないものとするため、該データ信号は平面視下側のドライバ 9 に入力される。

データラッチ11は、データ用シフトレジスタ10にデータ信号が格納された場合には、所定のラッチ信号の有為なエッジが現れる度に、データ用シフトレジスタ10に格納されているデータ信号をラッチする。また、データラッチ11は、データ用シフトレジスタ10にデータ信号が格納されなかった場合には、それまで当該データラッチ11がラッチしていたデータ信号を再びラッチする。なお、初期状態にあっては、前記それまでデータラッチ11がラッチしていたデータ信号として、走査電極をNon-Selection状態とするデータ信号がラッチされているとする。即ち、データラッチ11には、ディスプレイコントローラ4から出力されるデータ信号が補完されてなるデータ信号がラッチされる。

[0019]

データ生成回路 1 2 は、データラッチ 1 1 にラッチされているデータ信号に対応する D D S 駆動のための電圧パターンのデータを各走査電極それぞれについて生成する。

レベルシフタ13は、データ生成回路12で生成された電圧パターンのデータを取得し 50

、その取得されたデータが示す電圧パターンを各走査電極それぞれに印加する。

データ電極駆動回路8は、コレステリック液晶パネル6の平面視上側に配され、各データ電極の平面視上端それぞれに接続される。そして、データ電極駆動回路8は、ディスプレイコントローラ4から出力されるビットマップデータが表示されるように、コレステリック液晶層をDDS駆動して書き換えるための電圧パターンをデータ電極に印加する。

### [0020]

そして、ディスプレイ 5 は、走査電極及びデータ電極に印加された電圧によって当該走査電極及びデータ電極間に電位差を生じさせ、コレステリック液晶パネル 6 の各画素に電圧を印加して D D S 駆動することで、当該各画素におけるコレステリック液晶の配向状態(白色、黒色)を変化させ、表示対象画像をコレステリック液晶パネル 6 に表示する。また、ディスプレイ 5 は、コレステリック液晶パネル 6 の全画素行(平面視横方向に伸びている行の画素群)をNon-Selection状態とする指令(以下「Non-Selection状態指令」とも呼ぶ。)が C P U 2 から出力されると、走査電極及びデータ電極に所定電圧を印加し、それらの電圧によって電位差を生じさせ、Non-Selection状態に変化させる。

### [0021]

< ディスプレイコントローラの動作 >

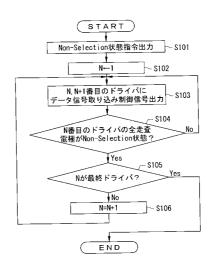

次に、ディスプレイコントローラ 4 で実行されるドライバ駆動許可処理について説明する。このドライバ駆動許可処理は、コンテンツの切り替え表示要求(ディスプレイ 5 の表示状態の書き換え指令)があると実行される処理であって、図 4 に示すように、まずそのステップ S 1 0 1 で、Non-Selection状態指令をディスプレイ 5 (走査電極駆動回路 7、データ電極駆動回路 8 )に出力する。

### [0022]

次にステップ S 1 0 2 に移行して、新しいデータ信号を取り込ませるドライバ 9 を設定するための変数 N を「 1 」とする。

次にステップS103に移行して、平面視上側からN番目とN+1番目のドライバ9のデータ用シフトレジスタ10に、データ信号を取り込むことを示す制御信号を出力する。

次にステップ S 1 0 4 に移行して、平面視上側から N 番目のドライバ 9 の全走査電極が Non-Selection状態であるか否かを判定する。そして、全走査電極が Non-Selection状態である場合には(Yes)ステップ S 1 0 5 に移行し、Non-Selection状態ではない走査電極もある場合には(No)前記ステップ S 1 0 3 に移行する。

### [0023]

前記ステップS105では、変数Nがドライバ9の総数と等しいか否かを判定する。そして、ドライバ9の総数と等しい場合には(Yes)この演算処理を終了し、等しくない場合には(No)ステップS106に移行する。

前記ステップS106では、変数Nに「1」を加算して新しい変数Nとした後、前記ステップS103に移行する。

### [0024]

< 電子ブックリーダの具体的動作 >

次に、本実施形態の電子ブックリーダ1の動作を具体的状況に基づいて説明する。

まず、利用者が所望のコンテンツを選択し、その選択されたコンテンツの先頭ページをディスプレイ5に表示させる書き換え指令をCPU2に出力したとする。すると、CPU2によって、前記先頭ページの画像のビットマップデータが生成され、そのビットマップデータがVRAM3に格納され、また、ディスプレイコントローラ4によって、その格納されたビットマップデータがVRAM3から読み出され、そのビットマップデータが平面視上側の画素行のものから順にディスプレイ5のデータ電極駆動回路8に出力される。そして、データ電極駆動回路8によって、そのビットマップデータに基づき、コレステリック液晶層をDDS駆動して書き換えるための電圧パターンがデータ電極に印加される。

### [0025]

さらに、ディスプレイコントローラ 4 によって、ドライバ駆動許可処理が実行され、図 4 に示すように、まずそのステップS101で、Non-Selection状態指令がディスプレイ

20

30

40

20

30

40

50

5(走査電極駆動回路 7、データ電極駆動回路 8)に出力される。すると、走査電極駆動回路 7 及びデータ電極駆動回路 8によって、走査電極及びデータ電極に所定電圧が印加され、その印加された電圧によって各画素に電位差を生じさせ、コレステリック液晶パネル6の全画素行をNon-Selection状態とする。なお、ステップ S 1 0 1 では、実際に走査電極 7 及びデータ電極 8 にNon-Selection状態とするためのデータを印加するのみとし、コレステリック液晶パネル6に電圧印加を行わなくてもよい。また、ステップ S 1 0 2 で、変数 N が「1」とされ、ステップ S 1 0 3 で、平面視上側から1番目と2番目のドライバ9のデータ用シフトレジスタ10に、データ信号を取り込むことを示す制御信号が出力される。

## [0026]

また、ディスプレイコントローラ4によって、ドライバ駆動許可処理によってデータ信号の取得が許可された平面視上側から1番目と2番目のドライバ9の各画素行それぞれをPreparation状態、Selection状態、Evolution状態、Non-Selection状態のいずれの状態とするのかを示すデータ信号が走査電極駆動回路7に出力される。すると、1番目と2番目のドライバ9のデータ用シフトレジスタ10によって、読込用クロック信号の有為なエッジが現れる度に、ディスプレイコントローラ4から出力されるデータ信号が平面視上側にある走査電極に対応づけられているものから順に、1走査電極分ずつ取得される。その結果、データ信号を取り込むことを示す制御信号が出力されたデータ用シフトレジスタ10には、対応付けられている走査電極の新しいデータ信号が格納される。

### [0027]

また、平面視上側から1番目と2番目のドライバ9のデータラッチ11によって、データ用シフトレジスタ10に格納されているデータ信号がラッチされる。その際、データ用シフトレジスタ10にデータ信号が格納されなかった(取得されなかった)ドライバ9のデータラッチ11には、ステップS101で入力されたNon-Selection状態とするデータ信号がラッチされる。その結果、データラッチ11には、ディスプレイコントローラ4から出力されるデータ信号が補完されてなるコレステリック液晶パネル6の全走査電極のデータ信号がラッチされる。

### [0028]

さらに、データ生成回路 1 2 によって、データラッチ 1 1 にラッチされたデータ信号に対応する D D S 駆動のための電圧パターンのデータが各走査電極それぞれについて生成される。また、レベルシフタ 1 3 によって、データ生成回路 1 2 で生成された電圧パターンのデータが取得され、そのデータが示す電圧パターンが走査電極それぞれに印加される。また、ステップ S 1 0 4 の判定が「No」となり、前記ステップ S 1 0 3 から上記フローが繰り返し実行され、図 5 に示すように、平面視上側の画素行から順次Preparation状態、Selection状態、Evolution状態、Non-Selection状態と遷移していく。

### [0029]

さらに、平面視上端のドライバ9の全走査電極がNon-Selection状態となったとする。すると、ステップS104の判定が「Yes」となり、ステップS105の判定が「No」となり、ステップS106で、変数Nに「1」が加算されて新しい変数N「2」とされ、前記ステップS103に戻り、平面視上側から2番目と3番目のドライバ9に、データ信号を取り込むことを示す制御信号が出力される。そして、ディスプレイコントローラ4によって、平面視上側から2番目と3番目のドライバ9の各画素行それぞれに対応するデータ信号が走査電極駆動回路7に出力される。すると、平面視上側から2番目と3番目のドライバ9によって、そのデータ信号が取得された後、その他のドライバ9で補完され、その補完されたデータ信号が示す電圧パターンが走査電極それぞれに印加される。

## [0030]

また、ステップS104を経て、上記フローが前記ステップS103から繰り返し実行され、平面視上側から2番目のドライバ9の全走査電極がNon-Selection状態となったとする。前記ステップS104の判定が「Yes」となり、前記ステップS105の判定が再び「No」となり、前記ステップS106で、変数Nに「1」が加算されて新しい変数

N「2」とされ、上記フローが前記ステップS103から繰り返し実行される。

### [0031]

このように、本実施形態の電子ブックリーダ1にあっては、データ信号を取り込むことを示す制御信号が入力されたドライバ9に当該データ信号が示す電圧パターンを印加させ、前記制御信号が入力されなかったドライバ9に駆動対象の走査電極に対応する画素列をNon-Selection状態とする電圧パターンを印加させるようにし、また、前記Non-Selection状態となるドライバ9に取得させるデータ信号を省略したデータ信号を用いるようにした。そのため、コレステリック液晶パネル6を適切にDDS駆動することができ、前記省略したデータ信号の分だけ、取得させるデータの数を少なくすることができ、その結果、データ信号を読み込むためのクロック信号の周波数を低くすることができる。

### [0032]

例えば、走査電極駆動回路7内のドライバ9の総数が10個である場合には、データ信号を取得させるドライバ9が2つであると、読込用クロックの周波数は1/5となる。

また、クロック信号の周波数を低くすると、表示書き換えの消費電力を小さくでき、また、走査電極駆動回路7及びデータ電極駆動回路8の動作を安定化することができる。

### [0033]

### < 第 2 実施形態 >

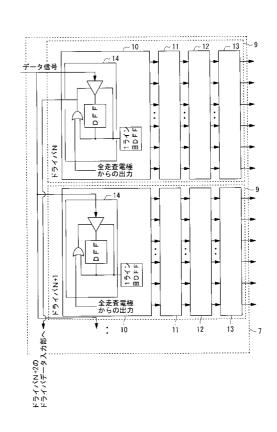

次に、本発明の画像表示装置を電子ブックリーダ1に用いた第2実施形態を説明する。この第2実施形態は、ドライバ9にデータ信号を取り込むことを示す制御信号を当うにで生成がまり平面視上側のドライバ9のデータ用シフトレジスタ10で生成するようので生成が、前記第1実施形態とは異なる。具体的には、第2実施形態では、ドライバ9のデータ用シフトレジスタ10の構成と、ドライバ駆動許可処理のフローの構成とが異なる。するに示すように、平面視上側のドライバ9からで生産でであると、平面視上側から1番目と2番目のドライバ9では、ディスプレイコントローラ4から平面視上側から1番をPreparation状態とするデータ信号が出力されると)、読込用クロック信号の有為なエッジが現れるの状態が引きれるデータ信号を平面視上側にある走査電極に対応づけられているをに、前記出力されるデータ信号を平面視上側にある走査電極に対応でいるものが出力されたデータ用シフトレジスタ10には、対応付けられている走査電極がNon-Selection状態となると、当該ドライバ9によるデータ信号の取り込みを停止し、且つ、平面視2つ下側のドライバ9にデータ信号を取り込むことを示す制御信号を出力する。

### [0034]

## < ディスプレイコントローラの動作 >

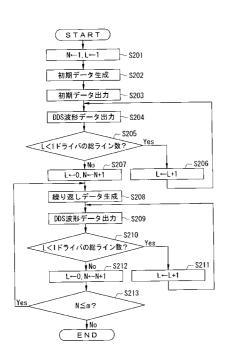

次に、ディスプレイコントローラ 4 で実行されるドライバ駆動許可処理について説明する。このドライバ駆動許可処理は、コンテンツの切り替え表示要求(ディスプレイ 5 の表示状態の書き換え指令)があると実行される処理であって、図 7 に示すように、まずそのステップ S 2 0 1 で、新しいデータ信号を取り込ませるドライバ 9 を設定するための変数 N 及び変数 L を初期化して「1」とする。

### [0035]

次にステップS202に移行して、図8(a)に示すように、平面視上側からN番目とN+1番目のドライバ9の平面視上端の走査電極に対応する画素行をPreparation状態とし、且つ、当該ドライバ9の他の走査電極に対応する画素行をNon-Selection状態とするデータ信号(以下、「初期データ」とも呼ぶ。))を生成する。

次にステップS203に移行して、前記ステップS202で生成された初期データをディスプレイ5(走査電極駆動回路7、データ電極駆動回路8)に出力する。

### [0036]

次にステップS204に移行して、前記ステップS202で生成された初期データに基づき、直前に出力したデータ信号に引き続くデータ信号(以下、「DDS波形データ」とも呼ぶ。)を生成し、その生成されたDDS波形データをディスプレイ5に出力する。

10

20

30

40

具体的には、データ信号としては、図8に示すように、各画素行の状態の組み合わせか らなる複数のパターンを所定の順序で繰り返し出力するようになっている。具体的には、 まず、図8(b)に示すように、まず、平面視上側から2番目のドライバ9の平面視上端 の 走 査 電 に 対 応 す る 画 素 行 を Preparation状 態 に 維 持 し つ つ 、 1 番 目 の ド ラ イ バ 9 の 平 面 視上側から1番目と2番目の走査電極に対応する画素行をPreparation状態とし、その他 の画素行をNon-Selection状態とするパターンを示すDDS波形データを出力する。次い で、平面視上側から2番目のドライバ9の平面視上端の走査電に対応する画素行をPrepar ation状態に維持しつつ、1番目のドライバ 9 の平面視上側から 1 ~ 3 番目の走査電極に 対応する画素行をPreparation状態とし、その他の画素行をNon-Selection状態とするパタ ーンを示す D D S 波形データを出力する。そして、Preparation状態とする画素行を平面 視下側へと徐々に増やしていき、所定個数(予め設定されたPreparation期間に対応する 個数)となると、以下同様に、Selection状態とする画素行、Evolution状態とする画素行 、 Non-Selection状態とする 画 素 行 を 平 面 視 上 側 か ら 平 面 視 下 側 へ と 徐 々 に 増 や し て い く パターンを示すデータ信号を順次出力する。なお、上記データ信号の出力を繰り返すうち に、前記 2 つのドライバ 9 のうち、平面視上側のドライバ 9 の平面視下端の画素行をEvol ution状態とするパターンを示すデータ信号が出力されたときには、次いで、平面視下側 のドライバ9の状態を示すパターンを平面視上側のドライバ9のパターンとし且つ平面視 下 側 の ドラ イ バ 9 の 全 画 素 行 を Non-Se lection 状 態 と す る パ タ ー ン を 示 す デ ー タ 信 号 ( 以 下、「繰り返しデータ」とも呼ぶ。)を出力する。

### [0037]

次にステップS205に移行して、変数Lが1つのドライバ9の総ライン数より小さいか否かを判定する。そして、総ライン数より小さい場合には(Yes)ステップS206に移行し、総ライン数以上である場合には(No)ステップS207に移行する。

前記ステップS206では、変数Lに「1」を加算して新しい変数「1」としてから、前記ステップS203に移行する。

### [0038]

一方、前記ステップS207では、変数Lを「0」とし、また、変数Nに「1」を加算 して新しい変数Nとしてから、ステップS208に移行する。

次にステップS208に移行して、繰り返しデータを生成する。

次にステップS209に移行して、前記ステップS208で生成された繰り返しデータに基づき、直前に出力したDDS波形データに引き続くDDS波形データを生成し、その生成されたDDS波形データをディスプレイ5に出力する。

### [0039]

次にステップS210に移行して、変数Lが1つのドライバ9の総ライン数より小さいか否かを判定する。そして、総ライン数より小さい場合には(Yes)ステップS211に移行し、総ライン数以上である場合には(No)ステップS212に移行する。

次にステップ S 2 1 1 に移行して、変数 L に「 1 」を加算して新しい変数 L としてから、前記ステップ S 2 0 9 に移行する。

## [0040]

一方、前記ステップS212では、変数 L を「 0 」とし、また、変数 N に「 1 」を加算 して新しい変数 N としてから、ステップS213に移行する。

前記ステップS213では、変数Nがドライバ9の総数m以下であるか否かを判定する。そして、ドライバ9の総数以下である場合には(Yes)前記ステップS207に移行し、ドライバ9の総数より大きい場合には(No)この演算処理を終了する。

### [ 0 0 4 1 ]

<電子ブックリーダの具体的動作>

次に、本実施形態の電子ブックリーダ1の動作を具体的状況に基づいて説明する。

まず、利用者が所望のコンテンツを選択し、その選択されたコンテンツの先頭ページをディスプレイ 5 に表示させる書き換え指令をCPU2に出力したとする。すると、CPU2によって、前記先頭ページの画像のビットマップデータが生成され、そのビットマップ

20

10

30

40

20

30

50

データがVRAM3に格納され、また、ディスプレイコントローラ4によって、その格納されたビットマップデータがVRAM3から読み出され、そのビットマップデータが平面視上側の画素行のものから順にディスプレイ5のデータ電極駆動回路8に出力される。そして、データ電極駆動回路8によって、そのビットマップデータに基づき、コレステリック液晶層をDDS駆動して書き換えるための電圧パターンがデータ電極に印加される。

[0042]

さらに、ディスプレイコントローラ4によって、ドライバ駆動許可処理が実行され、図7に示すように、まず、そのステップS201で、変数N及び変数Lが初期化されて「1」とされる。次いで、ステップS202で、その初期化された変数Nに基づいて初期データが生成され、ステップS203で、その生成された初期データがディスプレイ5(走査電極駆動回路7、データ電極駆動回路8)に出力される。すると、平面視上側から1番目と2番目のドライバ9がデータ信号を取り込み可能な状態となり、走査電極駆動回路7及びデータ電極駆動回路8によって、走査電極及びデータ電極に所定電圧が印加され、その印加された所定電圧によって各画素に電位差を生じさせ、平面視上側から1番目と2番目のドライバ9の中面視上端の走査電極に対応する画素行がPreparation状態となり、当該ドライバ9の他の走査電極に対応する画素行がNon-Selection状態となる。なお、その際、その他のドライバ9に対応する全画素行もNon-Selection状態となる。

[0043]

また、ステップS204で、前記出力された初期データに引き続くDDS波形データがディスプレイ5に出力される。すると、ディスプレイ5によって、平面視上側から2番目のドライバ9の平面視上端の走査電に対応する画素行がPreparation状態に維持された状態で、1番目のドライバ9の平面視上側から1番目と2番目の走査電極に対応する画素行がPreparation状態となり、その他の画素行がNon-Selection状態となる。

[0044]

さらに、ステップS205の判定が「Yes」となり、ステップS206で、変数Lに「1」が加算されて新しい変数L「2」とされ、前記ステップS204に戻り、当該ステップS204で前回出力されたDDS波形データに引き続くDDS波形データがディスプレイ5に出力される。すると、ディスプレイ5によって、平面視上側から2番目のドライバ9の平面視上端の走査電に対応する画素行がPreparation状態に維持された状態で、平面視上側から1番目のドライバ9の平面視上側から1~3番目の走査電極に対応する画素行がPreparation状態となり、その他の画素行がNon-Selection状態となる。

[0045]

また、前記ステップS205の判定が「No」となり、前記ステップS206から上記フローが繰り返し実行され、平面視上端のドライバ9の画素行が順次Preparation状態、Selection状態、Evolution状態、Non-Selection状態と遷移していく。

さらに、変数しが1つのドライバ9の総ライン数と等しくなり、平面視上側から1番目のドライバ9の全走査電極がNon-Selection状態となったとする。すると、平面視上側から1番目のドライバ9によるデータ信号の取り込みが停止され、データ用シフトレジスタ10から平面視上側から3番目のドライバ9にデータ信号を取り込むことを示す制御信号が出力され、平面視上側から2番目と3番目のドライバ9がデータ信号を取り込みでで、数しが「0」とされ、また、変数Nに「1」が加算されて新しい変数N「2」とされ、ステップS209で、ステップS209で、ステップS209で、ステップS209で、ステップS209で、カロロの対象ので、繰り返しデータが生成されるのことなり、ステップS209に戻りで、さらに、11、が加算されて新しい変数し「2」とされ、前記ステップS211で、変数しに「1」が加算されて新しい変数し「2」とされ、前記ステップS211から上記フローが繰り返し実行され、平面視上側から2番目のドライバ9の画素行が順次Preparation状態、Selection状態、Evolution状態、Non-Selection状態と遷移していく。

#### [0046]

さらに、変数しが1つのドライバ9の総ライン数と等しくなり、平面視上側から2番目 のドライバ9の全走査電極がNon-Selection状態となったとする。すると、平面視上側か ら2番目のドライバ9によるデータ信号の取り込みが停止され、データ用シフトレジスタ 1 0 から平面視上側から 4 番目のドライバ 9 にデータ信号を取り込むことを示す制御信号 が 出 力 さ れ 、 平 面 視 上 側 か ら 3 番 目 と 4 番 目 の ド ラ イ バ 9 が デ ー タ 信 号 を 取 り 込 み 可 能 な 状態となる。また、ステップS210の判定が「No」となり、ステップS212で、変 数Lが「0」とされ、また、変数Nに「1」が加算されて新しい変数N「3」とされる。 そして、ステップS213の判定が「No」となり、前記ステップS208から上記フロ ー が 繰 り 返 し 実 行 さ れ 、 そ の 結 果 、 平 面 視 上 側 か ら 全 画 素 行 が 順 次 Preparation状 態 、 Se I ection状態、Evolution状態、Non-Selection状態と遷移していく。

[0047]

なお、本実施形態では、平面視上側から1番目と2番目のドライバ9にあっては、ディ スプレイコントローラ 4 から平面視上端の走査電極をPreparation状態とするデータ信号 が出力されると、当該ドライバ9にデータ信号を取り込む例を示したが、これに限られる ものではない。例えば、平面視上側から1番目と2番目のドライバ9にあっては、全走査 電極にNon-Selection状態とするデータ信号が出力されていない場合、つまり、Preparati on状態、Selection状態及びEvolution状態、もしくはそれ以外の適当な状態を用意し、そ のいずれかの状態とするデータ信号が出力された場合に当該ドライバ9にデータ信号を取 り込むようにしてもよい。

[0048]

また、ドライバ 9 の全走査電極がNon-Selection状態になると、当該ドライバ 9 による デ ー タ 信 号 の 取 り 込 み を 停 止 し 、 且 つ 、 平 面 視 2 つ 下 側 の ド ラ イ バ 9 に デ ー タ 信 号 を 取 り 込むことを示す制御信号を出力する例を示したが、これに限られるものではない。例えば 、ドライバ9の出力が240ビットである場合には、1bit、10bit、20bit・・・の 走査電極がNon-Selection状態となったときに、当該ドライバ 9 によるデータ信号の取り 込 み を 停 止 し 、 且 つ 、 平 面 視 2 つ 下 側 の ド ラ イ バ 9 に デ ー タ 信 号 を 取 り 込 む こ と を 示 す 制 御信号を出力するようにしてもよい。つまり、DDS駆動にあっては、Preparation状態 やEvolution状態とするデータ信号があると、 1 0 0 ライン程度の期間、Non-Selection状 態とするデータ信号が現れないため、全走査電極の状態(全データ信号)を調べることな く 、 全 走 査 電 極 が Non - Se l ect i on状 態 と な る こ と を 検 出 で き る 。

[0049]

さらに、データ信号を取り込み可能なドライバ9の数を2個とする例を示したが、これ に限定されるものではない。例えば、ドライバ9の出力ピン数が少なく、Preparation状 態 、 Selection状態 及 び Evolution状態 が 3 個 以 上 の ド ラ イ バ 9 に ま た が る 場 合 に は 、 デ ー 夕信号を取り込み可能なドライバ9の数を3個以上(同数)としてもよい。

以上、上記実施形態では、図3のドライバデータ入力部14が特許請求の範囲のデータ 信号入力手段を構成し、以下同様に、図3のデータ用シフトレジスタ10、データラッチ 1 1 、 デ ー タ 生 成 回 路 1 2 、 レ ベ ル シ フ タ 1 3 が 電 圧 印 加 手 段 を 構 成 し 、 図 6 の デ ー タ 用 シフトレジスタ10が制御信号出力手段を構成し、図1のディスプレイコントローラ4が 制御信号出力手段及びデータ信号出力手段を構成する。

なお、本発明の走査電極駆動回路及び画像表示装置は、上記実施の形態の内容に限定さ れるものではなく、本発明の趣旨を逸脱しない範囲で適宜変更可能である。

【図面の簡単な説明】

[0051]

- 【図1】電子ブックリーダの内部構成を示すブロック図である。

- 【図2】データ信号を説明するための説明図である。

- 【 図 3 】図 1 の 走 査 電 極 駆 動 回 路 の 内 部 構 成 を 示 す ブ ロ ッ ク 図 で あ る 。

- 【図4】ドライバ駆動許可処理を説明するためのフローチャートである。

20

10

30

50

- 【図5】電子ブックリーダの動作を説明するための説明図である。

- 【図6】第2実施形態の走査電極駆動回路の内部構成を示すブロック図である。

- 【図7】ドライバ駆動許可処理を説明するためのフローチャートである。

- 【図8】電子ブックリーダの動作を説明するための説明図である。

### 【符号の説明】

### [0052]

1 は電子ブックリーダ、 2 は C P U、 3 は V R A M、 4 はディスプレイコントローラ、 5 はディスプレイ、 6 はコレステリック液晶パネル、 7 は走査電極駆動回路、 8 はデータ電極駆動回路、 9 はドライバ、 1 0 はデータ用シフトレジスタ、 1 1 はデータラッチ、 1 2 はデータ生成回路、 1 3 はレベルシフタ、 1 4 はドライバデータ入力部

# 【図1】

### 【図2】

【図3】 【図4】

【図5】 【図6】

## 【図7】

## 【図8】

# フロントページの続き

(51) Int.CI. F I テーマコード (参考)

G 0 9 G 3/20 6 2 3 V

F ターム(参考) 5C006 AF43 AF59 AF71 BA11 BB12 BB14 BC11 BC16 BC24 BF06

EB05 FA15 FA48

5C080 AA10 BB06 DD26 JJ02 JJ07

| 专利名称(译)        | 显示体驱动电路和扫描电极驱动电路                                                                                                                                                                                                                                                          | <u> </u> |            |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|--|--|--|

| 公开(公告)号        | JP2006267560A                                                                                                                                                                                                                                                             | 公开(公告)日  | 2006-10-05 |  |  |  |

| 申请号            | JP2005085688                                                                                                                                                                                                                                                              | 申请日      | 2005-03-24 |  |  |  |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                 |          |            |  |  |  |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                   |          |            |  |  |  |

| [标]发明人         | 澤田宗徳                                                                                                                                                                                                                                                                      |          |            |  |  |  |

| 发明人            | 澤田 宗徳                                                                                                                                                                                                                                                                     |          |            |  |  |  |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                               |          |            |  |  |  |

| FI分类号          | G09G3/36 G02F1/133.560 G09G3/20.611.A G09G3/20.611.G G09G3/20.612.U G09G3/20.623.V                                                                                                                                                                                        |          |            |  |  |  |

| F-TERM分类号      | 2H093/NA10 2H093/ND39 2H093/ND41 2H093/NF28 5C006/AF43 5C006/AF59 5C006/AF71 5C006 /BA11 5C006/BB12 5C006/BB14 5C006/BC11 5C006/BC16 5C006/BC24 5C006/BF06 5C006/EB05 5C006/FA15 5C006/FA48 5C080/AA10 5C080/BB06 5C080/DD26 5C080/JJ02 5C080/JJ07 2H193 /ZB44 2H193/ZQ31 |          |            |  |  |  |

| 代理人(译)         | 须泽 修                                                                                                                                                                                                                                                                      |          |            |  |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                 |          |            |  |  |  |

### 摘要(译)

要解决的问题:降低时钟信号的频率以读取数据信号。 解决方案:由数据信号指示的电压模式被施加到驱动器9,该驱动器9上输入了指示捕获数据信号的控制信号,而未输入控制信号的驱动器9对应于要驱动的扫描电极。 施加了用于将像素列设置为非选择状态的电压图案,并且使用了通过省略由驱动器9在非选择状态下获得的数据信号而获得的数据信号。 因此,可以通过DDS适当地驱动胆甾型液晶面板6,并且可以通过省略的数据信号的数量来减少要获取的数据的数量,并且因此可以减少用于读取数据信号的时钟信号的频率。 可以降低。 [选择图]图3