# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-350378 (P2006-350378A)

(43) 公開日 平成18年12月28日(2006.12.28)

| (51) Int.C1. |       |                          | F I            |            |     |         |                  | テーマコー          |                            |

|--------------|-------|--------------------------|----------------|------------|-----|---------|------------------|----------------|----------------------------|

| G09G         | 3/36  | (2006.01)                | GO9G           | 3/36       |     |         |                  | 2HO93          |                            |

| G09G         | 3/20  | (2006.01)                | GO9G           | 3/20       | 6   | 1 1 A   |                  | 5C006          |                            |

| G02F         | 1/133 | (2006.01)                | GO9G           | 3/20       | 6   | 1 1 C   |                  | 5C080          |                            |

|              |       |                          | GO9G           | 3/20       | 6   | 1 1 G   |                  |                |                            |

|              |       |                          | GO9G           | 3/20       | 6   | 23B     |                  |                |                            |

|              |       |                          | 審査請            | 求有:        | 請求項 | の数 2    | OL               | (全 10 頁)       | 最終頁に続く                     |

| (21) 出願番号    |       | 特願2006-225135(           | (P2006-225135) | (71) 出力    | 願人  | 5991276 | 67               |                |                            |

| (22) 出願日     |       | 平成18年8月22日 (2006.8.22)   |                | エルジー       |     | - フィ    | - フィリップス エルシーディー |                |                            |

| (62) 分割の表示   |       | 特願平8-310263の分割           |                |            |     | カン      | パニー              | リミテッド          |                            |

| 原出願日         |       | 平成8年11月21日 (1996. 11.21) |                |            |     | 大韓民[    | 国ソウ              | <b>カル</b> , ヨン | <b>ドンポーク</b> ,             |

|              |       |                          |                |            |     | ヨイド・    | ードン              | 20             |                            |

|              |       |                          |                | (74)代      | 理人  | 1000644 | 147              |                |                            |

|              |       |                          |                |            |     | 弁理士     |                  | 正夫             |                            |

|              |       |                          |                | (74)代3     |     | 1000851 |                  |                |                            |

|              |       |                          |                |            |     | 弁理士     |                  | 伸晃             |                            |

|              |       |                          |                | (74) 代3    |     | 1000941 |                  |                |                            |

|              |       |                          |                |            |     | 弁理士     |                  | 談              |                            |

|              |       |                          |                | (74) 代3    |     | 1000969 |                  |                |                            |

|              |       |                          |                | <i>(</i> ) |     | 弁理士     |                  | 伸一             |                            |

|              |       |                          |                | (74)代3     | 理人  | 1001014 |                  |                |                            |

|              |       |                          |                |            |     | 弁理士     | 越智               | 隆夫             | - 44- <del></del> 1- 44- 4 |

|              |       |                          |                |            |     |         |                  | <b>1</b>       | 長終頁に続く                     |

### (54) 【発明の名称】液晶表示装置の駆動装置

# (57)【要約】

【課題】高周波で動作されることにより発生する問題点を解決し、メイン駆動周波数を減少させた液晶表示装置のデータドライバを提供する。

【解決手段】ラッチクロック信号を出力し、第1クロック信号に相応するスタート信号を受信するためのm(整数)-ビットレジスタ回路21と、それぞれn(整数)-ビットデータを有する全ての映像信号を同時に受信し、ソース映像信号に当たる少なくとも2セットの3種の映像信号をラッチし出力するデータラッチ回路22,23と、第3信号発生回路のロード信号に基づいて映像信号を貯蔵及び出力し、前記レジスタのラッチクロック信号に相応する前記データラッチ回路の映像信号をラッチするラインラッチ回路25と、ラインラッチの映像信号をアナログ信号に変換するD/A変換回路27と、D/A変換回路からアナログ信号を出力させるデータ出力回路29とを備えた単一集積回路と;で構成されることを特徴とする。

【選択図】図5

### 【特許請求の範囲】

### 【請求項1】

スタート信号を外部に出力する第1信号発生回路と、第1クロック信号を外部に出力する第2信号発生回路と、ロード信号を外部に出力する第3信号発生回路と、周波数を有するソース映像信号を外部的に発生させるための発生手段と、前記第1クロック信号に相応するスタート信号を受信し、ラッチクロック信号を出力するm(整数)-ビットレジスタ回路と、それぞれn(整数)-ビットデータを有する前記全ての映像信号を同時に受信、ソース映像信号に当たる少なくとも2セットの3種の映像信号をラッチし出力するでリッチ回路と、前記第3信号発生回路のロード信号に基づいて映像信号を格納及びークラッチ回路と、前記レジスタのラッチクロック信号に相応する前記データラッチ回路の映像信号を格納及びカッチするラインラッチの回路と、ラインラッチの映像信号をアナログ信号に変換するD/A変換回路と、 D/A 変換回路と、 ラインラッチの時像信号を出力させるデータ出力回路とを備えた単一集積回路と、 を備え、前記第1クロック信号の周波数が、 3種の映像信号のセット数により、前記ソース映像信号の周波数に比べて減少されるようにすることを特徴とする液晶表示装置の駆動装置。

### 【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明は、液晶表示装置の駆動装置に関するもので、特に液晶表示装置のデータドライバに関するものである。

#### 【背景技術】

### [0002]

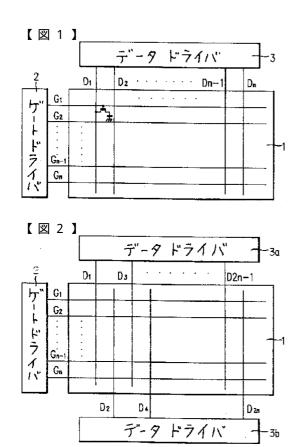

一般的なアクティブマトリックス型(Active Matrix)液晶表示装置は、図1に示すように、ゲートライン(G1~Gn)及びデータライン(D1~Dn)と、各画素をスイッチングする薄膜トランジスタと、画素電極とが配列されている下板と、色相を示すためのカラーフィルタ及び共通電極で構成される上板と、そして前記2枚の上下板の間に埋められている液晶で構成される液晶パネル1と、前記液晶パネル1の各ゲートライン(G1~Gn)に駆動信号を順次に印加するゲートドライバ2と、前記液晶パネル1の各データライン(D1~Dn)に映像データを印加するデータドライバ3とを備える。

### [00003]

このように構成された一般的な液晶表示装置において、最近は液晶パネル 1 の大型化、高解像度化が指向されている。このように、大型化、高解像度化されていくと、液晶表示装置を駆動するために各ドライバ 2 、 3 の駆動周波数が高くなるが、このような高周波で直接駆動可能なドライバ I C の開発は難しい。又、直接可能なドライバ I C が開発されても、高周波 E M I の問題のため、直接駆動が不可能である。

### [0004]

よって、図 2 に示すように、奇数ラインと偶数ラインとに分離して液晶パネル 1 の両側にデータドライバ 3 a , 3 b を形成し、駆動周波数を半減させたことがあった。しかし、図 2 のような液晶表示装置においては、ドライバが両側に形成されるため、液晶表示装置全体で実際に映像をディスプレイする液晶パネルの占める面積が相対的に狭くなり、これにより、大型画面を得るには限界があった。

### [00005]

上述した従来の液晶表示装置の図1のデータドライバ3を添付図面に基づき説明する。

# [0006]

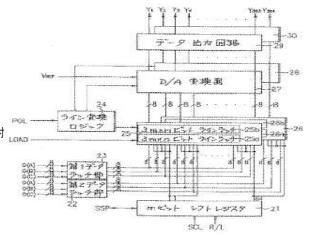

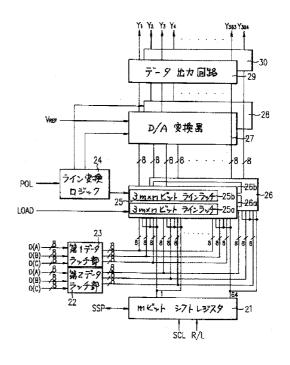

図3は、従来の液晶表示装置のデータドライバの構成ブロック図である。

# [0007]

従来の液晶表示装置のデータドライバは、ソーススタートパルス(SSP)をソースパルスクロック(SCL)によりシフトさせてラッチクロックを出力させるm ビットシフトレジスタ 1 1 と、ソースクロック(SCL)によりディスプレイデータの 3 種 (DA(n), DB(n), D C(n)) をラッチ (Latch) させて出力するデータラッチ部 1 2 と、反転 (Inversion) のた

20

30

50

40

10

20

30

40

50

めに外部のPOL信号により水平区間ごとに極性を切り換えるライン変換ロジック(Line Conversion Logic)14と、前記シフトレジスタ11から出力されたラッチクロックにより前記データラッチ部12から出力された一水平ラインの全てのディスプレイデータを外部のロード(LOAD)信号及び前記ライン変換ロジック14の出力によりライン別にラッチさせ貯蔵する3mxnビットの2ラインラッチ部13と、前記ラインラッチ部12から出力されたデータを液晶に印加するアナログ信号に変換するために外部基準電圧により形成された2n個のレベルのうちの1つの電圧を選択して出力するD/A変換器15と、前記D/A変換器15から出力される信号を充分な駆動能力と出力電圧偏差の少ない安定された電圧に増幅して液晶に印加するデータ出力回路16とを備える。

[00008]

このように構成された従来のデータドライバの動作について説明する。

[0009]

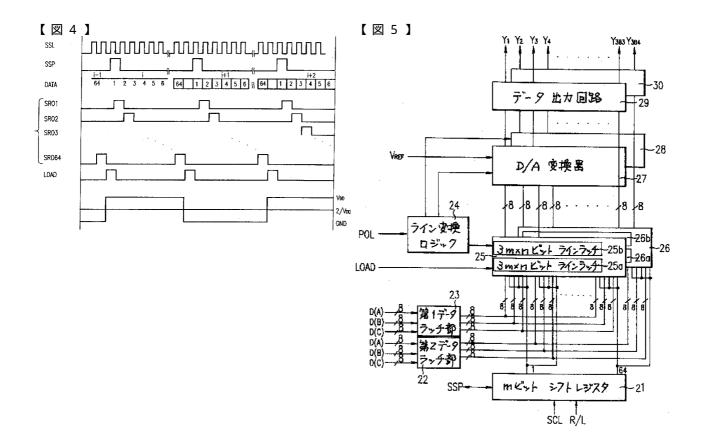

図4は、従来のデータドライバの動作タイミング図である。

[0010]

まず、シフトレジスタ11は、ソースクロック(SCL)とソーススタートパルス(SSP)を入力してm個のラッチクロック(SR01、SR02、SR03、・・・、SR0m)(m= 64)を順次にラインラッチ部13へ出力する。ソースクロック(SCL)は、X G A で約65MHzの周波数を有するクロック信号である。

[0011]

そして、データラッチ部12は、 n ビットディスプレイデータの3種(DA(n),DB(n), D C(n)) を前記ソースクロック (SCL) の下降エッジにラッチさせてラインラッチ部13へ出力する。したがって、ラインラッチ部13は、前記ソースクロックの下降エッジにラッチされた n ビットディスプレイデータを前記シフトレジスタ11から出力されたラッチクロック (SR01, SR02, SR03,・・・, SR0m)により3m× n ビットの1番目のラインラッチ部13aにラッチさせる。一ラインデータは一水平ラインのディスプレイデータを貯蔵した後に外部のロード(LOAD)信号により一度に2番目のラインラッチ部13bへ貯蔵される。同時に次のラインデータはシフトレジスタ11から出力されたラッチクロック(SR01, SR02,SR03,・・・, SR0m)により1番目のラインラッチ部にラッチされる。このような動作は繰り返し行われる。

[0012]

このようにラインラッチ部 1 3 により貯蔵されたラインデータは D / A 変換器 1 5 へ出力される。

[0013]

D / A 変換器 1 5 は、内部のデータで外部基準電圧(V R E F )により形成された 2 n 個のレベルのうちの前記ラインラッチ部 1 3 から入力されたラインデータに相応する 1 つの電圧を選択して出力する。この際、外部の P O L 信号によりライン変換ロジック 1 4 はラインごとの極性を転換して反転を容易にする。

[0014]

前記 D / A 変換器 1 5 から選択されて出力されたアナログ信号はデータ出力回路 1 6 により充分な駆動能力と出力電圧偏差の少ない安定な電圧として液晶に印加されてディスプレイされる。

【発明の開示】

【発明が解決しようとする課題】

[0015]

しかし、このような従来のデータドライバにおいては、次のような問題点があった。

[0016]

最近の液晶表示装置の大画面・高解像度の傾向にしたがい、液晶ノートパーソルナルコンピューター、モニタなどの応用において、最大の難題は、解像度に応ずる高い動作周波数の問題(XGAは65MHz、EWSは107MHz)であり、既存のデータドライバICの動作周波数は5V駆動時に55MHz(3.3V駆動時に40MHz)であるため

10

20

30

40

50

、直接駆動が不可能である。又、直接駆動可能なドライバICが開発されるとしても、高 周波EMIの問題のため、直接駆動が不可能である。

### [0017]

一方、上記のような従来のデータドライバの外部にラインメモリを設け、データの 2 分割駆動、又はIC別分割駆動を介して周波数を 1 / 2 に低くすることはできる。しかし、この場合にはラインメモリの使用により製品のコスト及び重量が増加する。したがって、消費電力及び体積も増加する。

# [ 0 0 1 8 ]

本発明は、前述した問題点を解決するためのもので、その目的は、高周波で動作されることにより発生する問題点を解決し、メイン駆動周波数を減少させた液晶表示装置のデータドライバを提供することにある。

### 【課題を解決するための手段】

### [0019]

このような目的を達成するための本発明の液晶表示装置の駆動装置は、スタート信号を外部に出力する第1信号発生回路と;第1クロック信号を外部に出力する第2信号発生回路と;周波数を有するソース映像信号を外部に出力する第3信号発生回路と;周波数を有するソース映像信号を外部に出力させるための発生手段と;そしてラッチクロック信号を出力し、前記第1クロック信号に相応するスタート信号を受信するためのm(整数)-ビットレジスタ回路と、それぞれn(整数)-ビットデータを有する前記全ての映像信号を同時に受信し、ソース映像信号に当たる少なくとも2セットの3種の映像信号を同時に受信でリンクに当たる少なくとも2セットの3種の映像信号をラッチし出力するデータしまび出力するが3種の映像信号を開放しまするラインラッチの関路と、ラインラッチの映像信号を出力に変換するD/A変換回路からアナログ信号を出力させるデータ出力回路とを備えた単同路と;で構成され、前記第1クロック信号の周波数が3種の映像信号のセット数により前記ソース映像信号の周波数に比べて減少されるようにすることを特徴とする。

# [0020]

### [0021]

又、本発明の液晶表示装置の駆動装置は、ソーススタート信号を外部に出力する第1信号発生回路と;第1クロック信号を外部に出力する第2信号発生回路と;ロード信号を外部に出力する第3信号発生回路と;をして第1クロック信号に相応するソーススタート信号をシフティングさせ、サンプリングクロック信号を出力するレジスタ回路と、LCDピクセルにそれぞれ表れる全ての映像信号を同時に受信し、少なくとも2セットの3種の映像信号をサンプリングし出力するデータサンプリング回路と、前記第3信号発生回路のロード信号に基づいて映像信号を貯蔵及び出力し、前記シフトレジスタのラッチクロック信号に相応する前記データラッチの映像信

号をラッチし、前記第3信号発生回路のロード信号に相応する前記映像信号を貯蔵して出力する3m× n ラインラッチ回路と、データラッチから映像信号の極性を反転させる極性反転回路と、前記ラッチ回路の映像信号をアナログ信号に変換するD/A変換回路と、前記D/A変換回路からアナログ信号を出力させるデータ出力回路とを備えた単一集積回路と;で構成され、前記3種の映像信号の数により駆動装置の駆動周波数が減少されるようにすることを特徴とする。

【発明の効果】

[0022]

上述したような本発明の液晶表示装置の駆動装置は、次のような効果がある。

[ 0 0 2 3 ]

すなわち、本発明の駆動装置はメイン駆動周波数を 1 / 2 又は 1 / 3 にドライバ自体で低くすることにより、外部のメモリ及び回路を無くし、高周波 E M I 等に有利であるモジュールにより作ることができ、共にコストの節減、製品の目方及び体積の減少、消費電力の減少等の効果が得られる。

[0024]

又、ノートパーソルナルコンピューター及びモニタに X G A 、 E W S 解像度をシングル 、又はダブル構造で実現できる。

【発明を実施するための最良の形態】

[0025]

発明の実施の形態1.

以下、図面に基づき本発明の実施の形態1を説明する。

[0026]

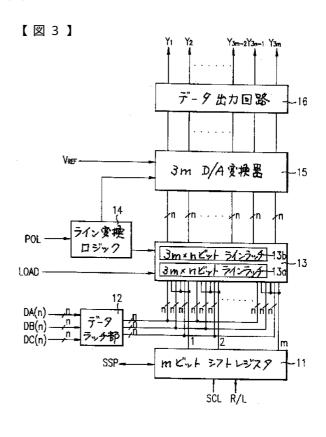

図5は、データラインの奇数部分と偶数部分に印加されるデータを分離して並列に処理することによりデータドライバの動作周波数を半減させた実施の形態1のIC構造であり、図7は、その動作の波形である。なお、図5において、スタート信号(SSP)を外部に出力する第1信号発生回路と、第1クロック信号を外部に出力する第2信号発生回路と、ロード信号(LOAD)を外部に出力する第3信号発生回路と、周波数を有するソース映像信号を外部に出力させるための発生手段と、極性を有する信号を外部に出力するための第4信号発生回路と、データラッチから映像信号の極性を反転させる極性反転回路は図示が省略されている。また、3種の映像信号A‐Cは、例えば、それぞれ各ピクセルのR、G、Bの値である。

[0027]

mビットのシフトレジスタ 2 1 には、周波数の 1 / 2 のソースクロック (SCL) が印加され、このソースクロックとソーススタートパルス (SSP) によりラッチパルス (図 7 のSR01, SR02,・・・)を発生する。又、ドライバICの外部で奇数、偶数に分離されたデータは、第 1 データラッチ部 2 2 と第 2 データラッチ部 2 3 にそれぞれラッチされる。そして、第 1 、第 2 ラッチ部 2 2 、 2 3 にラッチされた n ビット奇数データの 3 種と偶数データの 3 種はシフトレジスタ 2 7 のラッチパルスにより 3 m×n ビットの奇数ラインの第 1 ラッチ 2 5 a と偶数ラインの第 1 ラッチ 2 5 a と偶数ラインの第 1 ラッチ 2 6 a にそれぞれラッチされる。

[0028]

第1ラッチライン25a、26aに貯蔵された一水平ラインのディスプレイデータは、ロード信号の1度で、奇数と偶数の第2ラインラッチ25b、26bに貯蔵されると共に次のラインのデータはシフトレジスタのラッチパルスにより第1ラインラッチ25a、26aに順次にラッチされる。奇数と偶数の第2ラインラッチ25b、26bに貯蔵されたラインデータはそれぞれのD/A変換器27、28により2つの基準電圧の中で該電圧を選択するようになる。

[0029]

この際、ライン変換ロジック24は、電圧の極性を切換って反転(Inversion)を容易にする。選択された基準電圧は、データ出力回路29、30を介して充分な駆動能力と出力電圧偏差の少ない安定された電圧として液晶に印加される。

10

20

30

40

50

10

20

30

40

[0030]

一方、上記の実施の形態において、データを到着する順序どおりに第1、第2ラッチ部22、23に貯蔵させて動作させ、2つのデータ出力回路29、30の出力端子を3個ずつ交互に液晶パネルのデータラインと連結させる方法もある。

[0031]

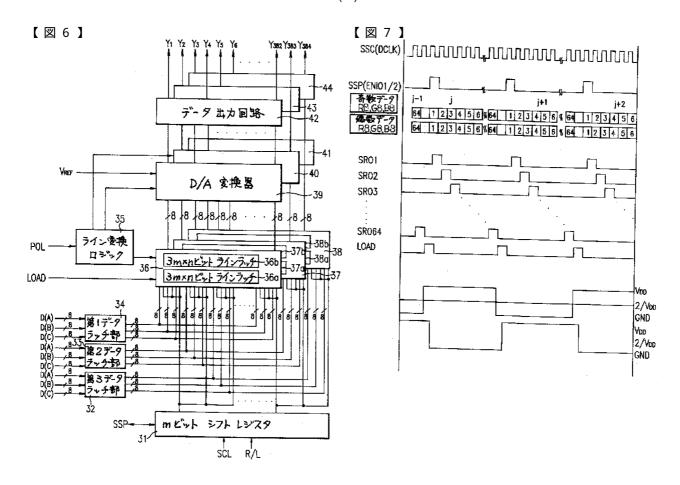

発明の実施の形態2.図6は、本発明の実施の形態2である。

[0032]

実施の形態 1 では、データを奇数と偶数と分離したが、本実施の形態では、3 つのデータラッチ部 3 2 、 3 3 、 3 4 を設け、第 1 データラインのデータは第 1 ラッチ部 3 2 に、第 2 データラインのデータは第 2 ラッチ部 3 3 に、第 3 データラインのデータは第 3 ラッチ部 3 4 に印加し、第 4 データライン、第 5 データライン、第 6 データラインのデータを再び第 1 、第 2 、第 3 ラッチ部にそれぞれ印加する方法でデータを分離する。

[0033]

又、シフトレジスタ31には並列駆動しない場合の1/3の周波数を印加することにより、結局、データドライバICの動作周波数を1/3に減少させ得る。

[0034]

その以外の動作は、実施の形態1と同様である。

[0035]

上記の発明の実施の形態 1、2は、データドライバを液晶パネルの一方にのみ取り付けた場合であるが、これのようなドライバを図2に示すようにダブル構造に形成すると、メイン駆動周波数を2倍も減少させ得る。

【図面の簡単な説明】

- [0036]

- 【図1】一般的な液晶表示装置の構成ブロック図。

- 【 図 2 】 一 般 的 な ダ ブ ル ド ラ イ バ を 有 す る 液 晶 表 示 装 置 の 構 成 ブ ロ ッ ク 図 。

- 【図3】従来の液晶表示装置のデータドライバの構成ブロック図。

- 【図4】図3のドライバの動作タイミング図。

- 【 図 5 】 本 発 明 の 実 施 の 形 態 1 の 液 晶 表 示 装 置 の デ ー タ ド ラ イ バ の 構 成 ブ ロ ッ ク 図 。

- 【図6】本発明の実施の形態2の液晶表示装置のデータドライバの構成ブロック図。

- 【図7】本発明の実施の形態1のドライバの動作タイミング図。

【符号の説明】

- [0037]

- 2 1 、 3 1 シフトレジスタ

- 22、23、32、33、34 データラッチ部

- 2 4 、 3 5 ライン変換ロジック

- 25、26、36、37、38 ラインラッチ部

- 25a、25b、26a、26b、36a、36b、37a、37b、38a、38b ラインメモリ

- 27、28、39、40、41 D/A変換器

- 29、30、42、43、44 データ出力回路

### 【手続補正書】

【提出日】平成18年9月20日(2006.9.20)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

# 【請求項1】

2m個のラインを含むアクティブマトリックス型液晶パネルと該液晶パネルの一方の側辺に配置された液晶パネル駆動装置とからなる液晶表示装置において、該駆動装置は一水平走査期間の初めに発生されたスタートパルス(SSP)をクロックパルスによりシフトして、該一走査期間に、クロックパルス間隔だけシフトしたm個のラッチクロックパルスを生成するシフトレジスタ(21)、

デジタルな画素データの系列における連続する奇数ライン画素データと偶数ライン画素データの2個の画素データを同時的に一時保持するラッチ部(22,23)、

ー水平期間におけるm個の奇数ライン画素データの各々を保持する第1の奇数ラインラッチ(25a)と一水平期間におけるm個の偶数ライン画素データの各々を保持する第1の偶数ラインラッチ(26a)、

該第1の奇数ラインラッチと第1の偶数ラインラッチのそれぞれは、該シフトレジスタからのラッチクロックパルスの各々に応答し、該ラッチ部に保持されている奇数ライン画素データと偶数ライン画素データを同時にラッチして、一水平走査期間にm個の奇数ライン画

素データとm個の偶数ライン画素データを順次保持するようにしており、

m個の奇数ライン画素データを保持する第2の奇数ラインラッチ(25b)とm個の偶数ライン 画素データを保持する第2の偶数ラインラッチ(26b)、

該第2の奇数ラインラッチと第2の偶数ラインラッチのそれぞれは、一水平期間毎にロード信号(LOAD)に応答して、該第1の奇数ラインラッチに保持されている画素データの全て及び該第1の偶数ラインラッチに保持されている画素データの全てを同時にラッチしており、

ー水平期間毎に、該第2の奇数ラインラッチ及び該第2の偶数ラインラッチに保持されているデジタルな画素データの各々全てを同時に変換して、該液晶パネルの奇数ライン( $Y_1$ ,  $Y_3$ --- $Y_3$ 84)と偶数ライン( $Y_2$ ,  $Y_4$ --- $Y_3$ 84)に与えているD/A変換器(27)とからなるものである、液晶表示装置。

### 【請求項2】

k×m個のラインを含むアクティブマトリックス型液晶パネルと該液晶パネルの一方の側辺に配置された液晶パネル駆動装置とからなる液晶表示装置において、該駆動装置は一水平走査期間の初めに発生されたスタートパルス(SSP)をクロックパルスによりシフトして、該一走査期間に、クロックパルス間隔だけシフトしたm個のラッチクロックパルスを生成するシフトレジスタ(31)、

デジタルな画素データの系列における連続する i番目ライン画素データ、 i+1番目ライン画素データ、 -----、及び i+(k-1)番目ライン画素データのk個の画素データを同時的に一時保持するラッチ部 (32,33,34)、

ー水平期間におけるm個のi番目ライン画素データの各々を保持する第1のi番目ラインラッチ (36a)、一水平期間におけるm個のi+1番目ライン画素データの各々を保持する第1のi+ 1番目ラインラッチ (37a)、-----、及び一水平期間におけるm個のi+(k-1)番目ライン画素データの各々を保持する第1のi+(k-1)番目ラインラッチ (38a)、

該第1のi番目ラインラッチ~第1のi+(k-1)番目ラインラッチのそれぞれは、該シフトレジスタからのラッチクロックパルスの各々に応答し、該ラッチ部に保持されているi番目ライン画素データ~i+(k-1)番目ライン画素データを同時にラッチして、一水平走査期間にm個のi番目ライン画素データとm個のi+(k-1)番目ライン画素データを順次保持するようにしており、

m個のライン画素データを保持する第2のi番目ラインラッチ(36b)とm個のi+1番目ライン画素データを保持する第2のi+1番目ラインラッチ(37b)、----、m個のi+(k-1)番目ライン画素データを保持する第2のi+(k-1)番目ラッチ(38b)、

該第2のi番目ラインラッチ~第2のi+(k-1)番目ラインラッチのそれぞれは、一水平期間毎にロード信号(LOAD)に応答して、該第1のi番目ラインラッチに保持されている画素データの全て~該第1のi+(k-1)番目ラインラッチに保持されている画素データの全てを同時にラッチしており、

ー水平期間毎に、該第2のi番目ラインラッチ~該第2のi+(k-1)番目ラインラッチに保持されているデジタルな画素データの各々全てを同時に変換して、該液晶パネルのi番目ライン~i+(k-1)番目ラインに与えているD/A変換器(39)とからなるものである、液晶表示装置。

# フロントページの続き

F I テーマコード (参考) G 0 9 G 3/20 6 2 3 F G 0 9 G 3/20 6 2 3 H G 0 9 G 3/20 6 4 1 C G 0 2 F 1/133 5 5 5 0

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(72)発明者 ヨン ヒ ギュン

大韓民国 ソウル ドボン-グ ドボン-ドン 568-43

Fターム(参考) 2H093 NA16 NA43 NB07 NC16 NC22 NC26 NC34 ND34 ND39 ND40

ND54 ND60

5C006 AA16 AF83 BB16 BC16 BF03 BF04 BF25 FA32 FA48

5C080 AA10 BB05 DD27 EE29 FF11 JJ02 JJ04

| 专利名称(译)        | 液晶显示装置的驱动装置                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|--|

| 公开(公告)号        | <u>JP2006350378A</u>                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2006-12-28 |  |  |  |  |

| 申请号            | JP2006225135                                                                                                                                                                                                                                                                                                                                | 申请日     | 2006-08-22 |  |  |  |  |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                    |         |            |  |  |  |  |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                            |         |            |  |  |  |  |

| [标]发明人         | ヨンヒギュン                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |  |  |

| 发明人            | ヨンヒギュン                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |  |  |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |  |

| FI分类号          | G09G3/36 G09G3/20.611.A G09G3/20.611.C G09G3/20.611.G G09G3/20.623.B G09G3/20.623.F G09G3/20.623.G G09G3/20.623.H G09G3/20.641.C G02F1/133.505 G02F1/133.550                                                                                                                                                                                |         |            |  |  |  |  |

| F-TERM分类号      | 2H093/NA16 2H093/NA43 2H093/NB07 2H093/NC16 2H093/NC22 2H093/NC26 2H093/NC34 2H093 /ND34 2H093/ND39 2H093/ND40 2H093/ND54 2H093/ND60 5C006/AA16 5C006/AF83 5C006/BB16 5C006/BC16 5C006/BF03 5C006/BF04 5C006/BF25 5C006/FA32 5C006/FA48 5C080/AA10 5C080 /BB05 5C080/DD27 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ04 2H193/ZA04 2H193/ZF37 |         |            |  |  |  |  |

| 代理人(译)         | 臼井伸一<br>朝日 伸光                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |  |  |

# 摘要(译)

要解决的问题:提供液晶显示装置的数据驱动器,其解决了由高频操作引起的问题并降低了主驱动频率。 一种m(整数)位寄存器电路,用于输出锁存时钟信号并用于接收对应于第一时钟信号的起始信号,以及m(整数)位寄存器电路,用于输出所有视频信号数据锁存电路22和23,用于锁存和输出对应于源视频信号的至少两组三种视频信号,并根据第三信号发生电路的负载信号存储和输出视频信号,用于锁存数据的视频信号的线锁存电路25锁存对应于寄存器,视频信号线锁存器和d的锁存时钟信号电路/A转换电路27,其从d的模拟信号转换/A转换器以及用于输出模拟信号的数据输出电路29。 点域5