(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2001 - 324964

(P2001 - 324964A)

(43)公開日 平成13年11月22日(2001.11.22)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I           | テ-マコード* (参考) |

|--------------------------|------|---------------|--------------|

| G 0 9 G 3/36             |      | G 0 9 G 3/36  | 2 H 0 9 3    |

| G 0 2 F 1/133            | 575  | G 0 2 F 1/133 | 5 C 0 0 6    |

| G 0 9 G 3/20             | 641  | G 0 9 G 3/20  | 5 C 0 8 0    |

審査請求 未請求 請求項の数 50 L (全 12数)

(21)出願番号 特願2000 - 143529(P2000 - 143529)

(71)出願人 598010562

東芝エルエスアイシステムサポート株式会

社

神奈川県川崎市幸区堀川町580番地

000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

新田 義真

神奈川県川崎市幸区堀川町580番地 東芝エ

ルエスアイシステムサポート株式会社内

(74)代理人 100058479

弁理士 鈴江 武彦 (外6名)

(22)出願日 平成12年5月16日(2000.5.16)

最終頁に続く

(54)【発明の名称】階調表示LCDコントローラ

(57)【要約】

【課題】 LCDコントローラ内の階調変換を不要にする。

【解決手段】 4階調(2ビット)表示に関し、メモリ13は、2つの領域が設けられる。アドレスADD, ..., ADD+(N-1)により選択される一の領域には、一フレーム分のN画素の最下位ビットBIT0が格納され、アドレスADD+N, ..., ADD+(N-1)+Nにより選択される他の領域には、一フレーム分のN画素の最上位ビットBIT1が格納される。アドレスカウンタ15Aは、アドレス信号ADD, ..., ADD+(N-1)を生成する。加算器23は、フレームカウンタの値“1”, “2”, “3”に基づき、アドレス信号ADD, ..., ADD+(N-1)に、N(特定値)×1又はN×0を加算する。N×1の加算回数は、2回、N×0の加算回数は、1回である。

**【特許請求の範囲】**

【請求項1】 メモリにアドレス信号を供給し、かつ、前記メモリから読み出されたデータをLCDドライバに供給して、 $2^n$  ( $n$ は、2以上の自然数)階調の画像表示を行うためのLCDコントローラにおいて、

1から $2^n - 1$ までの値をカウントするフレームカウンタと、

前記メモリに格納された画素の階調を表すnビットのうちの1ビットを、前記フレームカウンタの値に基づいて、1フレーム分、前記メモリから読み出すための前記アドレス信号を生成するアドレスカウンタと、

前記nビットのうちの1ビットを前記メモリから読み出す場合に、前記アドレス信号に、特定値 $\times i$  ( $i$ は、 $0, \dots, n-1$ )を加算し、前記メモリから読み出す前記nビットのうちの1ビットを決定する加算器と、

前記フレームカウンタの値に基づいて、前記nビットのうちの最上位ビットBIT $n-1$ を $2^{(n-1)}$ 回、ビットBIT $n-j$ を $2^{(n-j)}$ 回 ( $j$ は、 $2, \dots, n-1$ 。 $n=2$ の場合を除く。)、最下位ビットBIT0を $2^0$ 回、前記メモリから読み出すための $x, y$ 格納テーブルとを具備することを特徴とする階調表示LCDコントローラ。

【請求項2】 前記メモリには、前記nビットに対応してn個の領域が設けられ、各領域には、前記nビットのうちの1ビットが1フレーム分格納され、前記n個の領域のうちの1つに格納されたデータは、前記アドレス信号に前記(特定値 $\times i$ )を加算した値により読み出されることを特徴とする請求項1記載の階調表示LCDコントローラ。

【請求項3】 前記n個の領域の各々には、マスクRO30Mに保存されたデータがそのまま書き込まれるか、又は、全く書き込まれないことを特徴とする請求項2記載の階調表示LCDコントローラ。

【請求項4】 前記メモリから読み出されたデータは、前記LCDコントローラで階調変換されることなく、LCDドライバに供給されることを特徴とする請求項1記載の階調表示LCDコントローラ。

【請求項5】 前記メモリは、ディスプレイRAMであることを特徴とする請求項1記載の階調表示LCDコントローラ。

**【発明の詳細な説明】**

**【0001】**

【発明の属する技術分野】本発明は、階調表示LCDコントローラに関し、特に、CPUとLCDコントローラが同一のバスに接続されるシステムに使用される。

**【0002】**

【従来の技術】図13は、従来の階調表示LCDコントローラの主要部を示している。

【0003】バス11には、CPU12、メモリ(ディスプレイRAM)13及びLCDコントローラ14が接続され、

続される。

【0004】LCDコントローラ14において、アドレスカウンタ15は、メモリ13からデータを読み出すための連続したアドレス信号を生成する。アドレス信号は、バス11を経由して、順次、メモリ13に入力される。これに伴い、メモリ13は、アドレス信号により指定されるアドレス(メモリセル)から、順次、データをバス11に出力する。

【0005】このデータは、例えば、画素(ピクセル)単位で、メモリ13からバス11に読み出され、さらに、階調表示LCDコントローラ14に転送される。また、例えば、1画素が8階調から構成される場合、1画素分のデータは、3ビットBIT2, BIT1, BIT0となる。つまり、3ビットデータが、順次、メモリ13から階調表示LCDコントローラ14に転送される。

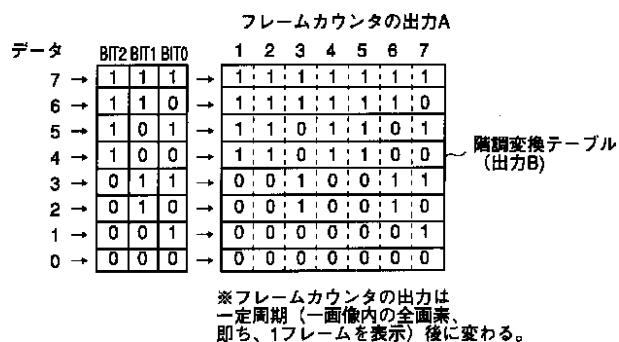

【0006】メモリ13から読み出されたデータは、階調表示LCDコントローラ14内のキャッシュメモリ16に格納される。メモリ13から読み出されたデータ(3ビット)は、階調変換テーブル19に基づいて、 $7 (= 2^3 - 1)$ 値データに変換される。つまり、この7値データ“\*\*\*\*\*” (“1”的数により、画素の濃度が表される。“1”的数は、0~7個の8通り存在する。)により、1画素の階調が表される。

【0007】1画素の階調表示は、7値データを、一定周期、即ち、一画面全体(1フレーム)を走査する時間(例えば、1/60[s] ~ 1/120[s])ごとに、順次、1値ずつ、バッファ20を経由して、LCDドライバ21に出力することにより行われる。出力の順番は、フレームカウンタ18の出力信号A (= 1, 2, ..., 7)により制御される。

【0008】なお、キャッシュメモリ16は、階調変換テーブル19における変換速度(3ビットデータから7値データへの変換速度)が、3ビットデータBIT2, BIT1, BIT0が階調表示LCDコントローラ14に入力される速度よりも遅い場合に必要な要素である。

【0009】従って、階調変換テーブル19における変換速度が、3ビットデータBIT2, BIT1, BIT0が階調表示LCDコントローラ14に入力される速度と同じか又はそれよりも速い場合には、キャッシュメモリ16は、不要である。

【0010】以下、図13の階調表示LCDコントローラを用いた場合の具体的な動作について、図13乃至図15を参照しながら説明する。まず、前提条件として、1画像を構成する複数の画素のうち、メモリ13から読み出される1画素分のデータが、3ビット(8階調)BIT2, BIT1, BIT0、即ち、0, 1, 2, ..., 7(十進数)で表されるものとする。

【0011】メモリ13に対するアクセス動作画像表示は、CRT表示と同様に、画像を構成する画素を1つずつ順次走査していくことにより行うため、アド

レスカウンタ15は、連続した値を持つアドレス信号を、1つずつ、順次、出力する。

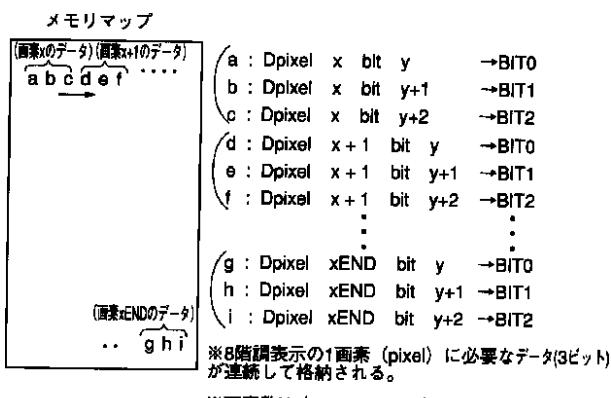

【0012】一方、図14のメモリマップに示すように、各画素のデータ（濃度値）a, b, c, d, e, f, … g, h, iは、アドレスカウンタ15から出力される連続する値を持つアドレス信号に対応して、メモリ13内の連続するアドレスに規則的に格納される。

【0013】従って、アドレスカウンタ15から出力されるアドレス信号が変化することにより、メモリ13からは、画素データa, b, c, d, e, f, … g, h, iが、順次、出力される。なお、本例では、a, b, cにより1画素分のデータが構成され、同様に、d, e, fにより1画素分のデータが構成される。

【0014】実際は、1回の読み出し動作により、複数ビットのデータが一度に読み出される。例えば、1回の読み出し動作により6ビットの画素データa, b, c, d, e, fが、同時に読み出され、バス11に出力される。

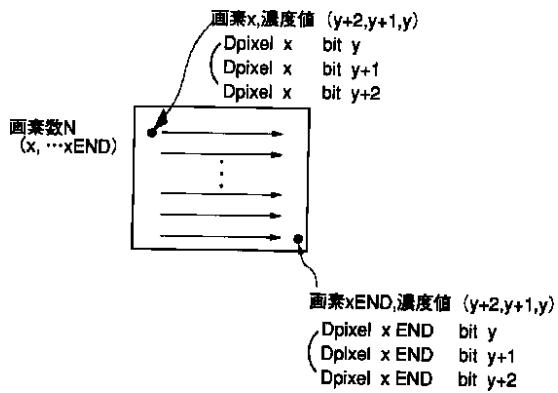

【0015】ところで、図14において、Dpixel<sub>x</sub>は、ディスプレイ(LCD)内の画素(ピクセル)の位置、即ち、ディスプレイ内の位置xに存在する1つの画素を示し、Dpixel<sub>x bit y</sub>は、位置xに存在する画素の濃度値の最下位ビットBIT0が“y”であることを示している。また、Dpixel<sub>x bit y + 1</sub>は、位置xに存在する画素の濃度値のビットBIT1が“y + 1”であることを示し、Dpixel<sub>x bit y + 2</sub>は、位置xに存在する画素の濃度値の最上位ビットBIT2が“y + 2”であることを示している。

【0016】LCDドライバ21に対するドライブ動作

まず、上述のアクセス動作により、例えば、ディスプレイ内の位置xに存在する画素(図14を参照)のデータ、即ち、アドレスa, b, cのデータBIT2, BIT1, BIT0が読み出され、かつ、そのデータ値(画素の濃度値)が“5”であると仮定する。

【0017】画素の濃度値が“5”的場合、メモリ13から読み出されるデータは、図15に示すように、BIT2 = “1”, BIT1 = “0”, BIT0 = “1”となる。そして、このデータが階調変換テーブル19により変換されると、図15に示すように、“1101101”という7値データになる。本例では、この7値データのうちの1つを、フレームカウンタ18の出力信号Aに基づいて、LCDドライバ21に出力する。

【0018】例えば、フレームカウンタ18の出力信号Aが“1(十進数)”の場合には、3ビットデータBIT2, BIT1, BIT0が入力され、階調変換テーブル19により7値データ“1101101”が生成された後に、7値データの最も左の値が選択され、出力信号Bとして、“1”が出力される。

(3)

4

【0019】この後、一定周期(例えば、1/60[s] ~ 1/120[s])が経過すると(この間に1画面内の全画素(1フレーム)の走査が終了する。)、フレームカウンタ18の出力信号Aが“2(十進数)”に変化する。フレームカウンタ18の出力信号Aが“2(十進数)”の場合には、3ビットデータBIT2, BIT1, BIT0が入力され、階調変換テーブル19により7値データ“1101101”が生成された後に、7値データの最も左から2番目の値が選択され、出力信号Bとして、“1”が出力される。

【0020】そして、同様の動作は、フレームカウンタ18の出力信号Aが“7(十進数)”になるまで行われる。

【0021】本例では、上述の一定周期ごとに、3ビットデータ(濃度値)BIT2, BIT1, BIT0が階調変換テーブル19により7値データに変換され、かつ、この7値データのうちの1つがフレームカウンタ18の出力信号Aの値に基づいてLCDドライバ21に出力される。

【0022】例えば、ディスプレイ内の位置xの画素の濃度値が“5”的場合には、7値データは、図15に示すように、“1101101”という値になる。ここで、例えば、“1”を黒とし、“0”を白とすると、7値データは、“黒黑白黒黑白黒”となる。この7値データを、一定周期(1フレーム周期)、例えば、1/60[s] ~ 1/120[s]ごとに、順次、高速に出力し、ディスプレイ内の位置xの画素を表示すると、その位置xの画素は、人間の目には、白の黒の中間の色、即ち、灰として見えるようになる(7値データが“1111111”的とき完全な黒、“0000000”的とき完全な白とする。)。

【0023】なお、1画素のデータ(濃度値)が3ビットであり、バス11の本数が8本(8ビット分)ある場合には、一度に、2画素分のデータ(6本のバス11が必要)を、メモリ13からLCDコントローラ14に転送できる。但し、1回の読み出し動作により、2画素分(6ビット)のデータをメモリ13から読み出せるものとする。また、ローカルバス22の本数が8本の場合には、8画素分のデータを、同時に、LCDコントローラ14からLCDドライバ21に転送できる。

【0024】つまり、バス11及びローカルバス22が、共に、8本の場合には、4回の読み出し動作で、メモリ13から8(=2×4)画素分のデータを読み出した後に、フレームカウンタ18の値及び階調変換テーブル19により得られる8画素分のデータを、一度に、LCDドライバ21に転送することができる。

【0025】

【発明が解決しようとする課題】図13に示すように、CPU12とLCDコントローラ14が同一のバス11に接続されるシステムでは、メモリ(ディスプレイRAM)

M) 13からLCDコントローラ14にデータBIT2,BIT1,BIT0を転送する際に、バス11が使用される。この時、バス11は、データ転送用配線として機能しているため、CPU12は、他の処理のために、バス11を使用することができない。

【0026】そして、メモリ13からLCDコントローラ14へのデータ転送のためにバス11を使用している時間、即ち、バス11の占有率は、転送するデータのビット数が大きくなればなるほど、増加する。例えば、2階調(白、黒)のモノクロ表示を基準にした場合、これを、 $4 (= 2^2)$ 階調のモノクロ表示にすると、バスの占有率は、2倍に増え、また、これを、 $8 (= 2^3)$ 階調のモノクロ表示にすると、バスの占有率は、4倍に増え、さらに、これを、 $16 (= 2^4)$ 階調のモノクロ表示にすると、バスの占有率は、4倍に増える(バス11の占有率は、バス11の本数を一定とすると、転送するデータのビット数の増加に比例して増加する。)。

【0027】従って、例えば、1画素の階調数を増やすほど、メモリ13からLCDコントローラ13へのデータ転送のためにバス11を使用している時間が長くなり、この間、CPU12のバス11の使用が制限される。

【0028】ところで、LCDコントローラ14内にキャッシュメモリ16を設けることにより、バスの占有率を減らすことができるが、この場合、大容量のキャッシュメモリが必要となるため、製造コストが増大するという問題が生じる。

【0029】本発明は、上述の問題を解決するためになされたもので、その目的は、1画素の階調数を増加しても、キャッシュメモリを設けることなしに、常に、LCDコントローラ13へのデータ転送に関するバスの占有率を一定(例えば、モノクロ表示と同じ)にすることができる階調表示LCDコントローラを提供することにある。

### 【0030】

【課題を解決するための手段】上記目的を達成するため、本発明の階調表示LCDコントローラは、メモリにアドレス信号を供給し、かつ、前記メモリから読み出されたデータをLCDドライバに供給して、 $2^n$ (nは、2以上の自然数)階調の画像表示を行うものであり、1から $2^n - 1$ までの値をカウントするフレームカウンタと、前記メモリに格納された画素の階調を表すnビットのうちの1ビットを、前記フレームカウンタの値に基づいて、1フレーム分、前記メモリから読み出すための前記アドレス信号を生成するアドレスカウンタと、前記nビットのうちの1ビットを前記メモリから読み出す場合に、前記アドレス信号に、特定値×i(iは、0, ..., n-1)を加算し、前記メモリから読み出す前記nビットのうちの1ビットを決定する加算器と、前記フレームカウンタの値に基づいて、前記nビットのうちの最上

位ビットBITn-1を $2^{(n-1)}$ 回、ビットBITn-jを $2^{(n-j)}$ 回(jは、2, ..., n-1,n=2の場合を除く。)、最下位ビットBIT0を2<sup>0</sup>回、前記メモリから読み出すためのx,y格納テーブルとを備える。

【0031】前記メモリには、前記nビットに対応してn個の領域が設けられ、各領域には、前記nビットのうちの1ビットが1フレーム分格納され、前記n個の領域のうちの1つに格納されたデータは、前記アドレス信号に前記(特定値×i)を加算した値により読み出される。

【0032】前記n個の領域の各々には、マスクROMに保存されたデータがそのまま書き込まれるか、又は、全く書き込まれない。

【0033】前記メモリから読み出されたデータは、前記LCDコントローラで階調変換されることなく、LCDドライバに供給される。

【0034】前記メモリは、ディスプレイRAMである。

### 【0035】

【発明の実施の形態】以下、図面を参照しながら、本発明の階調表示LCDコントローラについて詳細に説明する。

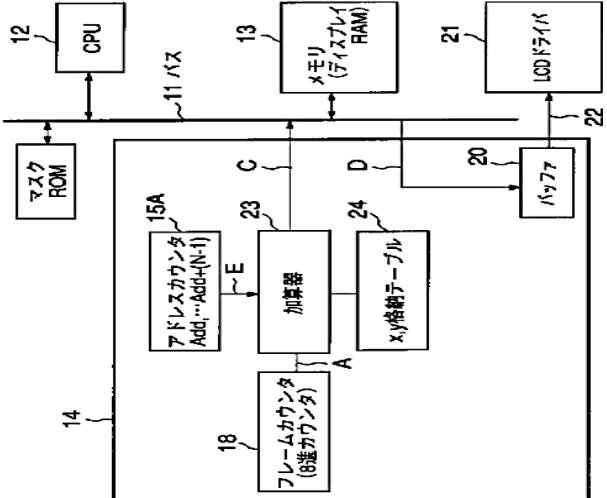

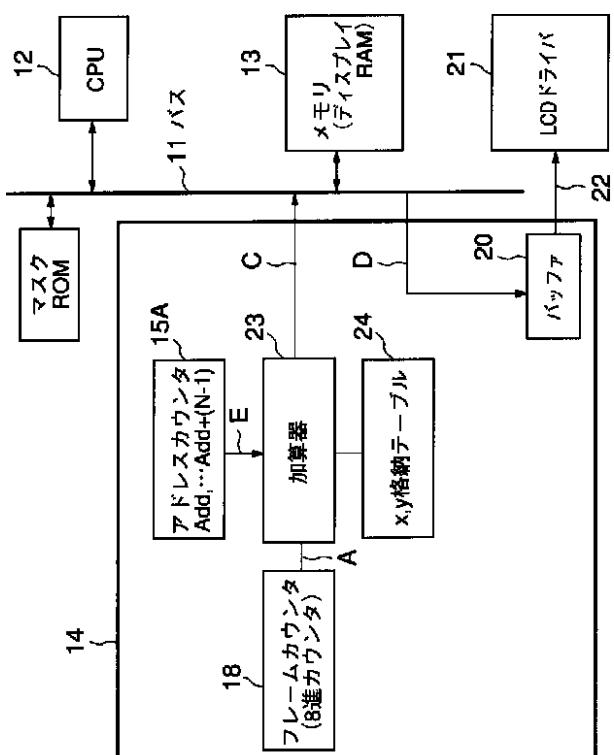

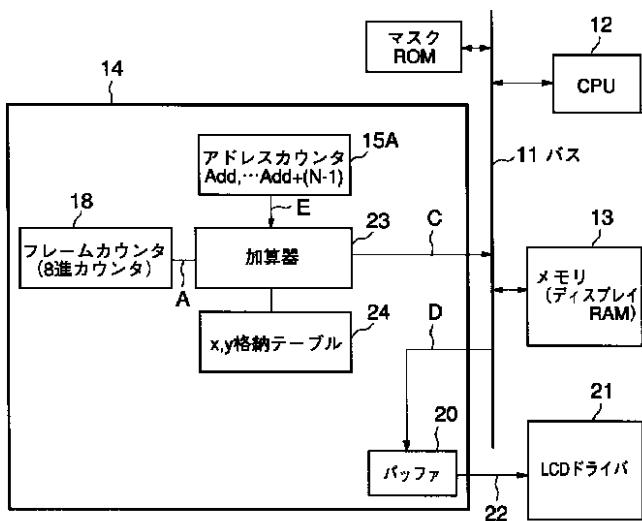

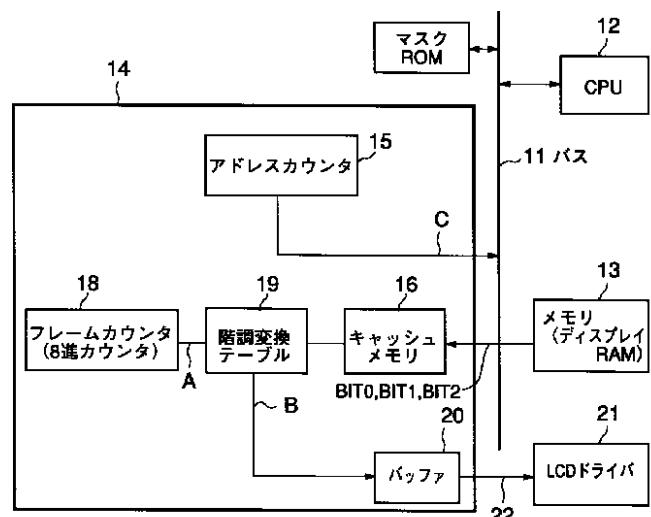

【0036】[A] 図1は、本発明の階調表示LCDコントローラの主要部を示している。

【0037】バス11には、CPU12、メモリ(ディスプレイRAM)13及びLCDコントローラ14が接続される。

【0038】LCDコントローラ14において、アドレスカウンタ15Aは、メモリ13からデータを読み出すための連続したアドレス信号を生成する。ここで、本発明では、連続したアドレス信号に、フレームカウンタ18の出力信号Aの値に応じて、それぞれ特定値×i(i=0, 1, 2, ..., n-1)を加算器23により加算している。但し、nは、1画素を表すビット数である(nビットのとき、2<sup>n</sup>階調表示となる。)。なお、“特定値×i”的意味については、後に、詳述することにする。

【0039】アドレスカウンタ15Aの出力信号に特定値×iを加算することにより得られるアドレス信号Cは、バス11を経由して、順次、メモリ13に入力される。これに伴い、メモリ13は、アドレス信号Cにより指定されるアドレス(メモリセル)から、順次、データをバス11に出力する。

【0040】ここで、本発明では、メモリ13から読み出されるデータは、既に、階調変換されたデータとなっており、このデータが、階調表示LCDコントローラ14に入力され、さらに、LCDドライバ21に供給される。但し、メモリ13には、従来と同様に、ディスプレイ内の各画素の濃度値が、nビットデータ(2<sup>n</sup>階調表

示の場合)として格納される。

【0041】つまり、本発明では、メモリ13におけるデータ(各画素の濃度値)の格納方法(メモリマップ)を特別なものとし、かつ、データ読み出し時に、アドレスカウンタ15Aの出力信号に特定値 $\times i$ を加算することにより得られるアドレス信号Cを用いることにより、メモリ13から、直接、階調変換されたデータを読み出すことを可能にする。これについては、後に、詳述する。

【0042】そして、例えば、1画素が8階調から構成される場合、1画素分のデータは、3ビットBIT2, BIT1, BIT0となる。本発明では、この3ビットデータに基づいて、順次、メモリ13から、階調変換された $7 (= 2^3 - 1)$ 値データが出力される。

【0043】また、7値データ“\*\*\*\*\*”は、例えば、“1”的数により、画素の濃度(階調)、即ち、白(0個/7) 灰 黒(7個/7)を表す (“1”的数は、0~7個の8通り存在する。)。

【0044】さらに、7値データは、フレームカウンタ18の出力信号Aの値に基づいて、一定周期、即ち、一画面全体(1フレーム)を走査する時間(例えば、1/60[s]~1/120[s])ごとに、順次、1値ずつ、メモリ13からバス11に出力される。

【0045】なお、従来のLCDコントローラ(図13参照)では、2^n階調表示の場合、メモリ13から読み出されたnビットデータ(濃度値)を、LCDコントローラ14においてデコードし、かつ、階調変換テーブル19に基づいて、nビットデータを $(2^n - 1)$ 値データに変換している。

【0046】従って、上述したように、LCDコントローラ14における変換速度(又はLCDドライバ21へのデータ転送速度)が、LCDコントローラ14に入力されるnビットデータの転送速度よりも遅い場合には、キャッシュメモリ16を設けるなどの対策が必要であった(キャッシュメモリ16を設けない場合には、データ転送に長時間を要し、この間、バス11を他の目的で使用できない。)。

【0047】これに対し、本発明では、ディスプレイ内の各画素の階調数( $2^n$ )、即ち、メモリ13に格納される1画素分のビット数(n)にかかわらず、メモリ13からは、常に、階調変換された $(2^n - 1)$ 値データのうちの1つが出力されることになる。また、LCDコントローラ14では、データのデコード動作や、階調変換動作などが不要である。

【0048】従って、本発明のLCDコントローラでは、画素の階調数によらず、かつ、キャッシュメモリを設けることなく、メモリ13から出力されるデータを、直ちに、LCDコントローラ14内に取り込むことができるため、バス11の占有率を減らすことができる。

【0049】[B] 次に、本発明の概念について説明

する(図1参照)。

【0050】まず、2^n階調表示について検討する。2^n階調表示では、メモリ13内には、1画素分のデータ(濃度値)として、nビットデータBITn-1, ..., BIT1, BIT0が格納される。また、LCDドライバ21により実際に表示を行う場合には、このnビットデータBITn-1, ..., BIT1, BIT0を、 $(2^n - 1)$ 値データに変換する必要がある。

【0051】ここで、nビットデータと $(2^n - 1)$ 値データの関係について考える。簡単のため、n=3とする。

【0052】データ(濃度値)“0(例えば、完全な白)”, “1”, “2”, “3”, “4”, “5”, “6”, “7(例えば、完全な黒)”は、3ビットデータ“BIT2, BIT1, BIT0”では、それぞれ、“000”, “001”, “010”, “011”, “100”, “101”, “110”, “111”で表すことができる。

【0053】また、データ(濃度値)“0”, “1”, “2”, “3”, “4”, “5”, “6”, “7”を、7値データ“\*\*\*\*\*”(\*は、“0”又は“1”)で表すためには、それぞれ、7値データ“\*\*\*\*\*”のうち“1”的数を、0個、1個、2個、3個、4個、5個、6個、7個とすればよい。

【0054】ここで、上記及びを比較すると、3ビットデータの最上位ビットBIT2を4回、ビットBIT1を2回、最下位ビットBIT0を1回、それぞれメモリ13から読み出すと、7値データが得られることがわかる。

【0055】例えば、データ“5”的場合を考えると、3ビットデータ“BIT2, BIT1, BIT0”は、“101”となる。そして、BIT2を4回、BIT1を2回、BIT0を1回読み出すと、“1”的数は、“1”(BIT2)×4+“0”(BIT1)×2+“1”(BIT0)×1 = “5”となり、7値データを表現できることになる。

【0056】7値データ“\*\*\*\*\*”のうち、どの部分を“1(例えば、黒)”にするかは、様々な手法が考えられているが、例えば、データ“5”的場合、データ読み出し順序を、BIT2 BIT2 BIT1 BIT2 BIT2 BIT1 BIT0とすることにより、7値データ“1101101”を得ることができる。

【0057】なお、以上は、データ“5”以外の他のデータにおいても同様である。

【0058】[C] 本発明では、上述の概念を実現するため、メモリ13内におけるデータの格納方法(メモリマップ)及びメモリ13に対するアクセス方法を特徴的なものとしている。

【0059】データの格納方法(メモリマップ)

1画素が $2^n$ 階調( $n$ ビット)で表される場合、メモリ領域は、 $n$ 個の領域から構成される。そして、各領域には、ディスプレイ内の各画素の濃度値( $n$ ビット)のうちの1つが格納される。

【0060】また、例えば、BIT0(最下位ビット)が記憶される領域では、連続したアドレスADD, ADD+1, ..., ADD+(N-1)に、それぞれディスプレイ内の各画素のBIT0が格納される。但し、Nは、画素数である。また、BIT1が記憶される領域では、連続したアドレスADD, ADD+1, ..., ADD+(N-1)にそれぞれ(特定値×1)を加算したアドレスに、ディスプレイ内の各画素のBIT1が格納される。

【0061】ここで、1回の読み出し動作(1つのアドレス信号)により1つのセル(1ビット)が選択される場合には、特定値は、画素数Nに等しくなる。

【0062】同様に、BITn-1が記憶される領域では、連続したアドレスADD, ADD+1, ..., ADD+(N-1)にそれぞれ(特定値×(n-1))を加算したアドレスに、ディスプレイ内の各画素のBITn-1が格納される。

【0063】具体例を示すこととする。

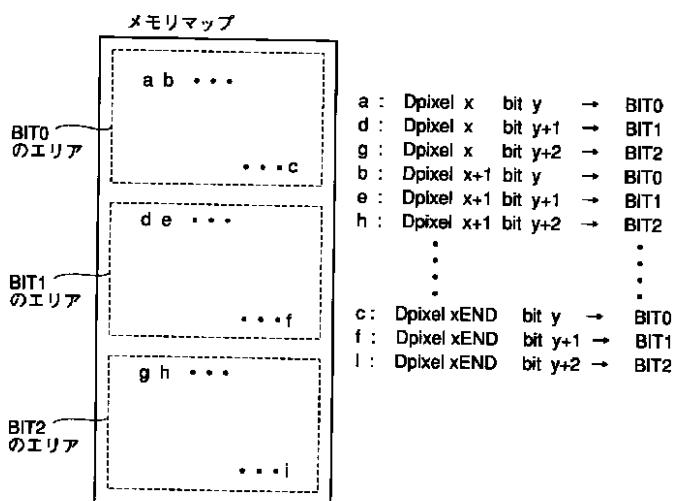

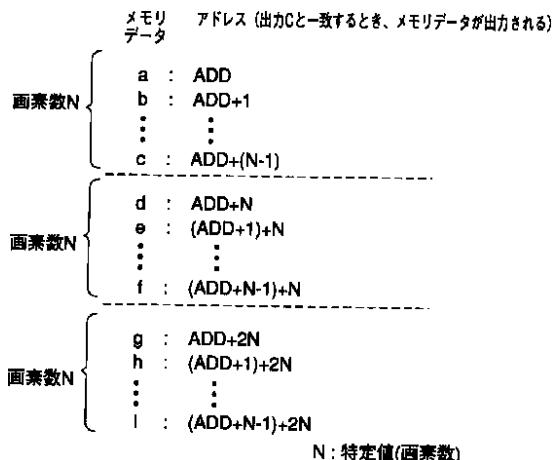

【0064】図2のメモリマップに示すように、1画素が8階調(3ビット)で表される場合、メモリ領域は、3個の領域、即ち、BIT0(最下位ビット)を記憶する領域、BIT1を記憶する領域、BIT2(最上位ビット)を記憶する領域から構成される。

【0065】BIT0が記憶される領域では、連続したアドレスADD, ADD+1, ..., ADD+(N-1)に、それぞれディスプレイ内の各画素のBIT0(=a, b, ..., c)が格納される(Nは、画素数)。また、BIT1が記憶される領域では、連続したアドレスADD, ADD+1, ..., ADD+(N-1)にそれぞれ(特定値×1)を加算したアドレスに、各画素のBIT1(=d, e, ..., f)が格納される。さらに、BIT2が記憶される領域では、連続したアドレスADD, ADD+1, ..., ADD+(N-1)にそれぞれ(特定値×2)を加算したアドレスに、各画素のBIT2(=g, h, ..., i)が格納される。

【0066】ところで、図2において、Dpixel<sub>x</sub>は、ディスプレイ(LCD)内の画素(ピクセル)の位置、即ち、ディスプレイ内の位置xに存在する1つの画素を示している(実際は、位置は、x, yで表されるが、簡単のため、yについては省略している。)。

【0067】また、Dpixel<sub>x bit y</sub>は、位置xに存在する画素の濃度値の最下位ビットBIT0が“y”であることを示し、Dpixel<sub>x bit y+1</sub>は、位置xに存在する画素の濃度値のビットBIT1が“y+1”であることを示し、Dpi

<sub>x el x bit y+2</sub>は、位置xに存在する画素の濃度値の最上位ビットBIT2が“y+2”であることを示している。

【0068】そして、メモリの各領域から読み出されるデータa, b, ..., c(BIT0), d, e, ..., f(BIT1), g, h, ..., i(BIT2)は、それぞれ1フレーム分の画素データを構成している。従って、例えば、図3に示すように、メモリ内の1つの領域から連続的に読み出されたデータ(N個)により、N画素のディスプレイが表示される。

【0069】メモリ13に対するアクセス方法例えば、1画素が8階調(3ビット)で表される場合、1画像は、7フレームにより構成される。つまり、各画素の濃度(モノクロ表示の場合、黒 灰 白)は、7値(“1”又は“0”的数により濃度を表現する。)を、一定周期(一フレーム周期)、例えば、1/60[s]~1/120[s]ごとに、LCDドライバに与えることにより表される。

【0070】ここで、本発明では、7値データを、メモリ(ディスプレイRAM)から直接読み出し、これを、LCDコントローラを経由して、LCDドライバに供給するため、メモリに対するアクセス方法を工夫している。

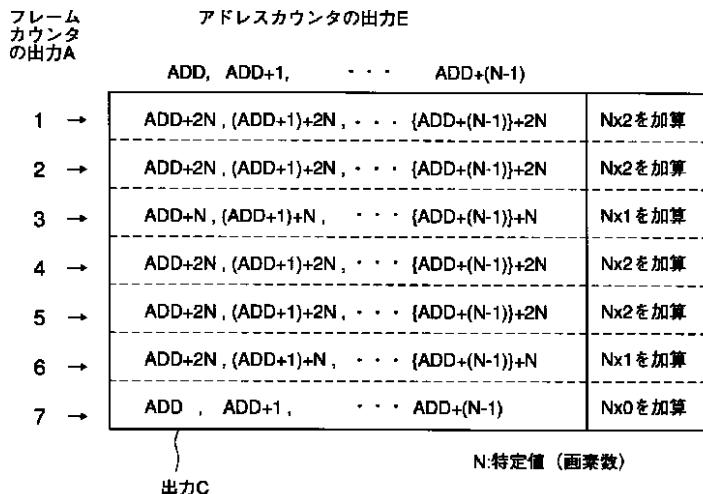

【0071】即ち、図4に示すように、フレームカウンタの出力信号Aの値に応じて、アドレスカウンタの出力信号ADD, ADD+1, ..., ADD+(N-1)に、特定値×i(iは、0又は1又は2)を加算し、これを、メモリ13に対するアドレス信号として用いる。但し、Nは、画素数であり、また、ADD, ADD+1, ..., ADD+(N-1)により、図2におけるBIT0(a, b, ..., c)がメモリ13から読み出されるものとする。

【0072】また、1つのアドレス信号により1つのアドレス(セル)が選択され、1つのデータが読み出されるものとする。この場合、上述の特定値は、画素数Nに等しくなる。

【0073】例えば、図4に示すように、フレームカウンタの出力信号Aが“1”的場合には(1回目のフレーム走査)、加算器により、ADD+2N, (ADD+1)+2N, ..., {ADD+(N-1)}+2Nが生成され、これが、アドレス信号Cとしてメモリ13に供給される。この時、図5に示すように、メモリデータとしては、g, h, ..., i(BIT2)が出力される。

【0074】また、図4に示すように、フレームカウンタの出力信号Aが“2”的場合には(2回目のフレーム走査)、加算器により、ADD+2N, (ADD+1)+2N, ..., {ADD+(N-1)}+2Nが生成され、これが、アドレス信号Cとしてメモリ13に供給される。この時、図5に示すように、メモリデータとしては、g, h, ..., i(BIT2)が出力される。

【0075】また、図4に示すように、フレームカウンタの出力信号Aが“3”的場合には(3回目のフレーム走査)、加算器により、ADD+N, (ADD+1)+N, … {ADD+(N-1)}+Nが生成され、これが、アドレス信号Cとしてメモリ13に供給される。この時、図5に示すように、メモリデータとしては、d, e, … f(BIT1)が出力される。

【0076】そして、同様の動作は、フレームカウンタの値Aが“7”になるまで、繰り返し行われる。

【0077】以上の動作を、ある1つの画素xについてみると、フレームカウンタの値Aが“1”から“7”になるまでに、一定周期T(1/60[s]~1/120[s])ごとに、7回の表示が行われる。

【0078】即ち、時刻tにおいて、アドレスカウンタの出力信号Eに、“N(特定値=画素数)×2”を加算したアドレス信号に基づいて、BIT2が読み出され、画素xの表示(黒又は白)が行われる。

【0079】時刻t+Tにおいて、アドレスカウンタの出力信号Eに、“N×2”を加算したアドレス信号に基づいて、BIT2が読み出され、画素xの表示(黒又は白)が行われる。

【0080】時刻t+2Tにおいて、アドレスカウンタの出力信号Eに、“N×1”を加算したアドレス信号に基づいて、BIT1が読み出され、画素xの表示(黒又は白)が行われる。

【0081】時刻t+3Tにおいて、アドレスカウンタの出力信号Eに、“N×2”を加算したアドレス信号に基づいて、BIT2が読み出され、画素xの表示(黒又は白)が行われる。

【0082】時刻t+4Tにおいて、アドレスカウンタの出力信号Eに、“N×2”を加算したアドレス信号に基づいて、BIT2が読み出され、画素xの表示(黒又は白)が行われる。

【0083】時刻t+5Tにおいて、アドレスカウンタの出力信号Eに、“N×1”を加算したアドレス信号に基づいて、BIT1が読み出され、画素xの表示(黒又は白)が行われる。

【0084】時刻t+6Tにおいて、アドレスカウンタの出力信号Eに、“N×0”を加算したアドレス信号に基づいて、BIT0が読み出され、画素xの表示(黒又は白)が行われる。

【0085】例えば、画素xの濃度値が“5”的場合には、BIT2, BIT1, BIT0は、それぞれ“1”, “0”, “1”であるから、メモリ13からは、一定周期Tで、“1101101”が読み出され、例えば、“0”“白”、“1”“黒”とすると、画素xについては、一定周期Tで、“黒黑白黒黑白黒”が表示されることになる。

【0086】なお、本発明では、上述したように、8階調表示の場合には、BIT2を4回、BIT1を2回、

BIT0を1回読み出すことが重要であり、その順序は、特に、限定されるものではない。

【0087】一般には、2<sup>n</sup>階調表示の場合、BITn-1を2<sup>n-1</sup>回、…BIT1を2<sup>1</sup>回、BIT0を2<sup>0</sup>回読み出せばよい。

【0088】[D] 以下、図1の階調表示LCDコントローラを用いた場合の具体的な動作について、図1及び図6を参照しながら説明する。前提条件として、1画素分のデータが、3ビット(8階調)BIT2, BIT1, BIT0、即ち、0, 1, 2, … 7(十進数)で表されるものとする。

【0089】画像表示は、CRT表示と同様に、画像を構成する画素を1つずつ順次走査していくことにより行うため、アドレスカウンタ15Aは、連続した値を持つアドレス信号ADD, ADD+1, ADD+(N-1)を、1つずつ、順次、出力する。

【0090】まず、フレームカウンタ18の出力信号Aが“1”的場合、加算器23において、アドレス信号ADD, ADD+1, ADD+(N-1)に、N(特定値)×2が加算され、その結果、得られた信号ADD+2N, (ADD+1)+2N, {ADD+(N-1)}+2Nが、アドレス信号Cとして、バス11を経由してメモリ13に供給される。

【0091】この時、メモリ13からは、1フレーム分のBIT2(=g, h, … i)が、順次、出力される。このBIT2は、バス11を経由して、LCDコントローラ14に入力される。さらに、BIT2は、LCDコントローラ14から、ローカルバス22を経由して、LCDドライバ21に供給される。

【0092】次に、フレームカウンタ18の出力信号Aが“2”的場合、出力信号Aが“1”的場合と同様の動作が行われる。

【0093】次に、フレームカウンタ18の出力信号Aが“3”的場合、加算器23において、アドレス信号ADD, ADD+1, ADD+(N-1)に、N(特定値)×1が加算され、その結果、得られた信号ADD+N, (ADD+1)+N, {ADD+(N-1)}+Nが、アドレス信号Cとして、バス11を経由してメモリ13に供給される。

【0094】この時、メモリ13からは、1フレーム分のBIT1(=d, e, … f)が、順次、出力される。このBIT1は、バス11を経由して、LCDコントローラ14に入力される。さらに、BIT1は、LCDコントローラ14から、ローカルバス22を経由して、LCDドライバ21に供給される。

【0095】次に、フレームカウンタ18の出力信号Aが“4”的場合、出力信号Aが“1”的場合と同様の動作が行われる。

【0096】次に、フレームカウンタ18の出力信号Aが“5”的場合、出力信号Aが“1”的場合と同様の動

作が行われる。

【0097】次に、フレームカウンタ18の出力信号Aが“6”的場合、出力信号Aが“3”的場合と同様の動作が行われる。

【0098】次に、フレームカウンタ18の出力信号Aが“7”的場合、加算器23において、アドレス信号ADD, ADD+1, ADD+(N-1)に、N(特定値)×0が加算され、その結果、得られた信号ADD, (ADD+1), {ADD+(N-1)}が、アドレス信号Cとして、バス11を経由してメモリ13に供給される。

【0099】この時、メモリ13からは、1フレーム分のBIT0 (=a, b, … c)が、順次、出力される。このBIT0は、バス11を経由して、LCDコントローラ14に入力される。さらに、BIT0は、LCDコントローラ14から、ローカルバス22を経由して、LCDドライバ21に供給される。

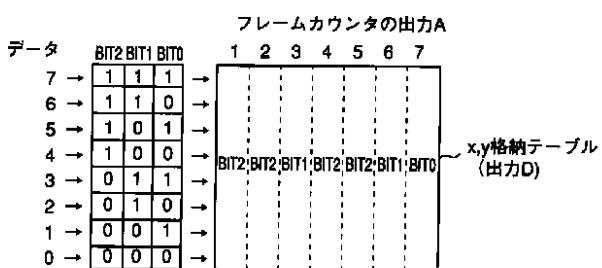

【0100】本例では、x, y格納テーブル(本明細書では、簡単のため、yについては省略している。)24を、図6に示すような関係に設定している。

【0101】即ち、8階調(3ビット)表示に関し、BIT2を4回、BIT1を2回、BIT0を1回出力するために、フレームカウンタ18の出力信号が、“1”, “2”, “3”, “4”, “5”, “6”, “7”的とき、それぞれ、BIT2, BIT2, BIT1, BIT2, BIT2, BIT1, BIT0を出力するようにしている。しかし、これは、一例であり、この順序を変えてもよいことは言うまでもない。

【0102】本発明によれば、ディスプレイ内の各画素の階調数(2<sup>n</sup>)、即ち、メモリ13に格納される1画素分のビット数(n)にかかわらず、メモリ13からは、常に、階調変換された(2<sup>n</sup>-1)値データのうちの1つが出力されることになる。また、LCDコントローラ14では、データのデコード動作や、階調変換動作などが不要である。

【0103】従って、本発明のLCDコントローラでは、画素の階調数によらず、かつ、キャッシュメモリを設けることなく、メモリ13から出力されるデータを、直ちに、LCDコントローラ14内に取り込むことができるため、バス11の占有率を減らすことができる。

【0104】例えば、従来では、メモリ13からLCDコントローラ14へのデータ転送のためにバス11を使用している時間、即ち、バス11の占有率は、転送するデータのビット数が大きくなればなるほど、増加する。これに対し、本発明では、例えば、2階調(白、黒)のモノクロ表示を基準にした場合、これを、4 (=2<sup>2</sup>)階調のモノクロ表示にしても、バスの占有率は、2階調のモノクロ表示と同じであり、また、これを、8 (=2<sup>3</sup>)階調のモノクロ表示にしても、2階調のモノクロ表示と同じである。

【0105】つまり、本発明によれば、画素の階調数が増えてても、CPU12のバス11の使用が制限されることはない。

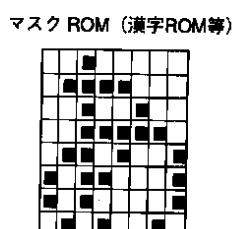

【0106】[E] データ格納に関する優位性

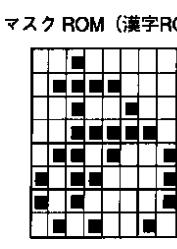

図1に示すように、例えば、マスクROM(漢字ROMなど)に保存されたデータは、一度、メモリ(ディスプレイRAM)13に格納され、この後、メモリ13のデータを読み出し、ディスプレイ表示を行う。

【0107】ここで、従来では、例えば、マスクROMから読み出した文字データ(8バイト)は、(8×n)バイトのデータに変換され(2<sup>n</sup>階調表示の場合)、これがメモリ13に格納される。このため、データ加工のための処理が必要となり、そのためのソフトウェアも必要となる。

【0108】これに対し、本発明では、例えば、マスクROMから読み出した文字データ(8バイト)は、加工されずに(階調数2<sup>n</sup>にも関係しない)、そのままメモリ13に格納される。つまり、本発明では、メモリ13の各エリア(BITn, … BIT1, BIT0)に、マスクROMから読み出した文字データ(8バイト)がそのまま書き込まれるか、又は何も書き込まれない。

【0109】従って、本発明では、マスクROMから読み出したデータを加工する必要がなく、従来技術に比べ、データ加工のためのソフトウェアが必要ないという優位性を有する。

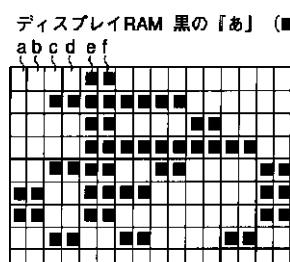

【0110】具体例について検討する。なお、以下の例では、簡単のため、1画素を4階調(2ビット)で表現する場合について説明する。

【0111】従来方式

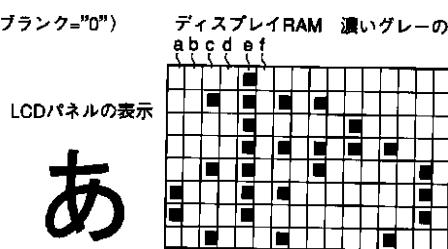

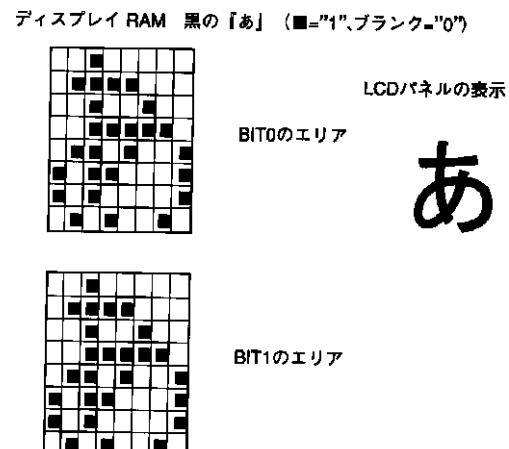

4階調表示では、1画素が2ビットで表現される。このため、例えば、図7に示すように、マスクROMに保存された「あ」という文字を読み出し、メモリ13に格納しようとする場合、図8又は図9に示すように、「あ」という文字は、8バイトデータから16バイトデータに変換された後に、メモリ13に格納される(図8及び図9は、図14のメモリマップに対応している。)。

【0112】そして、例えば、黒の「あ」の場合(図8)、2ビットデータe, f(いずれも“1”)により、1画素が表現される。つまり、eが“BIT1”、fが“BIT0”として、メモリ13から読み出され、LCDコントローラ14に供給される。同様に、例えば、濃いグレーの「あ」の場合(図9)、2ビットデータe(=“1”), f(=“0”)により、1画素が表現される。つまり、eが“BIT1”、fが“BIT0”として、メモリ13から読み出され、LCDコントローラ14に供給される。

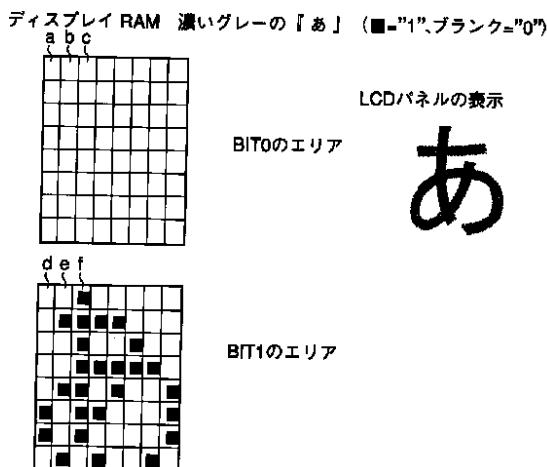

【0113】本発明の方式

本発明では、例えば、図10に示すように、マスクROMに保存された「あ」という文字を読み出し、メモリ1

3に格納しようとする場合、図11又は図12に示すように、1画素の階調数に関係なく、「あ」という文字は、8バイトデータのまま、メモリ13に格納される（図11及び図12は、図2のメモリマップに対応している。）。

【0114】そして、例えば、黒の「あ」の場合（図11）、2ビットデータc,f（いずれも“1”）により、1画素が表現される。つまり、cが“BIT0”に相当し、fが“BIT1”に相当し、3値データ（BIT1を2回、BIT0を1回）は、一フレーム間隔（フレームカウンタの値に従う。）で、順次、読み出される。同様に、例えば、濃いグレーの「あ」の場合（図12）、2ビットデータc（＝“0”），f（＝“1”）により、1画素が表現される。つまり、cが“BIT0”に相当し、fが“BIT1”に相当し、3値データ（BIT1を2回、BIT0を1回）は、一フレーム間隔（フレームカウンタの値に従う。）で、順次、読み出される。

#### 【0115】[F] その他

なお、上述の実施の形態においては、例えば、“0”＝“白”、“1”＝“黒”で説明した箇所があるが、本発明は、当然に、白と黒が反転関係にあるLCD（“0”＝“黒”、“1”＝“白”）にも適用できる。また、本発明は、疑似カラーLCDに適用することも可能である。

#### 【0116】

【発明の効果】以上、説明したように、本発明によれば、ディスプレイ内の各画素の階調数（ $2^n$ ）、即ち、メモリ（ディスプレイRAM）に格納される1画素分のビット数（n）にかかわらず、メモリからは、常に、階調変換された（ $2^n - 1$ ）値データのうちの1つが出力されることになる。また、LCDコントローラでは、データのデコード動作や、階調変換動作などが不要である。

【0117】従って、本発明のLCDコントローラでは、1画素の階調数を増加しても、キャッシュメモリを設けることなしに、常に、LCDコントローラへのデータ転送に関するバスの占有率を一定（2階調のモノクロ表示と同じ）にすることができます。つまり、1画素の階\*

\*階調数を増加しても、CPUにおけるバスの使用が制限されることもない。また、メモリに対するデータの格納に関して、マスクROMのデータを変換する必要がないため、ソフト的にも簡略化される。

#### 【図面の簡単な説明】

【図1】本発明の実施の形態に関するLCDコントローラを示す図。

【図2】図1のメモリのメモリマップを示す図。

【図3】ディスプレイと画素の関係を示す図。

【図4】アドレスカウンタの出力に特定値を加算する方法の一例を示す図。

【図5】メモリ内のデータとアドレスの関係を示す図。

【図6】x,y格納テーブルの一例を示す図。

【図7】マスクROM内の文字データを示す図。

【図8】従来のメモリ内の文字データを示す図。

【図9】従来のメモリ内の文字データを示す図。

【図10】マスクROM内の文字データを示す図。

【図11】本発明のメモリ内の文字データを示す図。

【図12】本発明のメモリ内の文字データを示す図。

【図13】従来のLCDコントローラを示す図。

【図14】図13のメモリのメモリマップを示す図。

【図15】階調変換テーブルの一例を示す図。

#### 【符号の説明】

|             |             |

|-------------|-------------|

| 1 1         | : バス、       |

| 1 2         | : CPU、      |

| 1 3         | : メモリ（ディスプレ |

| 1 4         | : LCDコントロー  |

| 1 5 , 1 5 A | : アドレスカウンタ、 |

| 1 6         | : キャッシュメモリ、 |

| 1 8         | : フレームカウンタ、 |

| 1 9         | : 階調変換テーブル、 |

| 2 0         | : パッファ、     |

| 2 1         | : LCDドライバ、  |

| 2 2         | : ローカルバス、   |

| 2 3         | : 加算器、      |

| 2 4         | : x,y格納テーブ  |

|             | ル。          |

【図7】

【図8】

【図9】

【図1】

【図2】

【図3】

【図5】

【図6】

\*フレームカウンタの出力に応じて

BIT2を4回、BIT1を2回、BIT0を1回

だけ出力する。

順序は、一例であり、重要ではない。

\*フレームカウンタの出力は

一定周期(一画像内の全画素、

即ち、1フレームを表示)後に変わる。

【図10】

【図4】

【図11】

【図12】

【図13】

【図14】

【図15】

フロントページの続き

F ターム(参考) 2H093 NA55 NA59 NC11 NC27 NC29

ND03 ND49

5C006 AA14 AF02 AF04 AF44 BF02

BF15 BF22 BF49 EA03 FA43

FA52 FA56

5C080 AA10 BB05 CC03 DD22 DD27

DD30 EE29 JJ01 JJ02 KK02

|                |                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 灰色显示LCD控制器                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2001324964A</a>                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2001-11-22 |

| 申请号            | JP2000143529                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2000-05-16 |

| [标]申请(专利权)人(译) | 东芝LSI SYST支持<br>株式会社东芝                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 东芝LSI眼系统支持有限责任公司<br>东芝公司                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 新田義真                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 新田 義真                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/36 G02F1/133.575 G09G3/20.641.E                                                                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 2H093/NA55 2H093/NA59 2H093/NC11 2H093/NC27 2H093/NC29 2H093/ND03 2H093/ND49 5C006 /AA14 5C006/AF02 5C006/AF04 5C006/AF44 5C006/BF02 5C006/BF15 5C006/BF22 5C006/BF49 5C006/EA03 5C006/FA43 5C006/FA52 5C006/FA56 5C080/AA10 5C080/BB05 5C080/CC03 5C080 /DD22 5C080/DD27 5C080/DD30 5C080/EE29 5C080/JJ01 5C080/JJ02 5C080/KK02 2H193/ZD25 2H193/ZD30 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

要解决的问题：消除LCD控制器中的灰度转换需求。四级（2位）显示在存储器中提供了两个区域。一帧的N个像素的最低有效位BIT0存储在由地址ADD，... ADD + (N-1) 和地址ADD + N，... ADD + (N-1) 选择的一个区域中，在由+N选择的另一区域中，存储一帧的N个像素的最高有效位BIT1。地址计数器15A产生地址信号ADD，... ADD + (N-1)。加法器23基于帧计数器值“1”，“2”和“3”将N（特定值）×1或N×0加到地址信号ADD，... ADD + (N-1)。要添加。N×1被添加两次，并且N×0被添加一次。