(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-25277

(P2007-25277A)

(43) 公開日 平成19年2月1日(2007.2.1)

| (51) Int.C1.                        | F 1                          | テーマコード (参考)                                                                                                                                                    |

|-------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>G09G 3/36</b>                    | <b>(2006.01)</b>             | G09G 3/36 2H093                                                                                                                                                |

| <b>G09G 3/20</b>                    | <b>(2006.01)</b>             | G09G 3/20 611D 5C006                                                                                                                                           |

| <b>G02F 1/133</b>                   | <b>(2006.01)</b>             | G09G 3/20 623V 5C080                                                                                                                                           |

|                                     |                              | G09G 3/20 623J                                                                                                                                                 |

|                                     |                              | G09G 3/20 623R                                                                                                                                                 |

| 審査請求 未請求 請求項の数 1 O L (全 9 頁) 最終頁に続く |                              |                                                                                                                                                                |

| (21) 出願番号                           | 特願2005-207503 (P2005-207503) | (71) 出願人 000004329                                                                                                                                             |

| (22) 出願日                            | 平成17年7月15日 (2005.7.15)       | 日本ビクター株式会社<br>神奈川県横浜市神奈川区守屋町3丁目12<br>番地                                                                                                                        |

|                                     |                              | (74) 代理人 100089956                                                                                                                                             |

|                                     |                              | 弁理士 永井 利和                                                                                                                                                      |

|                                     |                              | (72) 発明者 内山 裕治<br>神奈川県横浜市神奈川区守屋町3丁目12<br>番地 日本ビクター株式会社内                                                                                                        |

|                                     |                              | F ターム (参考) 2H093 NA16 NC13 NC16 NC22 NC24<br>NC25 NC26 NC34 NC35 ND06<br>ND15<br>5C006 AC21 BB16 BC16 BC23 FA31<br>FA36 FA37<br>5C080 AA10 BB05 DD01 DD10 JJ02 |

## (54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】多相化された画像信号を用いる液晶表示パネルにおける各相の系列配線の相互間で結合インピーダンスに起因して生じる信号クロストークを抑制して、高品質な画像表示を実現する。

【解決手段】多相化された画像信号Ev[1]～Ev[8]は各単相処理回路10-1～8でそれぞれ処理が施され、D/A変換された後、液晶表示パネルへ出力される。各単相処理回路10-X:(X=1～8)は、入力画像信号Ev[X]を遅延させて出力する遅延回路21と、各入力画像信号Ev[1]～Ev[8]に対して前記各結合インピーダンスによるクロストーク量を打ち消すための重み付けを施した信号を出力する各重み付け処理回路X-1～8と、重み付け後の各信号を加算する加算回路22と、遅延回路21の画像信号出力と加算回路22の加算信号とを加算する加算回路3とからなる。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

液晶表示パネルが、複数の列信号電極と、複数の行走査電極と、前記列信号電極と前記行走査電極との各交差部にマトリクス状に配列したスイッチングトランジスタおよび画素電極を含む表示画素と、前記複数の列信号電極に表示信号を順次サンプリングするためにシフトレジスタ回路とスイッチング回路群を含む列信号電極駆動回路と、前記複数の行走査電極に行選択パルスを供給するシフトレジスタ回路を含む行走査電極駆動回路と、前記列信号電極を隣接するN本(2の自然数)の列信号電極毎にグループ化すると共に、前記各グループのN本の列信号電極内の対応する列信号電極に前記スイッチ回路群を介して共通に接続されるN本の画像信号入力線とで構成されており、N系列の同時並列信号に変換された各画像信号が前記液晶表示パネルの各画像信号入力線に供給される液晶表示装置において、

前記N系列の各画像信号毎に設けた単相処理回路により前記各画像信号を補正して前記液晶表示パネル側の対応する各画像信号入力線へ出力する信号補正回路を設け、

前記各単相処理回路は、

自らが補正対象とする画像信号を遅延して出力させる遅延手段と、

前記N系列の各画像信号毎に設けられ、前記液晶表示パネル側の回路における自らが補正対象とする画像信号に対応する信号系統と他の入力画像信号に対応する各信号系統との間に介在する結合インピーダンスに起因して発生する信号クロストークを打ち消すための重み付け係数を設定して、前記各画像信号に対する重み付け処理を行う各重み付け処理手段と、

前記各重み付け処理手段による重み付け処理後の各信号を加算する第1加算手段と、

前記遅延手段が出力させる画像信号と前記第1加算手段による加算後の信号とを加算して出力する第2加算手段と

からなることを特徴とする液晶表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は液晶表示装置に係り、特に多相化された画像信号によって表示が行われる投射型ディスプレいやビューファインダ、ヘッドマウントディスプレイ等に適用され、多相化信号相互間のクロストークを低減化して高画質な画像を表示させるための改善に関する。

## 【背景技術】

## 【0002】

アクティブマトリクス型の液晶表示装置では、各画素に印加する画像信号を保持する補助容量(電荷保持容量)の周波数特性や、画素のオン/オフの切り換えを行うトランジスタのスイッチング特性の制約から、下記特許文献1, 2, 3に示されるように、画像信号をN相(Nは2以上の整数)に多相化させて入力する方式が採用されており、それによって1相毎の動作速度を低減化させている。

## 【0003】

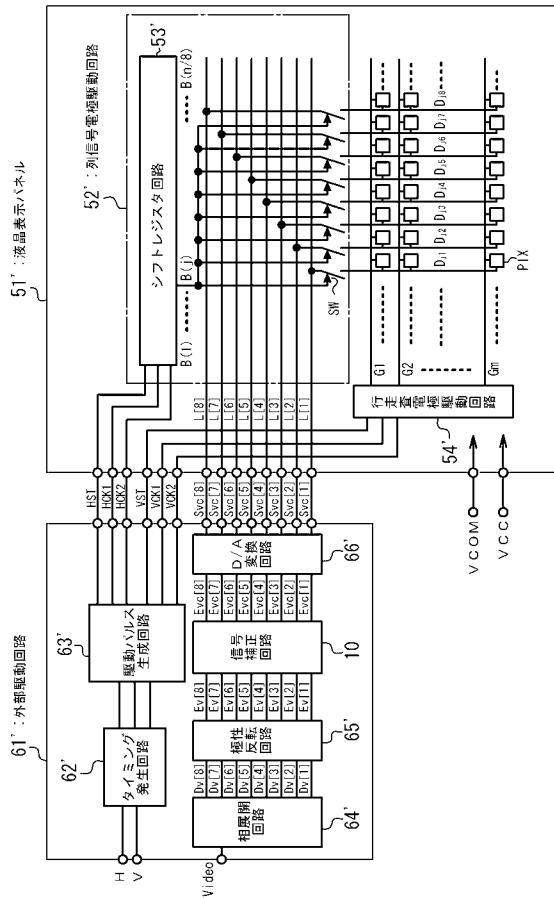

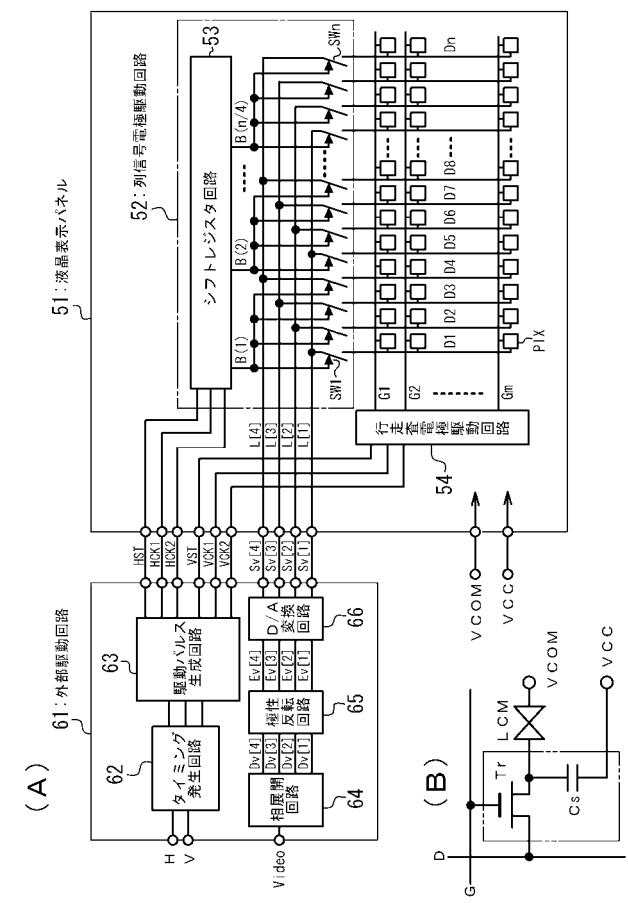

図4(A)は従来の液晶表示装置の一例を示す構成図である。同図において、液晶表示パネル51には複数の列信号電極D1, D2, ..., Dnと行走査電極G1, G2, ..., Gmとが互いに直交する方向に形成されており、各電極D1~Dn, G1~Gmの各交差部には表示画素PIXが形成されている。この表示画素PIXは、図4(B)に示すように、スイッチングトランジスタTrと、補助容量Csと、図示しない表示画素電極と透明基板(共通電極)との間に封止された液晶表示体LCMとで構成されており、共通電極には共通直流電圧(VCOM)が、補助容量Csの一方の電極には共通直流電圧(VCC)がそれぞれ印加されるようになっている。尚、図4(B)では列信号電極は代表してDで表し、行走査電極は代表してGで表している。

## 【0004】

列電極駆動回路52はシフトレジスタ回路53およびスイッチ回路群SW1~SWnより構

成され、スイッチ回路群  $S W_1 \sim S W_n$  の入力側には  $N$  本（この場合は 4 相に多相化されており  $N = 4$ ）の画像信号入力線  $L[1], L[2], L[3], L[4]$  が各々水平方向に隣接する 4 画素ピッチおきに（4 信号電極おきに）接続されている。隣接する 4 つのスイッチ回路を 1 グループとして、各スイッチ制御端子には前記シフトレジスタ回路 5 3 の各段の出力線  $B(1), B(2), \dots, B(n/4)$  が順番にグループ単位で接続されている。また、行走査電極駆動回路 5 4 はシフトレジスタ回路で構成され、各段の出力線は各々行走査電極  $G_1, G_2, \dots, G_m$  に接続され、各行走査電極  $G_1, G_2, \dots, G_m$  は各々同一行に位置する表示画素  $P_{IX}$  のスイッチングトランジスタ  $T_r$  のゲート端子に接続されている。

## 【0005】

また、液晶表示パネル 5 1 には図示するように外部駆動回路 6 1 が接続されている。この外部駆動回路 6 1 はタイミング発生回路 6 2、駆動パルス生成回路 6 3、相展開回路 6 4、及び極性反転回路 6 5 で構成されている。タイミング発生回路 6 2 は前段から水平同期信号  $H$ 、垂直同期信号  $V$  を受け、これらに同期した水平、垂直およびクロック等のタイミング信号と、画像信号を並列相展開するのに必要なタイミング信号を発生する。前記駆動パルス生成回路 6 3 はタイミング発生回路 6 2 から水平、垂直、クロック信号を受け、液晶表示パネル 5 1 の列電極駆動回路 5 2 で用いる駆動信号  $HST$ （水平スタート信号）、 $HCK$ （水平シフトクロック信号）1,  $HCK$ （水平シフトクロック信号）2 および行走査電極駆動回路 5 4 で用いる駆動信号  $VST$ （垂直スタート信号）、 $VCK$ （垂直シフトクロック信号）1,  $VCK$ （垂直シフトクロック信号）2 を生成する。

## 【0006】

外部より入力されるディジタル画像信号  $Video$  は相展開回路 6 4 により予め隣接する  $N$  個の表示画素に対応した  $N$  系列（図示例では  $N = 4$ ）の同時並列信号  $Dv[1] \sim Dv[4]$  に変換される。即ち、この信号  $Dv[1] \sim Dv[4]$  は画像信号  $Video$  が画像信号入力線  $L[1] \sim L[4]$  に対してサイクリック的に順に入力されるような態様で分配される。また、相展開した画像信号  $Dv[1] \sim Dv[4]$  は極性反転回路 6 5 によって 1 フレーム期間毎に極性が反転する交流化信号  $Ev[1] \sim Ev[4]$  に変換された後、D/A 変換回路 6 6 によってアナログ画像信号  $Sv[1] \sim Sv[4]$  に変換されて液晶表示パネル 5 1 の画像信号入力線  $L[1], L[2], L[3], L[4]$  に同時並列入力される。このように画像信号を 1 フレーム期間毎に変化する交流化信号に変換するのは、表示体である液晶を交流電圧で駆動することによって材料劣化や焼き付きを防止するためである。

## 【0007】

そして、外部駆動回路 6 1 から液晶表示パネル 5 1 の列信号電極駆動回路 5 2 のシフトレジスタ回路 5 3 に  $HST, HCK_1, HCK_2$  の各駆動パルスが供給されることにより、列信号電極駆動回路 5 2 の構成要素であるシフトレジスタ 5 3 が駆動され、各出力段  $B(1) \sim B(n/4)$  に順次パルスが output される。この列信号電極駆動回路 5 2 のスイッチ群  $S W_1 \sim S W_n$  はこのシフトレジスタ回路 5 3 の出力により順次オンとなり、前記画像信号入力線  $L[1], L[2], L[3], L[4]$  に並列入力される画像信号  $Sv[1] \sim Sv[4]$  を隣接する 4 本の組（グループ）の列信号電極（ $D_1, D_2, D_3, D_4$ ），（ $D_5, D_6, D_7, D_8$ ），…毎に順次並列的にサンプリングする。このように、画像信号（表示信号） $Sv[1] \sim Sv[4]$  を  $N$  相（ $N = 4$ ）の並列信号として処理することにより、シフトレジスタの駆動クロックレートおよび表示信号のレートを  $1/N$  に低減することが可能であり、より高画素数の表示装置への対応を可能としている。

## 【0008】

一方、前記外部駆動回路 6 1 から行走査電極駆動回路 5 4 に  $VST, VCK_1, VCK_2$  の各駆動パルスを供給することにより、行走査電極  $G_1, G_2, \dots, G_m$  には順次選択パルスが送出され、列信号電極  $D_1 \sim D_n$  と行走査電極  $G_1 \sim G_m$  の各交差部に設けられた表示画素  $P_{IX}$  のスイッチングトランジスタ  $T_r$  の各行を順次オン状態とする。その結果、列信号電極  $D$  にサンプリングした表示信号がスイッチングトランジスタ  $T_r$  を介して液晶表示体  $L_{CM}$  に供給される。補助容量  $C_s$  はスイッチングトランジスタ  $T_r$  がオフの期間での液晶駆動電圧を保持し、高デューティ駆動を実現する目的で設けられている。

10

20

30

40

50

## 【0009】

ところで、前記液晶表示パネル51では各表示画素PIXの補助容量Csの一方の電極には共通直流電圧(VCC)が印加されるため、各電極が共通に接続された関係になっている。その場合、各補助容量Csに蓄積された画像信号のクロストークが発生して画像の表示品質が低下するという問題がある。特に、前記のように多相化された画像信号を補助容量Csに同時に書き込むと、電圧変動量が大きくなつて画像の表示品質に与える影響が大きくなる。

## 【0010】

そこで、下記特許文献4では、多相化した入力画像信号の各相の表示画素PIXでは共通配線とするが、多相化間では別配線とした構成として、補助容量Csを介した信号のクロストークの発生を抑制した液晶表示装置が提案されている。また、下記特許文献5には、多相化された画像信号の加算結果を用いて補助容量Csの電圧変動分を補償する信号を作成し、その補償信号を個別の画像信号に加えることによりクロストークの発生を防止する液晶表示装置が開示されている。

10

【特許文献1】特開平8-292416号公報

【特許文献2】特開平11-133932号公報

【特許文献3】特開2003-140622号公報

【特許文献4】特開2004-045469号公報

【特許文献5】特開2004-206050号公報

【発明の開示】

20

【発明が解決しようとする課題】

## 【0011】

上記のように、画像信号を多相化して液晶表示パネルに入力する方式の液晶表示装置において、画像信号のクロストークを防止するための提案がなされているが、ある程度の改善は図れるものの未だ十分とはいえない。これは、特許文献4及び5の提案では、液晶表示パネル51における各表示画素PIXの補助容量Csの一方の端子に直流電圧(VCC)の印加用電極が共通に接続されていることが画像信号のクロストークの発生原因になっているとみなして対策を施しているが、それだけではなく、実際には多相化された画像信号の配線部分やスイッチングトランジスタTrの部分で生じるクロストークも存在するからである。

30

## 【0012】

そして、表示画像の高解像度化には表示画素PIXの微細化が必要不可欠であるが、その微細化は信号配線間の結合インピーダンスを介しての信号クロストーク量を増加させて、画像の表示品質を劣化させることになる。そこで、本発明は、液晶表示パネルにおける配線相互間等の結合インピーダンスに起因して生じる画像信号のクロストークを抑制させて表示品質を向上させた液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

## 【0013】

本発明は、液晶表示パネルが、複数の列信号電極と、複数の行走査電極と、前記列信号電極と前記行走査電極との各交差部にマトリクス状に配列したスイッチングトランジスタおよび画素電極を含む表示画素と、前記複数の列信号電極に表示信号を順次サンプリングするためにシフトレジスタ回路とスイッチング回路群を含む列信号電極駆動回路と、前記複数の行走査電極に行選択パルスを供給するシフトレジスタ回路を含む行走査電極駆動回路と、前記列信号電極を隣接するN本(2の自然数)の列信号電極毎にグループ化すると共に、前記各グループのN本の列信号電極内の対応する列信号電極に前記スイッチ回路群を介して共通に接続されるN本の画像信号入力線とで構成されており、N系列の同時並列信号に変換された各画像信号が前記液晶表示パネルの各画像信号入力線に供給される液晶表示装置において、前記N系列の各画像信号毎に設けた単相処理回路により前記各画像信号を補正して前記液晶表示パネル側の対応する各画像信号入力線へ出力する信号補正回路を設け、前記各単相処理回路は、自らが補正対象とする画像信号を遅延して出力させる

40

50

遅延手段と、前記N系列の各画像信号毎に設けられ、前記液晶表示パネル側の回路における自らが補正対象とする画像信号に対応する信号系統と他の入力画像信号に対応する各信号系統との間に介在する結合インピーダンスに起因して発生する信号クロストークを打ち消すための重み付け係数を設定して、前記各画像信号に対する重み付け処理を行う各重み付け手段と、前記各重み付け処理手段による重み付け処理後の各信号を加算する第1加算手段と、前記遅延手段が出力させる画像信号と前記第1加算手段による加算後の信号とを加算して出力する第2加算手段とからなることを特徴とする液晶表示装置に係る。

#### 【0014】

本発明では、各重み付け手段と第1加算手段により、N系列の各画像信号を用いて液晶表示パネル側における各信号系統間の結合インピーダンスによる信号クロストークを打ち消すための信号を作成し、予め液晶表示パネル側の各画像信号入力線へ出力する各画像信号に加算している。従って、結果的に、液晶表示パネルでの画像表示段階では信号クロストークによる表示品質の劣化が抑制できる。尚、遅延手段は各重み付け手段と第1加算手段での処理に要する遅延時間分だけ画像信号を遅延出力することで、第2加算手段での加算タイミングを適正化している。

#### 【発明の効果】

#### 【0015】

本発明は、多相化された画像信号を用いて表示動作を行う液晶表示装置において、液晶表示パネルにおける配線相互間等の結合インピーダンスに起因して生じる画像信号のクロストークを抑制し、高品質な画像表示を実現する。

#### 【発明を実施するための最良の形態】

#### 【0016】

以下、本発明の実施形態を図1から図3を用いて詳細に説明する。先ず、図1はこの実施形態に係る液晶表示装置の構成図であり、液晶表示パネル51' と外部駆動回路61' とからなるが、上記の図4の液晶表示装置が画像信号を4相に多相化した場合であるのに対して、8相に多相した場合の回路構成になっている。尤も、液晶表示装置としての基本的構成と動作は、多相化数の相違に基づく点を除いて、図4の装置に準じたものとなり、ここではそれらの具体的な説明は省略する。尚、図1において「Y」(但し、Yは符号)で示される回路要素等は、図4において「Y」として示されている回路要素等に対応する。

#### 【0017】

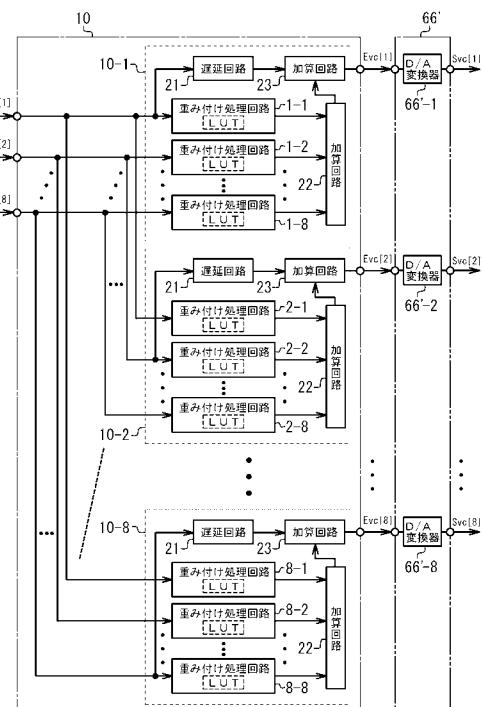

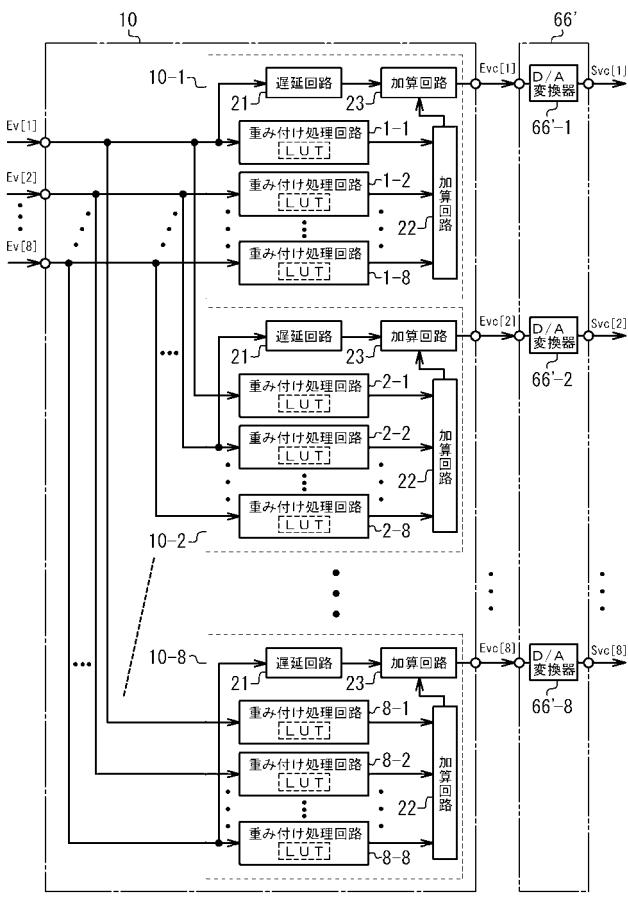

その前提で、図1と図4とを比較すれば明らかなように、この実施形態の液晶表示装置の特徴は、外部駆動回路61'における極性反転回路65' とD/A変換回路66'との間に信号補正回路10が設けられている点にある。そして、その信号補正回路10の具体的な回路構成は図2に示され、信号補正回路10には極性反転回路65'で処理された8相の交流化画像信号Ev[1]~Ev[8]が入力されており、各相の画像信号Ev[1]~Ev[8]がそれぞれ単相処理回路10-1~8で補正された後、その補正後の画像信号Evc[1]~Evc[8]が次段のD/A変換回路66'の各D/A変換器に出力されるようになっている。

#### 【0018】

信号補正回路10において多相化された全ての画像信号Ev[1]~Ev[8]が各単相処理回路10-1~8に入力されており、各単相処理回路10-X: (X=1~8)は、各画像信号Ev[1]~Ev[8]がそれぞれ入力されている重み付け処理回路X-1~8と、画像信号Ev[1]~Ev[8]の内の画像信号Ev[X]のみが入力されている遅延回路21と、各重み付け処理回路X-1~8による処理後の信号を全て加算する加算回路22と、遅延回路21で遅延せしめられた画像信号Ev[X]に加算回路22の加算結果を加算する加算回路23とからなり、その加算回路23の加算信号Evc[X]がD/A変換回路66'のD/A変換器66'-Xに出力されている。

#### 【0019】

ところで、各単相処理回路10-Xにおける各重み付け処理回路X-1~8は、それぞれ固有に入出力関係を規定したLUT(Look Up Table)を内蔵させており、LUTを参照して入力信号Ev[1]~Ev[8]に重み付けを行った信号を出力させるようになっている。そして、その重み付け処理は、液晶表示パネル51'側の回路に構成される各相間の結合インピーダンスによる信号クロストークを打ち消すための重み付け係数を設定して、前記各画像信号に対する重み付け処理を行う各重み付け手段と、前記各重み付け処理手段による重み付け処理後の各信号を加算する第1加算手段と、前記遅延手段が出力させる画像信号と前記第1加算手段による加算後の信号とを加算して出力する第2加算手段とからなることを特徴とする液晶表示装置に係る。

10

20

30

40

50

ダンスによって生じる信号クロストークを低減化させるための信号を生成する処理であり、各 LUT は液晶表示パネル 51' 側での各相の画像信号入力線 L[1] ~ L[8] に係る系統と各系統相互間のインピーダンスを考慮して個別に設定される。

【0020】

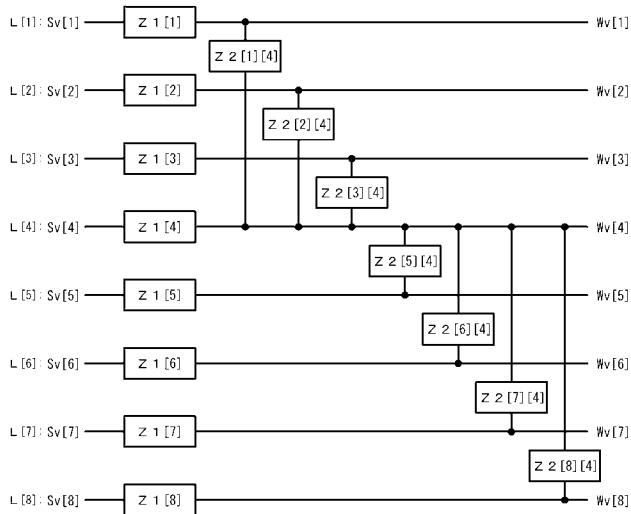

具体的には、先ず、液晶表示パネル 51' における各相の画像信号入力線 L[1] ~ L[8] に係る系統にはそれぞれ固有に直列インピーダンス  $Z_1[1] \sim Z_1[8]$  が存在すると共に、各系統相互間にもそれぞれ固有な結合インピーダンスが存在し、例えば、画像信号入力線 L[4] に係る系統と他の各画像信号入力線 L[1] ~ L[3], L[5] ~ L[8] に係る系統との間の結合インピーダンスを  $Z_2[1][4], Z_2[2][4], Z_2[3][4], Z_2[5][4], Z_2[6][4], Z_2[7][4], Z_2[8][4]$  とすると、図 3 に示すような回路が構成されていると仮定できる。尚、同図において、Sv[1] ~ Sv[8] は入力画像信号の電圧であり、Wv[1] ~ Wv[8] は実際に印加される出力画像信号の電圧である。

【0021】

その場合、第 4 相目の画像信号入力線 L[4] における出力画像信号の電圧 Wv[4] は次の数式 1 で表すことができる。

【数 1】

$$Wv[4] = \sum_{i=1}^3 \{ F_4(i) - Q_4(i) \} + \sum_{i=5}^8 \{ F_4(i) - Q_4(i) \}$$

$$F_4(i) = \frac{Z_2[i][4] + Z_1[i]}{Z_1[4] + Z_2[i][4] + Z_1[i]} Sv[4] \quad 20$$

$$Q_4(i) = \frac{Z_1[4]}{Z_1[4] + Z_2[i][4] + Z_1[i]} Sv[i]$$

ここで、 $F_4(i)$  における  $Sv[4]$  の係数は結合インピーダンスによる信号電圧の変化を規定するものであり、 $Q_4(i)$  における  $Sv[i]$  の係数は結合インピーダンスによる信号クロストークによる電圧変化を規定するものである。

また、一般に第 X 相目の画像信号入力線 L[X] における出力画像信号の電圧 Wv[X] は次の数式 2 で表すことができる。

【数 2】

$$Wv[X] = \sum_{i=1}^{X-1} \{ F_X(i) - Q_X(i) \} + \sum_{i=X+1}^8 \{ F_X(i) - Q_X(i) \}$$

$$F_X(i) = \frac{Z_2[i][X] + Z_1[i]}{Z_1[X] + Z_2[i][X] + Z_1[i]} Sv[X]$$

$$Q_X(i) = \frac{Z_1[X]}{Z_1[X] + Z_2[i][X] + Z_1[i]} Sv[i]$$

【0022】

従って、図 2 に戻って、第 X 相目の信号処理を実行する単相処理回路 10-X の各重み付け処理回路 X-i が内蔵する LUT については、 $i = 1 \sim (X-1), (X+1) \sim 8$  の重み付け処理回路 X-i では次の数式 3 に相当するゲイン係数を用いたリニアテーブルを用い、

【数 3】

$$\frac{Z_1[X]}{Z_1[X] + Z_2[i][X] + Z_1[i]}$$

また、重み付け処理回路 X-X では次の数式 4 に相当するゲイン係数を用いたリニアテーブルを用いることにより、

10

20

30

40

## 【数4】

$$\frac{1}{8} \left( \sum_{i=1}^{X-1} \{ 1 \neq Fx(i) \} + \sum_{i=X+1}^8 \{ 1 \neq Fx(i) \} + 1 \right)$$

前記結合インピーダンスによって発生する信号クロストークによる電圧変化をキャンセルさせることができになる。

## 【0023】

前記のように、各単相処理回路10-Xにおいて、各重み付け処理回路X-1~8の出力は加算回路22で加算され、その加算結果が加算回路23によって遅延回路21で遅延せしめられている画像信号Ev[X]に加算される。そして、その加算後の信号Evc[X]に予め画像信号入力線L[X]に係る系統と他の各画像信号入力線との間に生じるクロストークをキャンセルする信号が含まれていることは前記のとおりであり、D/A変換回路66'のD/A変換器66'-Xでアナログ信号Svc[X]に変換されて液晶表示パネル51'の画像信号入力線L[X]の系統に供給されると、クロストークによる画質の劣化がない画像表示が実現できる。

## 【0024】

尚、この実施形態では各単相処理回路10-Xをハードウェアで構成した場合について説明したが、各重み付け処理回路X-1~8と遅延回路21と加算回路22と加算回路23の機能をソフトウェア処理によって実行させるようにしてもよい。

10

20

30

40

## 【産業上の利用可能性】

## 【0025】

本発明は、多相化された画像信号を用いて表示動作を行う液晶表示装置に適用できる。

## 【図面の簡単な説明】

## 【0026】

【図1】本発明の実施形態に係る液晶表示装置（多相化数：8）の構成図である。

【図2】信号補正回路とD/A変換回路のブロック図である。

【図3】液晶表示パネルにおける各画像信号入力線の直列インピーダンスと画像信号入力線L[4]に係る系統と他の各画像信号入力線に係る系統との間に介在する結合インピーダンスを示す図である。

【図4】従来の液晶表示装置（多相化数：4）の構成図である。

## 【符号の説明】

## 【0027】

1-1~8...重み付け処理回路、10...信号補正回路、10-1~8...単相処理回路、21...遅延回路、22, 23...加算回路、51, 51'...液晶表示パネル、52, 52'...列信号電極駆動回路、53, 53'...シフトレジスタ回路、54, 54'...行走査電極駆動回路、61, 61'...外部駆動回路、62, 62'...タイミング発生回路、63, 63'...駆動パルス生成回路、64, 64'...相展開回路、65, 65'...極性反転回路、66, 66'...D/A変換回路、B(1)~B(n/4), B(j), B(n/8)...出力線、Cs...容量、D, D1~Dn...列信号電極、G, G1~Gm...行走査電極、HST...水平スタート信号、HCK1, HCK2...水平シフトクロック信号、L1~L4...画像信号入力線、LCM...液晶表示体、PIX...表示画素、Tr...スイッチングトランジスタ、VST...垂直スタート信号、VCK1, VCK2...垂直シフトクロック信号、VCOM, VCC...共通直流電圧。

〔 図 1 〕

【 図 2 】

〔 図 3 〕

〔 図 4 〕

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 02 F 1/133 550

|                |                                                                                                                                                                                                                                                                         |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2007025277A</a>                                                                                                                                                                                                                                           | 公开(公告)日 | 2007-02-01 |

| 申请号            | JP2005207503                                                                                                                                                                                                                                                            | 申请日     | 2005-07-15 |

| [标]申请(专利权)人(译) | 日本胜利株式会社                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 日本有限公司Victor公司                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 内山 裕治                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 内山 裕治                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G09G3/36 G09G3/20.611.D G09G3/20.623.V G09G3/20.623.J G09G3/20.623.R G02F1/133.550                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NC13 2H093/NC16 2H093/NC22 2H093/NC24 2H093/NC25 2H093/NC26 2H093/NC34 2H093/NC35 2H093/ND06 2H093/ND15 5C006/AC21 5C006/BB16 5C006/BC16 5C006/BC23 5C006/FA31 5C006/FA36 5C006/FA37 5C080/AA10 5C080/BB05 5C080/DD01 5C080/DD10 5C080/JJ02 2H193/ZA04 |         |            |

| 代理人(译)         | 永井 利和                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                               |         |            |

### 摘要(译)

要解决的问题：通过抑制由使用多相图像信号的液晶显示面板中的每相的串联布线之间的耦合阻抗引起的信号串扰来抑制高质量图像显示。多相图像信号Ev [1]至Ev [8]在每个单相处理电路10-1至8中进行处理，D / A转换，然后转移至液晶显示板并输出。每个单相处理电路10-X：(X = 1到8)包括用于延迟和输出输入图像信号Ev [X]的延迟电路21，用于延迟输入图像信号Ev [X]的延迟电路21加权处理电路X-1至X-8，用于输出加权信号，用于消除由于各自的耦合阻抗引起的串扰量，加法电路22，用于相加加权信号，以及加法电路23，用于将加法电路22的图像信号输出和加法信号相加。.The