(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-202215

(P2005-202215A)

(43) 公開日 平成17年7月28日(2005.7.28)

(51) Int.Cl.<sup>7</sup>**G09G 3/36****G02F 1/133****G09G 3/20**

F 1

G09G 3/36

G02F 1/133 550

G09G 3/20 611A

G09G 3/20 624B

G09G 3/20 641A

テーマコード(参考)

2H093

5C006

5C080

審査請求 未請求 請求項の数 2 O L (全 8 頁)

(21) 出願番号

特願2004-9259(P2004-9259)

(22) 出願日

平成16年1月16日(2004.1.16)

(71) 出願人 000166948

ミヨタ株式会社

長野県北佐久郡御代田町大字御代田410

7番地5

(72) 発明者 金井 智良

長野県北佐久郡御代田町大字御代田410

7番地5 ミヨタ株式会社内

F ターム(参考) 2H093 NA16 NA51 NC09 NC11 NC24

NC26 NC34 ND39

5C006 AA15 AF21 BB16 BC03 BC06

BC12 BC20 BF04 BF24 BF26

BF34 BF37 FA47

5C080 AA10 BB05 DD26 FF11 GG12

JJ03 JJ04

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】 消費電力が少ない液晶表示装置を提供する。

【解決手段】 液晶表示画素に、少なくとも、液晶表示電極と、該液晶表示電極を駆動するための処理回路と、画像データを記憶する複数個のゲート容量とを形成した液晶表示装置とし、前記ゲート容量にNビット(Nは正の整数)のデジタル値を保持し、該デジタル値を時間信号に変換してから液晶表示電極を駆動する液晶表示装置とする。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

液晶表示画素に、少なくとも、液晶表示電極と、該液晶表示電極を駆動するための処理回路と、画像データを記憶する複数個のゲート容量とを形成したことを特徴とする液晶表示装置。

**【請求項 2】**

前記ゲート容量にNビット（Nは正の整数）のデジタル値を保持し、該デジタル値を時間信号に変換してから前記液晶表示電極を駆動することを特徴とする液晶表示装置。

**【発明の詳細な説明】****【技術分野】**

10

**【0001】**

本発明は液晶表示装置に関するものである。

**【背景技術】****【0002】**

現在、液晶表示装置としてTN（ツイステッド・ネマティック）液晶を使用したTFT液晶装置が数多く生産されている。テレビやノートパソコンをはじめ多くの電気製品の表示部として使用されている。ビデオカメラやデジタルスチルカメラなどの携帯製品においては、電池容量の関係で消費電力の低減が要求されていて、液晶表示装置に対しても低消費電力化が要求されている。

**【0003】**

20

液晶表示装置は、液晶表示部の他に、画像処理装置を実装している。ここで、表示システムは、中央処理装置（以下CPU、Central Processing Unit）において行なわれた演算処理結果を受取り、液晶表示部に映像を表示するまでの処理を行う機能を有するシステムのことである。また、画像処理装置とは、表示システムにおいて、CPUにおいて行なわれた演算結果を受け取り、液晶表示部に送る画像データを形成する装置のことである。液晶表示部とは、複数の液晶表示画素から構成され映像が表示される領域のことである。画像処理装置は、大量の画像データを高速に表示するために、画像処理専用の演算処理装置（以下GPU、Graphic Processing Unit）や、画像データを保存するための記憶装置であるVRAM（Video Random Access Memory）、表示処理装置などから構成されていることが多い。これらの装置を駆動するために電力が消費される。

**【0004】**

TFT液晶表示装置は階調に対応したアナログ電圧を液晶表示電極に印加することで階調表示を行っているのが一般的である。フレームメモリから読み出されたデジタルのビデオ信号をアナログ電圧に変換するにはDA変換器が必要であり、そこで消費される電力は他の回路に比べて多い。格子状に配列された液晶表示画素の場合、通常は列の数と同じDA変換器を設けているので、解像度を上げるとDA変換機の数が増え、そこで消費電力が問題になっている。

**【0005】**

30

そこで、例えば、前記GPUで行われていた演算処理の一部を液晶表示画素内部で分担し、VRAMを不要とすることで消費電力を低減するための技術が開発されている。具体的には、液晶表示画素に形成する液晶駆動回路の中にデジタル映像信号を保持する回路を設けて、フレームメモリを使用しないようにすることで表示システム全体での消費電力の低減を図っている。（例えば特許文献1参照）

**【0006】**

40

**【特許文献1】特開2003-167558号公報****【発明の開示】****【発明が解決しようとする課題】****【0007】**

液晶表示画素に形成する液晶駆動回路の中にデジタル映像信号を保持する回路を設けて

50

、フレームメモリを使用しないようにすることで表示システム全体での消費電力の低減を図っているが、液晶表示画素と同じ数だけある液晶駆動回路にそれぞれD A変換器が必要になり、その部分での消費電力が増えてしまう。

本発明は消費電力の大きいD A変換器の使用をやめ、消費電力が少ない液晶表示装置を提供することを目的としている。

**【課題を解決するための手段】**

**【0008】**

液晶表示画素に、少なくとも、液晶表示電極と、該液晶表示電極を駆動するための処理回路と、画像データを記憶する複数個のゲート容量とを形成した液晶表示装置とする。

**【0009】**

前記ゲート容量にNビット（Nは正の整数）のデジタル値を保持し、該デジタル値を時間信号に変換してから液晶表示電極を駆動する液晶表示装置とする。

消費電力が多いD A変換器を使用しないで、C-MOSロジック回路で液晶駆動信号を作成する。

**【発明の効果】**

**【0010】**

液晶表示画素に画像データを記憶する複数個のゲート容量を形成したので、画像記憶回路が不要にできた。また、スタティックRAMにデータを記憶させるより面積も小さくすることができた。ゲート容量にデータを記憶した場合は、ダイナミックRAMと同じようにリフレッシュを行わないと、記憶したデータが失われてしまう。しかし、本発明の場合はダイナミックRAMと違って、データの読み出し動作を行わないので、小さなゲート容量で、次のフィールドの映像信号データを記憶するまでの期間、前の記憶内容を保持することができた。

**【0011】**

液晶表示電極を駆動する信号を、D A変換器を使用しないで作成できるので、消費電力が少ない液晶表示装置ができた。

**【発明を実施するための最良の形態】**

**【0012】**

液晶表示画素に、少なくとも、液晶表示電極と、該液晶表示電極を駆動するための処理回路と、画像データを記憶する複数個のゲート容量とを形成した液晶表示装置とし、前記ゲート容量にNビット（Nは正の整数）のデジタル値を保持し、該デジタル値を時間信号に変換してから液晶表示電極を駆動する液晶表示装置とする。

C-MOSロジック回路のコンパレータによりPWM（パルス幅変調）したハイとローの信号で液晶を駆動する。

**【実施例1】**

**【0013】**

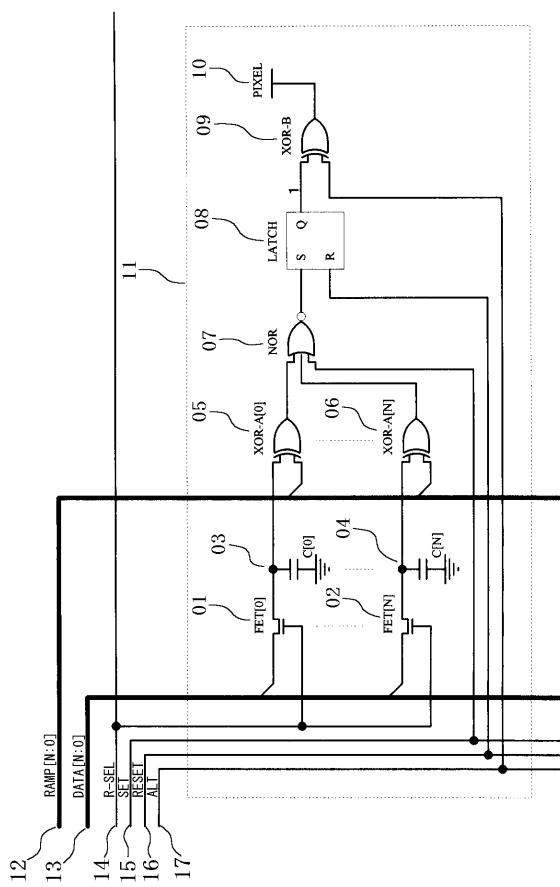

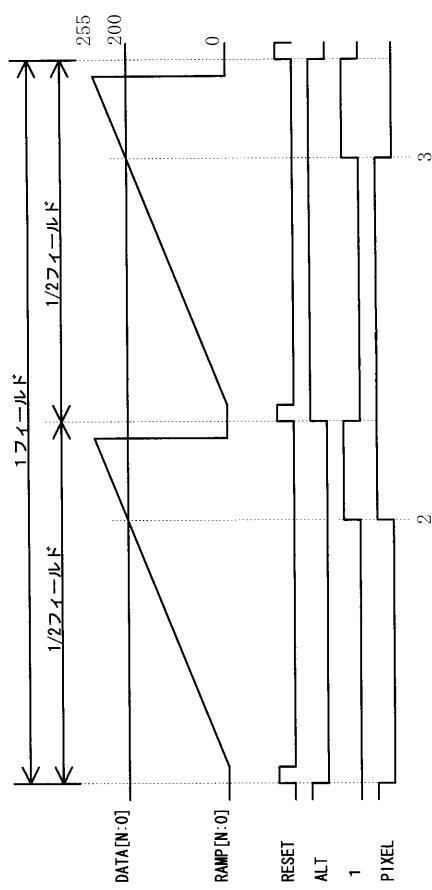

図1は本発明の液晶表示装置に形成した液晶表示電極を駆動するための回路図である。点線11に囲まれた部分が液晶表示画素1つに形成した駆動回路である。図2は液晶表示画素を1フィールド分駆動する回路の動作を示す信号波形図であり、映像信号DATA[N:0]13が8ビットで、値が10進数で200の場合を示している。

**【0014】**

図1において、01は0ビット目のFET[0]であり、02はNビット目のFET[N]である。図では省略されているが、0~NのN+1個のFETが形成されている。03は0ビット目のゲート容量C[0]であり、04はNビット目のゲート容量C[N]であり、前記各FETに対応して形成されている。05は0ビット目のエクスクルーシブOR回路XOR-A[0]であり、06はNビット目のエクスクルーシブOR回路XOR-A[N]であり、これも前記各FETに対応して形成されている。07はNOR回路NOR、08はラッチ回路LATCH、09はエクスクルーシブOR回路XOR-B、10は液晶表示電極PIXEL、11は液晶表示電極駆動回路、12はランプ信号線RAMP[N:0]、13はデータ線DATA[N:0]、14は液晶表示画素セレクト信号線R-

10

20

30

40

50

S E L、1 5はセット信号線S E T、1 6はリセット信号線R E S E T、1 7は反転信号線A L T、1は：ラッチ回路0 8の出力信号線である。映像信号D A T A [ N : 0 ] 1 3は映像信号の階調により任意のビット数にすることができる。例えば、2 5 6階調の場合ビット数は8でNは7になる。同様にランプ信号R A M P [ N : 0 ] 1 2、F E T [ N ] 0 2、ゲート容量C [ N ] 0 4、X O R - A [ N ] 0 6のNも7になる。

#### 【0 0 1 5】

各F E TのゲートはR - S E L 1 4、ドレインはD A T A [ N : 0 ] 1 3、ソースはそれぞれ対応するX O R - A及びゲート容量Cに接続されている。N O R 7には前記X O R - Aの出力とセット信号が入力される。N O R 7の出力はL A T C H 0 8の入力Sに接続され、L A T C H 0 8の入力RにはR E S E T 1 6が接続されている。X O R - B 0 9の入力にはL A T C H 0 8の出力とA L T 1 7が接続されている。X O R - B 0 9の出力はP I X E L 1 0に接続されている。10

#### 【0 0 1 6】

図2は、1フィールド分のD A T A [ N : 0 ]、R A M P [ N : 0 ]、R E S E T、A L T、ラッチ回路0 8の出力信号1、P I X E Lの信号波形を示している。

#### 【0 0 1 7】

図1と図2を使って液晶表示電極駆動回路の動作を説明する。複数ビットのデータの値は10進数で表してしる。D A T A [ N : 0 ] 1 3のデータはR - S E L 1 4によりF E T [ 0 ] 0 1 ~ F E T [ N ] 0 2がオンしている間にX O R - A [ 0 ] 0 5 ~ X O R - A [ N ] 0 6のゲート容量C [ 0 ] 0 3 ~ C [ N ] 0 4に保持されて、F E T [ 0 ] 0 1 ~ F E T [ N ] 0 2がオフの時はハイまたはロウの値を保持している。ゲート容量C [ 0 ] 0 3 ~ C [ N ] 0 4が保持しているデータが2 0 0のときにフィールドの開始からR A M P [ N : 0 ] 1 2を0から2 5 5まで増やしていく、ゲート容量C [ 0 ] 0 3 ~ C [ N ] 0 4に保持されているデータとR A M P [ N : 0 ] 1 2のN + 1ビットの値をX O R - A [ 0 ] 0 5 ~ X O R - A [ N ] 0 6で比較する。20

#### 【0 0 1 8】

S E T 1 5は通常ハイでR A M P [ N : 0 ] 1 2の値が変化してからX O R - A [ 0 ] 0 5 ~ X O R - A [ N ] 0 6の出力が確定した後でロウにして、次にR A M P [ N : 0 ] 1 2が変化する前にハイに戻す。ゲート容量C [ 0 ] 0 3 ~ C [ N ] 0 4に保持されているデータとR A M P [ N : 0 ] 1 2の値が等しくないときはX O R - A [ 0 ] 0 5 ~ X O R - A [ N ] 0 6の1つ以上の出力がハイになり、S E T 1 5の値に関わらずN O R 0 7の出力はロウのままである。等しいときはX O R - A [ 0 ] 0 5 ~ X O R - A [ N ] 0 6の全ての出力がロウになるので、S E T 1 5がロウになったタイミングでN O R 0 7の出力はハイになる。30

#### 【0 0 1 9】

図2のR E S E T波形で示すように1 / 2フィールドの開始でR E S E T 1 6をハイにしてL A T C H 0 8の出力QをロウしてからR E S E T 1 6をハイに戻す。N O R 0 7の出力がハイになるとL A T C H 0 8の入力Sもハイになって、出力Qは次の1 / 2フィールドの開始までハイを保持する。図2の2と3の部分はD A T A [ N : 0 ] 1 3とR A M P [ N : 0 ] 1 2の値が等しくなったときにL A T C H 0 8の出力Qの1の部分がロウからハイに変化する状態を示していて、1 / 2フィールド毎に同じ動作を繰り返す。この部分がP W M（パルス幅変調）の結果を表している。D A T A [ N : 0 ] 1 3が8ビットで値が2 0 0の場合はデジタル値の比は2 0 0 / 2 5 6になる。図2の1の波形は後半の1 / 2フィールドの開始でロウになり、3の部分でハイになってから1 / 2フィールドの終わりでロウになる。図2の1 / 2フィールドの時間は2 5 6とした場合、1の波形がロウの時間と1 / 2フィールドの時間の比も2 0 0 / 2 5 6になり、デジタル値がパルスの幅（時間）に変換された様子が分かる。40

#### 【0 0 2 0】

L A T C H 0 8の出力1は図2の1の波形で示すようにハイとロウの時間が同じにはならないが、A L T 1 7を1 / 2フィールド毎にハイとロウにすることでX O R - B 0 9の50

出力PIXEL10は、図2のPIXEL波形のように1フィールド間のハイとロウの時間が等しくなる。PIXEL10は液晶の片側の電極で、もう一方の電極をPIXEL10のハイとロウの電圧の中間にすることでDCバランスが保たれる。図1のXOR-A[0]05からNビット目のXOR-A[N]06、NOR07、LATC08、XOR-B09はC-MOSロジック回路で形成されているため、消費電力は極めて少ない。

#### 【実施例2】

##### 【0021】

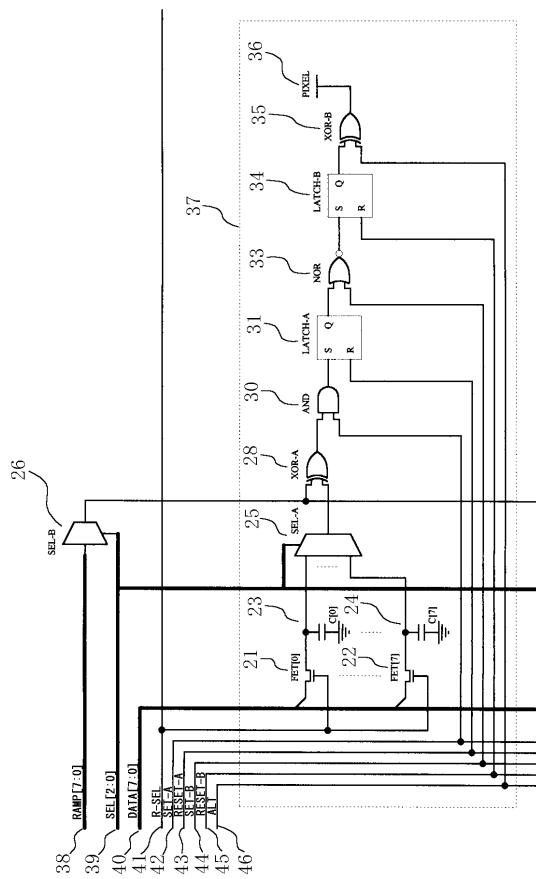

図3は本発明の液晶表示装置に形成した液晶表示電極を駆動するための第2実施例の回路図である。第1実施例である図1の回路がN+1ビット同時に比較を行ったのに対して1ビットずつ比較する回路で、点線37に囲まれた部分が液晶表示画素1つに対応する駆動回路である。映像データがビット0からビット7までの8ビットの場合の動作を説明する。

##### 【0022】

図3において、21は0ビット目のFETでFET[0]、22は7ビット目のFETでFET[7]である。図では省略されているが、0~NのN+1個のFETが形成されている。23は0ビット目のゲート容量C[0]で、24は7ビット目のゲート容量C[7]であり、前記各FETに対応して形成されている。25はデータセレクタ回路SEL-A、26はデータセレクタ回路SEL-Bである。28はエクスクルーシブOR回路XOR-A、30はAND回路AND、31はラッチ回路LATC-A、33はNOR回路NOR、34はラッチ回路LATC-B、35はエクスクルーシブOR回路XOR-B、36は液晶表示電極PIXEL、37は液晶表示電極駆動回路、38はRAMP信号線RAMP[7:0]、39はデータセレクト信号線SEL[2:0]、40はデータ線DATA[7:0]、41は液晶表示画素セレクト信号線R-SEL、42はセット信号線SET-A、43はリセット信号線RESET-A、44はセット信号線SET-B、45はリセット信号線RESET-B、46は反転信号線ALTである。

##### 【0023】

各FETのゲートはR-SEL42、ドレインはDATA[7:0]40、ソースはそれに対応するゲート容量C及びSEL-A25に接続されている。XOR-A28にはSEL-A25とSEL-B26の出力入力される。AND30にはXOR28の出力とSET-A41が接続され、出力はLATC-A31の入力Sに接続されている。LATC-A31の入力RにRESET-A43が接続されている。NOR33にはLATC-H-B34の出力とSET-B44が接続されている。NOR33の出力はLATC-H-B34の入力Sに接続され、LATC-B34の入力RにはRESET-B45が接続されている。LATC-B34の出力とALT46はXOR-Bに接続されており、XOR-B35の出力はPIXEL36に接続されている。SEL[2:0]はデータセレクタ回路25、26に接続されている。

##### 【0024】

映像信号DATA[7:0]40のデータはR-SEL41によりFET[0]21~FET[7]22がオンしている間にSEL-A25のゲート容量C[0]23~C[7]24に蓄積されて、FET[0]21~FET[7]22がオフの時はハイまたはロウの値を保持している。1/2フィールドの開始からRAMP[7:0]38を0から255まで増やしていく、RAMP[7:0]38の値が変化した後でゲート容量C[0]23~C[7]24とRAMP[7:0]38の対応する1ビットのデータをSEL[2:0]39の信号によりSEL-A25とSEL-B26でそれぞれ選択してXOR-A28で比較する。

##### 【0025】

ビット0を比較する前にRESET-A43をハイにしてLATC-A31の出力Qにロウを保持させてからRESET-A43をロウに戻す。各ビットでXOR-A28の出力が確定した後でAND30の入力SET-A42をハイにするとXOR-A28の出力と同じ値がLATC-A31の入力Sに入り、その後SET-A42をロウに戻す。

この動作を DATA [ 7 : 0 ] 40 と RAMP [ 7 : 0 ] 38 の値を固定した状態でビット 0 からビット 7 まで 8 回繰り返す。

#### 【0026】

XOR - A 28 の比較結果が一致しないビットがあると LATCH - A 31 の入力 S がハイになり出力 Q は RESET - A 43 がハイになるまでハイを保持する。全てのビットが一致した場合は LATCH - A 31 の出力 Q はロウのままである。8 ビットの比較が終了したとき NOR 33 の入力 SET - B 44 をロウにすると LATCH - B 34 の入力 S に LATCH - A 31 の出力 Q の反転信号が入力される。その後 SET - B 44 をハイに戻す。1 / 2 フィールドの開始毎に RESET B 45 をハイにして LATCH - B 34 の出力 Q にロウを保持させてから RESET B 45 をロウにしておく。全てのビットが一致した場合は LATCH - B 34 の入力 S にハイが入力されるので、LATCH - B 34 の出力 Q は次の 1 / 2 フィールドの開始までハイを保持する。10

#### 【0027】

DATA [ 7 : 0 ] 40 の値が 200 の場合を例にとると、図 2 の 2 と 3 の位置で RAMP [ 7 : 0 ] 38 の値と等しくなり、XOR - A 28 の出力は 8 回の比較で全てロウになる。LATCH - A 31 の入力 S にはロウが入力され続けるので出力 Q はロウのままである。その後 SET - B 44 をロウにすると LATCH - B 34 の入力 S にハイが入力されて、出力 Q は次の 1 / 2 フィールドの開始までハイを保持し続け図 2 の 1 の波形になる。20

LATCH - B 34 の出力 Q は図 2 の 1 の波形で示すようにハイとロウの時間が同じにはならないが、ALT 46 を 1 / 2 フィールド毎にハイとロウにすることで XOR - B 35 の出力 PIXEL 36 は、図 2 の PIXEL 波形のように 1 フィールド間のハイとロウの時間が等しくなる。PIXEL 36 は液晶の片側の電極で、もう一方の電極を PIXEL 36 のハイとロウの電圧の中間にすることで DC バランスが保たれる。図 3 の SEL - A 25, SEL - B 26, XOR - A 28, AND 30, LATCH - A 31, NOR 33, LATCH - B 34, XOR - B 35 は CMOS ロジック回路で形成されているため、消費電力は極めて少ない。20

#### 【0028】

本発明はデジタル映像信号を PWM ( パルス幅変調 ) してパルスの幅により液晶をオン・オフさせて階調を表しているので、FLC ( 強誘電性液晶 ) のように応答速度が速い液晶を使った液晶表示装置に特に適している。30

#### 【図面の簡単な説明】

#### 【0029】

【図 1】本発明の液晶表示装置に形成した液晶表示電極を駆動するための回路

【図 2】液晶表示画素 11 を 1 フィールド分駆動する回路の動作を示す信号波形図

【図 3】本発明の液晶表示装置に形成した液晶表示電極を駆動するための第 2 実施例の回路図

#### 【符号の説明】

#### 【0030】

|     |               |                         |    |

|-----|---------------|-------------------------|----|

| 0 1 | FET [ 0 ]     | : 0 ビット目の FET           | 40 |

| 0 2 | FET [ N ]     | : N ビット目の FET           |    |

| 0 3 | C [ 0 ]       | : 0 ビット目のゲート容量          |    |

| 0 4 | C [ N ]       | : N ビット目のゲート容量          |    |

| 0 5 | XOR - A [ 0 ] | : 0 ビット目のエクスクルーシブ OR 回路 |    |

| 0 6 | XOR - A [ N ] | : N ビット目のエクスクルーシブ OR 回路 |    |

| 0 7 | NOR           | : NOR 回路                |    |

| 0 8 | LATCH         | : ラッチ回路                 |    |

| 0 9 | XOR - B       | : エクスクルーシブ OR 回路        |    |

| 1 0 | PIXEL         | : 液晶表示電極                |    |

| 1 1 |               | : 液晶表示電極駆動回路            |    |

50

|     |                   |                    |    |

|-----|-------------------|--------------------|----|

| 1 2 | R A M P [ N : 0 ] | : R A M P 信号線      |    |

| 1 3 | D A T A [ N : 0 ] | : データ線             |    |

| 1 4 | R - S E L         | : 液晶表示画素セレクト信号線    |    |

| 1 5 | S E T             | : セット信号線           |    |

| 1 6 | R E S E T         | : リセット信号線          |    |

| 1 7 | A L T             | : 反転信号線            |    |

| 1   |                   | : ラッチ回路 0 8 の出力信号線 |    |

| 2 1 | F E T [ 0 ]       | : 0 ビット目の F E T    |    |

| 2 2 | F E T [ 7 ]       | : 7 ビット目の F E T    |    |

| 2 3 | C [ 0 ]           | : 0 ビット目のゲート容量     | 10 |

| 2 4 | C [ 7 ]           | : 7 ビット目のゲート容量     |    |

| 2 5 | S E L - A         | : データセレクタ回路        |    |

| 2 6 | S E L - B         | : データセレクタ回路        |    |

| 2 8 | X O R - A         | : エクスクルーシブ O R 回路  |    |

| 3 0 | A N D             | : A N D 回路         |    |

| 3 1 | L A T C H - A     | : ラッチ回路            |    |

| 3 3 | N O R             | : N O R 回路         |    |

| 3 4 | L A T C H - B     | : ラッチ回路            |    |

| 3 5 | X O R - B         | : エクスクルーシブ O R 回路  |    |

| 3 6 | P I X E L         | : 液晶表示電極           | 20 |

| 3 7 |                   | : 液晶表示電極駆動回路       |    |

| 3 8 | R A M P [ 7 : 0 ] | : R A M P 信号線      |    |

| 3 9 | S E L [ 2 : 0 ]   | : データセレクト信号線       |    |

| 4 0 | D A T A [ 7 : 0 ] | : データ線             |    |

| 4 1 | R - S E L         | : 液晶表示画素セレクト信号線    |    |

| 4 2 | S E T - A         | : セット信号線           |    |

| 4 3 | R E S E T - A     | : リセット信号線          |    |

| 4 4 | S E T - B         | : セット信号線           |    |

| 4 5 | R E S E T - B     | : リセット信号線          |    |

| 4 6 | A L T             | : 反転信号線            | 30 |

【図1】

【図2】

【図3】

|                |                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2005202215A</a>                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2005-07-28 |

| 申请号            | JP2004009259                                                                                                                                                                                                                                                                                                                              | 申请日     | 2004-01-16 |

| [标]申请(专利权)人(译) | 西铁城控股株式会社                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | ミヨタ株式会社                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 金井智良                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 金井 智良                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.611.A G09G3/20.624.B G09G3/20.641.A                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA51 2H093/NC09 2H093/NC11 2H093/NC24 2H093/NC26 2H093/NC34 2H093/ND39 5C006/AA15 5C006/AF21 5C006/BB16 5C006/BC03 5C006/BC06 5C006/BC12 5C006/BC20 5C006/BF04 5C006/BF24 5C006/BF26 5C006/BF34 5C006/BF37 5C006/FA47 5C080/AA10 5C080/BB05 5C080/DD26 5C080/FF11 5C080/GG12 5C080/JJ03 5C080/JJ04 2H193/ZA04 2H193/ZD21 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                 |         |            |

### 摘要(译)

提供了一种具有低功耗的液晶显示装置。 提供一种液晶显示装置，其中在液晶显示像素中至少形成有液晶显示电极，用于驱动液晶显示电极的处理电路以及用于存储图像数据的多个栅极电容器。 提供一种液晶显示装置，其在电容器中保持N位 ( N 为正整数 ) 数字值，并将该数字值转换为时间信号，然后驱动液晶显示电极。 [选型图]图1